#### RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL ' DE LA PROPRIÉTÉ INDUSTRIELLE

(1) N° de publication : (A n'utiliser que pour les

commandes de reproduction).

2 482 368

PARIS

Α1

# DEMANDE DE BREVET D'INVENTION

21)

73)

Titulaire: Idem (71)

N° 80 10566

| (54)            | Opérateur logique à injection par le substrat et son procédé de fabrication.   |

|-----------------|--------------------------------------------------------------------------------|

| <b>61</b>       | Classification internationale (Int. Cl. 3). H 01 L 27/06, 21/72; H 03 K 19/08. |

| 22<br>) 32 (31) | Date de dépôt                                                                  |

|                 |                                                                                |

| 41)             | Date de la mise à la disposition du  • public de la demande                    |

| 71)             | Déposant : Société dite : THOMSON-CSF, société anonyme, résidant en France.    |

|                 |                                                                                |

| (72)            | Invention do . Maurica Donov                                                   |

La présente invention concerne une structure d'opérateur logique à injection par le substrat de type SFL et son procédé de fabrication et plus particulièrement une telle structure et un tel procédé de fabrication qui soient compatibles avec la formation sur une même plaquette de circuits intégrés de composants de type bipolaire classiques.

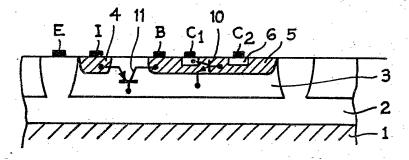

La figure l représente de façon très schématilogique de type I<sup>2</sup>L (abréque une structure d'opérateur 10 viation provenant des termes anglo-saxons Integrated Injection Logic ou logique intégrée à injection). Comme cela est bien connu, cette structure est de façon générale formée sur un substrat 1 de type P surmonté d'une couche enterrée 2 de type N et d'une couche épitaxiée 3 également 15 de type N mais à niveau de dopage plus faible. Dans la couche épitaxiée 3, sont formées au moins deux zones distinctes 4 et 5 de type P. A l'intérieur de la zone 5 de type P sont formées plusieurs zones 6 de type N. Une métallisation d'injecteur I est solidaire de la zone 4, une 20 métallisation de base B et solidaire de la zone 5 et des métallisations de collecteur C1, C2... sont solidaires des zones 6. Une métallisation d'émetteur E est solidaire de la couche 3 de type N ou, comme cela est représenté, de zones à fort niveau de dopage de type N rejoignant la 25 couche enterrée 2. Comme cela est connu, cette structure est équivalente à l'association d'un premier transistor logique NPN 10 et d'un second transistor injecteur 11. La figure 1 indique quelles couches constituent l'émetteur, la base et le collecteur de chacun de ces transis-30 tors 10 et 11.

Parmi les nombreux avantages de la technologie I<sup>2</sup>L, on s'interessera plus particulièrement ici au fait que cette technologie est compatible avec la technologie classique de constitution de transistors bipolaires. On peut ainsi élaborer sur un même substrat 1 de type P, revêtu de couches enterrées localisées ou non 2 à haut

niveau de dopage et d'une couche épitaxiée 3 à niveau de dopage plus faible, dans des emplacements distincts d'une même plaquette de circuit intégré, des transistors bipolaires classiques et des circuits logiques de techno- logie 1<sup>2</sup>L.

La figure 2 représente une variante de circuit logique de type I'L selon laquelle l'injection se fait par le substrat. Cette technologie couramment désignée dans la technique par le sigle SFL (d'après les termes 10 anglo-saxons Substrate Fed Logic ou logique alimentée par le substrat). Dans la figure 2, on a utilisé autant que faire se pouvait les mêmes références qu'en figure 1 pour désigner des couches identiques ou correspondantes. La différence principale entre les figures 1 et 2 est 15 que le transistor injecteur 11 est vertical au lieu d'être latéral. Son émetteur au lieu d'être constitué d'une couche 4 formée à partir de la surface dans la couche épitaxiée 3 de type N est maintenant constitué par le substrat 1 de type P. Cette technologie SFL présente par rapport 20 à la technologie I<sup>2</sup>L classique, l'avantage d'une plus grande miniaturisation puisque l'on supprime sur la surface du substrat la zone 4 ainsi que la zone de type N séparant cette zone 4 de la zone 5.

Néanmoins, cette technologie SFL n'a pas donné

25 lieu à de nombreuses applications pratiques étant donné

ses grandes difficultés technologiques de réalisation.

On notera en effet que, si l'on considère la zone de

type N séparant le substrat l de type P de la couche 5

de type P, cette zone doit à la fois présenter un niveau

30 de dopage relativement élevé au voisinage du substrat

et un niveau de dopage relativement faible au voisinage

de l'inter-face avec la couche 5. D'autre part, la couche

l de type P à l'interface avec la couche de type N (2,3)

doit présenter un niveau de dopage élevé. Ceci a conduit

35 dans la pratique antérieure à utiliser des substrats de

type P fortement dopé (plus de 5 x 10<sup>18</sup> at/cm<sup>3</sup>). Cette utilisation de substrats de type P à niveau de dopage élevé présente d'une part l'inconvénient de rendre difficile les opérations de dopage de la face avant du substrat en raison des phénomènes parasites d'autodopage liés à des exo-diffusions à partir de la face arrière et d'autre part de rendre la technologie SFL peu compatible avec la technologie de fabrication de transistors bipolaires classiques qui utilise des substrats relativement faiblement dopés (de l'ordre de 10<sup>15</sup> at/cm<sup>3</sup>).

Parmi les diverses tentatives de l'art antérieur pour réaliser des structures du type de celle illustrée en figure 2, on peut citer celles qui consistaient à former la couche 2 à partir d'une couche enterrée dans un 15 substrat de type P+, puis à former des couches 3 de type N et 5 de type P par épitaxies successives. Une autre tentative a consisté à former les couches de type N 2 et 3 par épitaxies successives, puis à former la couche de type P5 par diffusion localisée . Ces procédés se sont 20 révélés fort complexes sans fournir pour autant de résultats satisfaisants ni assurer une compatibilité avec les technologies bipolaires classiques et ce, essentiellement du fait qu'il n'est pas possible de réaliser industriellement dans l'état actuel de la technique courante des 25 couches épitaxiées localisées et limitées aux emplacements d'une pastille de circuit intégré comportant des circuits logiques de technologie SFL.

Ainsi, un objet de la présente invention est de prévoir un nouveau procédé de fabrication d'opéra-30 teurlogique à injection par le substrat (SFL).

Un autre objet de la présente invention est de prévoir un tel procédé de fabrication compatible avec la fabrication simultanée de composants bipolaires isolés par jonction disposés sur la même pastille de cir-35 cuit intégré.

Un autre objet de la présente invention est de prévoir une nouvelle structure d'opérateur logique de type SFL obtenu par les procédés visés ci-dessus. Pour atteindre ces objets ainsi que d'autres, la présente invention prévoit une nouvelle structure d'opérateur logique à injection par le substrat (SFL) élaborée à partir d'un substrat de type P faiblement dopé, comprenant successivement, à partir du substrat, et sous les zones correspondant à chaque collecteur du transistor NPN de l'opérateur : une première couche de type P à forte concentration résultant d'une implantation de bore dans le substrat ; une deuxième couche de type N à forte concentration résultant d'une implantation de phosphore dans la première implantation ; une troisième couche de type N à faible concentration résultant d'une épitaxié ; une quatrième couche de type P à concentration moyenne résultant d'une diffusion de bore dans la couche épitaxiée ; et une cinquième couche de type N à forte concentration résultant d'une diffusion.

10

15

20

25

30

35

Le procédé de fabrication de la structure ci-dessus résulte de l'exposé de ses caractéristiques. Un avantage de ce procédé est qu'il permet de réaliser simultanément pour une même plaquette des transistors de type bipolaire. Pour ce faire, on prévoit les couches implantées successives de bore et de phosphore seulement aux emplacements où l'on compte implanter une structure logique de type SFL. Et, dans les emplacements où l'on compte disposer des structures de type bipolaires classiques, on forme une couche enterrée de type N par implantation ou diffusion d'antimoine, une surimplantation localisée de phosphore étant réalisée à l'intérieur de cette implantation d'antimoine aux emplacements où l'on souhaite voir remonter davantage la couche enterrée pour qu'elle rejoigne des diffusions

faites à partir de la surface du dispositif permettant d'assurer une liaison à relativement bonne conductivité avec la couche enterrée.

On notera que l'un des aspects de la présente invention réside dans le choix de la combinaison des 5 dopants destinés à former des couches successives, ces dopants étant choisis en fonction des densités selon lesquelles on peut les implanter ou les diffuser et de leur vitesse de diffusion relative. En effet, en raison du grand nombre d'étapes thermiques nécessi-10 tées par le procédé selon la présente invention, il importe que l'on n'ait pas implanté de façon profonde un dopant diffusant plus rapidement qu'un autre dopant implanté moins profondément car au cours d'une diffusion longue, le dopant le plus profond viendrait 15 diffuser au-delà du dopant le moins profond créant une zone d'un type de conductivité indésiré (couche fantôme). On pourra réaliser des variantes de la présente invention en modifiant les éléments dopants 20 choisis, mais il conviendra alors de s'assurer que les mêmes relations existent entre les vitesses de diffusion de ces autres dopants.

Ces objets, caractéristiques et avantages ainsi que d'autres de la présente invention seront exposés plus en détail dans la description suivante de modes de réalisation particuliers, faite en relation avec les figures jointes parmi lesquelles :

25

30

la figure 1 représente un exemple de structure classique de type  ${\ I}^2L$  et a déjà été décrite précédemment ;

la figure 2 représente un exemple de structure classique de type SFL et a déjà été décrite précédemment ;

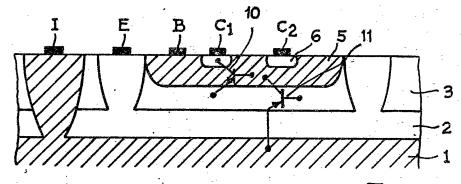

la figure 3 représente un exemple de struc-35 ture SFL selon la présente invention ; les figures 4 à 12 représentent les étapes successives de fabrication conjointes d'une structure SFL et d'une structure bipolaire classique; et

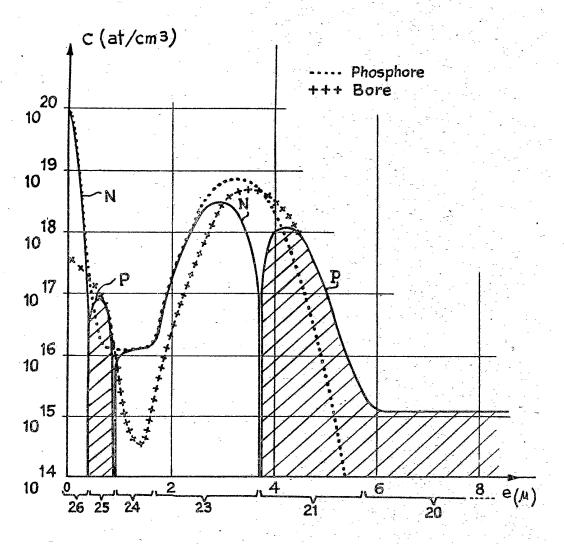

la figure 13 représente des profils de concentration d'impuretés dopantes dans une structure selon la présente invention.

5

10

15

20

25

30

35

Comme cela est d'usage dans le domaine des semiconducteurs, les figures ne sont pas l'échelle et certaines des dimensions ont été dilatées par rapport aux autres pour faciliter la lisibilité et la compréhension.

La figure 3 représente de façon très schématique un opérateur logique à injection par le substrat (SFL) selon la présente invention. Cet opérateur est élaboré sur un substrat 20 de type P à faible niveau de dopage, par exemple compris entre 10<sup>15</sup> et 10<sup>16</sup> at/cm<sup>3</sup>, c'est-à-dire compatible avec l'emploi de technologie bipolaire. Sur ce substrat, se trouve une couche 21 de type P à niveau de dopage plus élevé que celui du substrat résultant de l'exo-diffusion d'une couche initialement implantée dans le substrat. La liaison entre cette couche 21 et la surface du dispositif dont est solidaire une électrode d'injecteur I est assurée par un mur diffusé 22. Au-dessus de la couche 21 se trouve une couche 23 à niveau de dopage élevé de type N (niveau de dopage supérieur à  $10^{18}$  at/cm<sup>3</sup>). Une couche épitaxiée 24 à faible niveau de dopage de type N, par exemple de l'ordre de 1016 at/ cm<sup>3</sup>, recouvre ensuite l'ensemble du dispositif. Dans cette couche épitaxiée 24 sont formées successivement par diffusion une couche de type P 25 à faible niveau de dopage (inférieur à 10<sup>17</sup> at/cm<sup>3</sup>), une couche 26 de type N à niveau de dopage très élevé, par exemple supérieur à 10<sup>20</sup> at/cm<sup>3</sup>. Une électrode E d'émetteur du transistor NPN est disposée au-dessus d'une zone où

5

10

15

20

25

30

35

est effectuée une diffusion profonde fortement dopée de type N 27 rejoignant la couche enterrée 23. Des métallisations de base sont formées au-dessus de régions 28 à diffusion profonde de type P. Ces diffusions profondes sont indiquées comme pénétrant partiellement dans la couche enterrée 23. En fait, leur rôle essentiel est d'assurer la conduction entre l'électrode de base et la couche 25. Leur excès de profondeur résulte du fait qu'elles sont élaborées, comme on le verra ci-après, en même temps que les murs 22, ce qui permet d'économiser des étapes de fabrication sans nuire à la qualité du dispositif. Enfin, des électrodes de collecteurs C1, C2 sont formées audessus des zones superficielles 26. La référence 29 désigne une couche isolante, par exemple une couche d'oxyde représentée fort schématiquement.

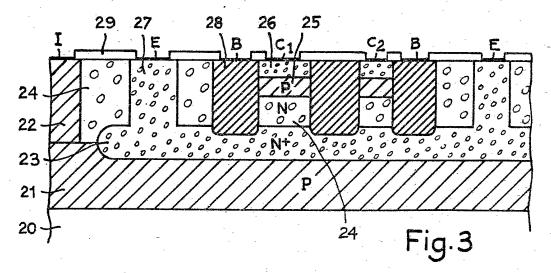

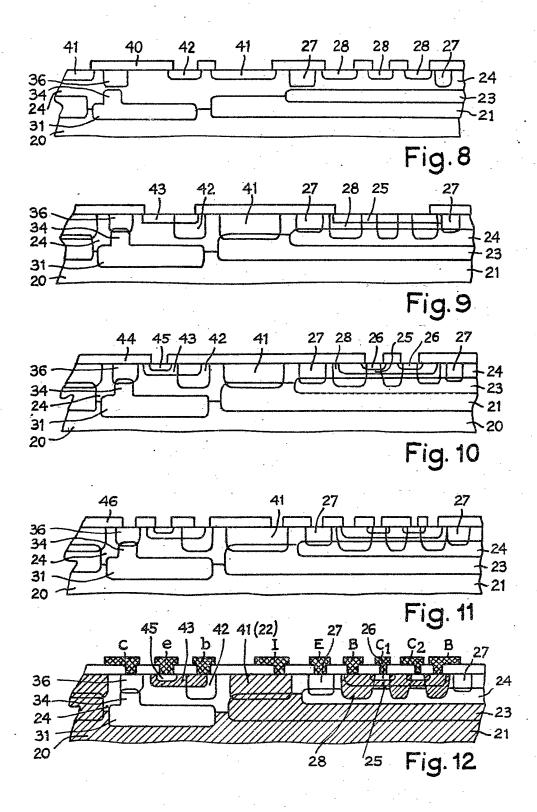

Les figures 4 à 12 représentent de façon schématique des étapes successives de fabrication conjointe sur un substrat de type P d'un transistor selon la technologie bipolaire classique dans la partie gauche des figures sous l'accolade A et d'un opérateur de type SFL dans la partie droite de la figure sous l'accolade B. Les diverses couches et régions seront désignées par de mêmes références dans ces diverses figures alors même qu'elles n'ont pas strictement la même configuration dans ces figures, notamment du fait que leurs dimensions s'accroissent par diffusion au cours des diverses étapes thermiques. En outre, on utilisera autant que faire se peut pour les figures 4 à 12 les mêmes références que celles précédemment utilisées en figure 3.

La figure 4 représente un substrat 20 de type P d'un niveau de dopage de l'ordre de 10<sup>15</sup> at/cm<sup>3</sup>. Ce substrat est recouvert d'une couche de masquage d'oxyde de silicium 30 dans une fenêtre de laquelle

est formée par diffusion d'antimoine (Sb) une région 31 de type N destinée à servir de semelle enterrée pour une structure de type bipolaire linéaire.

Dans l'étape représentée en figure 5, une couche de masquage 32 est disposée au-dessus de la couche 31 de type N et une implantation de bore est réalisée dans le substrat pour fournir une couche 21 de type P à niveau de dopage élevé. Entre ces deux étapes est intercalé un recuit de la couche enterrée 31 d'antimoine par exemple à 1260°C pendant 3 heures en atmosphère d'azote. L'implantation de bore 21 peut par exemple être faite sous l'effet d'une tension de 180 kV et à des doses de l'ordre de 10<sup>15</sup> at/cm<sup>2</sup>.

Dans l'étape de la figure 6, une nouvelle couche de masquage 33 est formée sur le substrat. Ce masque est ouvert au-dessus d'un emplacement limité de la couche 31 et d'un large emplacement de la couche 21 pour y former des couches implantées 34 et 23. Cette implantation peut également avoir lieu sous l'effet d'une tension accélératrice de 180 kV avec une densité de  $2 \times 10^{14}$  à  $10^{15}$  at/cm<sup>2</sup>.

Comme le représente la figure 7, après un recuit des implantations, on procède à la croissance d'une couche épitaxiée 24 à faible niveau de dopage de type N. Cette couche épitaxiée peut par exemple avoir une épaisseur de l'ordre de 3 à 5 microns et une résistivité de l'ordre de 1,5 à 4 ohms/cm. Sur la couche épitaxiée est formé après diverses étapes de recuit, un masque 35 ouvert en des emplacements, tels que représentés sur la figure, au droit desquels on souhaite former des murs de type N<sup>†</sup> rejoignant les couches enterrées profondes 23 et 34 de type N. A ce propos, on notera que l'implantation de phosphore 34 qui présente une vitesse de diffusion plus importante que l'implantation d'antimoine 31 fournit une partie

en saillie vers le haut après les étapes thermiques de diffusion. Dans les fenêtres du masque 35 sont formées par pré-dépôt de phosphore (par exemple à partir de POCl<sub>3</sub>) des régions 36 et 27 de type N<sup>+</sup>, la région 36 se trouvant en regard de la région 34.

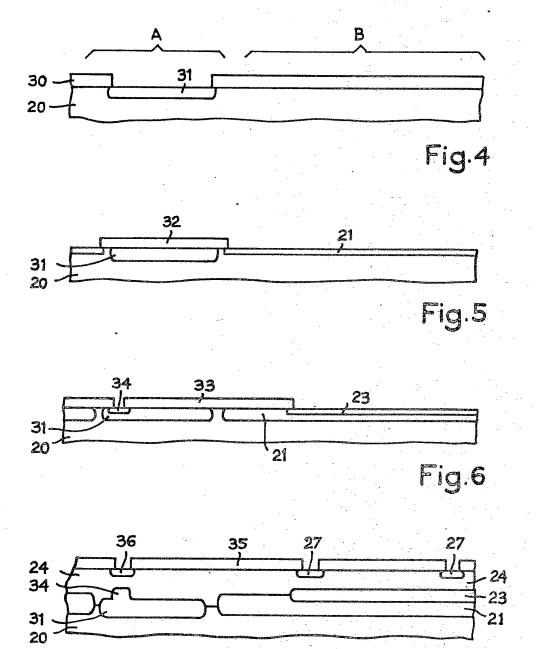

Dans l'étape de la figure 8, un masque 40 est formé sur le substrat, ce masque comprenant des fenêtres dans lesquelles est pré-déposé du bore.

Les zones destinées à former des murs d'isolement rejoignant les fondations enterrées profondes 21 de type P sont désignées par la référence 41; les zones destinées à servir de base pour les transistors bipolaires sont désignées par la référence 42; et les zones destinées à servir de contact de base pour les transistors NPN des opérateurs SFL sont désignées par la référence 28. Au cours des diverses étapes d'échauffement thermique, on notera que les zones 27 et 36 illustrées en figure 7 s'approfondissent et tendent à rejoindre les zones en regard 34 et 23.

Dans l'étape représentée en figure 9, on procède à la formation des zones de base de type P par implantation de bore à relativement faible densité par exemple avec une énergie de 180 keV et une densité de 2 x 10<sup>13</sup> at/cm<sup>2</sup>. Ces zones de base sont désignées par la référence 43 pour les transistors bipolaires linéaires et par la référence 25 pour les transistors NPN des opérateurs SFL.

Dans l'étape illustrée en figure 10, on utilise un masque 44 pour former les zones de type N d'émetteur des transistors bipolaires et les zones de collecteurs des transistors NPN d'opérateurs SFL. Ceci peut être réalisé par pré-dépôt de phosphore à partir de POCl<sub>3</sub> suivi d'une étape de recuit ou encore par diffusion d'arsenic. On obtient ainsi une zone d'émetteur 45 pour les transistors bipolaires normaux

et des zones de collecteurs 26 pour les opérateurs de type SFL.

5

10

La figure 11 représente une étape de formation d'un masque 46 dans lequel sont ouvertes des fenêtres aux emplacements où l'on souhaite déposer des métallisations sur le semiconducteur. Ces métallisations sont illustrées en figure 12. On peut voir les métallisations de collecteur, d'émetteur et de base c, e, b des transistors bipolaires normaux et les métallisations I, E, B,C<sub>1</sub>, C<sub>2</sub> de l'opérateur de type SFL.

Dans la figure 12, comme dans la précédente figure 3, les zones correspondant à des dopages de type P sont représentées hachurées.

15 La figure 13 représente une courbe indiquant en ordonnées une concentration C en at/cm3 (échelle logarithmique) et en abscisse l'épaisseur e en microns de silicium en partant de la surface. Cette figure représente à titre d'exemple non limitatif des profils de dopage au droit des collecteurs C, et C, de la 20 structure SFL, qui peuvent être obtenus par le procédé de fabrication selon la présente invention. On a indiqué en abscisse les couches correspondantes 26, 25, 24, 23, 21 et 20. On notera à ce propos que la notion de couche est relativement arbitraire. En effet, il 25 est difficile de dire par exemple que les zones 24 et 23 forment des couches distinctes étant donné qu'il s'agit d'une zone N à profil de concentration variable. Néanmoins, cette appellation a été maintenue ici étant donné son caractère usuel et simplificateur. 30 Dans la figure 13, les diverses courbes en trait pleinreprésentent les profils de concentration nette correspondant aux diverses zones. Les zones de type P résultantes ont été indiquées par des hachures. La courbe en pointillés indique la concentration en phos-35

phore pour les diverses profondeurs et la courbe formée de croix successives indique la concentration en bore en fonction de la profondeur. Bien entendu; quand le dopage en phosphore est plus important que le dopage en bore, on obtient une couche de type N et dans le cas inverse une couche de type P. On notera que, dans l'exemple représenté, la couche épitaxiée a une épaisseur de l'ordre de 4 microns.

La présente invention n'est pas limitée aux modes de réalisation qui ont été explicitement décrits. Elle en englobe les diverses variantes et généralisations incluses dans le domaine des revendications ci-après.

### REVENDICATIONS

- 1. Opérateur logique à injection par le substrat (SFL) formé d'un transistor RNP et d'un transistor NPN, élaboré à partir d'un substrat de type P faiblement dopé, caractérisé en ce qu'il comprend successivement à partir du substrat sous les zones correspondant à chaque collecteur du transistor NPN:

- une première couche de type P à forte concentration résultant d'une implantation de bore dans le substrat;

5

10

15

20

25

30

35

- une deuxième couche de type N à forte concentration résultant d'une implantation de phosphore dans la première implantation;

- une troisième couche de type N à faible concentration résultant d'une épitaxie ;

- une quatrième couche de type P à concentration moyenne résultant d'une diffusion de bore dans la couche épitaxiée;

- une cinquième couche de type N à forte concentration résultant d'une diffusion.

- 2. Opérateur logique selon la revendication 1, caractérisé en ce qu'il comprend en-dessous des métallisations de base du transistor NPN et en partant de ces métallisations, une couche profonde de type P établissant la liaison avec la quatrième couche de type P et s'arrêtant dans la deuxième couche de type N.

- 3. Opérateur logique selon la revendication 1, caractérisé en ce qu'il comprend en-dessous des métallisations d'accès à l'émetteur du transistor NPN une couche de type N profonde à forte concentration rejoignant la deuxième couche de type N.

- 4. Opérateur logique selon la revendication 1, caractérisé en ce qu'il comprend en-dessous des métallisations d'accès à l'injecteur une zone de type P à

diffusion profonde et à forte concentration rejoignant la première couche de type P.

- 5. Structure de circuit intégré combinant des opérateurs logiques à injection par le substrat (SFL) et des transistors de technologie bipolaire classique, caractérisée en ce qu'elle comprend un substrat de type P recouvert d'une couche épitaxiée, le substrat ayant reçu ayant l'épitaxie:

- dans les emplacements correspondant aux composants bipolaires linéaires une couche enterrée d'antimoine ou d'arsenic, et

10

15

20

25

30

35

- dans les emplacements correspondants aux opérateurs SFL une couche enterrée de bore et une couche enterrée locale de phosphore.

- 6. Procédé de fabrication d'un opérateur logique à injection par le substrat (SFL) selon la revendication 1 à partir d'un substrat de type P faiblement dopé caractérisé en ce qu'il comprend les étapes suivantes :

- a) introduire une couche de bore à haute concentration dans le substrat,

- b) introduire dans ce substrat une couche de phosphore aux emplacements autres que ceux pour lesquels on veut établir un contact sur la face supérieure avec une métallisation d'injecteur,

- c) former une couche épitaxiée de type N faiblement dopée,

- d) introduiredes atomes de phosphore à concentration élevée aux emplacements correspondant aux contacts métalliques qui permettent d'accéder à l'émetteur du transistor NPN,

- e) introduire aux emplacements correspondant aux contacts de base du transistor NPN, des atomes de bore à concentration élevée,

- f) implanter aux emplacements correspondant

à la base du transistor NPN de l'opérateur SFL des atomes de hore à plus faible concentration,

- g) introduire aux emplacements correspondant aux collecteurs des atomes d'un produit dopant tel que du phosphore ou de l'arsenic;

- h) procéder de façon intermédiaire et finale à des traitements thermiques propres à faire diffuser les atomes implantés,

5

10

15.

20

25

30

35

- i) procéder aux métallisations d'injecteurs,

d'émetteurs, de bases et de collecteurs.

- 7. Procédé de fabrication conjointe sur une même plaquette de circuit intégré d'opérateur SFL selon le procédé de la revendication 6 et de transistors bipolaires linéaires classiques, caractérisé en ce que, dans les emplacements correspondant aux transistors bipolaires linéaires classiques :

- une implantation d'antimoine est effectuée dans le substrat,

- l'étape a est évitée par masquage,

- l'étape b est masquée sauf en des emplacements d'étendue limitée pour lesquels on veut établir une liaison entre la surface supérieure de la plaquette terminée et la couche enterrée d'antimoine.

- 8. Procédé selon les revendications 6 et 7, caractérisé en ce que, lors de l'étape d), on implante simultanément du phosphore aux emplacements correspondant aux contacts de collecteurs des transistors bipolaires linéaires.

- 9. Procédé selon les revendications 6 et 7 caractérisé en ce que lors de l'étape e), on implante simultanément du bore aux emplacements correspondant aux contacts de base des transistors bipolaires linéaires.

- 10. Procédé selon les revendications 6 et 7, caractérisé en ce que lors de l'étape f), on implante simultanément du bore aux emplacements correspondant aux bases des transistors bipolaires linéaires.

11. Procédé selon les revendications 6 et 7, caractérisé en ce que, lors de l'étape g), on implante simultanément un dopant de type N aux emplacements correspondant aux émetteurs des transistors bipolaires linéaires.

### 1/4

Fig.1

Fig.2

Fig.7

Fig. 13