**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                                                                                                                                                                                                                                                                                   |                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| (51) Int. Cl. <sup>7</sup><br>B24B 37/04<br>H01L 21/3105                                                                                                                                                                                                                                                                                                          | (45) 공고일자 2004년04월28일<br>(11) 등록번호 10-0412165<br>(24) 등록일자 2003년12월 10일 |

| (21) 출원번호 10-1998-0709557<br>(22) 출원일자 1998년 11월 21일<br>번역문제출일자 1998년 11월 21일                                                                                                                                                                                                                                                                                     | (65) 공개번호 10-2000-0015996<br>(43) 공개일자 2000년 03월 25일                    |

| (86) 국제출원번호 PCT/US1997/008786<br>(86) 국제출원일자 1997년 05월 21일<br>(81) 지정국 국내특허 : 아일랜드 알바니아 오스트레일리아 보스니아-헤르체고비나<br>바베이도스 불가리아 브라질 캐나다 중국 쿠바 체코 에스토니아 그<br>루지야 헝가리 이스라엘 아이슬란드 일본 AP ARIPO특허 : 케냐 레소토<br>말라위 수단 스와질랜드 케냐<br>EA 유라시아특허 : 아르메니아 벨라루스 키르기즈<br>EP 유럽특허 : 오스트리아 벨기에 스위스 독일 덴마크 스페인 프랑스<br>영국 그리스 이탈리아 룩셈부르크 모나코 네덜란드 포르투칼 스웨덴<br>오스트리아 스위스 독일 덴마크 스페인 핀란드 영국 | (87) 국제공개번호 WO 1997/44160<br>(87) 국제공개일자 1997년 11월 27일                  |

| (30) 우선권주장 08/651,896 1996년 05월 21일 미국(US)                                                                                                                                                                                                                                                                                                                        |                                                                         |

| (73) 특허권자 마이크론 테크놀로지 인코포레이티드<br>미국, 아이다호 83707-0006, 보이세, 피.오.박스 6, 사우쓰 패드럴웨이 8000<br>로빈슨 칼 엠.                                                                                                                                                                                                                                                                    |                                                                         |

| (72) 발명자 미국, 아이다호 83706, 보이즈, 에이치씨 33 박스 1333<br>워커 마이클 에이.                                                                                                                                                                                                                                                                                                       |                                                                         |

| (74) 대리인 미국, 아이다호 83704, 보이즈, 골든로드 드라이브 10866<br>이병호                                                                                                                                                                                                                                                                                                              |                                                                         |

**심사관 : 권영호**

**(54) 스톱-온-피쳐반도체웨이퍼의화학적-기계적평탄화방법**

**영세서**

**기술분야**

**<1> 기술 분야**

본 발명은 반도체 웨이퍼들의 화학-기계적 평탄화(chemical-mechanical planarization; CMP) 방법에 관한 것으로, 특히, 스톱-온-피쳐(Stop-On-Feature; SOF) 웨이퍼의 표면에 걸쳐 균일한 표면을 생성하는 화학-기계적 평탄화 방법에 관한 것이다.

**배경기술**

**<3> 발명의 배경**

화학-기계적 평탄화(CMP) 공정들은 초고밀도의 집적 회로들(ultra-high density integrated circuits)의 생성에서 웨이퍼의 표면층을 평탄화하기 위해 종종 사용된다. 여러 CMP 공정들에 있어서, 웨이퍼는 제어된 화학적 상태, 압력, 속도 및 온도 조건들 하에서 CMP 매체에 노출된다. 종래의 CMP 매체는 연마 패드(polishing pad)들과 슬러리(slurry)들을 포함하며, 특히 작은 연삭 입자(abrasive particle)들과 반응성 화학 약품(reactive chemicals)들을 포함하는 슬러리 용액은 연마 패드 상의 평탄화 표면을 덮는다. 이 웨이퍼 및/또는 연마 패드는 서로에 대해 이동되어 CMP 매체가 웨이퍼의 표면을 제거하도록 한다.

**<5>**

CMP 공정들은 웨이퍼 상의 균일하고 평탄한 표면을 희망하는 종단점(end-point)에서 일관되고 정확하게 평탄화해야만 한다. 웨이퍼 상에 여러 재료로 이루어진 층을 침착하고, 웨이퍼와 다른 재료층을 포토리소그래픽, 에칭 및 도핑 공정으로 처리함으로써 단일 웨이퍼 상에 수백 개의 마이크로 전자 장치가 통상적으로 제조된다. 초고밀도의 집적 회로를 제조하기 위해서, CMP 공정은 다이(die)의 소자 부분들의 기하학적 형태(geometries)가 웨이퍼의 전체 표면에 걸쳐 정확하게 배치될 수 있도록 아주 평탄한 표면을 제공해야만 한다. 예를들면, 현재의 리소그래픽 기술은 대략 0.1~0.5µm의 허용차 내에서 회로 패턴들에 정확하게 초점을 맞추어야만 한다. 만약 웨이퍼의 표면이 고도로 평탄하지 않다면, 회로 패턴은 몇몇 영역에서 충분하게 초점이 맞지 않을 것이고, 그 결과 결함이 있는 장치들이 생성되게 된다. 따라서, 웨이퍼 상에서 균일하게 평탄한 표면을 일관되고 정확하게 평탄화하는 것이 중요하다.

**<6>**

그러나, 현재의 CMP 공정들은 웨이퍼 전체에 걸쳐 충분히 균일하고 평탄한 표면을 일관되게 생성

하지 못한다. 웨이퍼의 표면에서 재료가 제거되는 레이트("연마 레이트")는 결과의 표면의 균일성에 영향을 끼치는데, 웨이퍼 상의 하나의 영역으로부터 다른 영역으로 레이트가 변하기 때문이다. 이 연마 레이트는 몇몇 이유로 인해 웨이퍼의 표면에서 변하게 되는데, 이러한 이유로는 다음과 같은 것들이 있다: (1) 웨이퍼의 표면과 훼이퍼의 중심에서 그 에지(edge)로의 연마 패드 사이의 상대적인 속도 차이; (2) 웨이퍼의 표면에 걸친 슬러리 분배 및 유동 레이트(flow rate)들에서의 차이; (3) 웨이퍼에 걸친 재료의 구성에서의 변화; (4) 웨이퍼의 활판술(typography)의 비균일 정도; (5) 웨이퍼의 표면과 연마 패드의 표면이 CMP 공정을 통해 서로 평행하게 되지 않음; (6) 슬러리 온도가 웨이퍼의 표면에 걸쳐 변함; (7) 연마 패드 변화 상태가 연마 패드의 균일성을 감소시킴. 따라서, 웨이퍼의 연마 레이트가 웨이퍼의 한 영역에서 다른 영역까지 변할 수 있기 때문에, 현재의 CMP 공정들은 웨이퍼 상에서 충분하게 평탄한 표면을 일관되게 생성하지 못한다.

<7> 웨이퍼 표면의 균일도와 평탄도를 향상시키기 위한 CMP 공정의 비교적 새로운 양상은 스톱-온-피쳐 웨이퍼 설계이다. 전형적인 SOF 웨이퍼에 있어서, 제 1의 재료층은 웨이퍼 기판과 이 기판 상에 제조된 피쳐(featIre)들 위에 짐작되고, 제 2의 재료층은 제 1의 층 위에 짐작된다. 제 1의 층은 비교적 낮은 연마 레이트(polishing rate)를 갖는 재료로 이루어지고, 제 2의 층은 비교적 높은 연마 레이트를 갖는 재료로 이루어진다. 동작에 있어서, 제 2의 층은 제 1의 층이 노출될 때까지 평탄화된다. 제 1의 층이 제 2의 층보다 낮은 연마 레이트를 갖기 때문에, 제 2의 층의 임의의 높은 영역이 제 1의 층의 노출된 영역보다 더 빨리 제거될 것이다. 따라서, SOF 설계는 CMP 공정에 의해 웨이퍼의 높은 지점을 낮은 지점보다 더 빨리 제거하도록 하기 때문에 웨이퍼의 균일성과 평탄도를 향상시킨다.

<8> 현재의 CMP 산화물 공정들로 SOF 웨이퍼를 평탄화할 때 발생하는 문제점은 결과의 웨이퍼의 표면이 여전히 몇몇 마이크로 전자 장치들에 대해서 충분히 균일하게 평탄하지 않다는 것이다. 예를들면, 일반적으로 종래의 CMP 공정들은 SOF 웨이퍼 상에서 제 1 및 제 2의 층의 재료들간의 계면(interface)들에서  $2000\text{ \AA} \sim 3000\text{ \AA}$ 의 단계적 높이를 갖는 완성된 표면을 생성한다. SOF 웨이퍼의 평탄화된 표면은 웨이퍼로부터 재료를 제거하기 위해 현재의 CMP 공정이 주로 연마 패드의 기계적 연마와 슬러리의 입자들에 의존하기 때문에 충분히 균일하지 못할 수 있고; 따라서 제 1의 층의 몇몇 영역은 웨이퍼의 표면과 연마 패드의 표면이 서로 평행하지 않을 때, 또는 슬러리가 웨이퍼 아래에서 균일하게 분배되지 않을 때 다른 영역들에 앞서 노출될 것이다.

<9> 종래의 CMP 공정들로 SOF 웨이퍼들을 평탄화할 때 발생하는 다른 문제점은 연마 패드 균일도가 패드의 한 영역에서 다른 영역까지 제거 레이트가 크게 변하도록 감소하는 점이다. 제 1의 층이 딱딱하기 때문에, 웨이퍼 상에서 초기에 노출된 두 소자 영역들은 패드 상의 국부화된 영역들을 연마시키며(abrade) 그 결과 패드는 국부화된 영역에서 높은 제거 레이트를 갖게된다. 역으로, 웨이퍼 상의 부드러운 제 2의 층은 다른 영역의 패드에 글레이즈(glaze)를 입혀서 패드로 하여금 글레이즈된(glazed) 영역 상에서 낮은 제거 레이트를 갖도록 한다. 따라서, 종래의 SOF 웨이퍼 평탄화는 완성된 웨이퍼의 평탄도를 감소시키는 연마 패드 균일도의 큰 일탈(divergence)을 유발한다.

<10> 종래의 CMP 공정들은 제 1의 재료층보다 더 빠른 레이트로 제 2의 재료층을 화학적으로 제거하는 선택적인 슬러리를 사용함으로써 SOF 웨이퍼 상에서 단계적 높이를 감소시킨다. 처리량을 증가시키기 위해, 종래의 CMP 공정들은 또한 패드와 웨이퍼 사이에서 높은 상대적인 속도 및 패드-웨이퍼 계면에서의 고온을 사용한다. 그러나, 슬러리의 선택은 더 높은 온도에서 감소되는데, 그 이유는 열이 슬러리의 화학 약품으로 하여금 제 1의 층의 재료와 보다 더 적극적으로 반응하도록 하기 때문이다. 따라서, 슬러리가 제 2의 층에 대해 선택적이라 할지라도, 완성된 표면은 제 1의 층의 초기에 노출된 영역에서 낮은 포인트들을 갖게 될 것이다. 또한, 제 1의 층의 일부가 이제 노출되기 때문에, 연마 주기 동안 비균일성이 연마 패드에 나타나게 되어 비노출된 영역의 불균일한 연마로 나타나게 된다.

<11> 따라서, (1) 제 1의 층의 초기에 노출된 영역에서 제거되는 재료의 양을 감소시키고; (2) 제 2의 유전체층으로부터 재료가 빨리 평탄화되는 것을 여전히 허용하며; (3) 제 1의 층의 노출된 부분이 연마 패드와 제 2의 층의 동시적인 연마에 대해 갖게 되는 영향을 최소화하는 CMP 공정을 개발하는 것이 바람직하다.

## 12. 발명의 요약

<13> 본 발명의 반도체 웨이퍼의 화학-기계적 평탄화 방법에 있어서, 웨이퍼는 연마 패드의 평탄화 표면상의 용액(liquid solution) 중에 대해 배치된다. 패드 또는 웨이퍼의 적어도 하나는 비교적 낮은 제어된 속도로 다른 한쪽에 대해 이동되어 웨이퍼와 연마 패드 사이에서 실질적으로 연속적인 용액의 막을 제공한다. 패드 압반(pad platen)의 온도는 희망하는 용액의 온도를 유지하고 패드를 강하기 위해 제어된다.

<14> 본 발명에 따른 방법의 한 양호한 실시예에 있어서, 웨이퍼는 평탄화 표면과 슬러리 용액을 유지하기 위한 평탄화 표면에 형성된 다수의 웰(well)들을 갖는 고-슬러리-전송 패드(high-slurry-transport pad)상에 배치된다. 각 웰은 평탄화 표면상에 오픈 영역(open area)을 나타내는 개구를 평탄화 표면에서 갖는다. 개구는 바람직하게는 서로 이격되어 개구의 오픈 영역과 패드 전체에 걸친 평탄화 표면의 표면 영역 사이에서 실질적으로 일정한 레이트를 제공한다. 웰들은 선택적인 슬러리 용액으로 채워지고, 웨이퍼와 패드는 슬러리를 웰들로부터 도출하고 웨이퍼의 표면상의 층을 선택적으로 평탄화하기 위해 서로에 대해서 이동된다.

## 도면의 간단한 설명

- <15> 도 1은 종래 기술에 따른 종래의 연마 패드 상의 웨이퍼의 개략적인 평면도

<16> 도 2는 도 1의 웨이퍼와 연마 패드의 개략적인 단면도.

<17> 도 3은 본 발명에 따른 반도체 웨이퍼의 화학-기계적 평탄화를 위한 방법의 순서도.

- <18> 도 4는 본 발명의 방법에 따라 평탄화된 웨이퍼의 단면도.

- <19> 도 5A는 본 발명의 방법에 따라 사용된 연마 패드의 평면도.

- <20> 도 5B는 도 5A의 연마 패드의 단면도.

- <21> 도 6은 본 발명의 방법에 따라 사용된 다른 연마 패드의 평면도.

- <22> 도 7은 본 발명의 방법에 따라 사용된 다른 연마 패드의 평면도.

- <23> 도 8은 본 발명의 방법에 따라 사용된 다른 연마 패드의 평면도.

- <24> 도 9A는 동작의 한 시점에서 본 발명의 방법에 따라 사용된 연마 패드의 개략적인 단면도.

- <25> 도 9B는 동작의 후속하는 한 시점에서 도 9A의 연마 패드의 개략적인 단면도.

### 실시예

- <26> 본 발명은 연마 정지 층(polishing stop layer)이 노출된 이후에도 SOF 웨이퍼상의 평탄화된 표면의 균일도를 향상시키는 CMP 처리용 방법을 제공한다. 본 발명의 한 양호한 실시예에 있어서, 이 방법은 SOF 설계의 제 1의 층의 초기에 노출된 영역으로부터 재료가 평탄화되는 것을 실질적으로 방지하면서, 여전히 재료가 제 2의 외부 층으로부터 평탄화되는 것을 허용하는데 적합하다. 본 발명의 중요한 양상은 웨이퍼와 패드 사이에 실질적으로 연속적인 용액의 막을 보유하고 패드-웨이퍼 계면에서의 온도를 감소시키기 위해서 비교적 저속으로 웨이퍼와 연마 패드를 이동시키는 것이다. 본 발명의 중요한 다른 양상은 용액의 온도를 용액이 SOF 웨이퍼에 제 2의 외부 층에 대해 아주 선택적인 범위에 있도록 유지하기 위해 압반 온도를 제어하는 것이다. 웨이퍼와 패드 사이의 실질적으로 연속적인 액체의 막은 웨이퍼 전체에 걸쳐 용액의 더 균일한 분배를 제공하며, 이것은 패드-웨이퍼 계면에서의 온도를 감소시켜 용액의 화학 재료가 웨이퍼에서 재료를 더욱 선택적으로 제거하도록 한다. 또한, 더 낮은 압반 온도는 패드-웨이퍼 계면에서 온도를 감소시켜 용액의 선택적 제거 특성을 더 강화시키고 패드를 더 강하게 한다.

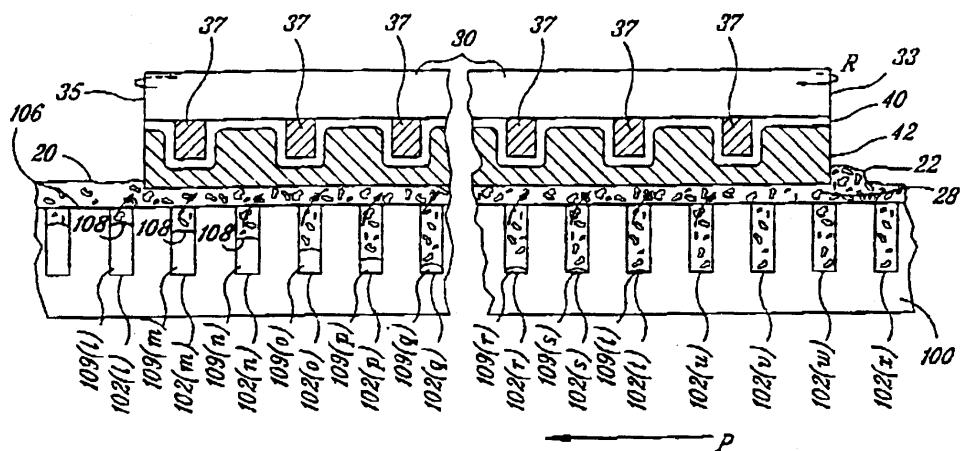

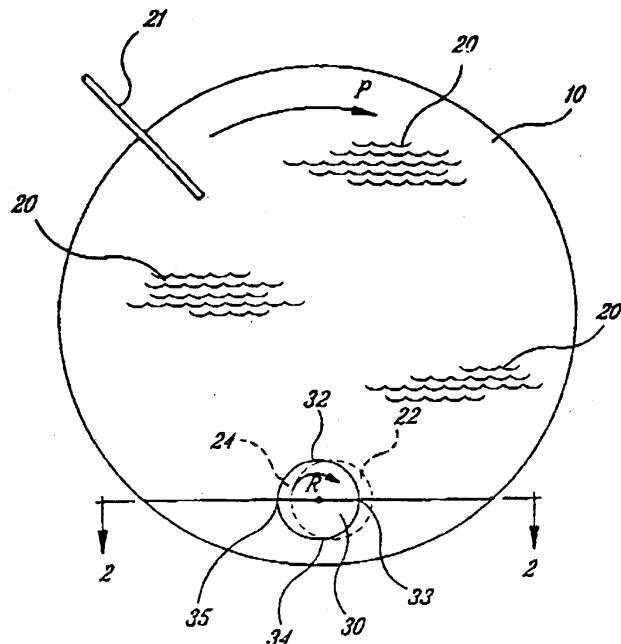

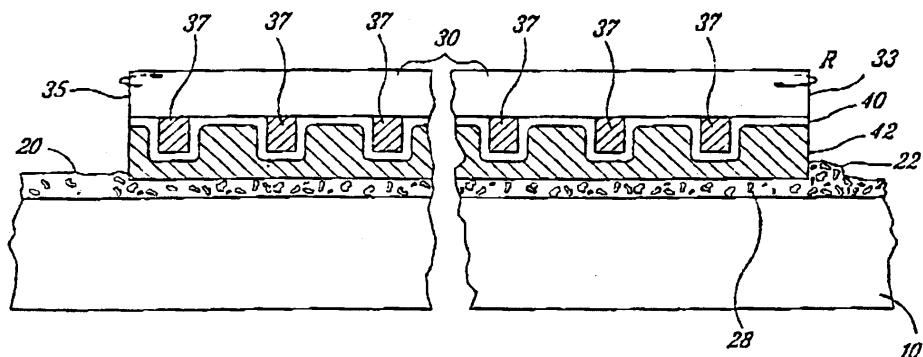

- <27> 도 1은 종래 기술에 따른 종래 연마 처리에 의해 평탄화된 웨이퍼(30)의 평면도이다. 연마 패드(10)는 화살표(P)로 도시된 방향으로 대략 40rpm으로 회전하며, 웨이퍼(30)는 화살표(R)로 도시된 방향으로 대략 10-30rpm으로 회전한다. 웨이퍼(30)는 회전하면서 연마 패드(10)에 걸쳐 이동된다. 슬러리(20)는 패이프(21)를 통해 연마 패드(10)의 상부에 방출된다(discharged). 웨이퍼(30)는 연마 패드(10)로부터 슬러리(20)를 떼어내고, 따라서 슬러리(20)는 웨이퍼(30) 주변에서 선두 에지(33)를 따라 대체로 내부 포인트(32)에서 외부 포인트(34)로 연장하는 높은 존(high zone; 22)을 형성하게 된다. 연마 패드(10)가 웨이퍼(30)의 아래에서 트레일링 에지(trailing edge:35)를 향해 진행할 때, 높은 존(22)에서의 슬러리의 초과분은 웨이퍼의 중심에서 트레일링 에지(35)로 슬러리를 비운다. 따라서 웨이퍼(30)는 중심에서 에지로의 균일하지 않은 슬러리 분배를 갖게되는데, 이것은 웨이퍼 표면의 균일도를 감소시킨다.

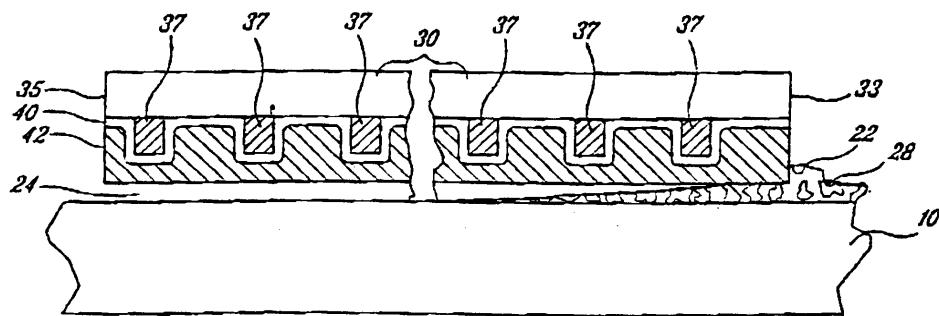

- <28> 도 2는 종래의 CMP 방법으로 평탄화된 SOF 웨이퍼(30)의 단면도를 개략적으로 도시한다. 웨이퍼(30)는 그 표면에 다수의 피쳐(feature; 37)들을 구비한다. 제 1의 유전체층(40)이 피쳐들(37)과 웨이퍼(30)상에 침착되고, 제 2의 유전체층(42)이 제 1의 유전체층(40) 위에 침착된다. 제 1의 유전체층(40)은, 본 발명의 배경 부분에 설명된 바와 같이, 결과의 유전체층의 평탄도를 향상시키기 위해 제 2의 유전체층(42)의 연마 레이트 보다 더 낮은 연마 레이트를 갖는다. 웨이퍼(30)는 제 2의 유전체층(42)의 표면이 슬러리(20)에 대향하여 위치하도록 연마 패드(10)의 반대편에 배치된다. 도 2에 양호하게 도시된 바와 같이, 슬러리(20)의 높은 존(high zone; 22)은 선두 에지(33)의 인접한 영역을 따라 형성되지만, 낮은 존(24)은 웨이퍼의 거의 중심에서 트레일링 에지(35)까지 실질적으로 슬러리(20)가 없다. 따라서, 결과의 표면의 기계적 및 화학적 제거는 슬러리가 웨이퍼의 전체 표면에 걸쳐 고르게 분배되지 않기 때문에 일반적으로 불균일하다.

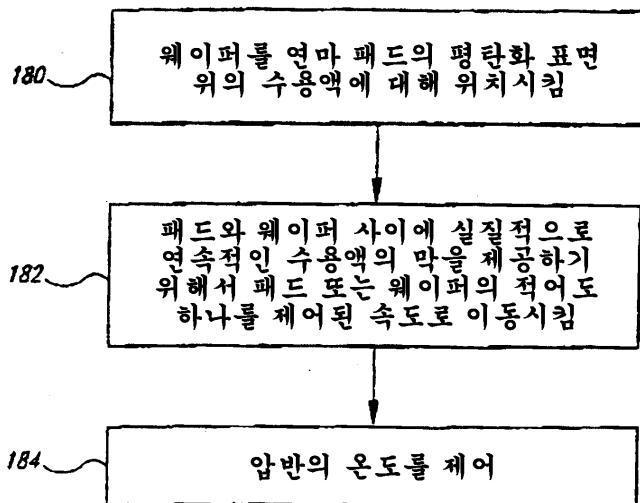

- <29> 도 3은 SOF 반도체 웨이퍼의 화학-기계적 평탄화 방법의 실시예의 단계를 설명한다. 본 방법의 첫 번째 단계(180)에서, 웨이퍼는 용액에 향하게 하여 연마 패드의 평탄화 표면상에 배치된다. 용액은 연삭 입자들로 웨이퍼로부터 재료를 기계적으로 제거하고 에칭 및/또는 산화 화학 약품으로 재료를 화학적으로 제거하는 종래의 CMP 슬러리일 수 있다. 양호한 실시예에 있어서, 연삭 입자들은 CeO<sub>2</sub>와 같은 실리콘 산화물에 선택적인 재료로 이루어진다. 용액은 실리콘 질화물(silicon nitride)의 하부층으로부터 실리콘 산화물을 선택적으로 제거하기 위한 활성제(active agent)와 같은 암모늄 수산화물(ammonium hydroxide)을 포함하는 용액과 같이, 연삭 입자들을 포함하지 않는 비-연삭 용액일 수도 있다. 비-연삭 용액의 경우에 있어서, 바람직하게는 연마 패드는 패드 상의 연삭 연마 표면(abrasive polishing surface)을 제공하기 위해 연삭 입자들이 주입된다.

- <30> 본 방법의 후속 단계(182)에 있어서, 웨이퍼와 패드 사이에 실질적으로 연속적인 용액의 막을 제공하기 위해서 패드와 패이려는 서로에 대해 비교적 낮은 속도로 이동된다. 일반적으로, 20-24 인치 직경의 패드가 대략 25-35rpm으로, 바람직하게는 30rpm으로 회전한다. 웨이퍼는 대략 10-30rpm으로, 바람직하게는 대략 15rpm으로 회전한다. 패드와 웨이퍼 사이의 상대적인 속도는 용액 상의 웨이퍼를 하이드로플레이닝(hydroplaning) 하도록 그리고 웨이퍼와 패드 사이에 실질적으로 연속적인 용액의 막을 제공하도록 제어된다. 특정 실시예에서, 델라웨어주 뉴아크의 로델(주)에 의해 제조되고, 표준의 퍼포레이션(standard perforation)을 갖는 Rodel IC-1000 퍼포레이팅된(perforated) 패드는 Rodel ILD-1300 슬러리(로델(주)에 의해 역시 제조됨)로 덮여진다. 본 방법에서 패드와 웨이퍼 사이에 실질적으로 연속적인 용액의 막을 제공하기 위해서, 바람직하게는 패드는 25-35rpm으로 회전하고, 웨이퍼는 바람직하게는 10-30 rpm으로 회전하며, 웨이퍼에 대한 하향력(down force)은 바람직하게는 5psi이다.

- <31> 웨이퍼와 패드 사이의 상대적인 속도는 웨이퍼로부터 재료의 선택적인 제거를 향상시키기 위해 종래의 CMP 기술에 비해 일반적으로 낮다. 낮은 상대적인 속도는 더 적은 연삭 입자가 웨이퍼의 표면을 연마하기 때문에 웨이퍼 재료의 비선택적인 기계적 제거를 감소시킨다. 또한 낮은 상대적인 속도들은 재료의 화학적인 선택적 제거를 향상시키는데, 그 이유는 더 균일한 용액의 막이 웨이퍼의 표면을 덮고 패

드-웨이퍼 계면에서의 온도가 감소되기 때문이다.

<32> 본 방법의 다른 후속하는 단계(184)에서, 패드의 온도는 웨이퍼로부터 재료의 선택적인 제거를 더 향상시키도록 제어된다. 패드 온도는 압반을 대략 85° F~105° F, 바람직하게는 대략 89° F~91° F로 유지함으로써 제어된다. 압반을 대략 115° F로 가열하는 종래의 CMP 처리와 비교해서, 압반 온도는 본 발명의 방법에서 상당히 낮다. 더 낮은 압반 온도는 슬러리의 화학 약품이 웨이퍼 상의 재료와 반응하는 레이트를 감소시켜 한 재료층의 선택적인 제거를 더 향상시킨다.

<33> 도 4를 참조하면, 도 3을 참조하여 전술된 방법에 따라 평탄화된 SOF 웨이퍼(30)가 도시된다. 패드는 대략 25~35 rpm으로 회전하고, 압반(12)은 대략 85° F~105° F로 가열된다. 슬러리(20)는 제 1의 유전체층(40)으로부터 크게 재료를 제거하지 않으면서 제 2의 유전체층(42)으로부터 재료를 제거하도록 웨이퍼(30) 상의 제 2의 유전체층에 대해 선택적이다. 따라서, 제 1의 유전체층(40)의 일부가 제 2의 층(42)이 완전히 평탄화되기 전에 노출될지라도, 웨이퍼(30)가 더 평탄화될 때 극소량의 재료가 제 1의 층(40)의 노출된 부분으로부터 제거된다.

<34> 도 3 및 도 4에 도시된 방법은 SOF 웨이퍼 상에 더 균일한 표면을 생성하는 데, 그 이유는 이것 이 웨이퍼의 기계적 연마를 감소시키고 제 2의 유전체층(42)의 선택적 제거를 향상시키기 때문이다. 본 발명은 패드와 웨이퍼 사이에 얇고 실질적으로 연속적인 용액의 막을 제공하는 상대 속도에서 패드와 웨이퍼를 서로에 대해 이동시킴으로써 재료의 기계적 제거를 감소시킨다. 따라서, 본 발명은 제 2의 유전체층(42)의 선택적 제거를 향상시키는데, 그 이유는 더 느린 패드 속도와, 더 낮은 패드-웨이퍼 계면 온도, 및 감소된 연마가 슬러리 화학 약품이 제 1의 유전체층(40)을 크게 제거하지 않으면서 제 2의 유전체층(42)을 활성적으로 제거하도록 하기 때문이다. 결과적으로, 도 3에 도시된 방법은 200 Å ~300 Å 사이의 단계적 높이를 갖는 웨이퍼를 생성한다.

<35> 도 3 및 도 4에 도시된 방법은 또한 웨이퍼의 표면을 더 균일하게 평탄화시키는데, 그 이유는 연마 패드 표면이 실질적으로 균일하게 열화되기 때문이다. 패드와 웨이퍼 사이의 실질적으로 연속적인 용액 막은 패드와 웨이퍼 사이의 접촉을 감소시킨다. 결과적으로, 웨이퍼 상의 초기에 노출된 두 성분 영역은 패드 상의 국부화된 영역을 연마하는 것이 실질적으로 방지된다. 따라서, 패드 전체에 걸친 연마 레이트의 공간적 차별은 본 발명에 의해 실질적으로 감소된다.

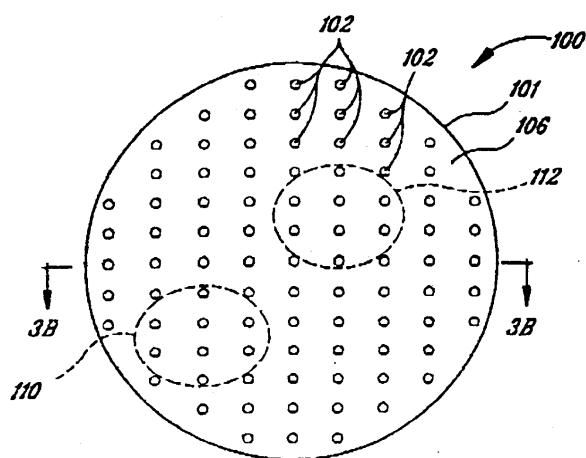

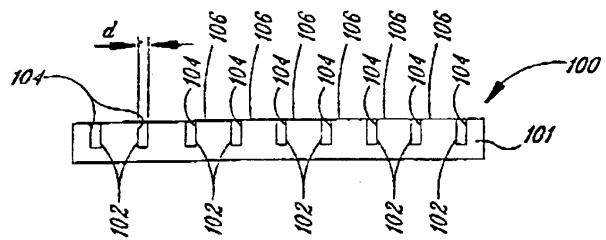

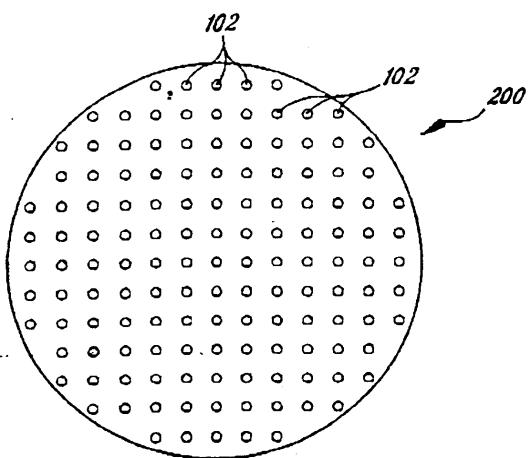

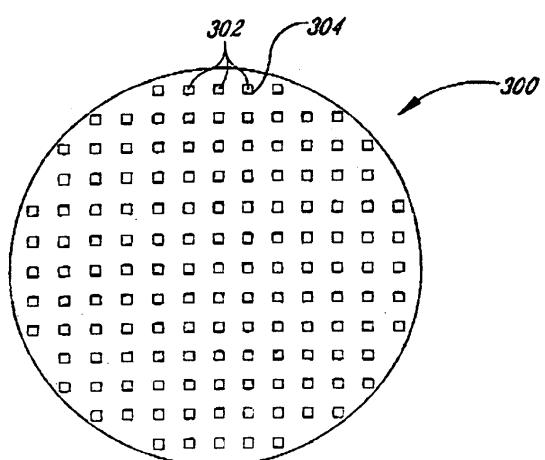

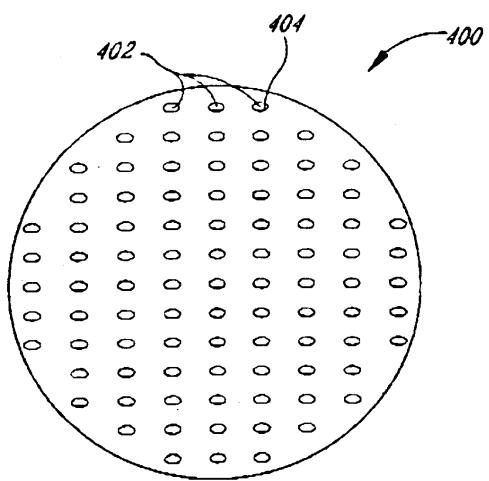

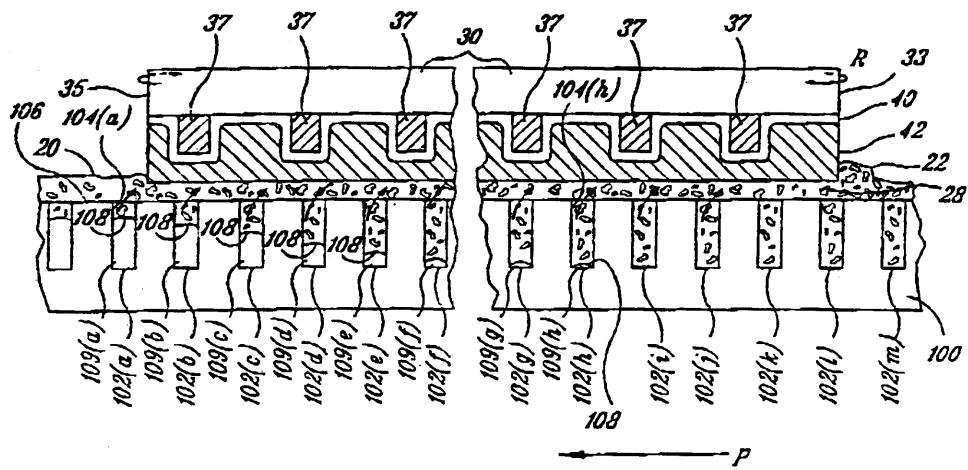

<36> 본 발명의 방법은 웨이퍼의 표면에 걸쳐 용액의 전송을 향상시키는 연마 패드에 의해 바람직하게 수행된다. 용액은 바람직하게는 CMP 슬러리이고, 이하, 슬러리에 대한 참조는 연삭 입자들을 포함하거나 또는 포함하지 않는 용액을 포함할 것이다. 도 5A 및 도 5B는 바디(body; 101)와 바디(101)에 형성된 다수의 웨들을 포함하는 적절한 고-슬러리-전송 연마 패드(100)를 도시한다. 바디(101)의 상부 표면은 평탄화 표면(106)을 나타내고, 각 웨은 평탄화 표면(106)에서 홀(holes; 104)을 갖는다. 홀(holes; 104)은 각각 오픈 영역을 구비하는데, 원형 홀의 경우에 있어서, 오픈 영역은 각 홀(holes; 104)의 직경(d)으로 결정된다. 홀(holes; 104)은 평탄화 표면(106)의 표면 영역에 대한 홀(holes; 104)의 오픈 영역의 비가 전체 패드(100)에 걸쳐 실질적으로 일정하도록 균일한 형태로 서로 이격되어 있다. 예를들면, 영역(110)에서 표면 영역(106)에 대한 홀(holes; 104)의 오픈 영역의 비는 다른 영역(112)의 것과 실질적으로 동일하다.

<37> 도 6 내지 도 8은 고-슬러리-전송 연마 패드의 다른 실시예를 도시한다. 도 6은 균일한 형태로 형성된 웨(102)를 갖는 연마 패드(200)를 도시하는데, 여기서 상기 웨(102)은 패드(200)의 표면 영역 전체에 걸쳐 일정한 거리로 서로 이격되어 있다. 도 7은 사각형 홀(304)을 갖는 웨(302)를 갖는 다른 연마 패드(300)를 도시하며, 도 8은 타원형 홀(404)을 갖는 웨(402)를 갖는 다른 패드(400)를 도시한다. 양호한 실시예에 있어서, 도 5A 및 도 5B에 도시된 패드(100 및 200)의 홀(holes; 104)과 같이 원형 홀을 갖는 패드가 본 발명의 방법에서 사용된다.

<38> 본 발명의 방법의 동작과 이점 및 고-슬러리-전송 패드가 도 9A 및 도 9B에 잘 도시되어 있다. 도 9A는 제 1의 시점에서 패드(100)에 의해 연마되는 SOF 웨이퍼(30)를 개략적으로 도시한다. 패드(100)는 방향(P)으로 25~35 rpm의 레이트로 회전하고, 웨이퍼(30)는 방향(R)으로 10 내지 30 rpm 사이의 속도로 회전하여, 웨이퍼(30)가 실질적으로 연속적인 슬러리의 막에 오르게 된다. 패드(100)는 일반적으로 웨이퍼(30)보다 훨씬 더 큰 직경을 가지며, 따라서 패드(100)는 웨이퍼(30)의 선속도(linear velocity)보다 훨씬 더 큰 선속도를 갖는다.

<39> 동작에 있어서, 웨(102(j) 내지 102(m))에 의해 도시된 바와 같이, 슬러리(20)는 웨(102)이 웨이퍼(30) 아래로 전달되기 전에 웨(102)를 채운다. 패드(100)와 웨이퍼(30) 사이의 속도에서의 차이는 웨(102)에서 슬러리(20)를 도출하는 패드의 평탄화 표면(106)을 따라 저(低)압력 영역을 생성한다 역으로, 웨(102h)은 평탄화 표면(106) 위의 저압력 영역이 웨(102(h))로부터 약간의 슬러리를 도출하기 때문에 슬러리(20)의 더 낮은 레벨(108)에 의해 경계 지워진 빈 공간(109(h))을 갖는다. 패드(100)가 웨이퍼(30) 아래에서 이동할 때, 슬러리는 웨이퍼(30)의 트레일링 에지(35)를 통과하여 전달될 때까지 웨로부터 계속적으로 도출된다. 따라서, 웨(102(a))에서, 슬러리의 더 낮은 레벨(108)은 자신의 홀(holes; 104(a)) 바로 밑에 존재한다.

<40> 도 9B는 웨(102(l))이 선두 에지(33)에서 트레일링 에지(35)로 이동한 후의 시점에서의 패드(100)를 도시한다. 웨(102(a))과 마찬가지로, 웨(102(l))의 슬러리는 웨에서 제 2의 유전체층(42)과 평탄화 표면(106) 사이의 공간으로 도출된다.

<41> 홀(holes; 104)의 크기는 웨(102)에서 슬러리를 도출하도록 평탄화 표면(106)에서 충분히 큰 압력 차이를 생성할 만큼 충분히 작다. 한 실시예에서, 원형 홀은 1 내지 3mm 사이의 직경을 가지지만, 다른 홀의 크기는 패드(100)와 웨이퍼(30) 사이의 속도 차에 따른 본 발명의 영역 내에 있다. 웨(102)의 깊이와 폭은 충분한 양의 슬러리(20)를 유지할 만큼 충분히 크기 때문에 웨은 웨이퍼(30)의 트레일링 에지(35)를 통과하는 시간까지 완전히 잠기지는 않는다.

<42> 도 9A 및 도 9B에 도시된 패드(100)와 같은 고-슬러리-전송 패드는 제2의 유전체층(42)에 선택적인 슬러리를 갖는 SOF 웨이퍼를 평탄화하기 위한 본 발명의 방법에 특히 유용하다. 패드(100)는 웨이퍼(30)와 패드(100) 사이에 실질적으로 연속적인 슬러리의 막을 제공하는 기능을 향상시킨다. 따라서, 본

발명의 방법에서 사용될 때, 고-슬러리-전송 패드는 제 1의 유전체총(40)의 초기에 노출된 영역으로부터 재료의 제거를 더 감소시킨다.

<43> 본 발명은 슬러리의 선택성에 의존하기 때문에 평탄화된 표면의 균일도를 크게 향상시키고, 기계적 평탄화를 감소하면서 화학적 평탄화를 최대화함으로써 이러한 선택성을 향상시킨다. 슬러리 용액의 선택성은 본 발명의 방법의 하기와 같은 양상에 의해 향상된다; (1) 패드와 패이려 사이에 실질적으로 연속적인 슬러리의 막을 제공하며 패드-웨이퍼 계면에서의 온도를 감소하는 낮은 속도에서 웨이퍼와 패드를 서로에 대해 이동시키고; (2) 패드-웨이퍼 계면에서의 온도를 감소시키기 위해 비교적 낮은 압반 온도를 사용한다. 슬러리의 선택성을 향상시키기 위해, 고-슬러리-전송 패드가 본 발명의 방법에서 바람직하게 사용된다 따라서, 본 발명은 제 1의 총의 초기에 노출된 영역으로부터 재료의 제거를 실질적으로 방지하면서, 여전히 상기 제 2의 유전체총으로부터 재료의 제거를 허용한다.

<44> 설명을 위해 본 발명의 특정 실시예가 상술되었지만, 본 발명의 취지와 영역을 벗어나지 않으면서 여러 수정예가 실시될 수 있음을 알 수 있을 것이다. 따라서, 본 발명은 첨부된 특허청구범위에 의해서만 제한된다.

### (57) 청구의 범위

#### 청구항 1

스톱-온-피쳐(stop-on-feature) 반도체 웨이퍼(30)의 스톱-온-피쳐 층으로부터 상부층을 선택적으로 제거하는 화학-기계적 평탄화 방법에 있어서,

상기 웨이퍼(30)를 연마 패드(10, 100, 200, 300, 400)의 평탄화 표면상의 용액 총(20)에 대향하여 배치하는 단계와;

상기 웨이퍼(30)와 상기 연마 패드 사이에 실질적으로 연속적인 용액의 막을 제공하기 위해 상기 패드 또는 상기 웨이퍼(30)중 적어도 하나를 다른 한쪽에 대해 소정의 속도로 이동시키는 단계; 및

용액의 희망하는 온도를 유지하고 상기 연마 패드를 강화하기 위해, 상기 패드(10, 100, 200, 300, 400)가 배치되는 압반(platen)의 온도를 제어하는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 2

제 1 항에 있어서, 상기 제어 단계는 상기 압반을 대략 85°F와 105°F(30°C와 40°C) 사이의 온도에서 유지시키는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 3

제 1 항에 있어서, 상기 제어 단계는 상기 압반을 대략 89°F와 91°F(31.6°C~ 32.7°C)의 온도에서 유지시키는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 4

제 1 항에 있어서, 상기 이동 단계는 상기 패드를 대략 20~200ft/min(0.10~100m/s)의 속도로 이동시키는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 5

제 1항에 있어서, 상기 이동 단계는 상기 패드를 대략 95ft/min(0.48m/s)의 속도로 이동시키는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 6

제 1 항에 있어서,

상기 이동 단계는 상기 패드를 대략 95ft/min(0.48m/s)의 속도로 이동시키며,

상기 제어 단계는 상기 압반을 대략 89°F~91°F(31.6°C~32.7°C)의 온도에서 유지시키는 단계를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 7

제 1 항에 있어서,

상기 수용액은 연삭 입자(abrasive particles)(28)을 포함하는 연마 슬러리(polishing slurry)를 포함하는 화학-기계적 평탄화 방법.

#### 청구항 8

제 1 항에 있어서,

상기 수용액은 연삭 입자들(28)이 없는 비-연삭 연마 용액을 포함하는 화학-기계적 평탄화 방법.

#### 청구항 9

제 8 항에 있어서,

상기 연마 패드는 연삭 입자들이 주입된 매트릭스 재료(matrix material)를 포함하는 화학-기계적 평탄화 방법.

**청구항 10**

제 2항에 있어서, 상기 이동 단계는 10~50rpm으로 상기 웨이퍼를 회전시키는 단계를 포함하는 화학-기계적 평탄화 방법.

**청구항 11**

제 4항에 있어서, 상기 이동 단계는 10~50rpm으로 상기 웨이퍼를 회전시키는 단계를 더 포함하는 화학-기계적 평탄화 방법.

**청구항 12**

제 1항에 있어서, 상기 상부층은 도핑된 실리콘 산화물로 이루어지고 상기 스톱-온-피쳐 층은 실리콘 질화물로 이루어지는 화학-기계적 평탄화 방법.

**청구항 13**

제 1 항 내지 제 12 항 중 어느 한 항에 있어서,

상기 연마 패드의 평탄화 표면은 상기 웨이퍼(30)와 상기 패드(10, 100, 200, 300, 400) 사이의 유체 전송을 향상시키도록 구성되고,

상기 용액의 희망하는 온도는 상기 용액이 상기 웨이퍼 상의 재료층에 대해 선택적이며 상기 패드를 강화하는 온도로 유지되는 화학-기계적 평탄화 방법.

**청구항 14**

제 13 항에 있어서,

상기 연마 패드는 슬러리 용액을 보유하기 위한 다수의 웰(Well)들을 구비하고, 상기 평탄화 표면은 표면 영역을 가지며, 각 웰은 상기 평탄화 표면상에서 오픈(open) 영역을 규정하는 개구(opening)를 가지며, 상기 개구들은 상기 패드를 걸쳐 상기 평탄화 표면의 영역과 상기 개구들의 오픈 영역 사이에 일정 레이트를 제공하기 위해서 서로 이격되어 있는 화학-기계적 평탄화 #방법.

**청구항 15**

제 13 항에 있어서,

상기 연마 패드는 상기 평탄화 표면에 형성된 그루브(grooves)들을 갖는 화학-기계적 평탄화 방법.

**청구항 16**

제 13 항에 있어서, 스톱-온-피쳐 층 설계의 한 층으로부터 재료를 선택적으로 제거하는 슬러리 용액을 선택하는 단계를 더 포함하는 화학-기계적 평탄화 방법.

**청구항 17**

제 14 항에 있어서,

홀들(holes)은 웨이퍼가 상기 웰들을 통과할 때 상기 웰들에 인접한 슬러리에 저(低)압력 영역을 생성하기 위한 크기를 가지며, 상기 웨이퍼 또는 상기 패드 중 적어도 하나를 다른 한쪽에 이동시키는 단계는 상기 웨이퍼 표면에 걸쳐 실질적으로 일정한 양의 슬러리 용액을 분배하기 위해, 상기 웰들내의 슬러리 용액의 일부가 상기 웰들에서 도출되어 상기 웨이퍼와 접촉하는 상대적인 속도로 상기 패드에 걸쳐 상기 웨이퍼를 미끌어져 움직이게 하는 단계를 포함하는 화학-기계적 평탄화 방법.

**청구항 18**

제 1 항에 있어서,

상기 웨이퍼는 대략 10~30rpm으로 회전하고, 상기 펀드는 대략 75~150ft/min(0.38~0.76m/s)의 속도로 이동하며;

상기 패드의 온도는 85° F와 95° F(30°C와 40°C) 사이에 있도록 유지되는 화학-기계적 평탄화 방법.

**청구항 19**

제 18 항에 있어서,

상기 용액은 연삭 입자들이 없는 비-연삭 용액을 포함하는 화학-기계적 평탄화 방법.

**청구항 20**

제 19항에 있어서, 상기 용액은 암모늄 수산화물을 포함하는 화학-기계적 평탄화 방법.

**청구항 21**

제 18 항에 있어서,

상기 연마 패드는 연삭 입자들이 주입된 화학-기계적 평탄화 방법.

청구항 22

제 13항에 있어서, 상기 이동 단계는 상기 패드를 대략 95rpm으로 이동시키는 단계를 포함하는 화학-기계적 평탄화 방법.

## 요약

본 발명은 스톰-온-피쳐 디자인 웨이퍼를 평탄화하는데 아주 유용한 반도체 웨이퍼를 화학-기계적 평탄화 방법이다. 초기에, 이 웨이퍼는 용액을 향하여 연마 패드의 평탄화 표면 위에 배치된다. 이 웨이퍼와 패드 사이에 실질적으로 연속적인 용액의 막을 유지하기 위해서 웨이퍼 또는 패드의 적어도 하나는 다른 한쪽에 대해 비교적 저속으로 이동된다. 또한 패드 압반의 온도는 용액이 웨이퍼상의 재료층에 대해 크게 선택적으로 되는 용액의 비교적 낮은 온도를 유지하기 위해 제어된다.

## 대표도

54

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5A

도면5B

도면6

도면7

도면8

도면9A

도면9B