(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7537571号**

**(P7537571)**

(45)発行日 令和6年8月21日(2024.8.21)

(24)登録日 令和6年8月13日(2024.8.13)

(51)国際特許分類

H 0 1 L 27/146 (2006.01)

H 0 4 N 25/70 (2023.01)

F I

H 0 1 L 27/146

H 0 4 N 25/70

E

請求項の数 5 (全46頁)

|                   |                                                                 |          |                                              |

|-------------------|-----------------------------------------------------------------|----------|----------------------------------------------|

| (21)出願番号          | 特願2023-135339(P2023-135339)                                     | (73)特許権者 | 000002185<br>ソニーグループ株式会社<br>東京都港区港南1丁目7番1号   |

| (22)出願日           | 令和5年8月23日(2023.8.23)                                            | (74)代理人  | 110001357<br>弁理士法人つばさ国際特許事務所                 |

| (62)分割の表示         | 特願2021-198113(P2021-198113<br>の分割<br>原出願日 平成28年9月30日(2016.9.30) | (72)発明者  | 富樫 秀晃<br>東京都港区港南1丁目7番1号 ソニー <sup>株式会社内</sup> |

| (65)公開番号          | 特開2023-157977(P2023-157977<br>A)                                | (72)発明者  | 古閑 史彦<br>東京都港区港南1丁目7番1号 ソニー <sup>株式会社内</sup> |

| (43)公開日           | 令和5年10月26日(2023.10.26)                                          | (72)発明者  | 山口 哲司<br>東京都港区港南1丁目7番1号 ソニー <sup>株式会社内</sup> |

| 審査請求日             | 令和5年8月23日(2023.8.23)                                            | (72)発明者  | 平田 晋太郎                                       |

| (31)優先権主張番号       | 特願2016-38777(P2016-38777)                                       |          |                                              |

| (32)優先日           | 平成28年3月1日(2016.3.1)                                             |          |                                              |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                                                         |          |                                              |

最終頁に続く

(54)【発明の名称】 光検出素子

**(57)【特許請求の範囲】****【請求項1】**

第1電極、光電変換層及び第2電極が積層されて成る光電変換部を備え、前記光電変換部は、更に、前記第1電極と離間して配置され、且つ、絶縁層を介して前記光電変換層と対向して配置された電荷蓄積用電極を有し、

前記光電変換層は、前記第1電極側から、下層半導体層と上層光電変換層との積層構造を有し、

前記下層半導体層は、酸化物半導体材料を含み、

前記下層半導体層を構成する材料は、前記上層光電変換層を構成する材料よりも高い移動度を有し、

前記下層半導体層は、前記絶縁層の開口部内を延在し、前記第1電極と電気的に接続され、前記第1電極の頂面の縁部は前記絶縁層で覆われる

光検出素子。

**【請求項2】**

前記絶縁層のうち、前記第1電極を覆う部分は、前記第1電極の厚み方向において、前記第1電極と前記光電変換層との間に配置される

請求項1に記載の光検出素子。

**【請求項3】**

前記光電変換部は、第1波長領域の光を光電変換するように構成される

請求項1に記載の光検出素子。

**【請求項 4】**

前記酸化物半導体材料は、インジウムを含む

請求項 1 に記載の光検出素子。

**【請求項 5】**

前記下層半導体層は酸化物半導体材料から成る

請求項 1 から請求項 4 のいずれか一項に記載の光検出素子。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、光検出素子に関する。

10

**【背景技術】****【0002】**

光電変換層に有機半導体材料を用いる撮像素子は、特定の色（波長帯）を光電変換することが可能である。そして、このような特徴を有するが故に、固体撮像装置における撮像素子として用いる場合、オンチップ・カラーフィルタ（O C C F）と撮像素子との組合せから副画素が成り、副画素が 2 次元配列されている、従来の固体撮像装置では不可能な、副画素を積層した構造（積層型撮像素子）を得ることが可能である（例えば、特開 2011-138927 参照）。また、デモザイク処理を必要としないことから、偽色が発生しないといった利点がある。尚、以下の説明において、半導体基板の上あるいは上方に設けられた光電変換部を備えた撮像素子を、便宜上、「第 1 タイプの撮像素子」と呼び、第 1 タイプの撮像素子を構成する光電変換部を、便宜上、「第 1 タイプの光電変換部」と呼び、半導体基板内に設けられた撮像素子を、便宜上、「第 2 タイプの撮像素子」と呼び、第 2 タイプの撮像素子を構成する光電変換部を、便宜上、「第 2 タイプの光電変換部」と呼ぶ場合がある。

20

**【0003】**

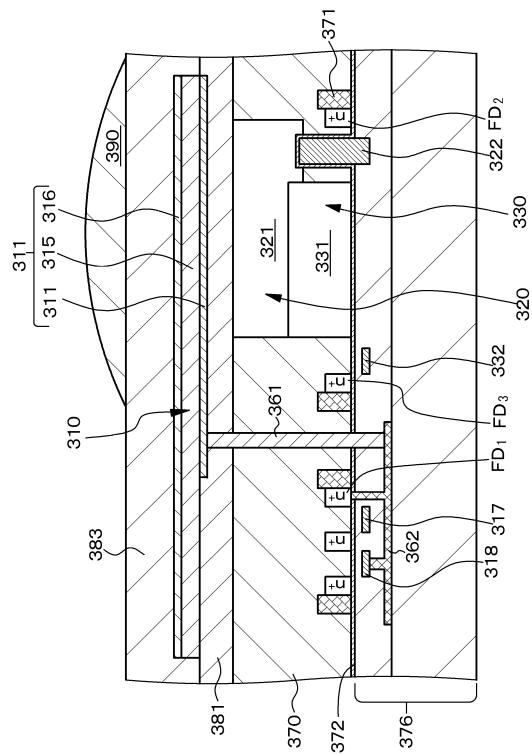

図 4 9 に従来の積層型撮像素子（積層型固体撮像装置）の構造例を示す。図 4 9 に示す例では、半導体基板 370 内に、第 2 タイプの撮像素子である第 3 撮像素子 330 及び第 2 撮像素子 320 を構成する第 2 タイプの光電変換部である第 3 光電変換部 331 及び第 2 光電変換部 321 が積層され、形成されている。また、半導体基板 370 の上方（具体的には、第 2 撮像素子 320 の上方）には、第 1 タイプの光電変換部である第 1 光電変換部 311 が配置されている。ここで、第 1 光電変換部 311 は、第 1 電極 311、有機材料から成る光電変換層 315、第 2 電極 316 を備えており、第 1 タイプの撮像素子である第 1 撮像素子 310 を構成する。第 2 光電変換部 321 及び第 3 光電変換部 331 においては、吸収係数の違いにより、それぞれ、例えば、青色及び赤色の光が光電変換される。また、第 1 光電変換部 311 においては、例えば、緑色の光が光電変換される。

30

**【0004】**

第 2 光電変換部 321 及び第 3 光電変換部 331 において光電変換によって生成した電荷は、これらの第 2 光電変換部 321 及び第 3 光電変換部 331 に一旦蓄積された後、それぞれ、縦型トランジスタ（ゲート部 322 を図示する）と転送トランジスタ（ゲート部 332 を図示する）によって第 2 浮遊拡散層（Floating Diffusion）F D 2 及び第 3 浮遊拡散層 F D 3 に転送され、更に、外部の読み出し回路（図示せず）に出力される。これらのトランジスタ及び浮遊拡散層 F D 2, F D 3 も半導体基板 370 に形成されている。

40

**【0005】**

第 1 光電変換部 311 において光電変換によって生成した電荷は、コンタクトホール部 361、配線層 362 を介して、半導体基板 370 に形成された第 1 浮遊拡散層 F D 1 に蓄積される。また、第 1 光電変換部 311 は、コンタクトホール部 361、配線層 362 を介して、電荷量を電圧に変換する增幅トランジスタのゲート部 318 にも接続されている。そして、第 1 浮遊拡散層 F D 1 は、リセット・トランジスタ（ゲート部 317 を図示する）の一部を構成している。尚、参照番号 371 は素子分離領域であり、参照番号 372 は半導体基板 370 の表面に形成された酸化膜であり、参照番号 376, 381 は層間

50

絶縁層であり、参照番号 3 8 3 は保護層であり、参照番号 3 9 0 はオンチップ・マイクロレンズである。

**【先行技術文献】**

**【特許文献】**

**【0 0 0 6】**

**【文献】特開 2 0 1 1 - 1 3 8 9 2 7**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 7】**

ところで、第 2 光電変換部 3 2 1 及び第 3 光電変換部 3 3 1 において光電変換によって生成した電荷は、第 2 光電変換部 3 2 1 及び第 3 光電変換部 3 3 1 に一旦蓄積された後、第 2 浮遊拡散層 F D 2 及び第 3 浮遊拡散層 F D 3 に転送される。それ故、第 2 光電変換部 3 2 1 及び第 3 光電変換部 3 3 1 を完全空乏化することができる。しかしながら、第 1 光電変換部 3 1 1 において光電変換によって生成した電荷は、直接、第 1 浮遊拡散層 F D 1 に蓄積される。それ故、第 1 光電変換部 3 1 1 を完全空乏化することは困難である。そして、以上の結果、k T C ノイズが大きくなり、ランダムノイズが悪化し、撮像画質の低下をもたらす。

10

**【0 0 0 8】**

従って、本開示の目的は、撮像画質の低下を抑制し得る構成、構造の光検出素子を提供することにある。

20

**【課題を解決するための手段】**

**【0 0 0 9】**

上記の目的を達成するための本開示の光検出素子は、第 1 電極、光電変換層及び第 2 電極が積層されて成る光電変換部を備えている。光電変換部は、更に、第 1 電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極を備えている。光電変換層は、第 1 電極側から、下層半導体層と上層光電変換層との積層構造を有する。下層半導体層は、酸化物半導体材料を含む。下層半導体層を構成する材料は、上層光電変換層を構成する材料よりも高い移動度を有する。

30

**【発明の効果】**

**【0 0 1 0】**

本開示の光検出素子にあっては、第 1 電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極が備えられているので、光電変換部に光が照射され、光電変換部において光電変換されるとき、光電変換層に電荷を蓄えることができる。それ故、露光開始時、電荷蓄積部を完全空乏化し、電荷を消去することが可能となる。その結果、k T C ノイズが大きくなり、ランダムノイズが悪化し、撮像画質の低下をもたらすといった現象の発生を抑制することができる。尚、本明細書に記載された効果はあくまで例示であって限定されるものでは無く、また、付加的な効果があつてもよい。

**【図面の簡単な説明】**

**【0 0 1 1】**

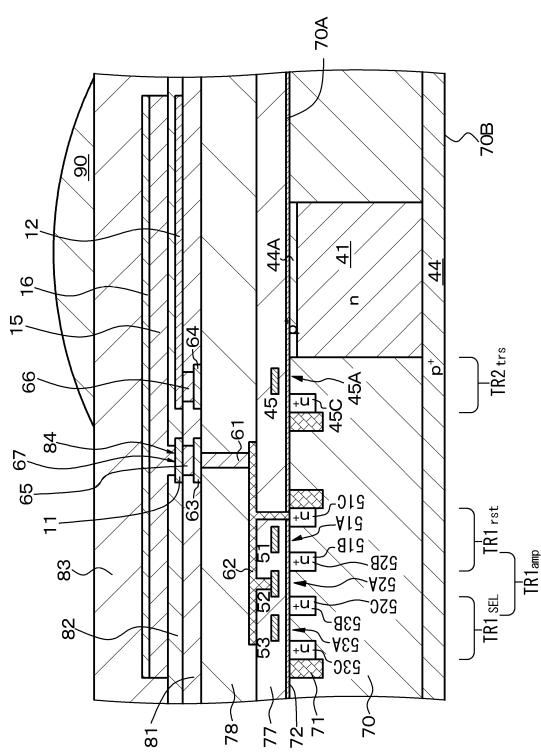

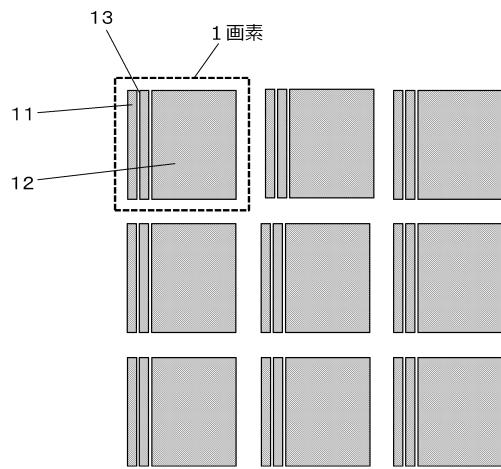

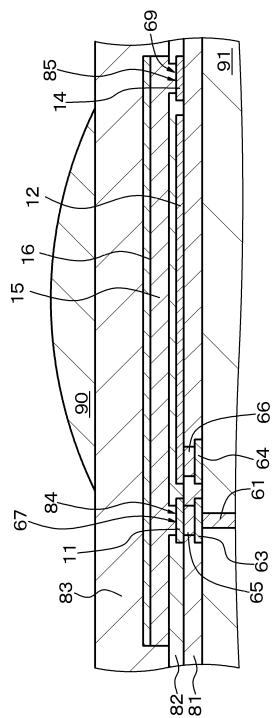

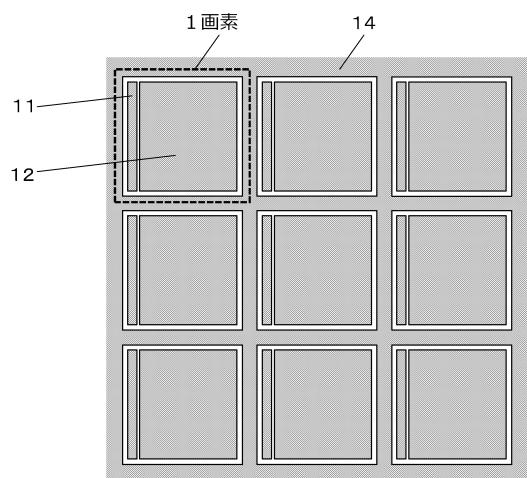

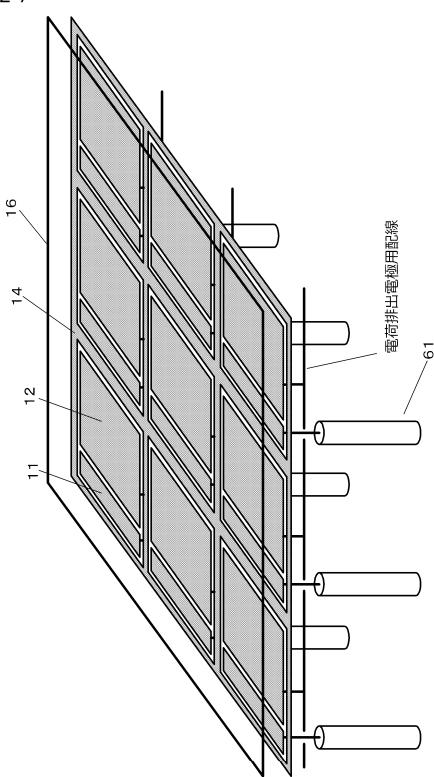

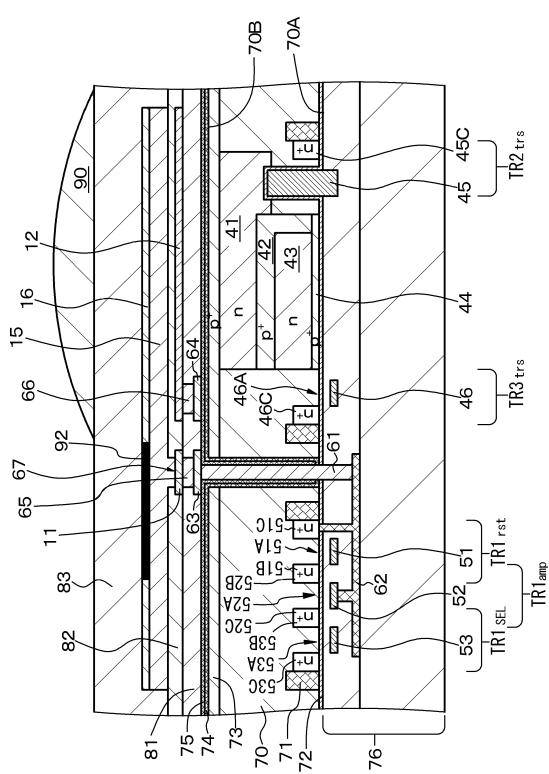

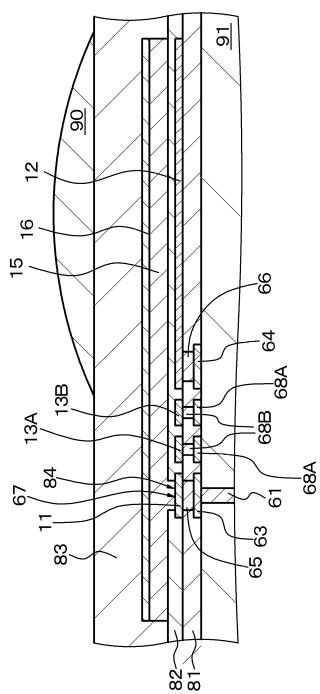

**【図 1】** 図 1 は、実施例 1 の撮像素子、積層型撮像素子の模式的な一部断面図である。

40

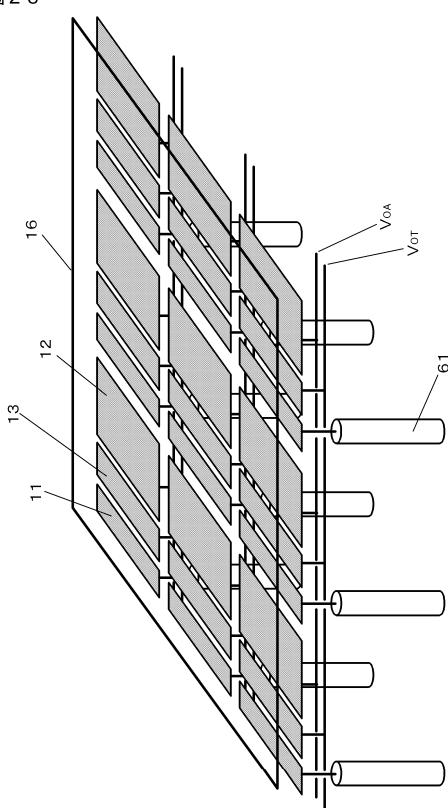

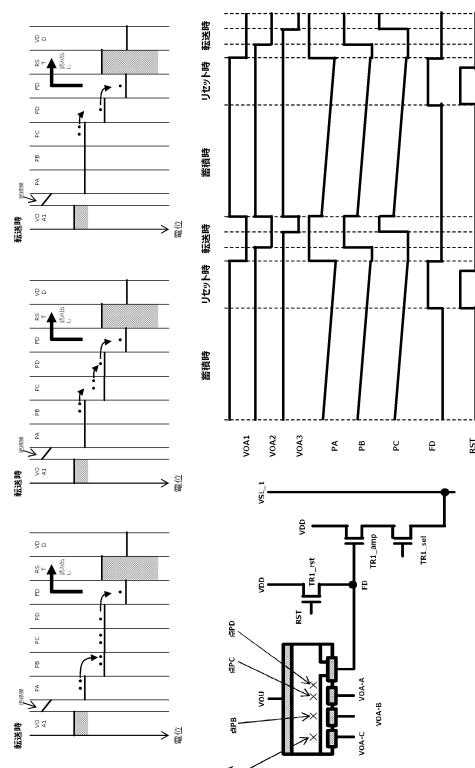

**【図 2】** 図 2 は、実施例 1 の撮像素子、積層型撮像素子の等価回路図である。

**【図 3】** 図 3 は、実施例 1 の撮像素子、積層型撮像素子の等価回路図である。

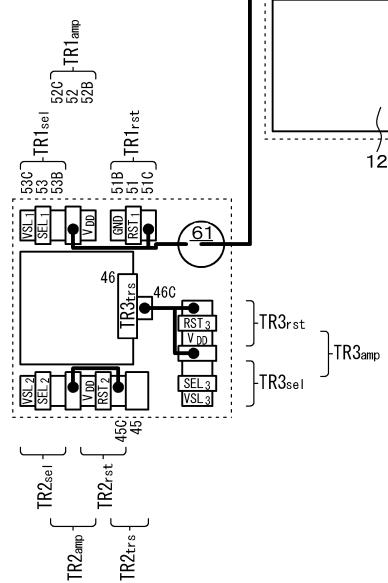

**【図 4】** 図 4 は、実施例 1 の撮像素子を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図である。

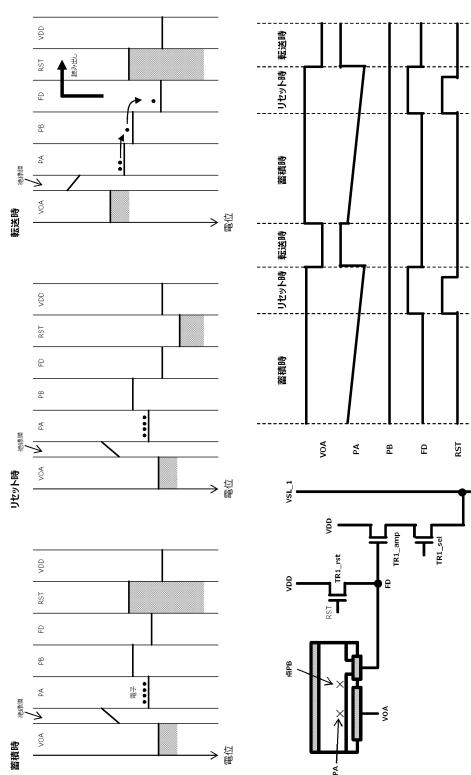

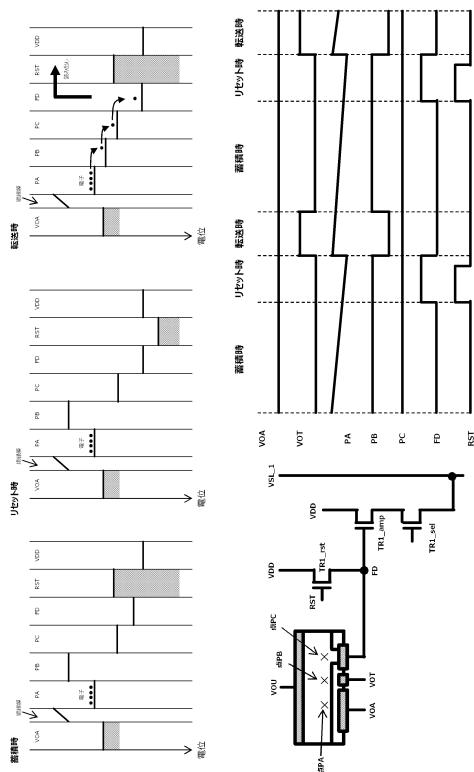

**【図 5】** 図 5 は、実施例 1 の撮像素子の動作時の各部位における電位の状態を模式的に示す図である。

**【図 6】** 図 6 は、実施例 1 の撮像素子を構成する第 1 電極及び電荷蓄積用電極の模式的な配置図である。

**【図 7】** 図 7 は、実施例 1 の撮像素子を構成する第 1 電極、電荷蓄積用電極、第 2 電極及

50

びコンタクトホール部の模式的な透視斜視図である。

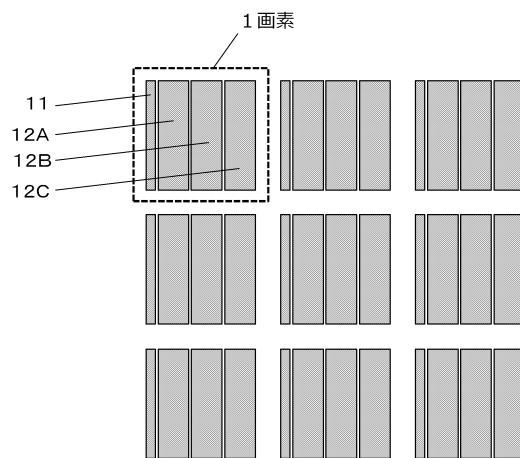

【図 8】図 8 は、実施例 1 の固体撮像装置の概念図である。

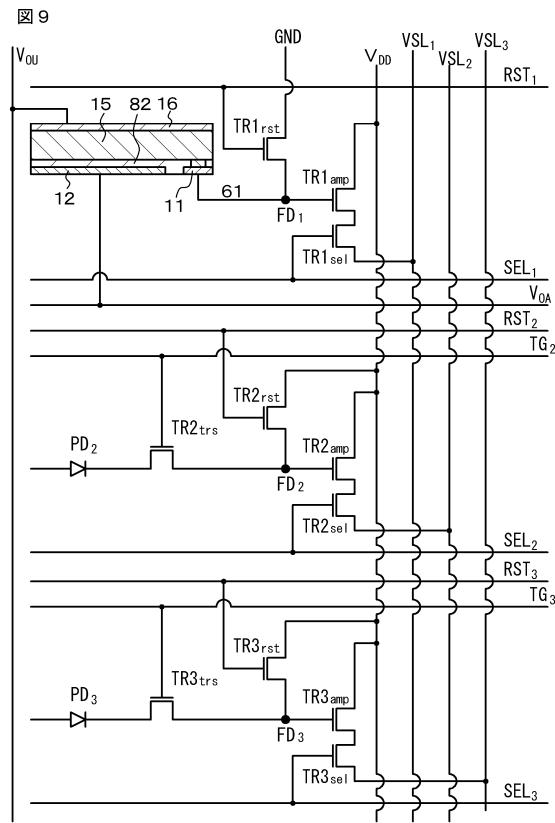

【図 9】図 9 は、実施例 1 の撮像素子、積層型撮像素子の変形例の等価回路図である。

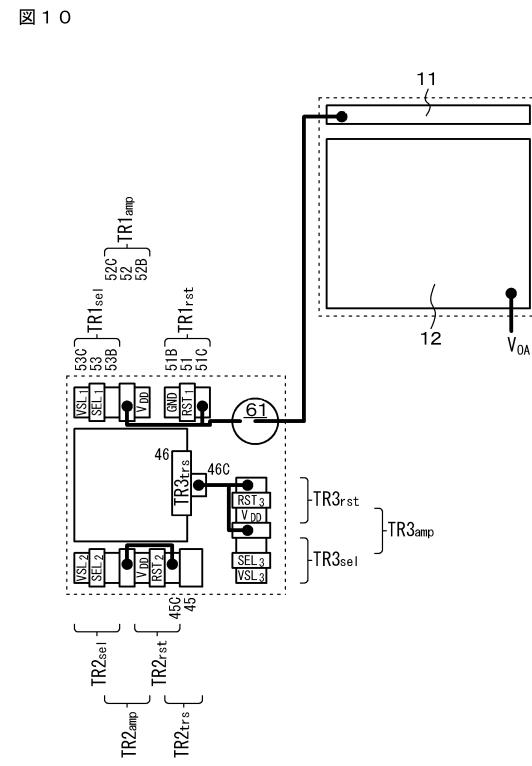

【図 10】図 10 は、図 9 に示した実施例 1 の撮像素子の変形例を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図である。

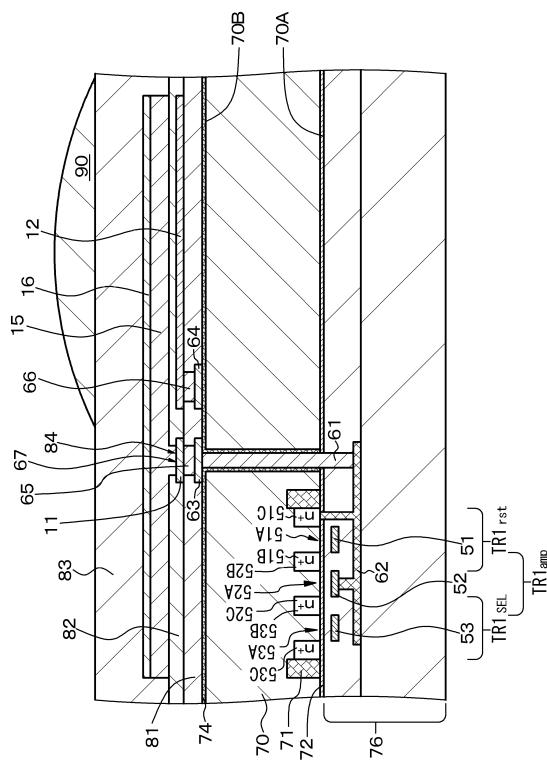

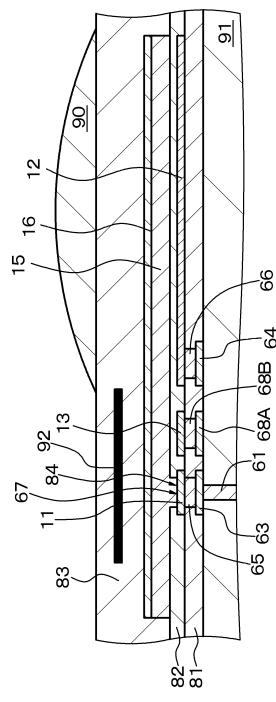

【図 11】図 11 は、実施例 2 の撮像素子、積層型撮像素子の模式的な一部断面図である。

【図 12】図 12 は、実施例 3 の撮像素子、積層型撮像素子の模式的な一部断面図である。

【図 13】図 13 は、実施例 3 の撮像素子、積層型撮像素子の変形例の模式的な一部断面図である。

【図 14】図 14 は、実施例 3 の撮像素子の別の変形例の模式的な一部断面図である。

10

【図 15】図 15 は、実施例 3 の撮像素子の更に別の変形例の模式的な一部断面図である。

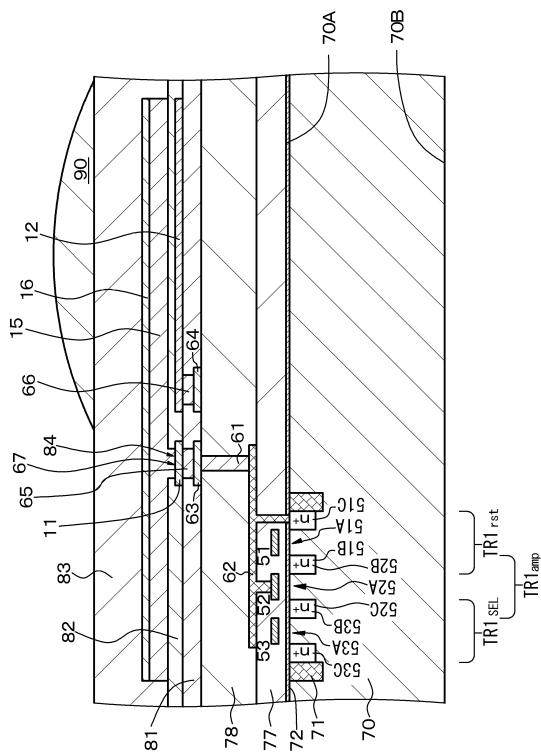

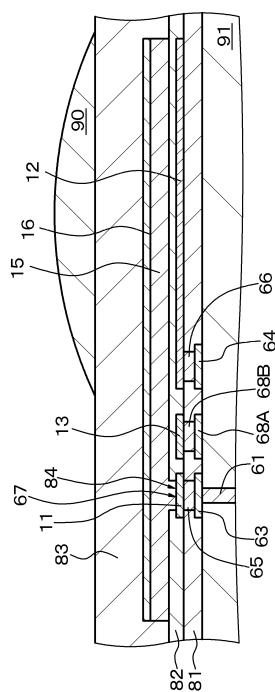

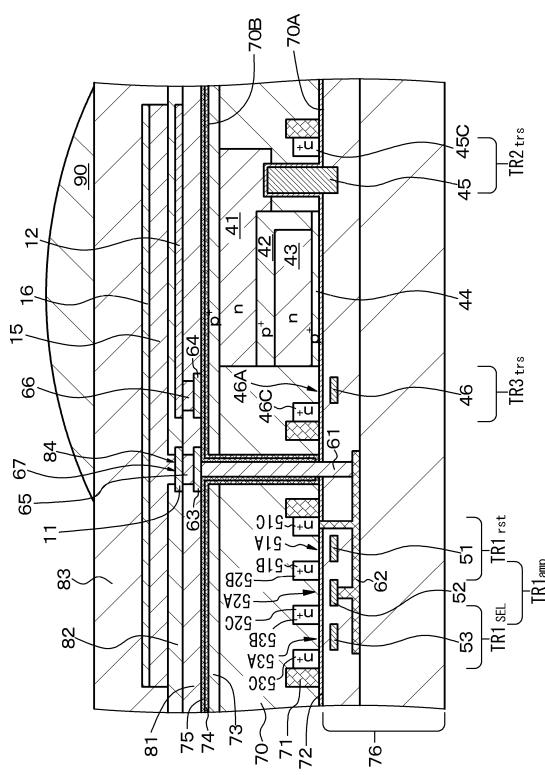

【図 16】図 16 は、実施例 4 の撮像素子、積層型撮像素子の一部分の模式的な一部断面図である。

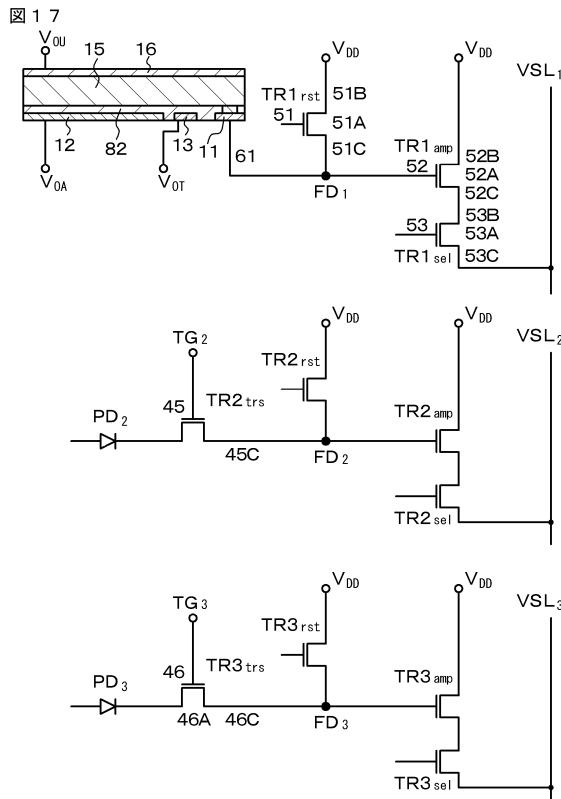

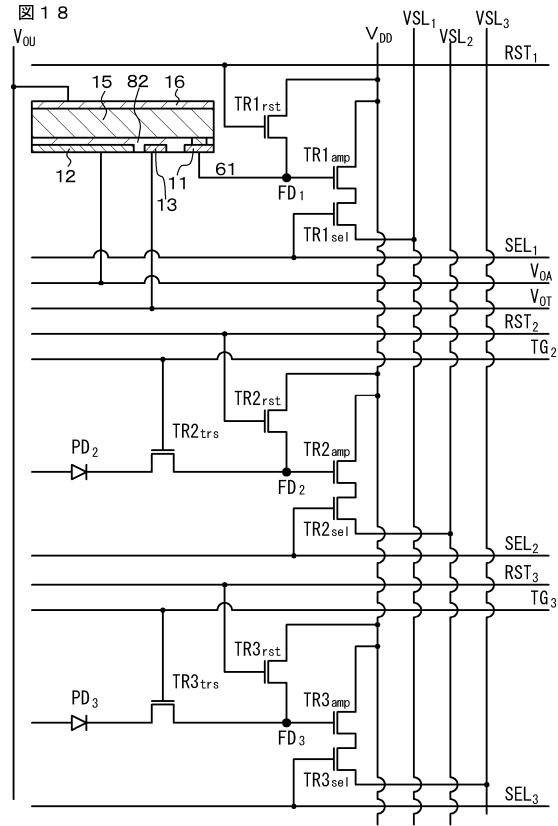

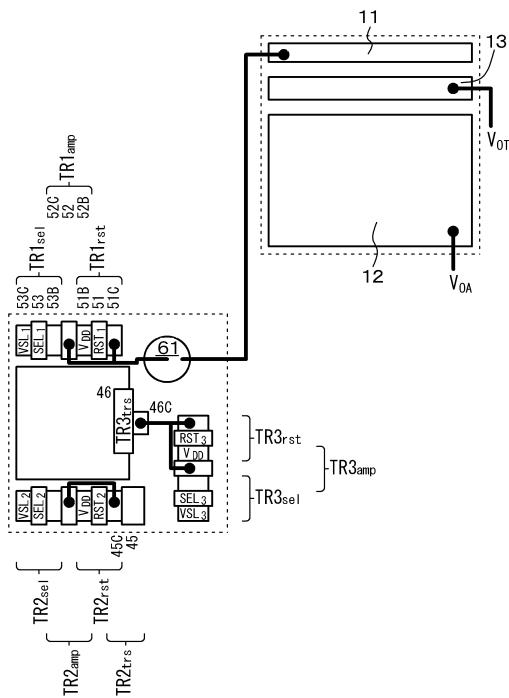

【図 17】図 17 は、実施例 4 の撮像素子、積層型撮像素子の等価回路図である。

【図 18】図 18 は、実施例 4 の撮像素子、積層型撮像素子の等価回路図である。

【図 19】図 19 は、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図である。

【図 20】図 20 は、実施例 4 の撮像素子の動作時の各部位における電位の状態を模式的に示す図である。

【図 21】図 21 は、実施例 4 の撮像素子の別の動作時の各部位における電位の状態を模式的に示す図である。

20

【図 22】図 22 は、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極及び電荷蓄積用電極の模式的な配置図である。

【図 23】図 23 は、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極、電荷蓄積用電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図である。

【図 24】図 24 は、実施例 4 の撮像素子の変形例を構成する第 1 電極、転送制御用電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図である。

【図 25】図 25 は、実施例 5 の撮像素子、積層型撮像素子の一部分の模式的な一部断面図である。

【図 26】図 26 は、実施例 5 の撮像素子を構成する第 1 電極、電荷蓄積用電極及び電荷排出電極の模式的な配置図である。

30

【図 27】図 27 は、実施例 5 の撮像素子を構成する第 1 電極、電荷蓄積用電極、電荷排出電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図である。

【図 28】図 28 は、実施例 6 の撮像素子、積層型撮像素子の一部分の模式的な一部断面図である。

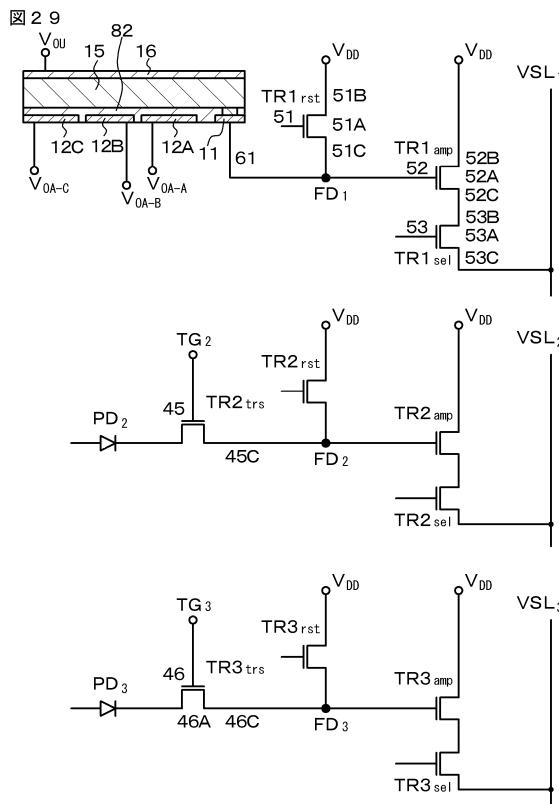

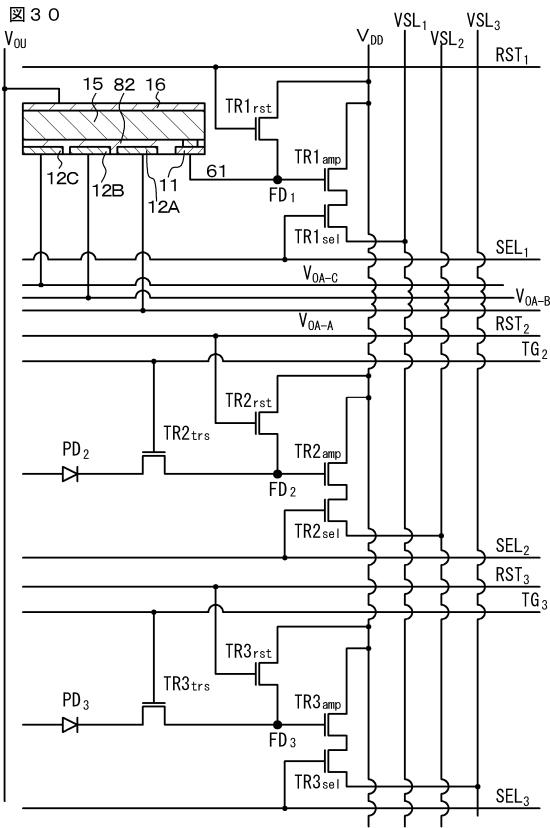

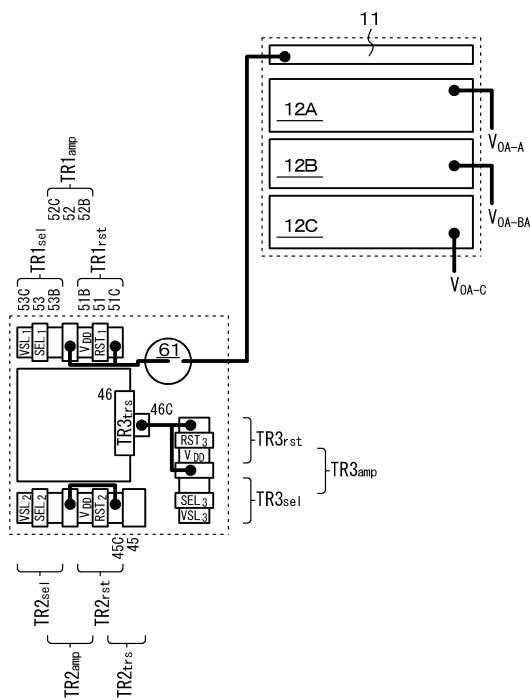

【図 29】図 29 は、実施例 6 の撮像素子、積層型撮像素子の等価回路図である。

【図 30】図 30 は、実施例 6 の撮像素子、積層型撮像素子の等価回路図である。

【図 31】図 31 は、実施例 6 の撮像素子を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図である。

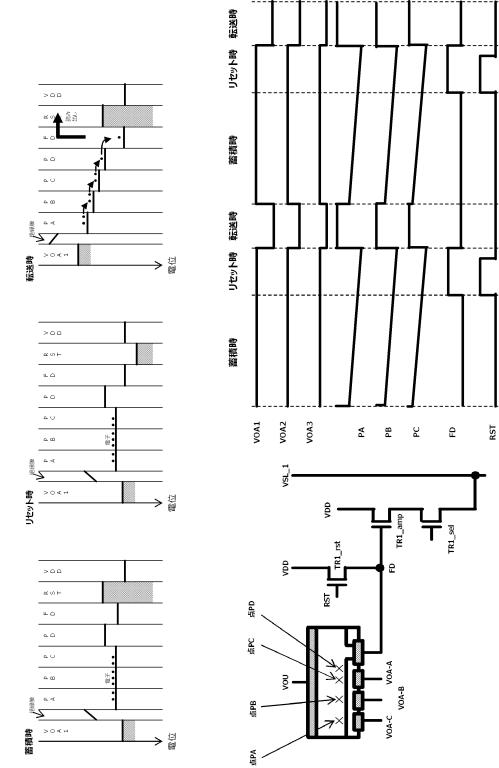

【図 32】図 32 は、実施例 6 の撮像素子の動作時の各部位における電位の状態を模式的に示す図である。

40

【図 33】図 33 は、実施例 6 の撮像素子の別の動作時（転送時）の各部位における電位の状態を模式的に示す図である。

【図 34】図 34 は、実施例 6 の撮像素子を構成する第 1 電極及び電荷蓄積用電極の模式的な配置図である。

【図 35】図 35 は、実施例 6 の撮像素子を構成する第 1 電極、電荷蓄積用電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図である。

【図 36】図 36 は、実施例 6 の撮像素子の変形例を構成する第 1 電極及び電荷蓄積用電極の模式的な配置図である。

【図 37】図 37 は、実施例 1 の撮像素子、積層型撮像素子の別の変形例の模式的な一部

50

断面図である。

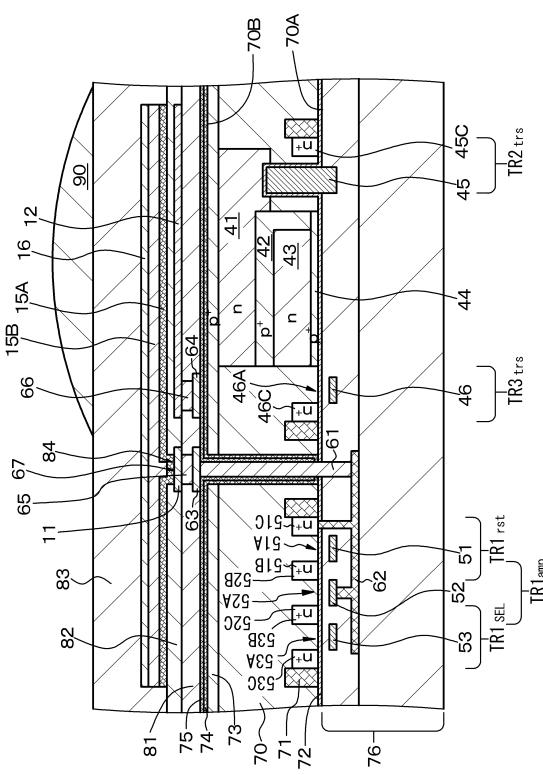

【図38】図38は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。

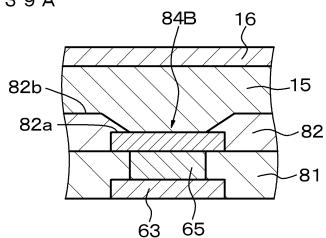

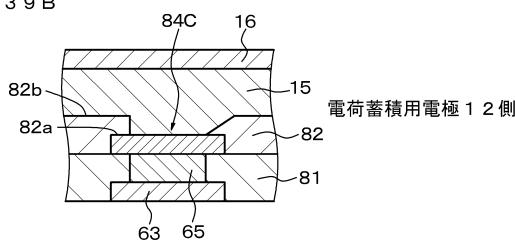

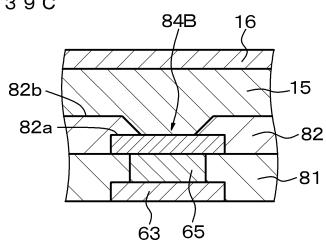

【図39】図39A、図39B及び図39Cは、実施例1の撮像素子、積層型撮像素子の更に別の変形例の第1電極の部分等の拡大された模式的な一部断面図である。

【図40】図40は、実施例5の撮像素子、積層型撮像素子の別の変形例の電荷排出電極の部分等の拡大された模式的な一部断面図である。

【図41】図41は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。

【図42】図42は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。 10

【図43】図43は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。

【図44】図44は、実施例4の撮像素子、積層型撮像素子の別の変形例の模式的な一部断面図である。

【図45】図45は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。

【図46】図46は、実施例1の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。

【図47】図47は、実施例4の撮像素子、積層型撮像素子の更に別の変形例の模式的な一部断面図である。 20

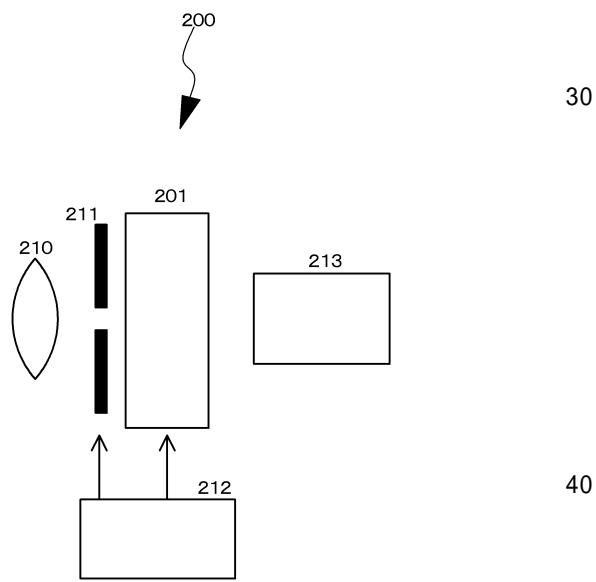

【図48】図48は、本開示の撮像素子、積層型撮像素子から構成された固体撮像装置を電子機器（カメラ）を用いた例の概念図である。

【図49】図49は、従来の積層型撮像素子（積層型固体撮像装置）の概念図である。

#### 【発明を実施するための形態】

##### 【0012】

以下、図面を参照して、実施例に基づき本開示を説明するが、本開示は実施例に限定されるものではなく、実施例における種々の数値や材料は例示である。尚、説明は、以下の順序で行う。

1. 本開示の撮像素子、本開示の積層型撮像素子及び本開示の第1の態様～第2の態様に係る固体撮像装置、並びに、固体撮像装置の駆動方法、全般に関する説明 30

2. 実施例1（本開示の撮像素子、本開示の積層型撮像素子及び本開示の第2の態様に係る固体撮像装置）

3. 実施例2（実施例1の変形）

4. 実施例3（実施例1～実施例2の変形）

5. 実施例4（実施例1～実施例3の変形、転送制御用電極を備えた撮像素子）

6. 実施例5（実施例1～実施例4の変形、電荷排出電極を備えた撮像素子）

7. 実施例6（実施例1～実施例5の変形、複数の電荷蓄積用電極セグメントを備えた撮像素子）

8. その他 40

##### 【0013】

本開示の撮像素子、本開示の積層型撮像素子及び本開示の第1の態様～第2の態様に係る固体撮像装置、並びに、固体撮像装置の駆動方法、全般に関する説明

本開示の撮像素子等にあっては、

半導体基板を更に備えており、

光電変換部は、半導体基板の上方に配置されている形態とすることができます。尚、第1電極、電荷蓄積用電極及び第2電極は、後述する駆動回路に接続されている。

##### 【0014】

光入射側に位置する第2電極は、複数の撮像素子において共通化されていてよい。即ち、第2電極を所謂ベタ電極とすることができます。光電変換層は、複数の撮像素子におい

て共通化されていてもよいし、即ち、複数の撮像素子において1層の光電変換層が形成されていてもよいし、撮像素子毎に設けられていてもよい。

#### 【0015】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、第1電極は、絶縁層に設けられた開口部内を延在し、光電変換層と接続されている形態とすることができる。あるいは又、光電変換層は、絶縁層に設けられた開口部内を延在し、第1電極と接続されている形態とすることができる、この場合、

第1電極の頂面の縁部は絶縁層で覆われており、

開口部の底面には第1電極が露出しており、

第1電極の頂面と接する絶縁層の面を第1面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第2面としたとき、開口部の側面は、第1面から第2面に向かって広がる傾斜を有する形態とすることができます、更には、第1面から第2面に向かって広がる傾斜を有する開口部の側面は、電荷蓄積用電極側に位置する形態とすることができます。尚、光電変換層と第1電極との間に他の層が形成されている形態（例えば、光電変換層と第1電極との間に電荷蓄積に適した材料層が形成されている形態）を包含する。

#### 【0016】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第1電極及び電荷蓄積用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第1電極に電位V11が印加され、電荷蓄積用電極に電位V12が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第1電極に電位V21が印加され、電荷蓄積用電極に電位V22が印加され、光電変換層に蓄積された電荷が第1電極を経由して制御部に読み出される構成とすることができます。但し、第1電極の電位が第2電極の電位よりも高い場合、

$V_{12} > V_{11}$ 、且つ、 $V_{22} < V_{21}$

であり、第1電極の電位が第2電極の電位よりも低い場合、

$V_{12} < V_{11}$ 、且つ、 $V_{22} > V_{21}$

である。

#### 【0017】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等にあっては、第1電極と電荷蓄積用電極との間に、第1電極及び電荷蓄積用電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された転送制御用電極（電荷転送電極）を更に備えている形態とすることができます。尚、このような形態の本開示の撮像素子等を、便宜上、『転送制御用電極を備えた本開示の撮像素子等』と呼ぶ。

#### 【0018】

また、転送制御用電極を備えた本開示の撮像素子等にあっては、

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第1電極、電荷蓄積用電極及び転送制御用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第1電極に電位V11が印加され、電荷蓄積用電極に電位V12が印加され、転送制御用電極に電位V13が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第1電極に電位V21が印加され、電荷蓄積用電極に電位V22が印加され、転送制御用電極に電位V23が印加され、光電変換層に蓄積された電荷が第1電極を介して制御部に読み出される構成とすることができます。但し、第1電極の電位が第2電極の電位よりも高い場合、

$V_{12} > V_{13}$ 、且つ、 $V_{22} < V_{23}$   $V_{21}$

であり、第1電極の電位が第2電極の電位よりも低い場合、

$V_{12} < V_{13}$ 、且つ、 $V_{22} > V_{23}$   $V_{21}$

である。

10

20

30

40

50

## 【0019】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等にあっては、光電変換層に接続され、第1電極及び電荷蓄積用電極と離間して配置された電荷排出電極を更に備えている形態とすることができます。尚、このような形態の本開示の撮像素子等を、便宜上、『電荷排出電極を備えた本開示の撮像素子等』と呼ぶ。そして、電荷排出電極を備えた本開示の撮像素子等において、電荷排出電極は、第1電極及び電荷蓄積用電極を取り囲むように（即ち、額縁状に）配置されている形態とすることができます。電荷排出電極は、複数の撮像素子において共有化（共通化）することができる。そして、この場合、

光電変換層は、絶縁層に設けられた第2開口部内を延在し、電荷排出電極と接続されており、

電荷排出電極の頂面の縁部は絶縁層で覆われており、

第2開口部の底面には電荷排出電極が露出しており、

電荷排出電極の頂面と接する絶縁層の面を第3面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第2面としたとき、第2開口部の側面は、第3面から第2面向かって広がる傾斜を有する形態とすることができます。

## 【0020】

更には、電荷排出電極を備えた本開示の撮像素子等にあっては、

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第1電極、電荷蓄積用電極及び電荷排出電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第1電極に電位V11が印加され、電荷蓄積用電極に電位V12が印加され、電荷排出電極に電位V14が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第1電極に電位V21が印加され、電荷蓄積用電極に電位V22が印加され、電荷排出電極に電位V24が印加され、光電変換層に蓄積された電荷が第1電極を介して制御部に読み出される構成とすることができます。但し、第1電極の電位が第2電極の電位よりも高い場合、

$V14 > V11$ 、且つ、 $V24 < V21$

であり、第1電極の電位が第2電極の電位よりも低い場合、

$V14 < V11$ 、且つ、 $V24 > V21$

である。

## 【0021】

更には、本開示の撮像素子等における以上に説明した各種の好ましい形態、構成において、電荷蓄積用電極は、複数の電荷蓄積用電極セグメントから構成されている形態とすることができます。尚、このような形態の本開示の撮像素子等を、便宜上、『複数の電荷蓄積用電極セグメントを備えた本開示の撮像素子等』と呼ぶ。電荷蓄積用電極セグメントの数は、2以上であればよい。そして、複数の電荷蓄積用電極セグメントを備えた本開示の撮像素子等にあっては、

第1電極の電位が第2電極の電位よりも高い場合、電荷転送期間において、第1電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第1電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも高く、

第1電極の電位が第2電極の電位よりも低い場合、電荷転送期間において、第1電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第1電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも低い形態とすることができます。

## 【0022】

以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、

半導体基板には、制御部を構成する少なくとも浮遊拡散層及び増幅トランジスタが設けられており、

第1電極は、浮遊拡散層及び増幅トランジスタのゲート部に接続されている構成とする

10

20

30

40

50

ことができ、この場合、更には、

半導体基板には、更に、制御部を構成するリセット・トランジスタ及び選択トランジスタが設けられており、

浮遊拡散層は、リセット・トランジスタの一方のソース／ドレイン領域に接続されており、

増幅トランジスタの一方のソース／ドレイン領域は、選択トランジスタの一方のソース／ドレイン領域に接続されており、選択トランジスタの他方のソース／ドレイン領域は信号線に接続されている構成とすることができる。

#### 【0023】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、電荷蓄積用電極の大きさは第1電極よりも大きい形態とすることができる。電荷蓄積用電極の面積をS1'、第1電極の面積をS1としたとき、限定するものではないが、

4 S1' / S1

を満足することが好ましい。

#### 【0024】

更には、以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、第2電極側から光が入射し、第2電極よりの光入射側には遮光層が形成されている形態とすることができる。あるいは又、第2電極側から光が入射し、第1電極（場合によっては、第1電極及び転送制御用電極）には光が入射しない形態とすることができ、この場合、第2電極よりの光入射側であって、第1電極（場合によっては、第1電極及び転送制御用電極）の上方には遮光層が形成されている構成とすることができ、あるいは又、

電荷蓄積用電極及び第2電極の上方にはオンチップ・マイクロ・レンズが設けられており、

オンチップ・マイクロ・レンズに入射する光は、電荷蓄積用電極に集光される構成とすることができる。ここで、遮光層は、第2電極の光入射側の面よりも上方に配設されてもよいし、第2電極の光入射側の面の上に配設されてもよい。場合によっては、第2電極に遮光層が形成されていてもよい。遮光層を構成する材料として、クロム(Cr)や銅(Cu)、アルミニウム(Al)、タングステン(W)、光を通さない樹脂(例えば、ポリイミド樹脂)を例示することができる。

#### 【0025】

本開示の撮像素子として、具体的には、青色の光(425nm乃至495nmの光)を吸収する光電変換層(便宜上、『第1タイプの青色光電変換層』と呼ぶ)を備えた青色に感度を有する撮像素子(便宜上、『第1タイプの青色用撮像素子』と呼ぶ)、緑色の光(495nm乃至570nmの光)を吸収する光電変換層(便宜上、『第1タイプの緑色光電変換層』と呼ぶ)を備えた緑色に感度を有する撮像素子(便宜上、『第1タイプの緑色用撮像素子』と呼ぶ)、赤色の光(620nm乃至750nmの光)を吸収する光電変換層(便宜上、『第1タイプの赤色光電変換層』と呼ぶ)を備えた赤色に感度を有する撮像素子(便宜上、『第1タイプの赤色用撮像素子』と呼ぶ)を挙げることができる。また、電荷蓄積用電極を備えていない従来の撮像素子であって、青色に感度を有する撮像素子を、便宜上、『第2タイプの青色用撮像素子』と呼び、緑色に感度を有する撮像素子を、便宜上、『第2タイプの緑色用撮像素子』と呼び、赤色に感度を有する撮像素子を、便宜上、『第2タイプの赤色用撮像素子』と呼び、第2タイプの青色用撮像素子を構成する光電変換層を、便宜上、『第2タイプの青色光電変換層』と呼び、第2タイプの緑色用撮像素子を構成する光電変換層を、便宜上、『第2タイプの緑色光電変換層』と呼び、第2タイプの赤色用撮像素子を構成する光電変換層を、便宜上、『第2タイプの赤色光電変換層』と呼ぶ。

#### 【0026】

本開示の積層型撮像素子は、少なくとも本開示の撮像素子(光電変換素子)を1つ有するが、具体的には、例えば、

[A] 第1タイプの青色用光電変換部、第1タイプの緑色用光電変換部及び第1タイプの

10

20

30

40

50

赤色用光電変換部が、垂直方向に積層され、

第1タイプの青色用撮像素子、第1タイプの緑色用撮像素子及び第1タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[B] 第1タイプの青色用光電変換部及び第1タイプの緑色用光電変換部が、垂直方向に積層され、

これらの2層の第1タイプの光電変換部の下方に、第2タイプの赤色用光電変換部が配置され、

第1タイプの青色用撮像素子、第1タイプの緑色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[C] 第1タイプの緑色用光電変換部の下方に、第2タイプの青色用光電変換部及び第2タイプの赤色用光電変換部が配置され、

第1タイプの緑色用撮像素子、第2タイプの青色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[D] 第1タイプの青色用光電変換部の下方に、第2タイプの緑色用光電変換部及び第2タイプの赤色用光電変換部が配置され、

第1タイプの青色用撮像素子、第2タイプの緑色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造を挙げることができる。尚、これらの撮像素子の光電変換部の垂直方向における配置順は、光入射方向から青色用光電変換部、緑色用光電変換部、赤色用光電変換部の順、あるいは、光入射方向から緑色用光電変換部、青色用光電変換部、赤色用光電変換部の順であることが好ましい。これは、より短い波長の光がより入射表面側において効率良く吸収されるからである。赤色は3色の中では最も長い波長であるので、光入射面から見て赤色用光電変換部を最下層に位置させることが好ましい。これらの撮像素子の積層構造によって、1つの画素が構成される。また、第1タイプの赤外線用光電変換部を備えていてもよい。ここで、第1タイプの赤外線用光電変換部の光電変換層は、例えば、有機系材料から構成され、第1タイプの撮像素子の積層構造の最下層であって、第2タイプの撮像素子よりも上に配置することが好ましい。あるいは又、第1タイプの光電変換部の下方に、第2タイプの赤外線用光電変換部を備えていてもよい。

#### 【0027】

第1タイプの撮像素子にあっては、例えば、第1電極が、半導体基板の上に設けられた層間絶縁層上に形成されている。半導体基板に形成された撮像素子は、裏面照射型とすることもできるし、表面照射型とすることもできる。

#### 【0028】

光電変換層を有機系材料から構成する場合、光電変換層を、

(1) p型有機半導体から構成する。

(2) n型有機半導体から構成する。

(3) p型有機半導体層 / n型有機半導体層の積層構造から構成する。p型有機半導体層 / p型有機半導体とn型有機半導体との混合層(バルクヘテロ構造) / n型有機半導体層の積層構造から構成する。p型有機半導体層 / p型有機半導体とn型有機半導体との混合層(バルクヘテロ構造)の積層構造から構成する。n型有機半導体層 / p型有機半導体とn型有機半導体との混合層(バルクヘテロ構造)の積層構造から構成する。

(4) p型有機半導体とn型有機半導体の混合(バルクヘテロ構造)から構成する。

の4態様のいずれかとすることができます。但し、積層順は任意に入れ替えた構成とすることができる。

#### 【0029】

p型有機半導体として、ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、ピレン誘導体、ペリレン誘導体、テトラセン誘導体、ペンタセン誘導体、キナクリドン誘導体、チオフェン誘導体、チエノチオフェン誘導体、ベンゾチオフェン誘導体、ベンゾチエノベンゾチオフェン誘導体、トリアリルアミン誘導体、カルバゾール誘導体、ペリレン誘導体、ピセン誘導体、クリセン誘導体、フルオランテン誘導体、フタロシアニン誘

10

20

30

40

50

導体、サブフタロシアニン誘導体、サブポルフィラジン誘導体、複素環化合物を配位子とする金属錯体、ポリチオフェン誘導体、ポリベンゾチアジアゾール誘導体、ポリフルオレン誘導体等を挙げることができる。n型有機半導体として、フラーレン及びフラーレン誘導体 例えは、C60や、C70, C74等のフラーレン(高次フラーレン)、内包フラーレン等)又はフラーレン誘導体(例えは、フラーレンフッ化物やPCBMフラーレン化合物、フラーレン多量体等)、p型有機半導体よりもHOMO及びLUMOが大きい(深い)有機半導体、透明な無機金属酸化物を挙げができる。n型有機半導体として、具体的には、窒素原子、酸素原子、硫黄原子を含有する複素環化合物、例えは、ピリジン誘導体、ピラジン誘導体、ピリミジン誘導体、トリアジン誘導体、キノリン誘導体、キノキサリン誘導体、イソキノリン誘導体、アクリジン誘導体、フェナジン誘導体、フェナントロリン誘導体、テトラゾール誘導体、ピラゾール誘導体、イミダゾール誘導体、チアゾール誘導体、オキサゾール誘導体、イミダゾール誘導体、ベンズイミダゾール誘導体、ベンゾトリアゾール誘導体、ベンズオキサゾール誘導体、ベンズオキサゾール誘導体、カルバゾール誘導体、ベンゾフラン誘導体、ジベンゾフラン誘導体、サブポルフィラジン誘導体、ポリフェニレンビニレン誘導体、ポリベンゾチアジアゾール誘導体、ポリフルオレン誘導体等を分子骨格の一部に有する有機分子、有機金属錯体やサブフタロシアニン誘導体を挙げができる。フラーレン誘導体に含まれる基等として、ハロゲン原子；直鎖、分岐若しくは環状のアルキル基若しくはフェニル基；直鎖若しくは縮環した芳香族化合物を有する基；ハロゲン化物を有する基；パーキャルフルオロアルキル基；パーフルオロアルキル基；シリルアルキル基；シリルアルコキシ基；アリールシリル基；アリールスルファニル基；アルキルスルファニル基；アリールスルホニル基；アルキルスルホニル基；アリールスルフィド基；アルキルスルフィド基；アミノ基；アルキルアミノ基；アリールアミノ基；ヒドロキシ基；アルコキシ基；アシルアミノ基；アシルオキシ基；カルボニル基；カルボキシ基；カルボキソアミド基；カルボアルコキシ基；アシル基；スルホニル基；シアノ基；ニトロ基；カルコゲン化物を有する基；ホスフィン基；ホスホン基；これらの誘導体を挙げができる。有機系材料から構成された光電変換層(『有機光電変換層』と呼ぶ場合がある)の厚さは、限定するものではないが、例えは、1×10-8m乃至5×10-7m、好ましくは2.5×10-8m乃至3×10-7m、より好ましくは2.5×10-8m乃至2×10-7m、一層好ましくは1×10-7m乃至1.8×10-7mを例示することができる。尚、有機半導体は、p型、n型と分類されることが多いが、p型とは正孔を輸送しやすいという意味であり、n型とは電子を輸送しやすいという意味であり、無機半導体のように熱励起の多数キャリアとして正孔又は電子を有しているという解釈に限定されない。

### 【0030】

あるいは又、緑色の波長の光を光電変換する有機光電変換層を構成する材料として、例えは、ローダミン系色素、メラシアニン系色素、キナクリドン誘導体、サブフタロシアニン系色素(サブフタロシアニン誘導体)等を挙げができるし、青色の光を光電変換する有機光電変換層を構成する材料として、例えは、クマリン酸色素、トリス-8-ヒドリキシキノリアルミニウム(A1q3)、メラシアニン系色素等を挙げができるし、赤色の光を光電変換する有機光電変換層を構成する材料として、例えは、フタロシアニン系色素、サブフタロシアニン系色素(サブフタロシアニン誘導体)を挙げができる。

### 【0031】

あるいは又、光電変換層を構成する無機系材料として、結晶シリコン、アモルファスシリコン、微結晶シリコン、結晶セレン、アモルファスセレン、及び、カルコパライト系化合物であるCIGS(CuInGaSe)、CIS(CuInSe<sub>2</sub>)、CuInS<sub>2</sub>、CuAlS<sub>2</sub>、CuAlSe<sub>2</sub>、CuGaS<sub>2</sub>、CuGaSe<sub>2</sub>、AgAlS<sub>2</sub>、AgAlSe<sub>2</sub>、AgInS<sub>2</sub>、AgInSe<sub>2</sub>、あるいは又、III-V族化合物であるGaAs、InP、AlGaAs、InGaP、AlGaInP、InGaAsP、更には、CdSe、CdS、In<sub>2</sub>Se<sub>3</sub>、In<sub>2</sub>S<sub>3</sub>、Bi<sub>2</sub>Se<sub>3</sub>、Bi<sub>2</sub>S<sub>3</sub>、ZnSe、ZnS、PbS

10

20

30

40

50

e、PbS等の化合物半導体を挙げることができる。加えて、これらの材料から成る量子ドットを光電変換層に使用することも可能である。

#### 【0032】

あるいは又、光電変換層を、下層半導体層と、上層光電変換層の積層構造とすることができます。このように下層半導体層を設けることで、電荷蓄積時の再結合を防止することができ、光電変換層に蓄積した電荷の第1電極への転送効率を増加させることができるとし、暗電流の生成を抑制することができる。上層光電変換層を構成する材料は、上記の光電変換層を構成する各種材料から、適宜、選択すればよい。一方、下層半導体層を構成する材料として、バンドギャップエネルギーの値が大きく（例えば、3.0 eV以上のバンドギャップエネルギーの値）、しかも、光電変換層を構成する材料よりも高い移動度を有する材料を用いることが好ましい。具体的には、IGZO等の酸化物半導体材料；遷移金属ダイカルコゲナイト；シリコンカーバイド；ダイヤモンド；グラフェン；カーボンナノチューブ；縮合多環炭化水素化合物や縮合複素環化合物等の有機半導体材料を挙げることができる。あるいは又、下層半導体層を構成する材料として、蓄積すべき電荷が正孔である場合、光電変換層を構成する材料のイオン化ポテンシャルよりも小さなイオン化ポテンシャルを有する材料を挙げることができるし、蓄積すべき電荷が電子である場合、光電変換層を構成する材料の電子親和力よりも大きな電子親和力を有する材料を挙げができる。あるいは又、下層半導体層を構成する材料における不純物濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 以下であることが好ましい。下層半導体層は、単層構成であってもよいし、多層構成であってもよい。また、電荷蓄積用電極の上方に位置する下層半導体層を構成する材料と、第1電極の上方に位置する下層半導体層を構成する材料とを、異ならせててもよい。

10

20

#### 【0033】

本開示の第1の態様～第2の態様に係る固体撮像装置によって、単板式カラー固体撮像装置を構成することができる。

#### 【0034】

積層型撮像素子を備えた本開示の第2の態様に係る固体撮像装置にあっては、ベイヤ配列の撮像素子を備えた固体撮像装置と異なり（即ち、カラーフィルタを用いて青色、緑色、赤色の分光を行うのではなく）、同一画素内で光の入射方向において、複数種の波長の光に対して感度を有する撮像素子を積層して1つの画素を構成するので、感度の向上及び単位体積当たりの画素密度の向上を図ることができる。また、有機系材料は吸収係数が高いいため、有機光電変換層の膜厚を従来のSi系光電変換層と比較して薄くすることができ、隣接画素からの光漏れや、光の入射角の制限が緩和される。更には、従来のSi系撮像素子では3色の画素間で補間処理を行って色信号を作成するために偽色が生じるが、積層型撮像素子を備えた本開示の第2の態様に係る固体撮像装置にあっては、偽色の発生が抑えられる。有機光電変換層それ自体がカラーフィルタとしても機能するので、カラーフィルタを配設しなくとも色分離が可能である。

30

#### 【0035】

一方、本開示の第1の態様に係る固体撮像装置にあっては、カラーフィルタを用いることで、青色、緑色、赤色の分光特性への要求を緩和することができるし、また、高い量産性を有する。本開示の第1の態様に係る固体撮像装置における撮像素子の配列として、ベイヤ配列の他、インターライン配列、GストライプRB市松配列、GストライプRB完全市松配列、市松補色配列、ストライプ配列、斜めストライプ配列、原色色差配列、フィールド色差順次配列、フレーム色差順次配列、MOS型配列、改良MOS型配列、フレームインターリープ配列、フィールドインターリープ配列を挙げることができる。ここで、1つの撮像素子によって1つの画素（あるいは副画素）が構成される。

40

#### 【0036】

本開示の撮像素子あるいは本開示の積層型撮像素子が複数配列された画素領域は、2次元アレイ状に規則的に複数配列された画素から構成される。画素領域は、通常、実際に光を受光し光電変換によって生成された信号電荷を増幅して駆動回路に読み出す有効画素領域と、黒レベルの基準になる光学的黒を出力するための黒基準画素領域とから構成されて

50

いる。黒基準画素領域は、通常は、有効画素領域の外周部に配置されている。

### 【0037】

以上に説明した各種の好ましい形態、構成を含む本開示の撮像素子等において、光が照射され、光電変換層で光電変換が生じ、正孔（ホール）と電子がキャリア分離される。そして、正孔が取り出される電極を陽極、電子が取り出される電極を陰極とする。第1電極が陽極を構成し、第2電極が陰極を構成する形態もあるし、逆に、第1電極が陰極を構成し、第2電極が陽極を構成する形態もある。

### 【0038】

積層型撮像素子を構成する場合、第1電極、電荷蓄積用電極、転送制御用電極、電荷排出電極及び第2電極は透明導電材料から成る構成とすることができます。尚、第1電極、電荷蓄積用電極、転送制御用電極及び電荷排出電極を総称して、『第1電極等』と呼ぶ場合がある。あるいは又、本開示の撮像素子等が、例えばベイヤ配列のように平面に配される場合には、第2電極は透明導電材料から成り、第1電極は金属材料から成る構成とすることができます。この場合、具体的には、光入射側に位置する第2電極は透明導電材料から成り、第1電極等は、例えば、A1-Nd（アルミニウム及びネオジウムの合金）又はASC（アルミニウム、サマリウム及び銅の合金）から成る構成とすることができます。尚、透明導電材料から成る電極を『透明電極』と呼ぶ場合がある。ここで、透明導電材料のバンドギャップエネルギーは、2.5eV以上、好ましくは3.1eV以上であることが望ましい。透明電極を構成する透明導電材料として、導電性のある金属酸化物を挙げることができ、具体的には、酸化インジウム、インジウム-錫酸化物（ITO, Indium Tin Oxide, SnドープのIn2O3、結晶性ITO及びアモルファスITOを含む）、酸化亜鉛にドーパントとしてインジウムを添加したインジウム-亜鉛酸化物（IZO, Indium Zinc Oxide）、酸化ガリウムにドーパントとしてインジウムを添加したインジウム-ガリウム酸化物（IGO）、酸化亜鉛にドーパントとしてインジウムとガリウムを添加したインジウム-ガリウム-亜鉛酸化物（IGZO, In-Ga-ZnO4）、酸化亜鉛にドーパントとしてインジウムと錫を添加したインジウム-錫-亜鉛酸化物（ITZO）、IFO（FドープのIn2O3）、酸化錫（SnO2）、ATO（SbドープのSnO2）、FTO（FドープのSnO2）、酸化亜鉛（他元素をドープしたZnOを含む）、酸化亜鉛にドーパントとしてアルミニウムを添加したアルミニウム-亜鉛酸化物（AZO）、酸化亜鉛にドーパントとしてガリウムを添加したガリウム-亜鉛酸化物（GZO）、酸化チタン（TiO2）、酸化チタンにドーパントとしてニオブを添加したニオブ-チタン酸化物（TNO）、酸化アンチモン、スピネル型酸化物、YbFe2O4構造を有する酸化物を例示することができます。あるいは又、ガリウム酸化物、チタン酸化物、ニオブ酸化物、ニッケル酸化物等を母層とする透明電極を挙げることができる。透明電極の厚さとして、2×10-8m乃至2×10-7m、好ましくは3×10-8m乃至1×10-7mを挙げることができる。第1電極が透明性を要求される場合、製造プロセスの簡素化といった観点から、電荷排出電極も透明導電材料から構成することが好ましい。

### 【0039】

あるいは又、透明性が不要である場合、正孔を取り出す電極としての機能を有する陽極を構成する導電材料として、高仕事関数（例えば、=4.5eV~5.5eV）を有する導電材料から構成することが好ましく、具体的には、金（Au）、銀（Ag）、クロム（Cr）、ニッケル（Ni）、パラジウム（Pd）、白金（Pt）、鉄（Fe）、イリジウム（Ir）、ゲルマニウム（Ge）、オスミウム（Os）、レニウム（Re）、テルル（Te）を例示することができる。一方、電子を取り出す電極としての機能を有する陰極を構成する導電材料として、低仕事関数（例えば、=3.5eV~4.5eV）を有する導電材料から構成することが好ましく、具体的には、アルカリ金属（例えばLi、Na、K等）及びそのフッ化物又は酸化物、アルカリ土類金属（例えばMg、Ca等）及びそのフッ化物又は酸化物、アルミニウム（Al）、亜鉛（Zn）、錫（Sn）、タリウム（Tl）、ナトリウム-カリウム合金、アルミニウム-リチウム合金、マグネシウム-銀合金、インジウム、イッテリビウム等の希土類金属、あるいは、これらの合金を挙げること

10

20

30

40

50

ができる。あるいは又、陽極や陰極を構成する材料として、白金( P t )、金( A u )、パラジウム( P d )、クロム( C r )、ニッケル( N i )、アルミニウム( A l )、銀( A g )、タンタル( T a )、タングステン( W )、銅( C u )、チタン( T i )、インジウム( I n )、錫( S n )、鉄( F e )、コバルト( C o )、モリブデン( M o )等の金属、あるいは、これらの金属元素を含む合金、これらの金属から成る導電性粒子、これらの金属を含む合金の導電性粒子、不純物を含有したポリシリコン、炭素系材料、酸化物半導体、カーボン・ナノ・チューブ、グラフェン等の導電性材料を挙げることができるし、これらの元素を含む層の積層構造とすることもできる。更には、陽極や陰極を構成する材料として、ポリ( 3 , 4 - エチレンジオキシチオフェン ) / ポリスチレンスルホン酸 [ P E D O T / P S S ] といった有機材料( 導電性高分子 )を挙げることもできる。また、これらの導電性材料をバインダー( 高分子 )に混合してペースト又はインクとしたものを硬化させ、電極として用いてよい。

#### 【 0 0 4 0 】

第1電極等や第2電極( 陽極や陰極 )の成膜方法として、乾式法あるいは湿式法を用いることが可能である。乾式法として、物理的気相成長法( P V D 法)及び化学的気相成長法( C V D 法)を挙げることができる。P V D 法の原理を用いた成膜方法として、抵抗加熱あるいは高周波加熱を用いた真空蒸着法、E B ( 電子ビーム ) 蒸着法、各種スパッタリング法( マグネットロンスパッタリング法、R F - D C 結合形バイアススパッタリング法、E C R スパッタリング法、対向ターゲットスパッタリング法、高周波スパッタリング法 ) 、イオンプレーティング法、レーザーアブレーション法、分子線エピタキシー法、レーザー転写法を挙げることができる。また、C V D 法として、プラズマ C V D 法、熱 C V D 法、有機金属( M O ) C V D 法、光 C V D 法を挙げができる。一方、湿式法として、電解メッキ法や無電解メッキ法、スピンドルコート法、インクジェット法、スプレー コート法、スタンプ法、マイクロコンタクトプリント法、フレキソ印刷法、オフセット印刷法、グラビア印刷法、ディップ法等の方法を挙げができる。パターニング法として、シャドーマスク、レーザー転写、フォトリソグラフィー等の化学的エッチング、紫外線やレーザー等による物理的エッチング等を挙げができる。第1電極等や第2電極の平坦化技術として、レーザー平坦化法、リフロー法、C M P ( Chemical Mechanical Polishing ) 法等を用いることができる。

#### 【 0 0 4 1 】

絶縁層を構成する材料として、酸化ケイ素系材料；窒化ケイ素( S i N Y ) ; 酸化アルミニウム( A l 2 O 3 ) 等の金属酸化物高誘電絶縁材料に例示される無機系絶縁材料だけでなく、ポリメチルメタクリレート( P M M A ) ; ポリビニルフェノール( P V P ) ; ポリビニルアルコール( P V A ) ; ポリイミド ; ポリカーボネート( P C ) ; ポリエチレンテレフタレート( P E T ) ; ポリスチレン ; N - 2 ( アミノエチル ) 3 - アミノプロピルトリメトキシシラン( A E A P T M S ) 、3 - メルカブトプロピルトリメトキシシラン( M P T M S ) 、オクタデシルトリクロロシラン( O T S ) 等のシラノール誘導体( シランカップリング剤 ) ; ノボラック型フェノール樹脂 ; フッ素系樹脂 ; オクタデカンチオール、ドデシルイソシアネイト等の一端に制御電極と結合可能な官能基を有する直鎖炭化水素類にて例示される有機系絶縁材料( 有機ポリマー )を挙げができるし、これらの組み合わせを用いることもできる。尚、酸化ケイ素系材料として、酸化シリコン( S i O X ) 、B P S G 、P S G 、B S G 、A s S G 、P b S G 、酸化窒化シリコン( S i O N ) 、S O G ( スピンオングラス ) 、低誘電率材料( 例えば、ポリアリールエーテル、シクロパーカルオロカーボンポリマー及びベンゾシクロブテン、環状フッ素樹脂、ポリテトラフルオロエチレン、フッ化アリールエーテル、フッ化ポリイミド、アモルファスカーボン、有機 S O G ) を例示することができる。各種層間絶縁層や絶縁膜を構成する材料も、これらの材料から適宜選択すればよい。

#### 【 0 0 4 2 】

制御部を構成する浮遊拡散層、増幅トランジスタ、リセット・トランジスタ及び選択トランジスタの構成、構造は、従来の浮遊拡散層、増幅トランジスタ、リセット・トランジ

スタ及び選択トランジスタの構成、構造と同様とすることができます。駆動回路も周知の構成、構造とすることができます。

#### 【 0 0 4 3 】

第1電極は、浮遊拡散層及び増幅トランジスタのゲート部に接続されているが、第1電極と浮遊拡散層及び増幅トランジスタのゲート部との接続のためにコンタクトホール部を形成すればよい。コンタクトホール部を構成する材料として、不純物がドーピングされたポリシリコンや、タンゲステン、Ti、Pt、Pd、Cu、TiW、TiN、TiNW、WSi2、MoSi2等の高融点金属や金属シリサイド、これらの材料から成る層の積層構造（例えば、Ti/TiN/W）を例示することができる。

#### 【 0 0 4 4 】

有機光電変換層と第1電極との間に、第1キャリアプロッキング層を設けてもよいし、有機光電変換層と第2電極との間に、第2キャリアプロッキング層を設けてもよい。また、第1キャリアプロッキング層と第1電極との間に第1電荷注入層を設けてもよいし、第2キャリアプロッキング層と第2電極との間に第2電荷注入層を設けてもよい。例えば、電子注入層を構成する材料として、例えば、リチウム(Li)、ナトリウム(Na)、カリウム(K)といったアルカリ金属及びそのフッ化物や酸化物、マグネシウム(Mg)、カルシウム(Ca)といったアルカリ土類金属及びそのフッ化物や酸化物を挙げることができる。

#### 【 0 0 4 5 】

各種有機層の成膜方法として、乾式成膜法及び湿式成膜法を挙げることができる。乾式成膜法として、抵抗加熱あるいは高周波加熱、電子ビーム加熱を用いた真空蒸着法、フラッシュ蒸着法、プラズマ蒸着法、EB蒸着法、各種スパッタリング法（2極スパッタリング法、直流スパッタリング法、直流マグネットロンスパッタリング法、高周波スパッタリング法、マグネットロンスパッタリング法、RF-DC結合形バイアススパッタリング法、ECRスパッタリング法、対向ターゲットスパッタリング法、高周波スパッタリング法、イオンビームスパッタリング法）、DC(Direct Current)法、RF法、多陰極法、活性化反応法、電界蒸着法、高周波イオンプレーティング法や反応性イオンプレーティング法等の各種イオンプレーティング法、レーザーアブレーション法、分子線エピタキシー法、レーザー転写法、分子線エピタキシー法(MBE法)を挙げることができる。また、CVD法として、プラズマCVD法、熱CVD法、MOCVD法、光CVD法を挙げができる。一方、湿式法として、具体的には、スピンドル法；浸漬法；キャスト法；マイクロコンタクトプリント法；ドロップキャスト法；クリーン印刷法やインクジェット印刷法、オフセット印刷法、グラビア印刷法、フレキソ印刷法といった各種印刷法；スタンプ法；スプレー法；エアドクターター法、ブレードコーラー法、ロッドコーラー法、ナイフコーラー法、スクイズコーラー法、リバースロールコーラー法、トランスファーロールコーラー法、グラビアコーラー法、キスコーラー法、キャストコーラー法、スプレーコーラー法、スリットオリフィスコーラー法、カレンダーコーラー法といった各種コーティング法を例示することができる。尚、塗布法においては、溶媒として、トルエン、クロロホルム、ヘキサン、エタノールといった無極性又は極性の低い有機溶媒を例示することができる。パターニング法として、シャドーマスク、レーザー転写、フォトリソグラフィー等の化学的エッチング、紫外線やレーザー等による物理的エッチング等を挙げることができる。各種有機層の平坦化技術として、レーザー平坦化法、リフロー法等を用いることができる。

#### 【 0 0 4 6 】

撮像素子あるいは固体撮像装置には、前述したとおり、必要に応じて、オンチップ・マイクロ・レンズや遮光層を設けてもよいし、撮像素子を駆動するための駆動回路や配線が設けられている。必要に応じて、撮像素子への光の入射を制御するためのシャッターを配設してもよいし、固体撮像装置の目的に応じて光学カットフィルタを具備してもよい。

#### 【 0 0 4 7 】

例えば、固体撮像装置を読み出し用集積回路(ROIC)と積層する場合、読み出し用集積

10

20

30

40

50

回路及び銅（Cu）から成る接続部が形成された駆動用基板と、接続部が形成された撮像素子とを、接続部同士が接するように重ね合わせ、接続部同士を接合することで、積層することができるし、接続部同士をハンダバンプ等を用いて接合することもできる。

**【実施例 1】**

**【0048】**

実施例 1 は、本開示の撮像素子、本開示の積層型撮像素子、及び、本開示の第 2 の態様に係る固体撮像装置に関する。

**【0049】**

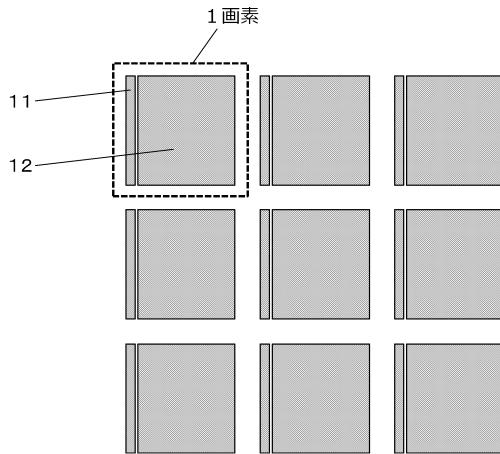

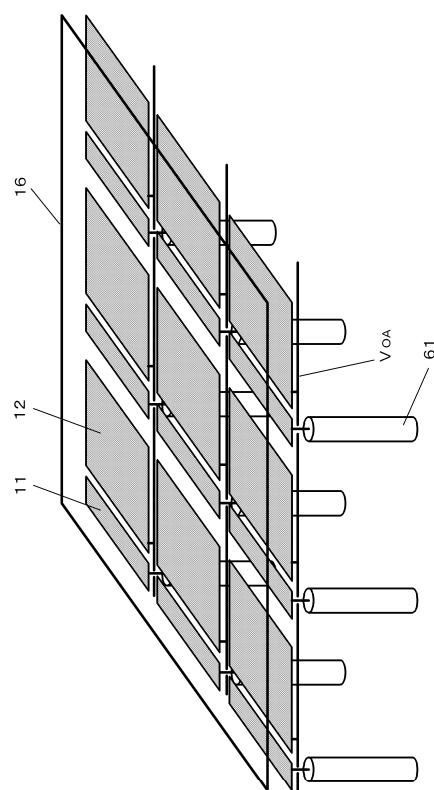

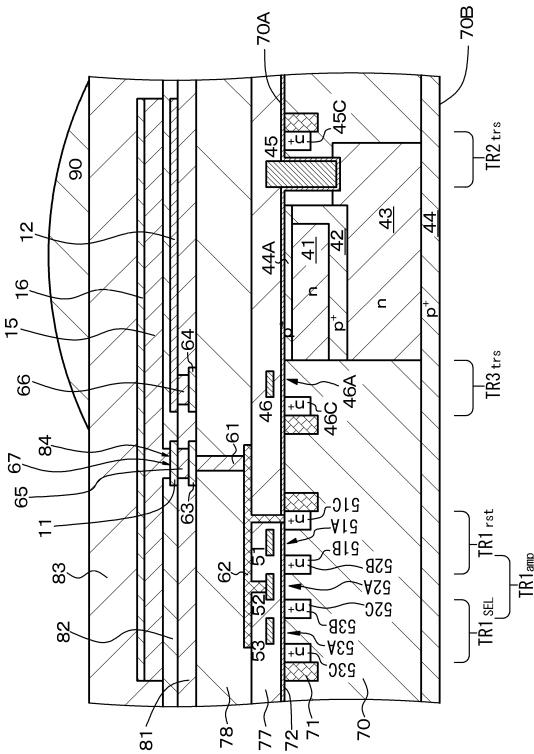

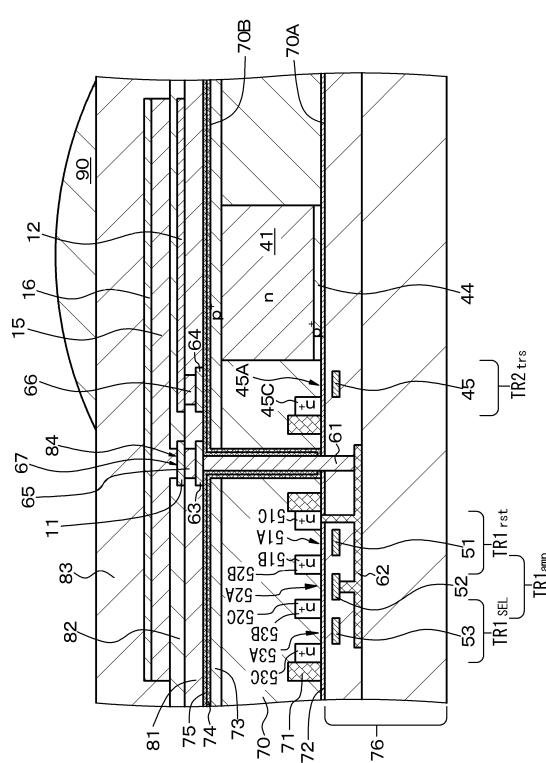

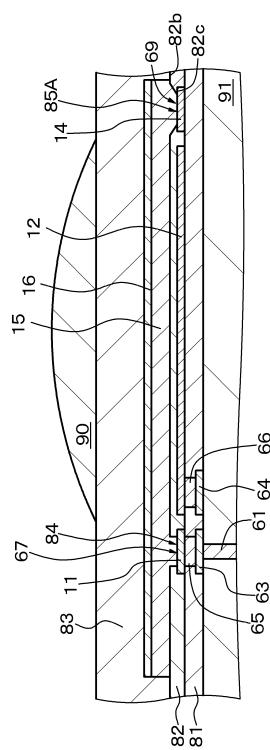

実施例 1 の撮像素子、積層型撮像素子の模式的な一部断面図を図 1 に示し、実施例 1 の撮像素子、積層型撮像素子の等価回路図を図 2 及び図 3 に示し、実施例 1 の撮像素子を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 4 に示し、実施例 1 の撮像素子の動作時の各部位における電位の状態を模式的に図 5 に示す。また、実施例 1 の撮像素子を構成する第 1 電極及び電荷蓄積用電極の模式的な配置図を図 6 に示し、実施例 1 の撮像素子を構成する第 1 電極、電荷蓄積用電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図を図 7 に示し、実施例 1 の固体撮像装置の概念図を図 8 に示す。

10

**【0050】**

実施例 1 の撮像素子（例えば、後述する緑色用撮像素子）は、第 1 電極 11、光電変換層 15 及び第 2 電極 16 が積層されて成る光電変換部を備えており、光電変換部は、更に、第 1 電極 11 と離間して配置され、且つ、絶縁層 82 を介して光電変換層 15 と対向して配置された電荷蓄積用電極 12 を備えている。

20

**【0051】**

また、実施例 1 の積層型撮像素子は、実施例 1 の撮像素子を少なくとも 1 つ、実施例 1 にあっては実施例 1 の撮像素子を 1 つ、有する。

**【0052】**

更には、実施例 1 の固体撮像装置は、実施例 1 の積層型撮像素子を、複数、備えている。

**【0053】**

そして、半導体基板（より具体的には、シリコン半導体層）70 を更に備えており、光電変換部は、半導体基板 70 の上方に配置されている。また、半導体基板 70 に設けられ、第 1 電極 11 が接続された駆動回路を有する制御部を更に備えている。ここで、半導体基板 70 における光入射面を上方とし、半導体基板 70 の反対側を下方とする。半導体基板 70 の下方には複数の配線から成る配線層 62 が設けられている。また、半導体基板 70 には、制御部を構成する少なくとも浮遊拡散層 FD1 及び増幅トランジスタ TR1amp が設けられており、第 1 電極 11 は、浮遊拡散層 FD1 及び増幅トランジスタ TR1amp のゲート部に接続されている。半導体基板 70 には、更に、制御部を構成するリセット・トランジスタ TR1rst 及び選択トランジスタ TR1sel が設けられている。また、浮遊拡散層 FD1 は、リセット・トランジスタ TR1rst の一方のソース / ドレイン領域に接続されており、増幅トランジスタ TR1amp の一方のソース / ドレイン領域は、選択トランジスタ TR1sel の一方のソース / ドレイン領域に接続されており、選択トランジスタ TR1sel の他方のソース / ドレイン領域は信号線 VSL1 に接続されている。これらの増幅トランジスタ TR1amp、リセット・トランジスタ TR1rst 及び選択トランジスタ TR1sel は、駆動回路を構成する。

30

**【0054】**

具体的には、実施例 1 の撮像素子、積層型撮像素子は、裏面照射型の撮像素子、積層型撮像素子であり、緑色の光を吸収する第 1 タイプの緑色光電変換層を備えた緑色に感度を有する第 1 タイプの実施例 1 の緑色用撮像素子（以下、『第 1 撮像素子』と呼ぶ）、青色の光を吸収する第 2 タイプの青色光電変換層を備えた青色に感度を有する第 2 タイプの従来の青色用撮像素子（以下、『第 2 撮像素子』と呼ぶ）、赤色の光を吸収する第 2 タイプの赤色光電変換層を備えた赤色に感度を有する第 2 タイプの従来の赤色用撮像素子（以下、『第 3 撮像素子』と呼ぶ）の 3 つの撮像素子が積層された構造を有する。ここで赤色用

40

50

撮像素子（第3撮像素子）及び青色用撮像素子（第2撮像素子）は、半導体基板70内に設けられており、第2撮像素子の方が、第3撮像素子よりも光入射側に位置する。また、緑色用撮像素子（第1撮像素子）は、青色用撮像素子（第2撮像素子）の上方に設けられている。第1撮像素子、第2撮像素子及び第3撮像素子の積層構造によって、1画素が構成される。カラーフィルタは設けられていない。

#### 【0055】

第1撮像素子にあっては、層間絶縁層81上に、第1電極11及び電荷蓄積用電極12が、離間して形成されている。層間絶縁層81及び電荷蓄積用電極12は、絶縁層82によって覆われている。絶縁層82上には光電変換層15が形成され、光電変換層15上には第2電極16が形成されている。第2電極16を含む全面には、保護層83が形成されており、保護層83上にオンチップ・マイクロ・レンズ90が設けられている。第1電極11、電荷蓄積用電極12及び第2電極16は、例えば、ITOから成る透明電極から構成されている。光電変換層15は、少なくとも緑色に感度を有する周知の有機光電変換材料（例えば、ローダミン系色素、メラシアニン系色素、キナクリドン等の有機系材料）を含む層から構成されている。また、光電変換層15は、更に、電荷蓄積に適した材料層を含む構成であってもよい。即ち、光電変換層15と第1電極11との間に（例えば、接続部67内に）、更に、電荷蓄積に適した材料層が形成されていてもよい。層間絶縁層81や絶縁層82、保護層83は、周知の絶縁材料（例えば、SiO<sub>2</sub>やSiN）から構成されている。光電変換層15と第1電極11とは、絶縁層82に設けられた接続部67によって接続されている。接続部67内には、光電変換層15が延在している。即ち、光電変換層15は、絶縁層82に設けられた開口部84内を延在し、第1電極11と接続されている。

10

#### 【0056】

電荷蓄積用電極12は駆動回路に接続されている。具体的には、電荷蓄積用電極12は、層間絶縁層81内に設けられた接続孔66、パッド部64及び配線VOAを介して、駆動回路を構成する垂直駆動回路112に接続されている。

20

#### 【0057】

電荷蓄積用電極12の大きさは第1電極11よりも大きい。電荷蓄積用電極12の面積をS1'、第1電極11の面積をS1としたとき、限定するものではないが、

4 S1' / S1

30

を満足することが好ましく、実施例1にあっては、限定するものではないが、例えば、

$S1' / S1 = 8$

とした。

#### 【0058】

半導体基板70の第1面（おもて面）70Aの側には素子分離領域71が形成され、また、半導体基板70の第1面70Aには酸化膜72が形成されている。更には、半導体基板70の第1面側には、第1撮像素子の制御部を構成するリセット・トランジスタTR1rst、増幅トランジスタTR1amp及び選択トランジスタTR1selが設けられ、更に、第1浮遊拡散層FD1が設けられている。

#### 【0059】

リセット・トランジスタTR1rstは、ゲート部51、チャネル形成領域51A、及び、ソース／ドレイン領域51B、51Cから構成されている。リセット・トランジスタTR1rstのゲート部51はリセット線RST1に接続され、リセット・トランジスタTR1rstの一方のソース／ドレイン領域51Cは、第1浮遊拡散層FD1を兼ねており、他方のソース／ドレイン領域51Bは、電源VDDに接続されている。

40

#### 【0060】

第1電極11は、層間絶縁層81内に設けられた接続孔65、パッド部63、半導体基板70及び層間絶縁層76に形成されたコンタクトホール部61、層間絶縁層76に形成された配線層62を介して、リセット・トランジスタTR1rstの一方のソース／ドレイン領域51C（第1浮遊拡散層FD1）に接続されている。

50

**【 0 0 6 1 】**

増幅トランジスタ T R 1amp は、ゲート部 5 2 、チャネル形成領域 5 2 A 、及び、ソース / ドレイン領域 5 2 B , 5 2 C から構成されている。ゲート部 5 2 は配線層 6 2 を介して、第 1 電極 1 1 及びリセット・トランジスタ T R 1rst の一方のソース / ドレイン領域 5 1 C ( 第 1 浮遊拡散層 F D 1 ) に接続されている。また、一方のソース / ドレイン領域 5 2 B は、リセット・トランジスタ T R 1rst を構成する他方のソース / ドレイン領域 5 1 B と、領域を共有しており、電源 V DD に接続されている。

**【 0 0 6 2 】**

選択トランジスタ T R 1sel は、ゲート部 5 3 、チャネル形成領域 5 3 A 、及び、ソース / ドレイン領域 5 3 B , 5 3 C から構成されている。ゲート部 5 3 は、選択線 S E L 1 に接続されている。また、一方のソース / ドレイン領域 5 3 B は、増幅トランジスタ T R 1amp を構成する他方のソース / ドレイン領域 5 2 C と、領域を共有しており、他方のソース / ドレイン領域 5 3 C は、信号線 ( データ出力線 ) V S L 1 ( 1 1 7 ) に接続されている。

10

**【 0 0 6 3 】**

第 2 撮像素子は、半導体基板 7 0 に設けられた n 型半導体領域 4 1 を光電変換層として備えている。縦型トランジスタから成る転送トランジスタ T R 2trs のゲート部 4 5 が、 n 型半導体領域 4 1 まで延びてあり、且つ、転送ゲート線 T G 2 に接続されている。また、転送トランジスタ T R 2trs のゲート部 4 5 の近傍の半導体基板 7 0 の領域 4 5 C には、第 2 浮遊拡散層 F D 2 が設けられている。 n 型半導体領域 4 1 に蓄積された電荷は、ゲート部 4 5 に沿って形成される転送チャネルを介して第 2 浮遊拡散層 F D 2 に読み出される。

20

**【 0 0 6 4 】**

第 2 撮像素子にあっては、更に、半導体基板 7 0 の第 1 面側に、第 2 撮像素子の制御部を構成するリセット・トランジスタ T R 2rst 、増幅トランジスタ T R 2amp 及び選択トランジスタ T R 2sel が設けられている。

**【 0 0 6 5 】**

リセット・トランジスタ T R 2rst は、ゲート部、チャネル形成領域、及び、ソース / ドレイン領域から構成されている。リセット・トランジスタ T R 2rst のゲート部はリセット線 R S T 2 に接続され、リセット・トランジスタ T R 2rst の一方のソース / ドレイン領域は電源 V DD に接続され、他方のソース / ドレイン領域は、第 2 浮遊拡散層 F D 2 を兼ねている。

30

**【 0 0 6 6 】**

増幅トランジスタ T R 2amp は、ゲート部、チャネル形成領域、及び、ソース / ドレイン領域から構成されている。ゲート部は、リセット・トランジスタ T R 2rst の他方のソース / ドレイン領域 ( 第 2 浮遊拡散層 F D 2 ) に接続されている。また、一方のソース / ドレイン領域は、リセット・トランジスタ T R 2rst を構成する一方のソース / ドレイン領域と、領域を共有しており、電源 V DD に接続されている。

**【 0 0 6 7 】**

選択トランジスタ T R 2sel は、ゲート部、チャネル形成領域、及び、ソース / ドレイン領域から構成されている。ゲート部は、選択線 S E L 2 に接続されている。また、一方のソース / ドレイン領域は、増幅トランジスタ T R 2amp を構成する他方のソース / ドレイン領域と、領域を共有しており、他方のソース / ドレイン領域は、信号線 ( データ出力線 ) V S L 2 に接続されている。

40

**【 0 0 6 8 】**

第 3 撮像素子は、半導体基板 7 0 に設けられた n 型半導体領域 4 3 を光電変換層として備えている。転送トランジスタ T R 3trs のゲート部 4 6 は転送ゲート線 T G 3 に接続されている。また、転送トランジスタ T R 3trs のゲート部 4 6 の近傍の半導体基板 7 0 の領域 4 6 C には、第 3 浮遊拡散層 F D 3 が設けられている。 n 型半導体領域 4 3 に蓄積された電荷は、ゲート部 4 6 に沿って形成される転送チャネル 4 6 A を介して第 3 浮遊拡散層 F D 3 に読み出される。

**【 0 0 6 9 】**

50

第3撮像素子にあっては、更に、半導体基板70の第1面側に、第3撮像素子の制御部を構成するリセット・トランジスタTR3rst、増幅トランジスタTR3amp及び選択トランジスタTR3selが設けられている。

#### 【0070】

リセット・トランジスタTR3rstは、ゲート部、チャネル形成領域、及び、ソース／ドレイン領域から構成されている。リセット・トランジスタTR3rstのゲート部はリセット線RST3に接続され、リセット・トランジスタTR3rstの一方のソース／ドレイン領域は電源VDDに接続され、他方のソース／ドレイン領域は、第3浮遊拡散層FD3を兼ねている。

#### 【0071】

増幅トランジスタTR3ampは、ゲート部、チャネル形成領域、及び、ソース／ドレイン領域から構成されている。ゲート部は、リセット・トランジスタTR3rstの他方のソース／ドレイン領域（第3浮遊拡散層FD3）に接続されている。また、一方のソース／ドレイン領域は、リセット・トランジスタTR3rstを構成する一方のソース／ドレイン領域と、領域を共有しており、電源VDDに接続されている。

10

#### 【0072】

選択トランジスタTR3selは、ゲート部、チャネル形成領域、及び、ソース／ドレイン領域から構成されている。ゲート部は、選択線SEL3に接続されている。また、一方のソース／ドレイン領域は、増幅トランジスタTR3ampを構成する他方のソース／ドレイン領域と、領域を共有しており、他方のソース／ドレイン領域は、信号線（データ出力線）VSL3に接続されている。

20

#### 【0073】

リセット線RST1, RST2, RST3、選択線SEL1, SEL2, SEL3、転送ゲート線TG2, TG3は、駆動回路を構成する垂直駆動回路112に接続され、信号線（データ出力線）VSL1, VSL2, VSL3は、駆動回路を構成するカラム信号処理回路113に接続されている。

#### 【0074】

n型半導体領域43と半導体基板70の表面70Aとの間にはp+層44が設けられており、暗電流発生を抑制している。n型半導体領域41とn型半導体領域43との間には、p+層42が形成されており、更には、n型半導体領域43の側面の一部はp+層42によって囲まれている。半導体基板70の裏面70Bの側には、p+層73が形成されており、p+層73から半導体基板70の内部のコンタクトホール部61を形成すべき部分には、HfO<sub>2</sub>膜74及び絶縁膜75が形成されている。層間絶縁層76には、複数の層に亘り配線が形成されているが、図示は省略した。

30

#### 【0075】

HfO<sub>2</sub>膜74は、負の固定電荷を有する膜であり、このような膜を設けることによって、暗電流の発生を抑制することができる。尚、HfO<sub>2</sub>膜の代わりに、酸化アルミニウム(A12O<sub>3</sub>)膜、酸化ジルコニア(ZrO<sub>2</sub>)膜、酸化タンタル(Ta2O<sub>5</sub>)膜、酸化チタン(TiO<sub>2</sub>)膜、酸化ランタン(La2O<sub>3</sub>)膜、酸化プラセオジム(Pr2O<sub>3</sub>)膜、酸化セリウム(CeO<sub>2</sub>)膜、酸化ネオジム(Nd2O<sub>3</sub>)膜、酸化プロメチウム(Pm2O<sub>3</sub>)膜、酸化サマリウム(Sm2O<sub>3</sub>)膜、酸化ユロピウム(Eu2O<sub>3</sub>)膜、酸化ガドリニウム(Gd2O<sub>3</sub>)膜、酸化テルビウム(Tb2O<sub>3</sub>)膜、酸化ジスプロシウム(Dy2O<sub>3</sub>)膜、酸化ホルミウム(Ho2O<sub>3</sub>)膜、酸化ツリウム(Tm2O<sub>3</sub>)膜、酸化イットリウム(Y2O<sub>3</sub>)膜、窒化ハフニウム膜、窒化アルミニウム膜、酸窒化ハフニウム膜、酸窒化アルミニウム膜を用いることもできる。これらの膜の成膜方法として、例えば、CVD法、PVD法、ALD法が挙げができる。

40

#### 【0076】

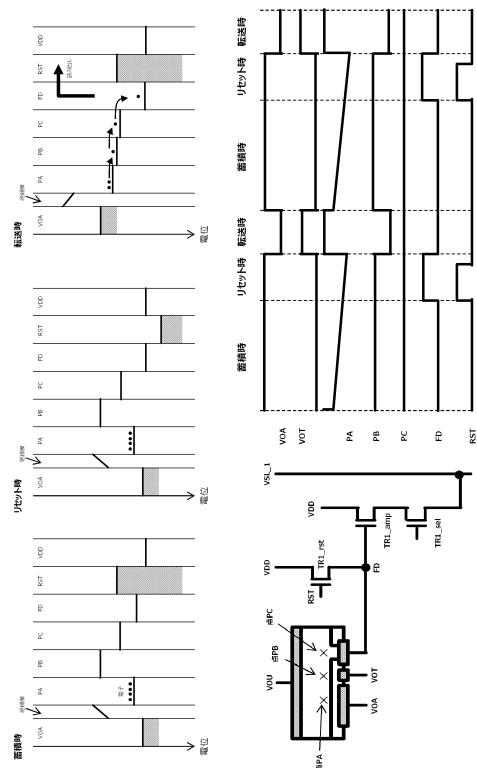

以下、図5を参照して、実施例1の撮像素子（第1撮像素子）の動作を説明する。ここで、第1電極11の電位を第2電極の電位よりも高くした。即ち、例えば、第1電極11

50

を正の電位とし、第2電極を負の電位とし、光電変換層15において光電変換によって生成した電子が浮遊拡散層に読み出される。他の実施例においても同様とする。尚、第1電極11を負の電位とし、第2電極を正の電位とし、光電変換層15において光電変換に基づき生成した正孔が浮遊拡散層に読み出される形態にあっては、以下の述べる電位の高低を逆にすればよい。

#### 【0077】

図5、後述する実施例4における図20、図21、実施例6における図32、図33中で使用している符号は、以下のとおりである。

P A . . . . . 電荷蓄積用電極12と対向した光電変換層15の領域の点P Aにおける電位、あるいは、電荷蓄積用電極セグメント12Cと対向した光電変換層15の領域の点P Aにおける電位

P B . . . . . 電荷蓄積用電極12と第1電極11の中間に位置する領域と対向した光電変換層15の領域の点P Bにおける電位、又は、転送制御用電極（電荷転送電極）13と対向した光電変換層15の領域の点P Bにおける電位、あるいは、電荷蓄積用電極セグメント12Bと対向した光電変換層15の領域の点P Bにおける電位

P C . . . . . 第1電極11と対向した光電変換層15の領域の点P Cにおける電位、あるいは、電荷蓄積用電極セグメント12Aと対向した光電変換層15の領域の点P Cにおける電位

P D . . . . . 電荷蓄積用電極セグメント12Cと第1電極11の中間に位置する領域と対向した光電変換層15の領域の点P Dにおける電位

F D . . . . . 第1浮遊拡散層FD1における電位

V O A . . . . . 電荷蓄積用電極12における電位

V O A - A . . . . 電荷蓄積用電極セグメント12Aにおける電位

V O A - B . . . . 電荷蓄積用電極セグメント12Bにおける電位

V O A - C . . . . 電荷蓄積用電極セグメント12Cにおける電位

V O T . . . . . 転送制御用電極（電荷転送電極）13における電位

R S T . . . . . リセット・トランジスタTR1rstのゲート部51における電位

V D D . . . . . 電源の電位

V S L\_1 . . . . 信号線（データ出力線）V S L1

T R 1 \_ r s t . . . リセット・トランジスタTR1rst

T R 1 \_ a m p . . 増幅トランジスタTR1amp

T R 1 \_ s e l . . 選択トランジスタTR1sel

#### 【0078】

電荷蓄積期間においては、駆動回路から、第1電極11に電位V11が印加され、電荷蓄積用電極12に電位V12が印加される。光電変換層15に入射された光によって光電変換層15において光電変換が生じる。光電変換によって生成した正孔は、第2電極16から配線VOUを介して駆動回路へと送出される。一方、第1電極11の電位を第2電極16の電位よりも高くしたので、即ち、例えば、第1電極11に正の電位が印加され、第2電極16に負の電位が印加されたので、V12 > V11、好ましくは、V12 > V11とする。これによって、光電変換によって生成した電子は、電荷蓄積用電極12に引き付けられ、電荷蓄積用電極12と対向した光電変換層15の領域に止まる。即ち、光電変換層15に電荷が蓄積される。V12 > V11であるが故に、光電変換層15の内部に生成した電子が、第1電極11に向かって移動することはない。光電変換の時間経過に伴い、電荷蓄積用電極12と対向した光電変換層15の領域における電位は、より負側の値となる。

#### 【0079】

電荷蓄積期間の後期において、リセット動作がなされる。これによって、第1浮遊拡散層FD1の電位がリセットされ、第1浮遊拡散層FD1の電位は電源の電位VDDとなる。

#### 【0080】

リセット動作の完了後、電荷の読み出しを行う。即ち、電荷転送期間において、駆動回路から、第1電極11に電位V21が印加され、電荷蓄積用電極12に電位V22が印加さ

10

20

30

40

50

れる。ここで、 $V_{22} < V_{21}$ とする。これによって、電荷蓄積用電極 12 と対向した光電変換層 15 の領域に止まっていた電子は、第 1 電極 11、更には、第 1 浮遊拡散層 FD1 へと読み出される。即ち、光電変換層 15 に蓄積された電荷が制御部に読み出される。

#### 【0081】

以上で、電荷蓄積、リセット動作、電荷転送といった一連の動作が完了する。

#### 【0082】

第 1 浮遊拡散層 FD1 へ電子が読み出された後の増幅トランジスタ TR1amp、選択トランジスタ TR1sel の動作は、従来のこれらのトランジスタの動作と同じである。また、第 2 撮像素子、第 3 撮像素子の電荷蓄積、リセット動作、電荷転送といった一連の動作は、従来の電荷蓄積、リセット動作、電荷転送といった一連の動作と同様である。また、第 1 浮遊拡散層 FD1 のリセットノイズは、従来と同様に、相関 2 重サンプリング (CDS, Correlated Double Sampling) 処理によって除去することができる。

10

#### 【0083】

以上のとおり、実施例 1 にあっては、第 1 電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極が備えられているので、光電変換部に光が照射され、光電変換部において光電変換されるとき、光電変換層と絶縁層と電荷蓄積用電極とによって一種のキャパシタが形成され、光電変換層に電荷を蓄えることができる。それ故、露光開始時、電荷蓄積部を完全空乏化し、電荷を消去することが可能となる。その結果、KTC ノイズが大きくなり、ランダムノイズが悪化し、撮像画質の低下をもたらすといった現象の発生を抑制することができる。また、全画素を一斉にリセットすることができるので、所謂グローバルシャッター機能を実現することができる。

20

#### 【0084】

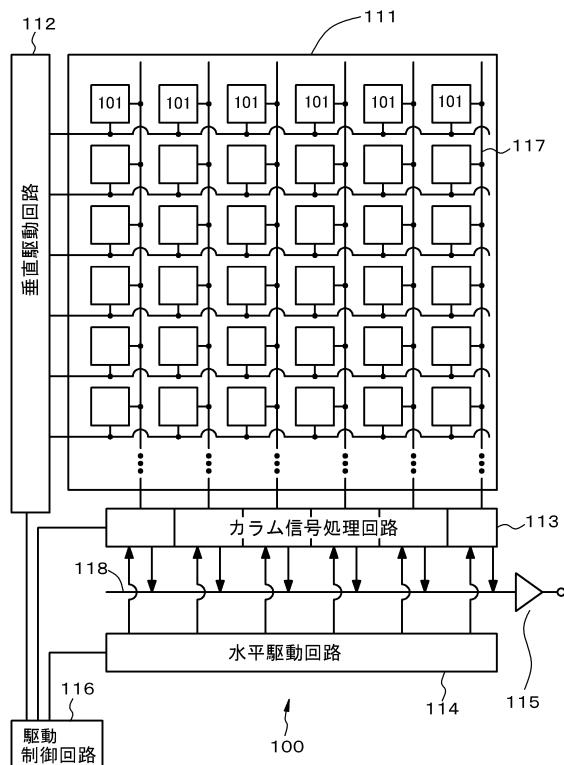

図 8 に、実施例 1 の固体撮像装置の概念図を示す。実施例 1 の固体撮像装置 100 は、積層型撮像素子 101 が 2 次元アレイ状に配列された撮像領域 111、並びに、その駆動回路（周辺回路）としての垂直駆動回路 112、カラム信号処理回路 113、水平駆動回路 114、出力回路 115 及び駆動制御回路 116 等から構成されている。尚、これらの回路は周知の回路から構成することができるし、また、他の回路構成（例えば、従来の CCD 撮像装置や CMOS 撮像装置にて用いられる各種の回路）を用いて構成することができることは云うまでもない。尚、図 8 において、積層型撮像素子 101 における参照番号「101」の表示は、1 行のみとした。

30

#### 【0085】

駆動制御回路 116 は、垂直同期信号、水平同期信号及びマスター・クロックに基づいて、垂直駆動回路 112、カラム信号処理回路 113 及び水平駆動回路 114 の動作の基準となるクロック信号や制御信号を生成する。そして、生成されたクロック信号や制御信号は、垂直駆動回路 112、カラム信号処理回路 113 及び水平駆動回路 114 に入力される。

#### 【0086】

垂直駆動回路 112 は、例えば、シフトレジスタによって構成され、撮像領域 111 の各積層型撮像素子 101 を行単位で順次垂直方向に選択走査する。そして、各積層型撮像素子 101 における受光量に応じて生成した電流（信号）に基づく画素信号（画像信号）は、信号線（データ出力線）117, VSL を介してカラム信号処理回路 113 に送られる。

40

#### 【0087】

カラム信号処理回路 113 は、例えば、積層型撮像素子 101 の列毎に配置されており、1 行分の積層型撮像素子 101 から出力される画像信号を撮像素子毎に黒基準画素（図示しないが、有効画素領域の周囲に形成される）からの信号によって、ノイズ除去や信号增幅の信号処理を行う。カラム信号処理回路 113 の出力段には、水平選択スイッチ（図示せず）が水平信号線 118 との間に接続されて設けられる。

#### 【0088】

水平駆動回路 114 は、例えばシフトレジスタによって構成され、水平走査パルスを順

50

次出力することによって、カラム信号処理回路 113 の各々を順次選択し、カラム信号処理回路 113 の各々から信号を水平信号線 118 に出力する。

#### 【0089】

出力回路 115 は、カラム信号処理回路 113 の各々から水平信号線 118 を介して順次供給される信号に対して、信号処理を行って出力する。

#### 【0090】

実施例 1 の撮像素子、積層型撮像素子の変形例の等価回路図を図 9 に示し、実施例 1 の撮像素子の変形例を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 10 に示すように、リセット・トランジスタ TR1rst の他方のソース / ドレイン領域 51B を、電源 VDD に接続する代わりに、接地してもよい。 10

#### 【0091】

実施例 1 の撮像素子、積層型撮像素子は、例えば、以下の方法で作製することができる。即ち、先ず、SOI 基板を準備する。そして、SOI 基板の表面に第 1 シリコン層をエピタキシャル成長法に基づき形成し、この第 1 シリコン層に、p+ 層 73、n 型半導体領域 41 を形成する。次いで、第 1 シリコン層上に第 2 シリコン層をエピタキシャル成長法に基づき形成し、この第 2 シリコン層に、素子分離領域 71、酸化膜 72、p+ 層 42、n 型半導体領域 43、p+ 層 44 を形成する。また、第 2 シリコン層に、撮像素子の制御部を構成する各種トランジスタ等を形成し、更にその上に、配線層 62 や層間絶縁層 76、各種配線を形成した後、層間絶縁層 76 と支持基板（図示せず）とを貼り合わせる。その後、SOI 基板を除去して第 1 シリコン層を露出させる。尚、第 2 シリコン層の表面が半導体基板 70 の表面 70A に該当し、第 1 シリコン層の表面が半導体基板 70 の裏面 70B に該当する。また、第 1 シリコン層と第 2 シリコン層を纏めて半導体基板 70 と表現している。次いで、半導体基板 70 の裏面 70B の側に、コンタクトホール部 61 を形成するための開口部を形成し、HfO<sub>2</sub> 膜 74、絶縁膜 75 及びコンタクトホール部 61 を形成し、更に、パッド部 63, 64、層間絶縁層 81、接続孔 65, 66、第 1 電極 11、電荷蓄積用電極 12、絶縁層 82 を形成する。次に、接続部 67 を開口し、光電変換層 15、第 2 電極 16、保護層 83 及びオンチップ・マイクロ・レンズ 90 を形成する。以上によって、実施例 1 の撮像素子、積層型撮像素子を得ることができる。 20

#### 【実施例 2】

#### 【0092】

実施例 2 は、実施例 1 の変形である。図 11 に模式的な一部断面図を示す実施例 2 の撮像素子、積層型撮像素子は、表面照射型の撮像素子、積層型撮像素子であり、緑色の光を吸収する第 1 タイプの緑色光電変換層を備えた緑色に感度を有する第 1 タイプの実施例 1 の緑色用撮像素子（第 1 撮像素子）、青色の光を吸収する第 2 タイプの青色光電変換層を備えた青色に感度を有する第 2 タイプの従来の青色用撮像素子（第 2 撮像素子）、赤色の光を吸収する第 2 タイプの赤色光電変換層を備えた赤色に感度を有する第 2 タイプの従来の赤色用撮像素子（第 3 撮像素子）の 3 つの撮像素子が積層された構造を有する。ここで赤色用撮像素子（第 3 撮像素子）及び青色用撮像素子（第 2 撮像素子）は、半導体基板 70 内に設けられており、第 2 撮像素子の方が、第 3 撮像素子よりも光入射側に位置する。また、緑色用撮像素子（第 1 撮像素子）は、青色用撮像素子（第 2 撮像素子）の上方に設けられている。 40

#### 【0093】

半導体基板 70 の表面 70A 側には、実施例 1 と同様に制御部を構成する各種トランジスタが設けられている。これらのトランジスタは、実質的に実施例 1 において説明したトランジスタと同様の構成、構造とすることができる。また、半導体基板 70 には、第 2 撮像素子、第 3 撮像素子が設けられているが、これらの撮像素子も、実質的に実施例 1 において説明した第 2 撮像素子、第 3 撮像素子と同様の構成、構造とすることができる。

#### 【0094】

半導体基板 70 の表面 70A の上には、層間絶縁層 77, 78 が形成されており、層間絶縁層 78 の上に、実施例 1 の撮像素子を構成する光電変換部（第 1 電極 11、光電変換

層 1 5 及び第 2 電極 1 6 )、並びに、電荷蓄積用電極 1 2 等が設けられている。

**【 0 0 9 5 】**

このように、表面照射型である点を除き、実施例 2 の撮像素子、積層型撮像素子の構成、構造は、実施例 1 の撮像素子、積層型撮像素子の構成、構造と同様とすることができるるので、詳細な説明は省略する。

**【実施例 3】**

**【 0 0 9 6 】**

実施例 3 は、実施例 1 及び実施例 2 の変形である。

**【 0 0 9 7 】**

図 1 2 に模式的な一部断面図を示す実施例 3 の撮像素子、積層型撮像素子は、裏面照射型の撮像素子、積層型撮像素子であり、第 1 タイプの実施例 1 の第 1 撮像素子、及び、第 2 タイプの第 2 撮像素子の 2 つの撮像素子が積層された構造を有する。また、図 1 3 に模式的な一部断面図を示す実施例 3 の撮像素子、積層型撮像素子の変形例は、表面照射型の撮像素子、積層型撮像素子であり、第 1 タイプの実施例 1 の第 1 撮像素子、及び、第 2 タイプの第 2 撮像素子の 2 つの撮像素子が積層された構造を有する。ここで、第 1 撮像素子は原色の光を吸収し、第 2 撮像素子は補色の光を吸収する。あるいは又、第 1 撮像素子は白色の光を吸収し、第 2 撮像素子は赤外線を吸収する。

10

**【 0 0 9 8 】**

図 1 4 に模式的な一部断面図を示す実施例 3 の撮像素子の変形例は、裏面照射型の撮像素子であり、第 1 タイプの実施例 1 の第 1 撮像素子から構成されている。また、図 1 5 に模式的な一部断面図を示す実施例 3 の撮像素子の変形例は、表面照射型の撮像素子であり、第 1 タイプの実施例 1 の第 1 撮像素子から構成されている。ここで、第 1 撮像素子は、赤色の光を吸収する撮像素子、緑色の光を吸収する撮像素子、青色の光を吸収する撮像素子の 3 種類の撮像素子から構成されている。更には、これらの撮像素子の複数から、本開示の第 1 の態様に係る固体撮像装置が構成される。複数のこれらの撮像素子の配置として、ベイヤ配列を挙げることができる。各撮像素子の光入射側には、必要に応じて、青色、緑色、赤色の分光を行うためのカラーフィルタが配設されている。

20

**【 0 0 9 9 】**

尚、第 1 タイプの実施例 1 の撮像素子を 1 つ、設ける代わりに、2 つ、積層する形態(即ち、光電変換部を 2 つ、積層し、半導体基板に 2 つの撮像素子の制御部を設ける形態)、あるいは又、3 つ、積層する形態(即ち、光電変換部を 3 つ、積層し、半導体基板に 3 つの撮像素子の制御部を設ける形態)とすることもできる。第 1 タイプの撮像素子と第 2 タイプの撮像素子の積層構造例を、以下の表に例示する。

30

**【 0 1 0 0 】**

40

50

【表 1】

|                      | 第1タイプ           | 第2タイプ                    | 参照図面           |

|----------------------|-----------------|--------------------------|----------------|

| 裏面照射型<br>及び<br>表面照射型 | 1<br>緑色         | 2<br>青色+赤色               | 図 1<br>図 1 1   |

|                      | 1<br>原色         | 1<br>補色                  | 図 1 2<br>図 1 3 |

|                      | 1<br>白色         | 1<br>赤外線                 |                |

|                      | 1<br>青色又は緑色又は赤色 | 0                        | 図 1 4<br>図 1 5 |

|                      | 2<br>緑色+赤外光     | 2<br>青色+赤色               |                |

|                      | 2<br>緑色+青色      | 1<br>赤色                  |                |

|                      | 2<br>白色+赤外光     | 0                        |                |

|                      | 3<br>緑色+青色+赤色   | 2<br>青緑色(エメラルド色)<br>+赤外光 |                |

|                      | 3<br>緑色+青色+赤色   | 1<br>赤外光                 |                |

|                      | 3<br>青色+緑色+赤色   | 0                        |                |

## 【実施例 4】

## 【0101】

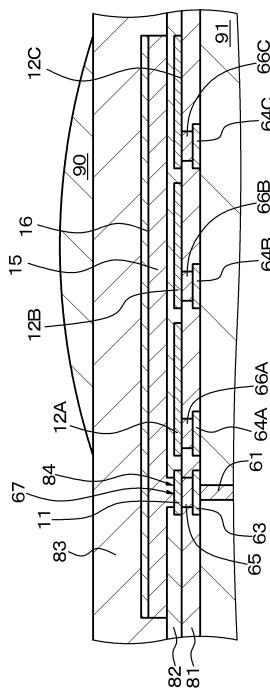

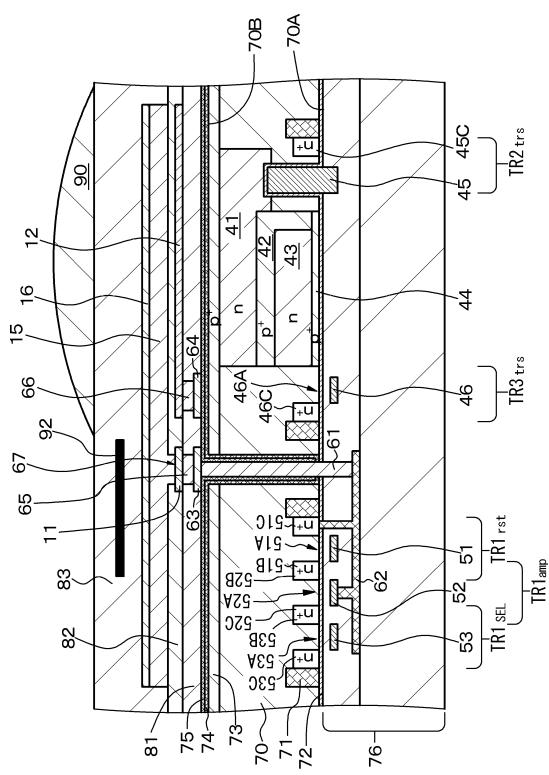

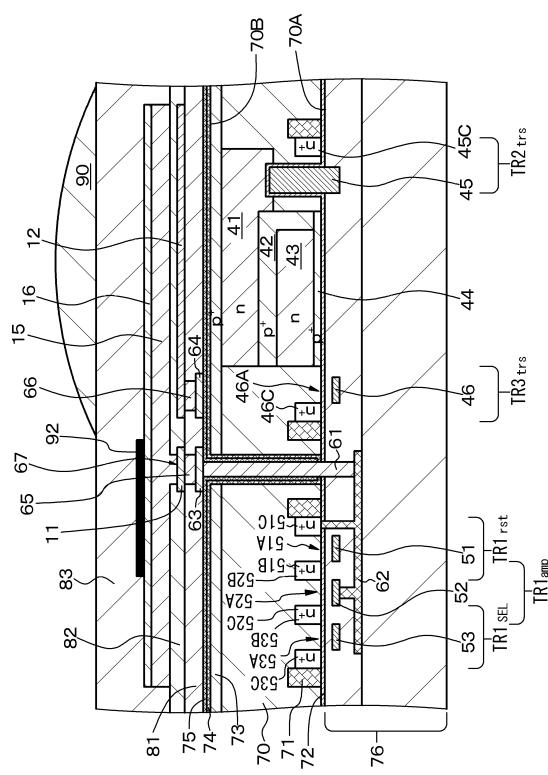

実施例 4 は、実施例 1 ~ 実施例 3 の変形であり、転送制御用電極（電荷転送電極）を備えた本開示の撮像素子等に関する。実施例 4 の撮像素子、積層型撮像素子の一部分の模式的な一部断面図を図 1 6 に示し、実施例 4 の撮像素子、積層型撮像素子の等価回路図を図 1 7 及び図 1 8 に示し、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 1 9 に示し、実施例 4 の撮像素子の動作時の各部位における電位の状態を模式的に図 2 0 及び図 2 1 に示す。また、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極及び電荷蓄積用電極の模式的な配置図を図 2 2 に示し、実施例 4 の撮像素子を構成する第 1 電極、転送制御用電極、電荷蓄積用電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図を図 2 3 に示す。

## 【0102】

実施例 4 の撮像素子、積層型撮像素子にあっては、第 1 電極 1 1 と電荷蓄積用電極 1 2 との間に、第 1 電極 1 1 及び電荷蓄積用電極 1 2 と離間して配置され、且つ、絶縁層 8 2 を介して光電変換層 1 5 と対向して配置された転送制御用電極（電荷転送電極）1 3 を更に備えている。転送制御用電極 1 3 は、層間絶縁層 8 1 内に設けられた接続孔 6 8 B、パッド部 6 8 A 及び配線 VOT を介して、駆動回路を構成する画素駆動回路に接続されている

10

20

30

40

50

。尚、層間絶縁層 8 1 より下方に位置する各種の撮像素子構成要素を、図面を簡素化するために、便宜上、纏めて、参考番号 9 1 で示す。

#### 【 0 1 0 3 】

以下、図 2 0、図 2 1 を参照して、実施例 4 の撮像素子（第 1 撮像素子）の動作を説明する。尚、図 2 0 と図 2 1 とでは、特に、電荷蓄積用電極 1 2 に印加される電位及び点 P B における電位の値が相違している。

#### 【 0 1 0 4 】

電荷蓄積期間において、駆動回路から、第 1 電極 1 1 に電位 V 11 が印加され、電荷蓄積用電極 1 2 に電位 V 12 が印加され、転送制御用電極 1 3 に電位 V 13 が印加される。光電変換層 1 5 に入射された光によって光電変換層 1 5 において光電変換が生じる。光電変換によって生成した正孔は、第 2 電極 1 6 から配線 V O U を介して駆動回路へと送出される。一方、第 1 電極 1 1 の電位を第 2 電極 1 6 の電位よりも高くしたので、即ち、例えば、第 1 電極 1 1 に正の電位が印加され、第 2 電極 1 6 に負の電位が印加されたとして、 $V_{12} > V_{13}$ （例えば、 $V_{12} > V_{11} > V_{13}$ 、又は、 $V_{11} > V_{12} > V_{13}$ ）とする。これによつて、光電変換によって生成した電子は、電荷蓄積用電極 1 2 に引き付けられ、電荷蓄積用電極 1 2 と対向した光電変換層 1 5 の領域に止まる。即ち、光電変換層 1 5 に電荷が蓄積される。 $V_{12} > V_{13}$ であるが故に、光電変換層 1 5 の内部に生成した電子が、第 1 電極 1 1 に向かって移動することを確実に防止することができる。光電変換の時間経過に伴い、電荷蓄積用電極 1 2 と対向した光電変換層 1 5 の領域における電位は、より負側の値となる。

10

#### 【 0 1 0 5 】

電荷蓄積期間の後期において、リセット動作がなされる。これによつて、第 1 浮遊拡散層 F D 1 の電位がリセットされ、第 1 浮遊拡散層 F D 1 の電位は電源の電位 V DD となる。

#### 【 0 1 0 6 】

リセット動作の完了後、電荷の読み出しを行う。即ち、電荷転送期間において、駆動回路から、第 1 電極 1 1 に電位 V 21 が印加され、電荷蓄積用電極 1 2 に電位 V 22 が印加され、転送制御用電極 1 3 に電位 V 23 が印加される。ここで、 $V_{22} = V_{23} = V_{21}$  とする。これによつて、電荷蓄積用電極 1 2 と対向した光電変換層 1 5 の領域に止まっていた電子は、第 1 電極 1 1 、更には、第 1 浮遊拡散層 F D 1 へと確実に読み出される。即ち、光電変換層 1 5 に蓄積された電荷が制御部に読み出される。

20

#### 【 0 1 0 7 】

以上で、電荷蓄積、リセット動作、電荷転送といった一連の動作が完了する。

#### 【 0 1 0 8 】

第 1 浮遊拡散層 F D 1 へ電子が読み出された後の増幅トランジスタ T R 1 amp、選択トランジスタ T R 1 sel の動作は、従来のこれらのトランジスタの動作と同じである。また、例えば、第 2 撮像素子、第 3 撮像素子の電荷蓄積、リセット動作、電荷転送といった一連の動作は、従来の電荷蓄積、リセット動作、電荷転送といった一連の動作と同様である。

30

#### 【 0 1 0 9 】

実施例 4 の撮像素子の変形例を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 2 4 に示すように、リセット・トランジスタ T R 1 rst の他方のソース / ドレイン領域 S 1 B を、電源 V DD に接続する代わりに、接地してもよい。

40

#### 【 実施例 5 】

#### 【 0 1 1 0 】

実施例 5 は、実施例 1 ~ 実施例 4 の変形であり、電荷排出電極を備えた本開示の撮像素子等に関する。実施例 5 の撮像素子、積層型撮像素子の一部分の模式的な一部断面図を図 2 5 に示し、実施例 5 の撮像素子を構成する第 1 電極、電荷蓄積用電極及び電荷排出電極の模式的な配置図を図 2 6 に示し、実施例 5 の撮像素子を構成する第 1 電極、電荷蓄積用電極、電荷排出電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図を図 2 7 に示す。

50

**【 0 1 1 1 】**

実施例 5 の撮像素子、積層型撮像素子にあっては、接続部 6 9 を介して光電変換層 1 5 に接続され、第 1 電極 1 1 及び電荷蓄積用電極 1 2 と離間して配置された電荷排出電極 1 4 を更に備えている。ここで、電荷排出電極 1 4 は、第 1 電極 1 1 及び電荷蓄積用電極 1 2 を取り囲むように（即ち、額縁状に）配置されている。電荷排出電極 1 4 は、駆動回路を構成する画素駆動回路に接続されている。接続部 6 9 内には、光電変換層 1 5 が延在している。即ち、光電変換層 1 5 は、絶縁層 8 2 に設けられた第 2 開口部 8 5 内を延在し、電荷排出電極 1 4 と接続されている。電荷排出電極 1 4 は、複数の撮像素子において共有化（共通化）されている。

**【 0 1 1 2 】**

実施例 5 にあっては、電荷蓄積期間において、駆動回路から、第 1 電極 1 1 に電位 V 11 が印加され、電荷蓄積用電極 1 2 に電位 V 12 が印加され、電荷排出電極 1 4 に電位 V 14 が印加され、光電変換層 1 5 に電荷が蓄積される。光電変換層 1 5 に入射された光によって光電変換層 1 5 において光電変換が生じる。光電変換によって生成した正孔は、第 2 電極 1 6 から配線 VOU を介して駆動回路へと送出される。一方、第 1 電極 1 1 の電位を第 2 電極 1 6 の電位よりも高くしたので、即ち、例えば、第 1 電極 1 1 に正の電位が印加され、第 2 電極 1 6 に負の電位が印加されたので、 $V_{14} > V_{11}$ （例えば、 $V_{12} > V_{14} > V_{11}$ ）とする。これによって、光電変換によって生成した電子は、電荷蓄積用電極 1 2 に引き付けられ、電荷蓄積用電極 1 2 と対向した光電変換層 1 5 の領域に止まり、第 1 電極 1 1 に向かって移動することを確実に防止することができる。但し、電荷蓄積用電極 1 2 による引き付けが充分ではなく、あるいは又、光電変換層 1 5 に蓄積しきれなかった電子（所謂オーバーフローした電子）は、電荷排出電極 1 4 を経由して、駆動回路に送出される。

**【 0 1 1 3 】**

電荷蓄積期間の後期において、リセット動作がなされる。これによって、第 1 浮遊拡散層 F D 1 の電位がリセットされ、第 1 浮遊拡散層 F D 1 の電位は電源の電位 V DD となる。

**【 0 1 1 4 】**

リセット動作の完了後、電荷の読み出しを行う。即ち、電荷転送期間において、駆動回路から、第 1 電極 1 1 に電位 V 21 が印加され、電荷蓄積用電極 1 2 に電位 V 22 が印加され、電荷排出電極 1 4 に電位 V 24 が印加される。ここで、 $V_{24} < V_{21}$ （例えば、 $V_{24} < V_{22} < V_{21}$ ）とする。これによって、電荷蓄積用電極 1 2 と対向した光電変換層 1 5 の領域に止まっていた電子は、第 1 電極 1 1 、更には、第 1 浮遊拡散層 F D 1 へと確実に読み出される。即ち、光電変換層 1 5 に蓄積された電荷が制御部に読み出される。

**【 0 1 1 5 】**

以上で、電荷蓄積、リセット動作、電荷転送といった一連の動作が完了する。

**【 0 1 1 6 】**

第 1 浮遊拡散層 F D 1 へ電子が読み出された後の増幅トランジスタ T R 1 amp、選択トランジスタ T R 1 sel の動作は、従来のこれらのトランジスタの動作と同じである。また、例えば、第 2 摄像素子、第 3 摄像素子の電荷蓄積、リセット動作、電荷転送といった一連の動作は、従来の電荷蓄積、リセット動作、電荷転送といった一連の動作と同様である。

**【 0 1 1 7 】**

実施例 5 にあっては、所謂オーバーフローした電子は電荷排出電極 1 4 を経由して駆動回路に送出されるので、隣接画素の電荷蓄積部への漏れ込みを抑制することができ、ブルーミングの発生を抑えることができる。そして、これにより、撮像素子の撮像性能を向上させることができる。

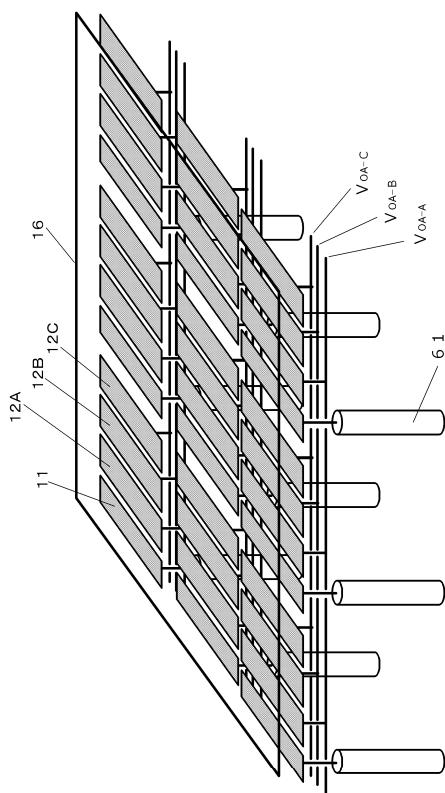

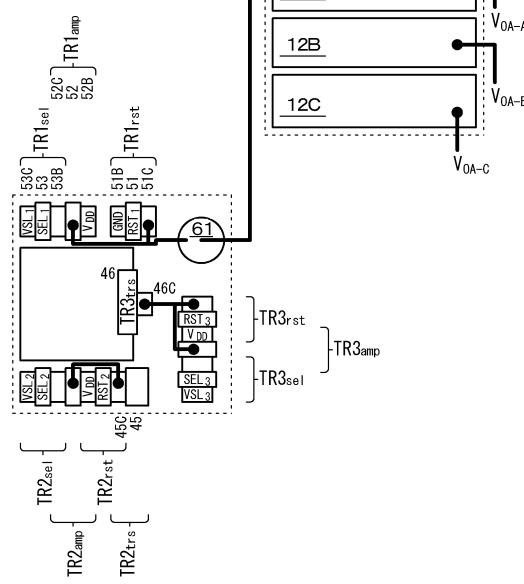

**【 実施例 6 】****【 0 1 1 8 】**

実施例 6 は、実施例 1 ~ 実施例 5 の変形であり、複数の電荷蓄積用電極セグメントを備えた本開示の撮像素子等に関する。

**【 0 1 1 9 】**

10

20

30

40

50

実施例 6 の撮像素子の一部分の模式的な一部断面図を図 28 に示し、実施例 6 の撮像素子、積層型撮像素子の等価回路図を図 29 及び図 30 に示し、実施例 6 の撮像素子を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 31 に示し、実施例 6 の撮像素子の動作時の各部位における電位の状態を模式的に図 32、図 33 に示す。また、実施例 6 の撮像素子を構成する第 1 電極及び電荷蓄積用電極の模式的な配置図を図 34 に示し、実施例 6 の撮像素子を構成する第 1 電極、電荷蓄積用電極、第 2 電極及びコンタクトホール部の模式的な透視斜視図を図 35 に示す。

#### 【 0 1 2 0 】

実施例 6において、電荷蓄積用電極 12 は、複数の電荷蓄積用電極セグメント 12A, 12B, 12C から構成されている。電荷蓄積用電極セグメントの数は、2 以上であればよく、実施例 6においては「3」とした。そして、実施例 6 の撮像素子、積層型撮像素子にあっては、第 1 電極 11 の電位が第 2 電極 16 の電位よりも高いので、即ち、例えば、第 1 電極 11 に正の電位が印加され、第 2 電極 16 に負の電位が印加されるので、電荷転送期間において、第 1 電極 11 に最も近い所に位置する電荷蓄積用電極セグメント 12A に印加される電位は、第 1 電極 11 に最も遠い所に位置する電荷蓄積用電極セグメント 12C に印加される電位よりも高い。このように、電荷蓄積用電極 12 に電位勾配を付与することで、電荷蓄積用電極 12 と対向した光電変換層 15 の領域に止まっていた電子は、第 1 電極 11、更には、第 1 浮遊拡散層 FD1 へと一層確実に読み出される。即ち、光電変換層 15 に蓄積された電荷が制御部に読み出される。

#### 【 0 1 2 1 】

図 32 に示す例では、電荷転送期間において、電荷蓄積用電極セグメント 12C の電位 < 電荷蓄積用電極セグメント 12B の電位 < 電荷蓄積用電極セグメント 12A の電位とすることで、光電変換層 15 の領域に止まっていた電子を、一斉に、第 1 浮遊拡散層 FD1 へと読み出す。一方、図 33 に示す例では、電荷転送期間において、電荷蓄積用電極セグメント 12C の電位、電荷蓄積用電極セグメント 12B の電位、電荷蓄積用電極セグメント 12A の電位を段々と変化させることで（即ち、階段状あるいはスロープ状に変化させることで）、電荷蓄積用電極セグメント 12C と対向する光電変換層 15 の領域に止まっていた電子を、電荷蓄積用電極セグメント 12B と対向する光電変換層 15 の領域に移動させ、次いで、電荷蓄積用電極セグメント 12B と対向する光電変換層 15 の領域に止まっていた電子を、電荷蓄積用電極セグメント 12A と対向する光電変換層 15 の領域に移動させ、次いで、電荷蓄積用電極セグメント 12A と対向する光電変換層 15 の領域に止まっていた電子を、第 1 浮遊拡散層 FD1 へと確実に読み出す。

#### 【 0 1 2 2 】

実施例 6 の撮像素子の変形例を構成する第 1 電極及び電荷蓄積用電極並びに制御部を構成するトランジスタの模式的な配置図を図 36 に示すように、リセット・トランジスタ TR1rst の他方のソース / ドレイン領域 51B を、電源 VDD に接続する代わりに、接地してもよい。

#### 【 0 1 2 3 】

以上、本開示を好ましい実施例に基づき説明したが、本開示はこれらの実施例に限定されるものではない。実施例にて説明した撮像素子、積層型撮像素子、固体撮像装置の構造や構成、製造条件、製造方法、使用した材料は例示であり、適宜変更することができる。1つの撮像素子に1つの浮遊拡散層を設ける形態だけでなく、複数の撮像素子に対して1つの浮遊拡散層を設ける形態とすることもできる。即ち、電荷転送期間のタイミングを適切に制御することで、複数の撮像素子が1つの浮遊拡散層を共有することが可能となる。そして、この場合、複数の撮像素子が1つのコンタクトホール部を共有することも可能となる。

#### 【 0 1 2 4 】

図 37 に、例えば、実施例 1 において説明した撮像素子、積層型撮像素子の変形例を示すように、第 1 電極 11 は、絶縁層 82 に設けられた開口部 84A 内を延在し、光電変換層 15 と接続されている構成とすることもできる。

10

20

30

40

50

### 【0125】

あるいは又、図38に、例えば、実施例1において説明した撮像素子、積層型撮像素子の変形例を示し、図39Aに第1電極の部分等の拡大された模式的な一部断面図を示すように、第1電極11の頂面の縁部は絶縁層82で覆われており、開口部84Bの底面には第1電極11が露出しており、第1電極11の頂面と接する絶縁層82の面を第1面82a、電荷蓄積用電極12と対向する光電変換層15の部分と接する絶縁層82の面を第2面82bとしたとき、開口部84Bの側面は、第1面82aから第2面82bに向かって広がる傾斜を有する。このように、開口部84Bの側面に傾斜を付けることで、光電変換層15から第1電極11への電荷の移動がより滑らかとなる。尚、図39Aに示した例では、開口部84Bの軸線を中心として、開口部84Bの側面は回転対称であるが、図39Bに示すように、第1面82aから第2面82bに向かって広がる傾斜を有する開口部84Cの側面が電荷蓄積用電極12側に位置するように、開口部84Cを設けてもよい。これによって、開口部84Cを挟んで電荷蓄積用電極12とは反対側の光電変換層15の部分からの電荷の移動が行われ難くなる。また、開口部84Bの側面は、第1面82aから第2面82bに向かって広がる傾斜を有するが、第2面82bにおける開口部84Bの側面の縁部は、図39Aに示したように、第1電極11の縁部よりも外側に位置してもよいし、図39Cに示すように、第1電極11の縁部よりも内側に位置してもよい。前者の構成を採用することで、電荷の転送が一層容易になるし、後者の構成を採用することで、開口部の形成時の形状バラツキを小さくすることができる。

10

### 【0126】

これらの開口部84B, 84Cは、絶縁層に開口部をエッチング法に基づき形成するときに形成するレジスト材料から成るエッチング用マスクをリフローすることで、エッチング用マスクの開口側面に傾斜を付け、このエッチング用マスクを用いて絶縁層82をエッチングすることで、形成することができる。

20

### 【0127】

あるいは又、実施例5において説明した電荷排出電極14に関して、図40に示すように、光電変換層15は、絶縁層82に設けられた第2開口部85A内を延在し、電荷排出電極14と接続されており、電荷排出電極14の頂面の縁部は絶縁層82で覆われており、第2開口部85Aの底面には電荷排出電極14が露出しており、電荷排出電極14の頂面と接する絶縁層82の面を第3面82c、電荷蓄積用電極12と対向する光電変換層15の部分と接する絶縁層82の面を第2面82bとしたとき、第2開口部85Aの側面は、第3面82cから第2面82bに向かって広がる傾斜を有する形態とすることができる。

30

### 【0128】

また、図41に、例えば、実施例1において説明した撮像素子、積層型撮像素子の変形例を示すように、第2電極16の側から光が入射し、第2電極16よりの光入射側には遮光層92が形成されている構成とすることもできる。尚、光電変換層よりも光入射側に設けられた各種配線を遮光層として機能させることもできる。

### 【0129】

尚、図41に示した例では、遮光層92は、第2電極16の上方に形成されているが、即ち、第2電極16よりの光入射側であって、第1電極11の上方に遮光層92が形成されているが、図42に示すように、第2電極16の光入射側の面の上に配設されてもよい。また、場合によっては、図43に示すように、第2電極16に遮光層92が形成されていてもよい。

40

### 【0130】

あるいは又、第2電極16側から光が入射し、第1電極11には光が入射しない構造とすることもできる。具体的には、図41に示したように、第2電極16よりの光入射側であって、第1電極11の上方には遮光層92が形成されている。あるいは又、図45に示すように、電荷蓄積用電極12及び第2電極16の上方にはオンチップ・マイクロ・レンズ90が設けられており、オンチップ・マイクロ・レンズ90に入射する光は、電荷蓄積用電極12に集光され、第1電極11には到達しない構造とすることもできる。尚、実施

50

例 4において説明したように、転送制御用電極 13 が設けられている場合、第 1 電極 11 及び転送制御用電極 13 には光が入射しない形態とすることもできる。具体的には、図 4 4 に図示するように、第 1 電極 11 及び転送制御用電極 13 の上方には遮光層 92 が形成されている構造とすることもできる。あるいは又、オンチップ・マイクロ・レンズ 90 に入射する光は、第 1 電極 11 及び転送制御用電極 13 には到達しない構造とすることもできる。

#### 【0131】

これらの構成、構造を採用することで、あるいは又、電荷蓄積用電極 12 の上方に位置する光電変換層 15 の部分のみに光が入射するように遮光層 92 を設け、あるいは又、オンチップ・マイクロ・レンズ 90 を設計することで、第 1 電極 11 の上方（あるいは、第 1 電極 11 及び転送制御用電極 13 の上方）に位置する光電変換層 15 の部分は光電変換に寄与しなくなるので、全画素をより確実に一斉にリセットすることができ、グローバルシャッター機能を一層容易に実現することができる。即ち、これらの構成、構造を有する撮像素子を、複数、備えた固体撮像装置の駆動方法にあっては、

全ての撮像素子において、一斉に、光電変換層 15 に電荷を蓄積しながら、第 1 電極 11 における電荷を系外に排出し、その後、

全ての撮像素子において、一斉に、光電変換層 15 に蓄積された電荷を第 1 電極 11 に転送し、転送完了後、順次、各撮像素子において第 1 電極 11 に転送された電荷を読み出す、

各工程を繰り返す。

#### 【0132】

光電変換層は 1 層からの構成に限定されない。例えば、実施例 1 において説明した撮像素子、積層型撮像素子の変形例を図 4 6 に示すように、光電変換層 15 を、例えば、IGZO から成る下層半導体層 15A と、実施例 1 において説明した光電変換層 15 を構成する材料から成る上層光電変換層 15B の積層構造とすることもできる。このように下層半導体層 15A を設けることで、電荷蓄積時の再結合を防止することができ、光電変換層 15 に蓄積した電荷の第 1 電極 11 への転送効率を増加させることができると、暗電流の生成を抑制することができる。また、実施例 4 の変形例として、図 4 7 に示すように、第 1 電極 11 に最も近い位置から電荷蓄積用電極 12 に向けて、複数の転送制御用電極を設けてよい。尚、図 4 7 には、2 つの転送制御用電極 13A, 13B を設けた例を示した。

#### 【0133】

以上に説明した各種の変形例は、実施例 1 以外の実施例に対しても適用することができるることは云うまでもない。

#### 【0134】

実施例においては、電子を信号電荷としており、半導体基板に形成された光電変換層の導電型を n 型としたが、正孔を信号電荷とする固体撮像装置にも適用できる。この場合には、各半導体領域を逆の導電型の半導体領域で構成すればよく、半導体基板に形成された光電変換層の導電型は p 型とすればよい。

#### 【0135】

また、実施例にあっては、入射光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されて成る CMOS 型固体撮像装置に適用した場合を例に挙げて説明したが、CMOS 型固体撮像装置への適用に限られるものではなく、CCD 型固体撮像装置に適用することもできる。後者の場合、信号電荷は、CCD 型構造の垂直転送レジスタによって垂直方向に転送され、水平転送レジスタによって水平方向に転送され、增幅されることにより画素信号（画像信号）が出力される。また、画素が 2 次元マトリックス状に形成され、画素列毎にカラム信号処理回路を配置して成るカラム方式の固体撮像装置全般に限定するものでもない。更には、場合によっては、選択トランジスタを省略することもできる。

#### 【0136】

更には、本開示の撮像素子、積層型撮像素子は、可視光の入射光量の分布を検知して画

10

20

30

40

50

像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは、粒子等の入射量の分布を画像として撮像する固体撮像装置にも適用可能である。また、広義には、圧力や静電容量等、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像装置（物理量分布検知装置）全般に対して適用可能である。

#### 【0137】

更には、撮像領域の各単位画素を行単位で順に走査して各単位画素から画素信号を読み出す固体撮像装置に限られるものではない。画素単位で任意の画素を選択して、選択画素から画素単位で画素信号を読み出すX-Yアドレス型の固体撮像装置に対しても適用可能である。固体撮像装置はワンチップとして形成された形態であってもよいし、撮像領域と、駆動回路又は光学系とを纏めてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。10

#### 【0138】

また、固体撮像装置への適用に限られるものではなく、撮像装置にも適用可能である。ここで、撮像装置とは、デジタルスチルカメラやビデオカメラ等のカメラシステムや、携帯電話機等の撮像機能を有する電子機器を指す。電子機器に搭載されるモジュール状の形態、即ち、カメラモジュールを撮像装置とする場合もある。

#### 【0139】

本開示の像素子、積層型像素子から構成された固体撮像装置201を電子機器（カメラ）200に用いた例を、図48に概念図として示す。電子機器200は、固体撮像装置201、光学レンズ210、シャッタ装置211、駆動回路212、及び、信号処理回路213を有する。光学レンズ210は、被写体からの像光（入射光）を固体撮像装置201の撮像面上に結像させる。これにより固体撮像装置201内に、一定期間、信号電荷が蓄積される。シャッタ装置211は、固体撮像装置201への光照射期間及び遮光期間を制御する。駆動回路212は、固体撮像装置201の転送動作等及びシャッタ装置211のシャッタ動作を制御する駆動信号を供給する。駆動回路212から供給される駆動信号（タイミング信号）により、固体撮像装置201の信号転送を行う。信号処理回路213は、各種の信号処理を行う。信号処理が行われた映像信号は、メモリ等の記憶媒体に記憶され、あるいは、モニタに出力される。このような電子機器200では、固体撮像装置201における画素サイズの微細化及び転送効率の向上を達成することができる、画素特性の向上が図られた電子機器200を得ることができる。固体撮像装置201を適用できる電子機器200としては、カメラに限られるものではなく、デジタルスチルカメラ、携帯電話機等のモバイル機器向けカメラモジュール等の撮像装置に適用可能である。2030

#### 【0140】

尚、本開示は、以下のような構成を取ることもできる。

##### [A01]《像素子》

第1電極、光電変換層及び第2電極が積層されて成る光電変換部を備えており、

光電変換部は、更に、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極を備えている像素子。

##### [A02]半導体基板を更に備えており、

光電変換部は、半導体基板の上方に配置されている[A01]に記載の像素子。40

[A03]第1電極は、絶縁層に設けられた開口部内を延在し、光電変換層と接続されている[A01]又は[A02]に記載の像素子。

[A04]光電変換層は、絶縁層に設けられた開口部内を延在し、第1電極と接続されている[A01]又は[A02]に記載の像素子。

##### [A05]第1電極の頂面の縁部は絶縁層で覆われており、

開口部の底面には第1電極が露出しており、

第1電極の頂面と接する絶縁層の面を第1面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第2面としたとき、開口部の側面は、第1面から第2面に向かって広がる傾斜を有する[A04]に記載の像素子。

##### [A06]第1面から第2面に向かって広がる傾斜を有する開口部の側面は、電荷蓄積用

10

20

30

40

50

電極側に位置する [ A 0 5 ] に記載の撮像素子。

[ A 0 7 ] 《第 1 電極及び電荷蓄積用電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第 1 電極及び電荷蓄積用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第 1 電極に電位 V 11 が印加され、電荷蓄積用電極に電位 V 12 が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第 1 電極に電位 V 21 が印加され、電荷蓄積用電極に電位 V 22 が印加され、光電変換層に蓄積された電荷が第 1 電極を経由して制御部に読み出される [ A 0 1 ] 乃至 [ A 0 6 ] のいずれか 1 項に記載の撮像素子。

但し、第 1 電極の電位が第 2 電極より高い場合、

$V_{12} > V_{11}$ 、且つ、 $V_{22} < V_{21}$

であり、第 1 電極の電位が第 2 電極より低い場合、

$V_{12} < V_{11}$ 、且つ、 $V_{22} > V_{21}$

である。

[ A 0 8 ] 《転送制御用電極》

第 1 電極と電荷蓄積用電極との間に、第 1 電極及び電荷蓄積用電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された転送制御用電極を更に備えている [ A 0 1 ] 乃至 [ A 0 6 ] のいずれか 1 項に記載の撮像素子。

[ A 0 9 ] 《第 1 電極、電荷蓄積用電極及び転送制御用電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第 1 電極、電荷蓄積用電極及び転送制御用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第 1 電極に電位 V 11 が印加され、電荷蓄積用電極に電位 V 12 が印加され、転送制御用電極に電位 V 13 が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第 1 電極に電位 V 21 が印加され、電荷蓄積用電極に電位 V 22 が印加され、転送制御用電極に電位 V 23 が印加され、光電変換層に蓄積された電荷が第 1 電極を介して制御部に読み出される [ A 0 8 ] に記載の撮像素子。

但し、第 1 電極の電位が第 2 電極より高い場合、

$V_{12} > V_{13}$ 、且つ、 $V_{22} > V_{23} > V_{21}$

であり、第 1 電極の電位が第 2 電極より低い場合、

$V_{12} < V_{13}$ 、且つ、 $V_{22} > V_{23} > V_{21}$

である。

[ A 1 0 ] 《電荷排出電極》

光電変換層に接続され、第 1 電極及び電荷蓄積用電極と離間して配置された電荷排出電極を更に備えている [ A 0 1 ] 乃至 [ A 0 9 ] のいずれか 1 項に記載の撮像素子。

[ A 1 1 ] 電荷排出電極は、第 1 電極及び電荷蓄積用電極を取り囲むように配置されている [ A 1 0 ] に記載の撮像素子。

[ A 1 2 ] 光電変換層は、絶縁層に設けられた第 2 開口部内を延在し、電荷排出電極と接続されており、

電荷排出電極の頂面の縁部は絶縁層で覆われており、

第 2 開口部の底面には電荷排出電極が露出しており、

電荷排出電極の頂面と接する絶縁層の面を第 3 面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第 2 面としたとき、第 2 開口部の側面は、第 3 面から第 2 面に向かって広がる傾斜を有する [ A 1 0 ] 又は [ A 1 1 ] に記載の撮像素子。

[ A 1 3 ] 《第 1 電極、電荷蓄積用電極及び電荷排出電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第 1 電極、電荷蓄積用電極及び電荷排出電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第 1 電極に電位 V 11 が印加され、電荷蓄積用電極に電位 V 12 が印加され、電荷排出電極に電位 V 14 が印加され、光電変換層に電荷が蓄積され、

10

20

30

40

50

電荷転送期間において、駆動回路から、第1電極に電位V21が印加され、電荷蓄積用電極に電位V22が印加され、電荷排出電極に電位V24が印加され、光電変換層に蓄積された電荷が第1電極を介して制御部に読み出される[A10]乃至[A12]のいずれか1項に記載の撮像素子。

但し、第1電極の電位が第2電極より高い場合、

$V_{14} > V_{11}$ 、且つ、 $V_{24} < V_{21}$

であり、第1電極の電位が第2電極より低い場合、

$V_{14} < V_{11}$ 、且つ、 $V_{24} > V_{21}$

である。

[A14]《電荷蓄積用電極セグメント》

電荷蓄積用電極は、複数の電荷蓄積用電極セグメントから構成されている[A01]乃至[A13]のいずれか1項に記載の撮像素子。

[A15]第1電極の電位が第2電極より高い場合、電荷転送期間において、第1電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第1電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも高く、

第1電極の電位が第2電極より低い場合、電荷転送期間において、第1電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第1電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも低い[A14]に記載の撮像素子。

[B01]半導体基板には、制御部を構成する少なくとも浮遊拡散層及び増幅トランジスタが設けられており、

第1電極は、浮遊拡散層及び増幅トランジスタのゲート部に接続されている[A01]乃至[A15]のいずれか1項に記載の撮像素子。

[B02]半導体基板には、更に、制御部を構成するリセット・トランジスタ及び選択トランジスタが設けられており、

浮遊拡散層は、リセット・トランジスタの一方のソース／ドレイン領域に接続されており、

増幅トランジスタの一方のソース／ドレイン領域は、選択トランジスタの一方のソース／ドレイン領域に接続されており、選択トランジスタの他方のソース／ドレイン領域は信号線に接続されている[B01]に記載の撮像素子。

[B03]電荷蓄積用電極の大きさは第1電極よりも大きい[A01]乃至[B02]のいずれか1項に記載の撮像素子。

[B04]第2電極側から光が入射し、第2電極よりの光入射側には遮光層が形成されている[A01]乃至[B03]のいずれか1項に記載の撮像素子。

[B05]第2電極側から光が入射し、第1電極には光が入射しない[A01]乃至[B03]のいずれか1項に記載の撮像素子。

[B06]第2電極よりの光入射側であって、第1電極の上方には遮光層が形成されている[B05]に記載の撮像素子。

[B07]電荷蓄積用電極及び第2電極の上方にはオンチップ・マイクロ・レンズが設けられており、

オンチップ・マイクロ・レンズに入射する光は、電荷蓄積用電極に集光される[B05]に記載の撮像素子。

[C01]《積層型撮像素子》

[A01]乃至[B07]のいずれか1項に記載の撮像素子を少なくとも1つ有する積層型撮像素子。

[D01]《固体撮像装置・・・第1の態様》

[A01]乃至[B04]のいずれか1項に記載の撮像素子を、複数、備えた固体撮像装置。

[D02]《固体撮像装置・・・第2の態様》

[C01]に記載の積層型撮像素子を、複数、備えた固体撮像装置。

10

20

30

40

50

## [ E 0 1 ] 《固体撮像装置の駆動方法》

第1電極、光電変換層及び第2電極が積層されて成る光電変換部を備えており、

光電変換部は、更に、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極を備えており、

第2電極側から光が入射し、第1電極には光が入射しない構造を有する撮像素子を、複数、備えた固体撮像装置の駆動方法であって、

全ての撮像素子において、一斉に、光電変換層に電荷を蓄積しながら、第1電極における電荷を系外に排出し、その後、

全ての撮像素子において、一斉に、光電変換層に蓄積された電荷を第1電極に転送し、転送完了後、順次、各撮像素子において第1電極に転送された電荷を読み出す、各工程を繰り返す固体撮像装置の駆動方法。

## 【符号の説明】

## 【0 1 4 1】

1 1 . . . 第1電極、1 2 . . . 電荷蓄積用電極、1 2 A , 1 2 B , 1 2 C . . . 電荷蓄積用電極セグメント、1 3 , 1 3 A , 1 3 B . . . 転送制御用電極（電荷転送電極）、1 4 . . . 電荷排出電極、1 5 . . . 光電変換層、1 6 . . . 第2電極、4 1 . . . 第2撮像素子を構成するn型半導体領域、4 3 . . . 第3撮像素子を構成するn型半導体領域、4 2 , 4 4 , 7 3 . . . p+層、F D 1 , F D 2 , F D 3 , 4 5 C , 4 6 C . . . 浮遊拡散層、T R 1 amp . . . 増幅トランジスタ、T R 1rst . . . リセット・トランジスタ、T R 1sel . . . 選択トランジスタ、5 1 . . . リセット・トランジスタT R 1rstのゲート部、5 1 A . . . リセット・トランジスタT R 1rstのチャネル形成領域、5 1 B , 5 1 C . . . リセット・トランジスタT R 1rstのソース／ドレイン領域、5 2 . . . 増幅トランジスタT R 1ampのゲート部、5 2 A . . . 増幅トランジスタT R 1ampチャネル形成領域、5 2 B , 5 2 C . . . 増幅トランジスタT R 1ampのソース／ドレイン領域、5 3 . . . 選択トランジスタT R 1selのゲート部、5 3 A . . . 選択トランジスタT R 1selのチャネル形成領域、5 3 B , 5 3 C . . . 選択トランジスタT R 1selのソース／ドレイン領域、T R 2 trs . . . 転送トランジスタ、4 5 . . . 転送トランジスタのゲート部、T R 2 rs t . . . リセット・トランジスタ、T R 2 amp . . . 増幅トランジスタ、T R 2 sel . . . 選択トランジスタ、T R 3 trs . . . 転送トランジスタ、4 6 . . . 転送トランジスタのゲート部、T R 3 rst . . . リセット・トランジスタ、T R 3 amp . . . 増幅トランジスタ、T R 3 sel . . . 選択トランジスタ、V DD . . . 電源、R S T 1 , R S T 2 , R S T 3 . . . リセット線、S E L 1 , S E L 2 , S E L 3 . . . 選択線、1 1 7 , V S L 1 , V S L 2 , V S L 3 . . . 信号線、T G 2 , T G 3 . . . 転送ゲート線、VOA , VOT , VOU . . . 配線、6 1 . . . コンタクトホール部、6 2 . . . 配線層、6 3 , 6 4 , 6 8 A . . . パッジ部、6 5 , 6 8 B . . . 接続孔、6 6 , 6 7 , 6 9 . . . 接続部、7 0 . . . 半導体基板、7 0 A . . . 半導体基板の第1面（おもて面）、7 0 B . . . 半導体基板の第2面（裏面）、7 1 . . . 素子分離領域、7 2 . . . 酸化膜、7 4 . . . HfO<sub>2</sub>膜、7 5 . . . 絶縁膜、7 6 . . . 層間絶縁層、7 7 , 7 8 , 8 1 . . . 層間絶縁層、8 2 . . . 絶縁層、8 2 a . . . 絶縁層の第1面、8 2 b . . . 絶縁層の第2面、8 2 c . . . 絶縁層の第3面、8 3 . . . 保護層、8 4 , 8 4 A , 8 4 B , 8 4 C . . . 開口部、8 5 , 8 5 A . . . 第2開口部、9 0 . . . オンチップ・マイクロ・レンズ、9 1 . . . 層間絶縁層8 1より下方に位置する各種の撮像素子構成要素、9 2 . . . 遮光層、1 0 0 . . . 固体撮像装置、1 0 1 . . . 積層型撮像素子、1 1 1 . . . 撮像領域、1 1 2 . . . 垂直駆動回路、1 1 3 . . . カラム信号処理回路、1 1 4 . . . 水平駆動回路、1 1 5 . . . 出力回路、1 1 6 . . . 駆動制御回路、1 1 8 . . . 水平信号線、2 0 0 . . . 電子機器（カメラ）、2 0 1 . . . 固体撮像装置、2 1 0 . . . 光学レンズ、2 1 1 . . . シャッタ装置、2 1 2 . . . 駆動回路、2 1 3 . . . 信号処理回路

10

20

30

40

50

## 【図面】

## 【図 1】

図 1

## 【図 2】

10

20

30

40

50

## 【図 3】

図 3

## 【図 4】

図 4

【図 5】

図 5

【図 6】

図 6

10

20

【図 7】

図 7

【図 8】

図 8

30

40

50

【 四 9 】

【 図 1 0 】

【図11】

図 1 1

【図12】

図 1 2

10

20

30

40

50

【図 1 3】

図 1 3

【図 1 4】

図 1 4

10

20

30

40

【図 1 5】

図 1 5

【図 1 6】

図 1 6

50

【図 1 7】

【図 1 8】

【図 1 9】

図 1.9

【図 2 0】

図 2.0

10

20

30

40

50

【図 2 1】

図 2 1

【図 2 2】

図 2 2

10

20

30

40

50

【図 2 3】

図 2 3

【図 2 4】

図 2 4

【図 2 5】

図 2 5

【図 2 6】

図 2 6

10

20

【図 2 7】

図 2 7

【図 2 8】

図 2 8

30

40

50

【図 2 9】

【図 3 0】

10

20

30

40

【図 3 1】

図 3 1

【図 3 2】

図 3 2

50

【図 3 3】

図 3 3

【図 3 4】

図 3 4

10

20

30

40

50

【図 3 5】

図 3 5

【図 3 6】

図 3 6

【図37】

図37

【 図 3 8 】

図38

【図39】

図 39 A

図 39 B

图 39c

【 四 0 】

図 4-0

10

20

30

40

50

【図4-1】

図 4-1

【図42】

図 4 2

【図43】

図 4-3

【図44】

図 4-4

10

20

30

40

50

【図45】

図45

【図46】

図46

【図47】

図47

【図48】

図48

10

20

30

40

50

【図 4 9】

図 4 9

10

20

30

40

50

---

フロントページの続き

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 渡部 泰一郎

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 安藤 良洋

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 片岡 豊隆

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 慶野 聰志

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

(72)発明者 兼田 有希央

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

審査官 脇水 佳弘

米国特許出願公開第2016/0037098(US, A1)

特開2015-050331(JP, A)

特開2016-063165(JP, A)

米国特許出願公開第2013/0093932(US, A1)

特開2014-127545(JP, A)

特開2012-234949(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H04N 25/70