US 20110267668A1

# (19) United States(12) Patent Application Publication

## Hagood, IV et al.

(54) **DISPLAY APPARATUS AND METHODS FOR MANUFACTURE THEREOF**

- (75) Inventors: Nesbitt W. Hagood, IV, Wellesley, MA (US); Jasper Lodewyk Steyn, Winchester, MA (US); Timothy J. Brosnihan, Natick, MA (US); Jignesh Gandhi, Burlington, MA (US); John J. Fijol, Shrewsbury, MA (US); Richard S. Payne, Andover, MA (US); Roger Barton, Grand Marais, MN (US)

- (73) Assignee: **Pixtronix, Inc.**, Andover, MA (US)

- (21) Appl. No.: 13/180,201

- (22) Filed: Jul. 11, 2011

#### **Related U.S. Application Data**

(63) Continuation of application No. 12/483,062, filed on Jun. 11, 2009, now Pat. No. 7,999,994, which is a continuation of application No. 12/045,518, filed on

## (10) Pub. No.: US 2011/0267668 A1 (43) Pub. Date: Nov. 3, 2011

Mar. 10, 2008, now abandoned, which is a continuation-in-part of application No. 11/906,383, filed on Oct. 1, 2007, now Pat. No. 7,636,189, said application No. 12/045,518 is a continuation of application No. 11/361,785, filed on Feb. 23, 2006, now Pat. No. 7,405, 852, said application No. 11/906,383 is a continuation of application No. 11/251,034, filed on Oct. 14, 2005, now Pat. No. 7,304,785.

## **Publication Classification**

- (51) Int. Cl. *G02B 26/02* (2006.01) *G02B 26/00* (2006.01)

- (52) U.S. Cl. ...... 359/230; 359/290

### (57) **ABSTRACT**

Display devices incorporating shutter-based light modulators are disclosed along with methods of manufacturing such devices. The methods are compatible with thin-film manufacturing processes known in the art and result in displays having lower power-consumption.

700

604

602

Ī.

ш

ш

ш

533

531

Figure 11

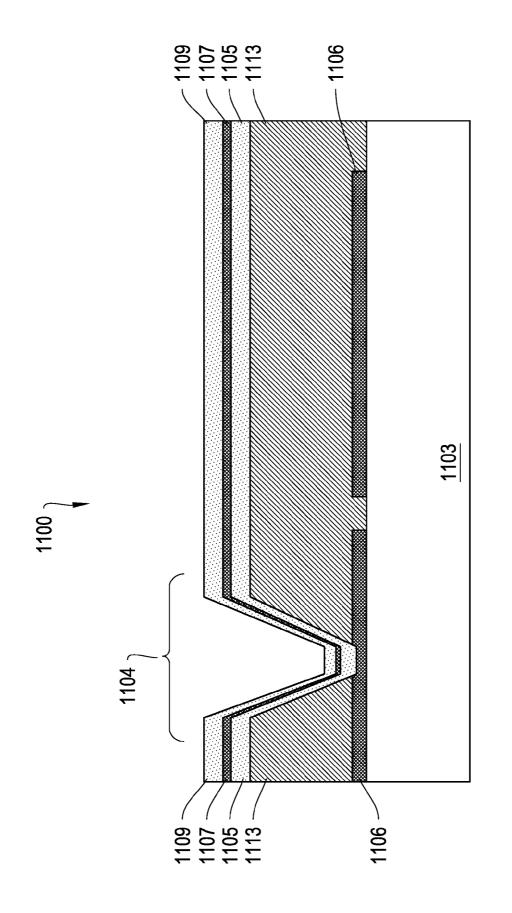

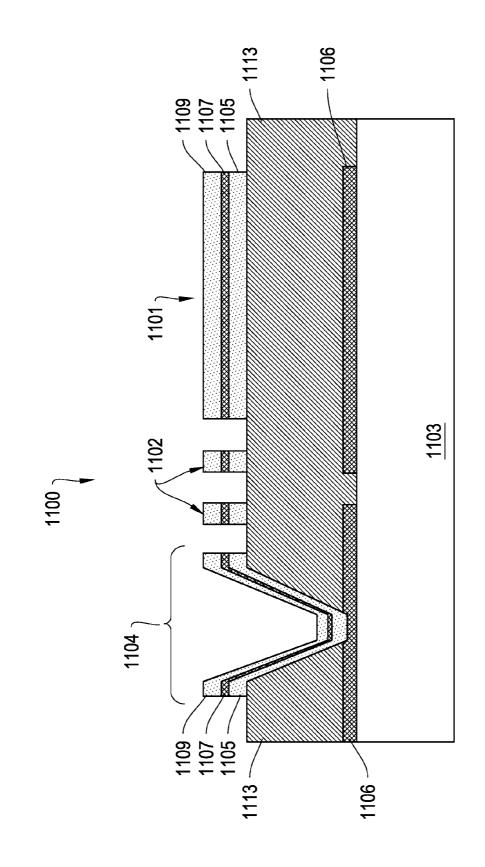

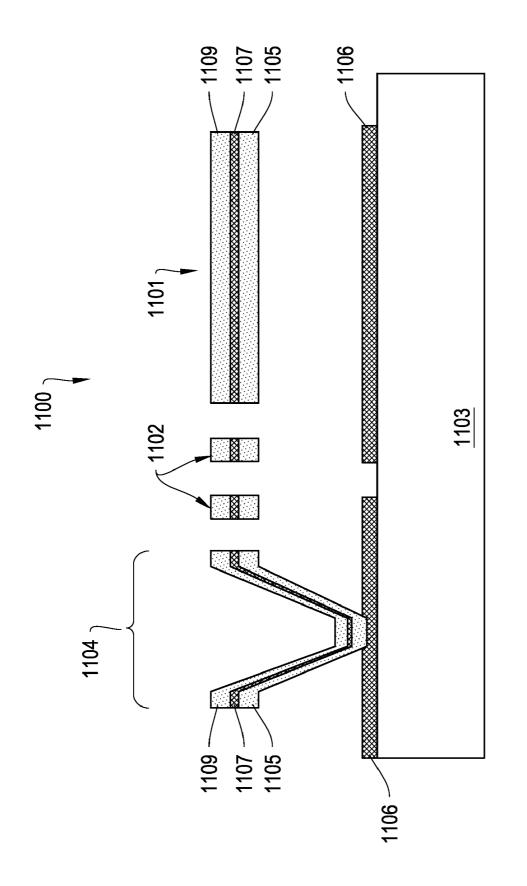

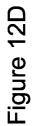

Figure 12A

Figure 12B

Figure 12C

1700 -

Figure 19A

Figure 20

# DISPLAY APPARATUS AND METHODS FOR MANUFACTURE THEREOF

## CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation of U.S. patent application Ser. No. 12/483,062 filed Jun. 11, 2009, which is a continuation of U.S. patent application Ser. No. 12/045,518 filed Mar. 10, 2008 and a continuation-in-part of U.S. patent application Ser. No. 11/906,383 filed Oct. 1, 2007. U.S. patent application Ser. No. 12/045,518 is a continuation of U.S. patent application Ser. No. 12/045,518 is a continuation of U.S. patent application Ser. No. 11/361,785, filed Feb. 23, 2006 and now U.S. Pat. No. 7,405,852. U.S. patent application Ser. No. 11/251,034, filed Oct. 14, 2005 and now U.S. Pat. No. 7,304,785. The disclosures of all of the foregoing are incorporated herein by reference in their entirety.

### FIELD OF THE INVENTION

**[0002]** In general, the invention relates to the field of imaging displays, in particular, the invention relates to MEMS-based displays and the manufacture thereof.

### BACKGROUND OF THE INVENTION

**[0003]** Displays built from mechanical light modulators are an attractive alternative to displays based on liquid crystal technology. Mechanical light modulators are fast enough to display video content with good viewing angles and with a wide range of color and grey scale. Mechanical light modulators have been successful in projection display applications. Backlit displays using mechanical light modulators have not yet demonstrated sufficiently attractive combinations of brightness and low power. There is a need in the art for fast, bright, low-powered mechanically actuated displays. Specifically there is a need for mechanically actuated displays that can be driven at high speeds and at low voltages for improved image quality and reduced power consumption.

**[0004]** In addition, a significant manufacturing industry has developed around the manufacturing of liquid crystal displays. Typical MEMS manufacturing techniques, however, are often incompatible with the processes used by the liquid crystal display industry in manufacturing the thin-film components used to control liquid crystal displays. To take advantage of the capital already invested in the display manufacturing industry, there is a need in the art, for methods of manufacturing MEMS-based displays that are compatible with of the processes used for liquid crystal display manufacturing.

### SUMMARY OF THE INVENTION

**[0005]** In a further aspect, the invention relates to a method of manufacturing a display. The method includes depositing a layer of light blocking material on top of a substantially transparent substrate. In one embodiment, the layer of light blocking includes a light-absorbing material. A plurality of light transmissive regions, such as apertures, are then formed in the light blocking layer. An insulating later is deposited on top of, and in some embodiments directly on top of, the light blocking metal layer, followed by the formation of vias in the insulating layer.

**[0006]** The method includes forming a plurality of thin-film components on the insulating layer. The plurality of thin-film components electrically connect to the light blocking layer at

the plurality of via holes. Then a plurality of light-modulating shutter assemblies are formed above, and in electrical communication with, the plurality of thin film components such that the thin-film components form a control matrix for controlling the light modulation of the plurality of light-modulating shutter assemblies.

**[0007]** In other embodiments, for example, embodiments in which the light blocking layer includes a conductive metal, electrical components are etched into the light blocking layer in addition to the light transmissive regions. In one particular embodiment, the electrical components of the light blocking layer are electrically connected to the shutter assemblies such that they are maintained at the same electric potential.

[0008] According to another aspect, the invention includes a MEMS display that includes a multilayer control matrix. The control matrix includes conductive components in at least first and second layers of the control matrix. The display also includes a MEMS light modulator and a conductive oxide electrical connection that connects at least one electrically conductive component in the first layer of the control matrix to an electrically conductive component in the second layer of the control matrix or to the MEMS light modulator. [0009] According to a further aspect, the invention relates to a MEMS-based shutter assembly for spatial light modulation. The shutter assembly includes a substrate, a shutter supported over the substrate, and an actuator for moving the shutter to selectively modulate light. The shutter includes at least two portions. A first portion, when the shutter is in a first position, is oriented substantially horizontally with respect to the substrate. The second portion, in the same position, is at least partially transverse to the first portion.

**[0010]** In an additional aspect, the invention relates to a MEMS-based spatial light modulator that includes a substrate and a moveable element supported over the substrate. The movable portion includes a compliant beam that exhibits an unbalanced state of stress such that the beam adopts a desired state of curvature.

**[0011]** According to yet another aspect, the invention relates to a MEMS device that includes a first component that defines a claim. The MEMS device also includes a beam suspended over the first component. The beam includes at least one layer of amorphous silicon, and a dimension of the beam normal to the plane defined by the first component is substantially greater than at least one dimension of the beam within the defined plane.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0012]** The foregoing discussion will be understood more readily from the following detailed description of the invention with reference to the following drawings:

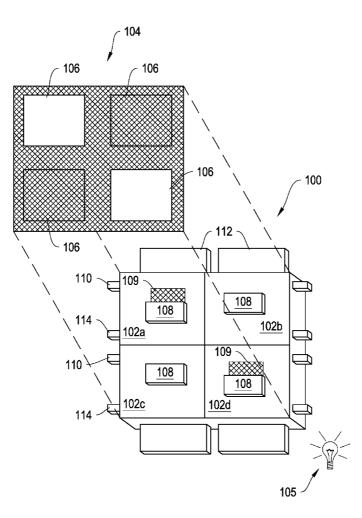

**[0013]** FIG. **1**A is an isometric view of display apparatus, according to an illustrative embodiment of the invention;

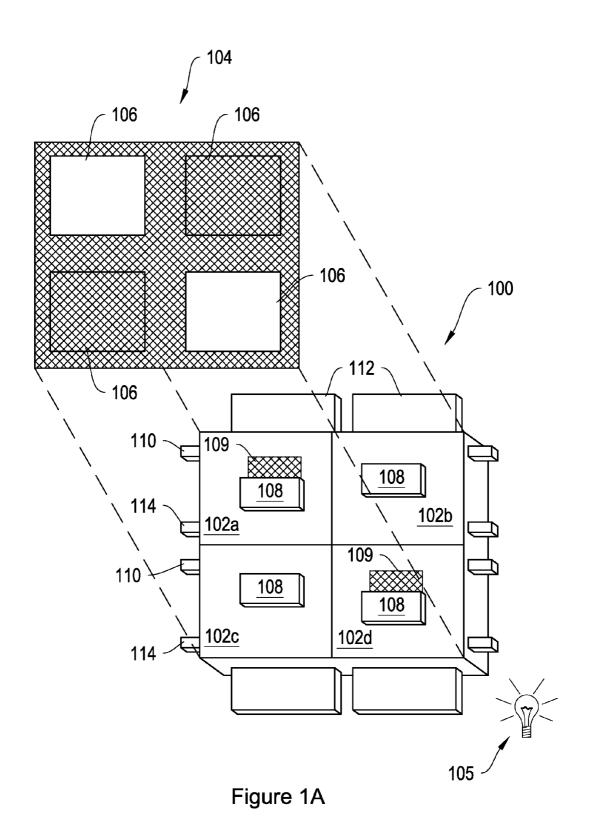

**[0014]** FIG. **1B** is diagram of an illustrative shutter assembly suitable for incorporation into the display apparatus of FIG. **1**A.

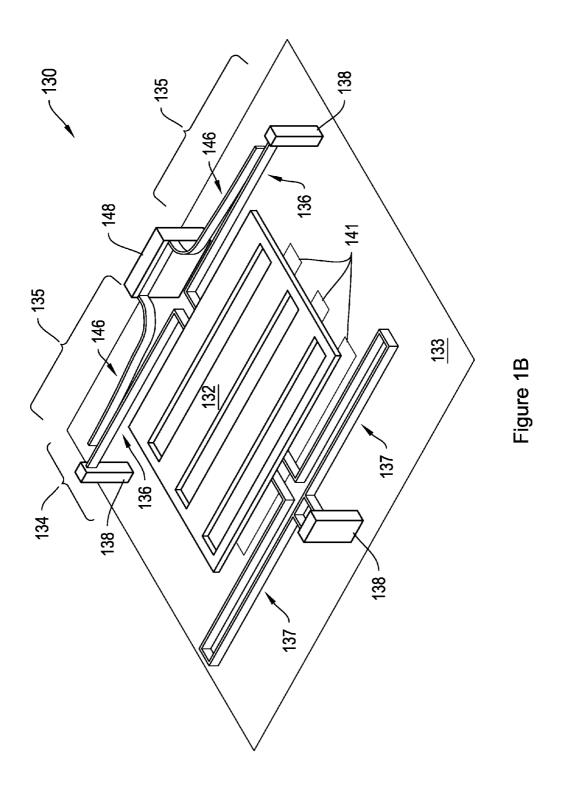

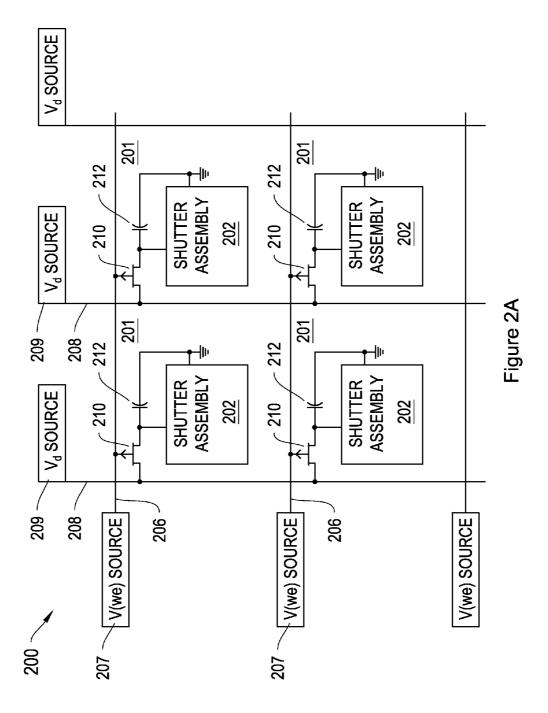

**[0015]** FIG. **2**A is a schematic diagram of a control matrix suitable for controlling the shutter assemblies of the display apparatus of FIG. **1**, according to an illustrative embodiment of the invention;

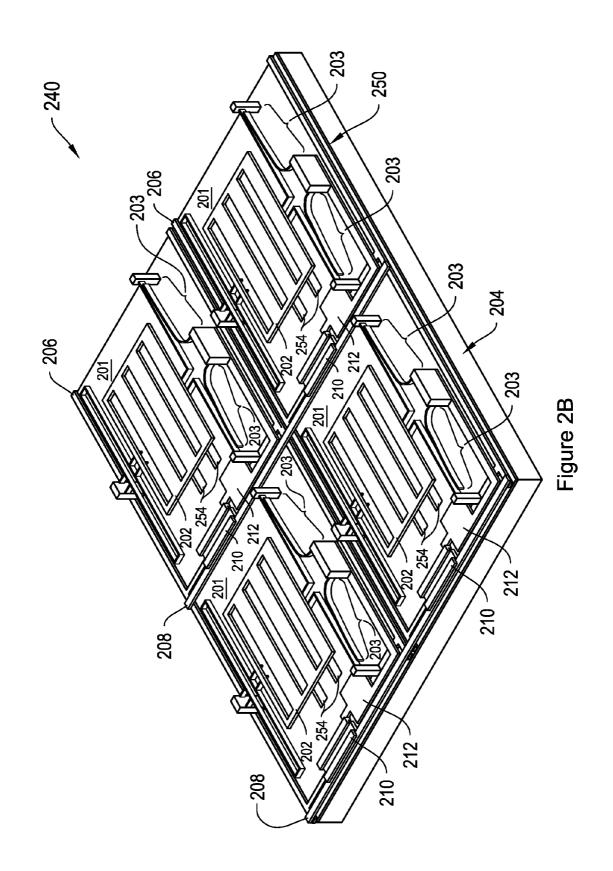

**[0016]** FIG. **2**B is an isometric view of an array of pixels incorporating the control matrix of FIG. **2**A and the shutter assembly of FIG. **1**B, according to an illustrative embodiment of the invention;

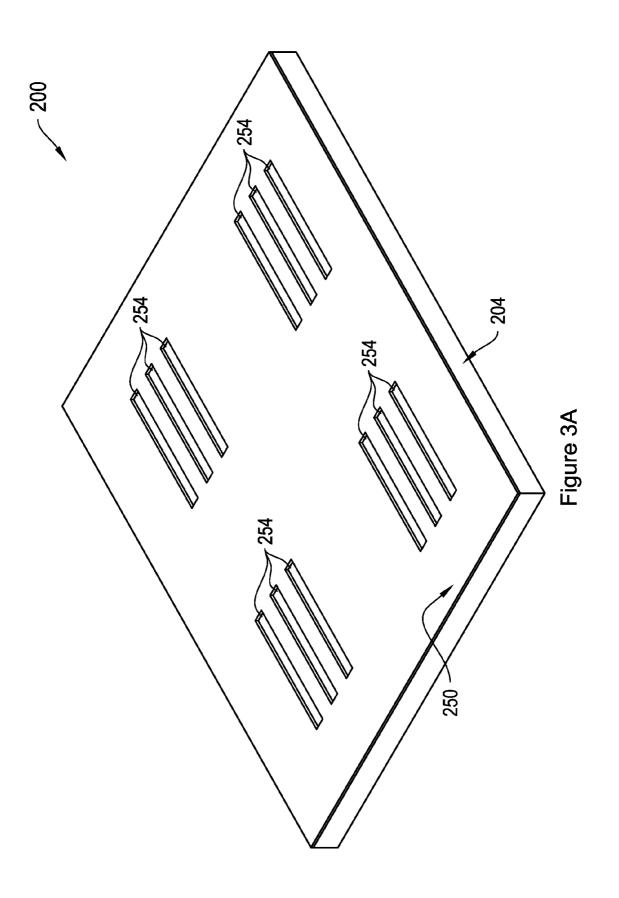

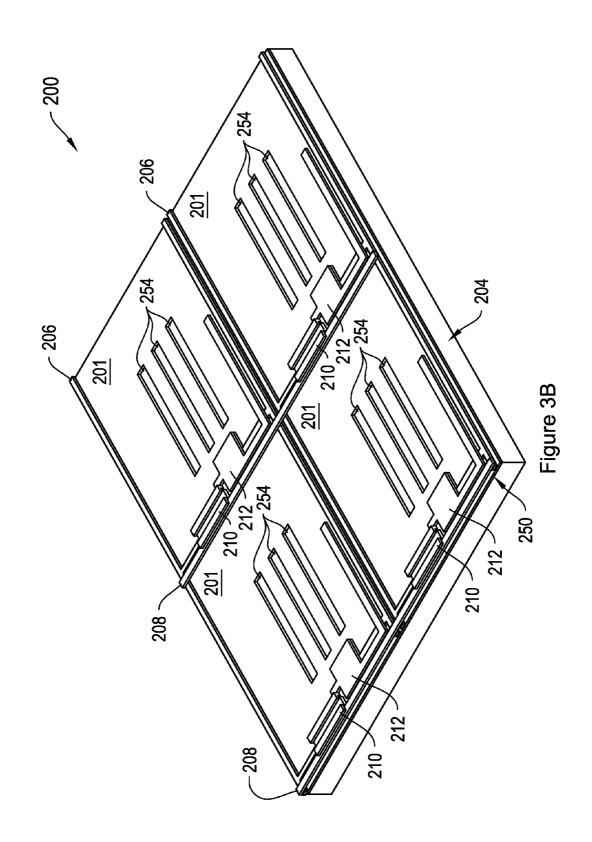

**[0017]** FIGS. **3A-3**B are isometric views of stages of construction of the control matrix of FIG. **2**B, according to an illustrative embodiment of the invention;

**[0018]** FIGS. **4**A-**4**B are cross sectional views of the construction of FIG. **2**B, according to an illustrative embodiment of the invention;

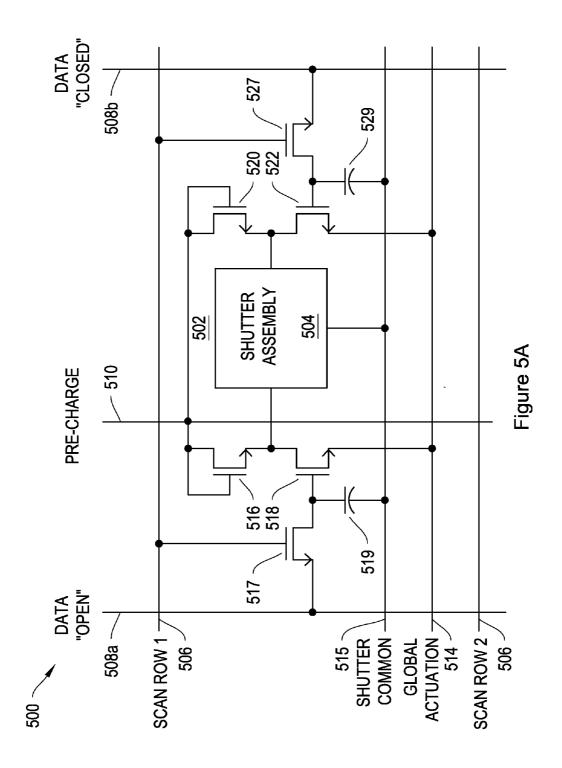

**[0019]** FIG. **5**A is a schematic diagram of a control matrix suitable for controlling the shutter assemblies of the display apparatus of FIG. **1**, according to an illustrative embodiment of the invention;

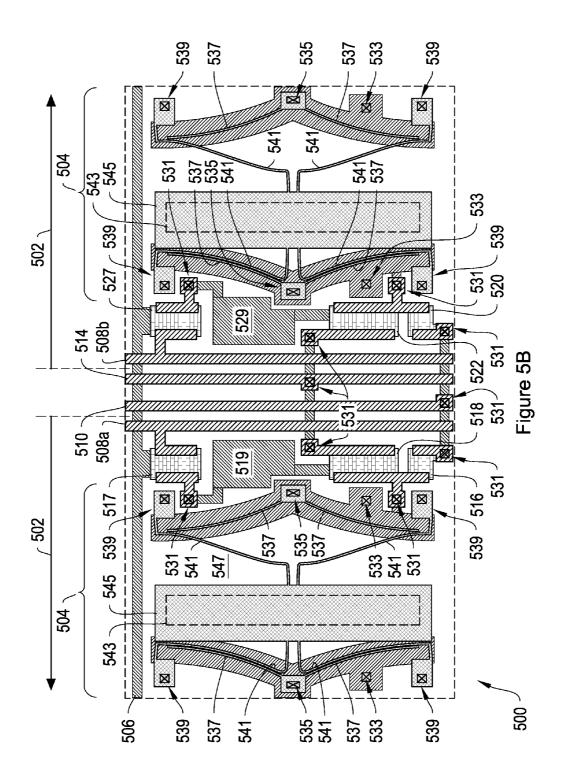

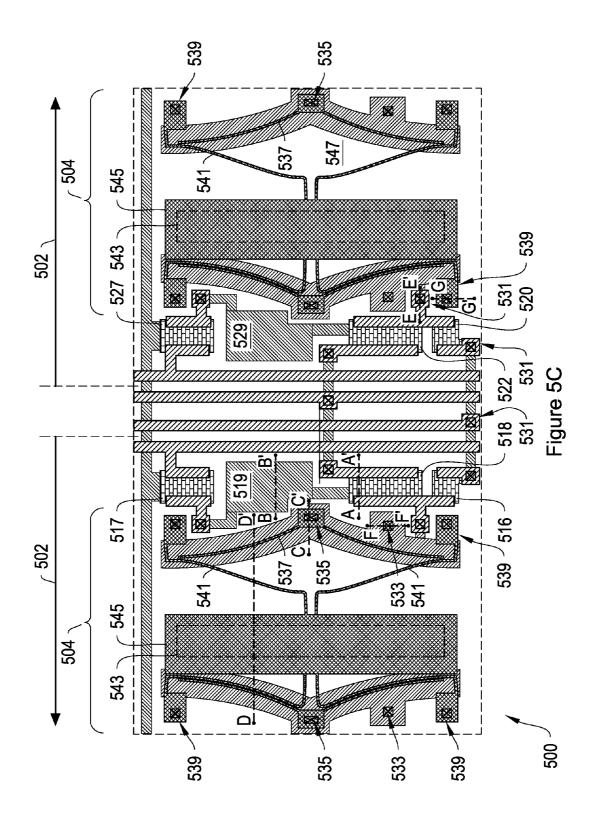

**[0020]** FIGS. **5**B and **5**C are plan view layouts of the control matrix from FIG. **5**A, according to an illustrative embodiment of the invention;

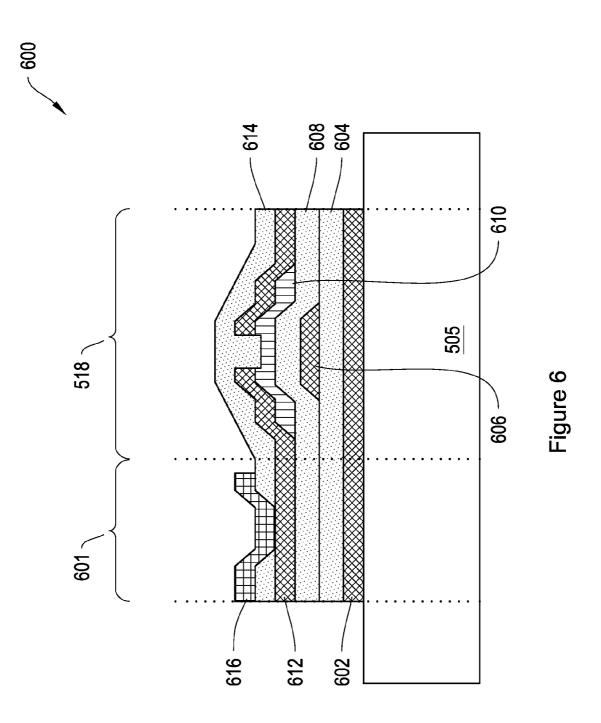

**[0021]** FIG. **6** is a cross sectional view of a transistor in the control matrix shown in FIG. **5**B, according to an illustrative embodiment of the invention;

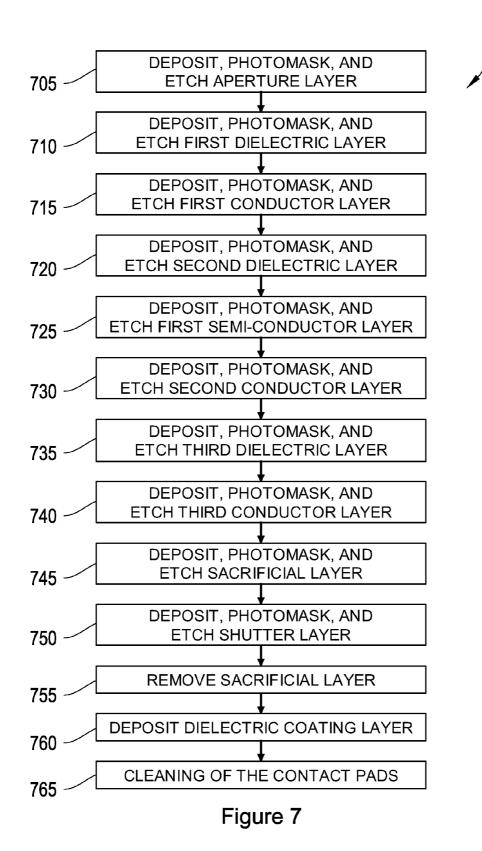

**[0022]** FIG. **7** is a flow chart of a method of fabricating the control matrix illustrated in FIG. **5**B, according to an illustrative embodiment of the invention;

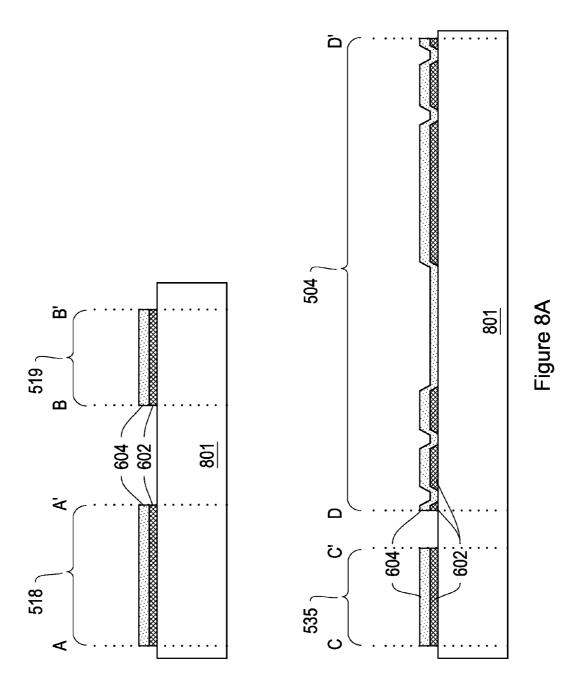

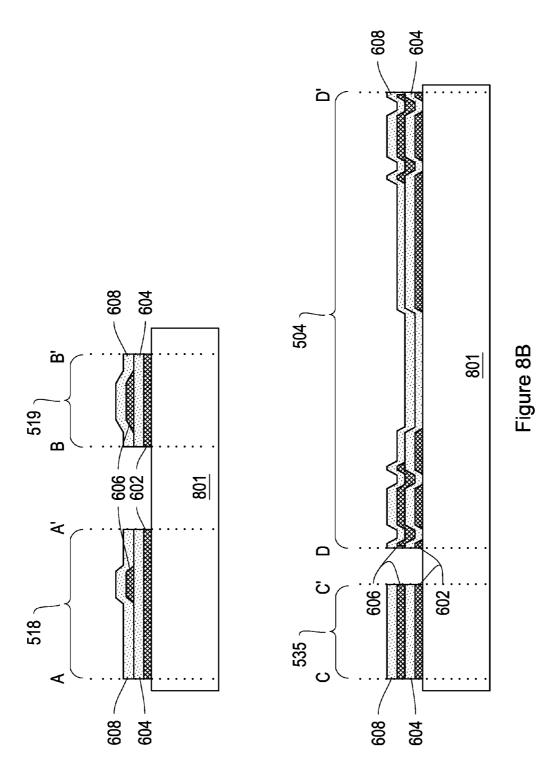

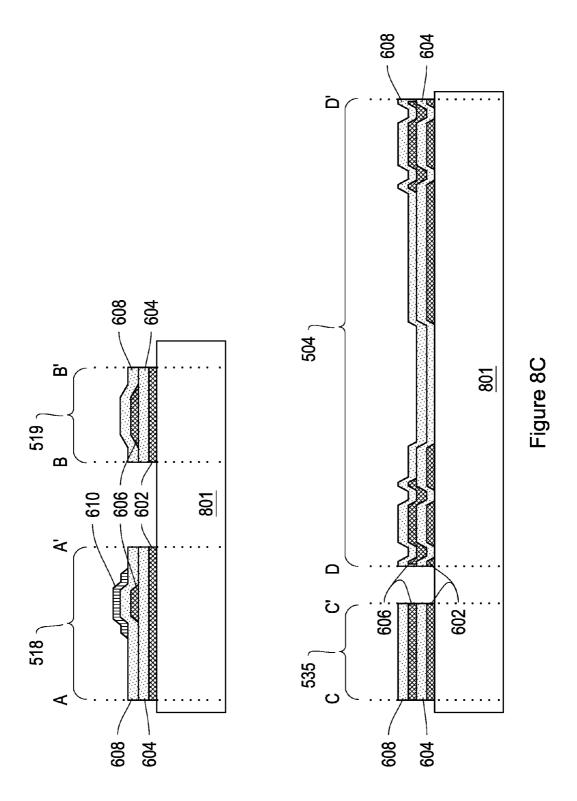

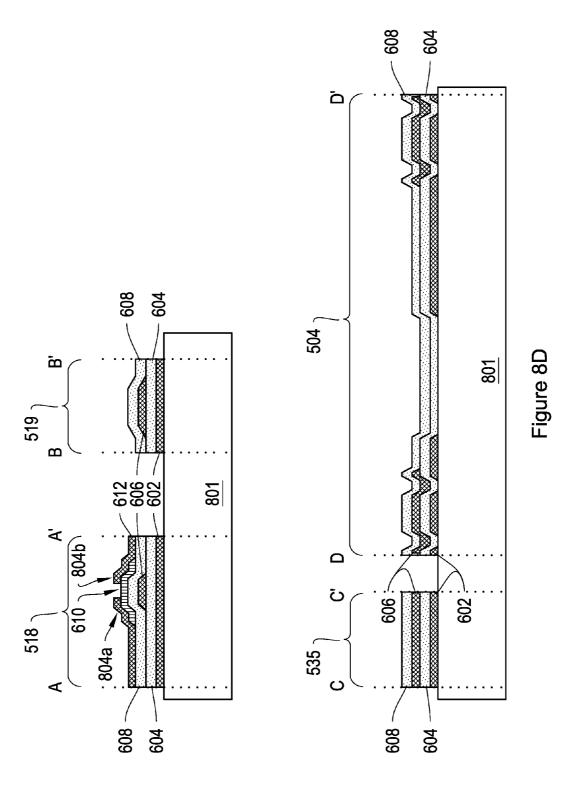

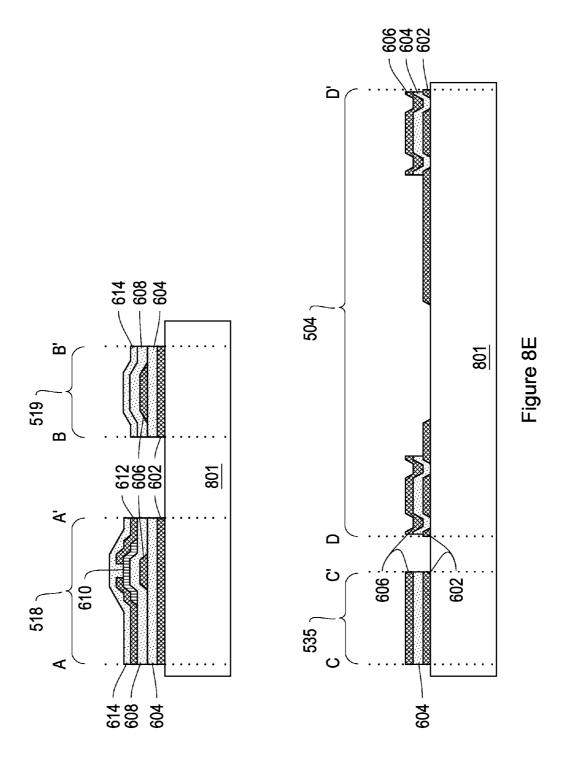

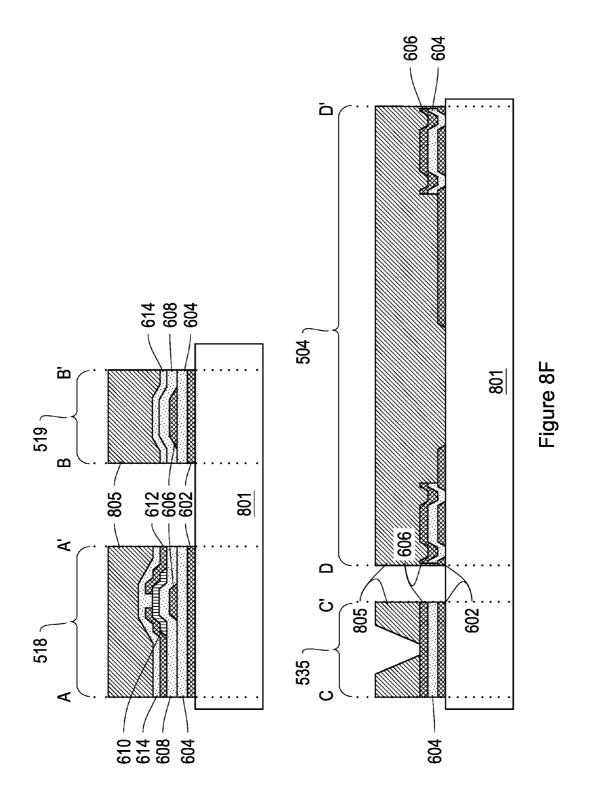

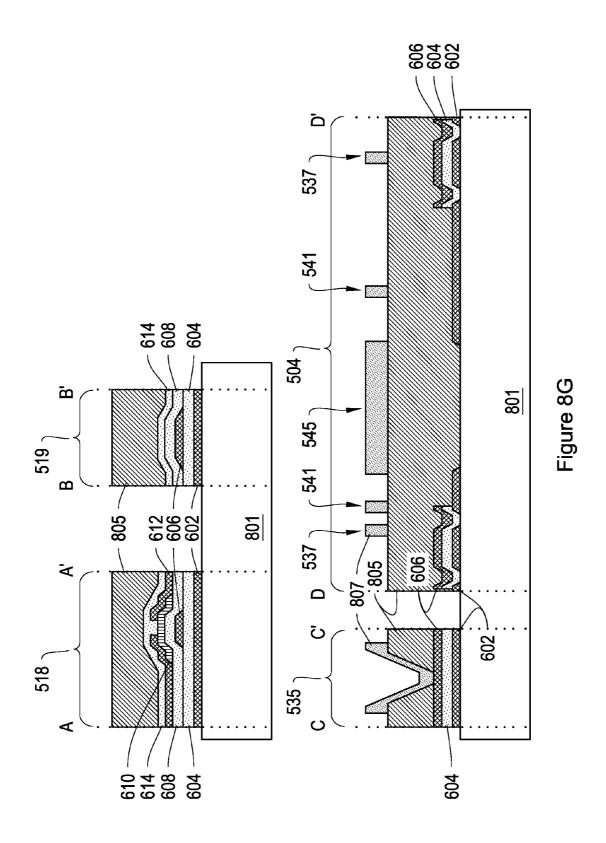

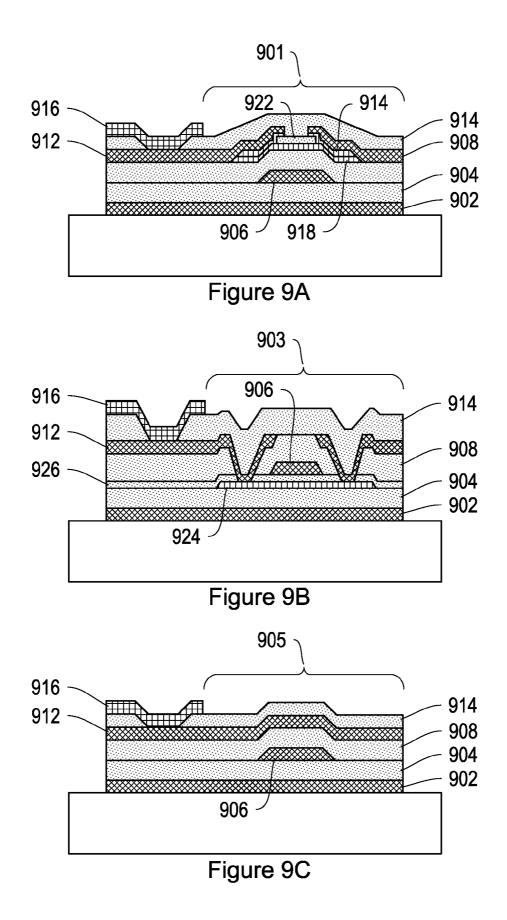

**[0023]** FIGS. **8**A-**8**H are cross sectional views of stages of construction of the control matrix of FIG. **5**C, according to an illustrative embodiment of the invention;

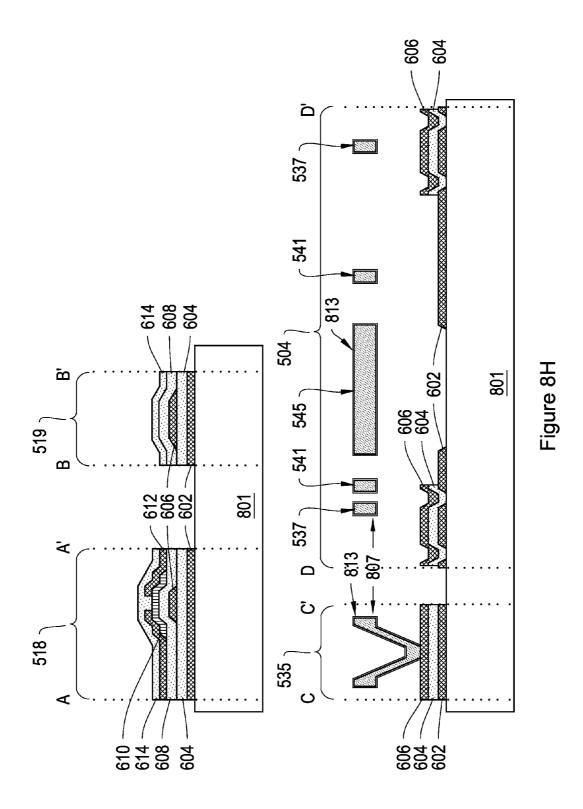

**[0024]** FIGS. **9**A-**9**C are cross sectional views of alternate switch structures for use in the control matrix of FIG. **5**B, according to an illustrative embodiment of the invention;

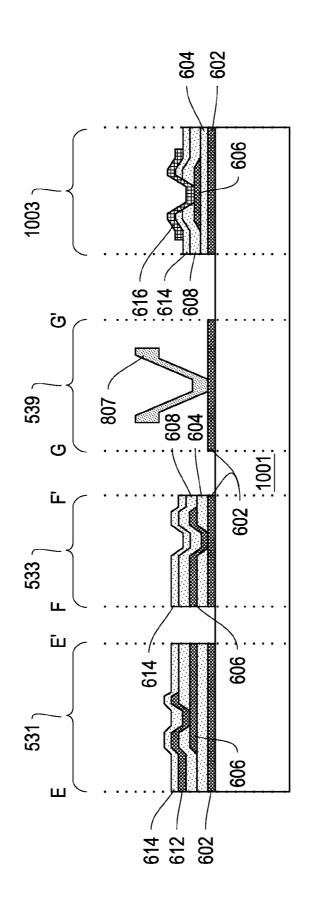

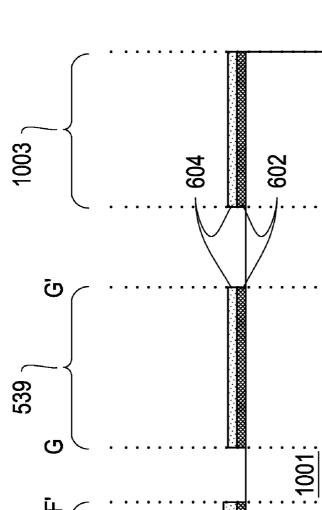

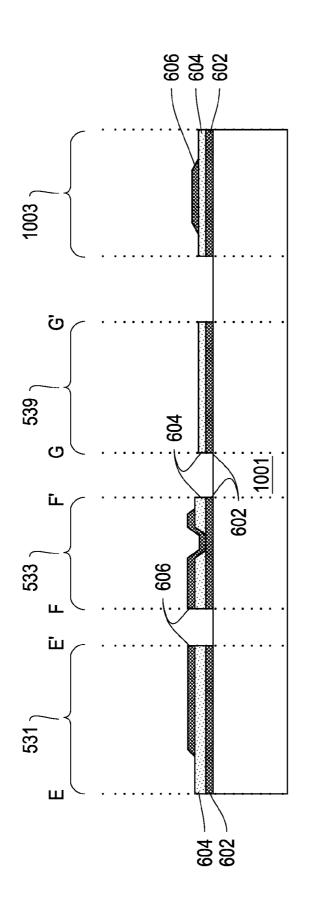

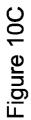

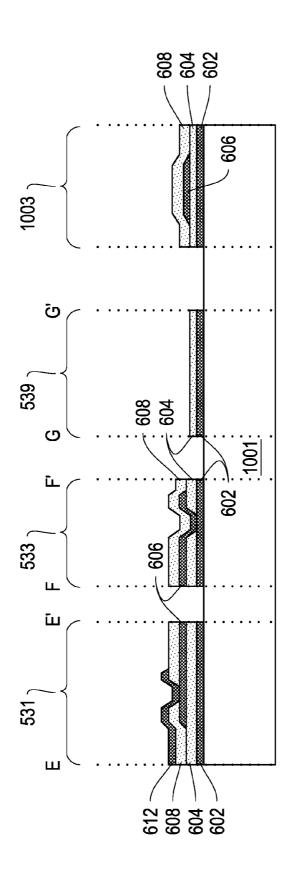

**[0025]** FIGS. **10A-10**F are cross sectional views of stages of construction of the control matrix of FIG. **5**C, according to an illustrative embodiment of the invention;

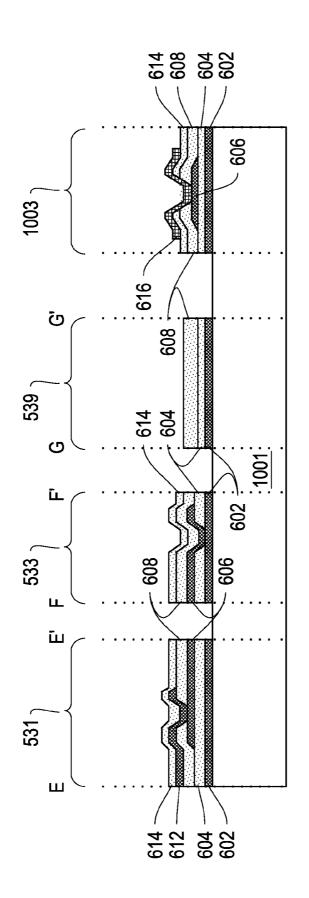

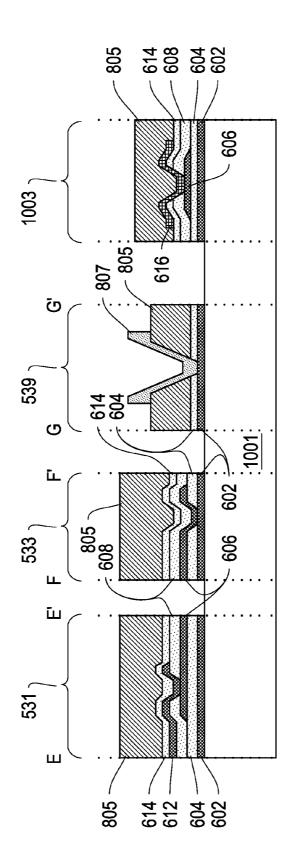

**[0026]** FIG. **11** is a cross sectional detail of a composite shutter assembly for use in the control matrix of FIG. **5**C, according to an illustrative embodiment of the invention;

**[0027]** FIGS. **12A-12**D are cross sectional views of stages of construction of the composite shutter assembly shown in FIG. **11**, according to an illustrative embodiment of the invention;

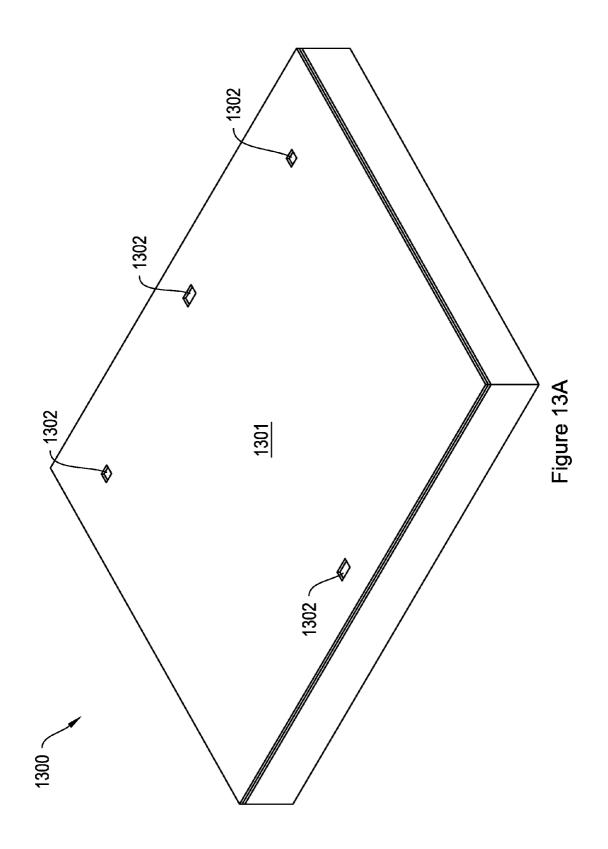

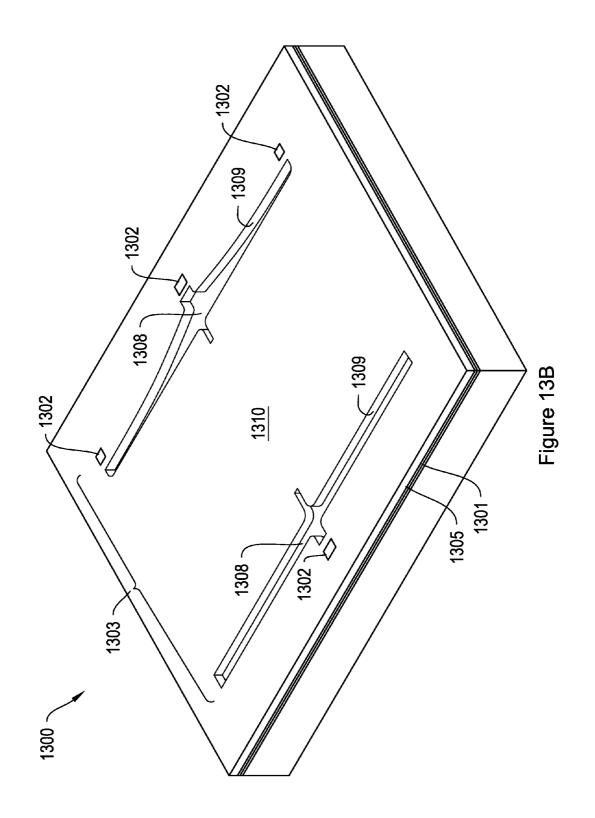

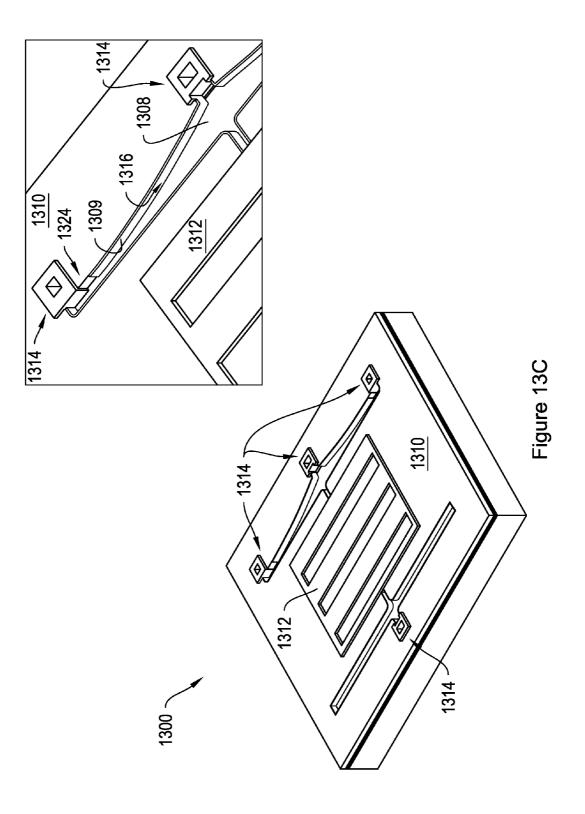

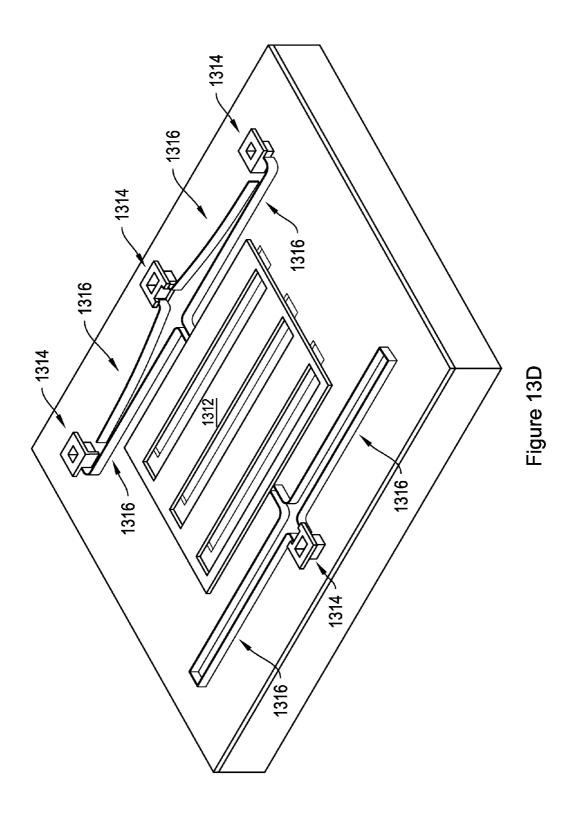

**[0028]** FIGS. **13A-13D** are isometric views of stages of construction of an alternate shutter assembly with narrow sidewall beams, according to an illustrative embodiment of the invention;

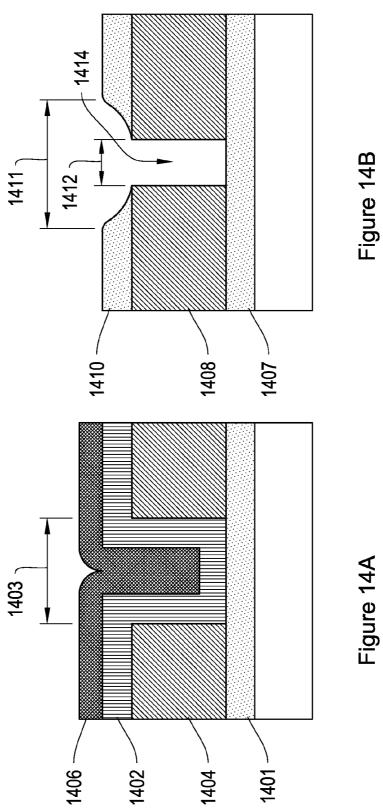

**[0029]** FIGS. **14**A and **14**B are cross sectional views of alternate methods for the formation of narrow beams, according to an illustrative embodiment of the invention;

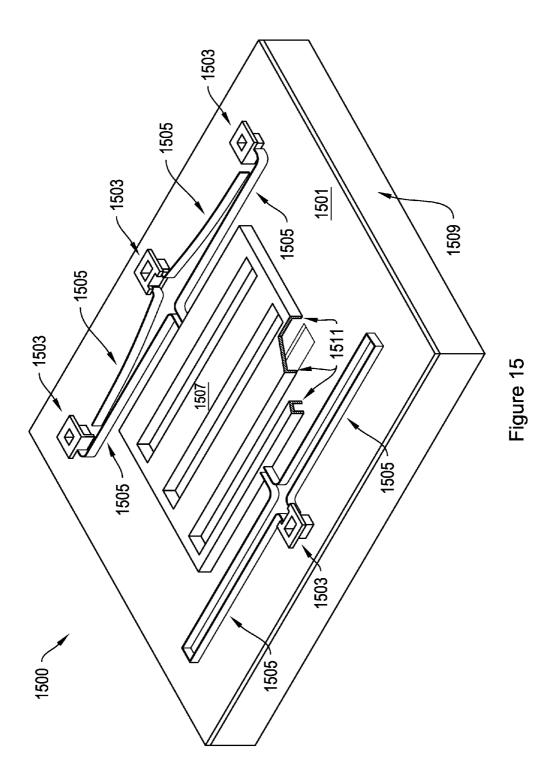

**[0030]** FIG. **15** is an isometric view of a shutter assembly with sidewall structures for improving strength, according to an illustrative embodiment of the invention;

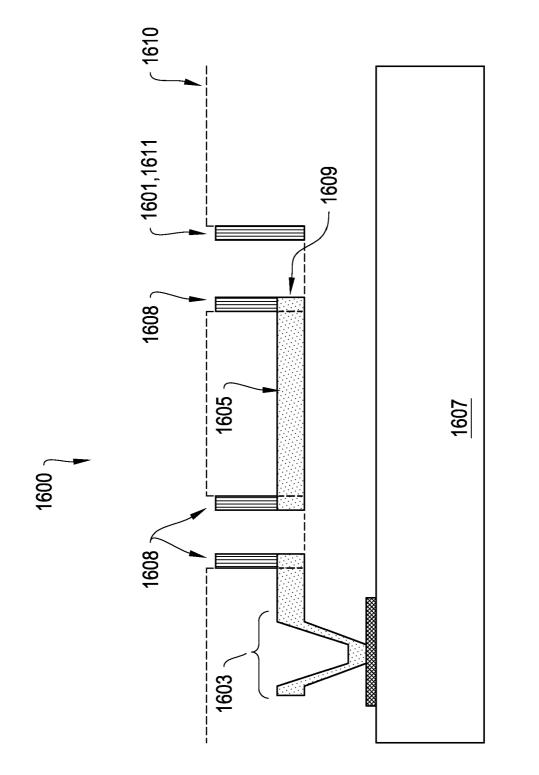

**[0031]** FIG. **16** is a cross section view of a shutter assembly wherein shutters and actuator beams are comprised of different materials, according to an illustrative embodiment of the invention;

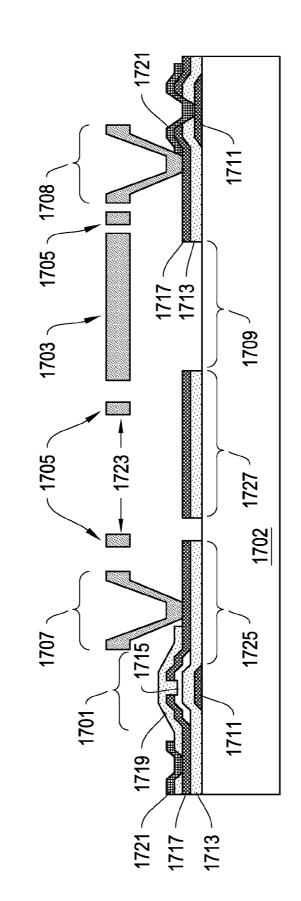

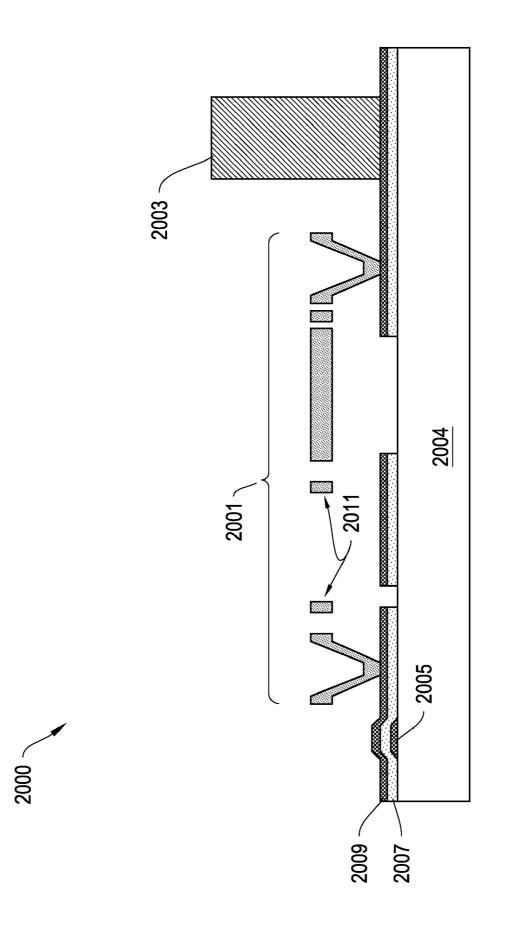

**[0032]** FIG. **17** is a cross section view of an alternate thin film structure for the shutter assembly, aperture, and associated control matrix, according to an illustrative embodiment of the invention;

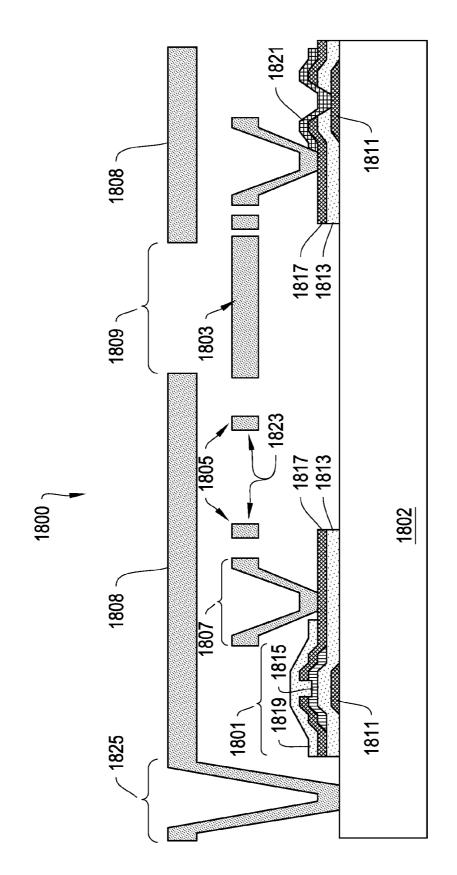

**[0033]** FIG. **18** is a cross section view of an alternate thin film structure for the shutter assembly, aperture, and associated control matrix, according to an illustrative embodiment of the invention;

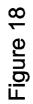

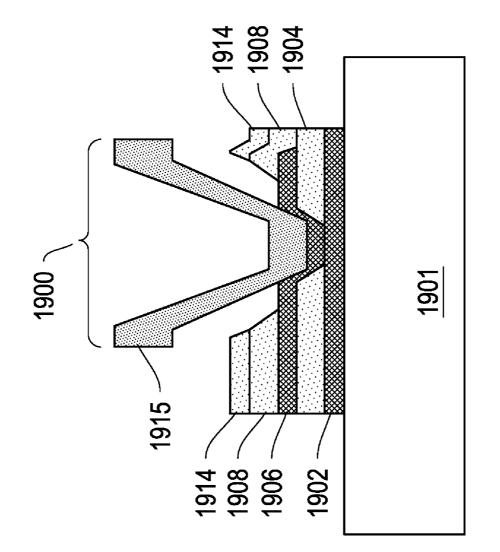

[0034] FIGS. 19A and 19B are cross sectional views of alternate via structures for use in a control matrix such as FIG. 5C, according to an illustrative embodiment of the invention; [0035] FIG. 20 is a cross section view of an alternate thin film structure including a shutter assembly and an assembly spacer; according to an illustrative embodiment of the invention;

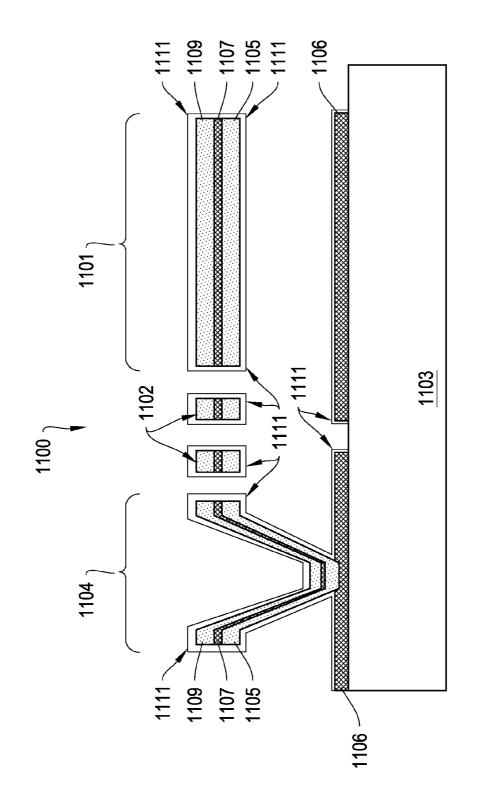

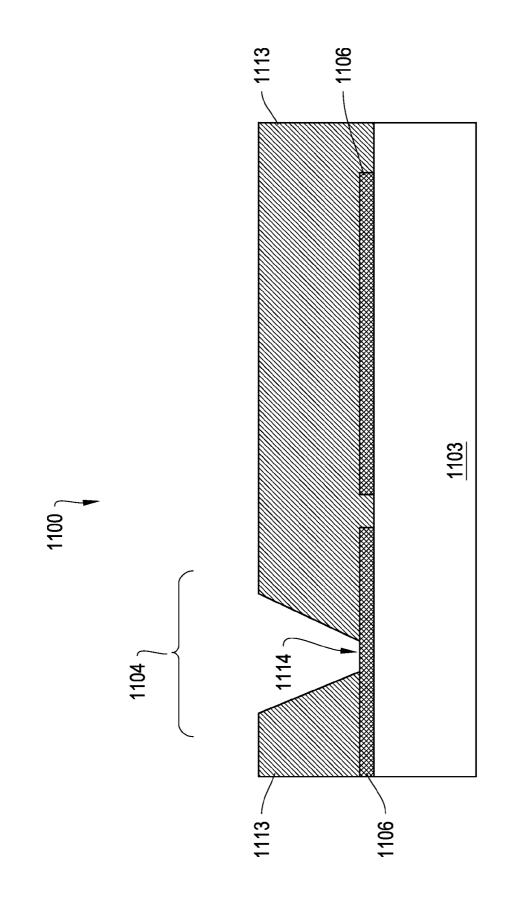

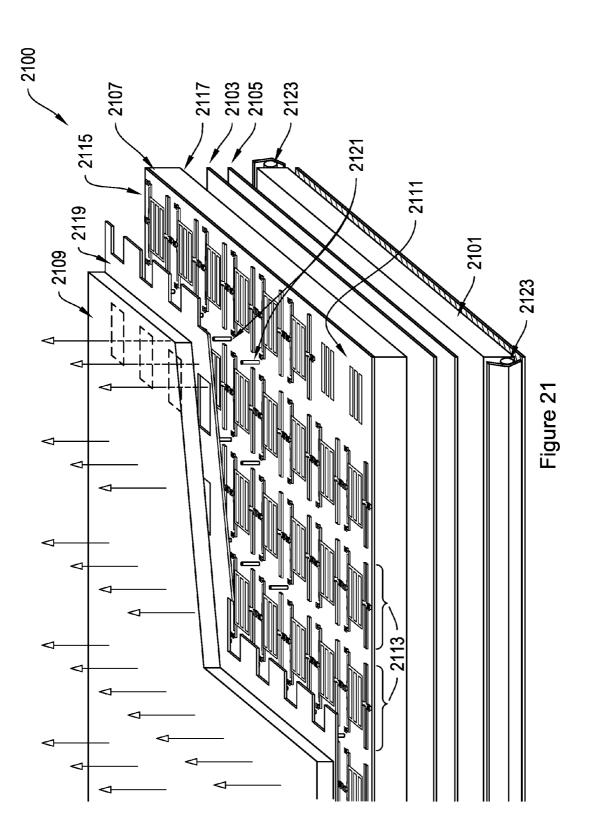

**[0036]** FIG. **21** is an assembly drawing of a display built into a MEMS-up configuration, according to an illustrative embodiment of the invention;

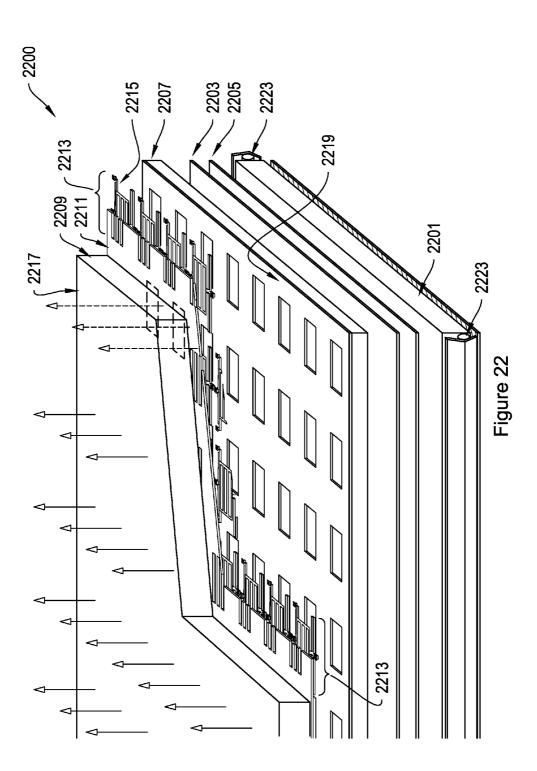

**[0037]** FIG. **22** is an assembly drawing of a display built into a MEMS-down configuration, according to an illustrative embodiment of the invention;

# DESCRIPTION OF CERTAIN ILLUSTRATIVE EMBODIMENTS

**[0038]** To provide an overall understanding of the invention, certain illustrative embodiments will now be described, including apparatus for displaying images and methods for manufacturing the same. However, it will be understood by one of ordinary skill in the art that the apparatus and methods described herein may be adapted and modified as is appropriate for the application being addressed and that the apparatus and methods described herein may be employed in other suitable applications, and that such other additions and modifications will not depart from the scope hereof.

[0039] FIG. 1A is an isometric view of a display apparatus 100, according to an illustrative embodiment of the invention. The display apparatus 100 includes a plurality of light modulators, in particular, a plurality of shutter assemblies 102a-102d (generally "shutter assemblies 102") arranged in rows and columns. In the display apparatus 100, shutter assemblies 102a and 102d are in the open state, allowing light to pass. Shutter assemblies 102b and 102c are in the closed state, obstructing the passage of light. By selectively setting the states of the shutter assemblies 102a-102d, the display apparatus 100 can be utilized to form an image 104 for a projection or backlit display, if illuminated by lamp 105. In another implementation the apparatus 100 may form an image by reflection of ambient light originating from the front of the apparatus.

[0040] In the display apparatus 100, each shutter assembly 102 corresponds to a pixel 106 in the image 104. In other implementations, the display apparatus 100 may utilize a plurality of shutter assemblies to form a pixel 106 in the image 104. For example, the display apparatus 100 may include three or more color-specific shutter assemblies 102, e.g., red, green and blue; red, green, blue and white; or cyan, magenta and yellow, etc. By selectively opening one or more of the color-specific shutter assemblies 102 corresponding to a particular pixel 106, the display apparatus 100 can generate a color pixel 106 in the image 104. In another example, the display apparatus 100 includes two or more shutter assemblies 102 per pixel 106 to provide grayscale in an image 104. With respect to an image, a "pixel" corresponds to the smallest picture element defined by the resolution of an image. With respect to structural components of the display apparatus 100, the term "pixel" refers to the combined mechanical and electrical components utilized to modulate the light that forms a single pixel of an image.

[0041] Each shutter assembly 102 includes a shutter 108 and an aperture 109. To illuminate a pixel 106 in the image 104, the shutter 108 is positioned such that it allows light to pass through the aperture 109 towards a viewer. To keep a pixel 106 unlit, the shutter 108 is positioned such that it obstructs the passage of light through the aperture 109. The aperture 109 is defined by an opening patterned through a reflective or light-absorbing material in each shutter assembly 102.

**[0042]** The display apparatus also includes a control matrix connected to the substrate and to the shutter assemblies for

controlling the movement of the shutters. The control matrix includes a series of electrical interconnects (e.g., interconnects 110, 112, and 114), including at least one write-enable interconnect 110 (also referred to as a "scan-line interconnect") per row of pixels, one data interconnect 112 for each column of pixels, and one common interconnect 114 providing a common voltage to all pixels, or at least to pixels from both multiple columns and multiples rows in the display apparatus 100. In response to the application of an appropriate voltage (the "write-enabling voltage,  $V_{we}$ "), the writeenable interconnect 110 for a given row of pixels prepares the pixels in the row to accept new shutter movement instructions. The data interconnects 112 communicate the new movement instructions in the form of data voltage pulses. The data voltage pulses applied to the data interconnects 112, in some implementations, directly contribute to an electrostatic movement of the shutters. In other implementations, the data voltage pulses control switches, e.g., transistors or other nonlinear circuit elements that control the application of separate actuation voltages, which are typically higher in magnitude than the data voltages, to the shutter assemblies 102. The application of these actuation voltages then results in the electrostatic driven movement of the shutters 108.

[0043] FIG. 1B is diagram of an illustrative shutter assembly 130 suitable for incorporation into the display apparatus 100 of FIG. 1A. The shutter assembly 130 includes a shutter 132 coupled to an actuator 134. The actuator 134 is formed from two separate compliant electrode beam actuators 135 (the "actuators 135"), as described in U.S. patent application Ser. No. 11/251,035, filed on Oct. 14, 2005. The shutter 132 couples on one side to the actuators 135. The actuators 135 move the shutter 132 transversely over a surface 133 in a plane of motion which is substantially parallel to the surface 133. The opposite side of the shutter 132 couples to a spring 137 which provides a restoring force opposing the forces exerted by the actuator 134.

[0044] Each actuator 135 includes a compliant load beam 136 connecting the shutter 132 to a load anchor 138. The load anchors 138 along with the compliant load beams 136 serve as mechanical supports, keeping the shutter 132 suspended proximate to the surface 133. The surface includes one or more aperture holes 141 for admitting the passage of light. The load anchors 138 physically connect the compliant load beams 136 and the shutter 132 to the surface 133 and electrically connect the load beams 136 to a bias voltage, in some instances, ground.

**[0045]** If the substrate is opaque, such as silicon, then aperture holes **141** are formed in the substrate by etching an array of holes through the substrate **204**. If the substrate **204** is transparent, such as glass or plastic, then the first step of the processing sequence involves depositing a light blocking layer onto the substrate and etching the light blocking layer into an array of holes **141**. The aperture holes **141** can be generally circular, elliptical, polygonal, serpentine, or irregular in shape.

[0046] Each actuator 135 also includes a compliant drive beam 146 positioned adjacent to each load beam 136. The drive beams 146 couple at one end to a drive beam anchor 148 shared between the drive beams 146. The other end of each drive beam 146 is free to move. Each drive beam 146 is curved such that it is closest to the load beam 136 near the free end of the drive beam 146 and the anchored end of the load beam 136. [0047] In operation, a display apparatus incorporating the shutter assembly 130 applies an electric potential to the drive beams 146 via the drive beam anchor 148. A second electric potential may be applied to the load beams 136. The resulting potential difference between the drive beams 146 and the load beams 136 pulls the free ends of the drive beams 146 towards the anchored ends of the load beams 136, and pulls the shutter ends of the load beams 136 toward the anchored ends of the drive beams 146 towards the drive beams 146, thereby driving the shutter 132 transversely towards the drive anchor 148. The compliant members 136 act as springs, such that when the voltage across the beams 136 and 146 potential is removed, the load beams 136 push the shutter 132 back into its initial position, releasing the stress stored in the load beams 136.

**[0048]** A shutter assembly, such as shutter assembly **130**, incorporates a passive restoring force, such as a spring, for returning a shutter to its rest position after voltages have been removed. Other shutter assemblies, as described in U.S. patent application Ser. Nos. 11/251,035 and 11/326,696, and as illustrated in FIG. **5**, incorporate a dual set of "open" and "closed" actuators and a separate sets of "open" and "closed" electrodes for moving the shutter into either an open or a closed state.

**[0049]** U.S. patent application Ser. Nos. 11/251,035 and 11/326,696 have described a variety of methods by which an array of shutters and apertures can be controlled via a control matrix to produce images, in many cases moving images, with appropriate gray scale. In some cases control is accomplished by means of a passive matrix array of row and column interconnects connected to driver circuits on the periphery of the display. In other cases it is appropriate to include switching and/or data storage elements within each pixel of the array (the so-called active matrix) to improve either the speed, the gray scale and/or the power dissipation performance of the display.

**[0050]** FIG. 2A is a conceptual diagram of an active control matrix 200 suitable for inclusion in the display apparatus 100 for addressing an array of pixels 240 (the "array 240"). Each pixel 201 includes an elastic shutter assembly 202, such as the shutter assembly 130 of FIG. 1B, controlled by an actuator 203. Each pixel also includes an aperture layer 250 that includes aperture holes 254. Further electrical and mechanical descriptions of shutter assemblies such as shutter assembly 202, and variations thereon, can be found in U.S. patent application Ser. Nos. 11/251,035 and 11/326,696.

**[0051]** The control matrix **200** is fabricated as a diffused or thin-film-deposited electrical circuit on the surface of a substrate **204** on which the shutter assemblies **202** are formed. The control matrix **200** includes a scan-line interconnect **206** for each row of pixels **201** in the control matrix **200** and a data-interconnect **208** for each column of pixels **201** in the control matrix **200**. Each scan-line interconnect **206** electrically connects a write-enabling voltage source **207** to the pixels **201** in a corresponding row of pixels **201**. Each data interconnect **208** electrically connects a data voltage source, ("Vd source") **209** to the pixels **201** in a corresponding column of pixels **201**. In control matrix **200**, the data voltage  $V_d$  provides the majority of the energy necessary for actuation of the shutter assemblies **202**. Thus, the data voltage source **209** also serves as an actuation voltage source.

**[0052]** FIG. 2B is an isometric view of a portion of the array of pixels 240 including the control matrix 200. Referring to FIGS. 2A and 2B, for each pixel 201 or for each shutter assembly in the array of pixels 240, the control matrix 200

includes a transistor 210 and a capacitor 212. The gate of each transistor 210 is electrically connected to the scan-line interconnect 206 of the row in the array 240 in which the pixel 201 is located. The source of each transistor 210 is electrically connected to its corresponding data interconnect 208. The actuators 203 of each shutter assembly include two electrodes. The drain of each transistor 210 is electrically connected in parallel to one electrode of the corresponding capacitor 212 and to the one of the electrodes of the corresponding actuator 203. The other electrode of the capacitor 212 and the other electrode of the actuator 203 in shutter assembly 202 are connected to a common or ground potential. [0053] In operation, to form an image, the control matrix 200 write-enables each row in the array 240 in sequence by applying  $V_{we}$  to each scan-line interconnect 206 in turn. For a write-enabled row, the application of  $V_{we}$  to the gates of the transistors 210 of the pixels 201 in the row allows the flow of current through the data interconnects 208 through the transistors to apply a potential to the actuator 203 of the shutter assembly 202. While the row is write-enabled, data voltages  $V_d$  are selectively applied to the data interconnects 208. In implementations providing analog gray scale, the data voltage applied to each data interconnect 208 is varied in relation to the desired brightness of the pixel 201 located at the intersection of the write-enabled scan-line interconnect 206 and the data interconnect 208. In implementations providing digital control schemes, the data voltage is selected to be either a relatively low magnitude voltage (i.e., a voltage near ground) or to meet or exceed  $V_{at}$  (the actuation threshold voltage). In response to the application of  $V_{at}$  to a data interconnect 208, the actuator 203 in the corresponding shutter assembly 202 actuates, opening the shutter in that shutter assembly 202. The voltage applied to the data interconnect 208 remains stored in the capacitor 212 of the pixel 201 even after the control matrix 200 ceases to apply  $V_{we}$  to a row. It is not necessary, therefore, to wait and hold the voltage  $V_{we}$  on a row for times long enough for the shutter assembly 202 to actuate; such actuation can proceed after the write-enabling voltage has been removed from the row. The voltage in the capacitors 212 in a row remain substantially stored until an entire video frame is written, and in some implementations until new data is written to the row.

[0054] The pixels 201 of the array 240 are formed on a substrate 204. The array includes an aperture layer 250, disposed on the substrate, which includes a set of aperture holes 254 for each pixel 201 in the array 240. The aperture holes 254 are aligned with the shutter assemblies 202 in each pixel. [0055] In alternative shutter assembly implementations, the shutter assembly together with the actuator can be made bi-stable. That is, the shutters can exist in at least two equilibrium positions (e.g. open or closed) with little or no power required to hold them in either position. More particularly, the shutter assembly can be mechanically bi-stable. Once the shutter of the shutter assembly is set in position, no electrical energy or holding voltage is required to maintain that position. The mechanical stresses on the physical elements of the shutter assembly can hold the shutter in place.

**[0056]** The shutter assembly together with the actuator can also be made electrically bi-stable. In an electrically bi-stable shutter assembly, there exists a range of voltages below the actuation voltage of the shutter assembly, which if applied to a closed actuator (with the shutter being either open or closed), hold the actuator closed and the shutter in position, even if an opposing force is exerted on the shutter. The opposing force may be exerted by a spring, or the opposing force may be exerted by an opposing actuator, such as an "open" or "closed" actuator.

# Generalized Process Flow

[0057] FIGS. 3A and 3B illustrate a first portion of a generalized process flow for fabrication of the pixels 201 of the array 240, according to an illustrative embodiment of the invention. In a first step, as illustrated in FIG. 3A, an aperture layer 250 is deposited and patterned onto a transparent substrate 204. In the second step, illustrated in FIG. 3B, the control matrix, including an array of thin film switches or transistors 210, is fabricated on top of the aperture layer 250 along with capacitors 212 and interconnects, such as scanline interconnect 206 or data interconnect 208. The processes employed to fabricate the transistors 210 shown in FIG. 3B can be typical of those known in the art for manufacturing active matrix arrays for use in liquid crystal displays. In the final step, the result of which is shown as FIG. 2B, a microelectro-mechanical (or MEMS) shutter assembly is formed on top of the array of thin film switches.

**[0058]** In one simple implementation, the aperture layer **250** is electrically isolated by an intervening dielectric layer from the control matrix. The aperture layer **250** can consist of thin film materials that are process compatible with the active matrix to be fabricated above it, but need not electrically connect to that active matrix. The aperture holes **254** can be generally circular, elliptical, polygonal, serpentine, or irregular in shape. In some implementations, the fabrication sequence for the second step (the formation of control matrix) need not include any switches, transistors, or capacitors but produces instead a lattice of row and column interconnects, separated by a dielectric layer. Such a control matrix is also referred to as a passive matrix as known in the art, for example, with respect to the fabrication of field emission cathodoluminescent displays.

**[0059]** In other implementations of the display, as will be described with respect to FIG. **17**, a separate aperture layer does not need to be fabricated as a first step in the sequence. The aperture holes may be fabricated instead using the same thin film materials and with the same processing steps used in the fabrication of active matrices or passive matrices directly onto glass substrates, as typically known in the art. Only the mask designs or pixel layouts need to be changed to accommodate the formation of aperture holes.

**[0060]** In another implementation, as will be described with respect to FIG. **18**, the aperture layer is fabricated as a last step in the processing sequence. The aperture layer is rigidly attached to the substrate but generally suspended above the shutter assembly, leaving room below for the free translational motion of the shutter assembly.

### The Aperture Layer

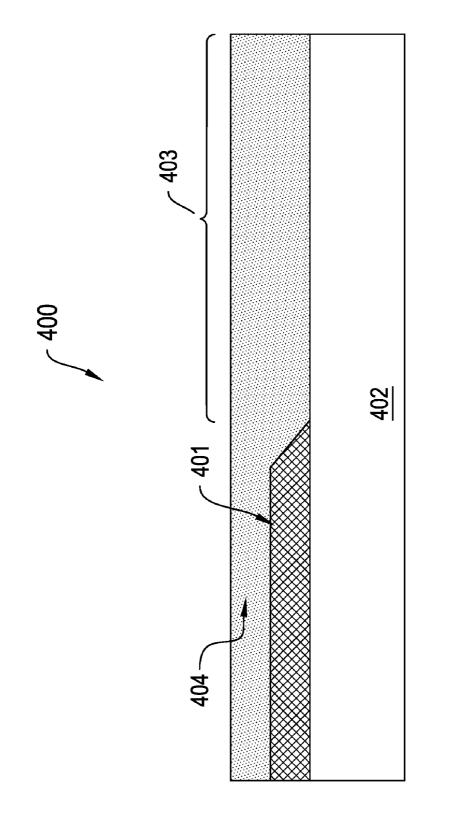

[0061] FIG. 4A illustrates one aperture layer structure 400 for the aperture layer 250 as might be produced in the first step of the fabrication sequence (FIG. 3A). The aperture layer structure 400 includes an aperture layer 401, deposited as a single thin film onto a glass substrate 402. The aperture layer 401 has been etched to produce a series of aperture holes 403 in the aperture layer 401. A dielectric layer 404 has been deposited over the top of the aperture layer 401 to isolate it from circuitry to be fabricated on top of it. The etched edge of the aperture layer **401** has been intentionally beveled to reduce the probability of cracks in the overlying dielectric layer **404**.

**[0062]** The aperture layer **401** is designed to block the passage of light from the backlight to the viewer. Appropriate materials for use as a light blocking aperture layer include metals, including without limitation Al, Cr, Au, Ag, Cu, Ni, Ta, Ti, Nd, Nb, W, Mo and/or alloys thereof. If deposited to thicknesses in excess of 30 nm such materials are effective at blocking the transmission of light. Deposition can be accomplished by evaporation, sputtering, or chemical vapor deposition.

[0063] In many implementations, it is preferable that the aperture layer 401 have the ability to absorb light. Most metal films absorb a certain fraction of light and reflect the rest. In some applications it is desired to avoid the reflection of ambient light impinging upon the aperture layer 401 to improve the contrast of the display. For such applications, the aperture layer 401 may be referred to as a "black matrix." Some metal alloys which are effective at absorbing light, i.e. for use in a black matrix, include, without limitation, MoCr, MoW, MoTi, MoTa, TiW, and TiCr. Metal films formed from the above alloys or simple metals, such as Ni and Cr with rough surfaces can also be effective at absorbing light. Such films can be produced by sputter deposition in high gas pressures (sputtering atmospheres in excess of 20 mtorr). Rough metal films can also be formed by the liquid spray or plasma spray application of a dispersion of metal particles, following by a thermal sintering step. A dielectric layer such as a dielectric layer 404 is then added to prevent spalling or flaking of the metal particles.

**[0064]** Semiconductor materials, such as amorphous or polycrystalline Si, Ge, CdTe, InGaAs, colloidal graphite (carbon) and alloys such as SiGe are also effective at absorbing light. These materials can be deposited in films having thicknesses in excess of 500 nm to prevent any transmission of light through the thin film. Metal oxides or nitrides can also be effective at absorbing light, including without limitation CuO, NiO, Cr<sub>2</sub>O<sub>3</sub>, AgO, SnO, ZnO, TiO, Ta<sub>2</sub>O<sub>5</sub>, MoO<sub>3</sub>, CrN, TiN, or TaN. The absorption of these oxides or nitrides improves if the oxides are prepared or deposited in non-stoichiometric fashion—often by sputtering or evaporation— especially if the deposition process results in a deficit of oxygen in the lattice. As with semiconductors, the metal oxides should be deposited to thicknesses in excess of 500 nm to prevent transmission of light through the film.

**[0065]** A class of materials, called cermets, is also effective at absorbing light. Cermets are typically composites of small metal particles suspended in an oxide or nitride matrix. Examples include Cr particles in a  $Cr_2O_3$  matrix or Cr particles in an SiO<sub>2</sub> matrix. Other metal particles suspended in the matrix can be Ni, Ti, Au, Ag, Mo, Nb, and carbon. Other matrix materials include TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, Al<sub>2</sub>O<sub>3</sub>, and Si<sub>3</sub>N<sub>4</sub>.

**[0066]** It is possible to create multi-layer absorbing structures using destructive interference of light between suitable thin film materials. A typical implementation would involve a partially reflecting layer of an oxide or nitride along with a metal of suitable reflectivity. The oxide can be a metal oxide e.g.  $CrO_2$ ,  $TiO_2$ ,  $Al_2O_3$  or  $SiO_2$  or a nitride like  $Si_3N_4$  and the metal can be suitable metals such as Cr, Mo, Al, Ta, Ti. In one implementation, for absorption of light entering from the substrate a thin layer, ranging from 10-500 nm of metal oxide is deposited first on the surface of substrate **402** followed by a 10-500 nm thick metal layer. In another implementation, for

absorption of light entering from the direction opposite of the substrate, the metal layer is deposited first followed by deposition of the metal oxide. In both cases the absorptivity of bi-layer stack can be optimized if the thickness of the oxide layer is chosen to be substantially equal to one quarter of 0.55 microns divided by the refractive index of the oxide layer.

**[0067]** In another implementation, a metal layer is deposited on a substrate followed by a suitable oxide layer of calculated thickness. Then, a thin layer of metal is deposited on top of the oxide such that the thin metal is only partially reflecting (thicknesses less than 0.02 microns). Partial reflection from the metal layer will destructively interfere with the reflection from substrate metal layer and thereby produce a black matrix effect. Absorption will be maximized if the thickness of the oxide layer is chosen to be substantially equal to one quarter of 0.55 microns divided by the refractive index of the oxide layer.

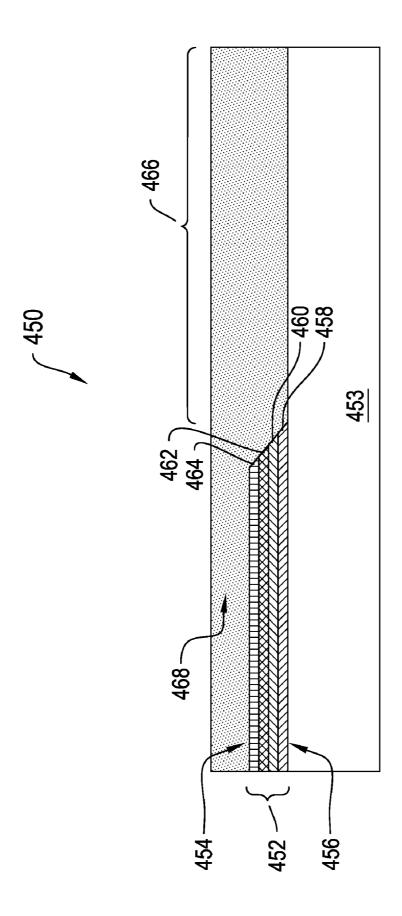

**[0068]** FIG. **4B** is an illustrative embodiment of a second aperture layer structure **450**. The second aperture layer structure **450** includes aperture layer **452**, which has one side which is reflective, while the other side is light-absorbing. As described in U.S. patent application Ser. No. 11/218,690, filed on Sep. 2, 2005, if one surface of an aperture layer is made of a reflective material, such as a metal, then the aperture layer can act as a mirror surface which recycles non-transmitted light back into an attached backlight for increased optical efficiency. Such reflectance can be enhanced if the metal is deposited in such as way as to produce a dense and smooth thin film, as can be achieved via sputtering or by ion assisted evaporation. Metal films with enhanced reflectivity include Ag, Au, and aluminum.

[0069] The aperture layer 452 is formed from a composite structure deposited on a substrate 453. The aperture layer 452 of FIG. 4B is designed to absorb light that impinges on the top surface 454 of the aperture layer 452, while reflecting light that is incident on the bottom 456 of the aperture layer 452, i.e. after transmission through the substrate 453. The aperture layer 452 includes 4 layers, a high refractive index layer 458, a low refractive index layer 460, a metal reflecting layer 462, and an absorbing layer 464. The aperture layer 452 is etched to form an aperture hole 466, and overlaid with a dielectric layer 468. Those skilled in the art will recognize that the coupling of refractive layers 458 and 460 with different refractive indices leads to a set of partially reflecting surfaces. By controlling the spacing between at least two of these partially reflecting surfaces it is possible to enhance the reflectivity of the film stack by means of optical interference. Multi-layer films can be designed to provide high reflectivity across a broad band of wavelengths or to have high reflectivity at a discrete number of individual wavelengths, for instance wavelengths that are matched to those emitted from the backlight.

**[0070]** Thin films which are candidates for the high refractive index layer **458** include, without limitation,  $TiO_2$ ,  $HfO_2$ ,  $Ta_2O_5$ ,  $Nb_2O_5$ ,  $Cr_2O_3$ ,  $Sc_2O_3$ ,  $Bi_2O_3$ ,  $In_2O_3$ , and  $Al_2O_3$ . Thin films which are candidates for the low index refractive layer **460** include  $SiO_2$ ,  $Si_3N_4$ , MgF<sub>2</sub>, CaF<sub>2</sub>, and HfF<sub>4</sub>, and diamond-like carbon. These films can be deposited by reactive sputtering, reactive evaporation, ion-assisted evaporation, ion-assisted ion beam sputtering, or by chemical vapor deposition. FIG. **4**B shows only a single pairing of a high index refractive layer with a low index refractive layer. Those skilled in the art will appreciate that the reflectivity can be enhanced by depositing, in sequence, multiple pairs of these

refractive layers. In many cases the reflectivity can be maximized for the visible spectrum if the thickness of each refractive layer (**460** and **458**) is chosen to be substantially equal to one quarter of 0.55 microns divided by the refractive index of the layer.

[0071] Any one of the two refractive layers 458 or 460 can be eliminated from the aperture layer 456 while still enhancing to a substantial degree the reflectivity of the aperture layer 452 over that of a simple metal deposited on top of a transparent substrate 453. Improvements can result as long as the refractive layer that is interposed between the metal layer 462 and the transparent substrate 453 has a refractive index less than that of the substrate 453.

[0072] The metal reflecting layer 462 in the aperture layer 452 will not only reflect incident light but also acts to block the transmission of light. Any of the metal films, and/or semiconductor materials, listed above for use as a light blocking aperture layer, may be utilized for the metal reflecting layer. [0073] The absorbing layer 464 acts to prevent reflections of light that arrive from the side opposite to that of the substrate 453. Any of the absorbing materials listed above for use with a black matrix may be employed as the top-most layer of the aperture layer 452.

**[0074]** The etch processes needed to form the aperture holes **466** can include RF or DC plasma etching, ion sputtering, or wet chemical etching.

**[0075]** In another implementation of the aperture layer **452**, a 2-layer thin film stack can be formed. First a metal film with enhanced reflectivity, such as Ag, Au, or Al, is deposited on a surface. Then one of the absorbing black matrix materials, listed above, is deposited on top of the metal.

**[0076]** There are implementations in which the order of the layers in the composite aperture layer shown in FIG. **4**B are preferably reversed, with the absorbing layer lying next to the substrate and the reflecting film stack pointing away from the substrate. Such implementations will be described with respect to FIG. **22**.

[0077] A preferred embodiment for fabrication of composite aperture layer 452 proceeds as follows: First, for the high refractive index layer 458, a 54 nm±3 nm thick layer of TiO<sub>2</sub> is deposited by reactive sputter deposition of Ti in a partial pressure of O<sub>2</sub>. Next, for the low refractive index layer 460, a 91 nm±5 nm film of SiO<sub>2</sub> is deposited by reactive sputter deposition of  $SiO_2$  in a partial pressure of  $O_2$ . Next, for the metal reflecting layer 462, a 100 nm±5 nm film of smooth Al is deposited by sputter deposition in a high vacuum, nonoxidizing ambient. Next, the three film 458, 460, and 462 are patterned to form aperture holes 466. Typical photoresists are applied as known in the art, then UV-exposed through photomask with the pattern of aperture holes 466. The photoresist is then chemically developed into an etching mask. The etching of the 3-film stack is performed with an ion beam milling system, with Ar ions, which removes each of the films in sequence but does not remove all the photoresist. After the etch of the thin films is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through ozone and/or plasma ashing.

**[0078]** Next, as the first component of absorbing layer **464**, a thin film of  $Si_3N_4$  with thickness 250 nm±10 nm is deposited by plasma assisted chemical vapor deposition. Next, as the second component of absorbing layer **464**, a 500 nm±40 nm thick layer of amorphous silicon is deposited by plasma assisted chemical vapor deposition. These films are then patterned with a similar photomask to form aperture holes **466**

using a photoresist expose and develop step similar to that described above. The etching of  $Si_3N_4$  and the amorphous silicon is then performed by means of reactive ion etching. Finally a 50 nm±4 nm film of  $Al_2O_3$  is deposited in blanket fashion by atomic layer deposition.

#### The Control Matrix

**[0079]** In another implementation the aperture layer can be utilized as one of the electrical components of the control matrix, with its own electrical connections to the control matrix in the upper layers. FIGS. **5**A through **5**C illustrate such an integrated design.

[0080] FIG. 5A is a schematic diagram of another control matrix 500 suitable for inclusion in the display apparatus 100 for addressing an array of pixels. Control matrix 500 controls an array of pixels 502 that include dual-actuator shutter assemblies 504 (i.e., shutter assemblies with both shutteropen and shutter-close actuators). FIG. 5B is a plan view layout of portions of two neighboring pixels 502 from an array of pixels 502. The layout of FIG. 5B provides one example of how the electrical components of control matrix 500 can be arranged within a pixel 502 for concurrent fabrication of an array of pixels 502 on a substrate. FIG. 5C is identical to FIG. 5B, and calls out additional features of the pixels 502. A layout such as FIG. 5B/5C can be utilized to produce photomasks for each of the functional layers of the pixels 502. The components of control matrix 500 are built up from a sequence of functional layers, and the photomasks are used to print the arrayed pattern for each layer across the substrate 505. The pixels in the array 502 are each substantially square in shape with a pitch, or repeat distance between pixels, in the range of 180 to 200 microns. FIG. 5C shows cross sectional markers AA'-GG', used as reference for the cross-sectional illustration of the sequential layers of various electrical and mechanical components, to be described with reference to FIGS. 6, 7, 8 and 10.

**[0081]** For purposes of illustration, only the conductor layers, semiconductor layers, and shutter layers are provided in detail in FIG. **5**B/**5**C. The locations of other patterned features, such as vias cut into dielectric layers or holes patterned into the aperture layer are indicated by symbol markings and/or dotted lines.

**[0082]** Referring to FIGS. **5**A and **5**B, the control matrix **500** includes a scan-line interconnect **506** for each row of pixels **502** in the control matrix **500**. The control matrix **500** also includes two data interconnects: one data-open interconnect **508***a* and one data-closed interconnect **508***b*, for each column of pixels **502** in the control matrix **500**. The control matrix **500** further includes a pre-charge interconnect **510**, a global actuation interconnect **514**, and a shutter common interconnect **515**. These interconnects **510**, **514** and **515** are shared among pixels **502** in multiple rows and multiple columns in the array. In one implementation (the one described in more detail below), the interconnects **510**, **514** and **515** are shared among all pixels **502** in the control matrix **500**.

[0083] Each pixel 502 in the control matrix includes a shutter-open charge transistor 516, a shutter-open discharge transistor 518, a shutter-open write-enable transistor 517, and a data store capacitor 519. Each pixel 502 in the control matrix 500 also includes a shutter-close charge transistor 520, and a shutter-close discharge transistor 522, a shutter-close writeenable transistor 527, and a data store capacitor 529.

**[0084]** Each pixel **502** in the control matrix includes a variety of via structures, which are indicated by the symbol of a

box with diagonals in FIG. **5**B/**5**C. Control matrix **500** includes several M1-M2 vias **531** (i.e., a via connecting a first metal layer M1 to a second metal layer M2), an Ap-M1 via **533** (i.e., a via connecting an aperture layer **547** to the first metal layer M1), two drive anchors **535**, four compliant drive beams **537**, four shutter anchors **539**, four compliant load beams **541**, an aperture hole **543**, and a shutter **545**. The aperture hole **543** is indicated by dotted line.

[0085] Portions of two neighboring pixels 502 are illustrated in FIGS. 5B and 5C. For each pixel 502 the shutter 545 closes over the aperture hole 543 by moving to the left. The shutter open actuation electronics for each pixel, including the transistors 516, 517, and 518, are positioned immediately to the right of each shutter assembly 504, (the two pixels are equivalent, but the shutter-open electronics are only included in FIG. 5B/5C for the left-most shutter assembly 504). The shutter close electronics for each pixel, including the transistors 520, 522, and 527, are positioned immediately to the left of each shutter assembly (again, the pixels 502 are equivalent, but the shutter-closed electronics are only illustrated for the right-most shutter assembly 504).

[0086] For a given pixel 502, the compliant load beams 541 mechanically connect the shutter 545 to the four shutter anchors 539 and suspend the shutter 545 above the substrate surface. The compliant drive beams 537, positioned adjacent to the load beams 541, are mechanically connected to the drive anchors 535. One set of drive beams 537 (located to the right of the shutter 545) is mechanically connected to a drive anchor and electrically connected, by means of both drive anchor 535 and an M1-M2 via 531, to the drain of the shutteropen charge transistor 516. By applying a voltage, greater than a minimum actuation voltage, between the drive beams 537 and load beams 541 on the right side of the shutter 545, the shutter 545 can be caused to move into the open position-i.e. to move away from the aperture hole 543. Together, the set of drive beams 537 and load beams 541 to the right of the shutter forms a shutter open actuator. The other set of drive beams 537 (located to the left of each shutter 545) is mechanically connected to a drive anchor 535 and electrically connected, by means of both the drive anchor 535 and an M1-M2 via 531, to the drain of the shutter-close charge transistor 520. By causing a voltage, greater than a minimum actuation voltage, to appear between the drive beams 537 and load beams 541 on the left side of the shutter 545, the shutter 545 can be caused to move into the closed position (as illustrated in FIG. 5B/5C)—i.e. to position over the top of aperture hole 543. The set of drive beams 537 and load beams 541 located to the left of the shutter 545 form a shutter close actuator.

**[0087]** In operation, the control matrix **500** is designed for independent control of distinct electrical functions, namely a) pre-charge of the actuators, b) pixel addressing and data storage, and c) global actuation of the pixels.

[0088] At the beginning of each frame addressing cycle the control matrix 500 applies a voltage to the pre-charge interconnect 510 which, because it is connected to both gate and drain of the shutter-open and shutter-close charge transistors 516 and 520, acts to turn both of these transistors 516 and 520 on. The pre-charge interconnect 510 is pulsed to a voltage in excess of the minimum required for actuation of the shutter 545, for instance to a voltage that exceeds 15 volts or in some embodiments exceeds 30 volts. After the actuators of each of the shutter-open and shutter-closed actuators have become charged, the voltage on the pre-charge interconnect 510 is returned to zero, and both of the shutter-open and shutterclose transistors **516** and **520** then return to their off states. The charge provided to each of the shutter-open and shutterclose actuators remains stored on each of the actuators since the transistors that feed these actuators have been returned to their off states.

[0089] Each row is then write-enabled in sequence, by placing a write-enable voltage  $V_{we}$  onto the scan line interconnect 506. While a particular row of pixels 502 is write-enabled, the control matrix 500 applies a data voltage to either the data-open interconnect 508*a* or the data-closed interconnect 508*b* corresponding to each column of pixels 502 in the control matrix 500. The application of  $V_{we}$  to the scan-line interconnect 506 for the write-enabled row turns on both of the write-enable transistors 517 and 527 of the pixels 502 in the corresponding scan line. The voltages applied to the data interconnects 508*a* and 508*b* are thereby allowed to be stored on the data store capacitors 519 and 529 of the respective pixels 502. Generally, to ensure proper actuation, a data voltage is allowed to be stored on only one storage capacitor 519 or 529 per shutter assembly 504.

[0090] In control matrix 500 the global actuation interconnect 514 is connected to the source of the both the shutteropen discharge switch transistor 518 and the shutter-close discharge transistor 522. Maintaining the global actuation interconnect 514 at a potential significantly above that of the shutter common interconnect 515 prevents the turn-on of any of the discharge switch transistors 518 or 522, regardless of what charge is stored on the capacitors 519 and 529. Global actuation in control matrix 500 is achieved by bringing the global actuation interconnect 514 to a potential that is equal to or less than that of the shutter common interconnect 515, making it possible for the discharge switch transistors 518 or 522 to turn-on in accordance to the whether a data voltage has been stored on ether capacitor 519 or 520. When switched to the on state, the shutter-open discharge switch transistor 518 or the shutter-close discharge transistor 522 will allow the charge to drain away from one or the other of their respective actuators. By turning on only the shutter-open discharge transistor 518, for example, the charge stored on drive beams 537 to the right of shutter 545 will drain out through the drive anchor 535, the M1-M2 via 531, through transistor 518, and out through the global actuation interconnect 514. As a result, a voltage exceeding the minimum actuation voltage will remain only between the shutter and the drive beams to the left of the shutter, and the shutter will be caused to move to the left and into the closed position.

[0091] Applying partial voltages to the data store capacitors **519** and **521** allows partial turn-on of the discharge switch transistors **518** and **522** during the time that the global actuation interconnect **514** is brought to its actuation potential. In this fashion, an analog voltage can be created on the shutter assembly **504**, providing for analog gray scale.

**[0092]** The layout shown in FIG. **5**B/5C includes portions of two neighboring pixels, between which some of the interconnects are singly assigned and some of the interconnects are shared in common. Each of these pixels contains one data-open interconnect **508***a* and one data-closed interconnect **508***b*, connecting all of the pixels **502** vertically along a single column of control matrix **500**. The two neighboring pixels **502** in FIG. **5**B/5C also share a common scan-line interconnect **506**, which connects all pixels **502** horizontally along a single row of control matrix **500**. The two neighboring pixels, however, share the pre-charge interconnect **510** and the global actuation interconnect **514** between them. These

two interconnects, oriented along the column direction, are placed between each of the two pixels **502** with electrical connections, through M1-M2 vias **531**, feeding voltage signals to both pixels on the right and on the left. At the periphery of the display (not shown) the pre-charge interconnect lines **510** and the global actuation interconnect lines **514** from multiple columns are further connected, respectively, to other pre-charge interconnect lines and other global actuation interconnect lines.

[0093] The control matrix 500 includes a shutter common interconnect 515, which in the layout of FIG. 5B/5C is established by a separate conducting layer, referred to as the aperture layer 547. The aperture layer 547, as was illustrated in FIGS. 3A and 3B, is fabricated as a distinct layer that underlies all other layers of the control matrix 500. In the preferred embodiment, the aperture layer 547 is fabricated from conductive materials. The patterned outline of the aperture layer is not illustrated in FIG. 5B/5C except for the location of the aperture hole 543. In control matrix 500, the aperture layer is used to make common electrical connection between all shutters 545 in all rows and all columns by means of the shutter anchors 539.

## Alternate Layouts

[0094] It should be appreciated that FIG. 5B/5C is just one example of a layout appropriate to the construction of control matrix 500. Many other equivalent layouts are possible. For instance the common interconnects 510 and 514 have been routed along the column direction in FIG. 5B/5C, but other embodiments are possible in which these interconnects are routed along the row direction. In FIG. 5B/5C the common interconnects 510 and 514 are established and/or patterned at the same metal level as the source and drain connections to the transistors, such as transistor 518. Other embodiments are possible, however, where these common interconnects 510 and 514 are established at the gate level of the thin film transistors, and still other embodiments are possible where these interconnects can be patterned as independent electrical connectors located in the underlying conductive aperture layer 547.

[0095] In the layout of control matrix 500 shown in FIG. 5B/5C, the shutter assemblies 504 are aligned such that the shutters 545 move in a direction parallel to the scan line interconnect 506. Other embodiments are possible in which the shutters 545 move parallel to the data interconnects 508*a* and 508*b*. Embodiments are also possible in which the electrical components such as transistor 518 or capacitor 519 are disposed not just to the left or right but also above or below the shutter assemblies 504. In FIG. 5B/5C the electrical components occupy different areas within the pixel 502. Other embodiments are possible, however, where components such as transistor 518 or capacitor 519 are built on other thin film layers which underlie the shutter assembly 504.

[0096] A number of different thin film switches, known in the art, can be utilized for the operation of control matrix 500. FIG. 6 illustrates one of several suitable switch structures in cross section. The structure illustrated in FIG. 6 includes the cross section of a transistor, such as shutter open discharge transistor 518. The structure of transistor 518 is similar to that used in the art for active matrix liquid crystal displays. The structure 600 of FIG. 6 also includes an electrode interconnect 601, such as are commonly used to connect to pixel capacitors in a liquid crystal display or as are commonly used connect to driver circuits on the periphery of a display. Transistor **518** represents, in particular, a structure that is known in the art as the inverted staggered back-channel-etched thin film transistor. Descriptions of the formation and function of this particular transistor as well as others can be found in the literature, such as in *Active Matrix Liquid Crystal Displays* by Willem den Boer (Elsevier, Amsterdam, 2005).

[0097] The transistor **518** is built from a distinct set of thin films or layers, the fabrication process for which will be described in more detail with respect to FIGS. **7-10**. In particular the transistor **518** is disposed on top of an aperture layer **602**. On top of the aperture layer is placed a first dielectric layer **604**. The elements of the transistor **518** include a first conductor layer **606**, a second dielectric layer **608**, a first semiconductor layer **610**, a second conductor layer **612**, a third dielectric layer **614**, and a third conductor layer **616**. The first conductor layer is also referred to in the art as a gate metal layer and transistor **518** is referred to as a bottom-gate transistor. The second conductor layer is also referred to in the art as a connector to the source and drain of the transistor **518**. The third conductor layer is also referred to in the art as an electrode or contact metal.

**[0098]** The semiconducting layer **610** is commonly formed from amorphous or polycrystalline silicon. The amorphous silicon can be deposited by either plasma enhanced chemical vapor deposition (PECVD) or by hot wire deposition from a precursor gas such as  $SiH_4$ . Other semiconducting materials that can be used at layer **610** include diamond-like carbon, Si, Ge, GaAs, CdTe or alloys thereof. Other techniques for formation of the semiconducting layer include low pressure chemical vapor deposition and sputtering.

**[0099]** The top surface of semiconducting layer **610** is doped with an impurity to increase the conductivity of the amorphous silicon and to provide for an ohmic contact between the amorphous silicon and the second conductor layer **612**. Conductivity-enhancing dopants typically used with either amorphous or polycrystalline silicon include phosphorus, arsenic, boron, or aluminum. These dopants can be included as part of a deposition step, i.e. by mixing dopant precursors with SiH<sub>4</sub> in the PECVD chamber, or added later by means for diffusion from a dopant gas or by ion implantation.

[0100] Thin film switches, such as representative transistor 518 shown in FIG. 6, are fabricated from a sequence of deposition, masking, and etch steps. The number of masks and/or deposition steps required for the formation of thin film switches, such as transistor 518, can vary between 3 and 10. At the same time, the deposition, patterning, and etching steps used to form the thin film switches are also used to form thin film components such as array interconnects between pixels, capacitors, or to form electrode contacts to driver chips on the periphery of the display. Similar and/or additional processing steps can be adapted to form thin film components useful in the MEMS shutter display, e.g. to form electrical connections between thin film switches and the aperture layer, such as aperture layer 602, or to form electrical connections between the switches, array interconnects, and the shutter assembly, such as shutter assembly 202 or shutter assembly 504.

#### Fabrication Procedure 700

**[0101]** FIG. 7 illustrates one example of a manufacturing process or procedure 700 for construction of a control matrix and associated shutter assembly. The procedure 700 of FIG. 7 includes steps for the formation of an aperture layer, such as aperture layer 250 or aperture layer 602. The procedure 700

also includes steps for the formation of a switch or transistor, such as transistor **210** or transistor **518**. The procedure **700** also includes steps for the fabrication of a shutter assembly, such as shutter assembly **202** or shutter assembly **504**. Procedure **700** of FIG. **7** is described below with respect to the formation of an inverted, staggered, back-channel etched transistor such as transistor **518**. Modifications or alternatives to procedure **700**, as may be appropriate for simplification of the process or for the formation of alternative thin film switches and control matrices will be discussed later with respect to FIG. **9**.

**[0102]** The procedure **700** begins at step **705** with the formation of an aperture layer **602** on a substrate. The aperture layer formation **705** includes the cleaning of the substrate, which can be glass or plastic, followed by the deposition and etch of the aperture layer **602**. Several implementations of step **705** have already been described with respect to FIGS. **4**A and **4**B. In some cases the aperture layer can be a composite aperture layer such as aperture layer **452**.

**[0103]** The procedure **700** continues at step **710** with the deposition and etch of the first dielectric layer, such as dielectric layer **604**. Suitable dielectric materials include, without limitation, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, HfO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub>, which can be deposited either by sputtering, evaporation, or chemical vapor deposition to thicknesses on the order of 0.1 to 2.0 microns. Typical photoresists are applied as known in the art, then UV-exposed through photomask patterns, such as are illustrated in layouts such as FIG. **5**, and finally developed into an etching mask. After the etch of the dielectric layer **604** is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through ozone and/or plasma ashing. Etch processes that can be used to pattern the first dielectric layer **604** include RF or DC plasma etching, sputter etching, or wet chemical etching.

[0104] The procedure 700 continues at step 715 with the deposition and etch of the first conductor layer, such as conductor laver 606. Suitable conductor materials include, without limitation, Al, Cu, Ag, Ni, Cr, Mo, W, Ti, Ta, Nd, Nb and alloys or combinations thereof. Some typical alloys used in the art include TiW, MoW, MoCr, AlNd, AlTa, and AlCr. Bilayer metals are also useful for application as the first conductive layer 606. Some bilayer metals that are useful include Cr on Al, Ta on Al, Ta on Ag, Ti on Al, or Mo on Al. Trilayer metal configurations are also known in the art, including Cr/Al/Cr or Cr/Al/Ti or Ti/Al/Ti, Cr/Al/Ta, or Cr/Ag/Ta. These metals or combinations of metals can be applied by DC or RF sputtering, evaporation, or in some cases by chemical vapor deposition. Suitable thicknesses can be in the range of 0.1 to 1.0 microns. For patterning of the first conducting layer 606, typical photoresists are applied as known in the art and exposed through photomask patterns such as are illustrated in layouts such as FIG. 5. After the etch of the conducting layer is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through ozone and/or plasma ashing. Etch processes that can be used to pattern the first conductor layer include RF or DC plasma etching, sputter etching, reactive ion milling, and/or wet chemical etching.

**[0105]** The procedure **700** continues at step **720** with the deposition and etch of the second dielectric layer, such as dielectric layer **608**. Suitable dielectric materials include, without limitation, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, HfO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub>, which can be deposited either by sputtering, evaporation, or chemical vapor deposition to thicknesses on the order

of 0.1 to 2.0 microns. Patterning is achieved by means of typical photoresists as known in the art and exposed through photomask patterns such as are illustrated in layouts like FIG. **5**. After the etch of the dielectric is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through ozone and/or plasma ashing. Etch processes that can be used to pattern the second dielectric layer **608** include RF or DC plasma etching, sputter etching, or wet chemical etching.

[0106] The procedure 700 continues at step 725 with the deposition and etch of the first semiconductor layer, such as semiconductor layer 610. Amorphous silicon is a typical semiconductor material applied at this step, deposited with a PECVD process at deposition temperatures in the range of 250 to 350 C. Polycrystalline silicon is an alternate semiconductor material for thin film transistors, but as will be shown in FIG. 9, the polycrystalline layer is typically applied at a step preceding, or situated below the first conductor laver 606. For the inverted, staggered, back channel etch transistor 518, a dual layer of amorphous silicon is deposited. For the first part of layer 610, amorphous silicon is deposited without any dopants to thicknesses in the range of 0.1 to 0.2 microns. The second part of layer 610 includes the deposition of heavily n-doped amorphous silicon, typically through the inclusion of PH3 gas in the PECVD chamber. The second or upper part of layer 610 is thinner, typically in the range of 0.02 to 0.05 microns. Patterning of the amorphous silicon transistor islands is then achieved by means of typical photoresists as known in the art and exposed through photomask patterns such as are illustrated in layouts such as FIG. 5. After the etch of the semiconductor is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through plasma ashing. Etch processes that can be used to pattern semiconductor islands include RF or DC plasma etching, sputter etching, reactive ion milling, or wet chemical etching.

[0107] The procedure 700 continues at step 730 with the deposition and etch of the second conductor layer, such as conductor layer 612. Suitable conductor materials include, without limitation, Al, Cu, Ag, Au, Ni, Cr, Mo, W, Ti, Ta, Nd, Nb and alloys or combinations thereof. Some typical alloys used in the art include TiW, MoW, MoCr, AlNd, AlTa, and AlCr. Bilayer metals are also useful for application as the first conductive layer. Some bilayer metals that are useful include Cr on Al, Ta on Al, Ta on Ag, Ti on Al, or Mo on Al. Trilayer metal configurations are also known in the art, including Cr/Al/Cr, or Cr/Al/Ti, or Ti/Al/Ti, or Cr/Al/Ta, or Cr/Ag/Ta. These metals or combinations of metals can be applied by DC or RF sputtering, evaporation, or in some cases by chemical vapor deposition. Suitable thicknesses can be in the range of 0.1 to 1.0 microns. For patterning of the second conducting layer 612, typical photoresists are applied as known in the art and exposed through photomask patterns such as are illustrated in layouts like FIG. 5. After the etch of the second conducting layer 612 is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through plasma ashing. Etch processes that can be used to pattern the second conductor layer 612 include RF or DC plasma etching, sputter etching, reactive ion milling, and/or wet chemical etching.

**[0108]** The procedure **700** continues at step **735** with the deposition and etch of the third dielectric layer, such as dielectric layer **614**. Suitable dielectric materials include  $SiO_2$ ,  $Si_3N_4$ ,  $Al_2O_3$ ,  $TiO_2$ ,  $HfO_2$ , and  $Ta_2O_5$ , which can be

deposited either by sputtering, evaporation, or chemical vapor deposition to thicknesses on the order of 0.2 to 2.0 microns. Patterning is achieved by means of typical photoresists as known in the art and exposed through photomask patterns such as are illustrated in layouts such as FIG. **5**. After the etch of the dielectric is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through plasma ashing. Etch processes that can be used to pattern the third dielectric layer **614** include RF or DC plasma etching, sputter etching, or wet chemical etching.

[0109] The procedure 700 continues at step 740 with the deposition and etch of the third conductor layer, such as conductor layer 616. Suitable conductor materials include, without limitation, Al, Cu, Ag, Au, Ni, Cr, Mo, W, Ti, Ta, Nd, Nb and alloys or combinations thereof. For the third conductor layer 616, which can serve as a contact or electrode layer, other conductive materials are applicable such as indium-tinoxide (ITO), indium zinc oxide (IZO), Al-doped tin oxide, fluorine-doped tin oxide, silver alloys and/or gold alloys. Other alloys, bi-layers, and/or tri-layers as listed for use as the second conductor layer 612 are also applicable. These metals or combinations of metals can be applied by DC or RF sputtering, evaporation, or in some cases by chemical vapor deposition. Suitable thicknesses can be in the range of 0.1 to 1.0 microns. For patterning of the third conducting layer 616, typical photoresists are applied as known in the art and exposed through photomask patterns such as are illustrated in layouts such as FIG. 5. After the etch of the third conductor layer 616 is complete the remaining photoresist is removed with either an aqueous or solvent-based stripper compound or through plasma ashing. Etch processes that can be used to pattern the third conductor layer 616 include RF or DC plasma etching, sputter etching, and/or wet chemical etching. [0110] The procedure 700 continues at step 745 with the deposition and patterning of the sacrificial layer, such as sacrificial layer 805 illustrated below in FIG. 8F. Suitable sacrificial layers 805 include polymers such as polyimide, dielectrics such as SiO<sub>2</sub>, or soft metals such as copper or aluminum. In some cases the sacrificial material is patterned by adding a layer of photoresist as known in the art, which is then exposed through a photomask and developed to form an etching mask. Etch processes available for the sacrificial materials include RF or DC plasma etching or wet chemical etching. In some cases sacrificial materials are available which are themselves photo-definable, meaning their patterns can be established by direct exposure to UV radiation through a photomask followed by immersion in a bath or spray of developer chemicals. In either case the pattern which is formed in the sacrificial layer 805 will act as a mold for the subsequent formation of the shutter layer 807. The sacrificial layer 805 is not removed until step 760 of procedure 700. Further details on available sacrificial materials are described with reference to FIG. 12.

**[0111]** The procedure **700** continues at step **750** with the deposition and patterning of the shutter layer, such as shutter layer **807** illustrated in FIG. **8**G. Suitable shutter materials used by themselves include, without limitation, metals such as Al, Cu, Ni, Cr, Mo, Ti, Ta, Nb, Nd, or alloys thereof; dielectric materials such as  $Al_2O_3$ ,  $SiO_2$ ,  $Ta_2O_5$ , or  $Si_3N_4$ ; or semiconducting materials such as diamond-like carbon, Si, Ge, GaAs, CdTe or alloys thereof. Further discussion of the material properties preferred for the shutter layer **807** can be found with reference to FIG. **11**. Layered combinations of

shutter layer materials can also be employed as further described under FIG. **11**. Shutter layers **807** can be deposited to thicknesses in the range of 0.1 microns to 5 microns. The deposition techniques that can be utilized for thicker shutter materials include DC or RF sputtering, chemical vapor deposition, and/or evaporation. In some cases the shutter material can be deposited from solution by electroless plating or electroplated after deposition of a conducting seed layer onto the exposed surfaces of the sacrificial layer **805**.

**[0112]** The procedure **700** continues at step **755** with the removal of the sacrificial layer **805**. This step, also referred to as the release step, is intended to free the shutter layer from the mold onto which it was deposited and enable elements formed in the shutter layer **807** to move freely, or at least move as constrained by its actuators and anchors or supports to the substrate. Polymer sacrificial layers **805** can be removed in an oxygen plasma, or in some cases by thermal pyrolysis. Certain inorganic sacrificial layers **805** (such as SiO<sub>2</sub>, Si, Cu, or Al) can be removed by wet chemical etching and/or vapor phase etching.

**[0113]** The procedure **700** continues at step **760** with the addition of a dielectric coating layer, such as dielectric coating **813** illustrated in FIG. **8**H. Dielectric coatings **813** can be applied in conformal fashion, such that all bottom, tops, and side surfaces of the shutters and beams are uniformly coated. Such thin films can be grown by thermal oxidation and/or by conformal chemical vapor deposition of an insulator such as  $Al_2O_3$ ,  $Cr_2O_3$ ,  $TiO_2$ ,  $HfO_2$ ,  $V_2O_5$ ,  $Nb_2O_5$ ,  $Ta_2O_5$ ,  $SiO_2$ , or  $Si_3N_4$ , or by depositing similar materials by means of atomic layer deposition. The dielectric coating layer **813** can be applied with thicknesses in the range of 10 nm to 1 micron. In some cases sputtering and evaporation can be used to deposit the dielectric coating **813** onto sidewalls.

[0114] The procedure 700 concludes at step 765 with the cleaning of contact pads. Since the dielectric coating 813 deposited at step 760 coats all surfaces uniformly, it is useful to remove the dielectric coating 813 over contact pads at the periphery of the display, where electrical connections need to be made to driver chips or source voltages. In one embodiment, a sputter etch using an inert gas such as Ar is sufficient to remove the dielectric coating 813 from all exposed surfaces. The sputter etch is preferably applied after the active area of the display has been protected or sealed with a cover sheet (such as a separate piece of glass). The cover sheet prevents the sputter etch from removing dielectric material from any of the shutter assemblies in the pixel area.

[0115] In another embodiment, which avoids the sputter etch at step 765, it is possible to pre-treat all contact areas on the periphery of the display so that the dielectric coating 813 applied at step 760 does not adhere to the contact areas and cannot therefore impede an ohmic contact. Such a non-adhering pre-treatment can be achieved by the spray or liquiddispensed application of certain compounds around the periphery of the display which alter the chemical reactivity of the contact surface. Exemplary surface treatments include the family of trichlorosilanes of chemical composition CH<sub>3</sub>  $(CH_2)_x$ SiCl<sub>3</sub> where x is a number greater than 7 and less than 30, perfluoro-octyltrichlorosilane (FOTS) and dimethyldichlorosilane (DMDCS). Alternative surface treatments include the group of alkanethiols of chemical composition  $CH_3(CH_2)$ , SH, where x is a number greater than 7 and less than 30. Such pre-treatments can be effective at blocking the deposition of certain dielectric materials if the deposition is carried out at low temperatures, usually less than 200 degrees

C. Such low temperature dielectric depositions can be achieved with the use of atomic layer chemical vapor deposition. The cleaning of the contact pads at step **765** can then be as simple as a heat treatment, exposure to UV radiation, or exposure to ozone to remove organic materials from the bond pads.

**[0116]** In another embodiment which avoids the sputter etch at step **765**, it is possible to cover or passivate the contact areas on the periphery of the display with a sacrificial material before deposition of the dielectric material at step **760** of procedure **700**. Examples of sacrificial materials which can be applied include photoresist, silicone sealing materials, or polydimethylsiloxane (PDMS). These are materials that can withstand the temperatures required for the dielectric deposition at step **760**, in the range of 100 to 300 C. A nozzle dispense tool can be used to deposit a relatively thick layer of these materials selectively in the region of the contact pads.

**[0117]** In the latter embodiment, where the contact area has been previously coated with a sacrificial material before the dielectric deposition, step **765** of procedure **700** entails a removal of the sacrificial material as well as any overlying dielectric material. In some cases the removal of the sacrificial material can be accomplished through a combination of mechanical abrasion, wet chemical or solvent dissolution, and/or oxygen plasma. In cases where the sacrificial material was deposited as a coherent and thick (>20 micron) film of sealant or elastomeric material, the sacrificial material may simply be pulled away with forceps or tweezers. The contact pads can then be further cleaned with either a detergent or a mild acid wash.

**[0118]** It should be appreciated that procedure **700** illustrates one sequence of processes appropriate to the formation of a control matrix, such as control matrix **500**, but many other process sequences are possible. In some cases the ordering of the steps can be altered. FIG. **9**, for instance, illustrate a structure for a top-gate polycrystalline silicon thin film transistor in which the semiconducting layer **610** is deposited after the first dielectric layer **604** and before the first conducting layer **606**.