## (12) 发明专利

(10) 授权公告号 CN 108886355 B

(45) 授权公告日 2022.03.29

(21) 申请号 201780018467.0

(72) 发明人 R·K·纳德卡尔尼

(22) 申请日 2017.03.10

A·科雷亚莱二世

(65) 同一申请的已公布的文献号

(74) 专利代理机构 北京市金杜律师事务所

申请公布号 CN 108886355 A

11256

(43) 申请公布日 2018.11.23

代理人 王茂华

(30) 优先权数据

(51) Int.CI.

15/087,812 2016.03.31 US

H03K 3/012 (2006.01)

(85) PCT国际申请进入国家阶段日

H03K 3/356 (2006.01)

2018.09.19

H03K 19/00 (2006.01)

H03K 19/017 (2006.01)

(86) PCT国际申请的申请数据

(56) 对比文件

PCT/US2017/021935 2017.03.10

CN 102624373 A, 2012.08.01

(87) PCT国际申请的公布数据

US 2008123382 A1, 2008.05.29

W02017/172329 EN 2017.10.05

US 5015880 A, 1991.05.14

(73) 专利权人 高通股份有限公司

US 2005077919 A1, 2005.04.14

地址 美国加利福尼亚州

审查员 杨苏倩

权利要求书2页 说明书10页 附图7页

## (54) 发明名称

高效功率电压电平转换器电路

## (57) 摘要

所公开的系统和方法涉及一种高效功率电压电平转换器。在其中第一电压域的第一供电电压(vdd1)与第二电压域的第二供电电压(vdd2)不同的正常模式中，所述电压电平转换器(250)转换所述第一电压域中的输入信号(a,a\_n)为所述第二电压域中的输出信号。在其中所述第一供电电压与所述第二供电电压大体上相同的旁路模式中，旁路电路(252)经配置以绕过所述电压电平转换器(250)且在所述第一电压域中提供所述输入信号作为所述输出信号，由此在所述旁路模式中避免所述电压电平转换器引入的延迟。此外，下电电路(275)经配置以在所述旁路模式中，但不在所述正常模式中，下电所述电压电平转换器。

1. 一种电子设备,其包括:

电压电平转换器,其经配置以,在其中第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中,转换所述第一电压域中的输入信号为所述第二电压域中的输出信号;

旁路电路,其经配置以,在其中所述第一供电电压与所述第二供电电压大体上相同的旁路模式中,基于旁路信号绕过所述电压电平转换器,且在所述第一电压域中提供所述输入信号作为所述输出信号;

下电电路,其经配置以在所述旁路模式中,但不在所述正常模式中,基于所述旁路信号下电所述电压电平转换器;以及

经配置以在所述旁路模式中,连接所述电压电平转换器的输出节点到供电电压或接地以防止所述输出节点在所述旁路模式中浮动的电路,其中该电路包括第四上拉晶体管,所述第四上拉晶体管被配置为在所述旁路模式中将所述电压电平转换器的输出节点连接至所述第二供电电压。

2. 根据权利要求1所述的电子设备,其中所述下电电路包括第一下拉晶体管,其经配置以在所述旁路模式中关断到所述电压电平转换器的接地连接。

3. 根据权利要求2所述的电子设备,其中所述下电电路包括经配置以,在所述旁路模式中,连接所述电压电平转换器的所述输出节点到所述第二供电电压的第一上拉晶体管。

4. 根据权利要求1所述的电子设备,其中所述下电电路包括经配置以,在所述旁路模式中,关断所述第二供电电压与所述电压电平转换器之间连接的第二上拉晶体管。

5. 根据权利要求4所述的电子设备,其中所述下电电路包括第二下拉晶体管,其经配置以在所述旁路模式中连接所述电压电平转换器的所述输出节点到接地。

6. 根据权利要求4所述的电子设备,其中所述下电电路进一步包括第三下拉晶体管,其经配置以在所述旁路模式中关断所述电压电平转换器与接地之间的连接。

7. 根据权利要求1所述的电子设备,其中所述旁路电路包括多路复用器,其经配置以在所述旁路模式中选择所述第一电压域中的所述输入信号,以及在所述正常模式中选择所述第二电压域中的所述电压电平转换器的所述输出节点。

8. 根据权利要求1所述的电子设备,其中所述第一电压域对应于包括逻辑单元的逻辑电压域,且所述第二电压域对应于包括存储器单元的存储器电压域,其中所述旁路模式对应于加速模式。

9. 根据权利要求1所述的电子设备,其集成到选自由以下组成的群组的装置中:机顶盒、音乐播放器、视频播放器、娱乐单元、导航装置、通信装置、个人数字助理PDA、固定位置数据单元、服务器、移动电话及计算机。

10. 一种电压电平转换的方法,所述方法包括:

在第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中,在电压电平转换器中转换所述第一电压域中的输入信号为所述第二电压域中的输出信号;

在所述第一供电电压与所述第二供电电压大体上相同的旁路模式中,基于旁路信号绕过所述电压电平转换器且在所述第一电压域中提供所述输入信号作为所述输出信号;

在所述旁路模式中,但不在所述正常模式中,基于所述旁路信号下电所述电压电平转换器;以及

在所述旁路模式中,连接所述电压电平转换器的输出节点到所述第二供电电压或接地以防止所述输出节点在所述旁路模式中浮动,其中将所述电压电平转换器的输出节点连接到第二电压包括导通第四上拉晶体管以在所述旁路模式中将所述电压电平转换器的输出节点连接到所述第二供电电压。

11.根据权利要求10所述的方法,其中下电所述电压电平转换器包括在所述旁路模式中断开第一下拉晶体管来将所述电压电平转换器自接地连接关断。

12.根据权利要求10所述的方法,其中下电所述电压电平转换器包括断开第二上拉晶体管,所述第二上拉晶体管经配置以在所述旁路模式中关断所述第二供电电压与所述电压电平转换器之间的连接。

13.根据权利要求10所述的方法,其包括在所述旁路模式中选择所述第一电压域中的所述输入信号,以及在所述正常模式中选择所述第二电压域中的所述电压电平转换器的所述输出节点。

14.根据权利要求10所述的方法,其中所述第一电压域对应于包括逻辑单元的逻辑电压域,且所述第二电压域对应于包括存储器单元的存储器电压域,其中所述旁路模式对应于加速模式。

15.一种电子设备,其包括用于执行根据权利要求10到14中任一权利要求所述的方法的装置。

## 高效功率电压电平转换器电路

### 技术领域

[0001] 所公开的方面涉及用于处理系统的电压电源。更具体地说，示范性方面针对于用于第一电压域与第二电压域之间的电压电平转换的高效功率电压电平转换器电路。

### 背景技术

[0002] 现代的处理系统(例如，系统级芯片或“SOC”)可包含多种子系统或组件，其可具有不同频率和功率考量。相应地，SOC的不同部分可具有不同供电电压。举例来说，存储器系统可包含存储器单元(例如，静态随机存取存储器或“SRAM”单元)，其可以供应有更高供电电压，而中央处理单元(central processing unit, CPU)或处理器核心的逻辑单元可能支持更低供电电压。因此，SOC可以被设计具有两个或超过两个电压岛或电压域(例如，逻辑电压域、存储器电压域等)，各电压域具有被定制成适合电压域中的组件(例如，逻辑单元、存储器单元等)的电压考量的对应电压电源。

[0003] 可能存在跨越两个电压域的信号，例如，逻辑电压域中的CPU发布的，到存储器电压域中的存储器系统的读取或写入命令。对于这种信号，转换电路，其在本领域中被称为“电压电平转换器”，可以被提供来将信号从第一电压域转换到第二电压域。然而，在一些情况下，可以动态地缩放一或多个电压域的电压，这可以导致第一和第二电压域的供电电压相等或大体上相同(例如，在“加速模式”中，如在本领域中已知，其中逻辑电压域的先前低供电电压可以被缩放到更高的供电电压来以更高的频率操作逻辑单元，并且其中逻辑电压域的更高供电电压可以大体上与存储器电压域的供电电压相同)。在所述情况下，将不需要第一和第二电压域之间的电压电平转换器，这是因为第一和第二电压域的供电电压大体上相同。

[0004] 然而，在常规的设计中，电压电平转换器可能仍然激活，且不必要地执行第一和第二电压域之间的信号的电压转换，即使第一和第二电压域的供电电压大体上相同。通过保持激活和处于信号路径中，电压电平转换器始终消耗功率且在信号路径中添加延迟，甚至当电压电平转换不被需要时也是如此。

### 发明内容

[0005] 本发明的示范性方面针对于用于高效功率电压电平转换器的系统和方法。在第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中，电压电平转换器转换所述第一电压域中的输入信号为所述第二电压域中的输出信号。在所述第一供电电压与所述第二供电电压大体上相同的旁路模式中，旁路电路经配置以绕过所述电压电平转换器且在所述第一电压域中提供所述输入信号作为所述输出信号，由此在所述旁路模式中避免所述电压电平转换器引入的延迟。进一步，下电电路经配置以在所述旁路模式中下电所述电压电平转换器，而不在所述正常模式中如此做。

[0006] 举例来说，一个示范性方面是针对一种设备，其包括：电压电平转换器，其经配置以，在第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中，转换

所述第一电压域中的输入信号为所述第二电压域中的输出信号；旁路电路，其经配置以，在所述第一供电电压与所述第二供电电压大体上相同的旁路模式中，绕过所述电压电平转换器，且在所述第一电压域中提供所述输入信号作为所述输出信号；以及下电电路，其经配置以在所述旁路模式中，但不在所述正常模式中，下电所述电压电平转换器。

[0007] 另一个示范性方面是针对电压电平转换的方法，所述方法包括：在第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中，在电压电平转换器中转换所述第一电压域中的输入信号为所述第二电压域中的输出信号；在所述第一供电电压与所述第二供电电压大体上相同的旁路模式中，绕过所述电压电平转换器且在所述第一电压域中提供所述输入信号作为所述输出信号；以及在所述旁路模式中，但不在所述正常模式中，下电所述电压电平转换器。

[0008] 又另一个示范性方面是针对一种设备，其包括：用于在第一电压域的第一供电电压与第二电压域的第二供电电压不同的正常模式中，转换所述第一电压域中的输入信号为所述第二电压域中的输出信号的装置；用于在所述第一供电电压与所述第二供电电压大体上相同的旁路模式中，绕过所述用于的转换装置，且在所述第一电压域中提供所述输入信号作为所述输出信号的装置；以及用于在所述旁路模式中，但不在所述正常模式中，下电所述电压电平转换器的装置。

## 附图说明

[0009] 呈现附图以辅助描述本发明的方面，且仅仅是为了说明所述方面而非限制所述方面而提供附图。

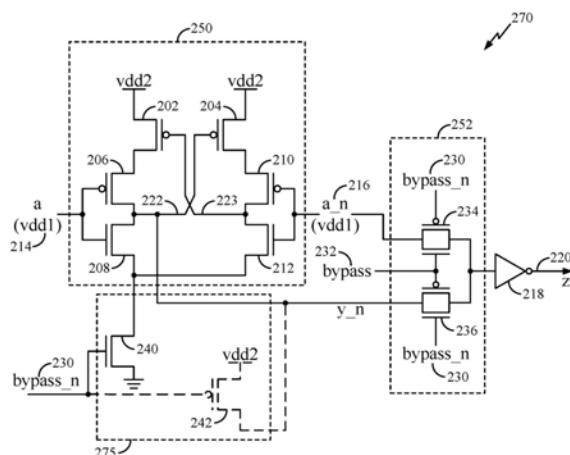

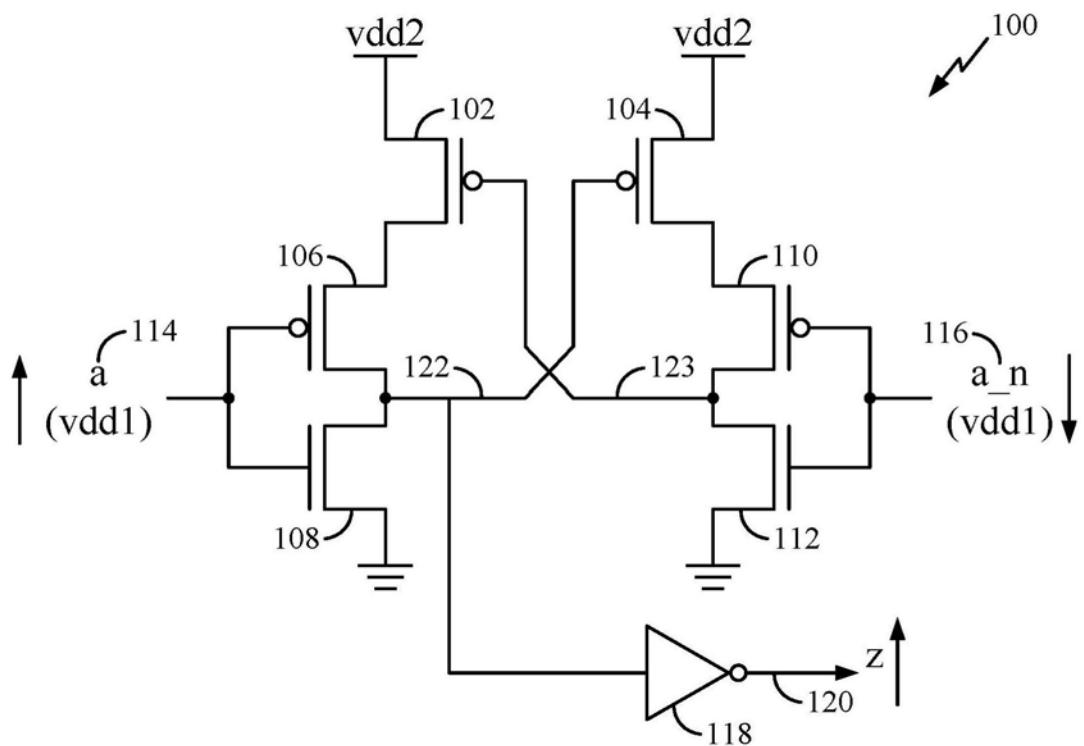

[0010] 图1A到B说明常规的电压电平转换器。

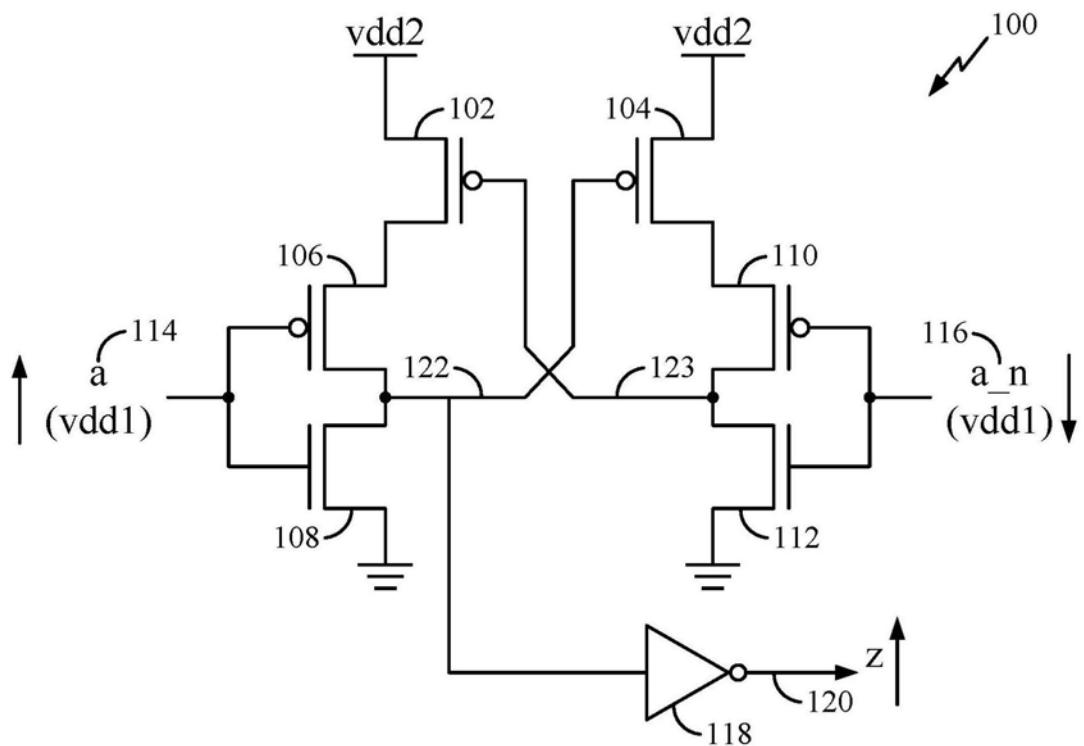

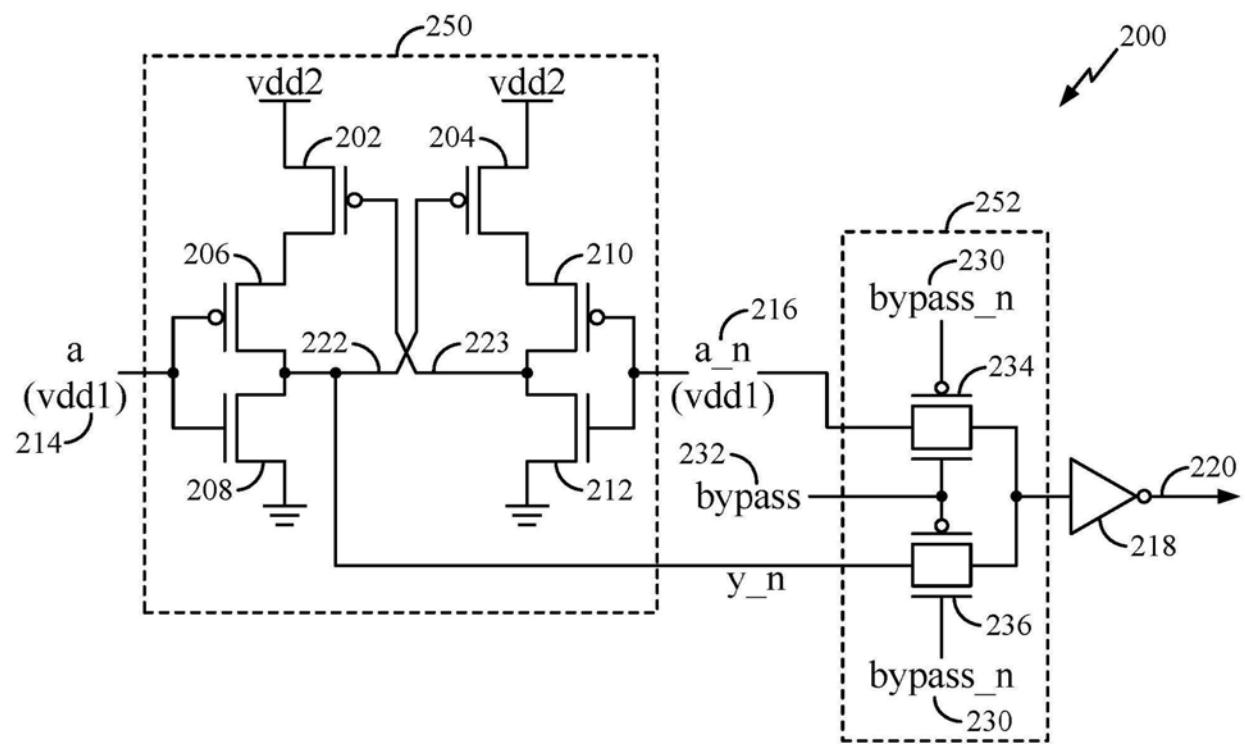

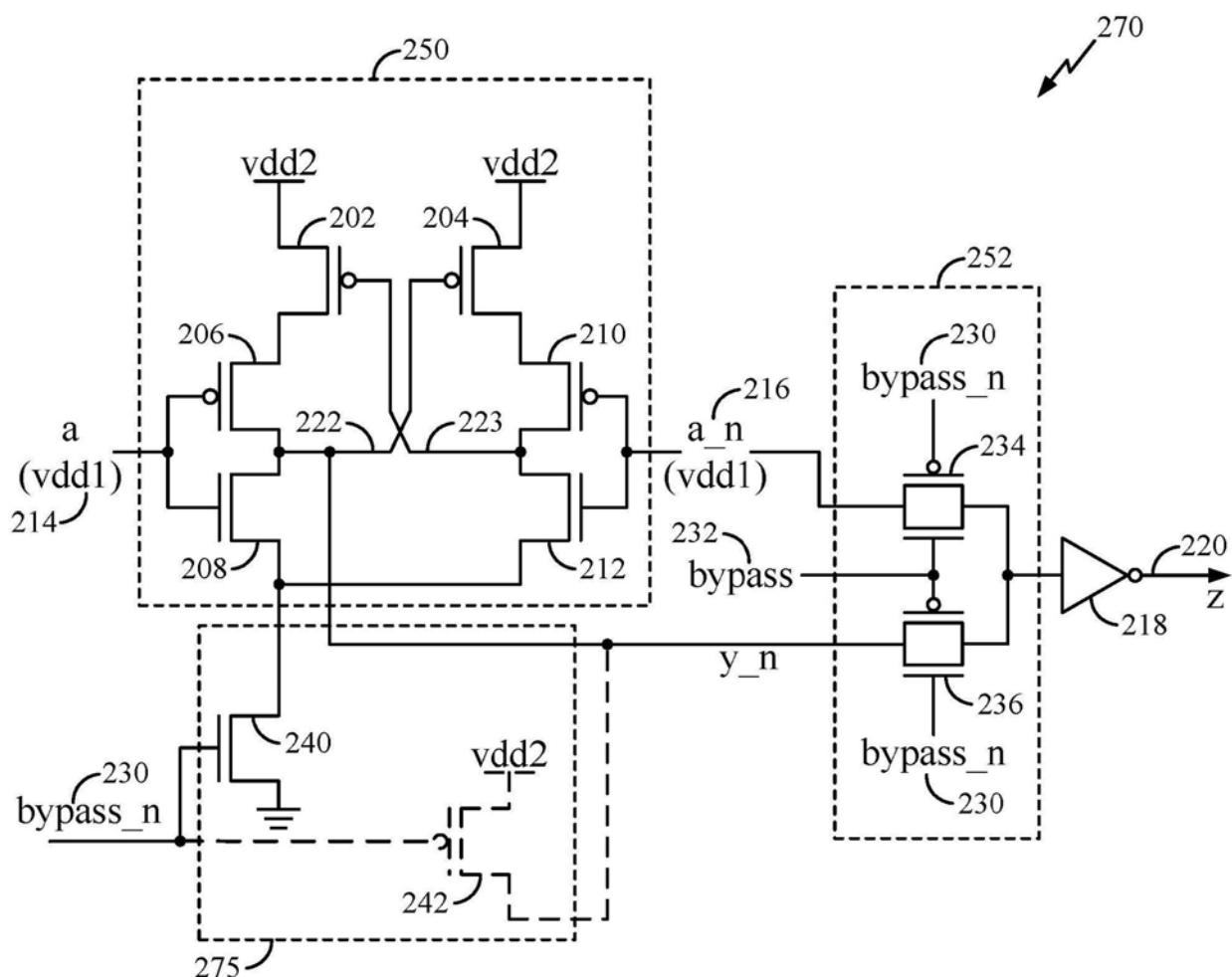

[0011] 图2A到D根据本发明的示范性方面说明关于电压电平转换器的电路。

[0012] 图3根据本发明的示范性方面说明对应于执行电压电平转换的方法的框图。

[0013] 图4说明其中可有利地利用本发明的方面的示范性计算装置。

## 具体实施方式

[0014] 在以下针对本发明的具体方面的描述和相关图式中公开本发明的各方面。可在不脱离本发明的范围的情况下设计替代方面。另外，将不会详细描述或将省略本发明的众所周知的元件以免混淆本发明的相关细节。

[0015] 词语“示范性”在本文中用于意味着“充当实例、例子或说明”。本文中描述为“示范性”的任何方面不必解释为比其它方面优选或有利。同样，术语“本发明的方面”并不要求本发明的所有方面都包含所论述的特征、优点或操作模式。

[0016] 本文中所使用的术语仅是出于描述特定方面的目的，且并不意图限制本发明的方面。如本文中所使用，除非上下文另外清楚地指示，否则单数形式“一(a/an)”及“所述”也意图包含复数形式。将进一步理解，术语“包括”和/或“包含”当在本文中使用时指定所叙述的特征、整数、步骤、操作、元件和/或组件的存在，但并不排除一或多个其它特征、整数、步骤、操作、元件、组件和/或其群组的存在或添加。

[0017] 此外，就将由(例如)计算装置的元件执行的动作的顺序而言描述许多方面。将认识到，本文中描述的各种动作可由具体电路(例如，专用集成电路(application specific

integrated circuit;ASIC)),由正由一或多个处理器执行的程序指令或由所述两个的组合来执行。另外,本文中所描述的这些动作序列可被视为全部在任何形式的计算机可读存储媒体内体现,在所述计算机可读存储媒体中存储有对应的计算机指令集,所述计算机指令在执行时将致使相关联的处理器执行本文中所描述的功能性。因此,本发明的各种方面可以数个不同形式来体现,预期所有形式属于所主张的标的物的范围内。另外,对于本文所描述的方面中的每一者,任何此类方面的对应形式可在本文中描述为(例如)“经配置以”执行所描述动作的“逻辑”。

[0018] 本公开的示范性方面针对于经配置以从第一电压域转换信号到第二电压域的电压电平转换器。在第一电压域等于第二电压域的情况下,包含选择性旁路电路来绕过电压电平转换器,以避免由第一和第二电压域之间的信号路径中的电压电平转换器引入的延迟。此外,在示范性方面中,可以包含电力控制电路来在电压电平转换器在上述方式中被略过时,下电或关闭电压电平转换器。因此,在示范性方面中,在信号路径中不需要电压电平转换器时,可以避免与电压电平转换器相关的功率消耗和延迟。现将在以下部分中,参考图式阐述这些和相关方面。

[0019] 首先,参考图1A到B,将描述常规的电压电平转换器100。电压电平转换器100经配置以转换第一供电电压VDD1供电的第一电压域中的互补输入信号a 114和a\_n 116为第二供电电压VDD2供电的第二电压域中的输出信号z 120。不失一般性,在正常操作状态下,第一供电电压VDD1可能小于第二电压源VDD2,而在一些例子中,第一和第二电压源VDD1和VDD2可以是大体上相同的电压值。虽然第一和第二电压源VDD1和VDD2可以采用不同值的特定条件或产生这些电压源的方式与本讨论没有密切关系,但是一个实例可以涉及包括具有逻辑单元的处理系统的处理器核心等等的第一电压域,其中第一电压源VDD1可以被称为逻辑供电电压;以及包括具有存储器单元的存储器系统的第二电压域,其中第二电压源VDD2可以被称为存储器供电电压。

[0020] 在图1A到B中说明的配置中,电压电平转换器100包括:上拉晶体管102和104,其可以配置有P沟道金属氧化物半导体(p-channel metal oxide semiconductor;PMOS)装置或P沟道场效应晶体管(p-channel field effect transistor;PFET);下拉晶体管108和112,其可以配置有n沟道金属氧化物半导体(n-channel metal oxide semiconductor;NMOS)装置或n沟道场效应晶体管(n-channel field effect transistor;NFET);以及上拉晶体管106和110,其可以被配置为PMOS装置或PFET。互补输入信号a 114和a\_n 116的电压电平转换的输出可以从节点122导出,其穿过反相器118可提供输出信号z 120。虽然如图1A到B中所说明的电压电平转换器100的可操作细节是众所周知的,但是将在以下部分提供一些简要细节,记住电压电平转换器的各种其它配置可能应用于本公开的示范性方面。

[0021] 参看图1A,说明输入信号a 114从低逻辑状态(例如,二进制“0”)上升或转变到高逻辑状态(例如,二进制“1”),且相应地,和输入信号a\_n 116下降的情况。相应地,在第一级中,上拉晶体管106将开始关闭,而下拉晶体管108将开始接通,其开始使节点122放电。另一侧,输入信号a\_n 116在接通上拉晶体管110同时下降,且关闭下拉晶体管112。一旦节点122下降到足够低的值,那么在第二级中,上拉晶体管104接通,且上拉晶体管104和110开始充电节点123到第二供电电压VDD2。

[0022] 随着节点123充电,上拉晶体管102开始关闭,其辅助下拉晶体管108进一步下拉节

点122。下拉节点122辅助上拉晶体管104被接通的过程,这进一步充电节点123。最终,上拉晶体管102被完全关闭,节点122转变成逻辑状态“0”,而节点123在第二电压域中转变成逻辑“1”。节点122和123维持其逻辑状态“0”和“1”,直到互补输入信号a 114和a\_n 116的值发生连续改变。

[0023] 因此,穿过反相器118之后,节点122的反相值作为输出信号z 120出现,其在第二电压域中上升,对应于第一电压域中输入信号a 114的上升和输入信号a\_n 116的下降。电压电平转换器100的以上标识的级在互补输入信号a 114和a\_n 116与输出信号z 120之间的路径中引入对应延迟或延时。

[0024] 现参看图1B,现将描述相反情境,其中输入信号a 114下降而a\_n 116上升。在此情况下,上拉晶体管110将开始关闭,而下拉晶体管112将开始接通,由此放电节点123。另一侧,在接通上拉晶体管106时,随着输入信号a 114下降,致使下拉晶体管108关闭。一旦节点123下降到足够低的值,那么在第二级中,上拉晶体管102接通,且上拉晶体管102和106开始充电节点122到第二供电电压VDD2。随着节点122充电,上拉晶体管104开始关闭,其辅助下拉晶体管112进一步下拉节点123。下拉节点123辅助上拉晶体管102被接通的过程,这进一步充电节点122。最终,上拉晶体管104完全关闭,且节点123转变成逻辑状态“0”,而节点122在第二电压域中转变成逻辑状态“1”。节点122的逻辑状态由反相器118反相,来在第二电压域中显现为下降输出信号z 120。节点122和123分别维持其逻辑状态“1”和“0”,直到互补输入信号a 114和a\_n 116发生连续转变。如可见,涉及电压电平转换器100操作的以上标识的级在此状况下同样导致显著延迟。

[0025] 对于第一和第二供电电压VDD1和VDD2电压值之间的差值较大的情形,电压电平转换器100左侧的上拉晶体管102和106的堆迭可以被变薄,以允许下拉晶体管108(例如)有效地在输入信号a 114上升(或从低到高转变)和相应地输入信号a\_n 116下降(或从高到低转变)的情况下下拉节点122。类似地,电压电平转换器100右侧上的上拉晶体管104和110的堆迭可以被变薄,以允许下拉晶体管112有效地在输入信号a 114下降和相应地输入信号a\_n 116上升的情况下下拉节点123。下拉和上拉晶体管的这一相对大小可以进一步增加来自互补输入信号a 114和a\_n 116和输出信号z 120的延迟。

[0026] 从电压电平转换器100的以上论述,可了解在图1A到B中所示出的两种情况下,引入了相当大的延迟。此外,各种上拉和下拉晶体管的接通和断开的多个阶段还消耗电力。在第一电压域的第一电压源VDD1与第二电压域的第二电压源VDD2大体上相同的情况下,在现将参考图2A到B论述的示范性方面中,与电压电平转换器100相关的延迟和电力可以被避免。

[0027] 参看图2A,示出电路200,其包括电压电平转换器250和旁路电路252。电压电平转换器250可以经配置以与参考图1A到B描述的常规的电压电平转换器100,或任何其它适于转换第一电压源VDD1供电的第一电压域中的互补输入信号a 214和a\_n 216为第二电压源VDD2供电的第二电压域中的节点222处衍生的中间输出信号y\_n的电压电平转换器配置相似。在实例方面中,第一电压域对应于包括逻辑单元的逻辑电压域,而第二电压域对应于包括存储器单元的存储器电压域。

[0028] 在电压电平转换器250的配置与电压电平转换器100的配置相似的各方面中,电压电平转换器250的组件可具有与电压电平转换器100的对应组件类似的功能性,并且因此将

出于简洁起见不重复电压电平转换器250的可操作细节。简要地,电压电平转换器250的上拉晶体管202、204、206、210和下拉晶体管208、212可以经配置以与电压电平转换器100的对应上拉晶体管102、104、106、110和下拉晶体管108、112类似。因此,节点222和223可以通过与如图1A到B中所描述的那样,节点122和123基于互补输入信号a 114和a\_n 116的上升和下降的类似方式,基于互补输入信号a 214和a\_n 216的上升和下降,接收转换到第二电压域的电压。

[0029] 进一步,电路200可以涉及几个操作模式。举例来说,正常工作方式可以被定义成包含第一电压源VDD1不同于(例如,小于或大于)第二电压源VDD2的情况,并且期望互补输入信号a 214和a\_n 216从第一电压域到第二电压域的电压电平转换。在正常模式中,电压电平转换器250的功能性可以大体类似于电压电平转换器100的功能性。

[0030] 电路200的第二操作模式被定义为旁路模式,其中第一电压源VDD1大体上与第二电压源VDD2相同,并且因此互补输入信号a 214和a\_n 216从第一电压域到第二电压域的电压电平转换在旁路模式中可以被避免。旁路模式可以例如对应于先前提及的加速模式,其中第一电压域(例如,逻辑电压域)与第二电压域(例如,存储器电压域)的供电电压可以相等或大体上相同。在此情形下,大体上相等应被本领域的技术人员理解为第一电压域与第二电压域之间的电压差足够小,使得更高电压域中应被断开的装置不被足够地接通以引起不必要的泄漏电流。在旁路模式中,旁路电路252可以被采用以绕过电压电平转换器250,且藉此避免互补输入信号a 214和a\_n 216穿越电压电平转换器250所引发的延迟。

[0031] 在一些方面中,旁路电路252可以实施为多路复用器或选择器,以用于:在旁路模式中,选择输入信号a\_n 216,作为旁路电路252的输出;以及在正常模式中,选择呈现为中间信号y\_n的节点222,作为旁路电路252的输出。为此目的,旁路电路252可包含两个发射栅极电路234和236,其各自由PFET和NFET装置的平行耦接形成。如果电路200将在旁路模式中被操作,那么可以断言信号bypass 232。bypass 232的互补被示出为信号bypass\_n 230。如果bypass 232为高,那么bypass\_n 230为低,且发射栅极电路234被接通来传递a\_n 216到旁路电路252的输出。另一方面,如果bypass 232为低,那么bypass\_n 230为高,且发射栅极电路236被接通来传递中间信号y\_n(即,节点222)到旁路电路252的输出。旁路电路252的输出通过反相器218被反相,来显现为电路200的输出信号z 220。因此,在旁路模式中,(例如,当bypass 232基于第一和第二供电电压VDD1和VDD2大体上相同而被断言时),a\_n 216可被选择为旁路电路252的输出,同时完全绕过电压电平转换器250和对应延迟。

[0032] 图2B到D说明关于可在旁路模式中用于电力节省的下电电路的示范性方面。如以下部分详细解释,下电电路可以在bypass 232被断言且电压电平转换器250被绕过时被选择性地部署。

[0033] 首先参考图2B,根据旁路模式中的电力节省的示范性方面,说明电路270。电路270包含加入图2A的电路200的下电电路275。更详细地,电路270还包含如上文参考图2A论述的电压电平转换器250和旁路电路252,且如所示出,下电电路275被耦接到电压电平转换器250。在旁路模式中,当断言bypass 232时,下电电路275经配置以选择性地下电电压电平转换器250。但在正常模式中,当bypass 232不被断言时(或换句话说,当bypass\_n 230被断言时),下电电路275保持电压电平转换器250激活以用于正常操作。将在下文进一步详细阐述下电电路275。

[0034] 如所示出,下电电路275包含第一下拉晶体管240(例如,NMOS电晶体或NFET)。伴随第一下拉晶体管240的栅极受bypass\_n 230控制,第一下拉晶体管240被串联连接到电压电平转换器250的下拉晶体管208和212中的每一个以及接地。因此,在正常模式中,当bypass 232不被断言而bypass\_n 230被断言时,第一下拉晶体管240被接通,其连接下拉晶体管208和212的源极端到接地,由此保持电压电平转换器250的正常配置,或换句话说,导致电压电平转换器250保持激活。另一方面,在旁路模式中,bypass232被断言,导致bypass\_n 230被驱动为低,且断开第一下拉晶体管240,继而,关断下拉晶体管208和212到接地的路径,且导致电压电平转换器250被下电。

[0035] 下电电路275还可包含第一上拉晶体管242(例如,PMOS晶体管或PFET),但这可以是任选的。当包含在下电电路275中时,第一上拉晶体管242被连接到电压电平转换器250的中间信号y\_n(或节点222)和第二供电电压VDD2,伴随第一上拉晶体管242的栅极仍然受bypass\_n 230控制。在正常模式中,bypass 232为低,且bypass\_n 230被断言,由此断开第一上拉晶体管242,其并不影响电压电平转换器250的正常配置。另一方面,在旁路模式中,bypass 232被断言,导致bypass\_n 230被驱动为低,且接通第一上拉晶体管242,由此连接节点222到第二供电电压VDD2且断开上拉晶体管204。因此可见,当被包含时,第一上拉晶体管242并不导致节点222在旁路模式中浮动(通过连接节点222到第二供电电压VDD2),其产生旁路电路252中的背面耦接的缩减,借此改进电路270在旁路模式中的性能。相应地,从第二电压源VDD2到上拉晶体管210和下拉晶体管212的电力供应同样在旁路模式中被切断。

[0036] 因此,在bypass\_n 230被断言时的旁路模式中,断开第一下拉晶体管240和接通第一上拉晶体管242的综合效应是将电压电平转换器250的全部开关晶体管与电力供应器隔开,由此下电电压电平转换器250。因此,当电压电平转换器250被绕过时(例如,当第一供电电压VDD1和第二VDD2大体上相同时),电压电平转换器250同样被下电,导致节省电力。

[0037] 在下电电路275不包含第一上拉晶体管242的状况下,将导致耦接到节点222的中间信号y\_n在旁路模式期间浮动,但电压电平转换器250将仍然保持下电,这是因为第一下拉晶体管240如先前描述将被关断。在下电电路275中不包含第一上拉晶体管242可以减小与下电电路275相关的面积。

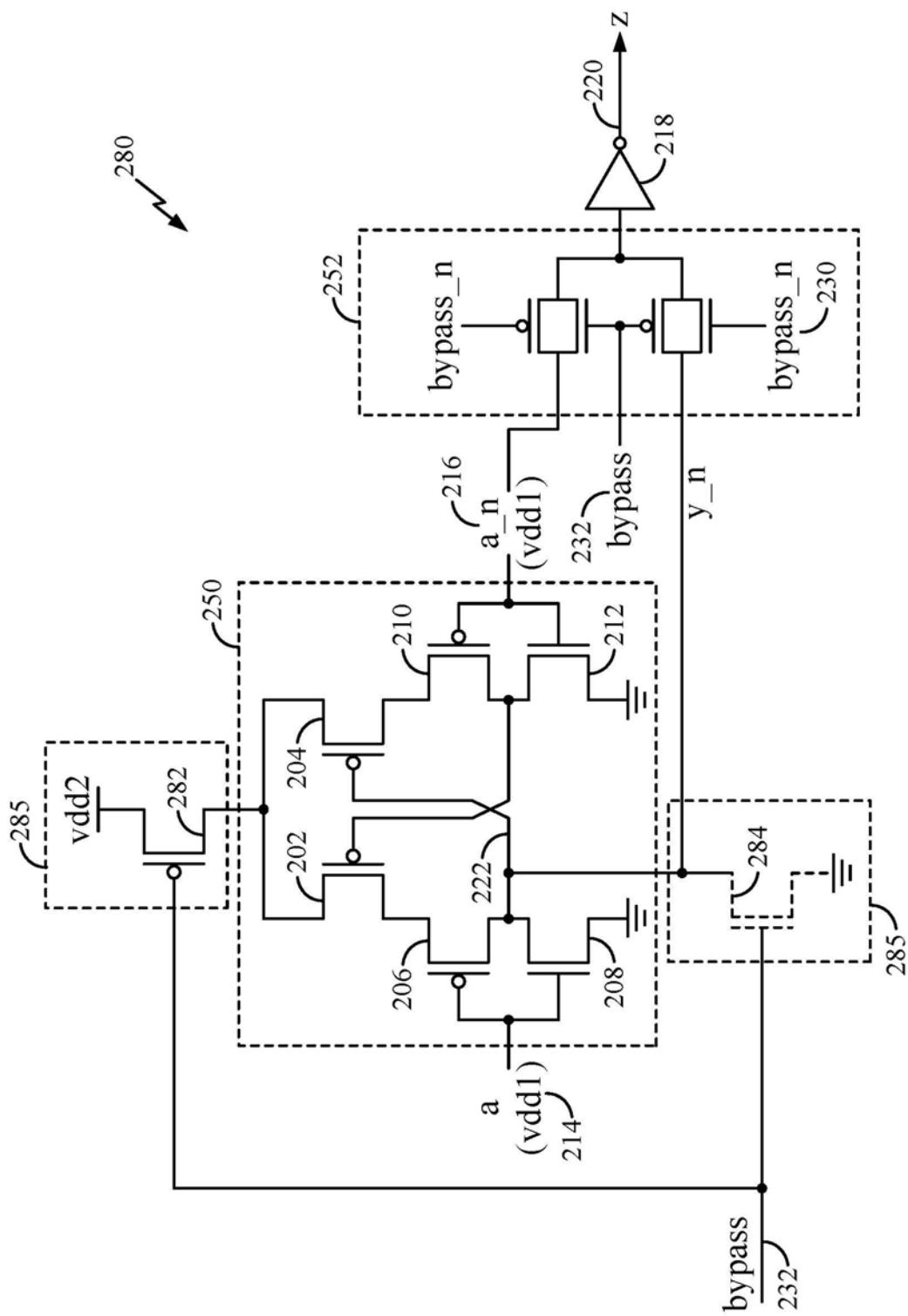

[0038] 随后,参考图2C,根据旁路模式中的电力节省的另一个示范性方面,说明电路280。类似于电路270,电路280还包含加入图2A的电路200的下电电路,其在此情况下,标识为下电电路285。更详细地,电路280还包含如上文参考图2A论述的电压电平转换器250和旁路电路252,且如所示出,下电电路285被耦接到电压电平转换器250。在旁路模式中,当断言bypass 232时,下电电路285经配置以选择性地下电电压电平转换器250。但在正常模式中,当bypass 232不被断言时(或换句话说,当bypass\_n 230被断言时),下电电路285保持电压电平转换器250激活以用于正常操作。将在下文进一步详细阐述下电电路285。

[0039] 如所示出,下电电路285包含耦接在第二供电电压VDD2与电压电平转换器250之间的第二上拉晶体管282(例如,来上拉如所示出的电压电平转换器250的晶体管202和204),伴随第二上拉晶体管282的栅极受bypass 232控制。在旁路模式中,当bypass232为高时,第二上拉晶体管282被断开,由此关断从第二供电电压VDD2到电压电平转换器250的电压供应,且导致节点222和信号y\_n浮动。另外,在正常模式中,bypass232为低导致第二上拉晶体管282被接通,且正常连接第二供电电压VDD2到电压电平转换器250。

[0040] 下电电路285可能任选地包含连接到电压电平转换器250的节点222的第二下拉晶体管284(例如,NMOS电晶体或NFET),伴随第二下拉晶体管284的栅极受bypass 232控制。当第二下拉晶体管284以此方式被配置时,在旁路模式中,当bypass 232为高时,第二下拉晶体管284被接通,连接节点222或信号y\_n到接地或逻辑“0”。因此,第二下拉晶体管284也可以防止节点222在旁路模式中浮动,减小旁路电路252中的背面耦接,借此改进电路280在旁路模式中的性能。在正常模式中,bypass 232为低导致第二下拉晶体管284被断开,移除对节点222或信号y\_n的任何影响。

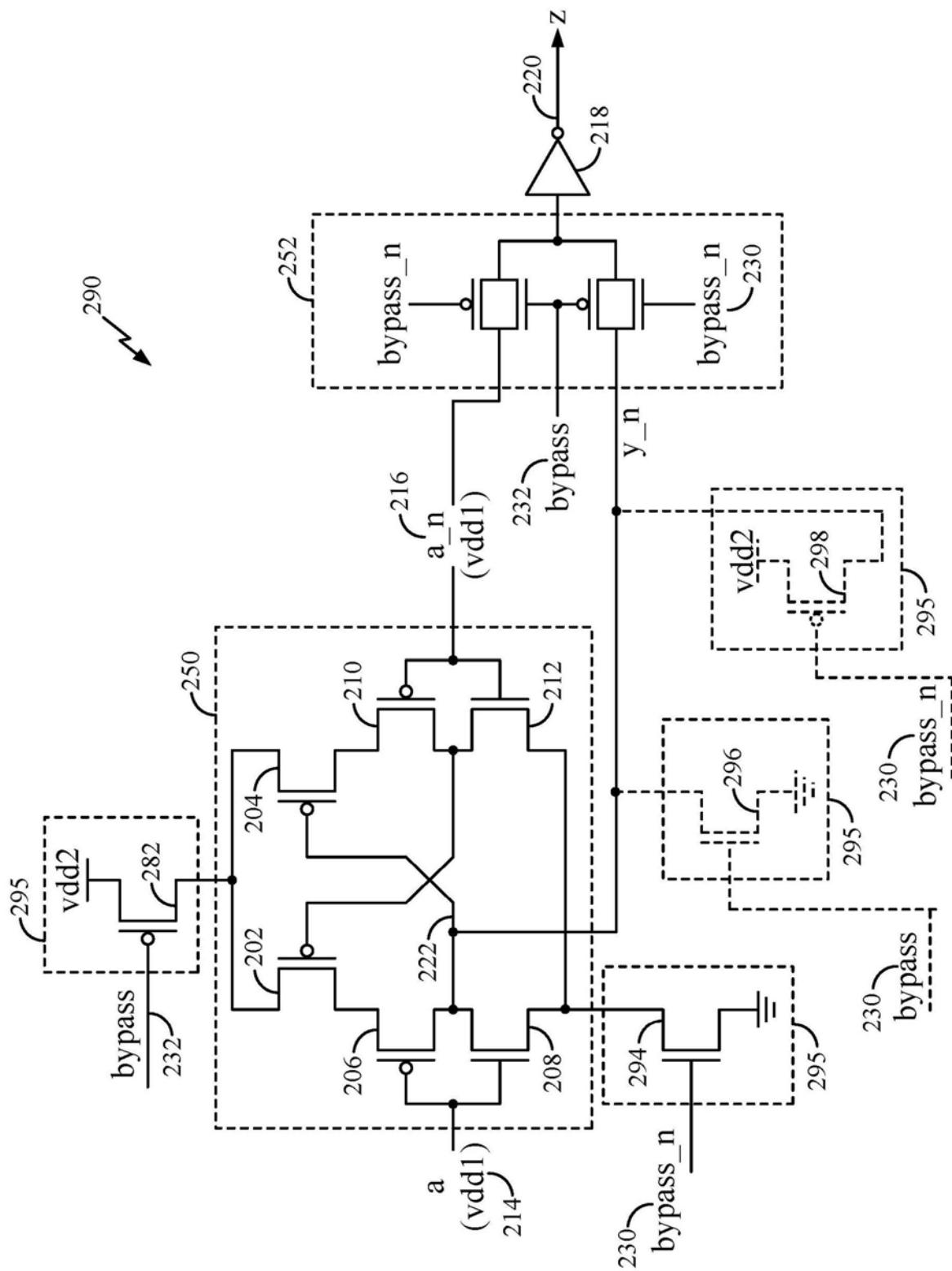

[0041] 现参考图2D,根据旁路模式中的电力节省的又另一个示范性方面,说明电路290。类似于电路270和280,电路290还包含加入图2A的电路200的下电电路,其在此情况下,标识为下电电路295。更详细地,电路290还包含如上文参考图2A论述的电压电平转换器250和旁路电路252,且如所示出,下电电路295被耦接到电压电平转换器250。在旁路模式中,当断言bypass 232时,下电电路295经配置以选择性地下电电压电平转换器250。但在正常模式中,当bypass 232不被断言时(或换句话说,当bypass\_n230被断言时),下电电路295保持电压电平转换器250激活以用于正常操作。将在下文进一步详细阐述下电电路295。

[0042] 如所示出,下电电路295还包含与上文所述的下电电路285的第二上拉晶体管282类似地配置,且耦接在第二供电电压VDD2与电压电平转换器250之间(例如,到如所示出的电压电平转换器250的上拉晶体管202和204)的第二上拉晶体管282,伴随第二上拉晶体管282的栅极受bypass 232控制。在旁路模式中,当bypass 232为高时,第二上拉晶体管282被类似地断开,由此关断从第二供电电压VDD2到电压电平转换器250的电压供应,导致节点222和信号y\_n浮动。另外,在正常模式中,bypass 232为低,导致第二上拉晶体管282被接通,且导致第二供电电压VDD2被正常耦接到电压电平转换器250。

[0043] 下电电路295还包含耦接在电压电平转换器250与接地之间的第三下拉晶体管294,伴随第三下拉晶体管294的栅极受bypass\_n 230控制。在旁路模式中,当bypass\_n 230为低时,第三下拉晶体管294被断开,由此关断电压电平转换器250的接地路径。另外,在正常模式中bypass\_n 230为高,导致第三下拉晶体管294被接通,且导致电压电平转换器250被正常耦接到接地。

[0044] 下电电路295可能任选地包含以下两个中的一个:第四下拉晶体管296或第四上拉晶体管298(但不包含两者),其连接到电压电平转换器250的节点222。如果第四下拉晶体管296被包含在下电电路295中,那么第四下拉晶体管296的栅极受bypass 232控制。在旁路模式中,当bypass 232为高时,第四下拉晶体管296被接通,由此连接节点222到接地或逻辑“0”。在正常模式中,bypass 232为低导致第四下拉晶体管296被断开,移除对节点222或信号y\_n的任何影响。

[0045] 另一方面,如果第四上拉晶体管298被包含在下电电路295中,那么第四上拉晶体管298的栅极受bypass\_n 230控制。在旁路模式中,当bypass\_n 230为低时,第四上拉晶体管298被接通,由此连接与节点222到第二供电电压VDD2或逻辑“1”。在正常模式中,bypass\_n 230为高,导致第四上拉晶体管298被断开,移除对节点222或信号y\_n的任何影响。如应了解,当第四下拉晶体管296或第四上拉晶体管298中的任一个被包含在下电电路295中时,如上配置,那么节点222被避免在旁路模式中浮动,其产生旁路电路252的中的背面耦接的缩减,借此改进电路290在旁路模式中的性能。

[0046] 因此,在示范性方面中,例如电路270、280或290的电路可以分别配置有下电电路275、285或295,以在电压电平转换器250不在旁路模式中被使用时避免功率消耗。电路270、280和290还包含旁路电路252以避免旁路模式中穿过电压电平转换器的延迟。

[0047] 进入旁路模式的情况下,例如,为了断言bypass 232,可能涉及检测第一和第二电压源VDD1和VDD2变成大体上相同的电压值。这一检测可以通过本领域中已知的方法和系统执行。举例来说,电池操作的移动装置的电池电量或充电状态可用于进入或退出旁路模式。为了说明,如果移动装置被插入外部电源,或电池电量为高(或高于特定电量),那么移动装置可以被编程以支持高效或加速模式,其中第一和第二电压源VDD1和VDD2可以被变成大体上相同。然而,如果电池电量下降到低于预定水平到低电池电量模式,那么,例如,可以保持第一和第二电压源VDD1和VDD2的分离电压电平,而可以退出旁路模式。数字和/或模拟电路可经配置以检测电池电量或到外部电源的连接,来相应地提供旁路模式是否可以被选择或正常操作状态是否适用于电压电平转换器的指示。在一些例子中,程序员或操作系统还可能提供可用于进入或退出旁路模式的软件控制。所属领域的技术人员将认识到旁路模式(例如,断言bypass 232)的检测或确定的各种其它选择方案,并且因此将不在此处更详细地论述它们。

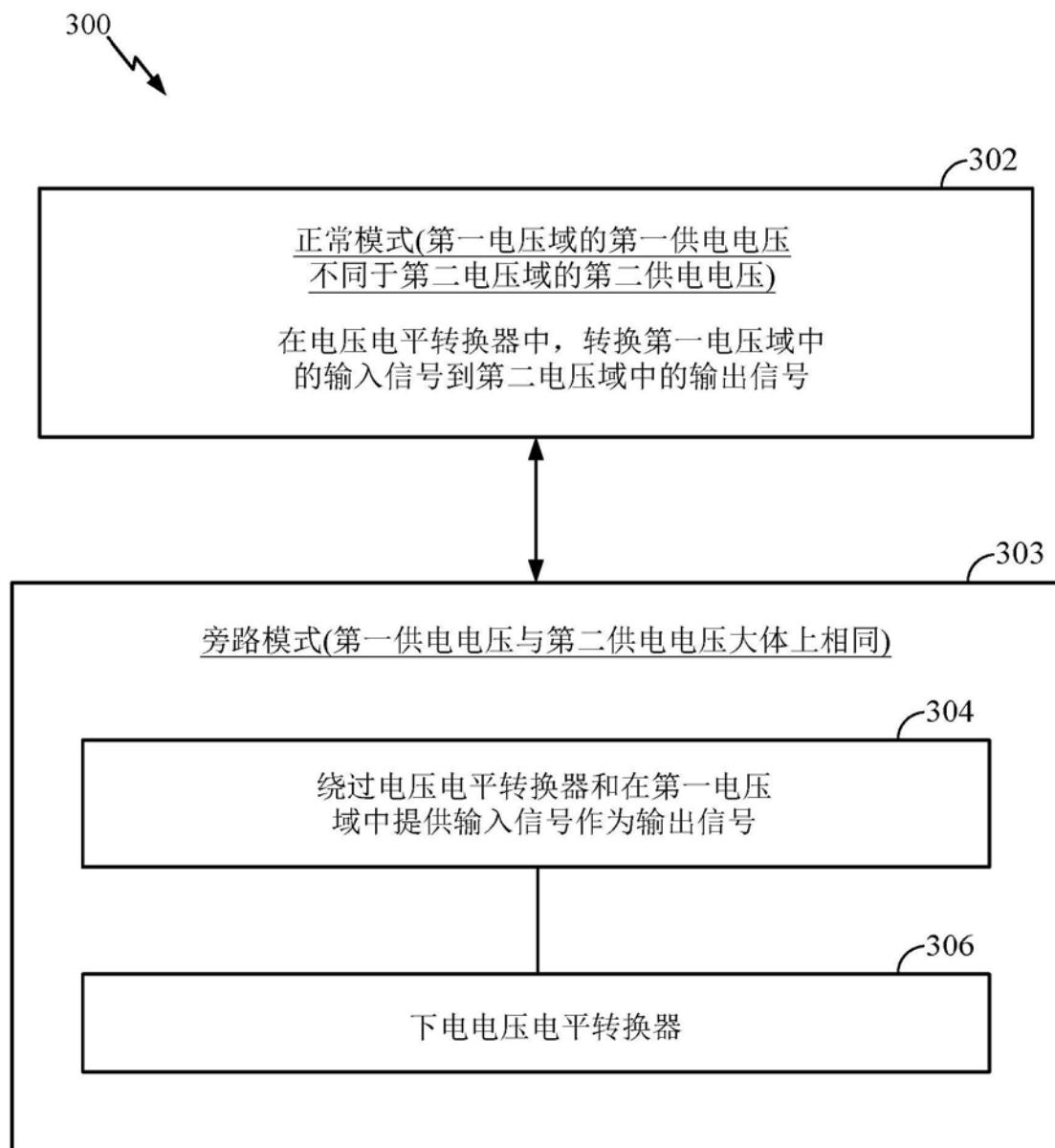

[0048] 应了解,示范性方面包含用于执行本文公开的过程、函数及/或算法的各种方法。举例来说,如图3中所说明,示范性方面可包括执行电压电平转换的一种方法(300)。方法300可包括框302,其例如关于电路270、280或290的正常工作方式,和框303,其可能例如关于电路270、280或290的旁路工作模式。图3示出框302与303之间的双向箭头,来指示视具体情况有可能从正常模式转变到旁路模式,或从旁路模式转变到正常模式。将在下文进一步详细阐述这些框302和303。

[0049] 如所提及,框302可能关于正常工作方式,其中第一电压域的第一供电电压VDD1不同于第二电压域的第二供电电压VDD2。在正常模式中,框302可包括,在正常模式中,例如在电压电平转换器250中,转换输入信号,例如,第一电压域中的输入信号a 214,到输出信号,例如第二电压域中的输出信号z 220。

[0050] 框303可能关于旁路工作模式,其中第一和第二供电电压VDD1和VDD2大体上相同。框303可包含框304和306,其可以同时进行。

[0051] 如此,框304可包括在旁路模式中,绕过电压电平转换器,和在第一电压域中提供输入信号作为输出信号。举例来说,框304可包括在断言bypass 232时使用旁路电路252绕过电压电平转换器250,和在第一电压域中提供输入信号作为输出信号。

[0052] 框306可包括选择性地在旁路模式中下电电压电平转换器。举例来说,框306可包括下电电压电平转换器250(例如,依据在示范性方面中是否选择用于电路270、280或290的实施方案,使用下电电路275、285或295)。特定地,使用本文中论述的下电技艺中的任一种,电压电平转换器250可以在旁路模式中被下电(当bypass 232为高且bypass\_n 230为低时),且电压电平转换器250可以在正常模式中保持激活(当bypass 232为低且bypass\_n 230为高时)。以此方式,方法300可用于在旁路模式中,当bypass 232被断言时,避免与电路270、280或290中的电压电平转换器250相关的延迟和功率。

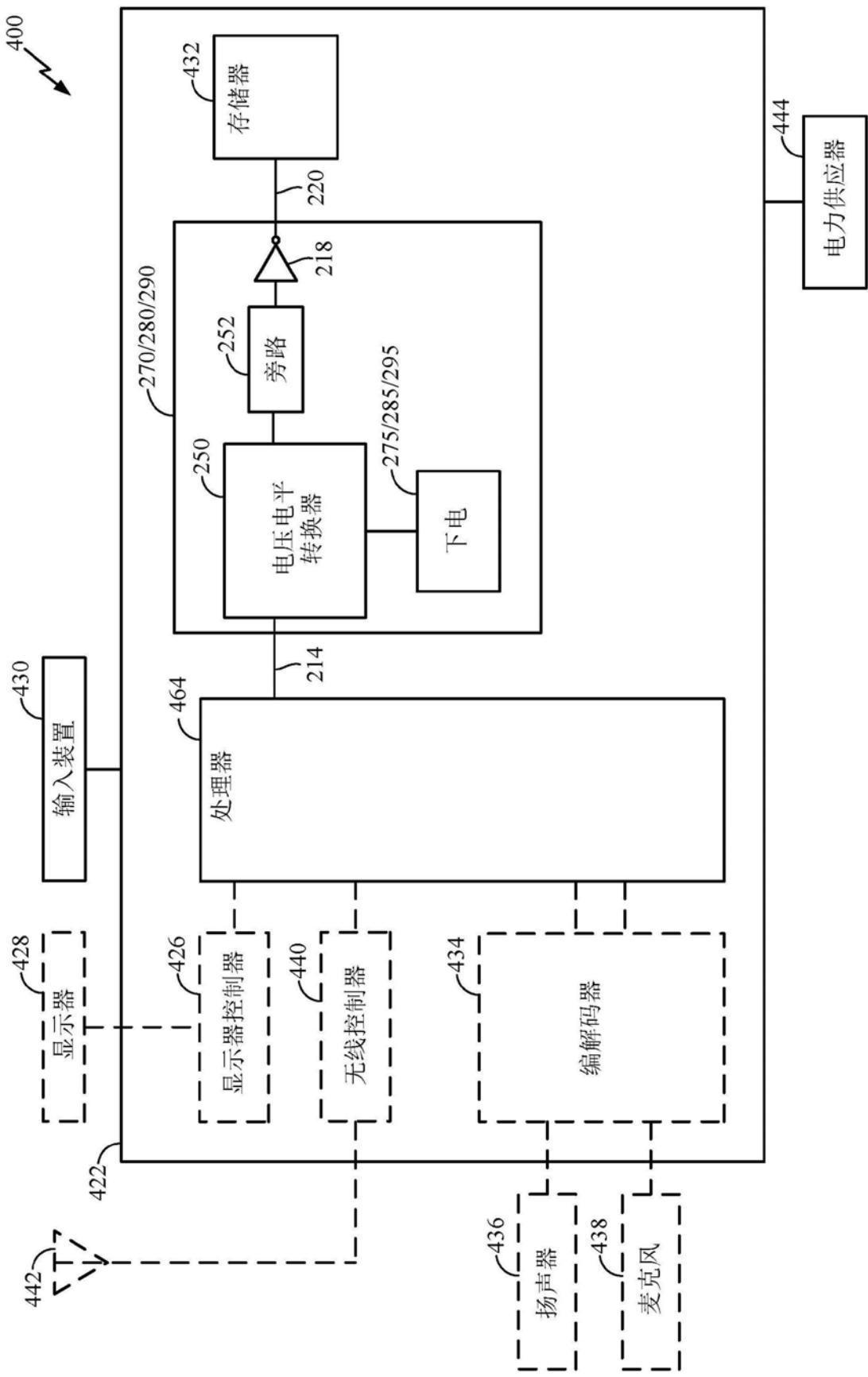

[0053] 现参考图4,描绘了计算装置的特定说明性方面的框图,其包含用于高效功率电压电平转换的电路,例如电路270、280或290,且一般将其表示为400。计算装置400可包含用于

执行上文参考图3论述的方法300的功能性。此外,在一些方面中,计算装置400可以经配置为无线通信装置。

[0054] 计算装置400被示出为包含处理器464和存储器432。在一些方面,处理器464可以属于具有第一供电电压VDD1的第一或逻辑电压域,而存储器432可以属于具有第二供电电压VDD2的第二或存储器电压域。因此,参考上文图2B到D描述的电路270、280或290的示意图被示出为配置在处理器464与存储器432之间。电路270/280/290例如可以在正常模式中使用电压电平转换器250执行输入信号a 214(例如,对应于从处理器464到存储器432的读取/写入命令)到输出信号z 220的电压电平转换。电路270/280/290可以被配置成使用旁路电路252和对应下电电路275/285/295绕过和下电电压电平转换器250,以在旁路模式中从处理器464提供互补输入信号a 214和a\_n 216作为输出信号z 220(而不经电压电平转换)到存储器432,其中第一和第二供电电压VDD1和VDD2在旁路模式中大体上相同。如先前所提及,旁路模式可以对应于本领域中已知的加速模式。应注意为清楚起见,图4中的电路270/280/290的表示省略对应图2B到D中所示出的各种细节。

[0055] 计算装置400也可以包含耦接到处理器464和显示器428的显示器控制器426。图4还示出可提供于计算装置400中的可选方面。举例来说,计算装置可以任选地包含耦接到处理器464的编码器/解码器(编解码器)434(例如,音频和/或语音编解码器),伴随耦接到编解码器434的扬声器436和麦克风438;以及耦接到处理器464的无线控制器440(其可包含调制解调器),伴随耦接到无线天线442的无线控制器440。

[0056] 在一或多种上述可选特征存在的实例方面中,处理器464、电路270/280/290、存储器432、编解码器434、显示器控制器426和无线控制器440可以包含在系统级封装或芯片上系统装置422中。在一些方面,输入装置430和电力供应器444可以被耦接到芯片上系统装置422(其中还应注意,第一和第二电压源VDD1和VDD2在一些状况下可以源自或由电力供应器444供电),而在一些方面中,显示器428、输入装置430、扬声器436、麦克风438、无线天线442和电力供应器444可以在芯片上系统装置422外部。然而,显示器428、输入装置430、扬声器436、麦克风438、无线天线442和电源444中的每一者可耦合到芯片上系统装置422的组件,例如接口或控制器。

[0057] 应注意虽然图4大致描绘计算装置,但是处理器464和存储器432还可以整合于机顶盒、音乐播放器、视频播放器、娱乐单元、导航装置、通信装置、个人数字助理(personal digital assistant;PDA)、固定位置数据单元、移动电话、服务器和计算机中。

[0058] 所属领域的技术人员应了解,可使用多种不同技术和技艺中的任一个来表示信息和信号。举例来说,可用电压、电流、电磁波、磁场或磁粒子、光场或光粒子或其任何组合来表示在整个上文描述中可能参考的数据、指令、命令、信息、信号、位、符号和码片。

[0059] 另外,所属领域的技术人员应了解,结合本文中所公开的方面描述的各种说明性逻辑块、模块、电路和算法步骤可实施为电子硬件、计算机软件或两者的组合。为清晰地说明硬件与软件的此可互换性,上文已大体就其功能性描述了各种说明性组件、块、模块、电路和步骤。此类功能性是实施为硬件还是软件取决于特定应用及强加于整个系统的设计约束。本领域技术人员可针对每一特定应用以不同方式来实施所描述的功能性,但这样的实施决策不应被解释为会引起脱离本发明的范围。

[0060] 本文中公开的方面描述的方法、序列和/或算法可以直接以硬件、以由处理器执行

的软件模块或以硬件与软件模块的组合来体现。软件模块可以驻留在RAM存储器、快闪存储器、ROM存储器、EPROM存储器、EEPROM存储器、寄存器、硬盘、可移动磁盘、CD-ROM，或所属领域中已知的任何其它形式的存储媒体中。示范性存储媒体耦合到处理器，使得处理器可从存储媒体读取信息和将信息写入到存储媒体。在替代方案中，存储媒体可与处理器成整体。

[0061] 因此，本发明的一方面可包括体现用于高效功率电压电平转换的一种方法的电脑可读媒体。因此，本发明不限于所说明的实例，且任何用于执行本文中所描述的功能性的装置包含于本发明的方面中。

[0062] 虽然前述公开内容示出本发明的说明性方面，但应注意，可在不脱离如由所附权利要求书界定的本发明的范围的情况下在本文中作出各种改变和修改。无需以任何特定次序来执行根据本文中所描述的本发明的方面的方法权利要求的功能、步骤和/或动作。此外，尽管可以单数形式描述或主张本发明的元件，但除非明确陈述限于单数，否则也涵盖复数形式。

图1A

图1B

图2A

图2B

图2C

图2D

图3

图4