(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-103424

(P2010-103424A)

(43) 公開日 平成22年5月6日(2010.5.6)

(51) Int.Cl.

H01L 33/32 (2010.01)

F 1

H01L 33/00

テーマコード(参考)

C 5 F 0 4 1

審査請求 未請求 請求項の数 11 O L (全 13 頁)

(21) 出願番号

特願2008-275683 (P2008-275683)

(22) 出願日

平成20年10月27日 (2008.10.27)

(71) 出願人 000002004

昭和電工株式会社

東京都港区芝大門1丁目13番9号

(74) 代理人 100104880

弁理士 古部 次郎

(74) 代理人 100118201

弁理士 千田 武

(74) 代理人 100107216

弁理士 伊與田 幸穂

(72) 発明者 菅野 進

千葉県市原市八幡海岸通5-1 昭和電工

株式会社内

F ターム(参考) 5F041 AA03 CA04 CA05 CA40 CA65

CA74 CA76 CA88

(54) 【発明の名称】半導体発光素子の製造方法

## (57) 【要約】

【課題】光取り出し効率に優れた半導体発光素子を高収率で製造が可能な半導体発光素子の製造方法を提供する。

【解決手段】基板11と基板11上に成膜されたIII族窒化物半導体の積層構造からなるIII族窒化物半導体層と有するウェーハの基板11の被研削面103を研削する研削工程と、研削工程により研削された基板11の被研削面103の表面粗さRaを3nm～25nmに調整する研磨工程と、研磨工程により表面粗さRaを調整した基板11の被研削面103側から、基板11を分割するための切断予定ラインに沿ってレーザL2を照射することにより、基板11の内部に加工変質部分41, 42を設けるレーザ加工工程と、レーザ加工工程により加工変質部分41, 42を設けた基板11を加工変質部分41, 42及び切断予定ラインに沿って分割する分割工程と、有することを特徴とする半導体発光素子の製造方法。

【選択図】図6

## 【特許請求の範囲】

## 【請求項 1】

III族窒化物半導体層を有する半導体発光素子の製造方法であって、

基板と当該基板上に成膜されたIII族窒化物半導体の積層構造からなるIII族窒化物半導体層とを有するウェーハの当該基板の被研削面を研削する研削工程と、

前記研削工程により研削された前記基板の前記被研削面の表面粗さ  $R_a$  を  $3 \text{ nm} \sim 25 \text{ nm}$  に調整する研磨工程と、

前記研磨工程により前記表面粗さ  $R_a$  を調整した前記基板の前記被研削面側から、当該基板を分割するための切断予定ラインに沿ってレーザを照射することにより、当該基板の内部に加工変質部分を設けるレーザ加工工程と、

前記レーザ加工工程により前記加工変質部分を設けた前記基板を当該加工変質部分及び前記切断予定ラインに沿って分割する分割工程と、

を有することを特徴とする半導体発光素子の製造方法。

## 【請求項 2】

前記レーザ加工工程は、前記基板の厚さ方向に断続的に複数の前記加工変質部分を設けることを特徴とする請求項 1 に記載の半導体発光素子の製造方法。

## 【請求項 3】

前記レーザ加工工程は、前記基板の内部の前記被研削面側から厚さ方向で(2/3)部の範囲に前記加工変質部分を設けることを特徴とする請求項 1 又は 2 に記載の半導体発光素子の製造方法。

## 【請求項 4】

前記レーザ加工工程は、前記基板に対して前記レーザをパルス照射することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 5】

前記分割工程において、前記基板を分割することにより当該基板の分割面を粗面とすることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 6】

前記基板上に成膜された前記III族窒化物半導体層側から前記切断予定ラインに沿ってレーザを照射することにより当該基板に割溝を形成する割溝形成工程をさらに有することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 7】

前記基板の表面に予め複数の凸部を形成する基板加工工程をさらに有することを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 8】

前記凸部を形成した前記基板の前記表面にIII族窒化物半導体からなるバッファ層をスパッタリングにより形成するバッファ層形成工程をさらに有することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 9】

前記基板は、サファイア又はシリコンカーバイドから選ばれることを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 10】

前記ウェーハの前記III族窒化物半導体層は、それぞれIII族窒化物化合物半導体を含むn型半導体層、発光層、p型半導体層が積層されることを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【請求項 11】

前記基板は、最大径が約  $100 \text{ mm}$  以上であることを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の半導体発光素子の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

10

20

30

40

50

本発明は、半導体発光素子の製造方法に関し、より詳しくは、ⅢⅢ族窒化物半導体を含む半導体発光素子の製造方法に関する。

【背景技術】

【0002】

近年、半導体発光素子用の材料としてⅢⅢ族窒化物半導体が注目を集めている。ⅢⅢ族窒化物半導体は、サファイア等の基板の上に、有機金属化学気相成長法(MOCVD法)や分子線エピタキシー法(MBE法)等によって成膜される。

このようなⅢⅢ族窒化物半導体を用いた半導体発光素子の光取り出し効率を改善する方法として、発光素子とその外部の媒体との屈折率の違いによって生じる発光素子の内部への光の閉じ込めを低減させる方法が挙げられる。

【0003】

例えば、特許文献1には、基板の表面に凹凸を加工し、基板とは異なる屈折率を有する層を凹凸に埋め込んで成長させ、これら凹凸状の屈折率界面を形成した後、その上に、発光層を含む半導体結晶層が積層された素子構造を形成することにより、発光層に生じた横方向の光を外界に向かわせる新規な構造が付与された発光素子が記載されている。

また、特許文献2には、基板裏面に凹凸を設け、光を基板側面に向けて反射させることによって、基板側面からの光の取り出し効率を上げた透光性電極を有する窒化物系化合物半導体発光素子が記載されている。

【0004】

一方、特許文献3には、化合物半導体発光素子ウェーハは、基板上に多数の化合物半導体発光素子が分離帯域を介して規則的に且つ連続的に配列され、このウェーハを保護膜が形成された面の分離帯域にレーザ法で割溝を形成する方法を経てこのウェーハをサファイア基板側から押し割って、個々のチップ状の化合物半導体発光素子が分離される。

さらに、特許文献4には、ウェーハを個々の素子に分割する方法として、半導体層が積層されたウェーハの基板内部に集光点を合わせてレーザ光を照射することにより改質領域を形成し、この改質領域によって切断起点領域を形成し、切断起点領域に沿ってウェーハを切断する方法が提案されている。この場合、基板内の所定の位置に改質領域を形成するために、レーザ光の焦光点を正確に合わせることが必要となる。

【0005】

また、半導体層の膜厚が5μm以上の場合は、半導体層膜厚が厚くなるほど、半導体層と基板の熱膨張係数の違いに起因して、基板の薄板化後のウェーハの反りも大きくなることが知られている(特許文献4参照)。このようなウェーハの反りは、基板裏面の表面粗さ(Ra)を調整することにより、ある程度調整が可能であり、基板の平坦性を保つために有効とされている。

【0006】

【特許文献1】特開2002-280611号公報

【特許文献2】特開2002-368261号公報

【特許文献3】特開2005-109432号公報

【特許文献4】特開2005-333122号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、例えば、基板の裏面側からレーザ光を照射する場合、上述したように、基板の平坦性を保つために、また、半導体素子の光取り出し効率を改善するために基板の裏面に形成された凹凸によって裏面の表面粗さ(Ra)が過度に大きくなると、レーザ光の焦光点を正確に合わせることが困難となる。そのため、ウェーハの基板内部に正確に改質領域を形成することができず、その結果、チップの不良品が多く発生するという問題がある。

【0008】

本発明の目的は、光取り出し効率に優れた半導体発光素子を高収率で製造が可能な半導

10

20

30

40

50

体発光素子の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明によれば、 $\text{III}$ 族窒化物半導体層を有する半導体発光素子の製造方法であって、基板と基板上に成膜された $\text{III}$ 族窒化物半導体の積層構造からなる $\text{III}$ 族窒化物半導体層とを有するウェーハの基板の被研削面を研削する研削工程と、研削工程により研削された基板の被研削面の表面粗さ $R_a$ を $3\text{ nm} \sim 25\text{ nm}$ に調整する研磨工程と、研磨工程により表面粗さ $R_a$ を調整した基板の被研削面側から、基板を分割するための切断予定ラインに沿ってレーザを照射することにより、基板の内部に加工変質部分を設けるレーザ加工工程と、レーザ加工工程により加工変質部分を設けた基板を加工変質部分及び切断予定ラインに沿って分割する分割工程と、を有することを特徴とする半導体発光素子の製造方法が提供される。

10

【0010】

ここで、本発明が適用される半導体発光素子の製造方法において、レーザ加工工程は、基板の厚さ方向に断続的に複数の加工変質部分を設けることが好ましい。

また、レーザ加工工程は、基板の内部の被研削面側から厚さ方向で(2/3)部の範囲に加工変質部分を設けることが好ましい。

さらに、レーザ加工工程は、基板に対してレーザをパルス照射することが好ましい。

【0011】

次に、本発明が適用される半導体発光素子の製造方法の分割工程において、基板を分割することにより基板の分割面を粗面とすることが好ましい。

20

また、基板上に成膜された $\text{III}$ 族窒化物半導体層側から切断予定ラインに沿ってレーザを照射することにより基板に割溝を形成する割溝形成工程をさらに有することが好ましい。

【0012】

また、本発明が適用される半導体発光素子の製造方法において、基板の表面に予め複数の凸部を形成する基板加工工程をさらに有することが好ましい。

さらに、凸部を形成した基板の表面に $\text{III}$ 族窒化物半導体からなるバッファ層をスパッタリングにより形成するバッファ層形成工程をさらに有することが好ましい。

30

【0013】

また、本発明が適用される半導体発光素子の製造方法において、基板は、サファイア又はシリコンカーバイドから選ばれることが好ましい。

さらに、ウェーハの $\text{III}$ 族窒化物半導体層は、それぞれ $\text{III}$ 族窒化物化合物半導体を含む $n$ 型半導体層、発光層、 $p$ 型半導体層が積層されることが好ましい。

また、本発明が適用される半導体発光素子の製造方法において、基板は最大径が約 $100\text{ mm}$ 以上であることが好ましい。

【発明の効果】

【0014】

本発明によれば、光取り出し効率に優れた半導体発光素子を高収率で製造が可能である。

40

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施の形態について詳細に説明する。尚、本発明は、以下の実施の形態に限定されるものではなく、その要旨の範囲内で種々変形して実施することが出来る。また、使用する図面は本実施の形態を説明するためのものであり、実際の大きさを表すものではない。

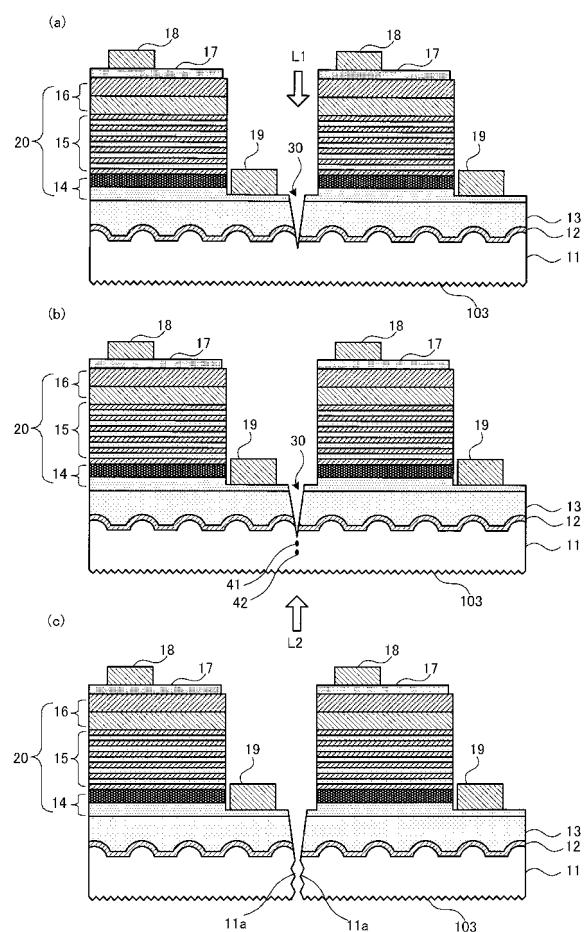

【0016】

(半導体発光素子Ⅰ)

図1は、 $\text{III}$ 族窒化物半導体層を有する半導体発光素子の一例を示した断面図である。図1に示すように、半導体発光素子Ⅰは、表面に複数の凸部102が形成された基板1

50

1と、基板11の複数の凸部102が形成された面上に成膜されたバッファ層12と、複数の凸部102を埋めるようにバッファ層12上に成膜された下地層13と、下地層13上にLED構造20が形成された構造を有している。

LED構造20は、n型半導体層14、発光層15、p型半導体層16が順次積層されている。LED構造20を構成するn型半導体層14は、n型コンタクト層14a及びn型クラッド層14bを有する。発光層15は、障壁層15a及び井戸層15bが交互に積層された構造を有する。p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bが積層されている。

さらに、p型半導体層16上に透明正極17が積層され、その上に正極ポンディングパッド18が形成されるとともに、n型半導体層14のn型コンタクト層14aに形成された露出領域14dに負極19が積層されている。

#### 【0017】

##### (基板11)

基板11は、II族窒化物化合物半導体とは異なる材料から構成される。基板11を構成する材料としては、例えば、サファイア、炭化ケイ素(シリコンカーバイド:SiC)、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。これらの中でも、サファイア、炭化ケイ素(シリコンカーバイド:SiC)が好ましく、サファイアが特に好ましい。

#### 【0018】

本実施の形態では、後述するように、基板11の被研削面103を所定の研削装置により研削し、その後、研磨装置により研磨することにより、基板11の厚さは、通常、170μm以下であり、好ましくは160μm以下となるように調整されている。但し、基板11の厚さは、通常、70μm以上である。

さらに、本実施の形態では、基板11の裏面である被研削面103の表面粗さRaが、3nm～25nm、好ましくは、5nm～20nmになるように調整されている。

基板11の裏面を上述した範囲の表面粗さRaを有する粗面として調整することにより、基板11の反りが低減し、基板11の平坦性を保つことができる。

また、被研削面103における光の乱反射により、半導体発光素子Iの光取り出し効率が増大する。

さらに、後述するように、基板11内部に改質領域を形成するために、基板11の被研削面103側からレーザ光を照射する際に、レーザ光の焦光点を正確に合わせることが可能となる。

#### 【0019】

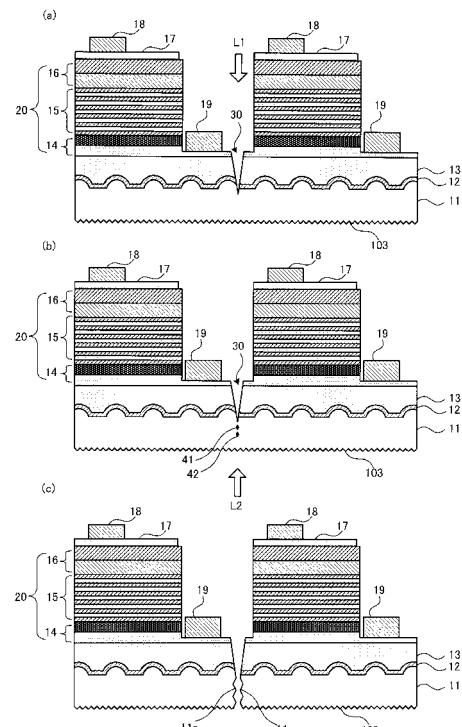

##### (複数の凸部102)

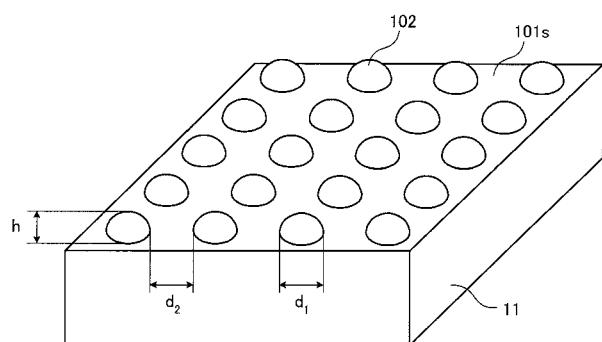

図2及び図3は、複数の凸部102が形成された基板11を説明する図である。図2に示すように、基板11に形成された複数の凸部102は、所定の最大径d<sub>1</sub>と高さhを有し、均一な大きさと均一な形状になるように形成されている。本実施の形態では、凸部102の形状は半球状である。尚、凸部102の形状は特に限定されない。

本実施の形態では、凸部102の最大径d<sub>1</sub>は、0.5μm～2μmの範囲である。凸部102の高さhは、0.5μm～2μmの範囲である。さらに、複数の凸部102は、基板11の表面に所定の間隔d<sub>2</sub>を設けて配置されている。本実施の形態では、複数の凸部102の間隔d<sub>2</sub>は、0.5μm～2μmの範囲である。

また、図3に示すように、複数の凸部102は、基板11の表面101s上に碁盤目状に等間隔に配置されている。

本実施形態では、基板11上に均一な形状の複数の凸部102を形成することにより、基板11と下地層13との界面が凹凸形状となる。そのため、このような構造を有する基

板11の上にLED構造20を設けた半導体発光素子Iは、界面における光の乱反射により、光取り出し効率がさらに増大する。

## 【0020】

## (バッファ層12)

バッファ層12は、後述するように半導体発光素子のLED構造を有する化合物半導体層を有機金属化学気相成長法(MOCVD)により成膜する際に、バッファ機能を発揮する薄膜層として基板11上に設けられる。バッファ層12を設けることにより、バッファ層12上に成膜される下地層13とさらにこの上に成膜されるLED構造20を有する化合物半導体層は、良好な配向性及び結晶性を有する結晶膜となる。

## 【0021】

バッファ層12を構成するIII族窒化物半導体としては、Alを含有することが好ましく、III族窒化物であるAlNを含むことが特に好ましい。バッファ層12を構成する材料としては、一般式AlGaInNで表されるIII族窒化物半導体であれば特に限定されない。さらに、V族として、AsやPが含有されても良い。バッファ層12が、Alを含む組成の場合、AlGaNとすることが好ましく、Alの組成が50%以上であることが好ましい。

本実施の形態では、バッファ層12の厚さは、0.01μm~0.5μmである。バッファ層12の厚さが過度に薄いと、バッファ層12による基板11と下地層13との格子定数の違いを緩和する効果が十分に得られない場合がある。バッファ層12の厚さが過度に厚いと、成膜処理時間が長くなり、生産性が低下する傾向がある。

## 【0022】

## (下地層13)

下地層13に用いる材料としては、Gaを含むIII族窒化物(GaN系化合物半導体)が用いられ、特に、AlGaN、又はGaNを好適に用いることができる。本実施の形態における下地層13は、LED構造20を有する化合物半導体層の下地層として機能するものである。

本実施の形態では、下地層13の厚さは、0.1μm以上、好ましく0.5μm以上、さらに好ましくは1μm以上である。但し、下地層13の厚さは、通常、10.0μm以下である。

## 【0023】

## (LED構造20)

前述したように、LED構造20を構成するn型半導体層14は、n型コンタクト層14a及びn型クラッド層14bを有する。発光層15は、障壁層15a及び井戸層15bが交互に積層された構造を有する。p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bが積層されている。

## 【0024】

## (n型半導体層14)

n型半導体層14のn型コンタクト層14aとしては、下地層13と同様にGaN系化合物半導体が用いられる。また、下地層13及びn型コンタクト層14aを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1μm~20μm、好ましくは0.5μm~15μm、さらに好ましくは1μm~12μmの範囲に設定することが好ましい。

## 【0025】

n型クラッド層14bは、AlGaN、GaN、GaInN等によって形成することができる。また、これらの構造のヘテロ接合や複数回積層した超格子構造としてもよい。GaNとする場合には、発光層15のGaNのバンドギャップよりも大きくすることが望ましい。n型クラッド層14bの膜厚は、好ましくは5nm~500nm、より好ましくは5nm~100nmの範囲である。

## 【0026】

## (発光層15)

10

20

30

40

50

発光層15は、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層され、且つ、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成される。本実施の形態では、発光層15は、6層の障壁層15aと5層の井戸層15bとが交互に繰り返して積層され、発光層15の最上層及び最下層に障壁層15aが配され、各障壁層15aの間に井戸層15bが配される構成とされている。

## 【0027】

障壁層15aとしては、例えば、インジウムを含有した窒化ガリウム系化合物半導体からなる井戸層15bよりもバンドギャップエネルギーが大きいAl<sub>c</sub>Ga<sub>1-c</sub>N(0.3)等の窒化ガリウム系化合物半導体を好適に用いることができる。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga<sub>1-s</sub>In<sub>s</sub>N(0 < s < 0.4)等の窒化ガリウムインジウムを用いることができる。

## 【0028】

## (p型半導体層16)

p型半導体層16は、p型クラッド層16a及びp型コンタクト層16bから構成される。p型クラッド層16aとしては、好ましくは、Al<sub>d</sub>Ga<sub>1-d</sub>N(0 < d < 0.4)のものが挙げられる。p型クラッド層16aの膜厚は、好ましくは1nm~400nmであり、より好ましくは5nm~100nmである。

p型コンタクト層16bとしては、少なくともAl<sub>e</sub>Ga<sub>1-e</sub>N(0 < e < 0.5)を含んでなる窒化ガリウム系化合物半導体層が挙げられる。p型コンタクト層16bの膜厚は、特に限定されないが、10nm~500nmが好ましく、より好ましくは50nm~200nmである。

## 【0029】

## (透明正極17)

透明正極17を構成する材料としては、例えば、ITO(In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>)、AZO(ZnO-Al<sub>2</sub>O<sub>3</sub>)、IZO(In<sub>2</sub>O<sub>3</sub>-ZnO)、GZO(ZnO-Ga<sub>2</sub>O<sub>3</sub>)等の従来公知の材料が挙げられる。また、透明正極17の構造は特に限定されず、従来公知の構造を採用することができる。透明正極17は、p型半導体層16上のほぼ全面を覆うように形成しても良く、格子状や樹形状に形成しても良い。

## 【0030】

## (正極ボンディングパッド18)

透明正極17上に形成される電極としての正極ボンディングパッド18は、例えば、従来公知のAu、Al、Ni、Cu等の材料から構成される。正極ボンディングパッド18の構造は特に限定されず、従来公知の構造を採用することができる。

正極ボンディングパッド18の厚さは、100nm~1000nmの範囲内であり、好ましくは300nm~500nmの範囲内である。

## 【0031】

## (負極19)

図1に示すように、負極19は、基板11上に成膜されたバッファ層12及び下地層13の上にさらに成膜されたLED構造20(n型半導体層14、発光層15及びp型半導体層16)において、n型半導体層14のn型コンタクト層14aに接するように形成される。このため、負極19を形成する際は、p型半導体層16、発光層15及びn型半導体層14の一部を除去し、n型コンタクト層14aの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けることができる。

## 【0032】

## (半導体発光素子の製造方法)

10

20

30

40

50

次に、本実施の形態が適用される半導体発光素子の製造方法について説明する。

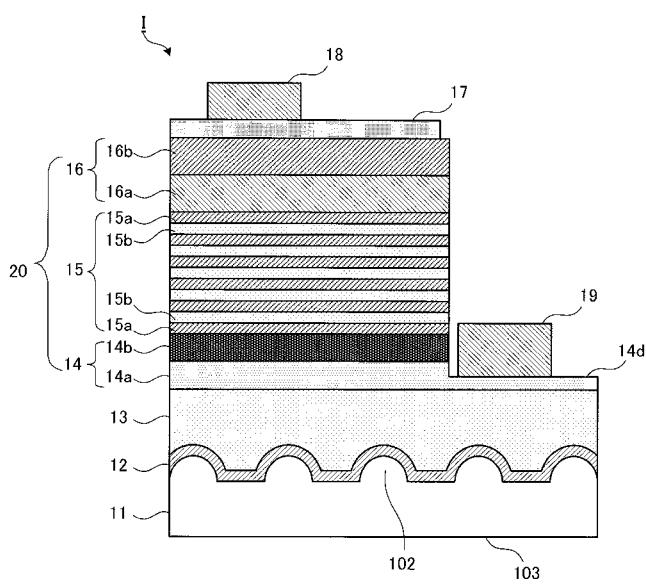

図4、図5、図6は、半導体発光素子の製造工程を説明する図である。

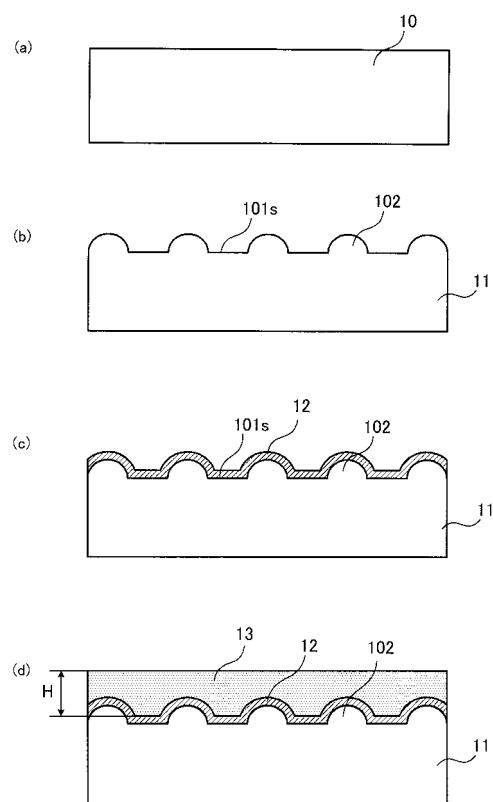

図4(a)に示すように、先ず、サファイア板10を準備する。サファイア板10の最大径は、通常、約50mm以上、好ましくは約100mm以上の範囲であり、約50mm～約200mmの範囲がより好ましい。厚さは、0.4mm～2mmの範囲が好ましい。

本実施の形態では、(1)最大径約50mmと厚さ0.7mmを有するサファイア板10、(2)最大径約100mmと厚さ1mmを有するサファイア板10、(3)最大径約150mmと厚さ1.3mmを有するサファイア板10を使用する。

#### 【0033】

次に、図4(b)に示すように、サファイア板10の表面に均一な形状を有する複数の凸部102が形成された基板11を加工する(基板加工工程)。基板11の加工では、基板11上における凸部102の平面配置を規定するマスクを形成するパターニングと、パターニングによって形成されたマスクを使って基板11をエッティングして凸部102を形成するエッティングとを行なう。パターニングは、一般的なフォトリソグラフィー法で行なうことができる。エッティングは、ドライエッティング法を用いることが好ましい。

#### 【0034】

尚、凸部102を形成する方法としては、上述したエッティング法に限定されない。例えば、サファイア板10に凸部102となる材料を、スパッタ法、蒸着法、CVD法等により積層させることにより凸部を形成してもよい。この場合、凸部102となる材料としては、サファイア板10とほぼ同等の屈折率を有する材料を用いることが好ましく、例えば、Al<sub>2</sub>O<sub>3</sub>、SiN、SiO<sub>2</sub>等を用いることができる。

#### 【0035】

続いて、図4(c)に示すように、基板11の表面101s上にIII族窒化物半導体からなるバッファ層12を形成する(バッファ層形成工程)。本実施の形態では、バッファ層12は、III族窒化物半導体をスパッタリングすることにより形成することが好ましい。スパッタリングによりバッファ層12を形成する場合、チャンバ内の窒素原料と不活性ガスの流量の比を、窒素原料が50%～100%、望ましくは75%となるようにすることができる。

#### 【0036】

また、スパッタ法によって、柱状結晶(多結晶)を有するバッファ層12を形成する場合、チャンバ内の窒素原料と不活性ガスの流量の比を、窒素原料が1%～50%、望ましくは25%となるようにすることが望ましい。これにより、V族元素を窒素とし、バッファ層12を成膜する際のガス中における窒素のガス分率を50%～99%以下の範囲とするとともに、バッファ層12を単結晶組織として形成する。その結果、短時間で良好な結晶性を有するバッファ層12を、特定の異方性を持つ配向膜として基板11上に成膜することができ、さらに、バッファ層12上に、結晶性の良好なIII族窒化物半導体を効率良く成長させることができとなる。

#### 【0037】

次に、図4(d)に示すように、本実施形態では、バッファ層12を形成工程の後、バッファ層12が形成された基板11の上面上に、凸部102を埋めるようにして、MOCVD法によりIII族窒化物半導体からなる下地層13を成膜する。尚、本実施の形態では、下地層13の最大厚さHは、凸部102の高さhの2倍以上であることが好ましい。

#### 【0038】

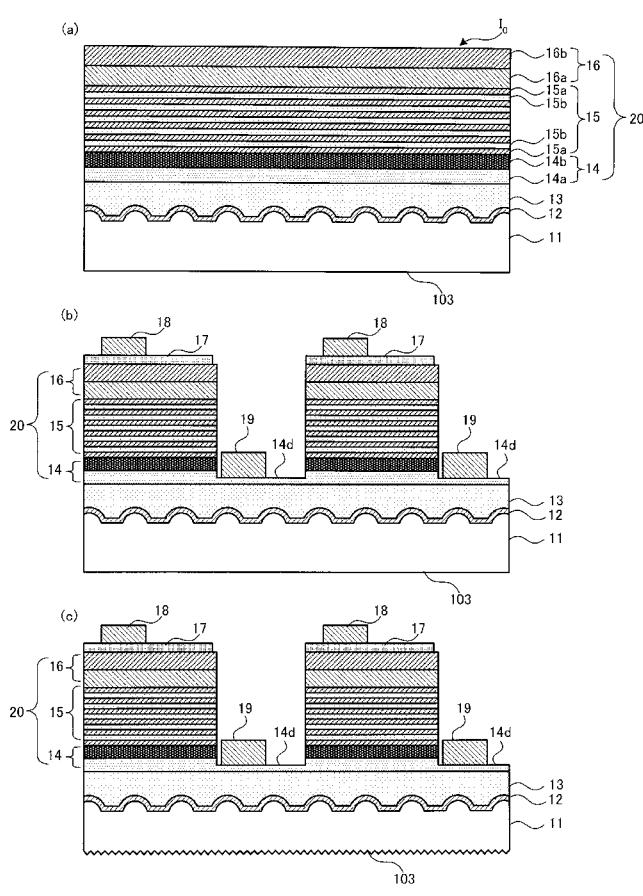

次に、図5(a)に示すように、成膜した下地層13上に、MOCVD法により、n型半導体層14、発光層15、及びp型半導体層16を順次積層し、半導体発光素子ウェーハI<sub>0</sub>を形成する。

#### 【0039】

下地層13、及びn型半導体層14、発光層15、p型半導体層16をMOCVD法で積層する場合に使用するキャリアガスとしては、例えば、水素(H<sub>2</sub>)、窒素(N<sub>2</sub>)；III族原料であるGa源としてトリメチルガリウム(TMG)、トリエチルガリウム(

10

20

30

40

50

TEG) ; Al 源としてトリメチルアルミニウム (TMA) 、トリエチルアルミニウム (TEA) ; In 源としてトリメチルインジウム (TMI) 、トリエチルインジウム (TEI) ; V 族原料である N 源としてアンモニア (NH<sub>3</sub>) 、ヒドラジン (N<sub>2</sub>H<sub>4</sub>) 等が用いられる。また、ドーパントとしては、n 型には Si 原料としてモノシリコン (SiH<sub>4</sub>) 、ジシリコン (Si<sub>2</sub>H<sub>6</sub>) ; Ge 原料としてゲルマンガス (GeH<sub>4</sub>) 、テトラメチルゲルマニウム ((CH<sub>3</sub>)<sub>4</sub>Ge) 、テトラエチルゲルマニウム ((C<sub>2</sub>H<sub>5</sub>)<sub>4</sub>Ge) 等の有機ゲルマニウム化合物 ; p 型には Mg 原料としてシクロペニタジエニルマグネシウム (Cp<sub>2</sub>Mg) を利用できる。

## 【0040】

本実施の形態において、基板 11 に下地層 13 を形成することにより、この上に成膜される III 族窒化物半導体からなる n 型半導体層 14 、発光層 15 、p 型半導体層 16 からなる LED 構造 20 の結晶の結晶性が良好となる。その結果、内部量子効率に優れ、リーケの少ない半導体発光素子 I が得られる。

尚、LED 構造 20 の内、下地層 13 を MOCVD 法によって形成した後、n 型コンタクト層 14a 及び n 型クラッド層 14b の各層をスパッタ法で形成し、その上の発光層 15 を MOCVD 法で形成し、そして、p 型半導体層 16 を構成する p 型クラッド層 16a 及び p 型コンタクト層 16b の各層を反応性スパッタ法で形成してもよい。

## 【0041】

次に、図 5 (b) に示すように、基板 11 上にバッファ層 12 、下地層 13 及び LED 構造 20 を成膜した後、LED 構造 20 の p 型半導体層 16 上に透明正極 17 を積層し、その上に正極ボンディングパッド 18 を形成する。続いて、LED 構造 20 の所定の位置をエッチング除去することにより、n 型半導体層 14 を露出させて露出領域 14d を形成し、露出領域 14d の各々に正極ボンディングパッド 18 と対になるように複数の負極 19 を形成する。

## 【0042】

負極 19 を形成する際は、まず、基板 11 上に形成された p 型半導体層 16 、発光層 15 及び n 型半導体層 14 の一部をドライエッチング等の方法によって除去し、n 型コンタクト層 14a の露出領域 14d を形成する。そして、この露出領域 14d 上に、例えば、露出領域 14d 表面側から順に、Ni 、Al 、Ti 、Au の各材料を従来公知の方法で積層することにより、詳細な図示を省略する 4 層構造の負極 19 を形成することができる。

## 【0043】

続いて、図 5 (c) に示すように、基板 11 が所定の厚さになるまで基板 11 の被研削面 103 を、研削及び研磨する (研削工程・研磨工程)。本実施の形態では、約 20 分間程度の研削工程により、基板 11 を研削し、基板 11 の厚さを、例えば、約 1000 μm から約 120 μm 迄減少させる。さらに、本実施の形態では、研削工程に続き、約 15 分間の研磨工程により、基板 11 の厚さを、約 120 μm から約 80 μm 迄に研磨する。

ここで、本実施の形態では、研削工程及び研磨工程により、基板 11 の厚さを調整するとともに、基板 11 の裏面である被研削面 103 の表面粗さ Ra を、3 nm ~ 25 nm 、好ましくは、5 nm ~ 20 nm になるように調整する。

## 【0044】

被研削面 103 の表面粗さ Ra を上述した範囲に調整する方法は特に限定されないが、例えば、基板 11 の被研削面 103 を研削・研磨する際に、被研削面 103 と所定の研削・研磨装置の研削定盤の被研削面 103 とが摺り合わされる部分に研削材または研磨材を供給する。研削材または研磨材の種類は特に限定されず、市販のスラリー型の研削材または研磨材を使用することができる。

## 【0045】

また、本実施の形態において、表面粗さ Ra のその測定方法は特に限定されないが、例えば、AFM (原子間力顕微鏡 ; Atomic Force Microscope) 、SEM (走査型電子顕微鏡 ; Scanning Electron Microscope) 等による視野角解析による公知の方法で、算術平均粗さ Ra として求めることができ

10

20

30

40

50

る。

【0046】

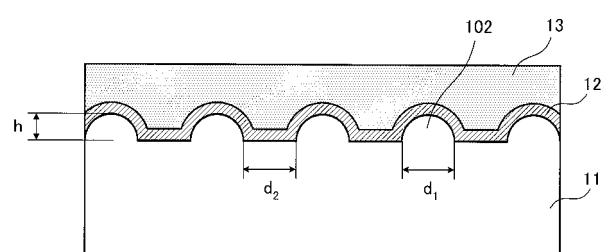

次に、図6(a)に示すように、LED構造20側からn型コンタクト層14aの露出領域14dにレーザL1を照射し割溝30を形成する(割溝形成工程)。割溝30は、後述するように、基板11を分割するための切断予定ラインに沿ってレーザL1を照射することにより形成する。割溝30の幅は特に制限されない。本実施の形態では、割溝30の深さは、通常、基板11の表面から6μm以上であり、10μm以上であることが好ましく、20μm以上であることがさらに好ましい。割溝30の深さが過度に小さいと、切断面が斜めに割れ、不良チップが生成する傾向がある。

【0047】

割溝30の断面形状は矩形、U字状、V字状等の形状が採用され、好ましくは、V字状またはU字状であり、V字状が特に好ましい。割溝30の断面形状がV字状の場合、チップ状に分割する際、V字状の最先端付近からクラックが発生し、不良率が低下する傾向がある。尚、割溝30の断面形状は、ビーム径および焦点位置等のレーザ光学系の制御によりコントロール可能である。

【0048】

続いて、図6(b)に示すように、前述した研磨工程により表面粗さRaを調整した基板11の被研削面103側から、基板11を分割するための切断予定ラインに沿ってレーザL2を照射することにより基板11の内部に加工変質部分(内部クラック)41,42を設ける(レーザ加工工程)。本実施の形態では、レーザ加工工程において、基板11の内部の被研削面側から厚さ方向で(2/3)部の範囲に、断続的に2個の加工変質部分41,42を設けている。

また、加工変質部分41,42は、基板11に設けた割溝30と基板11の厚さ方向に略同一の直線上に形成している。

【0049】

本実施の形態において加工変質部分41,42とは、例えば、サファイア製の基板11の内部にレーザL2の焦光点を合わせて照射することにより、基板11のレーザL2が照射された部分が溶融・再固化した改質領域や多光子吸収による改質領域等を言う。この場合、レーザ照射による溶融・再固化に伴い生じる微小なクラックの発生も含まれる。

【0050】

具体的には、例えば、ステルスレーザ加工機(図示せず)を用い、エキシマ励起のパルスレーザを照射しながら、基板11を分割するための切断予定ラインに沿ってレーザL2を照射する。この際、基板11上に照射するレーザL2の焦点を変化させることにより、基板11の厚さ方向において複数箇所(図6(b)では2箇所)に設けることが可能となる。

【0051】

使用するレーザとしては、例えば、CO2レーザ、YAG(イットリウム・アルミニウム・ガーネット)レーザ等が挙げられる。本実施の形態では、パルス照射のレーザを用いることが最も好ましい。本実施の形態では、レーザL2の波長としては、266nm又は355nmを使用している。また、基板11の切断予定ラインに沿ってレーザL2を間歇的に照射(パルス照射)することにより、基板11の内部に効果的にダメージを付与し、この部分を揮散あるいは強度的に弱い材質へと変換させることができる。この場合、パルス周期を、10~40Hzの範囲とすることが好ましい。

【0052】

次に、図6(c)に示すように、基板11を加工変質部分41,42に沿って切断し、複数のチップに分割する(分割工程)。具体的には、例えば、ブレーカ装置(図示せず)を用い、割溝30及び加工変質部分41,42に沿うようにブレード(図示せず)を押し当てることにより、加工変質部分41,42に沿って基板11を押し割り、複数のチップに分割する。

【0053】

10

20

30

40

50

本実施形態では、分割工程において、割溝30及び加工変質部分41,42に沿って基板11を個々の発光素子単位のチップに切断することで、加工変質部分41,42を起点として、基板11に亀裂を生じさせつつ、半導体発光素子ウェーハI<sub>0</sub>（図5（a）参照）を個々のチップ状態の半導体発光素子Iに分割することができる。

このとき、分割後の基板11の分割面（端面11a）には、加工変質部分41,42の少なくとも一部が残存する領域と、基板11を切断した際に分割面（端面11a）に生じる亀裂痕が不規則に残存する領域とが存在し、分割面（端面11a）のほぼ全体が粗面となる。

このように、基板11の分割面（端面11a）を粗面として形成することにより、分割面（端面11a）の表面積が増加し、入射した光を効率良く外部に出射できる基板11とすることができる、光取り出し効率に優れた半導体発光素子Iを製造することが可能となる。

#### 【0054】

本実施の形態においてIII族窒化物半導体発光素子は、通常、基板11上にLED構造20を成膜し、次いで、基板11の被研削面103を研削・研磨処理によって所定の厚さに調整し、その後、適当な大きさに切断し、所定の厚さの基板11を有する半導体発光素子チップとして得られる。

#### 【0055】

本実施の形態においては、半導体層と基板の熱膨張係数の違いに起因して、基板の薄板化後のウェーハの反りにも影響してくる。特に、発光層を含む半導体層の膜厚が5μm以上の場合には半導体層膜厚が厚くなるほど反りが大きくなり、その後のレーザ加工工程に悪い影響を及ぼす。

しかしながら、本実施の形態が適用される半導体発光素子の製造方法によれば、研磨工程において、研削工程で研削された基板の被研削面の表面粗さRaを3nm～25nmに調整することにより、レーザ加工工程における基板の平坦性を保つことができる。

このような効果は、基板、例えば、サファイア基板の最大径が、大きいものほど格別となる。本実施の形態では、最大径が、約50mm<約100mm<約150mmの順で、特に効果的であった。

#### 【0056】

上述したように、本実施の形態が適用される半導体発光素子Iは、例えば、これと蛍光体とを組み合わせてなるランプとして使用することができる。半導体発光素子Iと蛍光体とを組み合わせたランプは、当業者周知の手段によって当業者周知の構成とすることができる。また、従来より、III族窒化物半導体発光素子と蛍光体と組み合わせることによって発光色を変える技術を採用することが可能である。ランプの例としては、一般用途の砲弾型、携帯のバックライト用途のサイドビュー型、表示器に用いられるトップビュー型等いかなる用途にも用いることができる。

#### 【図面の簡単な説明】

#### 【0057】

【図1】III族窒化物半導体層を有する半導体発光素子の一例を示した断面図である。

【図2】複数の凸部が形成された基板を説明する図である。

【図3】複数の凸部が形成された基板を説明する図である。

【図4】半導体発光素子の製造工程を説明する図である。

【図5】半導体発光素子の製造工程を説明する図である。

【図6】半導体発光素子の製造工程を説明する図である。

#### 【符号の説明】

#### 【0058】

10...サファイア板、11...基板、11a...分割面（端面）、12...バッファ層、13...下地層、14...n型半導体層、15...発光層、16...p型半導体層、17...透明正極、18...正極ボンディングパッド、19...負極、20...LED構造、30...割溝、41,42...加工変質部分（内部クラック）、102...凸部、103...被研削面、I...半導体発光素

10

20

30

40

50

子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】