(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6370922号

(P6370922)

(45) 発行日 平成30年8月8日(2018.8.8)

(24) 登録日 平成30年7月20日(2018.7.20)

(51) Int.Cl.

H04L 25/49 (2006.01)

H03M 5/08 (2006.01)

F 1

H04L 25/49

H03M 5/08

H

請求項の数 15 (全 15 頁)

(21) 出願番号 特願2016-563826 (P2016-563826)

(86) (22) 出願日 平成27年3月11日 (2015.3.11)

(65) 公表番号 特表2017-517941 (P2017-517941A)

(43) 公表日 平成29年6月29日 (2017.6.29)

(86) 國際出願番号 PCT/US2015/020027

(87) 國際公開番号 WO2015/163989

(87) 國際公開日 平成27年10月29日 (2015.10.29)

審査請求日 平成30年2月14日 (2018.2.14)

(31) 優先権主張番号 14/258,980

(32) 優先日 平成26年4月22日 (2014.4.22)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔡田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】パルス幅変調データデコーダ

## (57) 【特許請求の範囲】

## 【請求項 1】

データ入力信号からのパルス幅変調されたデータを復号するための装置であって、前記データ入力信号は、ビットのシリアルストリームを含み、前記シリアルストリームの各ビットは、ビット時間にわたり、前記シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリングパルスを有し、前記装置は、

前記データ入力信号上の短いトレイリングパルスを抑制することと、前記データ入力信号上の長いトレイリングパルスを抑制しないことと、を含む、トレイリングパルスを短縮するために前記データ入力信号をフィルタリングするための手段と、

前記データ入力信号のトレイリングエッジで前記フィルタリングされたデータ入力信号をラッチするための手段と、

を備える、装置。

## 【請求項 2】

抑制されるトレイリングパルスの持続時間が較正される、請求項 1 に記載の装置。

## 【請求項 3】

前記較正は、3 の係数よりも大きい遅延の範囲を含む、請求項 2 に記載の装置。

## 【請求項 4】

前記較正は、デジタルで制御される、請求項 2 に記載の装置。

## 【請求項 5】

前記データ入力信号を受信し、前記ラッチするための手段が前記フィルタリングされた

10

20

データ信号をラッチするようにトリガするためのクロック出力信号を生成するように構成されたクロック生成器モジュールをさらに備える、請求項 1 に記載の装置。

**【請求項 6】**

前記クロック生成器モジュールは、前記データ入力信号に結合された入力、および前記クロック出力信号に結合された出力を有するインバータを備え、前記ラッチするための手段は、前記クロック出力信号のトレイリングエッジで前記フィルタリングされたデータ信号をラッチする、請求項 5 に記載の装置。

**【請求項 7】**

前記装置はデコーダであり、

前記データ入力信号を前記フィルタリングするための手段は、前記データ入力信号上の H i g h パルスの持続時間を短縮することによって、フィルタリングされたデータ信号を生成するように構成された片側パルスフィルタであり、ここにおいて、前記片側パルスフィルタは、前記データ入力信号上の短い H i g h パルスを抑制するように構成され、前記データ入力信号上の長い H i g h パルスを抑制しないように構成される。10

前記フィルタリングされたデータ入力信号を前記ラッチするための手段は、前記データ入力信号の各ビット時間の終わりに、前記フィルタリングされたデータ信号をラッチするように構成されたフリップフロップである、請求項 1 に記載の装置。

**【請求項 8】**

前記片側パルスフィルタは、立ち上がり遷移に関する入出力遅延よりも大きい立ち上がり遷移に関する入出力遅延を有する、請求項 7 に記載の装置。20

**【請求項 9】**

前記片側パルスフィルタの立ち上がり遷移に関する前記入出力遅延が較正されるように適合される、請求項 8 に記載の装置。

**【請求項 10】**

前記片側パルスフィルタは、

コンデンサと、

前記データ入力信号に基づいて前記コンデンサを放電するように構成された電流源と、を含み、

立ち上がり遷移に関する前記片側パルスフィルタの入出力遅延は、前記コンデンサのキャパシタンスと前記電流源の電流の積に基づく、30

請求項 7 に記載の装置。

**【請求項 11】**

データ入力信号からのパルス幅変調されたデータを復号するための方法であって、前記データ入力信号は、ビットのシリアルストリームを含み、前記シリアルストリームの各ビットは、ビット時間にわたり、前記シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリングパルスを有し、前記方法は、

前記トレイリングパルスを短縮するために前記データ入力信号をフィルタリングすることと、ここにおいて、前記データ入力信号をフィルタリングすることは、前記データ入力信号上の短いトレイリングパルスを抑制することと、前記データ入力信号上の長い H i g h トレイリングを抑制しないことと、を含む、40

前記データ入力信号のトレイリングエッジで前記フィルタリングされたデータ入力信号をラッチすることと、

を備える、方法。

**【請求項 12】**

抑制されるトレイリングパルスの持続時間を較正することをさらに備える、請求項 11 に記載の方法。

**【請求項 13】**

前記較正は、前記データ入力信号の同期状態中に実行される、請求項 12 に記載の方法。50

**【請求項 14】**

前記較正は、デジタルで制御される、請求項 1 2 に記載の方法。

【請求項 1 5】

前記フィルタリングされたデータ入力信号をラッチすることに使用するために、前記データ入力信号に基づいてクロック出力信号を生成することをさらに備える、請求項 1 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

[0001]本発明は、電子回路に関し、より具体的には、パルス幅変調されたデータを復号するための回路に関する。 10

【背景技術】

【0 0 0 2】

[0002]モバイルインダストリプロセッサインターフェース (M I P I :Mobile Industry Processor Interface) アライアンスは、M - P H Y と名付けられたシリアルインターフェース物理レイヤ (P H Y) に関する規格を定めてきた。M - P H Y は、例えば、携帯電話における回路間の通信のために使用されうる。M - P H Y の例となる使用は、プロセッサとメモリとの間のユニバーサルフラッシュストレージ (U F S) リンクに関するものである。

【0 0 0 3】

[0003]M - P H Y は、クロックがデータ信号に組み込まれているパルス幅変調 (P W M) を使用して通信する。データ信号は、ビットのシリアルストリームを含む。シリアルストリームの各ビットは、ビット時間と称されうる時間間隔にわたる。 20

【0 0 0 4】

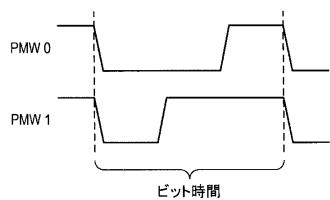

[0004]図 1 は、パルス幅変調されたデータの波形図である。図 1 は、M - P H Y とともに使用される波形を例示しているが、他の波形が異なる極性および異なるビットの定義とともに使用されうる。各ビット時間の始まりと終わりに、データ信号は、H i g h から L o w に遷移する。Z E R O (0) データ値は、H i g h 時間よりも広いL o w 時間を持つパルスによって表される。O N E (1) データ値は、L o w 時間よりも広いH i g h 時間を持つパルスによって表される。広いパルスの幅は、例えば、ビット時間の 3 分の 2 であります。 30

【0 0 0 5】

[0005]M - P H Y におけるデータレートは、「ギア」と表現される。各ギアは、表 1 で図示されているように、サポートされているデータレートの 3 対 1 の範囲 (three-to-one range) を有する。

【0 0 0 6】

【表1】

表1

| ギア | 最小<br>データレート | 最大<br>データレート |    |

|----|--------------|--------------|----|

| 1  | 3 Mbps       | 9 Mbps       | 10 |

| 2  | 6 Mbps       | 18 Mbps      |    |

| 3  | 12 Mbps      | 36 Mbps      |    |

| 4  | 24 Mbps      | 72 Mbps      |    |

| 5  | 48 Mbps      | 144 Mbps     | 20 |

| 6  | 96 Mbps      | 288 Mbps     |    |

| 7  | 192 Mbps     | 576 Mbps     |    |

## 【0007】

[0006] M - P H Y リンク上の通信は、バーストで生じうる。バーストは、受信機を送信機に同期させるのに役立つデータシーケンスを有する同期（S Y N C）状態を含む様々な状態を含む。S Y N C 状態は、例えば、データ値間の高密度の遷移を有しうる。ユーザデータは、8 B 1 0 B（10個のパルス幅変調されたビットとしてコーディングされた8個のデータビット）コーディングされたシンボルで構成されるP A Y L O A D 状態で通信される。

## 【0008】

[0007] 従来のP W M デコーダは、データを復元するためにオーバーサンプリングを使用する。例えば、デコーダは、受信されたデータ値を決定するために、ビット時間毎に12回、データ入力をサンプリングし、サンプルを分析しうる。このタイプのデコーダは、より高いギアで使用するには適していないことがある。

[0007A] 米国特許出願公開第U S 2 0 1 0 / 0 2 6 0 2 8 3号（A 1）は、値がディテイサイクル比でビットシグナリングされ、デューティサイクル比がシグナリングの伝送速度に依存して変化されるデューティサイクル変調ビットシグナリング方法および回路に関する。ビット期間は、長フェーズおよび短フェーズを含み、デューティサイクルは、長フェーズの持続時間と短フェーズの持続時間との比が伝送速度の低下に対して増大するよう変化される。デューティサイクル比は、伝送速度の1以上のレンジに従ってシグナリングの伝送速度に依存して変化される。高伝送速度レンジでは、デューティサイクルは固定比として規定され、低伝送速度レンジでは、デューティサイクルはビット期間の短フェーズの固定長によって規定される。

[0007B] 国際公開第2 0 1 3 / 0 4 8 3 9 5号（A 1）は、オーバークロッキングを使用する低電力データリカバリに関する。受信機は、送信機から受信された入力信号の第1

10

20

30

40

50

の立ち下がりエッジおよび第1の立ち上がりエッジを検出するエッジ検出器と、第1の立ち下がりエッジを検出することに応答して第1の方向のカウントを計数し、入力信号の第1の立ち上がりエッジを検出することに応答して第2の方向のカウントを計数するカウンタと、を含む。カウンタは、第1および第2の検出のカウントに基づいて最終カウント値を生成する。受信機は、最終カウント値に従ってなされる決定によって入力信号中のデータが論理的ハイまたは論理的ローのいずれの値であるかを決定する決定部を含む。

【発明の概要】

【0009】

[0008]ある態様では、データ入力信号からのパルス幅変調されたデータを復号するためのデコーダが提供され、データ入力信号は、ビットのシリアルストリームを含み、シリアルストリームの各ビットは、ビット時間にわたり、シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするHighパルスを有する。デコーダは、データ入力信号上のHighパルスの持続時間を短縮することによって、フィルタリングされたデータ信号を生成するように構成された片側パルスフィルタ(one-sided pulse filter)と、データ入力信号の各ビット時間の終わりに、フィルタリングされたデータ信号をラッチするように構成されたフリップフロップと、を含む。10

【0010】

[0009]ある態様では、データ入力信号からのパルス幅変調されたデータを復号するための方法が提供され、データ入力信号は、ビットのシリアルストリームを含み、シリアルストリームの各ビットは、ビット時間にわたり、シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリング(trailing)パルスを有する。方法は、トレイリングパルスを短縮するためにデータ入力信号をフィルタリングすることと、データ入力信号のトレイリングエッジでフィルタリングされたデータ入力信号をラッチすることと、を含む。20

【0011】

[0010]ある態様では、データ入力信号からのパルス幅変調されたデータを復号するための装置が提供され、データ入力信号は、ビットのシリアルストリームを含み、シリアルストリームの各ビットは、ビット時間にわたり、シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリングパルスを有する。装置は、トレイリングパルスを短縮するためにデータ入力信号をフィルタリングするための手段と、データ入力信号のトレイリングエッジでフィルタリングされたデータ入力信号をラッチするための手段と、を含む。30

【0012】

[0011]本発明の他の特徴および利点が、例として本発明の態様を例示している以下の説明から明らかであるはずである。

【0013】

[0012]本発明の詳細は、その構造と動作の両方に関して、添付の図面の検討によって部分的に突き止められ得、図面では、同様の参照番号は同様の部分を指す。

【図面の簡単な説明】

【0014】

40

【図1】パルス幅変調された(PWM)データの波形図である。

【図2】本明細書で開示される実施形態に係るPWMデコーダの機能ブロック図である。

【図3】図2のPWMデコーダの動作を例示する波形図である。

【図4】本明細書で開示される実施形態に係る片側パルスフィルタの回路図である。

【図5】図4の片側パルスフィルタの動作を例示する波形図である。

【図6】本明細書で開示される実施形態に係るパルス幅変調されたデータを復号するためのプロセスのフローチャートである。

【詳細な説明】

【0015】

[0019]添付の図面に関連して以下で述べられる詳細な説明は、様々な構成の説明として50

意図されており、本明細書で説明されている概念が実施されうる構成だけを表すようには意図されていない。詳細な説明は、様々な概念の完全な理解を提供する目的で、具体的な詳細を含む。しかしながら、これらの概念がこれらの具体的な詳細なしに実施されうることは当業者には明らかだろう。いくつかの事例では、周知の構造およびコンポーネントが、そのような概念を曖昧にすることを回避するために簡略化された形態で図示されている。

#### 【 0 0 1 6 】

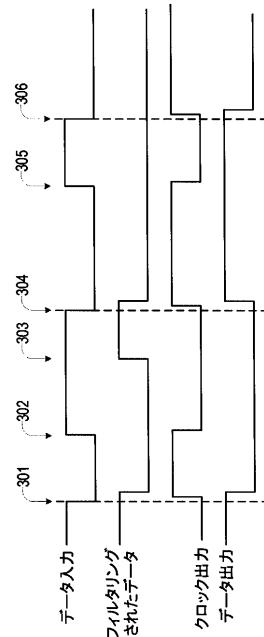

[0020]図2は、本明細書で開示される実施形態に係るPWMデコーダの機能ブロック図である。PWMデコーダは、多くの異なる方法で実装されうる。ある実施形態では、PWMデコーダは、相補型金属酸化膜半導体(CMOS)集積回路で実装される。

10

#### 【 0 0 1 7 】

[0021]デコーダは、データ入力信号(データ入力)上でデータのシリアルストリームを受信する。データ入力信号は、例えば、図1で例示されたような波形を使用してパルス幅変調される。デコーダは、データ入力信号におけるPWMコーディングされたデータの値をシグナリングするデータ出力信号(データ出力)を生成するために、データ入力信号におけるデータを復号する。PWMデコーダはまた、データ出力信号のタイミングをシグナリングするクロック出力信号(クロック出力)を供給することができる。

#### 【 0 0 1 8 】

[0022]デコーダは、データ入力信号を受信し、フィルタリングされたデータ信号(フィルタリングされたデータ)を生成する片側パルスフィルタ20を含む。片側パルスフィルタ20は、それが受信するパルスのHigh時間(または切断)を短縮する。片側パルスフィルタ20によるパルス短縮の量は、PWMデータZEROビットのHighパルスが完全に抑制され、フィルタリングされたデータ信号がデータZEROのビット時間の間にLowに留まるように、およびPWMデータONEビットのアクティブなパルスが完全には抑制されず、フィルタリングされたデータ信号がデータONEのビット時間の間にHighに遷移するように設定される。

20

#### 【 0 0 1 9 】

[0023]片側パルスフィルタ20は、立ち上がり遷移および立ち下がり遷移に関する異なる入出力遅延(input-to-output delays)を有するバッファと見なされる。したがって、片側パルスフィルタ20は、非対称フィルタと称される。立ち上がり遷移に関する遅延は、立ち下がり遷移に関する遅延よりも大きく、その結果Highパルスの持続時間が短縮される。立ち下がり遷移に関する遅延は短く、例えば、数ゲート分の遅延(a few gate delays)であります。

30

#### 【 0 0 2 0 】

[0024]信号遷移はエッジとも称され得、例えば、立ち上がり遷移は立ち上がりエッジとも称され得、立ち下がり遷移は立ち下がりエッジと称される。同様に、立ち上がり遷移は、LowレベルからHighレベルへの遷移と称され得、立ち下がり遷移は、HighレベルからLowレベルへの遷移と称される。

#### 【 0 0 2 1 】

[0025]デコーダは、ユーザデータを受信する前に立ち上がり遷移に関する遅延を較正することができる。立ち上がり遷移に関する遅延を較正することは、抑制されるHighパルスの持続時間の較正を提供する。例えば、遅延は、受信されたMPHYデータ信号の同期状態中に較正されうる。較正は、例えば、可能性のある遅延値の範囲中を掃引することを含むことができる。遅延値のいくつかであって、過度に長い遅延を有するものは、結果としてデータ出力信号がすべてZEROになることをもたらすだろう。他の遅延値であって、過度に短い遅延を有するものは、結果としてデータ出力信号がすべてONEになることをもたらすだろう。較正は、例えば、過度にHighである最低遅延値と、過度にLowである最高遅延値との中間の遅延を選択することができる。較正はまた、同期状態における予期されるパターンに基づいて特定の出力値を探索することができる。較正モジュールは、同期(SYNC)状態中、データ出力信号をモニタすることができる。データ出

40

50

力信号の値に基づいて、較正モジュールは、データ出力信号がもはや一定の Z E R O または O N E にならないように遅延設定を調整することができる。較正モジュールはまた、8 B 1 0 B 符号化され、3 ビット時間毎に少なくとも 1 つの遷移を有するデータパターンに関して検査することもできる。

#### 【 0 0 2 2 】

[0026] 片側パルスフィルタ 2 0 からのフィルタリングされたデータ信号は、フリップフロップ 4 5 において捕捉される。フリップフロップ 4 5 は、フィルタリングされたデータ信号に接続されたデータ入力 ( D ) 、クロック出力信号に接続されたクロック入力、およびデコーダのデータ出力信号に接続されたデータ出力 ( Q ) を有する。

#### 【 0 0 2 3 】

[0027] クロック生成器モジュール 3 0 は、クロック出力信号を供給する。図 2 で例示される実施形態では、クロック生成器モジュール 3 0 はインバータ 3 5 を含む。クロック生成器モジュール 3 0 は、データ入力信号からクロック出力信号を生成する。インバータ 3 5 は、データ入力信号に接続された入力、およびクロック出力信号に接続された出力を有する。したがって、クロック出力信号は、データ入力信号の論理的な補完物 ( complement ) である。他の実施形態では、クロック生成器モジュール 3 0 は、例えば、フロップフロップ 4 5 の特性に基づいて、他の回路を含むことができる。

#### 【 0 0 2 4 】

[0028] データ入力信号が各ビット時間の終わりに立ち下がるので、クロック出力信号は各ビット時間の終わりに立ち上がる。フリップフロップ 4 5 は立ち上がりエッジトリガされ ( rising-edge triggered ) 、クロック出力信号の立ち上がりエッジでフィルタリングされたデータ信号をラッチし、これは、各ビット時間の終わりに生じる。したがって、データ出力信号は、各ビット時間の終わりに、フィルタリングされたデータ信号の値に設定される。クロック生成器モジュール 3 0 および片側パルスフィルタ 2 0 は、それらの遅延がフリップフロップ 4 5 のタイミング要件を満たすように設計されうる。例えば、立ち下がり遷移に関する片側パルスフィルタ 2 0 の入力から出力までの最小遅延は、( クロック生成器モジュール 3 0 の遅延と比べて ) フリップフロップ 4 5 の保持時間要件を満たすように十分長くなくてはならない。

#### 【 0 0 2 5 】

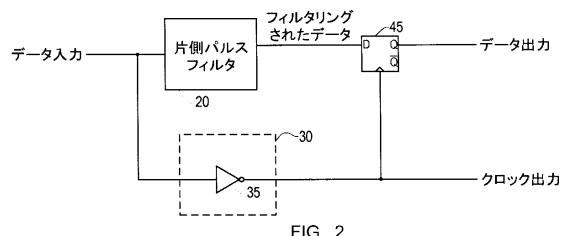

[0029] 図 3 は、図 2 の P W M デコーダの動作を例示する波形図である。図 3 は、時間 3 0 1 から時間 3 0 4 までのデータ O N E ビット時間、および時間 3 0 4 から時間 3 0 6 までのデータ Z E R O ビット時間を例示している。例示の明確性のために、波形は、ビット時間に対して小さい回路遅延、および瞬間的である信号遷移に関して例示されている。

#### 【 0 0 2 6 】

[0030] データ O N E ビット時間では、時間 3 0 1 で、データ入力信号は立ち下がり、その後まもなくフィルタリングされたデータ信号もまた立ち下がる。データ入力信号の立ち下がりからフィルタリングされたデータ信号の立ち下がりまでの遅延時間は、立ち下がり遷移に関する片側パルスフィルタ 2 0 の遅延である。時間 3 0 2 で、データ入力信号は立ち上がる。時間 3 0 3 で、フィルタリングされたデータ信号は立ち上がる。時間 3 0 2 から時間 3 0 3 までの遅延は、立ち上がり遷移に関する片側パルスフィルタ 2 0 の遅延である。時間 3 0 4 で、データ O N E ビット時間の終わりに、データ入力信号は立ち下がり、クロック出力信号は立ち上がる。クロック出力信号の立ち上がりエッジは、フリップフロップ 4 5 がフィルタリングされたデータ信号をラッチするようにトリガする。フィルタリングされたデータ信号はこの時 H i g h であるので、データ出力は O N E に設定され、これは、データ入力信号の P W M コーディングされた値に一致する。

#### 【 0 0 2 7 】

[0031] データ Z E R O ビット時間では、時間 3 0 4 で、データ入力信号は立ち下がり、その後まもなくフィルタリングされたデータ信号は、時間 3 0 1 にあったように立ち下がる。時間 3 0 5 で、データ入力信号は立ち上がる。時間 3 0 6 の、データ Z E R O ビット時間の終わりに、データ入力信号は立ち下がり、クロック出力信号は立ち上がる。時間 3

10

20

30

40

50

05から時間306までのデータ入力信号のアクティブ時間は、立ち上がり遷移に関する片側パルスフィルタ20の遅延よりも短い。したがって、フィルタリングされたデータ信号はLOWのままである。クロック出力信号の立ち上がりエッジは、フリップフロップ45がフィルタリングされたデータ信号をラッチするようにトリガする。フィルタデータ信号はこの時LOWであるので、データ出力は、ZEROに設定され、これは、データ入力信号のPWMコーディングされた値に一致する。

#### 【0028】

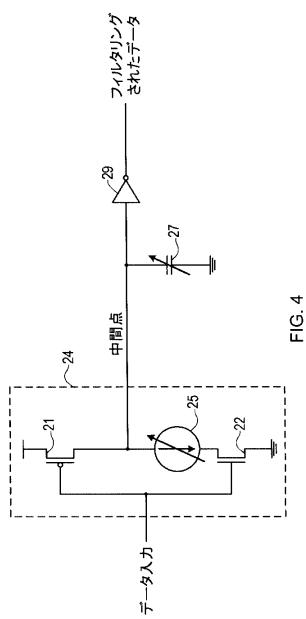

[0032]図4は、本明細書で開示される実施形態に係る片側パルスフィルタの回路図である。片側パルスフィルタは、図2のデコーダにおける片側パルスフィルタ20として使用されうる。

10

#### 【0029】

[0033]図4の片側パルスフィルタは、データ入力信号を受信し、パルスの短縮されたHigh時間を持つフィルタリングされたデータ信号を生成する。片側パルスフィルタは、パルス短縮の量を制御するために、コンデンサ27を放電する電流を使用する。電流は、データ入力信号に基づいてコンデンサ27を切替え可能に放電する電流源25からのものである。

#### 【0030】

[0034]片側パルスフィルタは、pチャネルトランジスタ、電流源25、およびnチャネルトランジスタ22から編成される第1のインバータ24を含む。インバータの出力は、片側パルスフィルタの中間点(Mid)に接続されている。第2のインバータ29は、中間点に接続された入力、およびフィルタリングされたデータ信号に接続された出力を有する。pチャネルトランジスタ21は、データ入力信号に接続されたゲート、電圧源に接続されたソース、および第1のインバータ24の出力に接続されたドレインを有する。nチャネルトランジスタ22は、データ入力信号に接続されたゲート、および接地基準に接続されたソースを有する。nチャネルトランジスタ22は、電流源25の1つの端子に接続されたドレインを有し、電流源25の他の端子は、第1のインバータ24の出力に接続されている。したがって、nチャネルトランジスタ22のチャネルは、電流源25と直列である。代わりとして、電流源25が接地基準に接続され、nチャネルトランジスタ22のドレインが片側パルスフィルタの中間点に接続されてもよい。電流源25は、データ入力信号がHighであるとき、コンデンサ27を放電する。

20

#### 【0031】

[0035]パルスの短縮の量(立ち上がり遷移に関する遅延)は、電流源25の電流およびコンデンサ27のキャパシタンスによって制御される。立ち上がり遷移に関する遅延は、電流源25の電流とコンデンサ27のキャパシタンスの積に基づく。電流源25およびコンデンサ27のうちの一方または両方は可変なものであり、その結果パルス短縮の量は、較正のために、および異なるギアのために調整ができる。較正は、デジタル値を調整することを含むことができる。例えば、電流源25は、電流モードデジタルアナログ変換器を含むことができる。代わりとしてまたは加えて、コンデンサ27は、例えば、片側パルスフィルタの中間点に切り替え可能に接続される複数のコンデンサを含むことができる。

30

#### 【0032】

[0036]遅延調整の範囲は、それとともにPWMデコーダが使用されることになるデータレートの範囲に基づいて選ばれうる。例えば、PWMデコーダがM-PHYのギア6で使用されることになる場合、遅延調整の範囲は3の係数(a factor of 3)よりも大きいことができる。ギア6に関するデータレートの範囲は、3の係数にわたる。片側パルスフィルタの調整範囲は、例えば、プロセス、電圧、および温度の変化を含むように3の係数よりも大きいことができる。別の例では、PWMデコーダがM-PHYのギア6および7で使用されることになる場合、一日の遅延調整(the day delay adjustments)の範囲は、6の係数(これは、ギア6における最小データレートとギア7における最大データレートの比である)よりも大きいことができる。

40

50

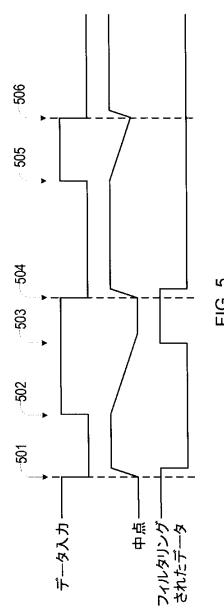

## 【0033】

[0037]図5は、図4の片側パルスフィルタの動作を例示する波形図である。図5は、時間501から時間504までのデータONEビット時間、および時間504から時間506までのデータZEROビット時間を例示している。

## 【0034】

[0038]データONEビット時間では、時間501で、データ入力信号が立ち下がる。このことは、pチャネルトランジスタ21をオンにし、中間点をHighに引っ張る(pull)。中間点上のHighレベルは、第2のインバータ29がフィルタリングされたデータ信号をLowに切り替えて駆動することを引き起こす。データ入力信号の立ち下がりからフィルタリングされたデータ信号の立ち下がりまでの遅延時間は、立ち下がり遷移に関する片側パルスフィルタの遅延である。この遅延は、pチャネルトランジスタ21がコンデンサを迅速に充電することができるとときに短くなる。10

## 【0035】

[0039]時間502で、データ入力信号は立ち上がる。このことは、pチャネルトランジスタ21をオフにし、nチャネルトランジスタ22をオンにし、これは、電流源25がコンデンサ27を放電することを可能にする。中間点上の電圧は、電流源25およびコンデンサ27によって決定されたレートで下降することになる。時間503で、中間点は、第2のインバータ28が切り替わることを引き起こすレベルに下がる。したがって、時間503で、フィルタリングされたデータ信号はHighに切り替わる。時間502から時間503までの遅延は、立ち上がり遷移に関する片側パルスフィルタの遅延である。フィルタリングされたデータ信号は、データONEビット時間の終わりを通り越してもHighのままである。20

## 【0036】

[0040]データZEROビット時間では、時間504で、データ入力信号が立ち下がる。時間501に関して説明されたように、このことは、フィルタリングされたデータ信号が立ち下がることを引き起こす。時間505で、データ入力信号は立ち上がる。このことは、pチャネルトランジスタ21をオフにし、nチャネルトランジスタ22をオンにし、これは、電流源25がコンデンサ27を放電することを可能にする。中間点上の電圧は、電流源25およびコンデンサ27によって決定されたレートで下降することになる。時間506で、データ入力信号は立ち下がる。この時中間点は、第2のインバータ29が切り替わることを引き起こすのに十分なほど下降していない。したがって時間503で、フィルタリングされたデータ信号は、データZEROビット時間の終わりを通り越してもLowのままである。30

## 【0037】

[0041]上記のシステムおよび方法は、M-PHY通信リンクで使用される信号の定義に関して説明された。他の通信リンクでは、他の信号極性およびビット値の定義が使用される。一般に、ビット時間の始まりにおける遷移(図1における立ち下がり)は、リーディング(leading)エッジと称され得、ビット時間の終わりにおける遷移(図1における立ち下がり)は、トレイリングエッジと称されうる。同様に、ビット時間の始まりにおけるパルス(図1におけるLow)は、リーディングパルスと称され得、ビット時間の終わりにおけるパルス(図1におけるHigh)は、トレイリングパルスと称されうる。加えて、ビット時間内のパルスは、例えば狭い、広い、短い、または長い、といった用語を使用して、それらの持続時間によって言及されうる。40

## 【0038】

[0042]図2のデコーダにおけるバリエーションが、他の信号極性およびビット値の定義で機能しうる。例えば、片側パルスフィルタ20は、それが受信するトレイリングパルスの持続時間を短縮(または切断)するように構成されうる。片側パルスフィルタ20は、短いトレイリングパルスを抑制し、(より短い持続時間にも関わらず)長いトレイリングパルスをパスする(pass)。同様に、フリップフロップ45は、データ入力信号のトレイリングエッジでフィルタリングされたデータ信号をラッチするように構成されうる。50

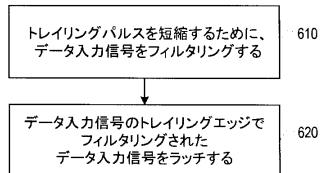

**【 0 0 3 9 】**

[0043]図6は、本明細書で開示される実施形態に係るパルス幅変調されたデータを復号するためのプロセスのフローチャートである。プロセスは、例えば、図2のPWMデコーダを使用して実装されうる。

**【 0 0 4 0 】**

[0044]ステップ610において、プロセスは、トレイリングパルスを短縮するためにデータ入力信号をフィルタリングする。フィルタリングは、データ入力信号上の短いトレイリングパルスを抑制するが、データ入力信号上の長いトレイリングパルスを抑制しない。抑制するパルスの持続時間は、較正によって決定されうる。例えば、図2のデコーダの片側パルスフィルタ20は、データ入力信号をフィルタリングするために使用されうる。

10

**【 0 0 4 1 】**

[0045]ステップ620において、プロセスは、データ入力信号のトレイリングエッジで(ステップ610からの)フィルタリングされたデータ入力信号をラッチする。例えば、図2のデコーダのフィリップフロップ45は、データ入力信号の立ち下がりエッジで片側パルスフィルタ20の出力をラッチすることができる。プロセスはまた、データ入力信号からクロック出力信号を生成することと、フィルタされたデータ入力信号をラッチすることをトリガるためにクロック出力信号を使用することと、を含むことができる。

**【 0 0 4 2 】**

[0046]図6のプロセスは、例えば、ステップを追加または変更することによって修正されうる。加えて、ステップは同時に実行されうる。

20

**【 0 0 4 3 】**

[0047]特定の実施形態が上で説明されているけれども、例えば、異なる信号極性およびデータビットの定義を有するものを含む多くのバリエーションが可能である。さらに、1つのモジュールによって実行されるように説明されている機能は、別のモジュールに移行されうるか、またはモジュール間に分配されうる。加えて、様々な実施形態の特徴が上で説明されたものとは異なる組み合わせで組み合されうる。

**【 0 0 4 4 】**

[0048]開示された実施形態の上記説明は、いかなる当業者も、本発明を製造または使用できるように提供されている。これらの実施形態に対する様々な修正は当業者に容易に明らかになり、本明細書で説明されている包括的な本質は本開示の範囲もしくは趣旨から逸脱することなく他の実施形態に適用されうる。したがって、本明細書で提示されている説明および図面は、本願発明の目下好まれている実施形態を表しており、したがって、本願発明によって広く考慮される主題の代表的なものであることは理解されるものとする。さらに、本願発明の範囲は、当業者には明白になりうる他の実施形態を十分に包含すること、およびそれに応じて本願発明の範囲が添付の請求項以外の何によっても限定されないことは理解される。

30

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

**[ C 1 ]**

データ入力信号からのパルス幅変調されたデータを復号するためのデコーダであって、前記データ入力信号は、ビットのシリアルストリームを含み、前記シリアルストリームの各ビットは、ビット時間にわたり、前記シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするHig hパルスを有し、前記デコーダは、前記データ入力信号上のHig hパルスの持続時間を短縮することによって、フィルタリングされたデータ信号を生成するように構成された片側パルスフィルタと、前記データ入力信号の各ビット時間の終わりに、前記フィルタリングされたデータ信号をラッチするように構成されたフリップフロップと、を備える、デコーダ。

40

**[ C 2 ]**

前記片側パルスフィルタは、前記データ入力信号上の短いHig hパルスを抑制するように構成される、C1に記載のデコーダ。

50

[ C 3 ]

前記片側パルスフィルタは、前記データ入力信号上の長いH i g h パルスを抑制しないように構成される、C 2に記載のデコーダ。

[ C 4 ]

前記片側パルスフィルタは、立ち下がり遷移に関する入出力遅延よりも大きい立ち上がり遷移に関する入出力遅延を有する、C 1に記載のデコーダ。

[ C 5 ]

前記片側パルスフィルタの立ち上がり遷移に関する前記入出力遅延が較正される、C 4に記載のデコーダ。

[ C 6 ]

前記較正是、3の係数よりも大きい遅延の範囲を含む、C 5に記載のデコーダ。

10

[ C 7 ]

前記片側パルスフィルタの立ち上がり遷移に関する前記入出力遅延は、前記データ入力信号の同期状態中に較正される、C 5に記載のデコーダ。

[ C 8 ]

前記較正是、デジタルで制御される、C 5に記載のデコーダ。

[ C 9 ]

前記片側パルスフィルタは、

コンデンサと、

前記データ入力信号に基づいて前記コンデンサを放電するように構成された電流源と、

を含み、

20

立ち上がり遷移に関する前記片側パルスフィルタの入出力遅延は、前記コンデンサのキャパシタンスと前記電流源の電流の積に基づく、

C 1に記載のデコーダ。

[ C 10 ]

前記電流源は、電流モードデジタルアナログ変換器を含む、C 9に記載のデコーダ。

[ C 11 ]

前記データ入力信号を受信し、前記フィルタリングされたデータ信号をラッチするよう構成された前記フリップフロップをトリガするためのクロック出力信号を生成するよう構成されたクロック生成器モジュールをさらに備える、C 1に記載のデコーダ。

30

[ C 12 ]

前記クロック生成器モジュールは、前記データ入力信号に結合された入力、および前記クロック出力信号に結合された出力を有するインバータを含み、前記フリップフロップは、前記クロック出力信号の立ち上がりエッジで前記フィルタリングされたデータ信号をラッチする、C 11に記載のデコーダ。

[ C 13 ]

データ入力信号からのパルス幅変調されたデータを復号するための方法であって、前記データ入力信号は、ビットのシリアルストリームを含み、前記シリアルストリームの各ビットは、ビット時間にわたり、前記シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリングパルスを有し、前記方法は、

40

前記トレイリングパルスを短縮するために前記データ入力信号をフィルタリングすることと、

前記データ入力信号のトレイリングエッジで前記フィルタリングされたデータ入力をラッチすることと、

を備える、方法。

[ C 14 ]

前記データ入力信号をフィルタリングすることは、前記データ入力信号上の短いトレイリングパルスを抑制することを含む、C 13に記載の方法。

[ C 15 ]

前記データ入力信号をフィルタリングすることは、前記データ入力信号上の長いH i g

50

h トレイリングを抑制しないことを含む、C 1 4 に記載の方法。

[ C 1 6 ]

抑制されるトレイリングパルスの持続時間を較正することをさらに備える、C 1 4 に記載の方法。

[ C 1 7 ]

前記較正は、前記データ入力信号の同期状態中に実行される、C 1 6 に記載の方法。

[ C 1 8 ]

前記較正は、デジタルで制御される、C 1 6 に記載の方法。

[ C 1 9 ]

前記フィルタリングされたデータ入力信号をラッチすることに使用するために、前記データ入力信号に基づいてクロック出力信号を生成することをさらに備える、C 1 3 に記載の方法。

10

[ C 2 0 ]

データ入力信号からのパルス幅変調されたデータを復号するための装置であって、前記データ入力信号は、ビットのシリアルストリームを含み、前記シリアルストリームの各ビットは、ビット時間にわたり、前記シリアルストリームの各ビットは、その持続時間がそれぞれのビットの値をシグナリングするトレイリングパルスを有し、前記装置は、

トレイリングパルスを短縮するために前記データ入力信号をフィルタリングするための手段と、

前記データ入力信号のトレイリングエッジで前記フィルタリングされたデータ入力をラッチするための手段と、

20

を備える、装置。

[ C 2 1 ]

前記データ入力信号をフィルタリングするための手段は、前記データ入力信号上の短いトレイリングパルスを抑制する、C 2 0 に記載の装置。

[ C 2 2 ]

前記データ入力信号をフィルタリングするための手段は、前記データ入力信号上の長いトレイリングパルスを抑制しない、C 2 1 に記載の装置。

[ C 2 3 ]

抑制されるトレイリングパルスの持続時間が較正される、C 2 1 に記載の装置。

30

[ C 2 4 ]

前記較正は、3 の係数よりも大きい遅延の範囲を含む、C 2 3 に記載の装置。

[ C 2 5 ]

前記較正は、デジタルで制御される、C 2 3 に記載の装置。

[ C 2 6 ]

前記データ入力信号を受信し、前記ラッチするための手段が前記フィルタリングされたデータ信号をラッチするようにトリガするためのクロック出力信号を生成するように構成されたクロック生成器モジュールをさらに備える、C 2 0 に記載の装置。

[ C 2 7 ]

前記クロック生成器モジュールは、前記データ入力信号に結合された入力、および前記クロック出力信号に結合された出力を有するインバータを備え、前記ラッチするための手段は、前記クロック出力信号のトレイリングエッジで前記フィルタリングされたデータ信号をラッチする、C 2 6 に記載の装置。

40

【図1】

図1

FIG. 1

【図3】

図3

FIG. 3

【図2】

図2

FIG. 2

【図4】

図4

FIG. 4

【図5】

図5

FIG. 5

## 【図6】

図6

FIG. 6

---

フロントページの続き

(72)発明者 ジュ、ジー

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 コン、シャオファ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 スン、リ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 シュ、ジー

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 阿部 弘

(56)参考文献 特表2011-503995(JP,A)

特開2010-283628(JP,A)

国際公開第2013/048395(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H04L 25/49

H03M 5/08