(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4533155号

(P4533155)

(45) 発行日 平成22年9月1日(2010.9.1)

(24) 登録日 平成22年6月18日(2010.6.18)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| H01L 21/8238 | (2006.01) |

| H01L 27/092  | (2006.01) |

| H01L 21/28   | (2006.01) |

| H01L 29/423  | (2006.01) |

| H01L 29/49   | (2006.01) |

|            |      |

|------------|------|

| H01L 27/08 | 321D |

| H01L 21/28 | 301R |

| H01L 29/58 | G    |

請求項の数 6 (全 11 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-5506 (P2005-5506)      |

| (22) 出願日  | 平成17年1月12日 (2005.1.12)        |

| (65) 公開番号 | 特開2006-196610 (P2006-196610A) |

| (43) 公開日  | 平成18年7月27日 (2006.7.27)        |

| 審査請求日     | 平成19年12月25日 (2007.12.25)      |

|           |                                                           |

|-----------|-----------------------------------------------------------|

| (73) 特許権者 | 308014341<br>富士通セミコンダクター株式会社<br>神奈川県横浜市港北区新横浜二丁目10番<br>23 |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                    |

| (72) 発明者  | 肖 石琴<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内                |

| (72) 発明者  | 池田 和人<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内               |

審査官 宇多川 勉

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2の素子分離領域を含む基板に第2の金属材料を含む絶縁膜を成膜し、前記絶縁膜上に第1の金属材料の層を成膜し、前記第1の金属材料の層上に前記第2の金属材料の層を成膜し、前記第1の素子分離領域上の前記第2の金属材料の層の厚さが、前記第2の素子分離領域上の前記第2の金属材料の層の厚さよりも薄く残るように、前記第1の素子分離領域上の前記第2の金属材料の層の上部を除去し、

熱処理を行って、前記第1及び前記第2の金属材料を合金化し、

前記第1及び第2の素子分離領域上の構造が電気的に分離されるように、合金化された層及び前記絶縁膜をエッティングする

ことを特徴とする相補型の半導体装置を製造する製造方法。

## 【請求項 2】

前記第1及び前記第2の金属材料を合金化する熱処理の前又は後に、導電層が、前記第1及び第2の素子分離領域上に成膜される

ことを特徴とする請求項1記載の製造方法。

## 【請求項 3】

前記第1及び前記第2の金属材料を合金化する熱処理が行われる前に、ポリシリコンにより成る導電層が、前記第1及び第2の素子分離領域上に成膜される

ことを特徴とする請求項2記載の製造方法。

10

20

**【請求項 4】**

前記第1及び前記第2の金属材料を合金化する熱処理が行われた後に、タンゲステンより成る導電層が、前記第1及び第2の素子分離領域上に成膜されることを特徴とする請求項2記載の製造方法。

**【請求項 5】**

第1導電型及び第2導電型の電界効果トランジスタより成る相補型の半導体装置であつて、

前記第1導電型のトランジスタは、第1の金属材料及び第2の金属材料を含み、前記第1の金属材料に対する前記第2の金属材料の割合が第1の割合である第1材料層を含む第1ゲート電極を有し、

前記第2導電型のトランジスタは、前記第1の金属材料及び前記第2の金属材料を含み、前記第1の金属材料に対する前記第2の金属材料の割合が前記第1の割合よりも小さい第2の割合である第2材料層を含む第2ゲート電極を有し、

前記第1材料層の膜厚は前記第2材料層の膜厚よりも薄く、前記第1ゲート電極及び前記第2ゲート電極に対応するゲート酸化膜は前記第1の金属材料を含むことを特徴とする相補型の半導体装置。

**【請求項 6】**

第1及び第2の素子領域を含む基板に絶縁膜を成膜し、

前記絶縁膜上に第1の金属材料の層を成膜し、

前記第1の金属材料の層上に第2の金属材料の層を成膜し、

前記第1の素子領域上の前記第2の金属材料の層の少なくとも一部を除去し、

ポリシリコンより成る導電層を、前記第1の金属材料の層及び前記第2の金属材料の層上に成膜し、

熱処理を行って、前記第1及び前記第2の金属材料を合金化し、

前記第1及び第2の素子領域上の構造が電気的に分離されるように、前記導電層、合金化された層及び前記絶縁膜をエッチングする

ことを特徴とする相補型の半導体装置を製造する方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及びその製造方法に関する。

**【背景技術】****【0002】**

この種の技術分野では、半導体装置の微細化に伴って、それを構成する電界効果トランジスタも益々微細化されつつある。一方、一定値以上の静電容量を確保するために、ゲート絶縁膜の薄化も進んでいる。しかしながら、ゲート絶縁膜が薄化すると、ホウ素のような不純物の突き抜けや、絶縁膜からゲート電極への酸素の拡散等の好ましくない現象が起これりやすくなる。そこで、ハフニウム(Hf)を含む材料層のような高誘電率を有するゲート絶縁膜が使用されることも間々ある。誘電率の高い材料を使用することで、一定値以上の容量を確保しつつ、ゲート絶縁膜の厚みを過剰に薄化することを抑制するためである。

**【0003】**

しかしながら、そのような高誘電率の材料をゲート絶縁膜に使用すると、シリコンとハフニウムの結合(Si-Hf)のような不要な結合がゲート絶縁膜界面に生じ、望まれないエネルギー準位が形成され、デバイス特性に悪影響を及ぼすことが懸念される。例えば、悪影響の1つには、Vfbシフトと呼ばれる閾値のズレがある。このような不都合に対処するため、ゲート電極にポリシリコンを使用する代わりに、ゲート電極を金属にする試みがなされている。特許文献1,2に関連事項が記載されている。

**【0004】**

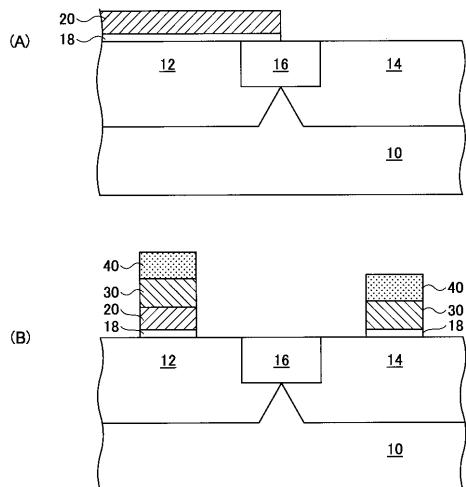

図1は、そのような半導体装置を製造する工程の一部を示す。図1(A)に示される工

10

20

30

40

50

程では、半導体基板 10 上に第 1 及び第 2 の素子分離領域 12, 14 及び絶縁体 16 が形成される。その構造上に、第 1 のゲート絶縁膜 18 が全面に成膜され、その上にタンゲステン窒化膜 20 が成膜され、第 2 の素子分離領域 12 上の絶縁膜 18 及びタンゲステン窒化膜 20 は除去される。図 1 (A) に示される構造に対して熱酸化が行われ、第 2 の素子分離領域 14 に熱酸化膜 28 が成膜され、全面にモリブデン (Mo) より成る導電層 30 及びタンゲステン (W) より成る導電層 40 が成膜される。その後、第 1 及び第 2 の素子分離領域 12, 14 に形成された層構造が電気的に分離され (エッチングされ)、図 1 (B) に示されるような構造が形成される。以後、当該技術分野で周知のプロセスが行われることで、相補型の半導体装置が形成される。

【特許文献 1】特開 2002-359295 号公報

10

【特許文献 2】特開 2003-273350 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0005】

しかしながら、そのような特許文献 1 記載発明による手法では、P 型のトランジスタと N 型のトランジスタを別々に作成しており、製造工程数が多い点で好ましくない。また、熱酸化により第 2 のゲート絶縁膜 28 を成膜する際に、タンゲステン窒化膜 20 も酸化されるので、デバイス特性に悪影響を与えることが懸念される。或いは、そのような不都合を回避するために、熱酸化の際にタンゲステン窒化膜 20 を保護膜で被覆して保護することも考えられるが、製造工程数が増えてしまう。一方、ゲート電極に金属を使用する際には、ゲート電極の仕事関数を適切に調整する必要がある。この点に関し、特許文献 2 記載発明では、ゲート電極を構成する金属に、酸素 (O) 又はフッ素 (F) をイオン注入により添加することで、仕事関数の調整を行おうとしている。しかしながら、O や F を添加するとゲート電極の抵抗値が上昇してしまうので、仕事関数の制御は容易ではない。しかも、イオン注入時のビームのエネルギー分布を考慮する必要があるので、仕事関数の制御は非常に困難になることが懸念される。

20

##### 【0006】

本発明は、上記の問題に鑑みてなされたものであり、その課題は、高誘電率のゲート絶縁膜を有する相補型電界効果トランジスタより成り、閾値変動 (V<sub>f b</sub> シフト) を小さく抑制することの可能な半導体装置を提供すること及びそのような半導体装置を簡易に作成する製造方法を提供することである。

30

##### 【課題を解決するための手段】

##### 【0007】

開示される発明の一形態による製造方法は、

第 1 及び第 2 の素子分離領域を含む基板に第 2 の金属材料を含む絶縁膜を成膜し、

前記絶縁膜上に第 1 の金属材料の層を成膜し、

前記第 1 の金属材料の層上に前記第 2 の金属材料の層を成膜し、

前記第 1 の素子分離領域上の前記第 2 の金属材料の層の厚さが、前記第 2 の素子分離領域上の前記第 2 の金属材料の層の厚さよりも薄く残るように、前記第 1 の素子分離領域上の前記第 2 の金属材料の層の上部を除去し、

40

熱処理を行って、前記第 1 及び前記第 2 の金属材料を合金化し、

前記第 1 及び第 2 の素子分離領域上の構造が電気的に分離されるように、合金化された層及び前記絶縁膜をエッチングする

ことを特徴とする相補型の半導体装置を製造する製造方法である。

##### 【発明の効果】

##### 【0008】

本発明によれば、高誘電率のゲート絶縁膜を有する相補型電界効果トランジスタにおける閾値変動 (V<sub>f b</sub> シフト) を小さく抑制することができる。

##### 【発明を実施するための最良の形態】

##### 【0009】

50

本発明の一態様では、第1及び第2の素子分離領域を含む基板に絶縁膜が成膜され、前記絶縁膜上に第1の金属材料の層が成膜され、前記第1の導電性材料の層上に第2の金属材料の層が成膜され、前記第1の素子分離領域上の前記第2の金属材料の層の少なくとも一部が除去され、前記第1及び第2の素子分離領域上の構造が電気的に分離されるように、エッティングが行われ、熱処理が行われ、前記第1及び前記第2の金属材料が合金化される。

#### 【0010】

ポリシリコンの代わりに金属材料より成るゲート電極が形成されるので、ゲート絶縁膜との界面にて、Hf-Siのような望まれない結合は形成されなくなり、不都合な閾値変動は効果的に抑制される。また、ゲートの空乏化も抑制されるので、装置の高速動作を図ることもできる。相補的に動作する素子構造が、第1及び第2の素子分離領域に同時に形成されるので、相補型の半導体装置を簡易に作成することができる。金属材料に不純物を導入することに加えて、合金化される金属材料より成る層の膜厚を調整することで、ゲート電極が適切な物性（例えば、仕事関数値）を備えるように簡易に調整できる。

10

#### 【0011】

本発明の一態様では、前記第1及び前記第2の金属材料を合金化する熱処理が行われる前に、ポリシリコンより成る導電層が、前記第1及び第2の素子分離領域上に成膜される。これにより、導電層の活性化と合金化を同時に行うことができる。

#### 【0012】

本発明の一態様では、前記第1及び前記第2の金属材料を合金化する熱処理が行われた後に、タンゲステンより成る導電層が、前記第1及び第2の素子分離領域上に成膜される。ポリシリコンの活性化のような高温プロセス（一般に、合金化より高温のプロセスである。）を使用しなくて済むので、製造されるデバイスの更なる高品質化を図ることができる。

20

#### 【実施例1】

#### 【0013】

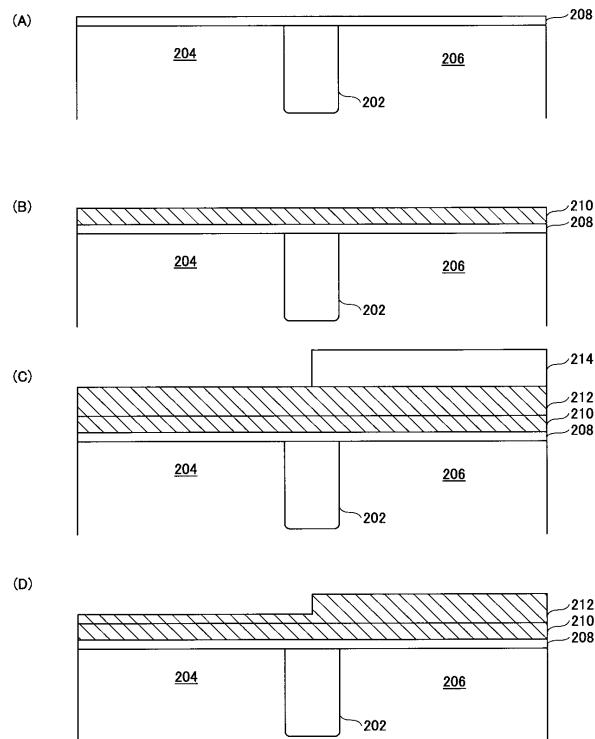

図2,3は、本発明の一実施例による半導体装置の製造工程（その1,2）を示す。図1(A)に示される工程では、絶縁体202により互いに電気的に分離された第1及び第2の素子分離領域204,206が、シリコン(Si)より成る半導体基板に形成される。簡単のため、素子分離領域の下地は描かれていない。第1及び第2の素子分離領域204,206内で素子を形成する領域が、P型又はN型の所定の導電性を備えるように、ウエルが形成される。ホウ素(B)や燐(P)のような所定の不純物を対象とする領域にイオン注入することによって、ウエルが形成される。第1及び第2の素子分離領域204,206の双方には、ゲート絶縁膜208が例えば4nmのような薄い膜厚で成膜される。膜厚の具体的な数値は单なる一例であり、他の数値が使用されてもよい。本実施例におけるゲート絶縁膜208は、ハフニウム(Hf)を含む高誘電率を有する材料より成り、例えば酸化ハフニウム(HfO<sub>2</sub>)である。しかしながら、本発明はこのような材料に限定されず、様々な材料が使用されてもよい。例えば、SiO<sub>2</sub>,SiON又はSiNであるシリコンより成る材料が使用されてもよい。HfO<sub>2</sub>,HfSiO<sub>x</sub>又はHfSiON<sub>x</sub>であるハフニウムを含む絶縁材料が使用されてもよい。Al<sub>2</sub>O<sub>3</sub>,HfAlO<sub>x</sub>又はHfAlON<sub>x</sub>であるアルミニウム含む材料が使用されてもよい。Zrを含む絶縁材料が使用されてもよい。Ta<sub>2</sub>O<sub>5</sub>より成る材料が使用されてもよい。更には、希土類金属を含む酸化絶縁膜が使用されてもよい。

30

40

#### 【0014】

図2(B)に示される工程では、ルテニウム(Ru)より成る第1の導電層210が、30nmの膜厚で全面に成膜される。この工程は、スパッタリング、化学蒸着体積(CVD)法その他の周知の成膜技術を用いて行われてもよい。本実施例では第1の導電層はRuより成るが、他の材料が使用されてもよい。例えば、白金(Plt)、酸化ルテニウム(RuO<sub>2</sub>)若しくはそれらの合金又はそれらの窒化物が使用されてもよい。膜厚は、上記の数値に限定されないが、導電層がバルクとしての性質を備え、適切な仕事関数の値を有

50

する程度に厚く形成される必要がある。第1の導電層210を構成する材料は、P型の電界効果トランジスタのゲート電極に多く含まれることになるので、その仕事関数が実質的に5.0eV（例えば、5.2電子ボルトでもよい）であるように材料が選択又は調整される。この場合における仕事関数は、真空中に孤立して存在する電子のポテンシャルエネルギー（真空準位）を基準にしている。

#### 【0015】

図2(C)に示される工程では、第1の導電層210上の全面に、第2の導電層212がスパッタリング等により例えば100nmの膜厚で成膜される。本実施例では、第2の導電層はHfより成るが、他の材料が使用されてもよい。例えば、ジルコニウム(Zr)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、チタニウム(Ti)、アルミニウム(Al)、バナジウム(V)、コバルト(Co)、ニオブ(Nb)、タンゲステン(W)若しくはそれらの合金又はそれらの窒化物が使用されてもよい。第1の導電層212を構成する材料は、N型の電界効果トランジスタのゲート電極に多く含まれることになるので、その仕事関数が実質的に4.0eV（例えば、4.2電子ボルトでもよい）であるように材料が選択又は調整される。第1及び第2の導電層210, 212を成膜する工程は、同一反応炉内で連続的に行ってもよいし、異なる反応炉で別々に行ってもよい。仕事関数の調整を正確に行う観点からは、同一反応炉内で（大気にさらすことなしに）連続的に行なうことが望ましい、即ちインサイト(Insitu)プロセスであることが望ましい。

#### 【0016】

次に、レジスト214が全面に成膜され、フォトリソグラフィ法のような技術を用いて、レジスト214が所定の形状に規定される。これにより、第1の素子分離領域204上のレジストが除去され、第2の素子分離領域206上のレジストが残される。

#### 【0017】

図2(D)に示される工程では、第1の素子分離領域204上の第2の導電層212がエッチングされ、その後にレジストが除去される。エッチングは、当該技術分野で周知の様々な技法を用いて行なうことができ、本実施例では、アルゴン(Ar)及び塩素(Cl)を含むガスを用いたドライエッチングが行われる。Arガスを用いるのは、エッチングの異方性を強化するためである。このエッチングでは、露出している第2の導電層212の全てを除去してもよいが、本実施例では10nm程度の膜厚を残している。これは、第1及び第2の導電層が合金化された後に、合金とゲート絶縁膜208との密着性を向上させるためである（合金化の工程については次に説明される。）。

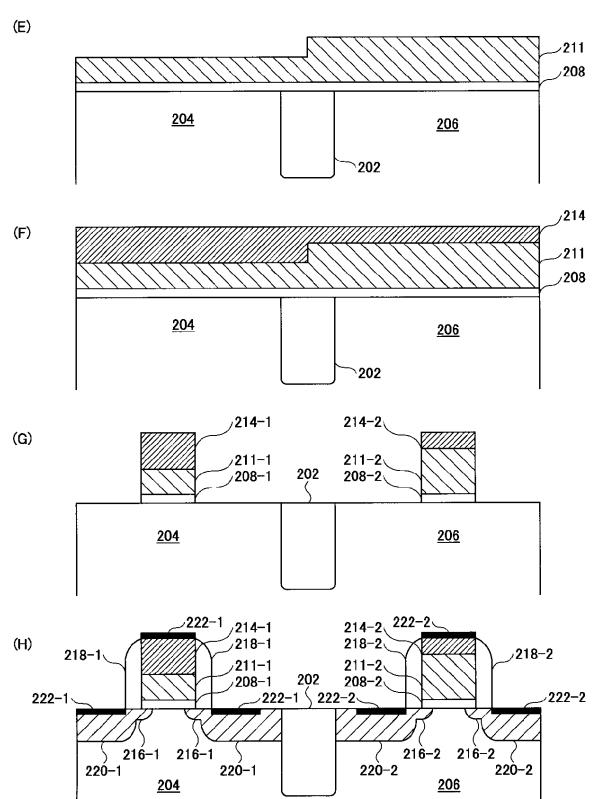

#### 【0018】

図3(E)に示される工程では、500～800程度の温度で熱処理が行われ、第1及び第2の導電層210, 212が合金化され、導電層211が形成される。第1の素子分離領域204における第1及び第2の導電層210, 212の膜厚の比率は、30nm/10nm(Ru/Hf)であるので、この領域はRuリッチな（ルテニウムに富んだ）領域になる。この合金化により、この領域の導電層211は、P型の電界効果トランジスタのゲート電極に相応しい特性（例えば、仕事関数が5.0eV程度であること）を備えることができる。しかも、導電層211は、Hfを含んでいるので、下地のゲート絶縁膜208との間で良好な密着性を得ることができる。

#### 【0019】

また、第2の素子分離領域206における第1及び第2の導電層210, 212の膜厚の比率は、100nm/30nm(Ru/Hf)であるので、この領域はHfリッチな（ハフニウムに富んだ）領域になる。この合金化により、この領域の導電層211は、N型の電界効果トランジスタのゲート電極に相応しい特性（例えば、仕事関数が4.0eV程度であること）を備えることができる。

#### 【0020】

図3(F)に示される工程では、合金化された導電層211上に、第3の導電層214が例えば200nmの膜厚で成膜される。第3の導電層214は、ポリシリコン(Pol)

10

20

30

40

50

y - Si) やタンゲステン (W) のような導電性の材料で構成できるが、本実施例では、Wで構成されている。後述の実施例2では、第3の導電層214がポリシリコンで構成される。第3の導電層214は、下地の合金化された導電層211の段差に対応する段差が形成されるが、この段差は平坦化される。平坦化は、当該技術分野で周知の様々な手法で行うことができ、本実施例では、化学機械研磨 (CMP) で行われている。この平坦化の工程により、第3の導電層214は、第1の素子分離領域上204で110nm程度の膜厚を有し、第2の素子分離領域206で20nm程度の膜厚を有し、双方の領域で実質的に等しい高さに揃えられる。

#### 【0021】

図3 (G) に示される工程では、第1及び第2の素子分離領域204, 206に形成される素子の形状に合わせてパターニングが行われる。パターニングは、例えばフォトリソグラフィ法を用いて行うことができる。例えば、平坦化された第3の導電層214 (図3 (F)) にレジストを塗布し、その一部を除去し、レジストで保護されていない領域をエッチングすることによって行うことができる。パターニングは、第1及び第2の素子分離領域204, 206に対して、別々に行われてもよいし、同時に行われてもよい。

#### 【0022】

図3 (H) に示されるように、相補型の電界効果トランジスタ (例えば、CMOSトランジスタ) が、周知の半導体製造プロセスを用いて形成される。例えば、図3 (G) の工程に続いて、LDD (lightly doped drain) 構造216-1, 2が形成され、多層ゲート電極構造の各々に側壁218-1, 2がそれぞれ形成され、ソース及びドレイン領域220-1, 2が形成され、露出している導電性の領域にニッケル (Ni) を含むシリサイド222-1, 2が形成され、図示の構造が形成される。

#### 【実施例2】

#### 【0023】

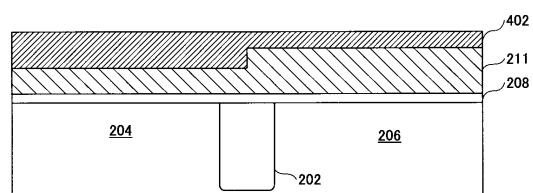

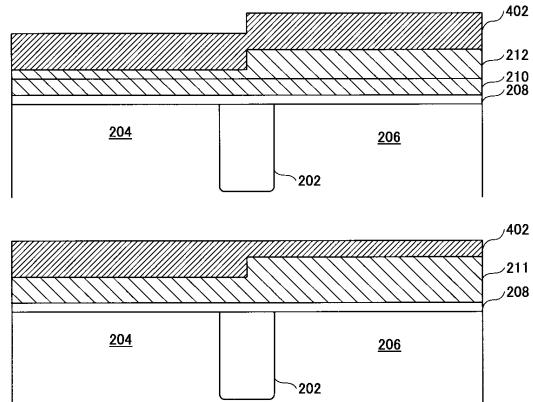

図4は、本発明の一実施例による半導体装置の製造工程の一部を示す。図2 (A) ~ (D) に示される工程に続いて、図4 (E), (F) に示される工程が行われる。本実施例では、図4 (E) に示されるように、第1及び第2の導電層210, 212が合金化される前に、ポリシリコン (Poly-Si) より成る第3の導電層402が、第2の導電層212上にCVD法等によって成膜される。第1及び第2の素子分離領域に形成される素子に合わせて、ホウ素 (B) やリン (P) 等の不純物がポリシリコンより成る第3の導電層214に注入される。その後、1000°C程度の高温の熱処理が行われ、第3の導電層214が活性化される。この熱処理により、第1及び第2の導電層210, 212の合金化を兼ねるようにすることができる。或いは、プロセス条件を変更して、第3の導電層214の活性化のための工程と、第1及び第2の導電層の合金化のための工程とを行ってもよい。

#### 【0024】

図4 (F) に示される工程では、合金化された導電層211上の第3の導電層402が、例えばCMPを用いて平坦化される。以後、図3 (F) 以降で説明済みの工程と同様な工程が行われる。

#### 【実施例3】

#### 【0025】

上記の実施例では、第1の導電層210はP型トランジスタのゲート電極の仕事関数に合わせて材料 (例えば、Ru) が選択され、第2の導電層212はN型トランジスタのゲート電極の仕事関数に合わせて材料 (例えば、Hf) が選択されていた。しかしながら、本発明はこのような態様に限定されない。N型トランジスタのゲート電極の仕事関数に合わせて第1の導電層210の材料が選択され、P型トランジスタのゲート電極の仕事関数に合わせて第2の導電層212の材料が選択されてもよい。

#### 【0026】

第1の導電層210がHfより成り、第2の導電層212がRuより成る場合には、図2 (D) に示される工程で、第1の素子分離領域204上の第2の導電層212を僅かに

10

20

30

40

50

残す必要はない。本実施例におけるその領域では、Hfが支配的になるので、ゲート絶縁層208との密着性は良好になるからである。

【0027】

以下、本発明により教示される手段を例示的に列挙する。

【0028】

(付記1)

P型及びN型の電界効果トランジスタより成る相補型の半導体装置であって、

前記P型のトランジスタは、第1の仕事関数値を有し、第1の金属材料に富んだ第1材料層より成る第1ゲート電極を有し、

前記N型のトランジスタは、第2の仕事関数値を有し、第2の金属材料に富んだ第2材料層より成る第2ゲート電極を有し、10

前記第1及び第2材料層は異なる膜厚を有する

ことを特徴とする相補型の半導体装置。

【0029】

(付記2)

前記第1又は第2の金属材料が、白金(Pt)、ルテニウム(Ru)、酸化ルテニウム(RuO<sub>2</sub>)若しくはそれらの合金又はそれらの窒化物より成る

ことを特徴とする付記1記載の半導体装置。

【0030】

(付記3)

前記第1又は第2の金属材料が、ハフニウム(Hf)、ジルコニウム(Zr)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、チタニウム(Ti)、アルミニウム(Al)、バナジウム(V)、コバルト(Co)、ニオブ(Nb)、タンクス滕(W)若しくはそれらの合金又はそれらの窒化物より成る

ことを特徴とする付記1記載の半導体装置。20

【0031】

(付記4)

前記P型及びN型のトランジスタのゲート絶縁膜が、SiO<sub>2</sub>、SiON又はSiNであるシリコンより成る材料、HfO<sub>2</sub>、HfSiO<sub>x</sub>又はHfSiON<sub>x</sub>であるハフニウムを含む絶縁材料、Al<sub>2</sub>O<sub>3</sub>、HfAlO<sub>x</sub>又はHfAlON<sub>x</sub>であるアルミニウム含む材料、Zrを含む絶縁材料、Ta<sub>2</sub>O<sub>5</sub>より成る材料又は希土類金属を含む酸化絶縁膜から構成される30

ことを特徴とする付記1記載の半導体装置。

【0032】

(付記5)

前記第1及び第2ゲート電極が、等しい膜厚を有する

ことを特徴とする付記1記載の半導体装置。

【0033】

(付記6)

第1及び第2の素子分離領域を含む基板に絶縁膜を成膜し、40

前記絶縁膜上に第1の金属材料の層を成膜し、

前記第1の導電性材料の層上に第2の金属材料の層を成膜し、

前記第1の素子分離領域上の前記第2の金属材料の層の少なくとも一部を除去し、

前記第1及び第2の素子分離領域上の構造が電気的に分離されるように、エッチングを行い、40

熱処理を行って、前記第1及び前記第2の金属材料を合金化する

ことを特徴とする相補型の半導体装置を製造する製造方法。

【0034】

(付記7)

前記第1又は第2の金属材料が、白金(Pt)、ルテニウム(Ru)、酸化ルテニウム50

(RuO<sub>2</sub>)若しくはそれらの合金又はそれらの窒化物より成ることを特徴とする付記6記載の製造方法。

**【0035】**

(付記8)

前記第1又は第2の金属材料が、ハフニウム(Hf)、ジルコニウム(Zr)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、チタニウム(Ti)、アルミニウム(Al)、バナジウム(V)、コバルト(Co)、ニオブ(Nb)、タンクステン(W)若しくはそれらの合金又はそれらの窒化物より成ることを特徴とする付記6記載の製造方法。

**【0036】**

10

(付記9)

前記絶縁膜が、SiO<sub>2</sub>、SiON又はSiNであるシリコンより成る材料、HfO<sub>2</sub>、HfSiO<sub>x</sub>又はHfSiON<sub>x</sub>であるハフニウムを含む絶縁材料、Al<sub>2</sub>O<sub>3</sub>、HfAlO<sub>x</sub>又はHfAlON<sub>x</sub>であるアルミニウム含む材料、Zrを含む絶縁材料、Ta<sub>2</sub>O<sub>5</sub>より成る材料又は希土類金属を含む酸化絶縁膜から構成されることを特徴とする付記6記載の製造方法。

**【0037】**

(付記10)

前記第1及び前記第2の金属材料を合金化する熱処理の前又は後に、導電層が、前記第1及び第2の素子分離領域上に成膜されることを特徴とする付記6記載の製造方法。

20

**【0038】**

(付記11)

前記第1及び前記第2の金属材料を合金化する熱処理が行われる前に、ポリシリコンより成る導電層が、前記第1及び第2の素子分離領域上に成膜されることを特徴とする付記10記載の製造方法。

**【0039】**

(付記12)

前記第1及び前記第2の金属材料を合金化する熱処理が行われた後に、タンクステンより成る導電層が、前記第1及び第2の素子分離領域上に成膜されることを特徴とする付記10記載の製造方法。

30

**【0040】**

(付記13)

前記第1の金属材料の仕事関数が4.0eVに実質的に等しく、前記第2の金属材料の仕事関数が5.0eVに実質的に等しいことを特徴とする付記6記載の製造方法。

**【図面の簡単な説明】**

**【0041】**

【図1】従来の半導体装置を製造する工程の一部を示す図である。

【図2】本発明の一実施例による半導体装置の製造工程を示す図(その1)である。

40

【図3】本発明の一実施例による半導体装置の製造工程を示す図(その2)である。

【図4】本発明の一実施例による半導体装置の製造工程を示す図である。

**【符号の説明】**

**【0042】**

10 半導体基板； 12, 14 素子分離領域； 16 絶縁体； 18 ゲート絶縁膜； 20 タンクステン窒化膜； 30 モリブデン層； 40 タンクステン層； 202 絶縁体； 204, 206 素子分離領域； 208 ゲート絶縁膜； 210 Ru層； 212 Hf層； 214 レジスト； 211 合金層； 214 タンクステン層； 216, 220 ソース/ドレイン領域； 218 側壁； 222 Niシリサイド；

50

## 402 ポリシリコン層

【図1】

従来の半導体装置を製造する工程の一部を示す図

【図2】

本発明の一実施例による半導体装置の製造工程を示す図(その1)

【図3】

本発明の一実施例による半導体装置の製造工程を示す図(その2)

【図4】

本発明の一実施例による半導体装置の製造工程を示す図

---

フロントページの続き

(56)参考文献 特開2004-228547(JP,A)

特開2002-217313(JP,A)

特表2006-524431(JP,A)

特表2008-510296(JP,A)

特表2006-518547(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8238

H01L 21/28

H01L 27/092

H01L 29/423

H01L 29/49