(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4768039号

(P4768039)

(45) 発行日 平成23年9月7日(2011.9.7)

(24) 登録日 平成23年6月24日(2011.6.24)

(51) Int.Cl.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J    |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 623R |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 623B |

|             |              |                  | G09G | 3/20 | 612E |

|             |              |                  | G09G | 3/20 | 623D |

請求項の数 8 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2009-48655 (P2009-48655)

(22) 出願日

平成21年3月2日(2009.3.2)

(65) 公開番号

特開2010-204312 (P2010-204312A)

(43) 公開日

平成22年9月16日(2010.9.16)

審査請求日

平成22年7月22日(2010.7.22)

早期審査対象出願

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100109210

弁理士 新居 広守

(72) 発明者 小嶋 寛

大阪府門真市大字門真1006番地 パナソニック セミコンダクターシステムテクノ株式会社内

(72) 発明者 小川 宗彦

大阪府門真市大字門真1006番地 パナソニック セミコンダクターシステムテクノ株式会社内

最終頁に続く

(54) 【発明の名称】表示駆動装置および表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画素列毎にソースラインを有する表示パネルを駆動する表示駆動装置であつて、ソースラインに画素信号を駆動するドライバと、前記画素信号の最大電圧と最小電圧の間の電圧である中間電圧を中間電圧線に出力する電源部と、

前記中間電圧線に接続された第3スイッチと、一端は前記第3スイッチに、他端は対応するソースラインに、接続された複数の第1スイッチと、一端は前記ドライバに、他端は対応するソースラインおよび対応する前記第1スイッチの他端に接続された複数の第2スイッチと、

画素信号の出力期間と次の画素信号の出力期間との間の切り替え期間において、第2スイッチを一時的にオフにするとともに、当該第2スイッチに対応する前記第1スイッチを一時的にオンにして、第1スイッチをオンにした後に第3スイッチをオンにする制御部とを有する表示駆動装置。

## 【請求項 2】

前記ドライバ、第1スイッチ、第2スイッチおよび制御部は第1の半導体基板に形成され、前記電源部は第2の半導体基板に形成される請求項1に記載の表示駆動装置。

## 【請求項 3】

前記制御部は、前記切り替え期間において、全ての第2スイッチを一時的にオフにする

10

20

とともに、当該第2スイッチに対応する全ての前記第1スイッチを一時的にオンにする請求項1または2に記載の表示駆動装置。

【請求項4】

前記中間電圧線は、第1のスイッチを介して第1の色に対応するソースラインに接続される第1電圧線と、第1のスイッチを介して第2の色に対応するソースラインに接続される第2電圧線とを含み、

前記電源部は、第1の色を表す画素信号の最大電圧と最小電圧の中間値である第1電圧を前記中間電圧として第1電圧線に出力し、第2の色を表す画素信号の最大電圧と最小電圧の中間値である第2電圧を前記中間電圧として第2電圧線に出力する

請求項1から3の何れかに記載の表示駆動装置。 10

【請求項5】

請求項1から4までのいずれかに記載の表示駆動装置と、前記表示駆動装置によって駆動される表示パネルとを備える表示装置。

【請求項6】

前記表示パネルは有機ELパネルである請求項5記載の表示装置。

【請求項7】

ソースラインに画素信号を駆動するためのドライバと、

前記画素信号の最大電圧と最小電圧の間の電圧である中間電圧を中間電圧線に出力する電源部と、

ソースラインに画素信号を駆動する時はドライバとソースラインを接続し、画素信号の切替期間にはソースラインとドライバを切り離し、前記ソースラインを他のソースラインと接続させた後、ソースラインと前記中間電圧線を接続する、制御部と、

を有する表示駆動装置。 20

【請求項8】

前記ドライバ、および制御部は第1の半導体基板に形成され、前記電源部は第2の半導体基板に形成される請求項7に記載の表示駆動装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はテレビジョン受像機、パーソナルコンピュータ、ワークステーション等に用いる表示装置および表示駆動装置に関するものである。 30

【背景技術】

【0002】

従来、液晶表示パネルでは、陽の映像信号と陰の映像信号を交互に駆動する、いわゆる、反転駆動が用いられる場合がある。この反転駆動において、消費電力削減のため駆動期間中にI C内の隣接する端子をショートさせ、電荷の再利用を行う技術がある（たとえば、特許文献1参照）。

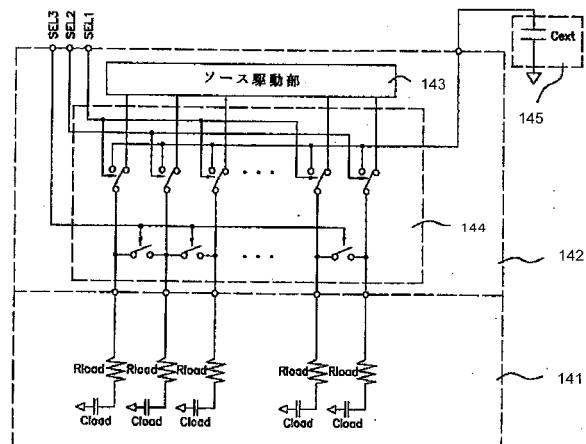

【0003】

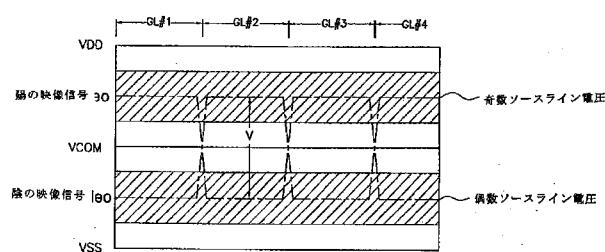

図11は、前記特許文献1に記載された、省電力化回路を図る従来の反転駆動方式の表示装置の構成図である。 40

【0004】

図11において、液晶パネル141は、ソース駆動部143とラインスイッチング部144によって構成されたソースドライバ142によって駆動され、さらに外部キャパシタ-145が接続された構成となっている。また、液晶パネル141の駆動方式の特徴である反転駆動方式として、図12は、従来の反転駆動における陽の映像信号および陰の映像信号を示す図である。同図における陽の映像信号、陰の映像信号は、ソースドライバ142から液晶パネル141に交互に供給される。

【特許文献1】特開2001-022329号公報

【発明の開示】

【発明が解決しようとする課題】

## 【0005】

従来の表示装置では、特許文献1に示す通り、陽の映像信号と陰の映像信号を交互に駆動するため（いわゆる、反転駆動を行うため）、その中間の信号レベルを通過することとなり有効であるが、たとえば有機ELパネルのように陽の映像信号と陰の映像信号を交互に駆動しない方式（いわゆる反転駆動ができない方式）については、隣接する端子を単にショートさせ外部キャパシターによる電荷の再利用はできず、省電力化が難しいという課題を有している。

## 【0006】

また、近年の多出力化、高負荷高速駆動によりICの発熱が課題となっている。

この発明は、上記従来の課題を解決するものであり、電荷の再利用を行い省電力化を図ると共に、発熱を低減する表示駆動装置および表示装置を提供することを目的とする。 10

## 【課題を解決するための手段】

## 【0007】

上記課題を解決するため本発明の表示駆動装置は、画素列毎にソースラインを有する表示パネルを駆動する表示駆動装置であって、ソースライン毎に設けられた第1スイッチと、ソースライン毎に設けられた第2スイッチと、ソースライン毎に設けられ、前記第2スイッチを介して当該ソースラインに画素信号を駆動するドライバと、前記画素信号の最大電圧と最小電圧の間の電圧である中間電圧を中間電圧線に出力する電源部と、各第1スイッチおよび各第2スイッチのオンおよびオフを制御する制御部とを備え、各第1スイッチの一端は前記中間電圧線に、他端は対応するソースラインに接続され、各第2スイッチの一端は前記ドライバに、他端は対応するソースラインおよび対応する前記第1スイッチの他端に接続され、前記制御部は、画素信号の出力期間と次の画素信号の出力期間との間の切り替え期間において、第2スイッチを一時的にオフにするとともに、当該第2スイッチに対応する前記第1スイッチを一時的にオンにする。 20

## 【0008】

この構成によれば、反転駆動を行わない表示パネル、例えば有機EL表示パネルにおいて、電荷再利用により発熱を低減し、加えて、再利用できない電荷変動を電源部に吸収させることによって表示駆動装置および表示パネルの発熱および消費電力を低減することができる。

## 【0009】

より詳しく説明すると、上記の切り替え期間において、第1スイッチは、全部または一部のソースライン同士を短絡し、かつ当該ソースラインを電源部に接続する。第2スイッチは、切り替え期間において、当該ソースラインをドライバから切り離す。例えば、ソースラインの総数が約6000本あるものとする。6000本のうち、上記の短絡直前において4000本が中間電圧よりも高く、2000本が中間電圧よりも低いとする。上記の短絡により、中間電圧よりも低い電圧の2000本と、中間電圧よりも電圧が高い4000本のうちの2000本とは、逆向きの電荷変動を相殺することになる（つまり電荷の再利用をすることになる）。これにより、発熱を低減することができる。なぜなら、逆向きの電荷変動を相殺できない従来技術では、全ての電荷変動をドライバが吸収し（つまりドライバに電流が流れ）、発熱するからである。 40

## 【0010】

さらに、中間電圧よりも電圧が高い4000本のうちの相殺されない2000本の電荷の変動は、第1スイッチを介して電源部に吸収される。これにより、ドライバでの発熱を電源部に転嫁することができる。

## 【0011】

このように、切り替え期間において、全部または一部のソースライン同士が短絡し、かつ当該ソースラインが電源部に接続される。これにより、短絡直前に中間電圧よりも高い電圧のソースラインと、短絡直前に中間電圧よりも低い電圧のソースラインとが電荷を相殺し合う。短絡しない場合にドライバが画素信号の電圧変化による電荷移動を全て吸収する必要がなく、発熱を低減することができる。加えて、相殺できない電荷は、ドライバで 50

はなく電源部が電荷の変動を吸収するので、ドライバでの発熱を電源部に転嫁することができる。

【0012】

ここで、前記ドライバ、第1スイッチ、第2スイッチおよび制御部は第1の半導体基板に形成され、前記電源部は第2の半導体基板に形成されるようにもよい。

【0013】

この構成によれば、電源部はドライバと異なる半導体基板に形成されるので、ドライバの発熱をより効率よく低減することができる。

【0014】

ここで、前記制御部は、前記切り替え期間において、全ての第2スイッチを一時的にオフにするとともに、当該第2スイッチに対応する全ての前記第1スイッチを一時的にオンにすることもよい。

10

【0015】

この構成によれば、制御部の回路構成を簡単にすることもできる、回路規模を少なくすることができる。

【0016】

ここで、前記制御部は、ソースライン毎に設けられた制御回路を有し、各制御回路は、対応するソースラインの画素信号と次の画素信号とが前記中間電圧をまたぐとき、前記切り替え期間において対応する第1スイッチおよび第2スイッチの一時的なオンおよびオフを行い、対応するソースラインの画素信号と次の画素信号とが前記中間電圧をまたがないとき、前記切り替え期間において対応する第1スイッチおよび第2スイッチの状態を維持することもよい。

20

【0017】

この構成によれば、ソースラインの画素信号と次の画素信号とが中間電圧をまたがないとき、当該ソースラインを電源部に接続しないので、発熱をさらに低減し、消費電力をより低減することができる。

【0018】

ここで、前記中間電圧線は、第1スイッチを介して第1の色に対応するソースラインに接続される第1電圧線と、第1スイッチを介して第2の色に対応するソースラインに接続される第2電圧線とを含み、前記電源部は、第1の色を表す画素信号の最大電圧と最小電圧の中間値である第1電圧を前記中間電圧として出力し、第2の色を表す画素信号の最大電圧と最小電圧の中間値である第2電圧を前記中間電圧として出力することもよい。

30

【0019】

この構成によれば、色毎に画素信号の電圧範囲が異なる場合に、電荷再利用の効率を上げ、さらに消費電力を低減することができる。

【0020】

ここで、さらに、前記中間電圧線と各第1スイッチとの間に挿入された第3スイッチを備え、前記制御部は、第1スイッチをオンにした後に第3スイッチを一時的にオンすることもよい。

40

【0021】

この構成によれば、第1スイッチによりソースライン同士を短絡した直後に、第3スイッチによりソースラインを電源部に接続するので、同時に接続する場合と比べて、ノイズおよび貫通電流の発生を抑えることができる。

【0022】

また、本発明の表示装置は上記の表示駆動装置と、前記表示駆動装置によって駆動される表示パネルとを備える。

【0023】

ここで、前記表示パネルは有機ELパネルであってもよい。

【発明の効果】

50

## 【0024】

本発明の表示装置によれば、反転駆動を行わない表示装置、たとえば有機ELにおいても、電荷再利用の実現が可能となり、かつ電源を外部に持つことによる発熱を低減し、省電力化を図ることができる。

## 【発明を実施するための最良の形態】

## 【0025】

## (第1の実施形態)

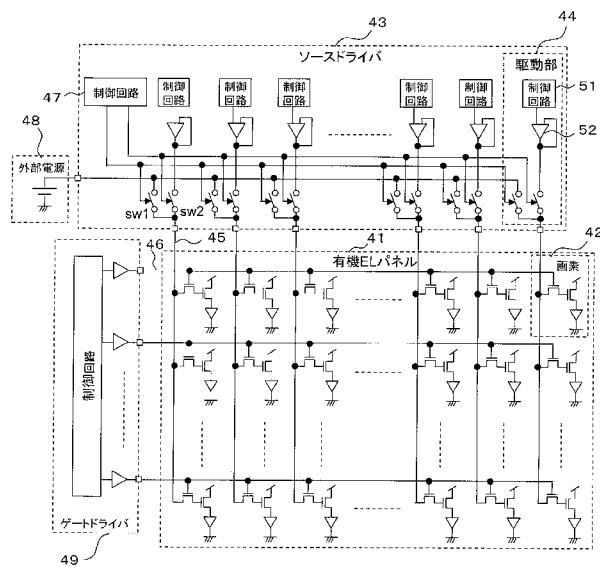

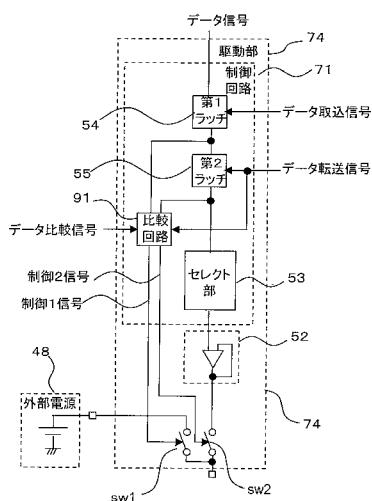

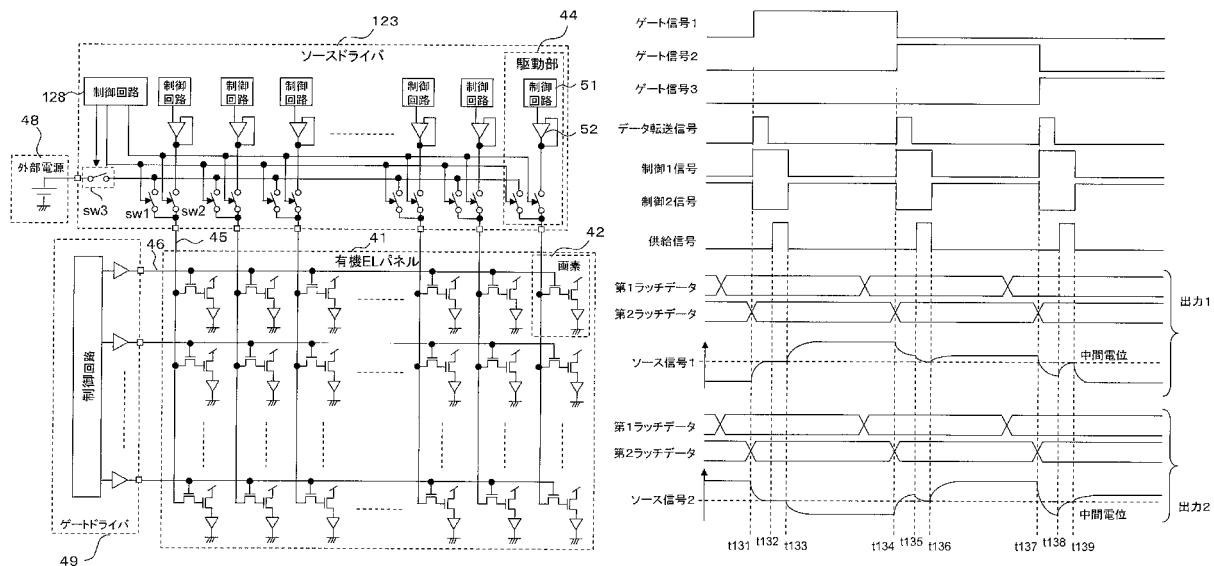

図1、図2は、本発明の第1の実施形態に係る表示装置、表示駆動装置の構成例を示すものである。

## 【0026】

図1は本実施形態に係る表示装置の全体構成図である。この表示装置は、表示パネルとしての有機ELパネル41と、ソースドライバ43と、外部電源48と、ゲートドライバ49とを備える。

## 【0027】

有機ELパネル41は、行列上に配置された複数の画素42と、画素の列毎に設けられたソースライン45と、画素の行毎に設けられたゲートライン46とを有する。

## 【0028】

ソースドライバ43は、外部電源48とともに、画素列毎にソースラインを有する表示パネルを駆動する表示駆動装置として機能する。

## 【0029】

この表示駆動装置は、ソースライン45毎に設けられた第1スイッチsw1と、ソースライン45毎に設けられた第2スイッチsw2と、ソースライン45毎に設けられ、前記第2スイッチsw2を介して当該ソースライン45に画素信号を駆動するドライバとしてのAMP部52と、前記画素信号の最大電圧と最小電圧の間の電圧である中間電圧を中間電圧線に出力する外部電源48と、各第1スイッチsw1および各第2スイッチsw2のオンおよびオフを制御する制御回路47とを備える。

## 【0030】

ソースドライバ43は、ソースライン毎に設けられた駆動部44と、制御回路47とを有する。

## 【0031】

各第1スイッチsw1の一端は前記中間電圧線に、他端は対応するソースラインに接続される。

## 【0032】

各第2スイッチsw2の一端は前記AMP部52に、他端は対応するソースライン45および対応する前記第1スイッチsw1の他端に接続される。

## 【0033】

制御回路47は、画素信号の出力期間と次の画素信号の出力期間との間の切り替え期間において、第2スイッチsw2を一時的にオフにするとともに、当該第2スイッチsw2に対応する第1スイッチsw1を一時的にオンにする。

## 【0034】

制御回路47が第1スイッチsw1および第2スイッチsw2を制御することにより、切り替え期間において、全部または一部のソースライン同士が短絡し、かつ当該ソースラインが電源部に接続される。これにより、短絡直前に中間電圧よりも高い電圧のソースラインと、短絡直前に中間電圧よりも低い電圧のソースラインとが電荷を相殺し合う。短絡しない場合にドライバが画素信号の電圧変化による電荷移動を全て吸収する必要がなく、発熱を低減することができる。加えて、相殺できない電荷は、ドライバではなく電源部が電荷の変動を吸収するので、ドライバでの発熱を電源部に転嫁することができる。

## 【0035】

駆動部44は、各ソースラインに対応して設けられ、図1の破線で示すように、制御回路51と、ドライバとしてのAMP部52と、第1スイッチsw1と第2スイッチsw2

10

20

30

40

50

とを含む。

【0036】

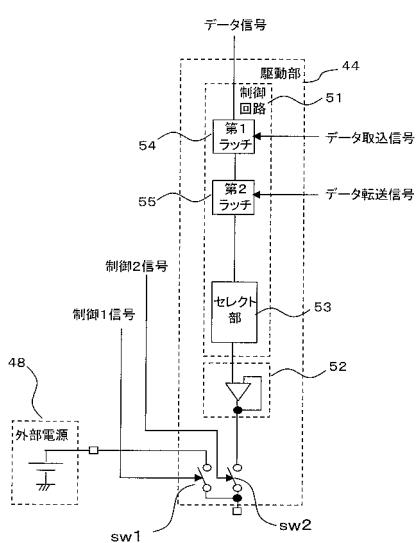

次に、図2は本実施形態に係る表示駆動装置内の駆動部44の詳細な構成例を示す図である。具体的には、ソースライン45を駆動するための駆動部44と、外部電源48と、制御回路47からの制御1信号および制御2信号との接続を示すものである。同図のように、駆動部44は、制御回路51と、AMP部52と、第1スイッチsw1と、第2スイッチsw2とを備える。制御回路51は、第1ラッチ54と、第2ラッチ55と、セレクト部53とを備える。

【0037】

第1ラッチ54は、デジタルのデータ信号として転送される画像データをデータ取込信号によって記憶する。第2ラッチ55は、第1ラッチ54の出力をデータ転送信号によって記憶する。第2ラッチ55の出力はデジタル信号をアナログ信号に変換するデジタル-アナログ変換器であるセレクト部53に入力される。セレクト部53によって変換されたアナログ信号はAMP部52に入力される。AMP部52は、アナログ画素信号を第2スイッチsw2を介してソースライン45に駆動するドライバとして機能する。

【0038】

また、AMP部52の出力は第2スイッチsw2を介してソースライン45に接続される。第2スイッチsw2は制御2信号により制御される。外部電源48は、第2スイッチsw2のソースライン側に接続され、かつ制御1信号によって制御される第1スイッチsw1を介してソースライン45に接続される。

【0039】

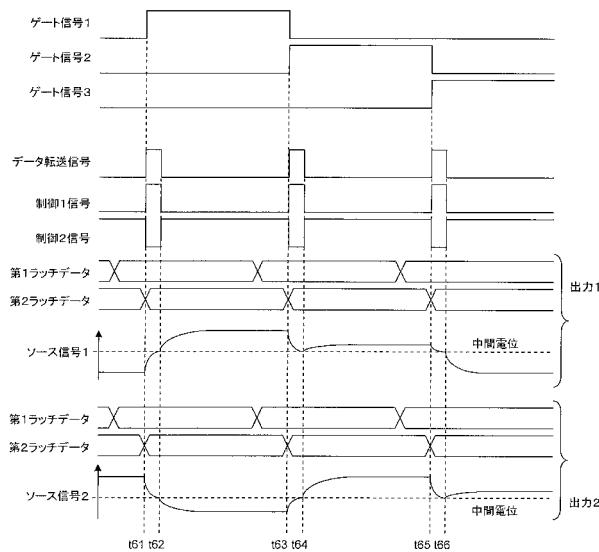

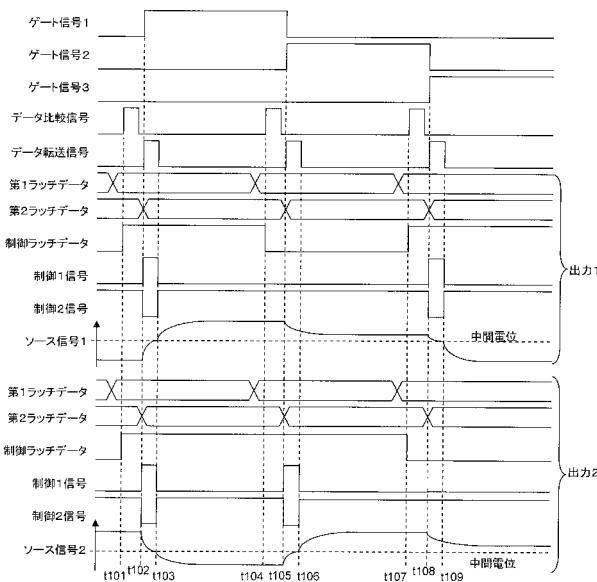

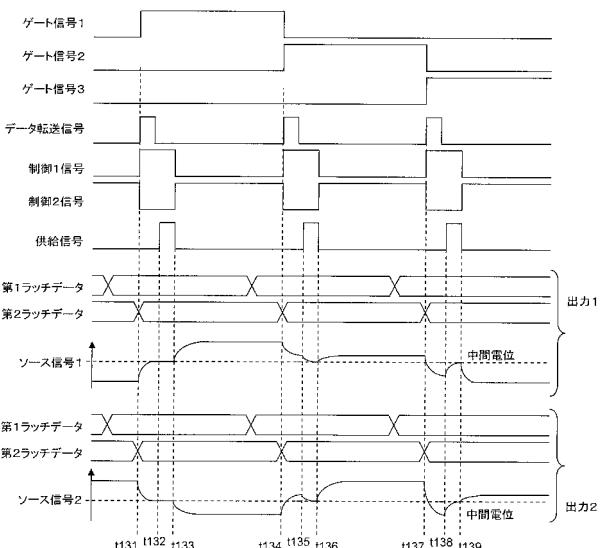

次に、図3を用いて、第1の実施形態における表示装置、表示駆動装置の動作を説明する。図3は第1の実施形態に係る表示装置の動作タイミングを示すタイムチャート図である。

【0040】

図3において、有機ELパネル41に複数存在するゲートライン46のうちの3ラインの信号レベル状態をゲート信号1、ゲート信号2、ゲート信号3とする。また有機ELパネル41に複数存在するソースライン45のうちの2ラインの信号レベル状態をソース信号1、ソース信号2とする。また、それぞれのソース信号の出力範囲の中間電位を破線で表す。

【0041】

なお、図3において、データ転送信号、制御1信号、制御2信号は図2に示した信号である。第1ラッチ54の出力は第1ラッチデータ、第2ラッチ55の出力は第2ラッチデータとしてある。

【0042】

また、図3において、ゲート信号1の立ち上がりをt61、ゲート信号2の立ち上がりをt63、ゲート信号3の立ち上がりをt65、データ転送信号の立ち下がりをt52、t54、t66とする。

【0043】

図3より、まず始めに、データ信号として伝送される画素データは、データ取込信号によって第1ラッチ54に取り込まれる。

【0044】

次に、この動作をソースドライバ43を構成するIC内のすべての駆動部44に対し順に行われる。すべての駆動部44に所望の画素データが第1ラッチ54の取り込まれた後、データ転送信号の立ち上がりt61に同期して第2ラッチ55にデータ転送されると同時に、ゲート信号1が立ち上がり、ゲート信号1に接続された複数の画素が、ソースライン45からの駆動可能状態となる。

【0045】

次に、第2ラッチ55に転送された画像データはセレクト部53へ入力される。セレクト部53によりデジタルからアナログに変換されたアナログ電圧はAMP部52へ伝達さ

10

20

30

40

50

れる。さらに、ソースライン 45 へ A M P 部 52 によって駆動された電圧が画素信号として出力される。制御 1 信号がハイの時、第 1 スイッチ s w 1 は接続状態となり、ロウの時、第 1 スイッチ s w 1 は切断状態となる。

【0046】

次に、制御 2 信号がハイの時、第 2 スイッチ s w 2 は接続状態となり、ロウの時、第 2 スイッチ s w 2 は切断状態となる。

【0047】

次に、制御 1 信号はデータ転送信号 58 に同期してハイになり、制御 2 信号はロウになることにより、第 1 スイッチ s w 1 が接続状態、第 2 スイッチ s w 2 は切断状態になり、ソースライン 45 は外部電源 48 の中間電圧線に接続され、t 61 から t 62 の間は各ソースライン 45 には外部電源 48 より供給される中間電圧が印加される。 10

【0048】

その後、制御 1 信号がロウ、制御 2 信号がハイになることにより、第 1 スイッチ s w 1 が切断され、第 2 スイッチ s w 2 が接続されることにより、ソースライン 45 には A M P 部 52 が接続され、画像データに応じた電圧がソースライン 45 に印加される。

【0049】

この動作をゲート信号 2、ゲート信号 3、・・・と、有機 E L パネル 41 の全ゲートライン 46 毎に繰り返すことにより、ゲート信号がハイ区間の画素 42 に画像データに対応した電圧が印加され、順に全ラインへの電圧印加を繰り返すことにより、1 フレームの表示がされる。 20

【0050】

以上、図面を用いて説明した本発明の第 1 の実施形態に係る表示装置および表示駆動装置は、たとえば、パネルすべてのソースラインの半分が 11V、残りの半分が 1V を印加していた状態であったとすると、制御 1 信号がハイ、かつ制御 2 信号がロウの時、一度外部電源 48 により全ソースライン 45 に 11V と 1V の中間である 6V を印加することにより、すべてのソースラインは 6V に収束する。

【0051】

この場合、11V のソースラインと 1V のソースラインの数がちょうど半分であるため、電荷保存則により、11V のソースラインから 1V のソースラインへ電荷が移動するため、外部電源からの電荷の供給は発生することなしに、6V までの電荷の供給をソースドライバ 43 から行うことなしに実施することが出来る。 30

【0052】

すなわち、本発明の第 1 の実施形態に係る表示装置は、陽の映像信号と陰の映像信号を交互に駆動しない（いわゆる反転駆動しない）有機 E L パネル 41 においても、常に外部電源 48 により一度中間電位を印加することができ、有機 E L パネル 41 への充放電電力は半分に抑えることが出来るため、省電力化が可能となる。

【0053】

さらに、有機 E L パネルの動作において、映像を表示する場合、11V のソースラインと 1V のソースラインの数がちょうど半分になることはほぼ無い。

【0054】

その理由は、FHD パネル（フルハイビジョンパネル）の場合、ソースラインは 1920 × 3 の 5760 ライン存在し、たとえば、11V のソースラインが 3840 ライン、1V のソースラインが 1920 ラインであった場合、制御 1 信号がハイ、かつ制御 2 信号がロウの時、電荷保存則により (11V - 1V) × 2 / 3 + 1V = 約 7.7V に収束し、外部電源 48 により 6V へ強制的に収束されるためである。 40

【0055】

しかし、本発明は外部電源 48 がソースドライバ 43 と異なる半導体基板に形成されている、或いは外部にある。

【0056】

これにより、約 7.7V - 6V = 約 1.7V の電位差を供給するための電力は外部電源 50

4 8 によって発生し、その電力に応じて外部電源 4 8 は発熱する。

【 0 0 5 7 】

すなわち、本発明の第 1 の実施形態に係る表示装置、表示駆動装置では、従来ソースドライバ 4 3 で駆動していた約 1.7 V 分の電力による発熱を外部電源 4 8 に移すことにより、ソースドライバ 4 3 の発熱量を減らすことができる。

【 0 0 5 8 】

さらに、発熱量を減らすことによりソースドライバ 4 3 を更に多出力化することができる。

【 0 0 5 9 】

すなわち、ソースドライバの使用数を減らすことによる有機 E L パネルのコスト削減が 10

出来る。

【 0 0 6 0 】

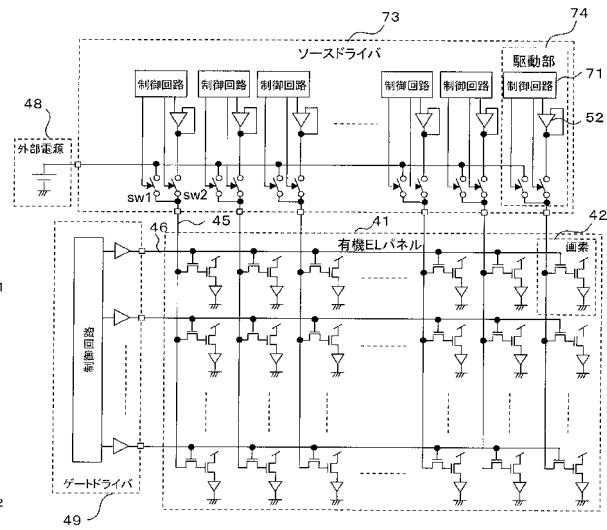

( 第 2 の実施形態 )

第 1 の実施形態では切り替え期間において全ソースライン 4 5 を短絡させて外部電源 4 8 に接続する例を説明した。つづいて、第 2 の実施形態では、切り替え期間において一部のソースライン 4 5 を短絡させて外部電源 4 8 に接続する表示制御部の構成について説明する。

【 0 0 6 1 】

すなわち、第 2 の実施形態の表示制御部は、ソースライン毎に設けられた制御回路を有し、各制御回路は、対応するソースラインの画素信号と次の画素信号とが外部電源 4 8 の中間電圧をまたぐとき、前記切り替え期間において対応する第 1 スイッチおよび第 2 スイッチの一時的なオンおよびオフを行い、対応するソースラインの画素信号と次の画素信号とが前記中間電圧をまたがないとき、前記切り替え期間において対応する第 1 スイッチおよび第 2 スイッチの状態を維持するように構成されている。

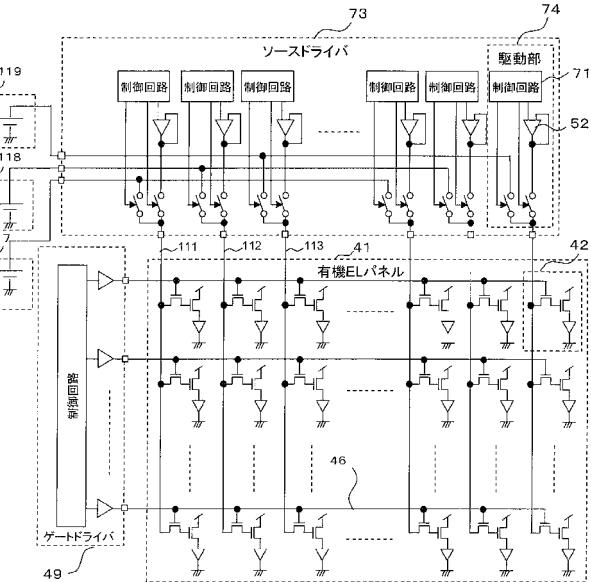

【 0 0 6 2 】

図 4 は第 2 の実施形態に係る表示装置の全体構成図である。同図の表示装置は図 1 に示した表示装置と比較して、ソースドライバ 4 3 の代わりにソースドライバ 7 3 を備える点が異なっている。同じ構成要素には同じ符号を付しているので、以下では同じ点は説明を省略して異なる点を中心に説明する。

【 0 0 6 3 】

ソースドライバ 7 3 は、図 1 のソースドライバ 4 3 と比べて、制御回路 4 7 が削除された点と、駆動部 4 4 の代わりに駆動部 7 4 を備える点とが異なっている。

【 0 0 6 4 】

駆動部 7 4 は、制御回路 7 1 、 A M P 部 5 2 、第 1 スイッチ s w 1 、第 2 スイッチ s w 2 を備える。

【 0 0 6 5 】

制御回路 7 1 は、図 1 の制御回路 5 1 の機能に加えて、現在の画素信号と次の画素信号とを比較し、比較の結果、現在の画素信号と次の画素信号とが前記中間電圧をまたぐか否かを判定し、判定結果に応じて、切り替え期間において第 1 スイッチおよび第 2 スイッチの一時的なオンおよびオフを行うか、第 1 スイッチおよび第 2 スイッチの状態を維持するかを決定する。

【 0 0 6 6 】

すなわち、制御回路 7 1 は、現在の画素信号と次の画素信号とが前記中間電圧をまたぐとき、前記切り替え期間において対応する第 1 スイッチおよび第 2 スイッチの一時的なオンおよびオフを行い、一方、画素信号と次の画素信号とが前記中間電圧をまたがないとき、前記切り替え期間において対応する第 1 スイッチおよび第 2 スイッチの状態を維持する。

【 0 0 6 7 】

図 5 は第 2 の実施形態に係る表示駆動装置内の駆動部 7 4 の詳細な構成例を示す図である。同図の駆動部 7 4 は、図 4 の駆動部 4 4 と比べて、比較回路 9 1 が追加されている点

10

20

30

40

50

が異なっている。

【0068】

比較回路91は、現在の画素信号（第2ラッチ55の画素データ）と次の画素信号（第1ラッチ54の画素データ）とを比較し、比較結果に応じて制御1信号および制御2信号を生成する回路である。

【0069】

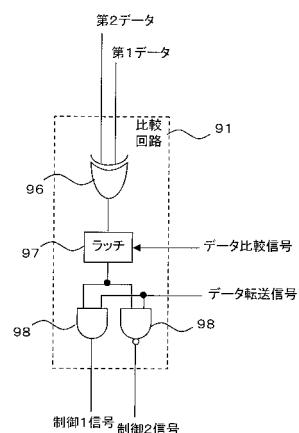

図6は第2の実施形態に係る比較回路91の詳細な構成例を示す図である。同図の比較回路91は、比較器96、ラッチ97、アンドゲート98、 NANDゲート99を備える。

【0070】

比較器96は、現在の画素信号（第2ラッチ55の画素データ）と次の画素信号（第1ラッチ54の画素データ）が前記中間電圧（画素データの中央値）をまたぐか否かを判定する。同図では、比較器96は、第2ラッチ55の画素データのMSB（最上位ビット）と第1ラッチ54の画素データのMSBとが一致するか否かを判定する排他的論理回路でよい。この場合、比較器96は、両MSBが一致しない場合は、両データが画素データの中央値をまたぐことを示す”1”出力し、両MSBが一致する場合は、両データが画素データの中央値をまたがないことを示す”0”を出力する。比較器96は、画素データがアナログ電圧に変換される前のデジタル画素データを比較するので、簡単な回路により実現することができる。

【0071】

ラッチ97は、比較器96の比較結果つまり、両MSBが一致しないか一致するかを示す1ビットのフラグをデータ比較信号のタイミングで取り込み保持する。

【0072】

アンドゲート98は、ラッチ97に保持されたフラグが1のとき（上記両データが上記中央値をまたぐとき）データ転送信号に同期して制御1信号を出力し、ラッチ97に保持されたフラグが”0”的き（上記両データが上記中央値をまたがないとき）データ転送信号に係わらず同期して制御1信号を出力し、ラッチ97のフラグが”1”的き（上記両データが上記中央値をまたぐとき）、データ転送信号に同期して（つまり切り替え期間において）、第1スイッチsw1を一時的にオンにする制御1信号を出力するとともに、対応する第2スイッチsw2を一時的にオフにする制御2信号を出力する。

【0073】

一方、アンドゲート98および NANDゲート99は、ラッチ97のフラグが”0”的き（上記両データが上記中央値をまたがないとき）、切り替え期間において制御1信号および制御2信号を変化させない。その結果、第1スイッチsw1および第2スイッチsw2の状態を維持する。

【0074】

また、図7を用いて、本発明の第2の実施形態における表示装置、表示駆動装置の動作を説明する。

【0075】

また、図7において、ゲート信号1の立ち上がりをt102、ゲート信号2の立ち上がりをt105、ゲート信号3の立ち上がりをt108、データ転送信号の立ち下がりをt103、t106、t109、データ比較信号の立ち上がりをt101、t104、t107とする。

【0076】

図7に示すデータ比較信号のハイ期間中に第1ラッチ54と第2ラッチ55の上位データを比較器96で比較する。

【0077】

次に、第1ラッチ54の出力データの最上位ビットを第1データとして比較器96に入力し、第2ラッチ55の出力データの最上位ビットを第2データとして比較器96に入力する。第1データと第2データが共にハイ、または共にロウのとき比較器96はロウを出力する。このロウ出力は、第1データと第2データとが上記の中央値をまたがないことを

10

20

30

40

50

意味する。また、第1データがハイで第2データがロウの場合、または第1データがロウで第2データがロウの場合、比較器96はハイを出力する。このハイ出力は、第1データと第2データとが上記の中央値をまたぐことを意味する。

【0078】

次に、比較器96にて出力された比較データは、データ比較信号の立ち上がりt101と同期してラッチ97に比較データが保持される。

【0079】

次に、データ転送信号の立ち上がりt102に同期して第2ラッチ55にデータ転送される。かつラッチ97の比較データがハイであればデータ転送信号のハイ期間に制御1信号、制御2信号のパルスが出力される。もし、比較データがロウであればデータ転送信号のハイ期間に制御1信号、制御2信号は変化しない。

【0080】

以上のように、本発明の第2の実施形態における表示装置、表示駆動装置では、陽の映像信号と陰の映像信号を交互に駆動しない有機ELパネルにおいても、画像データに応じて外部電源により一度中間電位を印加することが出来る。

【0081】

また、本実施形態に係る表示装置、表示駆動装置では、たとえば、前のラインが1Vを印加し、次のラインで11Vを印加する場合、画像データの最上位ビットはロウからハイになる。この場合、第1データ92がロウ、第2データ93がハイとなり、比較器96によりハイを出力する。

【0082】

つまり、中間電位6Vをまたぐかどうかを比較器96によって比較することにより、中間電位6Vをまたぐ場合は外部電源に接続する制御を行い、一度中間電位を印加することが出来る。

【0083】

また、中間電位6Vをまたがない場合、つまり、第1データ92と第2データ93が共にハイ、またはロウの場合は外部電源に接続しない制御を行うことで、無駄な電荷の移動を抑えることが出来、第1の実施形態に比べさらに省電力化を実現することが可能となる。

【0084】

また、本実施形態では、第1の実施形態と同様に、従来ソースドライバ73で駆動していた電力による発熱を外部電源48に移すことにより、ソースドライバ73の発熱量を減らすことが出来るため、ソースドライバ73を更に多出力化することが可能となること、ソースドライバの使用数を減らすことによる有機ELパネルのコスト削減が出来る。

【0085】

(第3の実施形態)

第1および第2の実施形態では、外部電源48から供給される中間電圧は1種類である。これに対して、第3の実施形態では、ソースラインにドライブすべき画素信号の電圧範囲が色によって異なる場合に、色毎に最適な中間電圧を供給する構成について説明する。

【0086】

図8は、本発明の第3の実施形態に係る表示装置、表示駆動装置の構成例を示すものである。図8の表示装置は、図4に示した表示装置と比較して、外部電源48の代わりに第1外部電源117、第2外部電源118、第3外部電源119を備える点が異なっている。同じ構成要素には同じ符号を付しているので、以下では同じ点は説明を省略して異なる点を中心に説明する。

【0087】

第1外部電源117は、複数のソースライン45のうちR(赤色)の画素列に対応するソースラインである第1ソースライン111に、対応する第1スイッチsw1を介して接続され、第1電圧を出力する。第1電圧は例えばR(赤色)を示す画素信号の最大値と最小値との間の中間値である。

10

20

30

40

50

## 【0088】

第2外部電源118は、複数のソースライン45のうちG(緑色)の画素列に対応するソースラインである第2ソースライン112に、対応する第1スイッチsw1を介して接続され、第2電圧を出力する。第2電圧は例えばG(緑色)を示す画素信号の最大値と最小値との間の中間値である。

## 【0089】

第3外部電源119は、複数のソースライン45のうちB(青色)の画素列に対応するソースラインである第3ソースライン113に、対応する第1スイッチsw1を介して接続され、第3電圧を出力する。第3電圧は例えばB(青色)を示す画素信号の最大値と最小値との間の中間値である。

10

## 【0090】

以上のように構成された第3の実施形態における表示装置および表示駆動装置の動作は、中間電圧を除いて第2の実施形態と同じである。第3の実施形態における中間電圧は、色によって画素信号の電圧範囲が異なる場合に、RGB個別の中間電位を上記の第1、第2、第3電圧として設定可能である。これにより、R用ソースライン、G用ソースライン、B用ソースライン個別に低消費電力化および発熱の低減を効率よく実現することができる。

## 【0091】

このように、外部電源をRGBそれぞれで分けることにより、たとえば、RGB毎に出力される電圧範囲が異なり、よって中間電位も異なる場合、最適な中間電位をRGBそれぞれで定めることができ、無駄のない省電力化が可能となる。

20

## 【0092】

なお、第1の実施形態において、外部電源48の代わりに第1外部電源117、第2外部電源118および第3外部電源119を備える構成にしてもよい。

## 【0093】

また、RGBのうち2色の画素信号の電圧範囲が同じであれば、3つの外部電源ではなく2つの外部電源を備えることが望ましい。

## 【0094】

複数の画素42の色表現がRGB以外の第1の色～第nの色で表現あってもよい。すなわち、RGBの3色固定だけではなく、4色、5色と増やすことで、色再現範囲を向上させることができる。

30

## 【0095】

また、第1の実施形態と同様に、従来ソースドライバ73で駆動していた電力による発熱を外部電源117、118、119に移すことにより、ソースドライバ73の発熱量を減らすことが出来るため、ソースドライバ73を更に多出力化することが可能となることで、ソースドライバの使用数を減らすことによる有機ELパネルのコスト削減が出来る。

## 【0096】

## (第4の実施形態)

第1の実施形態では、切り替え期間において、外部電源48は各第1スイッチsw1の一端に常に接続され、(A)各第1スイッチsw1がオンすることによりソースライン45同士が短絡するタイミングと、(B)各第2スイッチsw2がオフすることによりソースライン45と駆動部44とが切断されるタイミングと、(C)各ソースライン45に中間圧が印加されるタイミングとが同時に起こる構成について説明した。これに対して、第4の実施形態では、(A)および(B)のタイミングよりも(C)のタイミングを遅らせる構成について説明する。(C)のタイミングを遅らせるのは、ノイズの発生を回避し、貫通電流を防止するためである。

40

## 【0097】

図9は、本発明の第4の実施形態に係る表示装置、表示駆動装置の構成例を示すものである。図9の表示装置は、図1に示した表示装置と比較して、ソースドライバ43の変わりにソースドライバ123を備える点が異なっている。同じ構成要素には同じ符号を付し

50

ているので、以下では同じ点は説明を省略して異なる点を中心に説明する。

【0098】

ソースドライバ123は、ソースドライバ43と比べて、第3スイッチsw3が追加された点と、制御回路47の代わりに制御回路128を備える点とが異なっている。

【0099】

第3スイッチsw3は、外部電源48と各第1スイッチsw1とを接続する中間電圧線に挿入され、制御回路128からの供給信号がハイのときオンする。

【0100】

制御回路128は、制御回路47の機能に加えて、第3スイッチsw3をオンにするタイミングを制御することにより、上記の(A)および(B)のタイミングよりも(C)のタイミング(供給信号のタイミング)を遅らせる。

10

【0101】

次に、図10を用いて、本発明の第4の実施形態における表示装置、表示駆動装置の動作を説明する。第4の実施形態における表示装置、表示駆動装置の動作は、上記(A)および(B)のタイミングよりも(C)のタイミング(供給信号のタイミング)を遅らせる点を除いて、第1の実施形態と同様であるので、差異を中心に説明する。

【0102】

制御回路128からの供給信号がハイの時、第3スイッチsw3は接続状態となり、口ウの時、第3スイッチsw3は切断状態となる。同図のタイミングt131において、制御1信号はデータ転送信号に同期してハイになり、制御2信号はロウになることにより、第1スイッチsw1が接続状態、第2スイッチsw2は切断状態になる(上記(A)および(B))。

20

【0103】

このとき供給信号はロウのままであり、ソースライン45同士は短絡するが中間電圧は供給されていない。

【0104】

次に供給信号がハイとなり、ソースライン45には外部電源48が接続され、図10に示すように外部電源48より供給される中間電圧が印加される(上記(C))。

【0105】

その後、制御1信号がロウ、制御2信号がハイ、供給信号がロウになることにより、第1スイッチsw1が切断され、第2スイッチsw2が接続され、第3スイッチsw3が切断される。これにより、ソースライン45にはAMP部52が接続され、画像データに応じた電圧がソースライン45に印加される。この動作をライン毎に繰り返すことにより、ゲート信号がハイ区間の画素42に画像データに対応した電圧が印加され、順に全ラインへの電圧印加を繰り返すことにより、1フレームの表示がされる。

30

【0106】

以上のように、この実施の形態によれば、第1の実施形態と同様の効果に加えて、切り替え期間において、ソースライン45に中間電圧を印加するタイミングを遅延させることによって、ノイズの発生を抑制し、貫通電流を防止することができる。

【0107】

40

なお、中間電位の外部電源を設けていたが、第3の実施形態のように、複数の電位の複数の外部電源を設け、表示する画像データに最も近い電位の外部電源に接続するようになると、更に省電力化が可能となる。

【0108】

(まとめ)

以上、図面を用いて説明したように、本発明の第1～第4の実施形態に係る表示駆動装置および表示装置は、反転駆動を行わない表示装置、たとえば有機ELにおいても、電荷再利用の実現が可能となり、かつ電源を外部に持つことによる発熱対策も出来、多出力化が実現でき、低コスト化につながる。

【0109】

50

また、各駆動部で必要な場合のみ電荷再利用を行うことが出来る。

また、データとの比較を行うことで、たとえば I C 内部で閉じた効率的な電荷再利用を実現でき、無駄な消費電力を抑えることが出来る。

【 0 1 1 0 】

また、R G B それぞれで駆動部の電圧出力範囲の電圧が異なる場合、R G B それぞれの外部電源を設けることで、R G B それぞれの中間電位を供給することが出来、電荷再利用の効率をあげ低消費電力化を実現することが出来る。

【 0 1 1 1 】

また、それぞれのソースラインを互いに接続したあとに、外部電源を供給することにより、同時に接続する場合に比べて、ノイズや貫通電流の影響を抑えることが出来る。 10

【 0 1 1 2 】

( 比較例 )

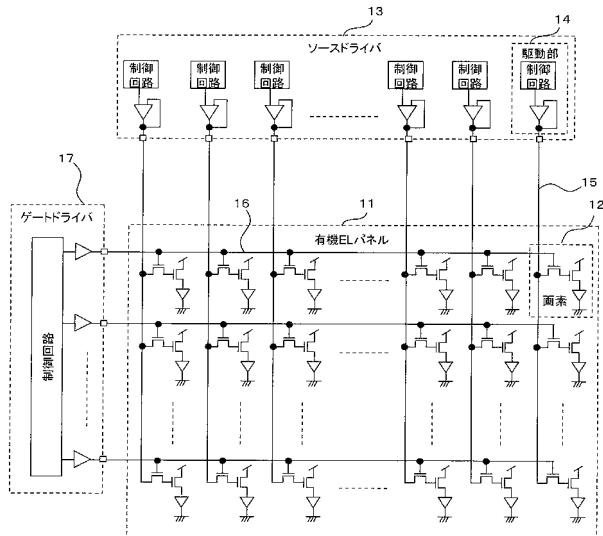

以下、本発明の実施形態における表示装置および表示駆動装置との比較例として、反転駆動をしない表示装置および表示駆動装置において本発明を適用しない場合の構成および動作を図面を参照しながら説明する。

【 0 1 1 3 】

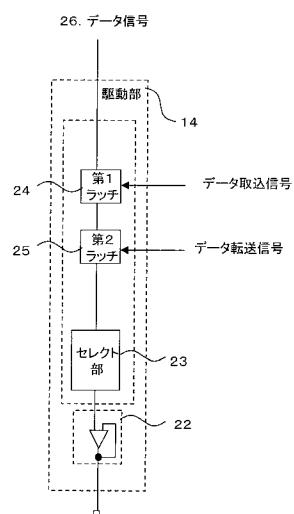

図 1 3、図 1 4 は比較例の有機 E L パネルを有する表示装置、駆動部の構成を示す図である。

【 0 1 1 4 】

図 1 3 において、表示装置は、有機 E L パネル 1 1、ソースドライバ 1 3、ゲートドライバ 1 7 を備える。有機 E L パネル 1 1 は、複数の画素 1 2 と、画素列毎のソースライン 1 5 と、画素行毎のゲートライン 1 6 を有する。ソースドライバ 1 3 は、ソースライン 1 5 毎の駆動部 1 4 を備える。 20

【 0 1 1 5 】

また、図 1 4 において、駆動部 1 4 は、A M P 部 2 2、セレクト部 2 3、第 1 ラッチ 2 4、第 2 ラッチ 2 5 を備える。

【 0 1 1 6 】

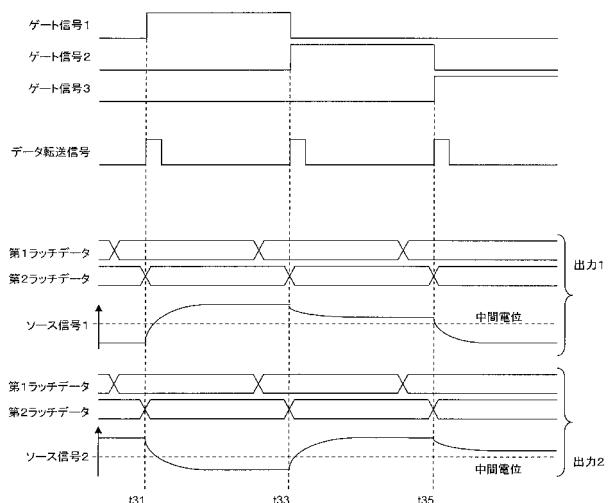

また、図 1 3、図 1 4 に示す表示装置の動作のタイミングチャートを図 1 5 に示す。

有機 E L パネル 1 1 に複数存在するゲートライン 1 6 のうちの 3 ラインの信号レベル状態をゲート信号 1、ゲート信号 2、ゲート信号 3 とする。また有機 E L パネル 1 1 に複数存在するソースライン 1 5 のうちの 2 ラインの信号レベル状態をソース信号 1、ソース信号 2 とする。また、それぞれのソース信号の出力範囲の中間電位を破線で表す。また、ゲート信号 1 の立ち上がりを t 3 1、ゲート信号 2 の立ち上がりを t 3 2、ゲート信号 3 の立ち上がりを t 3 3 とする。 30

【 0 1 1 7 】

以上のように構成された表示装置について、その動作を説明する。

データ信号として伝送される画像データは、データ取込信号によって第 1 ラッチ 2 4 に取り込まれる。この動作は、ソースドライバ 1 3 を構成する I C 内のすべての駆動部 1 4 に対し順に行われる。すべての駆動部 1 4 に所望の画像データが第 1 ラッチ 2 4 の取り込まれた後、図 1 5 に示すデータ転送信号の立ち上がり t 3 1 に同期して第 2 ラッチ 2 5 にデータ転送される。第 2 ラッチ 2 5 に転送された画像データはセレクト部 2 3 へ接続され所望のアナログ電圧が A M P 部 2 2 へ伝達され、ソースライン 1 5 へ A M P 部 2 2 によって電圧が outputされる。この動作をライン毎に繰り返すことにより、ゲート信号がハイ区間の画素 1 2 に画像データに対応した電圧が印加され、順に全ラインへの電圧印加を繰り返すことにより、1 フレームの表示がされる。 40

【 0 1 1 8 】

以上説明したように、ソースライン 1 5 の電荷変動は、ドライバとして A M P 部 2 2 が全て吸収することになる。つまり、切り替え期間毎に電荷変動量に対応する電流が A M P 部 2 2 に流れるので、A M P 部 2 2 において無駄に発熱し、電力を消費する。図 1 3 ~ 図 1 5 を用いて説明した比較例における表示装置では、省電力化が困難であり、さらに、発 50

熱に対しても課題を有している。これに対して、本発明の各実施形態における表示装置および表示駆動装置では、発熱および消費電力を低減することができる。

【産業上の利用可能性】

【0119】

本発明にかかる表示装置は、有機ELパネルなどの表示用に有用である。また電圧で駆動するプリンタドライバ等の用途にも応用できる。

【図面の簡単な説明】

【0120】

【図1】第1の実施形態に係る表示装置の全体構成図である。

【図2】第1の実施形態に係る表示駆動装置内の駆動部の詳細な構成例を示す図である。 10

【図3】第1の実施形態に係る表示装置の動作タイミングを示すタイムチャート図である

。

【図4】第2の実施形態に係る表示装置の全体構成図である。

【図5】第2の実施形態に係る表示駆動装置内の駆動部の詳細な構成例を示す図である。

【図6】第2の実施形態に係る比較回路の詳細な構成例を示す図である。

【図7】第2の実施形態に係る表示装置の動作タイミングを示すタイムチャート図である

。

【図8】第3の実施形態に係る表示装置の全体構成図である。

【図9】第4の実施形態に係る表示装置の全体構成図である。

【図10】第4の実施形態に係る表示装置の動作タイミングを示すタイムチャート図である。 20

【図11】従来の反転駆動方式の表示装置の全体構成を示す図である。

【図12】従来の反転駆動における陽の映像信号および陰の映像信号を示す図である。

【図13】比較例における反転駆動しない表示装置の全体構成を示す図である。

【図14】比較例における反転駆動しない駆動部の構成を示す図である。

【図15】比較例における反転駆動しない表示装置のタイミングチャート図である。

【符号の説明】

【0121】

2 1 駆動部

2 2 A M P 部

2 3 セレクト部

2 4 第1ラッチ

2 5 第2ラッチ

4 1 有機ELパネル

4 2 画素

4 3 ソースドライバ

4 4 駆動部

4 5 ソースライン

4 6 ゲートライン

4 7 制御回路

4 8 外部電源

4 9 ゲートドライバ

5 1 制御回路

5 2 A M P 部

5 3 セレクト部

5 4 第1ラッチ

5 5 第2ラッチ

7 3 ソースドライバ

7 4 駆動部

9 1 比較回路

30

40

50

|       |          |    |

|-------|----------|----|

| 9 6   | 比較器      |    |

| 9 7   | ラッチ      |    |

| 9 8   | アンドゲート   |    |

| 9 9   | NANDゲート  |    |

| 1 1 7 | 第1外部電源   |    |

| 1 1 8 | 第2外部電源   |    |

| 1 1 9 | 第3外部電源   |    |

| 1 1 1 | 第1ソースライン | 10 |

| 1 1 2 | 第2ソースライン |    |

| 1 1 3 | 第3ソースライン |    |

| 1 2 3 | ソースドライバ  |    |

| 1 2 8 | 制御回路     |    |

| s w 1 | 第1スイッチ   |    |

| s w 2 | 第2スイッチ   |    |

| s w 3 | 第3スイッチ   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【 図 9 】

【 囮 1 0 】

【図11】

【図13】

【図12】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 1 G |

| G 0 9 G | 3/20  | 6 1 1 A |

| G 0 9 G | 3/20  | 6 7 0 L |

| G 0 9 G | 3/20  | 6 4 1 C |

| H 0 5 B | 33/14 | A       |

(72)発明者 廣兼 康浩

大阪府門真市大字門真1006番地 パナソニック セミコンダクターシステムテクノ株式会社内

(72)発明者 西 和義

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 奈良田 新一

(56)参考文献 特開2002-229525 (JP, A)

国際公開第03/060867 (WO, A1)

特開2002-366112 (JP, A)

特開2008-241832 (JP, A)

特開2003-114645 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8