(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4115586号

(P4115586)

(45) 発行日 平成20年7月9日(2008.7.9)

(24) 登録日 平成20年4月25日(2008.4.25)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 29/78

627G

H01L 29/786 (2006.01)

H01L 29/78

627B

H01L 21/20 (2006.01)

H01L 21/20

請求項の数 11 (全 19 頁)

(21) 出願番号

特願平10-100644

(22) 出願日

平成10年3月27日(1998.3.27)

(65) 公開番号

特開平11-284200

(43) 公開日

平成11年10月15日(1999.10.15)

審査請求日

平成17年3月24日(2005.3.24)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 河本 充雄

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

石英基板上にゲイト電極を形成し、

前記ゲイト電極上にゲイト絶縁膜を形成し、

前記ゲイト絶縁膜上にアモルファスシリコン膜からなる第1の半導体薄膜を形成し、

前記第1の半導体薄膜表面を希ガスによってスパッタエッチング処理し、

前記第1の半導体薄膜の一部と接触する様にゲルマニウム膜を形成し、

600 を超えない第1の加熱処理を前記第1の半導体薄膜に施してポリシリコン膜からなる第2の半導体薄膜に変化させ、

700 を超える第2の加熱処理を前記第2の半導体薄膜に施す半導体装置の作製方法であって、

前記スパッタエッチング処理から前記第1の加熱処理までを大気開放せずに行うことを持つ特徴とする半導体装置の作製方法。

## 【請求項 2】

石英基板上にゲイト電極を形成し、

前記ゲイト電極上にゲイト絶縁膜を形成し、

前記ゲイト絶縁膜上にアモルファスシリコン膜からなる第1の半導体薄膜を形成し、

前記第1の半導体薄膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜に開孔部を設け、前記第1の半導体薄膜の一部を露出させ、

前記開孔部において露出した前記第1の半導体薄膜表面を希ガスによってスパッタエッ

10

20

チング処理し、

前記第1の半導体薄膜の一部と接触する様にゲルマニウム膜を形成し、

600 を超えない第1の加熱処理を前記第1の半導体薄膜に施して前記ゲルマニウム膜に接触させた部分から結晶成長させてポリシリコン膜からなる第2の半導体薄膜に変化させ、

700 を超える第2の加熱処理を前記第2の半導体薄膜に施す半導体装置の作製方法であって、

前記スパッタエッティング処理から前記第1の加熱処理までを大気開放せずに行うことを行う特徴とする半導体装置の作製方法。

【請求項3】

10

石英基板上にゲート電極を形成し、

前記ゲート電極上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にアモルファスシリコン膜からなる第1の半導体薄膜を形成し、

前記第1の半導体薄膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜に開孔部を設け、前記第1の半導体薄膜の一部を露出させ、

前記開孔部において露出した前記第1の半導体薄膜表面を希ガスによってスパッタエッティング処理し、

前記第1の半導体薄膜の一部と接触する様にゲルマニウム膜を形成し、

600 を超えない第1の加熱処理を前記第1の半導体薄膜に施して前記ゲルマニウム膜に接触させた部分から結晶成長させてポリシリコン膜からなる第2の半導体薄膜に変化させ、

前記ゲルマニウム膜及び前記マスク絶縁膜を除去し、

700 を超える第2の加熱処理を前記第2の半導体薄膜に施し、

前記第2の半導体薄膜上に、パターニングされた絶縁層を形成し、

前記第2の半導体薄膜及び前記パターニングされた絶縁層を覆う層間絶縁膜を形成し、

前記層間絶縁膜上に、コンタクトホールを介して前記第2の半導体薄膜と接続するソース配線及びドレイン配線を形成する半導体装置の作製方法であって、

前記スパッタエッティング処理から前記第1の加熱処理までを大気開放せずに行うことを行う特徴とする半導体装置の作製方法。

【請求項4】

30

石英基板上にゲート電極を形成し、

前記ゲート電極上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1のアモルファスシリコン膜からなる第1の半導体薄膜を形成し、

前記第1の半導体薄膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜に開孔部を設け、前記第1の半導体薄膜の一部を露出させ、

前記開孔部において露出した前記第1の半導体薄膜表面を希ガスによってスパッタエッティング処理し、

前記第1の半導体薄膜の一部と接触する様にゲルマニウム膜を形成し、

600 を超えない第1の加熱処理を前記第1の半導体薄膜に施して前記ゲルマニウム膜に接触させた部分から結晶成長させてポリシリコン膜からなる第2の半導体薄膜に変化させ、

前記ゲルマニウム膜及び前記マスク絶縁膜を除去し、

700 を超える第2の加熱処理を前記第2の半導体薄膜に施し、

前記第2の半導体薄膜上に、パターニングされた絶縁層を形成し、

前記第2の半導体薄膜及び前記パターニングされた絶縁層上に、第2のアモルファスシリコン膜を形成し、

前記第2のアモルファスシリコン膜上に、微結晶シリコン膜を形成し、

前記微結晶シリコン膜上に導電膜を形成し、当該導電膜をパターニングしてソース配線及びドレイン配線を形成し、

40

50

前記ソース配線及び前記ドレイン配線をマスクとして、前記第2のアモルファスシリコン膜及び前記微結晶シリコン膜をエッチングする半導体装置の作製方法であって、

前記スパッタエッチング処理から前記第1の加熱処理までを大気開放せずに行うことを持つ半導体装置の作製方法。

【請求項5】

請求項3又は請求項4において、前記パターニングされた絶縁層は、酸化シリコン膜であることを特徴とする半導体装置の作製方法。

【請求項6】

請求項1乃至請求項5のいずれか一において、前記ゲルマニウム膜はスパッタ法、プラズマCVD法又は減圧熱CVD法により形成されることを特徴とする半導体装置の作製方法。 10

【請求項7】

請求項1乃至請求項6のいずれか一において、前記第1の加熱処理として、ファーネスアニール、ランプアニール、レーザーアニールのいずれか一を用いることを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至請求項7のいずれか一において、前記第1の加熱処理を不活性雰囲気又は水素雰囲気中で行うことを特徴とする半導体装置の作製方法。

【請求項9】

請求項1乃至請求項8のいずれか一において、前記第1の加熱処理は450～600の温度範囲で行われることを特徴とする半導体装置の作製方法。 20

【請求項10】

請求項1乃至請求項9のいずれか一において、前記第2の加熱処理を酸化性雰囲気中で行うことを特徴とする半導体装置の作製方法。

【請求項11】

請求項1乃至請求項10のいずれか一において、前記第2の加熱処理は800～1050の温度範囲で行われることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【0001】

【発明が属する技術分野】 30

本願発明は半導体薄膜を用いて形成されたボトムゲイト型の薄膜トランジスタ（以下、TFTと略記する）でなる回路を有する半導体装置に関する。特に逆スタガ型TFTを用いた半導体装置に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置を指し、TFTなどの単体素子に限らず、半導体回路や電気光学装置並びにそれらを部品として搭載した電子機器をも含むものとする。

【0003】

【従来の技術】

近年、結晶性を有する半導体薄膜を用いて基板上にTFTを形成し、そのTFTでもって回路を構成した半導体装置が注目されている。半導体薄膜としては、多結晶シリコン（ポリシリコンとも呼ばれる）が最も一般的であるが、 $Si_x Ge_{1-x}$  ( $0 < X < 1$ ) で示される化合物半導体を利用する研究もなされている。 40

【0004】

ポリシリコン膜を用いたTFTは既に実用化の段階まできているが、膜質及び量産性の改善にはまだまだ開発の余地があり、さらなる技術開発が必要である。その様な中で、本出願人はポリシリコンの膜質の向上と量産性の向上とを同時に解決する手段として、特開平7-130652号公報に記載された技術を開示している。

【0005】

同公報に記載された技術は、非晶質半導体膜（代表的にはアモルファスシリコン）に対し 50

てシリコンの結晶化を促進させる触媒元素を添加して、その作用を利用して結晶化させる技術である。その結果、結晶化に必要な温度及び時間が低減され、スループットが飛躍的に向上した。さらに、得られたポリシリコンは非常に高い結晶性を有し、TFTの電気特性も大幅に向ふることが確認された。

**【0006】**

しかしながら、上記触媒元素として最も有効なニッケル(Ni)は金属元素であるため、ポリシリコン中に残存していると TFT 特性に悪影響を与えることが懸念された。そのため、本出願人は結晶化まで完了したら余分なニッケルを除去することが必要と考え、触媒元素のゲッタリングを行う技術を開発した(特開平9-312260号公報)。

**【0007】**

これらの公報に記載された技術は、どちらも結晶化を促進する触媒元素としてニッケル等の金属元素を用いることを主としており、ポリシリコンが得られた後は触媒元素そのものが不必要な存在であった。

**【0008】**

**【発明が解決しようとする課題】**

本願発明は上記問題点を鑑みてなされたものであり、量産性の高い作製方法で結晶性の高い半導体薄膜を形成する技術を提供することを課題とする。そして、その様な半導体薄膜を用いたTFTで回路を構成することで、半導体装置の製造歩留りや製造コストを低減することを課題とする。

**【0009】**

**【課題を解決するための手段】**

本願発明では、シリコンの結晶化を促進させる触媒元素として半導体であるゲルマニウム(Ge)を用いることでゲッタリングの不要なプロセスを提供する。ゲルマニウムはシリコンと非常に近い性質をもつため、シリコン中において非常に整合性の良い状態で存在する。即ち、触媒元素として利用した後で特に除去しなくても TFT 特性に悪影響を与えることがないという利点を有する。

**【0010】**

基本的にはアモルファスシリコン膜に対してゲルマニウムを添加し、ゲルマニウムの触媒作用を利用してアモルファスシリコンを結晶化させる技術である。これにより結晶化の低温化、処理時間の低減及び工程の短縮を同時に実現するものである。

**【0011】**

また、ゲルマニウムはシリコン中において非常に整合性よく存在するため、他の触媒元素を用いた場合に較べて非常に結晶性が高い。ゲルマニウムはその含有量に応じてシリコンのバンドギャップを連続的に変化させるため、ポリシリコンよりもバンドギャップの狭い活性層を形成することができる。この様な活性層を TFT に利用することによりポリシリコンの活性層を用いた TFT よりも高いモビリティ(電界効果移動度)を実現しうる。

**【0012】**

**【発明の実施の形態】**

上記構成からなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

**【0013】**

**【実施例】**

**〔実施例1〕**

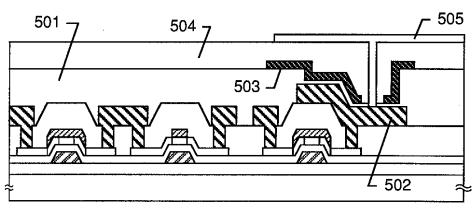

本願発明を用いた TFT の作製工程について図 1、2 を用いて説明する。なお、ここでは回路の基本構成として同一基板上において N TFT (N チャネル型 TFT) と P TFT (P チャネル型 TFT) とを相補的に組み合わせた CMOS 回路を作製する場合を例示する。

**【0014】**

まず、石英基板 101 上に酸化シリコン膜でなる下地膜 102 を設け、その上にゲート電極 103、104 を形成する。なお、図示されないがゲート電極に接続するゲート配線も

10

20

30

40

50

同時に形成される。

**【0015】**

なお、本実施例で石英基板を用いる理由は、後の熱酸化工程において 700 を超える高温処理が行われるので耐熱性の高い基板が必要だからである。従って、石英の代わりにシリコン基板、セラミックス基板又は結晶化ガラスなどを用いることもできる。石英の場合、下地膜は特に設けなくても構わない。

**【0016】**

また、本実施例ではゲイト電極 103、104 となる導電膜として窒化タンタル／タンタル／窒化タンタルの 3 層構造を採用する。また、その膜厚は 200~400 nm の厚さで制御する。本実施例の場合、前述の様に後工程で高温処理があるので耐熱性の高い導電膜を用いる必要がある。他にはクロム、チタン、タングステンなどを用いても良い。10

**【0017】**

そして、その上には  $\text{SiO}_x\text{N}_y$  で示される酸化窒化シリコン膜でなるゲイト絶縁膜 105 を 150nm の厚さに形成する。勿論、酸化シリコン、窒化シリコン又はそれらの積層構造を採用しても良い。

**【0018】**

次に、非晶質半導体膜であるアモルファスシリコン膜を 30nm の厚さに成膜し、パターニングして活性層 106、107 を形成する。アモルファスシリコン膜以外にも  $\text{Si}_x\text{Ge}_{1-x}$  ( $0 < x < 1$ ) で示されるシリコン・ゲルマニウム化合物などの化合物半導体を用いることができる。(図 1 (A))20

**【0019】**

次に、活性層 106、107 上に酸化シリコン膜でなるマスク絶縁膜 108 を形成し、パターニングにより開孔部 109 を形成する。この開孔部 109 は、後にソース領域やドレイン領域となる活性層が露出する様に形成される。

**【0020】**

そして、開孔部 109 が形成されたら、スパッタ法によりゲルマニウム膜 117 を形成して活性層 106、107 とゲルマニウム膜 117 とを接触させる。成膜にはゲルマニウムターゲットを用い、到達圧力  $4 \times 10^{-4}\text{Pa}$  以下、スパッタガスはアルゴン (Ar)、成膜温度は室温、成膜圧力は 0.4Pa、成膜時の DC 電流は

0.4A とする。30

**【0021】**

また、ゲルマニウム膜 110 の成膜は減圧熱 CVD 法やプラズマ CVD 法で行うことも可能である。ゲルマン ( $\text{GeH}_4$ ) は非常に分解しやすいガスであるので、450 度の低温で容易に分解してゲルマニウム膜を形成することができる。

**【0022】**

こうして図 1 (B) の状態が得られる。次に、600 で 12 時間の加熱処理を行い、アモルファスシリコン膜を結晶化させ、結晶半導体膜であるポリシリコン膜へと変化させる。この時、結晶化はまずアモルファスシリコン膜とゲルマニウム膜とが接触した領域(開孔部)で始まり、次第に矢印に示す方向に横方向の結晶成長が進行する。(図 1 (C))40

**【0023】**

なお、600 を超えるとアモルファスシリコン中における自然核発生が増加してしまい、横方向に進行する結晶成長を阻害してしまうため好ましくない。また、この結晶化工程はファーネスアニール、ランプアニール、レーザーアニールのいずれの手段を用いても良い。本実施例では形成された膜の均質性を重視してファーネスアニールを用いる。

**【0024】**

また、熱処理の雰囲気は不活性雰囲気又は水素雰囲気とすることが望ましい。酸素が存在するとゲルマニウム膜が容易に酸化され、不活性な酸化ゲルマニウム膜に変化してしまう。こうなると触媒作用が損なわれて結晶化不良が起こる場合があるの注意が必要である。

**【0025】**

また、本実施例の様にゲルマニウムを触媒元素として横方向に結晶成長させる場合、その50

成長距離が極めて短い点に注意が必要である。図1( C )の場合は丁度ソース領域とドレイン領域となる部分から結晶成長が始まり、チャネル形成領域となる部分の概略中央で成長がぶつかり合う。

#### 【 0 0 2 6 】

従って、少なくともチャネル形成領域の全域を結晶化させるには、ソース - ドレイン間を結ぶ方向におけるチャネル形成領域の幅(チャネル長)の少なくとも $1 / 2$ の距離を成長しなくてはならない。また、結晶成長がチャネル形成領域の概略中央でぶつかり合うため、その部分には粒界(図示せず)が形成される。

#### 【 0 0 2 7 】

本実施例の方式で結晶成長させる場合、熱処理の温度や処理時間によって横方向への成長距離も変化するが、スループットや装置性能を考えると $1 \mu\text{m}$ 程度成長させるのが限界と思われる。そういう意味で、本願発明を適用するデバイスサイズはチャネル長が $2 \mu\text{m}$ 以下、好ましくは $1 \mu\text{m}$ 以下(勿論、ゼロは含まない)であることが好ましいと言える。10

#### 【 0 0 2 8 】

こうして活性層111、112が得られたら、ゲルマニウム膜110を硫酸過水溶液( $\text{H}_2\text{SO}_4 : \text{H}_2\text{O}_2 = 1 : 1$ )で除去した後、マスク絶縁膜108を除去する。その後、900、30minの加熱処理を酸素雰囲気中で行う。(図1( D ))

#### 【 0 0 2 9 】

本願発明において、この高い温度(少なくとも結晶化工程における熱処理温度よりも高い温度)での加熱処理は非常に重要である。この工程を行うことで結晶粒界に存在するトラップ準位の低減と、結晶粒内の欠陥(積層欠陥など)を大幅に低減することができる。20

#### 【 0 0 3 0 】

本出願人は、上記の効果について次の様なモデルを考えている。ポリシリコン膜と下地となる石英(酸化珪素)とでは、熱膨張係数に10倍近くの差がある。従って、アモルファスシリコン膜からポリシリコン膜に変成した時点では、ポリシリコン膜が冷却される時に非常に大きな応力を発生する。

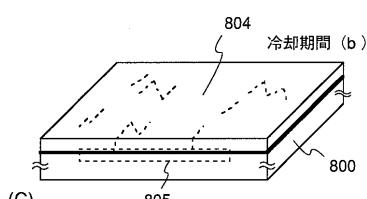

#### 【 0 0 3 1 】

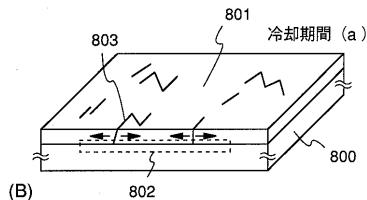

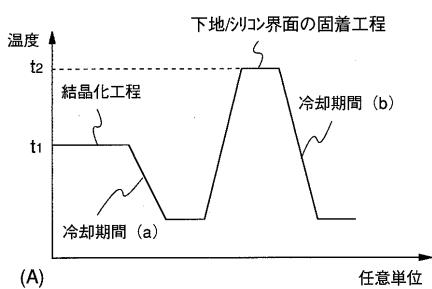

この事について、図8を用いて説明する。図8( A )は結晶化工程後のポリシリコン膜にかかる熱履歴を示している。まず、温度( $t_1$ )で結晶化されたポリシリコン膜は冷却期間( $a$ )を経て室温まで冷やされる。30

#### 【 0 0 3 2 】

ここで図8( B )に示すのは冷却期間( $a$ )にある時のポリシリコン膜であり、800は石英基板、801はポリシリコン膜である。この時、ポリシリコン膜801と石英基板800との界面802における密着性はあまり高くなく、それが原因となって多数の粒内欠陥を発生していると考えられる。

#### 【 0 0 3 3 】

即ち、熱膨張係数の差によって引っ張られたポリシリコン膜801は石英基板800上で非常に動きやすく、引っ張り応力などの力によって積層欠陥や転位などの欠陥803を容易に生じてしまうと考えられる。

#### 【 0 0 3 4 】

こうして得られたポリシリコン膜が図1( B )のポリシリコン膜108に相当する。その後、図8( A )に示す様に温度( $t_2$ )で熱処理工程が行われ、結晶粒内の欠陥(粒内欠陥)が殆ど消滅する。これは熱処理によって格子間に存在する格子侵入型シリコン原子が移動して欠陥を補償するためと考えられる。40

#### 【 0 0 3 5 】

この様な格子侵入型シリコン原子は熱酸化工程において大量に発生するため、上述の結晶化温度を超える温度での熱処理は、酸化性雰囲気中で行うとより効果的に欠陥を除去することが可能である。

#### 【 0 0 3 6 】

こうして熱処理によって粒内欠陥が除去された後、再び冷却期間( $b$ )を経て室温まで冷50

やされる。ここで結晶化工程の後の冷却期間（a）と異なる点は、石英基板800とアニール後のポリシリコン膜804との界面805が非常に密着性の高い状態となっている点である。（図8（C））

#### 【0037】

この様に密着性が高いと石英基板800に対してポリシリコン膜804が完全に固着されるので、ポリシリコン膜の冷却段階においてポリシリコン膜に応力が加わっても欠陥を発生するには至らない。即ち、再び欠陥が発生することを防ぐことができる。

#### 【0038】

この様に、結晶化が終了した後で結晶化工程の加熱処理を超える温度での熱処理を行うことにより、ポリシリコン膜と下地との界面を固着させ、粒内欠陥の除去と同時にその再発生を防ぐことができる。本出願人は、この熱処理工程をシリコン界面の固着工程と呼んでいる。10

#### 【0039】

なお、図8（A）では結晶化工程後に室温まで下げるプロセスを例にとっているが、結晶化が終了したらそのまま温度を上げて固着工程を行うこともできる。その様なプロセスを経ても同様の結晶性を有するポリシリコン膜を得ることが可能である。

#### 【0040】

こうして得られた活性層113、114は、単に結晶化を行っただけの活性層111、112に較べて格段に結晶粒内の欠陥数が少ないという特徴を有している。この欠陥数の差は電子スピン共鳴分析（Electron Spin Resonance：ESR）によってスピン密度の差となつて現れる。20

#### 【0041】

現状では活性層113、114のスピン密度は少なくとも $5 \times 10^{17}$ spins/cm<sup>3</sup>以下（好ましくは $3 \times 10^{17}$ spins/cm<sup>3</sup>以下）であることが判明している。ただし、この測定値は現存する測定装置の検出限界に近いので、実際のスピン密度はさらに低いと予想される。

#### 【0042】

また、触媒元素としてゲルマニウムを利用することで図1（D）に示す工程においてポリシリコン膜の異常酸化が防止される。本出願人によれば、結晶化の触媒としてニッケルを用いた場合、ニッケルシリサイドが集中的に酸化されて異常成長することがある。これは酸化性雰囲気に直接シリコンが触れない様にして熱酸化を行うことで防ぐことができるが、工程数の増加を招いていた。30

#### 【0043】

しかしながら、本願発明ではニッケルを用いずにシリコンとの整合性の高いゲルマニウムを触媒として用いているため、その様な局所的な異常酸化が起こらず、結晶化を終えたポリシリコン膜に対して直接熱処理をかけることができる。

#### 【0044】

なお、本実施例では900、30minの加熱処理としたが、代表的には800～1050（好ましくは850～900）の温度であり、その様な高い温度で熱処理を行う点に特徴がある。この工程では熱酸化機構が粒内欠陥の低減に大きく寄与すると思われる所以、熱酸化が起りやすい条件であることが望ましい。40

#### 【0045】

従って、スループットを考えると熱処理の下限温度は800が好ましく、上限は基板（本実施例では石英）の耐熱性を考慮して1050が好ましい。ただし、ゲルマニウムの融点が930～940であるので、より好ましくは900を上限とすると良い。

#### 【0046】

また、熱処理雰囲気は酸化性雰囲気であることが好ましいが、不活性雰囲気であっても構わない。酸化性雰囲気とする場合、ドライ酸素（O<sub>2</sub>）雰囲気、ウェット酸素（O<sub>2</sub>+H<sub>2</sub>）雰囲気、ハロゲン元素を含む雰囲気（O<sub>2</sub>+HCl等）のいずれかとすれば良い。

#### 【0047】

特に、ハロゲンを含む雰囲気で熱処理を行うと、ハロゲン元素のゲッタリング効果により50

ポリシリコンの格子間に存在する余分なゲルマニウムが揮発性のGeCl<sub>4</sub>の形で除去される。そのため、格子歪みの少ないポリシリコン膜を得るために有効な手段である。

#### 【0048】

さらに、酸化性雰囲気で800~1050の熱処理を行うと熱酸化膜(図面には記載していない)が形成されることでポリシリコン膜自体が薄膜化される。本願発明を実施するときは熱酸化工程による膜減りを考慮して成膜時のアモルファスシリコン膜の膜厚を決定し、最終的にTFTの活性層として利用するときの膜厚は5~50nm(好ましくは15~45nm)となる様に設計すると良い。膜厚が5nm以下となると正常なソース/ドレインコンタクトの形成が困難となり、50nmを超えると薄膜化による効果が薄れてしまう。

#### 【0049】

以上の様な構成の作製方法で得られた本実施例のポリシリコン膜は非常に高い結晶性を有し、薄膜トランジスタの活性層として最適な半導体薄膜である。また、本実施例のポリシリコン膜中にはゲルマニウムが存在する。SIMS(質量二次イオン分析)では $1 \times 10^{14}$ ~ $1 \times 10^{20}$ atoms/cm<sup>3</sup>(典型的には $1 \times 10^{18}$ ~ $1 \times 10^{19}$ atoms/cm<sup>3</sup>)の濃度でゲルマニウムが分布することが確認された。

#### 【0050】

なお、ゲルマニウムの濃度が $1 \times 10^{20}$ ~ $1 \times 10^{22}$ atoms/cm<sup>3</sup>となるとシリコンとゲルマニウムのアロイ化(バンドギャップも変化する)が起こり、Si<sub>x</sub>Ge<sub>1-x</sub>(0<x<1)で示されるシリコンゲルマニウム層になる。本実施例のポリシリコン膜はゲルマニウムが含まれる点では同じであるが、アロイ化していない点でシリコンゲルマニウム膜とは異なる点に特徴がある。

#### 【0051】

こうして活性層113、114が得られたら、120nm厚の酸化シリコン膜を成膜し、パターニングしてスペーサ絶縁層115、116を形成する。スペーサ絶縁層115、116を形成したら、次にn型を付与する不純物元素(本実施例ではリン)を添加して、n型不純物領域117を形成する。(図1(E))

#### 【0052】

本実施例ではプラズマドーピング法を用いてフォスфин(PH<sub>3</sub>)をドーピングガスとして使用する。加速電圧は10keVとし、 $5 \times 10^{14}$ atoms/cm<sup>2</sup>のドーズ量で添加すれば良い。なお、ドーピング条件は本実施例に限定する必要はなく、必要に応じて変更すれば良い。

#### 【0053】

こうして図1(E)の状態が得られたら、レジストマスク118を選択的に設けて、2度目のn型不純物の添加工程を行う。レジストマスク118はN TFTとなる領域では後にチャネル形成領域が形成される領域の上方に形成し、P TFTとなる領域はn型不純物が添加されない様に形成する。(図2(A))

#### 【0054】

ここでは加速電圧を90keVと先程より高めに設定し、ドーズ量は $3 \times 10^{13}$ atoms/cm<sup>2</sup>とする。この加速電圧ではスペーサ絶縁層115、116がマスクとして機能しないため、スペーサ絶縁層の端部(レジストマスク118で隠れない領域)の下のシリコン膜中にも不純物イオンが添加される。

#### 【0055】

この工程によりN TFTのソース領域119、ドレイン領域120、一対のLDD領域(低濃度不純物領域)121、チャネル形成領域122が画定する。なお、2度目のドーピング工程はそのままLDD領域の形成工程でもあるので、LDD領域として最適なドーピング量を実施者が適宜決定する必要がある。

#### 【0056】

次に、レジストマスク118を除去した後、N TFTとなる領域をレジストマスク123で完全に隠し、P型を付与する不純物元素(本実施例ではボロン)を添加する。ここではジボラン(B<sub>2</sub>H<sub>6</sub>)をドーピングガスとして用い、加速電圧は10keV、ドーズ量は1

10

20

30

40

50

$.3 \times 10^{15} \text{ atoms/cm}^2$  とする。(図2(B))

【0057】

この工程ではスペーサー絶縁層116が完全にマスクとして機能するため、その下には全く不純物が添加されず、スペーサ絶縁層116がそのままソース領域124、ドレイン領域125、チャネル形成領域126を画定させる。なお、図1(E)の工程でP TFTとなる領域にもリンが添加されているが、この工程によりp型に反転する。

【0058】

こうしてソース領域、ドレイン領域及びLD領域を形成する不純物イオンの添加工程が終了したら、レジストマスク123を除去し、不純物の活性化工程を行う。本実施例ではエキシマレーザー光を照射することで活性化を行うが、ファーネスアニールやランプアニールを用いても良い。勿論、それらを併用することもできる。(図2(C))

10

【0059】

なお、不純物の活性化工程の前にスペーサ絶縁層115、116を除去してしまって構わない。除去することでレーザー光照射による活性化の効率が大幅に向上升する。しかしながら、スペーサ絶縁層を除去するとチャネル形成領域が露出してしまうためできるだけ残した方が好ましい。

【0060】

次に、酸化シリコン膜でなる層間絶縁膜127を形成し、コンタクトホールを形成して、導電膜でなるソース配線128、129、ドレイン配線130を形成する。この時、ゲイト電極に接続したゲート配線とソース配線(又はドレイン配線)との電気的な接続をとるためのコンタクトホール(図示せず)も同時に形成しておく必要がある。

20

【0061】

そして最後に、全体に対して水素雰囲気中、350~2時間程度の加熱処理を行い、膜中(特にチャネル形成領域中)の不対結合手を水素終端する。以上の工程によって図2(D)に示す様な構造のCMOS回路が完成する。

【0062】

本実施例の工程で作製されたTFTの特徴としては、ソース領域又はドレイン領域にはチャネル形成領域よりも高い濃度でゲルマニウムが存在する点が挙げられる。これは結晶化の際にアモルファスシリコン膜とゲルマニウム膜とを後にソース領域又はドレイン領域となる部分で接触させているためである。

30

【0063】

また、チャネル形成領域は活性層が形成されてからの後工程で結晶性を乱される様な工程を通らないので、スピンドル密度が $5 \times 10^{17} \text{ spins/cm}^3$ 以下であるという優れた結晶性をそのまま残している。

【0064】

本願発明では、以上の様な工程で作製された逆スタガ型TFTでもって回路を構成する。なお、本実施例の作製工程は本願発明を実施するための一例に過ぎず、これに限定されるべきものではない。

【0065】

また、本実施例では行っていないがN TFTとP TFTに対してチャネルドープを行い、しきい値電圧を制御するなどの工夫は実施者が適宜行えば良い。

40

【0066】

本実施例の工程に従って作製された逆スタガ型TFTは、代表的な電気特性であるモビリティ(電界効果移動度)がN TFTで $200 \sim 350 \text{ cm}^2/\text{Vs}$ 、P TFTで $150 \sim 250 \text{ cm}^2/\text{Vs}$ であり、S値(サブスレッショルド係数)がN TFT、P TFTとともに $70 \sim 200 \text{ mV/decade}$ である。

【0067】

なお、本願発明の重要な構成はアモルファスシリコン膜をゲルマニウムを触媒として利用して結晶化させる点にあり、この構成はTFTの構造に限定されるものではない。従って、本願発明をプレーナ型TFTや順スタガ型TFT等のトップゲイト型TFTに適用する

50

ことも可能である。

**【0068】**

**[実施例2]**

本実施例では、実施例1とは異なる工程で作製された逆スタガ型TFTの例について図3を用いて説明する。

**【0069】**

まず、実施例1の工程に従って図1(D)の工程までを終了させる。ここまでで実質的に単結晶と見なせる活性層201、202が得られる。次に、活性層201、202の上に、酸化シリコン膜となるスペーサ絶縁層203、204を形成する。このスペーサ絶縁層の幅が後にチャネル形成領域の幅を決定する。(図3(A))

10

**【0070】**

次に、プラズマCVD法又は減圧熱CVD法を用いてアモルファスシリコン膜205を100nmの厚さに形成し、さらにその上に微結晶シリコン膜206を50nmの厚さに形成する。

(図3(B))

**【0071】**

アモルファスシリコン膜205の成膜条件は、成膜ガスとして100sccmのSiH<sub>4</sub>と300sccmのH<sub>2</sub>とを混合したガスを用い、成膜圧力は0.75torr、印加電力は20Wとする。また、微結晶シリコン膜206の成膜条件は、成膜ガスとして5sccmのSiH<sub>4</sub>と500sccmのH<sub>2</sub>とを混合したガスを用い、成膜圧力は0.75torr、印加電力は300Wとする。

**【0072】**

次に、アモルファスシリコン膜205及び微結晶シリコン膜206に対してn型を付与する不純物元素(本実施例ではリン)の添加を行い、n型のアモルファスシリコン膜207、n型の微結晶シリコン膜208を得る。(図3(C))

20

**【0073】**

この時、リンの添加条件は加速電圧を10keVとし、ドーズ量を $5 \times 10^{14}$ atoms/cm<sup>2</sup>とする。なお、アモルファスシリコン膜207と微結晶シリコン膜208との積層構造であるn型半導体層は、活性層からキャリアを取り出すための電極として機能するため、それに見合った導電性を有していれば良い。従って、本実施例の作製工程で採用した数値に限定する必要はない。

**【0074】**

30

また、最上層に微結晶シリコン膜を設けるのは、後に形成される導電膜からなる配線層とのオーミック接触を取りやすくするためである。アモルファスシリコン膜と導電膜とでは良好なオーミック接触をとることが難しいが、微結晶シリコンと導電膜となら問題ないレベルのオーミック接触が得られる。

**【0075】**

次に、NTFTとなる領域をレジストマスク209で隠し、p型を付与する不純物元素(本実施例ではボロン)を添加する。この工程によりPTFTとなる領域では先程形成されたn型半導体層が反転し、p型のアモルファスシリコン膜210とp型の微結晶シリコン膜211とからなるp型半導体層が形成される。(図3(D))

**【0076】**

40

この時、ボロンの添加条件は加速電圧を10keVとし、ドーズ量を $1.3 \times 10^{15}$ atoms/cm<sup>2</sup>とする。この場合も先程と同様に、活性層からキャリアを取り出すのに十分な導電性を持たせることができれば良い。

**【0077】**

不純物元素の添加工程が終了したら、レジストマスク209を除去して水素雰囲気中で350~1時間のファーネスアニール処理を行い、水素化工程を行う。本実施例ではこの水素化工程が先程添加した不純物の活性化工程を兼ねている。

**【0078】**

なお、本実施例では不純物を添加することによりn型半導体層とp型半導体層とを形成しているが、半導体層を成膜する際に成膜ガスにn型又はP型を付与する不純物を添加して

50

おくことも可能である。

#### 【0079】

次に、ゲイト電極に接続したゲイト配線上の一部（後に形成される配線と電気的に接続させる部分）に開孔部を有するレジストマスク（図示せず）を設け、ドライエッチングにより微結晶シリコン膜、アモルファスシリコン膜及びゲイト絶縁膜を順次エッチングしてコントクトホール（図示せず）を形成する。ドライエッチングは公知の技術範囲で行えば良い。

#### 【0080】

そして、図示しないレジストマスクを除去して、n型半導体層及びp型半導体層の上にアルミニウムを主成分とする材料からなる導電膜を成膜し、パターニングしてソース配線212、213及びドレイン配線214を形成する。なお、この時、先程のコントクトホールを介してゲイト配線とソース配線（ドレイン配線）とが電気的に接続される。

10

#### 【0081】

さらに、これらの配線をマスクとしてn型半導体層及びp型半導体層のエッチングを行う。このエッチングは先程のコントクトホールの形成時と同一条件で構わない。ただし、配線をエッチングしない条件で半導体層をエッチングできる様に条件を設定することが必要である。

#### 【0082】

半導体層のエッチングはスペーサ絶縁層203、204で止まり、ソース配線とドレイン配線とが電気的に完全に分離される。ここまで終了したら、水素雰囲気中で水素化を行い、図3（E）に示す構造のCMOS回路が完成する。

20

#### 【0083】

本実施例の構造は実施例1よりも1枚少ないマスク数（7枚）で逆スタガ型TFTを作製することができる。これにより歩留りの向上と製造コストの低減を図ることができる。勿論、実施例1の工程で作製されたTFTと較べて、本実施例のTFTの電気特性は何ら遜色のないものである。

#### 【0084】

##### 〔実施例3〕

本実施例では、実施例1においてゲルマニウム膜を成膜する代わりに溶液塗布法（スピント法）によりゲルマニウムを含む層を形成する場合について説明する。

30

#### 【0085】

本実施例では開孔部を設けたマスク絶縁膜上にゲルマニウムを含む溶液を塗布し、開孔部の底部に露出したアモルファスシリコン膜にゲルマニウムが保持された状態とする。溶液としては酸化ゲルマニウム（ $GeO_x$ 、代表的には $GeO_2$ ）、塩化ゲルマニウム（ $GeCl_4$ ）、臭化ゲルマニウム（ $GeBr_4$ ）、硫化ゲルマニウム（ $GeS_2$ ）、酢酸ゲルマニウム（ $Ge(C_2H_5CO_2)_2$ ）の水溶液が挙げられる。

#### 【0086】

また、場合によっては溶媒としてエタノール、イソプロピルアルコール等のアルコール系溶媒を用いても良い。

40

#### 【0087】

これらの溶液を100~1000ppmの濃度で作製し、塗布及びスピント乾燥することでアモルファスシリコン膜上にゲルマニウムを含む層が形成される。なお、アモルファスシリコン膜は疎水性を示すため、スピントの前に薄い酸化シリコン膜を形成して濡れ性を高めておくことが好ましい。

#### 【0088】

そして、スピントが終了したら、その状態で結晶化のための加熱処理を行い、ポリシリコン膜を得る。このポリシリコン膜の表面には高濃度にゲルマニウムが存在するので、フッ酸等のエッチャントで洗浄しておくと良い。

#### 【0089】

本実施例の構成を実施例1や実施例2に適用することで、容易に図2（D）や図3（E）

50

に示す様な TFT を作製することができる。

**【 0 0 9 0 】**

**[ 実施例 4 ]**

アモルファスシリコン膜に対してゲルマニウムを添加するに際して、イオンプランテーション法、プラズマドーピング法またはレーザードーピング法を利用することも可能である。

**【 0 0 9 1 】**

励起ガスとしてはゲルマン ( $\text{GeH}_4$ ) を用いれば良く、アモルファスシリコン膜中へは  $1 \times 10^{14} \sim 5 \times 10^{19} \text{ atoms/cm}^3$  (代表的には  $1 \times 10^{16} \sim 1 \times 10^{18} \text{ atoms/cm}^3$  ) の濃度でゲルマニウムが添加される様に調節することが好ましい。

10

**【 0 0 9 2 】**

アモルファスシリコン膜中に添加するゲルマニウムは  $1 \times 10^{14} \text{ atoms/cm}^3$  以上 (好ましくは  $1 \times 10^{16} \text{ atoms/cm}^3$  以上) でないと触媒として結晶化の助長効果を有効に利用することができない。また、添加量が多すぎるとゲルマニウム膜の物性に近くなり、TFT 特性が低下する。そのため、 $5 \times 10^{19} \text{ atoms/cm}^3$  以下、好ましくは  $1 \times 10^{18} \text{ atoms/cm}^3$  以下ぐらいに抑えておくことが望ましい。

**【 0 0 9 3 】**

こうして膜中にゲルマニウムが添加されたアモルファスシリコン膜は 450 ~ 650 の加熱処理により容易に結晶化する。本実施例で得られたポリシリコン膜はシリコン原子とゲルマニウム原子が置換された結合を多く含み、いわゆるシリコンゲルマニウム ( $\text{Si}_x \text{ Ge}_{1-x}$  で表される) になると思われる。

20

**【 0 0 9 4 】**

この様なシリコンゲルマニウム膜はシリコン膜よりも狭いバンドギャップを有するため、キャリア (電子または正孔) の移動度が向上することが知られている。ただし、ゲルマニウムの含有量によっては大きく TFT 特性が変化する場合もあるので注意が必要である。

**【 0 0 9 5 】**

本実施例の構成を実施例 1 や実施例 2 に適用することで、容易に図 2 (D) や図 3 (E) に示す様な TFT を作製することができる。

**【 0 0 9 6 】**

**[ 実施例 5 ]**

30

本実施例では活性層の両端から結晶成長させた実施例 1 と異なり、活性層の片側の端部 (ソース領域又はドレイン領域となる部分) から結晶成長させる場合について図 4 を用いて説明する。

**【 0 0 9 7 】**

まず、実施例 1 の工程に従ってマスク絶縁膜 401 の形成までを終了したら、パターニングにより開孔部 402 を形成する。この開孔部 402 は、後にソース領域となる部分のみに選択的に設け、活性層の片側端部のみが露出する様に形成される。そして、その上にゲルマニウム膜 403 をプラズマ CVD 法により形成する。(図 4 (A))

**【 0 0 9 8 】**

次に、この状態で 600 ~ 8 時間の加熱処理を行い、アモルファスシリコン膜をポリシリコン膜に結晶化させる。この時、結晶成長は矢印の方向に進行し、ポリシリコン膜からなる活性層 403、404 が形成される。(図 4 (B))

40

**【 0 0 9 9 】**

なお、実施例 1 で述べた様に、横方向への成長距離は  $1 \mu\text{m}$  程度が限界であるので本実施例ではチャネル長が少なくとも  $1 \mu\text{m}$  以下、好ましくは  $0.5 \mu\text{m}$  以下 (勿論、ゼロは含まれない) であることが望ましい。

**【 0 1 0 0 】**

こうして図 4 (B) の状態が得られたら、実施例 1 と同様の工程を経て TFT を完成させれば良い。勿論、実施例 2 の様な構造とすることもできるし、実施例 3、4 の構成を適用することも可能である。

50

## 【0101】

## 〔実施例6〕

ゲルマニウムを触媒元素として用いた結晶化工程を行う場合、結晶化時の処理雰囲気\_ADDRESS\_に存在する酸素量に注意する必要がある。実施例1でも説明した様にゲルマニウムは容易に酸化されて不活性な酸化ゲルマニウムになってしまうので、酸素を極力排除することが必要である。

## 【0102】

そのため、1 アモルファスシリコン膜の表面を清浄化する、2 ゲルマニウム膜を成膜する、3 加熱処理により結晶化する、という工程を大気開放しないで連続的に行うことが望ましい。

10

## 【0103】

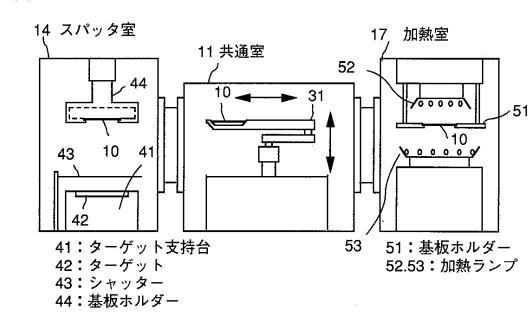

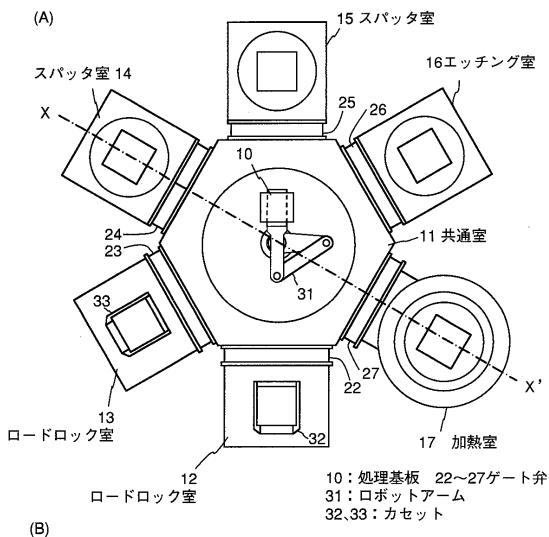

本実施例ではこの様な工程をマルチチャンバー（クラスターツール）方式の処理装置を用いて行う。ここで本実施例で用いる処理装置を図9に示す。なお、図9(A)は上面図であり、図9(B)は破線X-X'での断面構成図を示す。

## 【0104】

11は装置全体となる共通室、12、13はロードロック室、14、15はスパッタ室、16はエッチング室であり、17は加熱室であり、各室12~17はゲート弁を介して共通室11に連結されており、室11~17ごとに気密性を保持できるようになっている。

20

## 【0105】

また各室11~17ごとに減圧状態にするための排気系（図示せず）と、雰囲気制御用のガスやスパッタガスを供給するためのガス供給系（図示せず）とが設けられている。スパッタ室14、15、エッチング室16の排気系には到達真空度 $10^{-6}$ Paを実現するためにクライオポンプを備えている。

## 【0106】

共通室11には処理基板10を室12~17へ移動するためのロボットアーム31が設かれている。ロボットアーム31の基板保持部分は矢印で示すように3次元的に移動自在とされている。また、ロボットアーム31は処理基板10の素子形成面が下向きに搬送されるフェイスダウン方式となっており、素子形成面にパーティクル等のゴミが付着するのを防いでいる。

30

## 【0107】

ロードロック室12、13は処理基板10を装置外部に搬入・搬出するための室である。処理基板10は基板搬送カセット32、33に収納されて、装置に搬入・搬出される。

## 【0108】

スパッタ室14、15はほぼ同じ構造を有しており、図9(B)を用いてスパッタ室14の構成を説明する。本実施例ではスパッタ室14又は15でゲルマニウム膜が成膜される。

## 【0109】

スパッタ室14には、ターゲット支持台41、ターゲット42、シャッター43、フェイスダウン方式の基板ホルダー44が設けられている。基板ホルダー44は処理基板10の端部数ミリを支持するように設計されており、基板10の汚染をできるだけ小さくしている。

40

## 【0110】

また、ターゲット41を介してターゲットには図示しないDC電源からDC電流が供給される。スパッタ室14、15で成膜する材料によって、ガス供給系等の仕様が決められる。

## 【0111】

また、本実施例においては、エッチング室16はスパッタ室14、15とほぼ同様な構成であるが、DC電源の代わりにRF電源が接続されており、基板10にRF電力を供給して負のセルフバイアス電圧が印加される様になっている。

50

**【0112】**

本実施例ではエッティング室16でアモルファスシリコン膜の表面を希ガス（アルゴン、ヘリウムなど）で軽くスパッタする（表面層をエッティングすることになる）ことで表面クリーニングを行い、アモルファスシリコン膜の表面を清浄化している。

**【0113】**

加熱室17は結晶化工程用の室であり、スループットの点から加熱手段としてRTA処理を可能な構成とした。フェイスダウン方式の基板ホルダー51と、基板10を両面から加熱するために、赤外光を発する加熱ランプ52、53とが設けられている。加熱ランプ53が基板主表面を加熱するメインランプとなる。

**【0114】**

本実施例の、図9に示す処理装置の使用方法を以下に説明する。被処理基板（アモルファスシリコン膜上にマスク絶縁膜を形成した基板）10をロードロック室12からスパッタ装置内に搬送する。ロードロック室12を減圧状態にした後に窒素雰囲気とする。共通室11、スパッタ室14、15、エッティング室16も減圧状態にされ、到達圧力 $10^{-6}$ Paとされている。

10

**【0115】**

ゲート弁22を開放し、ロボットアーム31によって基板10をエッティング室16に移動する。なお、雰囲気の混合を避けるため、2つのゲート弁22、27は同時に開放しないように制御される。以下も同様である。エッティング室16の基板ホルダーに基板を固定し、基板にRF電力を印加しながらアルゴンガスによってスパッタ処理を行う。スパッタ処理によってアモルファスシリコン膜表面の不純物や自然酸化膜が除去される。

20

**【0116】**

次に、基板10をスパッタ室14に移動してゲルマニウム膜を成膜する。そして加熱室17に基板を移動する。加熱室17は窒素雰囲気とし、加熱ランプ52、53によって基板を加熱して、アモルファスシリコン膜を結晶化させる。結晶化工程が終了したら、基板をロードロック室13のカセット33内に移動し、スパッタ装置から搬出する。

**【0117】**

また、結晶化工程の前に、ゲルマニウム膜の酸化をできるだけ抑制するために、スパッタ室14でゲルマニウム膜を成膜した後、スパッタ室15でゲルマニウム表面に窒化シリコン膜、酸化窒化シリコン膜等の絶縁膜を成膜して、ゲルマニウム表面を覆ってしまうことも有効である。

30

**【0118】**

ゲルマニウム膜の表面を絶縁膜で覆うことで処理雰囲気に直接触れさせないで結晶化工程を行う、という構成は本実施例の様にマルチチャンバー方式の処理装置で用いるだけでなく、結晶化工程を外部の電熱炉で行う必要がある場合において特に有効な技術である。勿論、この構成を実施例1～5に示した構成と組み合わせることは容易である。

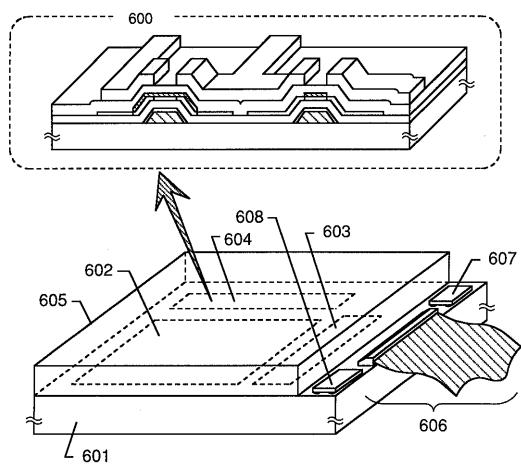

**【0119】****〔実施例7〕**

本実施例では、本願発明を用いてガラス基板上に複数のTFTを作製し、ドライバー回路と画素マトリクス回路とを一体形成したアクティブマトリクス型液晶表示装置を作製した場合の例について図5に示す。

40

**【0120】**

本実施例の構造は、実施例1の工程に多少の追加工程を加えるだけで実現することができる。まず、実施例1の工程に従って図2(D)の状態を得る。この時、画素マトリクス回路となる領域にはマトリクス状に配列されたNTFTを作製しておく。

**【0121】**

その上に第1の平坦化膜501として50nmの窒化シリコン膜、25nmの酸化シリコン膜及び1μm厚のポリイミド膜を順次積層した積層膜を形成する。ポリイミド以外にもアクリルなどの他の有機樹脂材料を用いても良い。

**【0122】**

50

次に、画素マトリクス回路を構成するTFTのドレイン電極502の上に開口部を設ける。この開口部は上から順にポリイミド膜、酸化シリコン膜までをエッティングし、最下層の窒化シリコン膜は残しておく。開口部を形成したら、チタンなどの導電膜でなるブラックマスク503を形成する。

【0123】

そして、さらに第2の平坦化膜504としてポリイミド膜を500nmの厚さに形成する。第2の平坦化膜504を形成したら、第1及び第2の平坦化膜にコンタクトホールを開けて透明導電膜（代表的にはITO膜）でなる画素電極505を形成する。

【0124】

この時、ドレイン電極502とブラックマスク503との間では、前述の50nm厚の窒化シリコン膜を誘電体とする補助容量が形成される。本実施例の構造ならばTFT上に補助容量が形成されるので、開口率を損なうことがない。10

【0125】

以上の様な工程を経て、図5に示す様な構造が完成する。実際のアクティブマトリクス型液晶表示装置は、画素電極を形成した後に配向膜を成膜し、対向電極との間に液晶を挟持して完成する。これらセル組み工程は公知の手段を用いて行えば良いので説明は省略する。10

【0126】

こうして形成されたアクティブマトリクス型液晶表示装置の外観を模式的に図6に示す。20

図6において、601は絶縁表面を有する基板、602は画素マトリクス回路、603はソースドライバー回路、604はゲイドドライバー回路、605は対向電極、606はFPC（フレキシブルプリントサーキット）、607、608は外付けされたICチップである。

【0127】

この時、例えばソースドライバー回路603やゲイドドライバー回路604は600で示される様なCMOS回路で構成される。

【0128】

また、本実施例において画素電極を反射率の高い材料とすれば容易に反射型液晶表示装置を作製することができる。

【0129】

以上の様に、本願発明を利用して作製されたTFTを用いて様々な回路を形成することで、基板上に回路を有する電気光学装置を実現することができる。なお、本実施例では液晶表示装置を例に挙げているが、EL（エレクトロルミネッセンス）表示装置やイメージセンサなどを作製することも可能である。30

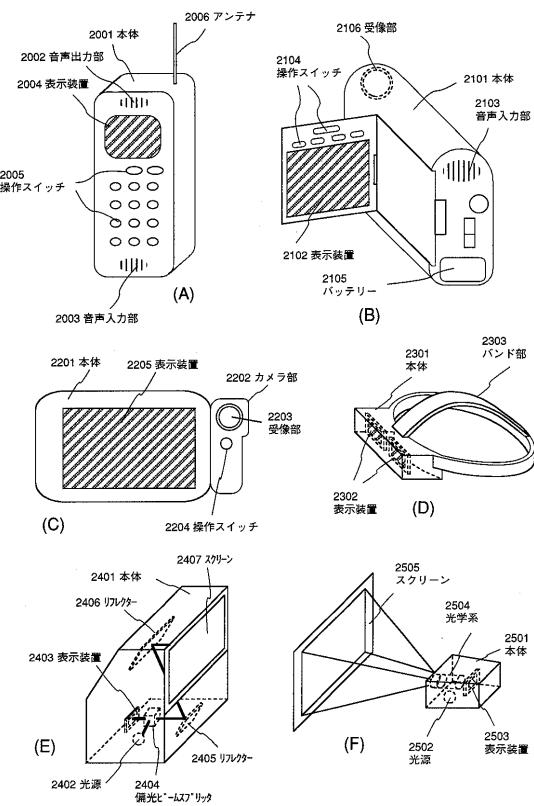

【0130】

〔実施例8〕

実施例1に示した様な電気光学装置は、様々な電子機器のディスプレイとして利用される。その様な電子機器としては、ビデオカメラ、スマートフォン、プロジェクター、プロジェクションTV、ヘッドマウントディスプレイ、カーナビゲーション、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話等）などが挙げられる。それらの一例を図7に示す。40

【0131】

図7(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示装置2004、操作スイッチ2005、アンテナ2006で構成される。本願発明を表示装置2004等に適用することができる。

【0132】

図7(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明を表示装置2102に適用することができる。

【0133】

10

20

30

40

50

図7( C )はモバイルコンピュータ( モービルコンピュータ )であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本願発明は表示装置2205等に適用できる。

【 0134 】

図7( D )はヘッドマウントディスプレイであり、本体2301、表示装置2302、バンド部2303で構成される。本発明は表示装置2302に適用することができる。

【 0135 】

図7( E )はリア型プロジェクターであり、本体2401、光源2402、表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本発明は表示装置2403に適用することができる。 10

【 0136 】

図7( F )はフロント型プロジェクターであり、本体2501、光源2502、表示装置2503、光学系2504、スクリーン2505で構成される。本発明は表示装置2503に適用することができる。

【 0137 】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。特に、携帯性を重視した電子機器には非常に効果的であると言える。

【 0138 】

【 発明の効果 】

本願発明を利用することで、量産性の高い作製工程で、結晶性の高い半導体薄膜を作製することが可能となる。そして、その様な半導体薄膜を活性層とする高性能なTFTを用いた回路を有する半導体装置を実現することができる。 20

【 図面の簡単な説明 】

- 【 図1 】 薄膜トランジスタの作製工程を示す図。

- 【 図2 】 薄膜トランジスタの作製工程を示す図。

- 【 図3 】 薄膜トランジスタの作製工程を示す図。

- 【 図4 】 薄膜トランジスタの作製工程を示す図。

- 【 図5 】 アクティブマトリクス型液晶表示装置の構成を示す図。

- 【 図6 】 アクティブマトリクス型液晶表示装置の構成を示す図。

- 【 図7 】 電子機器の構成を示す図。 30

- 【 図8 】 固着工程の概略を説明するための図。

- 【 図9 】 マルチチャンバー方式の処理装置の構成を示す図。

【図1】

101: 石英基板 102: 下地膜 103、104: ゲート電極

105: ゲート絶縁膜 106、107: 活性層 108: マスク絶縁膜

109: 開孔部 110: ゲート電極膜 111、112: 活性層

113、114: 活性層 115、116: ハーフ絶縁層

117: n型不純物領域

【図2】

118、123: レジストマスク 119、124: ソース領域

120、125: ドレイン領域 121: LDD領域(n-ch)

122、126: チャネル形成領域 127: 層間絶縁膜

128、129: ソース配線 130: ドレイン配線

【図3】

201、202: 活性層 203: ハーフ絶縁層

205: アモルファスシリコン膜 206: 微結晶シリコン膜

207: n型アモルファスシリコン膜 208: n型微結晶シリコン膜

209: レジストマスク 210: p型アモルファスシリコン膜

211: p型微結晶シリコン膜 212、213: ソース配線

214: ドレイン配線

【図4】

401: マスク絶縁膜 402: 開孔部 403、404: ホーリシリコン膜

【図5】

501: 第1の平坦化膜 502: 画素TFTのドレイン電極

503: ブラックマスク 504: 第2の平坦化膜 505: 画素電極

【図6】

601: 絶縁表面を有する基板 602: 画素マトリクス回路

603: ソースドライバ-回路 604: ゲイドドライバ-回路 605: 対向基板

606: FPC 607、608: ICチップ

【図7】

【図8】

【図9】

10: 处理基板 22~27ゲート弁

31: ロボットアーム

32,33: カセット

41: ターゲット支持台

42: ターゲット

43: シャッター

44: 基板ホルダー

---

フロントページの続き

(56)参考文献 特開平10-012889(JP,A)

特開平06-349734(JP,A)

特開平07-176479(JP,A)

特開平06-267978(JP,A)

特開平07-161995(JP,A)

特開平08-172195(JP,A)

特開平09-289167(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

H01L 21/20