(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6180138号

(P6180138)

(45) 発行日 平成29年8月16日(2017.8.16)

(24) 登録日 平成29年7月28日(2017.7.28)

|              |           |             |     |

|--------------|-----------|-------------|-----|

| (51) Int.Cl. | F 1       |             |     |

| HO4N 5/355   | (2011.01) | HO4N 5/355  | 540 |

| HO4N 5/374   | (2011.01) | HO4N 5/374  |     |

| HO4N 5/3745  | (2011.01) | HO4N 5/3745 |     |

| HO4N 5/235   | (2006.01) | HO4N 5/235  | 500 |

請求項の数 15 (全 26 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-48218 (P2013-48218)    |

| (22) 出願日  | 平成25年3月11日 (2013.3.11)        |

| (65) 公開番号 | 特開2014-175933 (P2014-175933A) |

| (43) 公開日  | 平成26年9月22日 (2014.9.22)        |

| 審査請求日     | 平成28年3月10日 (2016.3.10)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100094112<br>弁理士 岡部 譲                      |

| (74) 代理人  | 100096943<br>弁理士 白井 伸一                     |

| (74) 代理人  | 100101498<br>弁理士 越智 隆夫                     |

| (74) 代理人  | 100107401<br>弁理士 高橋 誠一郎                    |

| (74) 代理人  | 100106183<br>弁理士 吉澤 弘司                     |

| (74) 代理人  | 100128668<br>弁理士 斎藤 正巳                     |

最終頁に続く

(54) 【発明の名称】撮像素子、その駆動方法および撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

出力可能な信号量の異なる少なくとも第1の光電変換素子と第2の光電変換素子のうちの少なくとも一つで構成される画素の2次元配列を有する撮像素子の駆動方法において、

前記第1の光電変換素子および第2の光電変換素子から信号を読み出すために各画素を駆動する駆動ステップと、

前記駆動ステップを制御し、前記信号が読み出される光電変換素子が前記第1の光電変換素子と第2の光電変換素子のいずれであるかに従って、各画素を駆動する駆動タイミングを変更する制御ステップと、

を備え、

前記画素の2次元配列が、同一列の画素を共通に接続する出力線を含む場合に、前記駆動ステップは、各画素の光電変換素子から、前記出力線に信号を読み出すための駆動パルスを生成するステップを含み、前記制御ステップは、前記第1の光電変換素子から信号を読み出すための前記駆動パルスの期間と前記第2の光電変換素子から信号を読み出すための前記駆動パルスの期間を、各光電変換素子の出力可能な信号量に従って設定することを特徴とする撮像素子の駆動方法。

## 【請求項 2】

前記制御ステップは、前記出力可能な信号量が大きい光電変換素子の前記駆動パルスの期間を、前記出力可能な信号量が小さい光電変換素子の前記駆動パルスの期間よりも長く設定することを特徴とする請求項1に記載の撮像素子の駆動方法。

**【請求項 3】**

前記駆動ステップは、前記少なくとも第1の光電変換素子と第2の光電変換素子のいずれかで構成された画素の光電変換素子から前記出力線に信号を読み出すための前記駆動パルスを生成することを特徴とする請求項1又は2に記載の撮像素子の駆動方法。

**【請求項 4】**

前記駆動ステップは、前記少なくとも第1の光電変換素子と第2の光電変換素子とで構成された画素の各光電変換素子から前記出力線に信号を順次読み出すための前記駆動パルスを生成することを特徴とする請求項1又は2に記載の撮像素子の駆動方法。

**【請求項 5】**

前記第1の光電変換素子の前記出力可能な信号量が、前記第2の光電変換素子よりも大きいとき、前記駆動ステップは、前記第1の光電変換素子と複数の前記第2の光電変換素子で構成された画素の各光電変換素子から前記出力線に信号を読み出すための前記駆動パルスを生成し、前記駆動パルスは第2の光電変換素子それぞれの信号を順次読み出すための第1の駆動パルスと、前記第1の光電変換素子の信号を、前記複数の第2の光電変換素子のいずれかの信号の読み出しと並行して読み出すための第2の駆動パルスを含むことを特徴とする請求項1又は2に記載の撮像素子の駆動方法。10

**【請求項 6】**

出力可能な信号量の異なる少なくとも第1の光電変換素子と第2の光電変換素子のうちの少なくとも一つで構成される画素の2次元配列を有する撮像素子において、

前記2次元配列の同一列の画素に共通に接続する出力線と、20

各光電変換素子の信号を前記出力線に読み出すために各画素を駆動する駆動手段と、

前記駆動手段による駆動に従い、各画素の光電変換素子の信号を前記出力線に読み出す読み出し手段と、

前記駆動手段を制御し、駆動された各画素の光電変換素子が前記第1の光電変換素子と第2の光電変換素子のいずれであるかに従って、前記読み出し手段の駆動タイミングを変更する制御手段と、

を備え、

前記駆動手段は、前記読み出し手段を駆動するための駆動パルスを生成し、前記制御手段は、前記読み出し手段が前記第1の光電変換素子から信号を読み出すときの前記駆動パルスの期間と前記第2の光電変換素子から信号を読み出すときの前記駆動パルスの期間を、各光電変換素子の出力可能な信号量に従って設定することを特徴とする撮像素子。30

**【請求項 7】**

各画素は、前記第1の光電変換素子と複数の前記第2の光電変換素子で構成された画素であり、前記出力線は、第1の出力線と第2の出力線を含み、前記読み出し手段は、前記第1の光電変換素子の信号を前記第1の出力線に読み出し、前記複数の第2の光電変換素子の信号を前記第2の出力線に読み出し、前記複数の第2の光電変換素子は、前記読み出し手段を共有していることを特徴とする請求項6に記載の撮像素子。

**【請求項 8】**

前記制御手段は、前記出力可能な信号量が大きい光電変換素子の前記駆動パルスの期間を、前記出力可能な信号量が小さい光電変換素子の前記駆動パルスの期間よりも長く設定することを特徴とする請求項6に記載の撮像素子。40

**【請求項 9】**

前記2次元配列の各行の画素は、前記少なくとも第1の光電変換素子と第2の光電変換素子のいずれかで構成された画素であることを特徴とする請求項6又は8に記載の撮像素子。

**【請求項 10】**

各画素は、前記少なくとも第1の光電変換素子と第2の光電変換素子とで構成された画素であり、前記駆動手段は、前記読み出し手段が前記各画素の各光電変換素子の信号を前記出力線に順次読み出すための前記駆動パルスを生成することを特徴とする請求項6又は8に記載の撮像素子。50

**【請求項 1 1】**

前記読み出し手段は、前記各画素の各光電変換素子について共通であることを特徴とする請求項1 0に記載の撮像素子。

**【請求項 1 2】**

前記第1の光電変換素子の前記出力可能な信号量は、前記第2の光電変換素子よりも大きく、各画素は、前記第1の光電変換素子と複数の前記第2の光電変換素子で構成された画素であり、前記駆動手段は、前記読み出し手段が前記各画の各光電変換素子の信号を前記出力線に読み出すための前記駆動パルスを生成し、前記駆動パルスは第2の光電変換素子それぞれの信号を順次読み出すための第1の駆動パルスと前記第1の光電変換素子の信号を、前記複数の第2の光電変換素子のいずれかの信号の読み出しと並行して読み出すための第2の駆動パルスを含むことを特徴とする請求項6又は8に記載の撮像素子。10

**【請求項 1 3】**

被写体の光学像を形成する光学系と、

前記光学像を撮像する、請求項6乃至1 2のいずれか一項に記載の撮像素子と、

前記撮像素子から読み出された信号を処理する信号処理手段と、

備え、

前記信号処理手段は、前記信号のダイナミックレンジを拡大するための信号処理を行うことを特徴とする撮像装置。

**【請求項 1 4】**

出力可能な信号量の異なる少なくとも第1の光電変換素子と第2の光電変換素子のうちの少なくとも一つで構成される画素の2次元配列を有する撮像素子を制御するプログラムであり、20

コンピュータを、

各光電変換素子の信号を、前記2次元配列の各列の画素に共通に接続する出力線に読み出すために各画素を駆動する駆動手段、

前記駆動手段による駆動に従い、各画素の光電変換素子の信号を前記出力線に読み出す読み出し手段、

前記駆動手段を制御し、駆動された各画素の光電変換素子が前記第1の光電変換素子と第2の光電変換素子のいずれであるかに従って、前記読み出し手段の駆動タイミングを変更する制御手段、30

として機能させ、

前記駆動手段は、前記読み出し手段を駆動するための駆動パルスを生成し、前記制御手段は、前記読み出し手段が前記第1の光電変換素子から信号を読み出すときの前記駆動パルスの期間と前記第2の光電変換素子から信号を読み出すときの前記駆動パルスの期間を、各光電変換素子の出力可能な信号量に従って設定することを特徴とするプログラム。

**【請求項 1 5】**

請求項1 4のプログラムを記憶したコンピュータが読み取り可能な記憶媒体。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は撮像素子に関し、特に蓄積信号量が異なる光電変換素子を有する撮像素子に関する。40

**【背景技術】****【0 0 0 2】**

従来、デジタルカメラ等の撮像装置では、銀塩カメラにおける撮像フィルムの代わりとして、撮像素子が用いられている。近年、デジタルカメラ等に用いられる撮像素子において、画素の構成を工夫することにより、通常の撮像機能に加えて、さまざまな付加機能を持たせることが提案されている。例えば、第1の例として、撮像素子のダイナミックレンジを拡大させることが挙げられる。

**【0 0 0 3】**

50

従来の撮像素子は、人間の目と比較して、ダイナミックレンジが狭いことが知られている。この問題に対し、特許文献1では、従来の撮像素子と比較してダイナミックレンジを拡大させた撮像素子が開示されている。具体的には、撮像装置に、感度の異なる22の光電変換素子を設け、これら2つの光電変換素子を用いて取得した信号を合成することにより、ダイナミックレンジの拡大を実現させている。

#### 【0004】

特許文献2においても、特許文献1と同様、撮像装置に、感度の異なる光電変換素子を設けることにより、従来の撮像素子と比較してダイナミックレンジを拡大させた撮像素子が開示されている。特許文献1における撮像素子との違いは、合成に用いる信号を選択するための単位画素に含まれる、感度の異なる光電変換素子の数をより多くしたことである。

10 特許文献2に示されているように、単位画素内の感度の異なる光電変換素子が多いほど、ダイナミックレンジを拡大させる度合いを細かく調整できるようになる。すなわち、単位画素内に設けられた異なる感度の光電変換素子の個数が多いほど、被写体に応じて適したダイナミックレンジを得易くなると言える。

#### 【0005】

第2の例としては、撮像素子に、焦点検出素子としての機能も持たせることが挙げられる。従来の撮像装置においては、撮影レンズの焦点調節状態を検出し、検出結果をもとに自動で焦点調節を行う機能が広く搭載されているが、焦点調節状態を検出するための焦点検出素子を、撮像素子とは別に設けることが一般的であった。

#### 【0006】

これに対し、特許文献3では、瞳分割位相差方式によって、焦点検出素子としても使用可能な撮像素子が開示されている。具体的には、撮像素子における単位画素内の受光領域を、複数の領域に分割し、各々の領域から、撮像装置の光学系における異なる瞳面を通った光の信号を得るようにすることで、位相の異なる複数の信号を得る。これらの信号を、撮像、及び、焦点検出に用いることで、撮像素子を焦点検出素子として用いることを可能にしている。特許文献3に示されているように、単位画素内の領域の分割数が多いほど、焦点検出の解像度が向上する。すなわち、単位画素内に設けられた光電変換素子の数が多いほど、より正確な焦点検出を行うことが可能となる。また、撮像素子の全画素をこのような単位画素とすることによって、撮像領域における任意の場所で焦点検出を行うことが可能となる。

30

#### 【先行技術文献】

##### 【特許文献】

##### 【0007】

【特許文献1】特開2000-125209号公報

【特許文献2】特開2011-114680号公報

【特許文献2】特開2007-158692号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0008】

しかしながら、上述の特許文献に開示された従来技術では、付加機能の性能を向上させようとするほど、単位画素あたりに必要な光電変換素子の数が増加するため、撮像素子に含まれる光電変換素子の数が大幅に増加してしまう。このように増加した光電変換素子から信号を読み出そうとすると、光電変換素子の総数が増えるにしたがって、1フレーム分の信号の読み出しにかかる時間も増加してしまう。

40

そこで、本発明の目的は、蓄積する信号量の異なる光電変換素子を備えた撮像素子において、信号の読み出し時間を短縮することを可能にした撮像素子を提供することである。

##### 【課題を解決するための手段】

##### 【0009】

本発明によれば、出力可能な信号量の異なる少なくとも第1の光電変換素子と第2の光電変換素子のうちの少なくとも一つで構成される画素の2次元配列を有する撮像素子の駆

10

20

30

40

50

動方法において、第1の光電変換素子および第2の光電変換素子から信号を読み出すために各画素を駆動する駆動ステップと、駆動ステップを制御し、信号が読み出される光電変換素子が第1の光電変換素子と第2の光電変換素子のいずれであるかに従って、各画素を駆動する駆動タイミングを変更する制御ステップと、を備え、画素の2次元配列が、同一列の画素を共通に接続する出力線を含む場合に、駆動ステップは、各画素の光電変換素子から、出力線に信号を読み出すための駆動パルスを生成するステップを含み、制御ステップは、第1の光電変換素子から信号を読み出すための駆動パルスの期間と第2の光電変換素子から信号を読み出すための駆動パルスの期間を、各光電変換素子の出力可能な信号量に従って設定することを特徴とする撮像素子の駆動方法が提供される。

## 【発明の効果】

10

## 【0010】

本発明によれば、蓄積する信号量の異なる光電変換素子を備えた撮像素子において、駆動パルスの間隔を適宜設定することにより、信号読み出しにかかる時間の短縮を可能にした撮像素子を提供することが可能となる。

## 【図面の簡単な説明】

## 【0011】

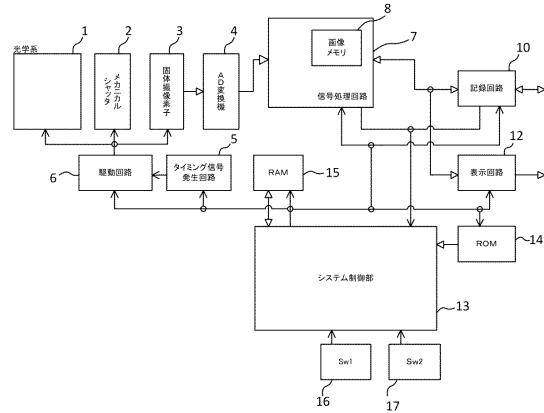

【図1】本発明の実施形態に係る撮像素子を適用した撮像装置の構成例を示すブロック図。

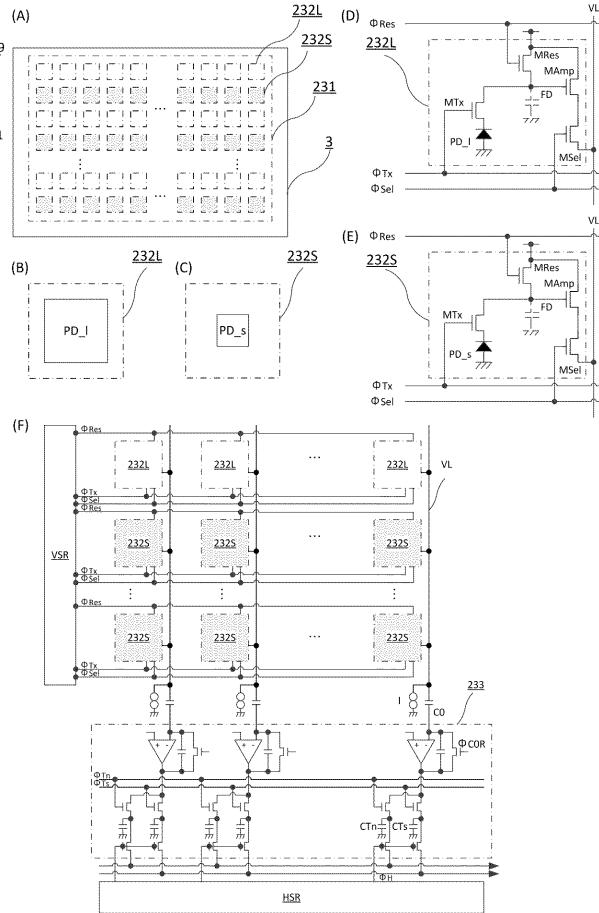

## 【図2】本発明の第1の実施例に係る撮像素子の構成を概略的に示す図。

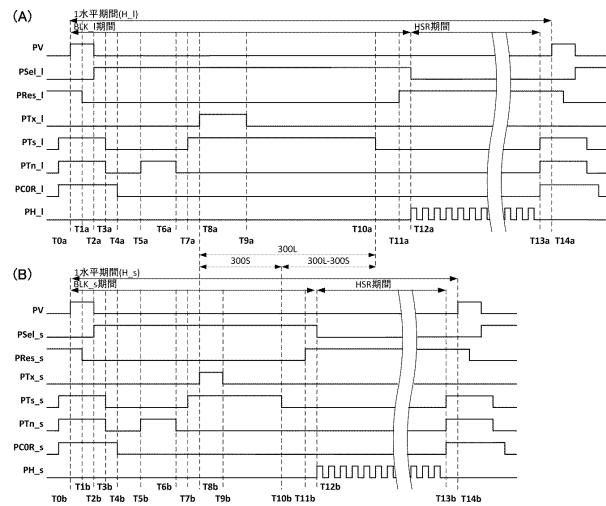

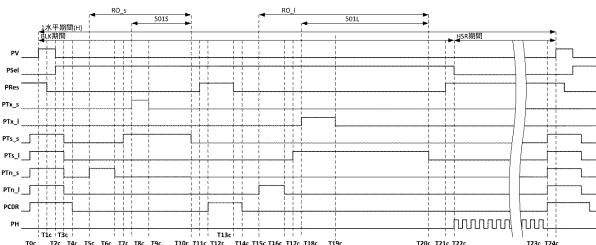

## 【図3】本発明の第1の実施例に係る撮像素子の駆動タイミングチャートを示す図。

20

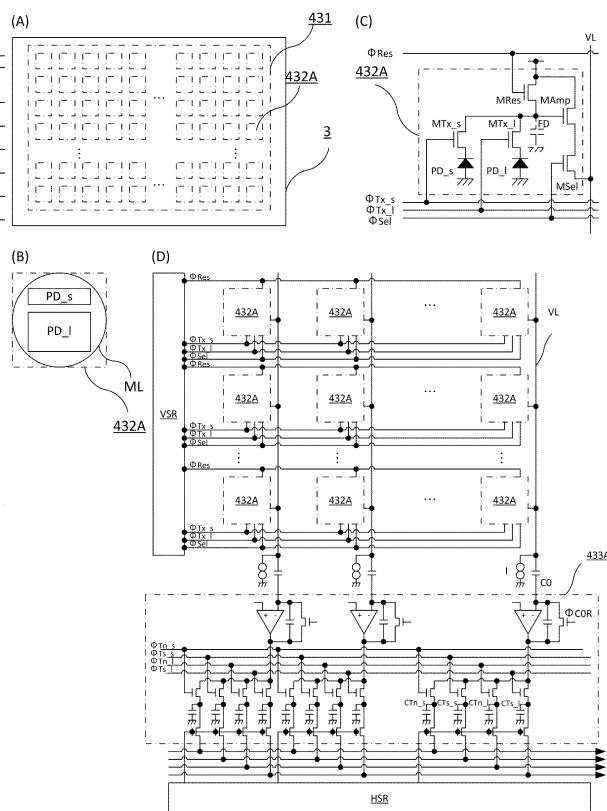

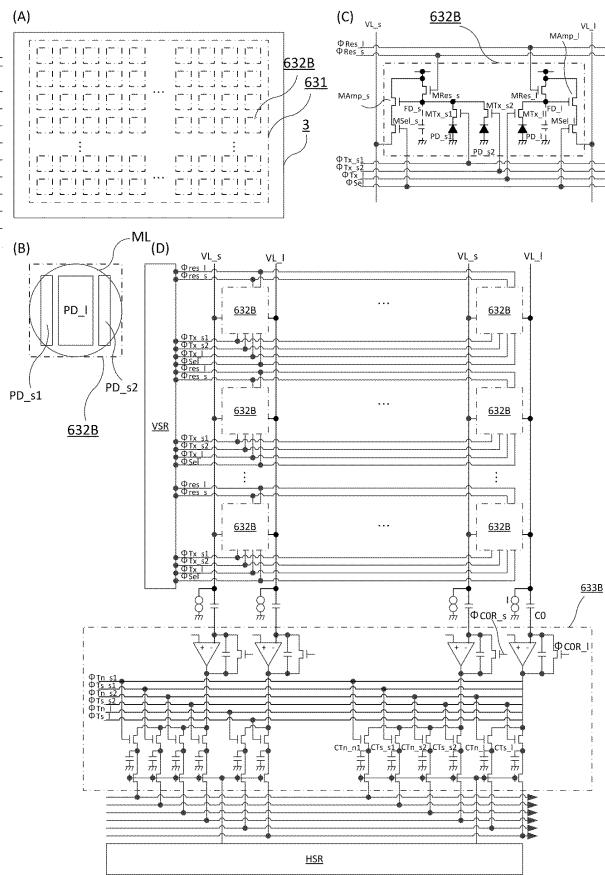

## 【図4】本発明の第2の実施例に係る撮像素子の構成を概略的に示す図。

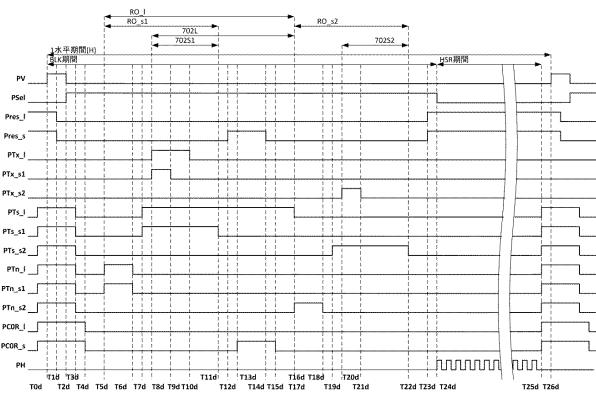

## 【図5】本発明の第2の実施例に係る撮像素子の駆動タイミングチャートを示す図。

## 【図6】本発明の第3の実施形態に係る撮像素子の構成を概略的に示す図。

## 【図7】本発明の第3の実施例に係る撮像素子の駆動タイミングチャートを示す図。

## 【発明を実施するための形態】

## 【0012】

以下、本発明の実施の形態について、添付図面を参照して詳細に説明する。

## 【0013】

本発明は、撮像素子を用いて撮像信号を取得することが可能な撮像装置に適用される。したがって、まずは、本発明を実施するための撮像装置の構成例について説明する。

30

## 【0014】

図7は、本発明の実施形態における、撮像システムとしての撮像装置の構成例を示すブロック図である。

## 【0015】

同図において、1は、レンズや絞りなどの光学部材からなる、撮像素子3に被写体からの光束（光学像）を導くための光学系である。2は、後述の撮像素子の露光時間を制御するために、撮像素子の遮光を行う遮光手段としての、メカニカルシャッタである。

## 【0016】

3は、照射された光を電気信号に変換して出力する撮像素子、4は、撮像素子3から出力された電気信号（アナログ信号）をデジタル画像信号に変換するA/D変換器である。5は、撮像素子3を動作させるために、駆動回路6に対して必要な制御信号を発生するタイミング信号発生回路、6は、光学系1、メカニカルシャッタ2及び撮像素子3の駆動パルスを生成する駆動回路である。

40

## 【0017】

7は、撮影した画像信号に対して各種補正等の信号処理を行う、信号処理手段としての信号処理回路である。8は、信号処理された画像データを記憶する画像メモリ、9は、撮像装置から取り外し可能であり、画像データを記憶する、画像記録媒体である。10は、信号処理された画像データを画像記録媒体9に記録する記録回路、11は、信号処理された画像データを表示する画像表示装置、12は、画像表示装置11に画像を表示する表示回路である。

50

## 【0018】

13は、撮像装置全体を制御するシステム制御部である。14は、記憶手段としての不揮発性メモリ(ROM)である。不揮発性メモリ14には、システム制御部13で実行される制御方法を記載したプログラム、プログラムを実行する際に使用されるパラメータやテーブル等の制御データ、及び、画像信号の各種補正に用いるデータを記憶しておく。15は、揮発性メモリ(RAM)である。揮発性メモリ15には、不揮発性メモリ14に記憶されたプログラム、制御データ及び補正データを転送して記憶しておき、システム制御部13が撮像装置を制御する際にそれらを読み出して使用する。

## 【0019】

16は、撮像装置が撮影動作を行うための、各種撮影準備動作の開始を指示するスイッチSw1、17は、撮像装置の撮影動作開始を指示するスイッチSw2である。

10

## 【0020】

以上が、本発明を実施するための撮像装置の構成例である。

## 【実施例1】

## 【0021】

以下、図1、図2を参照して、本発明の第1の実施例における、撮像素子3の構成、及び、その駆動方法について説明する。なお、図2において、図1と同じ部分は同じ符号を付して示す。

## 【0022】

図2は、本発明の第一の実施例に係わる撮像素子3の構成を概略的に示す図である。図2(A)は、撮像素子3における画素配列の一例を示す図である。図2(A)に示すように、撮像素子3に設けられた撮像領域31には、複数の画素232L、232Sが配されている。

20

## 【0023】

ここで、画素232Lと、232Sとは、蓄積する信号量がそれぞれ異なる光電変換素子を備えているものとする。例えば、撮像領域に設けられる複数の光電変換素子のうち、一部の光電変換素子の面積を異ならせることにより、蓄積する信号量が異なる光電変換素子を備えた、複数の画素を形成することができる。例えば、図2(B)および図2(C)に示すように、画素232Lにおける光電変換素子PD\_Iの面積と画素232Sにおける光電変換素子PD\_sの面積に、図のような大小関係を持たせる。この場合、第1の光電変換素子PD\_Iに対し、第2の光電変換素子PD\_sの面積が小さいため、PD\_sを備えた画素232Sが蓄積する信号量は、PD\_Iを備えた画素232Lが蓄積する信号量と比較して少なくなる。

30

## 【0024】

このように蓄積する信号量がそれぞれ異なる光電変換素子を設けることで、撮像素子から感度の異なる信号を得ることができる。このような撮像素子を撮像装置で用いることでの取得した画像信号を活用して、ダイナミックレンジを拡大させる等の信号処理を行うことが可能となる。

## 【0025】

ここで、図2(D)に、画素232Lの等価回路図を示す。画素232Lは、入射光を電荷に変換し、発生した信号電荷を蓄積する光電変換手段としてのフォトダイオードPD\_Iを備えている。更に、蓄積された信号電荷量に応じて增幅信号出力を出力線に出力する增幅手段としての増幅MOSトランジスタ(MAmp)、信号電荷を受け增幅用MOSトランジスタのゲート電極に接続するフローティングディフュージョン(FD)部を備える。また、フォトダイオードPD\_Iに蓄積した信号電荷のFD部への転送を制御する転送手段としての転送MOSトランジスタ(MTx)、FD部をリセットするリセット手段としてのリセットMOSトランジスタ(MRes)を備える。さらには、後段の読み出し回路に接続すべき画素を選択する選択手段としての選択MOSトランジスタ(MSel)を備え、これらによって画素232Lが構成されている。なお、増幅MOS MAmpのドレインおよびリセットMOS MResのドレインには金属配線を介して電源が接続され、電源電位が供給される。

40

## 【0026】

図2(E)は、画素232Sの等価回路図を示す。画素232Sの構成は、光電変換手段として

50

、フォトダイオードPD\_1ではなく、PD\_1よりも蓄積する信号量の少ないフォトダイオードPD\_sを備えているが、その他の構成要素については、画素232Lと同様であるため、説明は省略する。

#### 【0027】

図2(F)は、撮像素子3全体の等価回路図を示す。撮像素子3は、画素232L及び画素232Sのうち、信号を読み出すために同一時刻に選択される複数の画素が、同一の制御パルスによって制御されるよう構成されている。更に、同一時刻に選択される複数の画素は、画素232Lのみか、あるいは、画素232Sのみとなるように構成されている。

#### 【0028】

例えば、本実施例では、同一行に配された複数の画素に対し、MTx、MRes、MSelの各々のゲート電極に制御パルスを印加するための、制御線 TX、Res、Selが設けられている。すなわち、本実施例の撮像素子3の画素配列は、画素232Lのみが配置された行と画素232Sのみが配置された行からなる画素の2次元配列によって構成されている。10

#### 【0029】

垂直走査回路ブロックVSRは、制御線 TX、Res、Selを介して、画素232Lに対して制御パルスPTx\_I、PRes\_I、PSel\_Iを印加する。また、画素232Sに対しては、制御パルスPTx\_s、PRes\_s、PSel\_sを印加する。また、マトリクス状に配された複数の画素のうち、同一列に配された画素群に対し、選択された行の画素の増幅信号を出力する共通の垂直出力線VLが設けられている。尚、このような画素配置は、本発明を実施するための形態の一例であり、画素232Lと画素232Sとが異なる制御パルスによって制御されるという要旨を満たす限り、種々の変形及び変更が可能である。20

#### 【0030】

垂直出力線VLは、定電流源Iに接続されると共に、クランプ容量C0を介して列回路部233に接続される。制御線 CORを介して列回路部に印加される制御パルスによって、クランプ容量における信号レベルのクランプ動作が制御される。尚、制御線 CORからは、画素232Lからの信号読み出し時には制御パルスPCOR\_Iが、画素232Sからの信号読み出し時には制御パルスPCOR\_sが印加される。

#### 【0031】

列回路部233は垂直出力線VLごとに列メモリCTn、CTsを備え、制御線 Ts、Tnを介して印加される制御パルスに従って、選択された画素から出力される信号を、垂直出力線VLに接続されたクランプ容量C0を介して一時的に保持する。尚、制御線 Ts、Tnからは、画素232Lからの信号読み出し時には制御パルスPTs\_I、PTn\_Iが、画素232Sからの信号読み出し時には制御パルスPTs\_s、PTn\_sが印加される。30

#### 【0032】

列メモリCTn、CTsに保持された信号は、水平走査回路部HSRからの制御信号によって、後段の回路へと順次読み出される。尚、水平走査回路部HSRは、制御線 Hを介して、画素232Lからの信号読み出し時には制御パルスPH\_Iを、画素232Sからの信号読み出し時には制御パルスPH\_sを、列回路部233に印加する。

#### 【0033】

次に、図2に示した撮像素子3の動作を、図3を用いて説明する。本動作は、システム制御部13が不揮発性メモリ14に記憶されているプログラムを実行してタイミング信号発生回路5を制御し、駆動回路6の制御信号を発生させることで行われる。40

#### 【0034】

図3(A)は、図2に示した撮像素子3における、画素232Lからの信号読み出し動作を制御する、各制御パルスのタイミングチャートを示す。また、図3(B)は、図2に示した撮像素子203における、画素232Sからの信号読み出し動作を制御する各制御パルスのタイミングチャートを示す。

#### 【0035】

本実施例において、各画素からの信号読み出しを制御する制御パルスの駆動の順序は、画素232Lと、画素232Sとで等しい。ただし、本実施例においては、画素232Lと画素232Sと50

で制御パルスの駆動タイミングを異ならせることで、画素232Lの読み出し動作にかける時間に対し、画素232Sの読み出し動作にかける時間を短く設定している。このようにすることで、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現させている。

#### 【0036】

信号の読み出しあは、共通の制御パルスで制御される複数の画素からなる画素群の信号を、1水平期間で読み出す。水平期間を所望の回数繰り返すことにより、画素群を順々に選択しながら信号の読み出しを行い、所望の画素からの信号をすべて読み出す。この一連の動作を、1フレーム単位とする。ここでは、行単位で制御線を共有しているので、1行ずつ順々に読み出しを行う。該当行の信号の読み出し動作が終了した後に次の行の読み出し動作に移る。10

#### 【0037】

以下、図3(A)を参照しながら、画素232Lからの信号読み出し動作の一例について説明する。図3のタイミングチャートでは、各パルスのハイレベルで、制御対象のMOSがオンし、各パルスのローレベルで、制御対象のMOSがオフするものとする。

#### 【0038】

時刻T0aで不図示の行送りパルスPVが垂直走査回路に入力されると、制御パルスによる制御対象行の行送りが行われ、複数の画素行のうち1行分が、制御パルスによる制御対象として選択される。

#### 【0039】

時刻T1aで、PRes\_Iがローレベルとなることで、MResのゲートにPRes\_Iのローレベルが入力され、FDのリセットが解除される。時刻T2aでPSel\_Iがハイレベルとなり、選択MOS MSelがオンとなってn行目の画素が垂直出力線に接続される。時刻T3aでPTs\_IとPTn\_Iがローレベルとなり、列メモリCTs、CTnのリセットが解除される。時刻T4aでPCOR\_Iがローレベルとなり、クランプ容量C0のリセットが解除される。20

#### 【0040】

時刻T5aでPTn\_Iがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTnに伝達される。時刻T6aでPTn\_Iがローレベルとなり、この時点でのFDの電位に応じた信号が、基準信号として列メモリCTnに保持される。30

#### 【0041】

時刻T7aでPTs\_Iがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTsに伝達される。時刻T8aでPTs\_Iがハイレベルの間に、PTx\_Iがハイレベルとなり、転送MOS MTxがオンとなって、PD\_Iに蓄積されていた電荷がFDへと転送される。時刻T9aでPTx\_Iがローレベルとなり、転送MOS MTx\_Iがオフされて、電荷のFDへの転送が終了する。時刻T10aでPTs\_Iがローレベルとなり、この時点でのFDの電位に応じた信号が、光信号(撮像信号)として列メモリCTsに保持される。

#### 【0042】

時刻T11aでPRes\_Iがハイレベルとなって、FDのリセットが開始される。時刻T12aでPSel\_Iがローレベルになると、選択MOS MSelがオフとなり、画素の選択が解除される。また、不図示の列送りパルスPH\_Iの入力が開始され、読み出し領域の先頭列から末尾の列まで、列転送パルスが1列ずつ順にHに入力される。これによって、列メモリCTs、CTnに保持された信号は、1列分ずつ順番に撮像素子の出力端子から出力される。40

#### 【0043】

時刻T13aで、列送りパルスPH\_Iの入力が終了し、撮像素子からの信号出力が終了する。このタイミングで、PTs\_IとPTn\_Iがハイレベルとなり、列メモリCTs、CTnのリセットが開始される。同時に、PCOR\_Iがハイレベルとなり、クランプ容量C0のリセットが開始される。時刻T14aで不図示の行送りパルスPVが垂直走査回路に再度入力されると、読み出しを行う選択行の行送りが行われ、次の画素行が、制御パルスによる制御対象となる。50

**【 0 0 4 4 】**

以上が、画素232Lからなる画素行の信号読み出し動作である。

**【 0 0 4 5 】**

該当行の画素信号の読み出しが終了した後は、次の画素行の読み出し動作に移る。次の選択行が画素232Lを含む画素行であれば、図3(A)のタイミングチャートに示した読み出し動作を繰り返し、次の選択行が画素232Sのみによる画素行であれば、図3(B)のタイミングチャートに示した読み出し動作を行うようとする。

**【 0 0 4 6 】**

次に、図3(A)及び図3(B)を比較しながら、画素232Lからの信号読み出し動作と、画素232Sからの信号読み出し動作との差異について説明する。

10

**【 0 0 4 7 】**

前述したとおり、画素232Sは、駆動パルスPTx\_Iに代わる駆動パルスPTx\_s、駆動パルスPRes\_Iに代わる駆動パルスPRes\_s、駆動パルスPSeI\_Iに代わる駆動パルスPSeI\_sによって制御される。また、列回路部233は、駆動パルスPTs\_Iに代わる駆動パルスPTs\_s、駆動パルスPTn\_Iに代わる駆動パルスPTn\_s、駆動パルスPCOR\_Iに代わる駆動パルスPCOR\_s、駆動パルスPH\_Iに代わる駆動パルスPH\_sで制御される。各画素からの信号読み出しを制御する制御パルスの駆動の順序は、画素232Lと、画素232Sとで等しいので、図3(B)のタイミングチャートについて、図3(A)と差異のない内容に関しては、説明を省略する。

**【 0 0 4 8 】**

本実施例においては、画素22Lと画素232Sとで制御パルスの駆動タイミングを異ならせ、画素232Lの読み出し動作(列メモリへの読み出し)にかける時間に対し、画素232Sの読み出し動作にかける時間を短く設定している。具体的には、垂直出力線VLの電位が大きく変動するような駆動を行った後、次の駆動を行うまでの待ち時間を、垂直出力線VLの電位の可変幅に応じて異ならせるようにしている。

20

**【 0 0 4 9 】**

垂直出力線の電位が変動する際には、撮像素子3の垂直出力線VLごとに設けられた電流源Iによって電流が供給され、クランプ容量C0がチャージされる。電流源Iが理想的な定電流源であるような場合には、垂直出力線VLの電圧レベルの応答速度は、垂直出力線VLの電位の変動量に関わらず一定とみなすことができる。

**【 0 0 5 0 】**

30

しかし、実際の撮像素子においては、電流源Iの電流供給能力は有限である。更に、近年、撮像装置の高精細化、高画質化への要求から、撮像素子の多画素化が進んでいる。撮像素子の画素数が増えるほど、必要な電源回路の数も増大し、各々の電源回路に十分な供給能力を持たせることは難しくなる。

**【 0 0 5 1 】**

電流源Iの供給能力が有限であるような場合、垂直出力線VLの電圧レベルの応答速度は、画素からの出力信号の変動量の大きさに応じて異なり、変動量が大きい場合には応答速度が遅く、逆に、変動量が小さい場合には応答速度が速くなる。そのため、信号読み出し動作において、垂直出力線VLの電圧が大きく変動するような動作を行った時には、その後の動作のタイミングを、垂直出力線VLの電圧レベルが十分応答できることを考慮した時間間隔を置いて設定する必要がある。

40

**【 0 0 5 2 】**

図3の例では、画素に蓄積された電荷に応じた電圧レベルが、垂直出力線VLに反映される、T8a、T8bのタイミングにおいて、垂直出力線VLの電圧が大きく変化する。したがって、タイミングT8a、T8b後の駆動タイミングについては、垂直出力線VLの応答に必要な時間を考慮して、その後の動作の駆動パルスまでの間隔を設定する必要がある。

**【 0 0 5 3 】**

また、図2に例示した撮像素子においては、画素232Lは画素232Sと比較して蓄積可能な信号量が多い。PD以外の構成が画素232Lと画素232Sとで等しい場合、画素232Lと画素232SとではFD容量が等しいので、各々の画素が出力可能な信号の大きさは、PDの面積に比例す

50

る。従って、PDの面積の大きい画素232Lは、PDの面積の小さい画素232Sと比較して大きな信号を出力することが可能である。このため、画素232Lの信号読み出し時は、画素232Sの信号読み出し時と比較して、垂直出力線VLの電圧の変動幅が大きくなる。

#### 【0054】

したがって、画素232Lの信号読み出し動作の駆動タイミングには、垂直出力線VLの電圧レベルを十分応答させるために、特に長い時間間隔の設定が必要となる。一方で、画素232Sの信号読み出し動作の駆動タイミングについては、画素232Lと比較してより短い時間間隔の設定で、垂直出力線VLの電圧レベルの十分な応答が得られることとなる。

#### 【0055】

そこで、本実施例では、例えば画素232Lの蓄積信号が飽和した場合等、垂直出力線VLの電圧レベルの応答が遅くなる時、垂直出力線VLの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T8aからT10aまでの期間300Lを適宜決定する。10

#### 【0056】

また、画素232Sの読み出し動作でも、画素232Sの蓄積信号が飽和した場合等、直出力線VLの電圧レベルの応答が遅くなる時、垂直出力線VLの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T8bからT10bまでの期間300Sを適宜決定する。

#### 【0057】

この時、前述したとおり、画素232Lと比較して、画素232Sは蓄積できる信号量が少なく、垂直出力線VLの電圧レベルの変動幅が画素232Lと比較して小さいため、垂直出力線VLが十分応答するまでの時間は短くなる。したがって、時刻T8bから時刻T10bまでの駆動パルスの間隔300Sを、時刻T8aから時刻T10aまでの駆動パルスの間隔300Lと比較して、可能な範囲で短く設定することとする。20

#### 【0058】

時刻T10b以降の駆動パルスについては、図3(A)と同じ駆動間隔を保ったまま、間隔300Sが間隔300Lに対して短縮された分だけ前倒して、駆動するように設定する。また、行送りパルスPVの間隔についても、図3における間隔H\_Iに対する間隔H\_sのように、間隔300Sが間隔300Lに対して短縮された分だけ前倒して、駆動するように設定する。

#### 【0059】

尚、PDからFDへの電荷転送にかける時間については、画素232Lと画素232Sとで異なる必要はないが、図3に示したタイミングチャートの様に、画素232Lと画素232Sとで異なるようにしてもよい。具体的には、一般に、PD面積が異なれば、PDからFDへの電荷転送にかかる時間も異なる。そのため、図3に示したタイミングチャートでは、PD\_IからFD部への電荷転送にかける時間を、PD\_IからFD部へと電荷を十分に転送するために必要な時間を考慮して決定している。また、PD\_sからFD部への電荷転送にかける時間を、PD\_sからFDへと電荷を十分に転送するために必要な時間を考慮して決定している。30

#### 【0060】

例えば、ここでは、PD\_IからFD部への荷転送に必要な時間が、PD\_sからFD部への荷転送に必要な時間と比較して長いものとする。そこで、PD\_IからFD部への電荷転送開始時刻T8aからその終了時刻T9aまでの時間期間を次のように設定する。即ち、PD\_sからFD部への電荷転送開始時刻T8bからその終了時刻T9bまでの時間期間に対して、時刻T8aからT9aまでの時間期間が長くなうように設定する。40

#### 【0061】

以上に述べた例の他にも、信号の大きさや、素子の構成及びレイアウト等によって応答速度が異なる様な動作に関わる駆動パルスがあれば、画素232Lと画素232Sとで異なるタイミングで駆動するよう設定することができる。実際の撮像素子においては、各駆動パルスの間隔は、撮像素子の画素及び読み出し回路、周辺回路を構成する回路素子とそのレイアウトを考慮したシミュレーションによって決定すればよい。あるいは、実際の撮像素子を用いて測定を行い、各駆動パルスの間隔を決定してもよい。

#### 【0062】

また、画素232L、232Sの配置は撮像素子の設計段階で分かっている。従って、画素の読50

み出し順序に従って、画素232Lの読み出し時には図3(A)のタイミングチャートで駆動し、画素232Sの読み出し時には図3(B)のタイミングチャートで駆動する様、プログラムしておけばよい。

#### 【0063】

このようにすることで、本実施例の読み出し動作では、1フレーム分の読み出しに要する時間は

$$\begin{aligned} & [H_I] \times [\text{画素232Lの行数}] + [H_S] \times [\text{画素232Sの行数}] \\ & = [H_I] \times [\text{画素行の総数}] - [300L - 300S] \times [\text{画素232Sの行数}] \end{aligned}$$

となる。

#### 【0064】

したがって、従来の読み出し動作において1フレーム分の読み出しに要する時間

$$[H_I] \times [\text{画素行の総数}]$$

に対して、 $[300L - 300S] \times [\text{画素232Sの行数}]$ だけ短い時間で、1フレーム分の読み出しを完了することができる。

#### 【0065】

以上のように、各々の画素が扱う信号の大きさに応じて、駆動パルスの間隔を適宜設定することにより、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現することが可能となる。

#### 【実施例2】

#### 【0066】

以下、図4、図5を参照して、本発明の第2の実施例に係る撮像素子3の構成、及び、その駆動方法について説明する。なお、図4において、図1と同じ部分は同じ符号を付して示す。

#### 【0067】

図4は、本発明の第2の実施例に係る撮像素子3の構成を概略的に示す図である。

#### 【0068】

図4(A)は、撮像素子3における画素列の一例を示す図である。図4(A)に示すように、撮像素子3に設けられた撮像領域431には、複数の画素432Aが二次元に配されている。ここで、画素432Aは、蓄積する信号量がそれぞれ異なる、光電変換素子PD\_Iと、PD\_Sとを備えているものとする。図4(B)は、画素432Aにおける各光電変換素子PD\_I及びPD\_Sの面積の大小関係を模式的に示した図である。ここでは、PD\_Iに対し、PD\_Sの面積が小さくなるよう形成されているため、PD\_Sが蓄積する信号量は、PD\_Iが蓄積する信号量と比較して少なくなる。

#### 【0069】

このように、画素内に、蓄積する信号量がそれぞれ異なる光電変換素子を設けることで、撮像素子から感度の異なる信号を得ることができる。本実施例の撮像素子を撮像装置で用いることで、取得した画像信号を活用して、ダイナミックレンジを拡大させる等の信号処理を行うことが可能となる。

#### 【0070】

また、図4(B)のPD\_I、PD\_Sの上部に、共通のオンチップレンズMLを設けることで、PD\_I、PD\_Sのそれぞれに対し、撮像装置の光学系1の異なる瞳面を通った光が入射するようになるため、PDによって位相の異なる信号を得ることができる。これらの信号を、撮像、及び、焦点検出に用いることで、撮像素子3を、焦点検出素子として用いることも可能となる。

#### 【0071】

図4(C)は、画素432Aの等価回路図を示す。

#### 【0072】

画素432Aは、入射光を電荷に光電変換して発生した信号電荷を蓄積するための光電変換手段としてのフォトダイオードPD\_I、PD\_Sを備えている。更に、蓄積された信号電荷量に応じて増幅信号出力を出力する増幅手段としての増幅MOSトランジスタ(MAmp)、信号

10

20

30

40

50

電荷を受け増幅用MOSトランジスタのゲート電極に接続するフローティングディフュージョン(FD)部を備える。また、フォトダイオードPD<sub>1</sub>に蓄積した信号電荷のFD部への転送を制御する転送手段としての転送MOSトランジスタ(MTx<sub>1</sub>)を備える。これに関連して、フォトダイオードPD<sub>s</sub>に蓄積した信号電荷のFD部への転送を制御する転送手段としての転送MOSトランジスタ(MTx<sub>s</sub>)も備える。更に、FD部をリセットするリセット手段としてのリセットMOSトランジスタ(MRes)、後段の読み出し回路に接続する画素を選択する選択手段としての選択MOSトランジスタ(MSel)を備え、これらによって画素432Aは構成されている。なお、増幅MOS M<sub>Amp</sub>のドレインおよびリセットMOS M<sub>Res</sub>のドレインには金属配線を介して電源が接続され、電源電位が供給される。

## 【0073】

10

図4(D)は、撮像素子3全体の等価回路図を示す。

## 【0074】

撮像素子3は、画素432Aのうち、信号を読み出すために同一時刻に選択される複数の画素が、同一の制御パルスによって制御されるよう構成されている。例えば、ここでは、同一行に配された複数の画素に対し、MTx<sub>1</sub>、MTx<sub>s</sub>、MRes、MSelの各々のゲート電極に同一の制御パルスを印加するための、制御線 TX<sub>1</sub>、TX<sub>s</sub>、Res、Selが設けられている。

## 【0075】

垂直走査回路ブロックVSRは、制御線 TX<sub>1</sub>、TX<sub>s</sub>、Res、Selを介して、画素432Aに対して制御パルスPTx<sub>1</sub>、PTx<sub>s</sub>、PRes<sub>1</sub>、PSelを印加する。

20

## 【0076】

また、マトリクス状に配された複数の画素のうち、同一列に配された画素群に対し、選択された行の画素の増幅信号を出力する共通の垂直出力線VLが設けられている。

## 【0077】

尚、このような画素配置は本発明を実施するための形態の一例である。実際には、フォトダイオードPD<sub>1</sub>からFD部への電荷転送を制御する転送手段と、フォトダイオードPD<sub>s</sub>からFD部への電荷転送を制御する転送手段とが、異なる制御パルスによって制御されるという要旨を満たす限り、種々の変形及び変更が可能である。

## 【0078】

垂直出力線VLは、定電流源Iに接続されると共に、クランプ容量C<sub>0</sub>を介して列回路部433Aに接続される。制御線 CORを介して列回路部に印加される制御パルスによって、クランプ容量における信号レベルのクランプ動作が制御される。尚、制御線 CORからは、制御パルスPCORが印加される。

30

## 【0079】

列回路部433Aは垂直出力線VLごとに列メモリCTn<sub>s</sub>、CTs<sub>s</sub>、CTn<sub>1</sub>、CTs<sub>1</sub>を備える。これらは、制御線 Tn<sub>s</sub>、Tn<sub>1</sub>、Ts<sub>s</sub>、Ts<sub>1</sub>から印加される制御パルスPTn<sub>s</sub>、PTs<sub>s</sub>、PTn<sub>1</sub>、PTs<sub>1</sub>に従って、選択された画素から出力される信号を、垂直出力線VLに接続されたクランプ容量C<sub>0</sub>を介して一時的に保持する。

## 【0080】

列メモリCTn<sub>s</sub>、CTs<sub>s</sub>、CTn<sub>1</sub>、CTs<sub>1</sub>に保持された信号は、水平走査回路部HSRからの制御信号によって、後段の回路へと順次読み出される。

40

## 【0081】

次に、図4に示した撮像素子3の動作を、図5を用いて説明する。本動作は、システム制御部13が不揮発性メモリ14に記憶されているプログラムを実行してタイミング信号発生回路5を制御し、駆動回路6の制御信号を発生させることで行われる。

## 【0082】

図5は、図4に示した撮像素子3における、画素432Aからの信号読み出し動作を制御するための各制御パルスのタイミングチャートを示す。図5のタイミングチャートでは、各パルスのハイレベルで、制御対象のMOSがオンし、各パルスのローレベルで、制御対象のMOSがオフするものとする。

50

## 【0083】

本実施例においては、フォトダイオードPD\_1とPD\_sとで、FD部以降の読み出し回路を共有させているため、同一画素内のフォトダイオードPD\_sからの信号とフォトダイオードPD\_1からの信号とを、時刻を異ならせて順に読み出す。ここで、フォトダイオードPD\_1からの信号読み出し動作と比較して、フォトダイオードPD\_sからの信号読み出し動作における制御パルス間隔を短く設定し、画素432A全体の信号読み出し動作にかける時間を、従来より短く設定している。このようにすることで、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現させている。

## 【0084】

信号の読み出しへは、共通の制御パルスで制御される複数の画素からなる画素群の信号を、1水平期間で読み出す。水平期間を所望の回数繰り返すことにより、画素群を順々に選択しながら信号の読み出しを行い、所望の画素からの信号をすべて読み出す。この一連の動作を、1フレーム単位とする。ここでは、行単位で制御線を共有しているので、1行ずつ順々に読み出しを行う。該当行の信号の読み出し動作が終了した後に次の行の読み出し動作に移る。

## 【0085】

以下、図5を参照しながら、画素432Aからの信号読み出し動作の一例について説明する。

## 【0086】

時刻T0cで不図示の行送りパルスPVが垂直走査回路に入力されると、制御パルスによる制御対象行の行送りが行われ、複数の画素行のうち1行分が、制御パルスによる制御対象として選択される。時刻T1cで、PResがローレベルとなることで、MResのゲートにPResのローレベルが入力され、FDのリセットが解除される。

## 【0087】

時刻T2cでPSelがハイレベルとなり、選択MOS MSelがオンとなってn行目の画素が垂直出力線に接続される。時刻T3cでPTs\_s、PTn\_s、PTs\_l、PTn\_lがローレベルとなり、列メモリCTs\_s、CTn\_s、CTs\_l、CTn\_lのリセットが解除される。時刻T4cでPCORがローレベルとなり、クランプ容量C0のリセットが解除される。

## 【0088】

時刻T5cでPTn\_sがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTn\_sに伝達される。時刻T6cでPTn\_sがローレベルとなり、この時点でのFDの電位に応じた信号が、基準信号として列メモリCTn\_sに保持される。時刻T7cでPTs\_sがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTs\_sに伝達される。

## 【0089】

時刻T8cでPTs\_sがハイレベルの間に、PTx\_sがハイレベルとなり、転送MOS MTx\_sがオンとなって、PD\_sに蓄積されていた電荷がFDへと転送される。時刻T9cでPTx\_sがローレベルとなり、転送MOS MTx\_sがオフされて、電荷のFDへの転送が終了する。時刻T10cでPTs\_sがローレベルとなり、この時点でのFDの電位に応じた信号が、光信号（撮像信号）として列メモリCTs\_sに保持される。

## 【0090】

時刻T11cでPResがハイレベルとなって、FDのリセットが開始される。時刻T12cでPCORがハイレベルとなって、クランプ容量C0のリセットが開始される。時刻T13cでPResがローレベルとなって、FDのリセットが解除される。時刻T14cでPCORがハイレベルとなって、クランプ容量C0のリセットが解除される。

## 【0091】

時刻T15cでPTn\_lがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTn\_lに伝達される。時刻T16cでPTn\_lがローレベルとなり、この時点でのFDの電位に応じた信号が、基準信号として列

10

20

30

40

50

メモリCTn\_Iに保持される。時刻T17cでPTs\_Iがハイレベルとなると、垂直出力線が、FDに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTs\_Iに伝達される。

#### 【0092】

時刻T18cでPTs\_Iがハイレベルの間に、PTx\_Iがハイレベルとなり、転送MOS MTx\_Iがオンとなって、PD\_Iに蓄積されていた電荷がFDへと転送される。時刻T19cでPTx\_Iがローレベルとなり、転送MOS MTx\_Iがオフされて、電荷のFDへの転送が終了する。時刻T20cでPTs\_Iがローレベルとなり、この時点でのFDの電位に応じた信号が、光信号（撮像信号）として列メモリCTs\_Iに保持される。

#### 【0093】

時刻T21cでPResがハイレベルとなって、FDのリセットが開始される。時刻T22cでPSelがローレベルになると、選択MOS MSelがオフとなり、画素の選択が解除される。また、不図示の列送りパルスPHの入力が開始され、読み出し領域の先頭列から末尾の列まで、列転送パルスが1列ずつ順に Hに入力される。これによって、列メモリCTs\_s、CTn\_s、CTs\_I、CTn\_Iに保持された信号は、1列分ずつ順番に撮像素子の出力端子から出力される。

10

#### 【0094】

時刻T23cで、列送りパルスPH\_Iの入力が終了し、撮像素子からの信号出力が終了する。このタイミングで、PTs\_s、PTn\_s、PTs\_I、PTn\_Iがハイレベルとなり、列メモリCTs\_s、CTn\_s、CTs\_I、CTn\_Iのリセットが開始される。同時に、PCORがハイレベルとなり、クランプ容量C0のリセットが開始される。

20

#### 【0095】

時刻T24cで不図示の行送りパルスPVが垂直走査回路に再度入力されると、読み出しを行う選択行の行送りが行われ、次の画素行が、制御パルスによる制御対象となる。

#### 【0096】

以上が、画素432Aの信号読み出し動作である。該当行の画素信号の読み出しが終了した後は、次の画素行の読み出し動作に移る。

#### 【0097】

本実施例では、画素432Aに含まれるフォトダイオードの信号読み出し動作において、フォトダイオードPD\_Iの信号読み出し動作と比較して、フォトダイオードPD\_sの信号読み出し動作における制御パルスの期間を短く設定している。具体的には、垂直出力線VLの電位が大きく変動するような駆動を行った後、次の駆動を行うまでの待ち時間を、垂直出力線VLの電位の可変幅に応じて、各々のフォトダイオードからの信号読み出し動作ごとに異ならせるようにしている。

30

#### 【0098】

図5の例では、画素に蓄積された電荷に応じた電圧レベルが、垂直出力線VLに反映される、T8c、T18cのタイミングにおいて、垂直出力線VLの電圧が大きく変化する。したがって、タイミングT8c、T18c後の駆動タイミングについては、垂直出力線VLの応答に必要な時間を考慮して、駆動パルスの間隔を設定する必要がある。

#### 【0099】

また、図4に例示した撮像素子においては、大きい面積のフォトダイオードPD\_IはフォトダイオードPD\_sと比較して大きな信号を出力することが可能であるため、垂直出力線VLの電圧の変動幅が大きいと言える。したがって、フォトダイオードPD\_Iの信号読み出し動作の駆動タイミングには、垂直出力線VLの電圧レベルを十分応答させるために、特に長い時間間隔が必要となる。一方で、フォトダイオードPD\_sの信号読み出し動作の駆動タイミングについては、フォトダイオードPD\_Iと比較してより短い時間間隔の設定でも、垂直出力線VLの電圧レベルの十分な応答が得られることとなる。

40

#### 【0100】

そこで、本実施例では、例えばフォトダイオードPD\_Iの蓄積信号が飽和した場合等、垂直出力線VLの電圧レベルの応答が遅くなる時に垂直出力線VLの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T18cからT20cまでの期間501Lを適宜決定する。

50

**【0101】**

また、フォトダイオードPD\_sの読み出し動作でも同様である。フォトダイオードPD\_sの蓄積信号が飽和した場合等、直出力線VLの電圧レベルの応答が遅くなる時、垂直出力線VLの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T8cからT10cまでの期間501Sを適宜決定する。

**【0102】**

前述したとおり、フォトダイオードPD\_Iと比較して、フォトダイオードPD\_sは蓄積できる信号量が少なく、垂直出力線VLの電圧レベルの変動幅がフォトダイオードPD\_Iと比較して小さい。そのため、フォトダイオードPD\_sの読み出し動作時は、垂直出力線VLが十分応答するまでの時間がフォトダイオードPD\_Iの読み出し動作時に対して短くなる。10 したがって、時刻T8cからT10cまでの期間501Sを、時刻T18cから時刻T20cまでの駆動パルスの期間501Lと比較して、可能な範囲で短く設定することとする。

**【0103】**

尚、PDからFDへの電荷転送にかける時間については、PD\_IとPD\_sとで異ならせる必要はないが、図5に示したタイミングチャートの様に、PD\_IとPD\_sとで異ならせるようにしてもよい。具体的には、一般に、PD面積が異なれば、PDからFDへの電荷転送にかかる時間が異なる。そのため、図5に示したタイミングチャートでは、PD\_IからFD部への電荷転送にかける時間を、PD\_IからFD部へと電荷を十分に転送するために必要な時間を考慮して決定している。また、PD\_sからFD部への電荷転送にかける時間を、PD\_sからFDへと電荷を十分に転送するために必要な時間を考慮して決定している。20

**【0104】**

例えば、本実施例では、PD\_IからFD部への電荷転送に必要な時間が、PD\_sからFD部への電荷転送に必要な時間と比較して長いものとする。そこで、PD\_IからFD部への電荷転送開始時刻T18cからその終了時刻T19cまでの時間期間を次のように設定する。即ち、PD\_sからFD部への電荷転送開始時刻T8cからその終了時刻T9cまでの時間期間に対して、時刻T18cからT19cまでの時間期間を長く設定している。

**【0105】**

本実施例は上述の例に限らず、例えば、信号の大きさ、素子の構成及びレイアウト等によって応答速度が異なる動作に関わる駆動パルスに対し適用可能である。もし、そのような駆動パルスがあれば、フォトダイオードPD\_sの読み出し動作とフォトダイオードPD\_Iの読み出し動作とで、異なる駆動タイミングを設定すればよい。30

実際の撮像素子においては、各駆動パルスの間隔は、撮像素子の画素及び読み出し回路、周辺回路を構成する回路素子とそのレイアウトを考慮したシミュレーションによって決定すればよい。あるいは、実際の撮像素子を用いて測定を行い、各駆動パルスの間隔を決定してもよい。

**【0106】**

尚、ここでは、フォトダイオードPD\_sの信号読み出し(R0\_s)を行った後に、フォトダイオードPD\_Iの信号読み出し(R0\_I)を行う例について示した。しかし、R0\_sとR0\_Iの順序を入れ替えて、フォトダイオードPD\_Iの信号読み出しを先に行ってもよい。また、画素内の異なる感度のフォトダイオードの数を3またはそれ以上として、本実施例に従つた駆動タイミング制御を行って順次信号を読み出す構成としてもよい。40

**【0107】**

以上説明した本実施例の読み出し動作によれば、従来の読み出し動作において1フレーム分の読み出しに要する時間を、[501L - 501S] × [画素432Aの行数]だけ短縮して1フレーム分の読み出しを完了することが可能となる。

**【0108】**

以上の様に、各々の画素が扱う信号の大きさに応じて、駆動パルスの間隔を適宜設定することにより、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現することが可能となる。

**【実施例3】**

**【 0 1 0 9 】**

以下、図6、図7を参照して、本発明の第3の実施例における、撮像素子603の構成、及び、その駆動方法について説明する。なお、図6において、図1と同じ部分は同じ符号を付して示す。

**【 0 1 1 0 】**

図6は、本発明の第3の実施形態における、撮像素子3の構成を概略的に示す図である。

**【 0 1 1 1 】**

図6(A)は、撮像素子3における画素配列の一例を示す図である。図6(A)に示すように、撮像素子3に設けられた撮像領域631には、複数の画素32Bが二次元に配されている。

10

**【 0 1 1 2 】**

ここで、画素632Bは、蓄積する信号量がそれぞれ異なる、光電変換素子PD\_Iと、PD\_s1、PD\_s2とを備えているものとする。図6(B)は、画素632Bにおける光電変換素子PD\_I及びPD\_s1、PD\_s2の面積の大小関係を模式的に示す図である。ここでは、PD\_Iに対し、PD\_s1、PD\_s2の面積が小さくなるよう形成されているため、PD\_s1、PD\_s2が蓄積する信号量は、PD\_Iが蓄積する信号量と比較して少なくなる。

**【 0 1 1 3 】**

このように蓄積する信号量がそれぞれ異なる光電変換素子を設けることで、撮像素子から感度の異なる撮像信号を得ることができる。このような撮像素子を撮像装置で用いることで、取得した画像信号を活用して、ダイナミックレンジを拡大させる等の信号処理を行うことが可能となる。

20

**【 0 1 1 4 】**

また、図6(B)のPD\_I、PD\_s1、PD\_s2の上部に、共通のオンチップレンズMLを設ける。これにより、PD\_I、PD\_s1、PD\_s2に対し、撮像装置の光学系1においてそれぞれ異なる瞳面を通った光が入射するようになるため、PDによって位相の異なる信号を得ることができる。これらの信号を、撮像、及び、焦点検出に用いることで、撮像素子3を、焦点検出素子としても用いることが可能となる。

**【 0 1 1 5 】**

図6(C)は、画素632Bの等価回路図を示す。

30

**【 0 1 1 6 】**

画素632Bは、入射光を電荷に変換し、発生した信号電荷を蓄積するための、光電変換手段としてのフォトダイオードPD\_I、PD\_s1、PD\_s2を備えている。

**【 0 1 1 7 】**

フォトダイオードPD\_Iは、PD\_Iの電荷転送を制御する転送手段としての転送MOSトランジスタ(MTx\_I)を介し、FD部(FD\_I)に接続されている。また、FD部(FD\_I)は、蓄積された信号電荷量に応じて増幅信号を出力する増幅手段としての増幅MOSトランジスタ(MAmp\_I)のゲートに接続されている。増幅MOS(MAmp\_I)のドレイン側には金属配線を介して電源が接続され、電源電位が供給される。また、増幅MOS(MAmp\_I)のソース側には、後段の読み出し回路に接続する画素を選択する、選択手段としての選択MOSトランジスタ(MSel\_I)が接続されている。

40

**【 0 1 1 8 】**

フォトダイオードPD\_Iが接続されたFD\_Iは、FD\_Iをリセットするリセット手段としてのリセットMOSトランジスタ(MRes\_I)に接続される。

**【 0 1 1 9 】**

フォトダイオードPD\_Iより蓄積する信号量の少ないフォトダイオードPD\_s1は、転送MOSトランジスタ(MTx\_s1)を介し、PD\_Iの接続先とは異なるFD部及び増幅MOSトランジスタ(MAmp\_s)のゲートに接続されている。

**【 0 1 2 0 】**

蓄積する信号量がフォトダイオードPD\_Iより少ないフォトダイオードPD\_s2は、転送MOS

50

トランジスタ (MTx\_s2) を介し、PD\_s1と共通のFD部 (FD\_s) 及び増幅MOSトランジスタ (MAmp\_s) のゲートに接続されている。

【0121】

増幅MOS (MAmp\_s) のドレイン側には金属配線を介して電源が接続され、電源電位が供給される。また、増幅MOS (MAmp\_s) のソース側には、後段の読み出し回路に接続されるべき画素を選択する選択手段としての選択MOSトランジスタ (MSel\_s) が接続されている。

【0122】

フォトダイオードPD\_s1、PD\_s2が接続されたFD\_sは、FD\_sをリセットするリセット手段としてのリセットMOSトランジスタ (MRes\_s) に接続される。

10

【0123】

図6 (D) は、撮像素子3全体の等価回路図を示す。

【0124】

撮像素子3は、画素62Bのうち、信号を読み出すために同一時刻に選択される複数の画素が、同一の制御パルスによって制御されるよう構成されている。例えば、本実施例では、同一行に配された複数の画素に対し、MTx\_I、MTx\_s1、MTx\_s2、MRes\_I、MRes\_sの各々のゲート電極に制御パルスを印加する。このために、制御線 Tx\_I、Tx\_s1 Tx\_s2、Res\_I、Res\_sが設けられている。また、同一行に配された複数の画素に対し、MSel\_I、MSel\_sの各々のゲート電極に制御パルスを印加するための、制御線 Selが設けられている。

20

【0125】

垂直走査回路ブロックVSRは、制御線 Tx\_I、Tx\_s1、Tx\_s2、Res\_I、Res\_s、Selを介して、画素632Aに対して制御パルスPTx\_I、PTx\_s1、PTx\_s2、PRes\_I、PRes\_s、PSelを印加する。

【0126】

マトリクス状に配された複数の画素のうち、同一列に配された画素群の、フォトダイオードPD\_Iが接続された選択MOS (MSel\_I) は、共通の垂直出力線VL\_I (第1の出力線) に接続されている。また、マトリクス状に配された複数の画素のうち、同一列に配された画素群の、フォトダイオードPD\_s1、PD\_s2が接続された選択MOS (MSel\_s) は、共通の垂直出力線VL\_s(第2の出力線) に接続されている。

30

【0127】

尚、このような画素配置は本発明を実施するための形態の一例である。実際には、フォトダイオードPD\_IからFD部への電荷転送、フォトダイオードPD\_s1からFD部への電荷転送、フォトダイオードPD\_s2からFD部への電荷転送、の各々を制御する転送手段が、それ異なる制御パルスによって制御されればよい。したがって、この要旨を満たす限り、本実施例においても、種々の変形及び変更が可能である。

【0128】

垂直出力線VL\_Iは、定電流源 I に接続されると共に、クランプ容量C0を介して列回路部633Bに接続される。制御線 COR\_Iを介して列回路部に印加される制御パルスによって、クランプ容量における信号レベルのクランプ動作が制御される。尚、制御線 COR\_Iからは、制御パルスPCOR\_Iが印加される。

40

【0129】

また、垂直出力線VL\_sは、定電流源 I に接続されると共に、クランプ容量C0を介して列回路部633Bに接続される。制御線 COR\_sを介して列回路部に印加される制御パルスによって、クランプ容量における信号レベルのクランプ動作が制御される。尚、制御線 COR\_sからは、制御パルスPCOR\_sが印加される。

【0130】

列回路部633Bは垂直出力線VL\_Iごとに列メモリCTn\_I、CTs\_Iを備える。列メモリCTn\_I、CTs\_Iは、制御線 Ts\_I、Tn\_Iを介して印加される制御パルスPTn\_I、PTs\_Iに従って、選択された画素から出力される信号を、垂直出力線VLに接続されたクランプ容量C0を介

50

して一時的に保持する。

**【0131】**

また、列回路部633Bは垂直出力線VL\_sごとに列メモリCTn\_s1、CTs\_s1、CTn\_s2、CTs\_n2を備える。これらは、制御線Tn\_s1、Tn\_s1、Tn\_s2、Tn\_s2から印加される制御パルスPTn\_s1、PTs\_s1、PTn\_s2、PTs\_s2に従って、選択された画素からの信号を、垂直出力線VL\_sに接続されたクランプ容量C0を介して一時的に保持する。

**【0132】**

列メモリCTn\_s1、CTs\_s1、CTn\_s2、CTs\_n2、CTn\_I、CTs\_Iに保持された信号は、水平走査回路部HSRからの制御信号によって、後段の回路へと順次読み出される。

**【0133】**

次に、図6に示した撮像素子3の動作を、図7を用いて説明する。

**【0134】**

図7には、図6に示した撮像素子3における、画素632Bからの信号読み出し動作を制御する、各制御パルスのタイミングチャートを示した。図7のタイミングチャートでは、各パルスのハイレベルで、制御対象のMOSがオンし、各パルスのローレベルで、制御対象のMOSがオフするものとする。

**【0135】**

本実施例においては、フォトダイオートPD\_s1とPD\_s2とで、FD部以降の読み出し回路を共有させているため、フォトダイオードPD\_s1からの信号と、フォトダイオードPD\_s2からの信号とを、時刻を異なさせて順に読み出す。尚、フォトダイオードPD\_1は、フォトダイオートPD\_s1、PD\_s2とは別の読み出し回路を使用して信号読み出しを行う。そのため、フォトダイオードPD\_1からの信号と、フォトダイオードPD\_s1またはPD\_s2の一方からの信号とは、並行して読み出すことが可能である（第1の駆動パルス、第2の駆動パルス）。

**【0136】**

本実施例では、フォトダイオードPD\_Iの信号読み出し動作と比較して、フォトダイオードPD\_s1、PD\_s2の信号読み出し動作の制御パルスの期間を短く設定している。これにより、画素632B全体の信号読み出し動作にかける時間を、従来より短くしている。このようにすることで、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現させている。

**【0137】**

信号の読み出しあは、共通の制御パルスで制御される複数の画素からなる画素群の信号を、1水平期間で読み出す。水平期間を所望の回数繰り返すことにより、画素群を順々に選択しながら信号の読み出しを行い、所望の画素からの信号をすべて読み出す。この一連の動作を、1フレーム単位とする。ここでは、行単位で制御線を共有しているので、1行ずつ順々に読み出しを行う。該当行の信号の読み出し動作が終了した後に次の行の読み出し動作に移る。

**【0138】**

以下、図7を参照しながら、画素632Bからの信号読み出し動作の一例について説明する。本動作は、システム制御部13が不揮発性メモリ14に記憶されているプログラムを実行してタイミング信号発生回路5を制御し、駆動回路6の制御信号を発生させることで行われる。

**【0139】**

時刻T0dで不図示の行送りパルスPVが垂直走査回路に入力されると、制御パルスによる制御対象行の行送りが行われ、複数の画素行のうち1行分が、制御パルスによる制御対象として選択される。

**【0140】**

時刻T1dで、PRes\_I、PRes\_sがローレベルとなることで、MRes\_IのゲートにPRes\_I、MRes\_sのゲートにPRes\_sのローレベルが入力され、FDのリセットが解除される。時刻T2dでPSeIがハイレベルとなり、選択MOS MSeI\_I、MSeI\_sがオンとなってn行目の画素が垂直出

10

20

30

40

50

力線に接続される。

**【 0 1 4 1 】**

時刻T3dでPTs\_s、PTn\_s、PTs\_I、PTn\_Iがローレベルとなり、列メモリCTs\_s、CTn\_s、CTs\_I、CTn\_Iのリセットが解除される。時刻T4dでPCOR\_I、PCOR\_sがローレベルとなり、クランプ容量C0のリセットが解除される。

**【 0 1 4 2 】**

時刻T5dでPTn\_Iがハイレベルとなると、垂直出力線VL\_Iが、FD\_Iに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTn\_Iに伝達される。また、PTn\_s1がハイレベルとなると、垂直出力線VL\_sが、FD\_sに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTn\_s1に伝達される。

10

**【 0 1 4 3 】**

時刻T6dでPTn\_Iがローレベルとなり、この時点でのFD\_Iの電位に応じた信号が、基準信号として列メモリCTn\_Iに保持される。また、PTn\_s1がローレベルとなり、この時点でのFD\_sの電位に応じた信号が、基準信号として列メモリCTn\_s1に保持される。

**【 0 1 4 4 】**

時刻T7dでPTs\_Iがハイレベルとなると、垂直出力線VL\_Iが、FD\_Iに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTs\_Iに伝達される。また、PTs\_s1がハイレベルとなると、垂直出力線VL\_sが、FD\_sに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTs\_s1に伝達される。

20

**【 0 1 4 5 】**

時刻T8dで、PTs\_Iがハイレベルの間に、PTx\_Iがハイレベルとなり、転送MOS MTx\_Iがオンとなって、PD\_Iに蓄積されていた電荷がFD\_Iへと転送される。また、PTs\_s1がハイレベルの間に、PTx\_s1がハイレベルとなり、転送MOS MTx\_s1がオンとなって、PD\_s1に蓄積されていた電荷がFD\_sへと転送される。時刻T9dでPTx\_s1がローレベルとなり、転送MOS MTx\_s1がオフされて、電荷のFD\_sへの転送が終了する。

**【 0 1 4 6 】**

時刻T10dで、PTx\_Iがローレベルとなり、転送MOS MTx\_Iがオフされて、電荷のFD\_Iへの転送が終了する。

**【 0 1 4 7 】**

時刻T11dで、PTs\_Iがハイレベルの間、すなわち、FD\_Iの電位に応じた信号を列メモリCTs\_Iに伝達し続けている間に、PTs\_s1がローレベルとなる。これにより、この時点でのFD\_sの電位に応じた信号が、光信号（撮像信号）として列メモリCTs\_s1に保持される。

30

**【 0 1 4 8 】**

時刻T12dでPRes\_sがハイレベルとなって、FD\_sのリセットが開始される。時刻T13dでPCOR\_sがハイレベルとなって、垂直出力線VL\_sに接続されたクランプ容量C0のリセットが開始される。

**【 0 1 4 9 】**

時刻T14dでPRes\_sがローレベルとなって、FD\_sのリセットが解除される。時刻T15dでPCOR\_sがハイレベルとなって、垂直出力線VL\_sに接続されたクランプ容量C0のリセットが解除される。

40

**【 0 1 5 0 】**

時刻T16dでPTn\_s2がハイレベルとなると、垂直出力線が、FD\_sに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTn\_s2に伝達される。

**【 0 1 5 1 】**

時刻T17dでPTs\_Iがローレベルとなり、この時点でのFD\_Iの電位に応じた信号が、光信号（撮像信号）として列メモリCTs\_Iに保持される。

**【 0 1 5 2 】**

時刻T18dでPTn\_s2がローレベルとなり、この時点でのFD\_sの電位に応じた信号が、基準信号として列メモリCTn\_s2に保持される。

**【 0 1 5 3 】**

50

時刻T19dでPTs\_s2がハイレベルとなると、垂直出力線VL\_sが、FD\_sに蓄積された電荷量に応じた電圧レベルに変動し、クランプ容量C0を介して列メモリCTs\_s2に伝達される。時刻T20dでPTx\_s2がハイレベルとなり、転送MOS MTx\_s2がオンとなって、PD\_s2に蓄積されていた電荷がFD\_sへと転送される。時刻T21dでPTx\_s2がローレベルとなり、転送MOS MTx\_s2がオフされて、電荷のFD\_sへの転送が終了する。

#### 【 0 1 5 4 】

時刻T22dでPTs\_s2がローレベルとなり、この時点でのFD\_sの電位に応じた信号が、光信号（撮像信号）として列メモリCTs\_s2に保持される。

#### 【 0 1 5 5 】

時刻T23dでPRes\_I、PRes\_sがハイレベルとなって、FD\_I、FD\_sのリセットが開始される 10

。

#### 【 0 1 5 6 】

時刻T24dでPSel\_Iがローレベルになると、選択MOS MSel\_I、MSel\_sがオフとなり、画素の選択が解除される。また、不図示の列送りパルスPHの入力が開始され、読出し領域の先頭列から末尾の列まで、列転送パルスが1列ずつ順に Hに入力される。これによって、列メモリCTs\_I、CTn\_I、CTs\_s1、CTn\_s1、CTs\_s2、CTn\_s2に保持された信号は、1列分ずつ順番に撮像素子の出力端子から出力される。

#### 【 0 1 5 7 】

時刻T25dで、列送りパルスPH\_Iの入力が終了し、撮像素子からの信号出力が終了する。このタイミングで、PTs\_I、PTn\_I、PTs\_s1、PTn\_s1、PTs\_s2、PTn\_s2がハイレベルとなり、列メモリCTs\_I、CTn\_I、CTs\_s1、CTn\_s1、CTs\_s2、CTn\_s2のリセットが開始される。同時に、PCOR\_I、PCOR\_sがハイレベルとなり、クランプ容量C0のリセットが開始される。時刻T26dで不図示の行送りパルスPVが垂直走査回路に再度入力されると、読出しを行う選択行の行送りが行われ、次の画素行が、制御パルスによる制御対象となる。

以上が、画素632Bの信号読み出し動作である。該当行の画素信号の読み出しが終了した後は、次の画素行の読み出し動作に移る。

#### 【 0 1 5 8 】

本実施例では、画素632Bに含まれるフォトダイオードの信号読み出し動作において、フォトダイオードPD\_Iの信号読み出し動作と比較して、フォトダイオードPD\_s1、PD\_s2の信号読み出し動作の制御パルスの期間を短く設定している。具体的には、垂直出力線VL\_I、VL\_sの電位が大きく変動する駆動を行った後、次の動作のための駆動を行うまでの待ち時間を、垂直出力線VL\_I、VL\_sの電位の可変幅に応じて、フォトダイオードの信号読み出し動作ごとに異ならせている。 30

#### 【 0 1 5 9 】

図7の例では、PD\_s1、PD\_Iに蓄積された電荷に応じた電圧レベルが、垂直出力線VL\_s、VL\_Iに反映される、T8dのタイミングにおいて、垂直出力線VL\_s、VL\_Iの電圧が大きく変化する。また、PD\_s2に蓄積された電荷に応じた電圧レベルが、垂直出力線VL\_sに反映されるT20dのタイミングにおいて、垂直出力線VL\_sの電圧が大きく変化する。したがって、タイミングT8d、T20d後の駆動タイミングについては、垂直出力線VL\_s、VL\_Iの応答に必要な時間を考慮して、駆動パルスの間隔を設定する必要がある。 40

#### 【 0 1 6 0 】

また、図6に例示した撮像素子3においては、フォトダイオードPD\_IはフォトダイオードPD\_sと比較して蓄積可能な信号量が多い。FD\_I以降の構成と、FD\_s以降の構成とが等しい場合、PD\_Iからの信号とPD\_s1、PD\_s2からの信号は、等しいFD容量を介して出力されるので、各PDから各垂直出力線に出力可能な信号の大きさは、PDの面積に比例する。したがって、PDの面積の大きいPD\_Iは、PDの面積の小さいPD\_s1、PD\_s2と比較して大きな信号を出力することが可能であるため、垂直出力線VL\_Iの電圧の変動幅は、垂直出力線VL\_sの電圧の変動幅と比較して大きい。

#### 【 0 1 6 1 】

したがって、フォトダイオードPD\_Iの信号読み出し動作の駆動タイミングには、垂直出 50

力線VL\_Iの電圧レベルを十分応答させるために、特に長い時間間隔の設定が必要となる。一方で、フォトダイオードPD\_s1、PD\_s2の信号読み出し動作の駆動タイミングについては、フォトダイオードPD\_Iと比較してより短い時間間隔の設定で、垂直出力線VL\_sの電圧レベルの十分な応答が得られることとなる。

#### 【 0 1 6 2 】

そこで、本実施例では、フォトダイオードPD\_Iの蓄積信号が飽和した場合等、垂直出力線VL\_Iの電圧レベルの応答が遅くなる時、垂直出力線VL\_Iの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T8dからT16dまでの期間702Lを適宜決定する。

#### 【 0 1 6 3 】

また、フォトダイオードPD\_s1の読み出し動作についても同様である。フォトダイオードPD\_s1の蓄積信号が飽和した場合等、直出力線VL\_sの電圧レベルの応答が遅くなる時、垂直出力線VL\_sの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T8dからT11dまでの期間702S1を適宜決定する。10

#### 【 0 1 6 4 】

また、フォトダイオードPD\_s2の読み出し動作についても同様である。フォトダイオードPD\_s2の蓄積信号が飽和した場合等、直出力線VL\_sの電圧レベルの応答が遅くなる時、垂直出力線VL\_sの十分な応答を待って列メモリへの信号保持を行う。そのために、時刻T20dからT22dまでの期間702S2を適宜決定する。

#### 【 0 1 6 5 】

前述したとおり、フォトダイオードPD\_Iと比較して、フォトダイオードPD\_s1、PD\_s2は蓄積できる信号量が少ないため、垂直出力線VL\_sの電圧レベルの可変幅は垂直出力線VL\_Iと比較して小さい。そのため、前述したとおり、フォトダイオードPD\_s1、PD\_s2の読み出し動作時は、垂直出力線VL\_sが十分応答するまでの時間が、フォトダイオードPD\_Iの読み出し動作時に垂直出力線VL\_Iが十分応答するまでの時間に対して短くなる。従って、時刻T8dからT11dまでの期間702S1と時刻T20dからT22dまでの期間702S2を、時刻T8dからT17dまでの期間702Lと比較して、可能な範囲で短く設定する。20

#### 【 0 1 6 6 】

図7に示したタイミングチャートでは、T16dとT17dの時刻は同時となっているが、これらの時刻は、垂直出力線VL\_sの十分な応答に必要な期間702S及び垂直出力線VL\_Iの十分な応答に必要な期間702Lの長さに応じて決定されるので、この限りではない。また、他のタイミングについても同様に、垂直出力線VL\_sの十分な応答に必要な期間702S及び垂直出力線VL\_Iの十分な応答に必要な期間702Lの長さに応じて時刻が決定される。したがって、T11d以降の動作の駆動パルスの時刻及びT12d以降の駆動パルスの順序は図7に示した例に限定されない。30

#### 【 0 1 6 7 】

尚、PDからFDへの電荷転送にかける時間については、PD\_IとPD\_s1、PD\_s2とで異なる必要はないが、図7に示したタイミングチャートの様に、PD\_IとPD\_s1、PD\_s2とで異なるようにしてもよい。具体的には、一般に、PDの面積が異なればPDからFDへの電荷転送にかかる時間が異なる。そのため、図7に示したタイミングチャートでは、PD\_IからFD\_Iへの電荷転送にかける時間を、PD\_IからFD\_Iへと電荷を十分に転送するために必要な時間を考慮して決定している。また、PD\_s1、PD\_s2からFD\_sへの電荷転送にかける時間を、PD\_s1、PD\_s2からFD\_sへと電荷を十分に転送するために必要な時間を考慮して決定している。40

#### 【 0 1 6 8 】

例えば、ここでは、PD\_IからFD\_Iへの電荷転送に必要な時間が、PD\_s1、PD\_s2からFD\_sへの電荷転送に必要な時間と比較して長いものとする。そこで、PD\_IからFD\_Iへの電荷転送開始時刻T8dからその終了時刻T10dまでの時間期間を次のように設定する。即ち、PD\_s1からFD\_sへの電荷転送開始時刻T8dからその終了時刻T9dまでの時間期間に対して、時刻T8dからT10dまでの時間期間を長く設定している。同様に、PD\_IからFD\_Iへの電荷転送開始時刻T8dからその終了時刻T10dまでの時間期間を次のように設定する。即ち、PD\_s2からFD50

\_sへの電荷転送開始時刻T20dからその終了時刻T21dまでの時間期間に対して、時刻T8dからT10dまでの時間期間を長く設定している。

#### 【 0 1 6 9 】

本実施例は以上述べた例に限られず、例えば、信号の大きさ、素子の構成及びレイアウト等によって応答速度が異なる動作の駆動パルスにも適用可能である。もし、そのような駆動パルスがあれば、フォトダイオードPD\_s1、PD\_s2の読み出し動作とフォトダイオードPD\_Iの読み出し動作とで、異なるタイミングで駆動する設定にすればよい。

#### 【 0 1 7 0 】

また、PD\_s1、PD\_s2の出力可能な信号の大きさが異なり、それぞれの信号読み出し時で垂直出力線VL\_sの電圧の可変幅が異なる場合にも本発明を適用することが可能である。即ち、PD\_s1の読み出し動作と、PD\_s2のそれとで、異なるタイミングで駆動する様に設定すればよい。10

#### 【 0 1 7 1 】

実際の撮像素子においては、各駆動パルスの間隔は、撮像素子の画素及び読み出し回路、周辺回路を構成する回路素子とそのレイアウトを考慮したシミュレーションによって決定すればよい。あるいは、実際の撮像素子を用いて測定を行って各駆動パルスの間隔を決定してもよい。

#### 【 0 1 7 2 】

尚、ここでは、PD\_s1の信号読み出し(R0\_s1)を行った後に、PD\_s2の信号読み出し(R0\_s2)を行う例について示したが、R0\_s1とR0\_s2の順序を入れ替えて、PD\_s1の信号読み出しを先に行ってもよい。また、例えばPD\_s2を、PD\_s1およびPD\_Iのいずれの感度とも異なる感度のフォトダイオードにして、本実施例の駆動タイミング制御に従って信号を読み出す構成としてもよい。20

#### 【 0 1 7 3 】

更に、ここでは、PD\_s1の信号読み出し(R0\_s1)開始と同時に、PD\_Iの信号読み出し(R0\_I)を開始する例について示した。しかし、R0\_Iは、PD\_s1の読み出し動作R0\_s1、またはPD\_s2の読み出し動作R0\_s2のうち、先に行われる動作の開始時刻以降に開始すればよい。また、R0\_Iは、PD\_s1の読み出し動作R0\_s1、またはPD\_s2の読み出し動作R0\_s2のうち、後に行われる動作の終了時刻までに終了すればよい。例えば、図7の例では、T5d以降に開始し、T22dまでに終了するような任意のタイミングで行う様にすればよい。30

#### 【 0 1 7 4 】

本実施例の読み出し動作によれば、従来の読み出し動作での1フレームの読み出し時間を、([702L - 702S1] + [702L - 702S2]) × [画素632Bの行数]だけ短縮可能となる。これにより、フレームレートを容易に維持しながら1フレームの読み出しを完了することができる。

#### 【 0 1 7 5 】

以上の様に、各々の画素が扱う信号の大きさに応じて、駆動パルスの間隔を適宜設定することにより、本発明の目的である、1フレーム分の信号読み出しにかかる時間の短縮を実現することが可能となる。

#### 【 0 1 7 6 】

また、上述した実施形態において図3、図5及び図7に示した各駆動動作は、各駆動を実現する為のプログラムをメモリ(104など)から読み出してシステム制御部13のCPUが実行することによりその機能を実現させるものである。40

#### 【 0 1 7 7 】

上述したメモリは、光磁気ディスク装置、フラッシュメモリ等の不揮発性のメモリや、CD-ROM等の読み出しのみが可能な記憶媒体、RAM以外の揮発性のメモリで構成されてもよい。あるいは、これらの組合せによるコンピュータ読み取り、書き込み可能な記憶媒体より構成されてもよい。

#### 【 0 1 7 8 】

また、図3、図5及び図7に示した各駆動動作を実現する為のプログラムをコンピュー50

タ読み取り可能な記憶媒体に記録して、この記憶媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより各処理を行っても良い。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。具体的には、記憶媒体から読み出されたプログラムが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書きこまれる。その後、そのプログラムの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含む。

#### 【0179】

また、「コンピュータ読み取り可能な記憶媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD-ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらには、インターネット等のネットワークや電話回線等の通信回線を介してプログラムが送信された場合のサーバやクライアントとなるコンピュータシステム内部の揮発メモリ(RAM)のように、一定時間プログラムを保持しているものも含むものとする。

10

#### 【0180】

また、上記プログラムは、このプログラムを記憶装置等に格納したコンピュータシステムから、伝送媒体を介して、あるいは、伝送媒体中の伝送波により他のコンピュータシステムに伝送されてもよい。ここで、プログラムを伝送する「伝送媒体」は、インターネット等のネットワーク(通信網)や電話回線等の通信回線(通信線)のように情報を伝送する機能を有する媒体のことをいう。

20

#### 【0181】

また、上記プログラムは、前述した機能の一部を実現するものであっても良い。さらに、前述した機能をコンピュータシステムに既に記録されているプログラムとの組合せで実現できるもの、いわゆる差分ファイル(差分プログラム)であっても良い。

#### 【0182】

また、上記のプログラムを記録したコンピュータ読み取り可能な記憶媒体等のプログラムプロダクトも本発明の実施形態として適用することができる。上記のプログラム、記憶媒体、伝送媒体およびプログラムプロダクトは、本発明の範疇に含まれる。

30

#### 【0183】

以上、この発明の好ましい実施形態について図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等における変形、修正も含まれる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100134393

弁理士 木村 克彦

(74)代理人 100174230

弁理士 田中 尚文

(72)発明者 斎藤 槟子

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2000-059687(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257