(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4926692号

(P4926692)

(45) 発行日 平成24年5月9日(2012.5.9)

(24) 登録日 平成24年2月17日(2012.2.17)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| H01L 23/12 | (2006.01) | H01L 23/12 | 501B |

| H05K 3/28  | (2006.01) | H01L 23/12 | N    |

| H01L 25/10 | (2006.01) | H01L 23/12 | B    |

| H01L 25/11 | (2006.01) | H05K 3/28  | G    |

| H01L 25/18 | (2006.01) | H01L 25/14 | Z    |

請求項の数 9 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2006-351000 (P2006-351000)

(22) 出願日

平成18年12月27日 (2006.12.27)

(65) 公開番号

特開2008-166327 (P2008-166327A)

(43) 公開日

平成20年7月17日 (2008.7.17)

審査請求日

平成21年10月23日 (2009.10.23)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 荒井 直

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 小林 敏男

長野県長野市小島田町80番地 新光電氣

工業株式会社内

審査官 宮崎 園子

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法と半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

上下側を導通可能にする配線パターンを備えた複数のユニット配線板が、接続端子を介して相互接続されて積層されて構成されるベース配線板と、

前記ベース配線板の上に積層され、上下側を導通可能にする配線パターンを備えて、前記ベース配線板の前記配線パターンに接続端子を介して接続されたシリコンインターポーラーと、

前記複数のユニット配線板の間の隙間、及び前記ベース配線板と前記シリコンインターポーラーとの隙間に充填され、前記ベース配線板及び前記シリコンインターポーラーを一体化する樹脂部とを有し、

前記樹脂部は、前記隙間から前記ベース配線板及び前記シリコンインターポーラーの側方にかけて繋がって形成され、

前記シリコンインターポーラーはその上面が前記樹脂部から露出した状態で前記樹脂部に埋設され、かつ、前記ベース配線板の最下の前記ユニット配線板はその下面が前記樹脂部から露出した状態で前記樹脂部に埋設されていることを特徴とする配線基板。

## 【請求項 2】

前記ユニット配線板は、絶縁層の両面側にスルーホール導電層を介して相互接続された前記配線パターンがそれぞれ形成されて構成され、上側に配置された前記ユニット配線板の下面側の前記配線パターンに前記接続端子が設けられていることを特徴とする請求項1に記載の配線基板。

**【請求項 3】**

前記ベース配線板には、前記樹脂部に埋設された状態で半導体チップ及び受動部品のいずれか又は両方が接続されて実装されていることを特徴とする請求項 1 又は 2 に記載の配線基板。

**【請求項 4】**

前記半導体チップは、下側の前記ユニット配線板にフリップチップ接続され、前記ユニット配線板の間に充填された前記樹脂部に埋設されていることを特徴とする請求項 3 に記載の配線基板。

**【請求項 5】**

前記樹脂部はフィラーを含有し、前記樹脂部の熱膨張係数が 7 乃至 20 ppm / 10 かつ弾性率が 15 ~ 25 GPa であることを特徴とする請求項 1 又は 2 に記載の配線基板。

**【請求項 6】**

請求項 1 乃至 5 のいずれか一項の配線基板と、

前記シリコンインターポーラの上面側の前記配線パターンに接続されて実装された半導体チップとを有することを特徴とする半導体装置。

**【請求項 7】**

上下側を導通可能にする配線パターンを備えた複数のユニット配線板が、接続端子を介して相互接続されて積層されて構成されるベース配線板と、上下側を導通可能にする配線パターンを備えたシリコンインターポーラとを用意し、前記ベース配線板の前記配線パターンに前記シリコンインターポーラを接続端子を介して接続することにより、インターポーラ付き配線基板を得る工程と、

前記インターポーラ付き配線基板にモールド金型を設置し、真空トランスマーモールド法によって、前記複数のユニット配線板の隙間、及び前記ベース配線板と前記シリコンインターポーラとの隙間に樹脂を充填することにより、前記ベース配線板及び前記シリコンインターポーラを一体化する樹脂部を形成する工程とを有し、

前記シリコンインターポーラはその上面が前記樹脂部から露出した状態で前記樹脂部に埋設され、前記ベース配線板の最下の前記ユニット配線板はその下面が前記樹脂部から露出した状態で前記樹脂部に埋設されることを特徴とする配線基板の製造方法。

**【請求項 8】**

前記樹脂部を形成する工程において、前記モールド金型は下型及び下面に凹部を備えた上型から構成され、前記上型の凹部側の面に、前記樹脂部から前記上型を分離するためのリリースフィルムが設けられていることを特徴とする請求項 7 に記載の配線基板の製造方法。

**【請求項 9】**

前記樹脂部はフィラーを含有し、前記樹脂部の熱膨張係数が 7 乃至 20 ppm / で、かつ弾性率が 15 ~ 25 GPa であることを特徴とする請求項 7 又は 8 に記載の配線基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は配線基板及びその製造方法と半導体装置に係り、さらに詳しくは、高性能な半導体チップの実装に対応できるシリコンインターポーラが内蔵された配線基板及びその製造方法と半導体装置に関する。

**【背景技術】****【0002】**

従来、CPUなどの半導体チップが配線基板の上に実装されて構成される半導体装置がある。半導体チップを実装するための配線基板としては、ファインピッチの配線が多層化されて形成されたビルドアップ配線板が一般的に使用されている。

**【0003】**

10

20

30

40

50

近年では、半導体チップのさらなる高性能化に伴ってその接続電極のピッチが狭小化されてきている。ビルドアップ配線板の配線のファインピッチ化には限界があるので、そのような半導体チップをビルドアップ配線板に直接実装することが困難になりつつある。その対策として、上下側を導通可能にする微細配線を備えたシリコンインターポーラを介して半導体チップをビルドアップ配線板に接続する方法が提案されている。

#### 【0004】

特許文献1には、半導体チップ内の配線層数を減らすために半導体チップ内の配線の機能をインターポーラに移し、配線基板の上にインターポーラを介して半導体チップを実装することが記載されている。

#### 【0005】

特許文献2には、外部接続端子を備えた第1の配線基板に半導体素子が実装された上部装置部と、接続用電極を備えた第2の配線基板に半導体素子が実装された下部装置部との間に、インターポーラ基板を配設することが記載されている。

【特許文献1】特開2001-102479号公報

【特許文献2】特開2004-273938号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0006】

前述したように、半導体チップの高性能化に伴ってビルドアップ配線板の配線のさらなるファインピッチ化や多層化、さらにはシリコンインターポーラの導入が必要となり、これによって半導体装置のコスト上昇や歩留り低下を招きやすい。

#### 【0007】

例えば、ビルドアップ配線板のスルーホールランドから配線を引き回してシリコンインターポーラが接続されるインターポーラ用パッドを配置する際に、配線の引き回しの途中でスルーホールランドが邪魔になって配線を引き回せない場合は、ビルドアップ配線板の配線の層数を増やして対応する必要がある。

#### 【0008】

このとき、従来技術のビルドアップ配線板では、片面側の配線の追加のみで対応できる場合であっても、反りの発生を防止するためにコア基板の両面側に配線を対称に形成する必要があり、無駄なコストがかかる問題がある。

#### 【0009】

このように、従来技術のビルドアップ配線板では、半導体チップの高性能化に対応させる際に、不必要な配線を形成する必要があることから配線の層数が膨大になるケースが想定され、コスト上昇や歩留りの低下が懸念される。さらには、ビルドアップ配線板の上にシリコンインターポーラを接続してインターポーラ内蔵配線基板を構成する際に、高い信頼性が得られる構造が要求される。

#### 【0010】

本発明は以上の課題を鑑みて創作されたものであり、シリコンインターポーラを内蔵する配線基板において、シリコンインターポーラの仕様に対応させて配線パターンの層数を必要最小限に設定できると共に、製造工程が簡略化されて低コスト・高歩留りで製造される信頼性の高い配線基板及びその製造方法と半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0011】

上記課題を解決するため、本発明は配線基板に係り、上下側を導通可能にする配線パターンを備えた複数のユニット配線板が、接続端子を介して相互接続されて積層されて構成されるベース配線板と、前記ベース配線板の上に積層され、上下側を導通可能にする配線パターンを備えて、前記ベース配線板の前記配線パターンに接続端子を介して接続されたシリコンインターポーラと、前記複数のユニット配線板の間の隙間、及び前記ベース配線板と前記シリコンインターポーラとの隙間に充填され、前記ベース配線板及び前記シリコンインターポーラを一体化する樹脂部とを有することを特徴とする。

10

20

30

40

50

**【 0 0 1 2 】**

本発明の配線基板を構成するベース配線板は、上下側を導通可能にする配線パターンを備えた複数のユニット配線板が厚さ方向に積層されて接続端子を介して相互接続されて構成される。ベース配線板の上には高性能な半導体チップが実装される微細配線を備えたシリコンインターポーラが接続端子を介して接続されている。

**【 0 0 1 3 】**

さらに、複数のユニット配線板の隙間及びベース配線板とシリコンインターポーラとの隙間に樹脂部が充填されており、樹脂部がベース配線板及びシリコンインターポーラを一体化する基板として機能する。シリコンインターポーラはその上面の半導体チップ搭載面が露出した状態で樹脂部に埋設されている。

10

**【 0 0 1 4 】**

本発明の配線基板では、高性能な半導体チップの狭小ピッチの接続電極が微細配線を備えたシリコンインターポーラに接続され、シリコンインターポーラからベース配線板にピッチ変換される。

**【 0 0 1 5 】**

本発明では、上下側を導通可能にする配線パターンを備えたユニット配線板を1ユニットとして使用し、それを積層して接続することによりベース配線板を構成している。このため、従来技術のビルドアップ配線板と違って、配線の層数を増やす際に、反りの防止を考慮してコア基板の両面に配線パターンを対称に形成する必要はなく、シリコンインターポーラの仕様に対応させて必要最小限の配線パターンの層数でベース配線板を構成することができる。従って、不必要的配線パターンの形成によるコスト上昇や歩留り低下を招くおそれがない。

20

**【 0 0 1 6 】**

本発明の一つの好適な態様では、樹脂部の材料として、多量のフィラーを含むモールドコンパウンド樹脂（例えばシリカフィラーが85～90%含有されたエポキシ樹脂）が使用され、樹脂部の熱膨張係数が7～20 ppm/°Cであり、弾性率が15～25 GPaである。そのような樹脂材料から樹脂部を形成することにより、一般的な樹脂材料を使用する場合よりも、シリコンインターポーラ、ベース配線板及び樹脂部の間で熱膨張係数を近似させることができるので、配線基板の反りの発生を抑制することができる。さらには、樹脂部は、高い弾性率を有する樹脂材料から形成されるので、ベース配線板及びシリコンインターポーラを一体的に支持する剛性が高い基板として機能する。

30

**【 0 0 1 7 】**

このように、本発明では、ベース配線板及びシリコンインターポーラが、反りの発生を抑える剛性の強い樹脂によって封止されるので、信頼性の高い配線基板が構成される。

**【 0 0 1 8 】**

また、上記課題を解決するため、本発明は配線基板の製造方法に係り、上下側を導通可能にする配線パターンを備えた複数のユニット配線板が、接続端子を介して相互接続されて積層されて構成されるベース配線板と、上下側を導通可能にする配線パターンを備えたシリコンインターポーラとを用意し、前記ベース配線板の前記配線パターンに前記シリコンインターポーラを接続端子を介して接続することにより、インターポーラ付き配線基板を得る工程と、前記インターポーラ付き配線基板にモールド金型を設置し、真空トランスマーキュラード法によって、前記複数のユニット配線板の隙間、及び前記ベース配線板と前記シリコンインターポーラとの隙間に樹脂を充填することにより、前記ベース配線板及び前記シリコンインターポーラを一体化する樹脂部を形成する工程とを有することを特徴とする。

40

**【 0 0 1 9 】**

本発明の配線基板の製造方法を採用することにより、上記した配線基板を容易に製造することができる。本発明では、まず、複数のユニット配線板を積層してベース配線板を構成し、ベース配線板の上にシリコンインターポーラを接続してインターポーラ付き配線基板を得る。その後に、インターポーラ付き配線基板にモールド金型を設置し、真空トラン

50

スファモールド法によって複数のユニット配線板の隙間及びベース配線板とシリコンインターポーザとの隙間に樹脂を充填する。真空トランスファモールド法を使用することにより、フィラーを多量に含むモールドコンパウンド樹脂であっても微細な隙間に樹脂を信頼性よく充填することができる。

【発明の効果】

【0020】

以上説明したように、本発明の配線基板では、ユニット配線板が積層されたベース配線板の上にシリコンインターポーザが接続され、それらの隙間に樹脂が充填されて構成されるので、低コスト・高歩留りで製造されて高い信頼性が得られる。

【発明を実施するための最良の形態】

10

【0021】

以下、本発明の実施の形態について、添付の図面を参照して説明する。

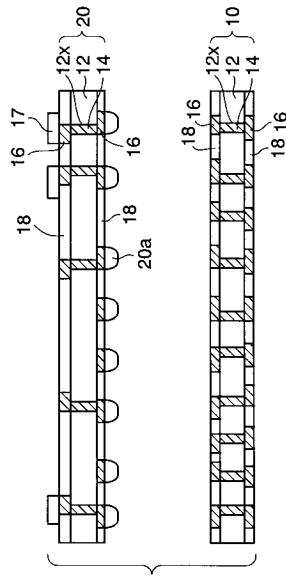

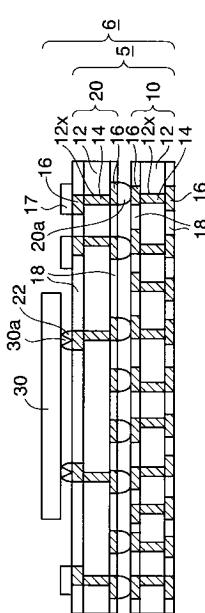

【0022】

図1～図6は本発明の実施形態の配線基板の製造方法を示す断面図、図7～図9は本発明の実施形態の配線基板を示す断面図、図10及び図11は同じく半導体装置を示す断面図である。

【0023】

本実施形態の配線基板の製造方法では、図1に示すように、まず、上下側を導通可能にする配線パターン16を備えたシート状の第1ユニット配線板10及び第2ユニット配線板20を用意する。第1ユニット配線板10では、ガラスクロスを含むエポキシ樹脂(ブリプレグ)などから形成された絶縁層12にスルーホール12xが形成されている。スルーホール12xの中には銅などからなるスルーホール導電層14が充填されている。

20

【0024】

さらに、絶縁層12の両面側には銅などからなる配線パターン16が形成されており、両面側の配線パターン16はスルーホール導電層14を介して相互接続されている。また、絶縁層12の両面側には、配線パターン16の接続部上に開口部が設けられたソルダレジスト18がそれぞれ形成されている。

【0025】

第2ユニット配線板20では、第1ユニット配線板10と同様に、絶縁層12の両面側に、スルーホール12x内のスルーホール導電層14を介して相互接続された配線パターン16がそれぞれ形成されている。また、第1ユニット配線板10と同様に、絶縁層12の両面側に配線パターン16の接続部上に開口部が設けられたソルダレジスト18がそれぞれ形成されている。また、第2ユニット配線板20の上面側の配線パターン16にはキャパシタ部品17が接続されて実装されている。なお、キャパシタ部品17の他に、抵抗部品やインダクタ部品などの受動部品が実装されていてもよい。

30

【0026】

さらに、第2ユニット配線板20では、絶縁層12の下面側の配線パターン16の接続部に接続端子20aが設けられている。接続端子20aは、銀(Ag)ペースト、はんだペースト、はんだボール、外面にはんだが被覆された銅ボール、又は金バンプなどから形成され、その高さは30～100μmに設定される。

40

【0027】

第1ユニット配線板10及び第2ユニット配線板20の各配線パターン16は、絶縁層12にスルーホール12xが形成され、次いでスルーホール12x内から絶縁層12の両面に繋がる金属層がめっきによって形成された後に、フォトリソグラフィ及びエッティングによって金属層がパターン化されて形成される。あるいは、銅張積層板を加工することに基づいてその両面側に配線パターンを形成してもよい。第1ユニット配線板10及び第2ユニット配線板20の各配線パターン16の最小幅は例えば30～50μmに設定される。

【0028】

なお、第1ユニット配線板10及び第2ユニット配線板20の各配線パターン16が両

50

面側に1層ずつ形成された形態を例示したが、配線パターン16が絶縁層12の両面側にn層(nは2以上の整数)でそれぞれ積層されていてもよい。また、第1、第2ユニット配線板10,20は、フレキシブル配線板であってもよいし、リジッド配線板であってもよい。

#### 【0029】

次いで、図2に示すように、第2ユニット配線板20の接続端子20aが第1ユニット配線板10の上側の配線パターン16の接続部に対応するように、第1ユニット配線板10の上に第2ユニット配線板20を配置する。さらに、180~220の温度で熱処理することにより、第2ユニット配線板20の接続端子20aを第1ユニット配線板10の上面の配線パターン16の接続部に接合する。第2ユニット配線板20の接続端子20aが金バンプからなる場合は、第1ユニット配線板10の配線パターン16の接続部に金層が形成され、超音波接合によって接続される。

10

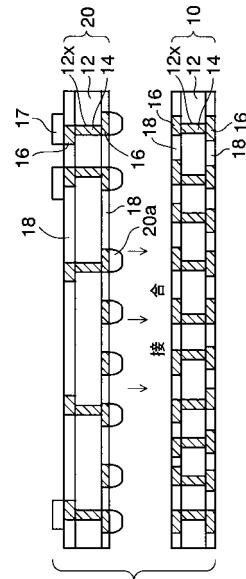

#### 【0030】

これにより、図3に示すように、2層の配線パターン16をそれぞれ備えた第1、第2ユニット配線板10,20が厚さ方向に3次元的に積層されて接続され、これによってベース配線板5が構成される。ベース配線板5は、スルーホール導電層14及び接続端子20aによって相互接続された4層の配線パターン16を備えて構成され、最上の配線パターン16にキャパシタ部品17が実装されている。なお、第2ユニット配線板20に接続端子20aを設ける代わりに、第1ユニット配線板10の上面の配線パターン16に接続端子を設けるようにしてもよい。

20

#### 【0031】

続いて、図4に示すように、上下側を導通可能にする配線パターン36を備えたシリコンインターポーザ30を用意する。シリコンインターポーザ30では、シリコン基板32にスルーホール32xが設けられており、シリコン基板32の両面及びスルーホール32xの内面に絶縁層33が形成されている。スルーホール32xの中には銅などからなるスルーホール導電層34が充填されている。さらに、シリコン基板32の両面側にはスルーホール導電層34を介して相互接続された銅などからなる配線パターン36がそれぞれ形成されている。

#### 【0032】

シリコンインターポーザ30は半導体集積回路の製造プロセスを使用して製造されるので、前述したベース配線板5の配線パターン16よりもファインピッチで形成され、その最小幅は例えば3~5μmで形成される。また、シリコンインターポーザ30の下面の配線パターン36には高さが30~100μmの金バンプなどからなる接続端子30aが設けられている。なお、シリコンインターポーザ30の配線パターン36はシリコン基板32の両面側に任意の層数で積層されていてもよい。

30

#### 【0033】

さらに、同じく図4に示すように、ベース配線板5の最上の配線パターン16のインターポーザ用の接続部にはんだボール又ははんだペーストからなるはんだ材22を形成する。続いて、シリコンインターポーザ30の接続端子30aがベース配線板5上のはんだ材22に対応するように、インターポーザ30をベース配線板5の上に配置する。さらに、180~220の温度で熱処理することにより、インターポーザ30の接続端子30aをベース配線板5に設けられたはんだ材22に接合してベース配線板5の配線パターン16に電気的に接続する。

40

#### 【0034】

これにより、図5に示すように、ベース配線板5の上にシリコンインターポーザ30が3次元的に積層されて接続され、これによってインターポーザ付き配線基板6が得られる。この時点では、第1ユニット配線板10と第2ユニット配線板20との間、及び第2ユニット配線板20とシリコンインターポーザ30との間には、第2ユニット配線板20の接続端子20a及びシリコンインターポーザ30の接続端子30aの厚みに相当する隙間がそれぞれ存在する。

50

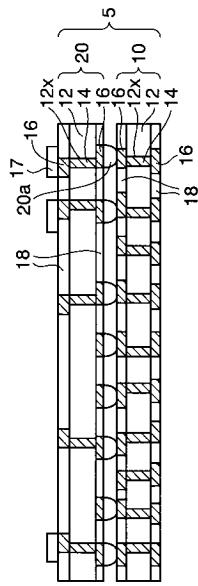

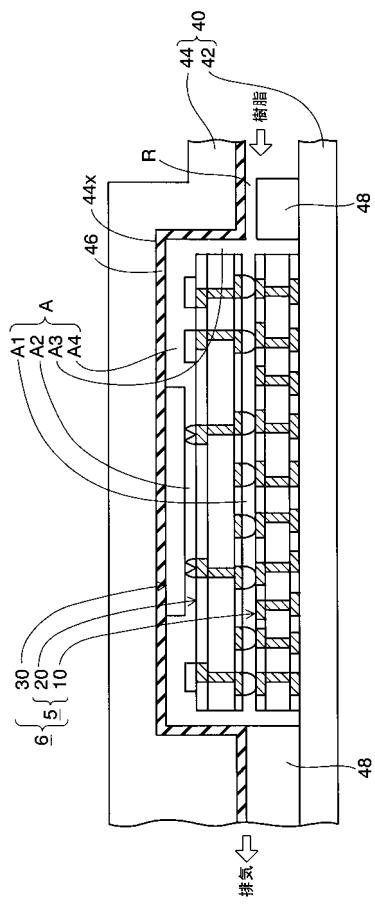

## 【0035】

次いで、図6に示すように、下型42及び上型44から基本構成されるモールド金型40を用意する。そして、下型42の上に図5のインターポーザ付き配線基板6を配置する。さらに、下面側に凹部44xを備えた上型44をインターポーザ付き配線基板6の上に配置する。上型44の下面にはリリースフィルム46が設けられており、インターポーザ付き配線基板6のシリコンインターポーザ30の上面はリリースフィルム46で押えられた状態となる。リリースフィルム46は、シリコンインターポーザ30を保護すると共に、樹脂を充填した後に上型44を樹脂から容易に分離するための剥離層として機能する。

## 【0036】

また、下型42の周縁部上にはインターポーザ付き配線基板6を取り囲むようにスペーサ48が配置されており、インターポーザ付き配線基板6の一辺の領域にはスペーサ48と上型44によって樹脂流入部Rが構成されている。また、樹脂流入部R以外の領域に配置されるスペーサ48は上型44の下に配置されたリリースフィルム46に接触しており、樹脂流入がそこでストップするようになっている。

10

## 【0037】

このようにして、インターポーザ付き配線基板6を下型42と上型44とによって挟むことにより、樹脂流入部Rとそれに繋がって樹脂が充填される空間Aが構成される。樹脂が充填される空間Aは、第1ユニット配線板10と第2ユニット配線板20との隙間A1、第2ユニット配線板20とシリコンインターポーザ30との隙間A2、ベース配線板5の外周側面とモールド金型40との隙間A3、及びシリコンインターポーザ30の周辺の隙間A4である。

20

## 【0038】

次いで、同じく図6に示すように、溶融された樹脂を樹脂流入部Rを通してモールド金型40によって構成される空間Aに流し込む。このとき、空間Aを減圧して（又は真空にして）エアを排気した状態で樹脂が流入される。このようにして、樹脂が樹脂流入部Rからモールド金型40の中の空間Aに流入し、第1ユニット配線板10と第2ユニット配線板20との隙間A1及び第2ユニット配線板20とシリコンインターポーザ30との隙間A2などに樹脂が充填される。

## 【0039】

さらに、空間Aに押し込まれた樹脂を熱処理して硬化させた後に、インターポーザ付き配線基板6からモールド金型40を取り外して樹脂を露出させる。このとき、上型44の下面にはリリースフィルム46が存在するので、上型44を樹脂から容易に取り外すことができる。その後に、樹脂流入部Rに形成された樹脂を折り取って廃棄する。

30

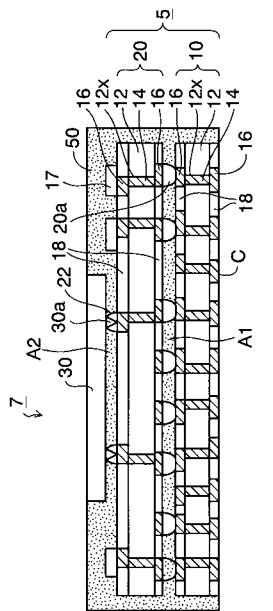

## 【0040】

これにより、図7に示すように、第1ユニット配線板10と第2ユニット配線板20との隙間A1及び第2ユニット配線板20とシリコンインターポーザ30との隙間A2などに樹脂が充填されて、ベース配線板5とシリコンインターポーザ30とを一体化する樹脂部50が形成される。なお、第1ユニット配線板10と第2ユニット配線板20との隙間A1及び第2ユニット配線板20とシリコンインターポーザ30との隙間A2が比較的広い（100μm程度）場合は、空間Aを減圧することなく大気の状態で樹脂を充填することも可能である。

40

## 【0041】

樹脂部50の材料としては、径が30μm程度以下のシリカフィラーが85～90%含有されたエポキシ樹脂（モールドコンパウンド樹脂）が好適に使用され、その熱膨張係数は7～20ppm/°Cであり、弾性率は15～25GPaである。樹脂部50はベース配線板5及びインターポーザ30を一体化する基板として機能し、上記した特性の樹脂材料を採用することにより、十分な剛性を有すると共に、後述するように反りの発生を抑制することができる。

## 【0042】

また、一般的に、毛細管現象を利用して液状樹脂を隙間に充填する方法では、フィラー

50

を多量に含む樹脂を狭い隙間に充填することは困難を極める。本実施形態では、第1ユニット配線板10と第2ユニット配線板20との隙間A1及び第2ユニット配線板20シリコンインターポーザ30との隙間A2がかなり狭い(例えば30μm)場合であっても、真空トランスファモールド法によって樹脂を充填するので、フィラーを多量に含む樹脂を狭い隙間に信頼性よく充填することが可能である。

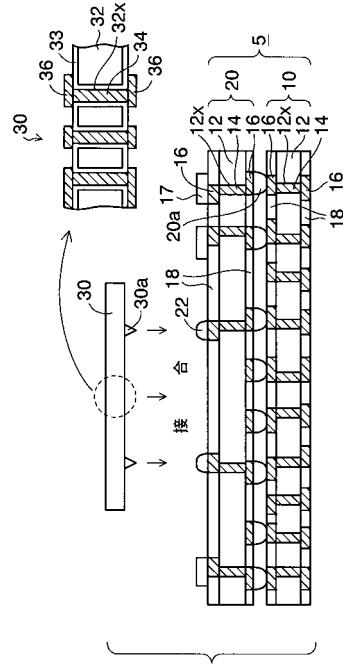

#### 【0043】

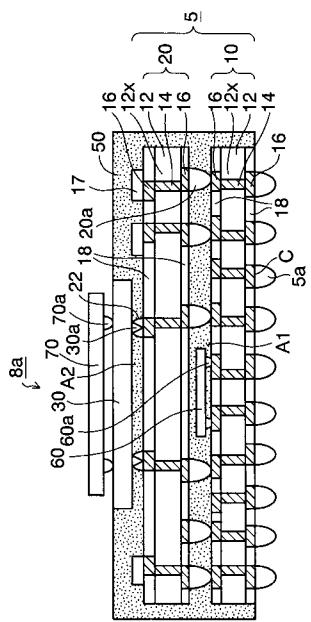

以上により、図7に示すように、本実施形態のインターポーザ内蔵配線基板7が得られる。図7に示すように、本実施形態のインターポーザ内蔵配線基板7では、第1ユニット配線板10の上に第2ユニット配線板20が厚さ方向に積層されて接続されてベース配線板5が構成されている。

10

#### 【0044】

第1ユニット配線板10では、絶縁層12の両面側に配線パターン16がそれぞれ形成されており、配線パターン16は絶縁層12のスルーホール12x内に充填されたスルーホール導電層14を介して相互接続されている。さらに、絶縁層12の両面側には配線パターン16の接続部上に開口部が設けられたソルダレジスト18がそれぞれ形成されている。

#### 【0045】

第2ユニット配線板20では、第1ユニット配線板10と同様に、絶縁層12の両面側にスルーホール導電層14を介して相互接続される配線パターン16がそれぞれ形成されている。また、絶縁層12の両面側には配線パターン16の接続部上に開口部が設けられたソルダレジスト18がそれぞれ形成されている。また、第2ユニット配線板20の上面の配線パターン16にキャパシタ部品17が接続されて実装されている。さらに、絶縁層12の下面側の配線パターン16の接続部に接続端子20aが設けられている。

20

#### 【0046】

そして、第1ユニット配線板10の配線パターン16の接続部に第2ユニット配線板20の接続端子20aが接合されて電気的に相互接続されている。

#### 【0047】

さらに、ベース配線板5の上にシリコンインターポーザ30が厚さ方向に積層されて接続されている。シリコンインターポーザ30では、前述した図4で説明したように、シリコン基板32の両面側にスルーホール導電層34を介して相互接続される配線パターン36が形成され、その下面の配線パターン36の接続部に金パンプなどからなる接続端子30aが設けられている。そして、シリコンインターポーザ30の接続端子30aがベース配線板5の配線パターン16の接続部にはんだ材22によって接合されている。

30

#### 【0048】

さらに、第1ユニット配線板10と第2ユニット配線板20との隙間A1及び第2ユニット配線板20シリコンインターポーザ30との隙間A2に樹脂部50が充填されている。樹脂部50はそれらの隙間A1,A2からベース配線板5及びシリコンインターポーザ30の側方にかけて繋がって一体的に形成されている。

#### 【0049】

ベース配線板5及びシリコンインターポーザ30の側面は樹脂部50で被覆されていると共に、ベース配線板5の上に実装されたキャパシタ部品17が樹脂部50の中に埋設されている。シリコンインターポーザ30はその上面の半導体チップ搭載面が露出した状態で樹脂部50に埋設されており、シリコンインターポーザ30の上面と樹脂部50の上面が同一面となっている。

40

#### 【0050】

このようにして、ベース配線板5及びシリコンインターポーザ30が樹脂部50によって一体化されており、樹脂部50はインターポーザ内蔵配線基板7の基板として機能する。図7には、外部接続方式をLGA(Land Grid Array)型として使用する例が示されており、ベース配線板5の下面の配線パターン16の接続部Cがランドとして使用される。

#### 【0051】

50

本実施形態では、樹脂部 50 の材料として、前述したように、反りの発生を防止するために熱膨張係数が 7 ~ 20 ppm / の樹脂が使用される。シリコンインターポーラ 30 の熱膨張係数が 3 ppm / 程度で、ベース配線板 5 の熱膨張係数が 18 ppm / 程度であり、一般的な樹脂材料（熱膨張係数：40 ~ 100 ppm / ）を使用する場合よりも、シリコンインターポーラ 30 、ベース配線板 5 及び樹脂部 50 の間で、熱膨張係数を近似させることができる。

#### 【0052】

シリコンインターポーラ 30 、ベース配線板 5 及び樹脂部 50 の間で熱膨張係数が大きく異なる場合、樹脂を熱処理して硬化させる際などに熱膨張係数の差に基づく熱応力の発生によってインターポーラ内蔵配線基板 7 に反りが発生しやすい。10 反りが発生すると、後工程でのハンドリングに支障をきたしたり、実装基板（マザーボード）に実装する際にそれらの接合の信頼性が低下するなどの不具合が発生したりするおそれがある。

#### 【0053】

しかしながら、本実施形態では、上記したように、シリコンインターポーラ 30 、ベース配線板 5 及び樹脂部 50 の間で熱膨張係数が近似しているので、インターポーラ内蔵配線基板 7 の反りの発生を抑制することができ、信頼性を向上させることができる。

#### 【0054】

また、真空トランスファモールド法によって、第 1 ユニット配線板 10 と第 2 ユニット配線板 20 の隙間 A1 及び第 2 ユニット配線板 20 とシリコンインターポーラ 30 との隙間 A2 に樹脂が信頼性よく充填されて樹脂部 50 が形成される。しかも、樹脂部 50 は、高い弾性率を有する樹脂材料から形成されるので、ベース配線板 5 及びシリコンインターポーラ 30 を一体的に支持する剛性の高い基板として機能する。20

#### 【0055】

さらには、本実施形態では、絶縁層 12 の両面側に相互接続された配線パターン 16 が設けられた第 1 、第 2 ユニット配線板 10 , 20 を 1 ユニットとしてそれぞれ使用し、それらを積層することによりベース配線板 5 を構成している。

#### 【0056】

このため、従来技術のビルトアップ配線板と違って、反りを防止するためにコア基板の両面に配線パターンを対称に形成する必要はなく、シリコンインターポーラ 30 の仕様に対応させて必要最小限の配線パターンの層数でベース配線板 5 を構成できる。従って、無駄な配線パターンを形成する必要がなくなるので、不必要的配線パターンの形成によるコスト上昇や歩留り低下を招くこともない。30

#### 【0057】

なお、本実施形態では、第 1 ユニット配線板 10 と第 2 ユニット配線板 20 を積層してベース配線板 5 を構成したが、ユニット配線板の積層数は、設計仕様に合わせて第 n ユニット配線板（n は 2 以上の整数）まで任意に設定して積層することができる。

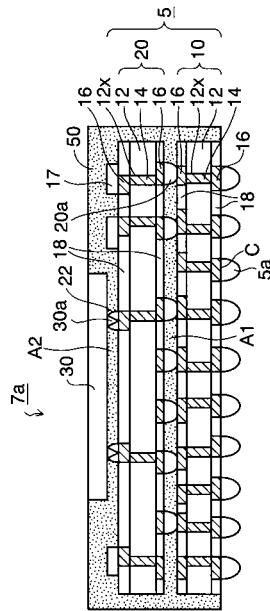

#### 【0058】

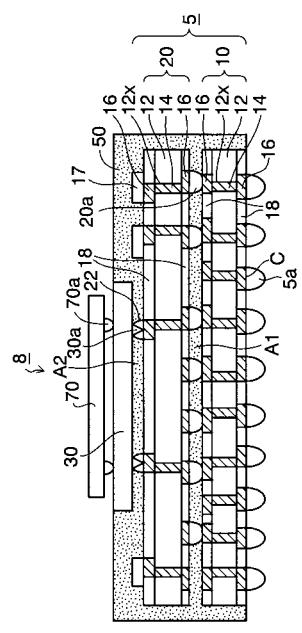

また、図 8 に示すインターポーラ内蔵基板 7a のように、図 7 のインターポーラ内蔵配線基板 7 の下面側の配線パターン 16 の接続部 C にはんだボールなどを搭載して外部接続端子 5a を設けて BGA (Ball Grid Array) 型として使用してもよい。あるいは、PGA (Pin Grid Array) 型として使用する場合は、インターポーラ内蔵配線基板 7 の下面側の配線パターン 16 の接続部 C にリードピンが設けられる。40

#### 【0059】

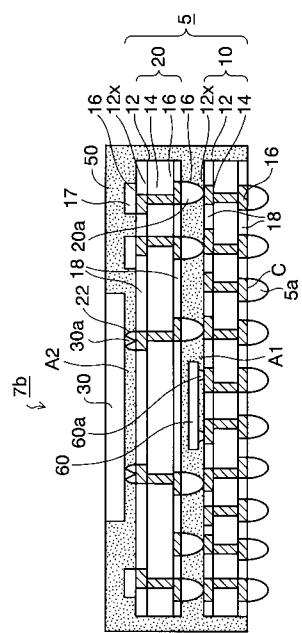

図 9 には、本実施形態の変形例のインターポーラ内蔵配線基板 7b が示されている。変形例のインターポーラ内蔵配線基板 7b では、図 8 のインターポーラ内蔵配線基板 7a の第 1 ユニット配線板 10 の上面の配線パターン 16 の接続部に半導体チップ 60 (LSI チップ) のバンプ 60a がフリップチップ接続されており、半導体チップ 60 が樹脂部 50 の中に埋設されている。第 1 ユニット配線板 10 と半導体チップ 60 との間の隙間に樹脂部 50 が充填されている。

#### 【0060】

10

20

30

40

50

半導体チップ 60 は、第 2 ユニット配線板 20 の接続端子 20a の高さによって構成される空間に収容され、樹脂部 50 で封止されている。第 2 ユニット配線板 20 の接続端子 20a は、半導体チップ 60 の厚みに合わせて第 1 ユニット配線板 10 と第 2 ユニット配線板 20 との間に半導体チップ 60 が収容されるようにその高さが調整される。変形例のインターポーザ内蔵配線基板 7b においても、前述したような真空トランスマールド法によって樹脂部 50 が充填される。

#### 【0061】

図 10 には本実施形態の半導体装置 8 が示されている。図 8 のインターポーザ内蔵配線基板 7a のシリコンインターポーザ 30 の上面の配線パターン 36 (図 4) の接続部に半導体チップ 70 (LSIチップ) のバンプ 70a がフリップチップ接続されて実装され、半導体装置 8 が構成される。ベース配線板 5 に実装されたキャパシタ部品 17 は半導体チップ 70 の電源ラインとグラウンドラインの間に接続されてデカップリングキャパシタとして機能する。10

#### 【0062】

半導体チップ 70 (シリコンチップ) は熱膨張係数が同一のシリコンインターポーザ 30 の上に実装されるので、半導体装置 8 の反りの発生を抑制することができる。なお、必要に応じて、シリコンインターポーザ 30 と半導体チップ 70 との隙間にアンダーフィル樹脂を充填してもよい。

#### 【0063】

なお、1つの配線基板から複数の個々の配線基板を多面取りする場合は、半導体チップ 70 を実装する前又は後に、配線基板が切断される。20

#### 【0064】

その他の形態としては、ベース配線板 5 の上にシリコンインターポーザ 30 が実装された構造のユニットを 2つ用意し、それらが対称になるように接続端子で接続することにより、配線基板の両面側にシリコンインターポーザが配置され、両面側に半導体チップが実装された形態としてもよい。この形態の場合、配線基板の下面周縁側の配線パターンに外部接続端子が接続される。

#### 【0065】

図 11 には、本発明の実施形態の変形例の半導体装置 8a が示されている。図 11 に示すように、変形例の半導体装置 8a では、図 9 のインターポーザ内蔵配線基板 7b のインターポーザ 30 に半導体チップ 70 のバンプ 70a がフリップチップ接続されて構成される。30

#### 【0066】

本実施形態の半導体装置 8, 8a では、狭小ピッチの接続電極を備えた高性能な半導体チップ 70 を実装する場合であっても、それに対応する微細な配線パターン 36 を備えたシリコンインターポーザ 30 の上に半導体チップ 70 を実装することにより、半導体チップ 70 の接続電極のピッチ変換を行ってベース配線板 5 に電気的に接続することができる。

#### 【0067】

また、前述したように、本実施形態のベース配線板 5 は、シリコンインターポーザの仕様に合わせて必要最小限のユニット配線板を積層して構成できるので、半導体装置のコスト低減及び歩留りの向上と製造工程の簡略化を図ることができる。40

#### 【図面の簡単な説明】

#### 【0068】

【図 1】図 1 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 1) である。

【図 2】図 2 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 2) である。

【図 3】図 3 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 3) である。

【図 4】図 4 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 4) である。

【図 5】図 5 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 5) である。

【図 6】図 6 は本発明の実施形態の配線基板の製造方法を示す断面図 (その 6) である。50

【図7】図7は本発明の実施形態のLGA型のインターポーザ内蔵配線基板を示す断面図である。

【図8】図8は本発明の実施形態のBGA型のインターポーザ内蔵配線基板を示す断面図である。

【図9】図9は本発明の実施形態の変形例のインターポーザ内蔵基板を示す断面図である。

【図10】図10は本発明の実施形態の半導体装置を示す断面図である。

【図11】図11は本発明の実施形態の変形例の半導体装置を示す断面図である。

【符号の説明】

【0069】

5...ベース配線板、6...インターポーザ付き配線基板、7, 7a, 7b...インターポーザ内蔵配線基板、8, 8a...半導体装置、10...第1ユニット配線板、12, 33...絶縁層、12x, 32x...スルーホール、14, 34...スルーホール導電層、16, 36...配線パターン、17...キャパシタ部品、18...ソルダレジスト、20...第2ユニット配線板、20a, 30a...接続端子、30...シリコンインターポーザ、32...シリコン基板、40...モールド金型、42...下型、44...上型、44x...凹部、46...リリースフィルム、48...スペーサ、50...樹脂部、60, 70...半導体チップ、60a, 70a...バンプ、A...空間、A1~A4...隙間。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

---

フロントページの続き

(51)Int.Cl. F I

H 05 K 1/18 (2006.01) H 05 K 1/18 L

H 01 L 23/14 (2006.01) H 01 L 23/14 S

(56)参考文献 特開2002-222901(JP,A)

特開2006-286677(JP,A)

特開2005-340389(JP,A)

特開2005-039232(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 12

H 01 L 23 / 14