(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6516610号

(P6516610)

(45) 発行日 令和1年5月22日(2019.5.22)

(24) 登録日 平成31年4月26日(2019.4.26)

|              |           |            |      |

|--------------|-----------|------------|------|

| (51) Int.Cl. | F 1       |            |      |

| H04L 9/10    | (2006.01) | H04L 9/00  | 621A |

| G06F 21/55   | (2013.01) | G06F 21/55 | 380  |

| G06F 21/75   | (2013.01) | G06F 21/75 |      |

| H04L 9/16    | (2006.01) | H04L 9/00  | 643  |

請求項の数 8 (全 17 頁)

(21) 出願番号 特願2015-145324 (P2015-145324)

(22) 出願日 平成27年7月22日 (2015.7.22)

(65) 公開番号 特開2017-28506 (P2017-28506A)

(43) 公開日 平成29年2月2日 (2017.2.2)

審査請求日 平成29年6月22日 (2017.6.22)

(73) 特許権者 591128453

株式会社メガチップス

大阪府大阪市淀川区宮原一丁目1番1号

(74) 代理人 100136353

弁理士 高尾 建吾

(72) 発明者 菅原 崇彦

大阪市淀川区宮原一丁目1番1号 株式会

社メガチップス内

(72) 発明者 油谷 大武

大阪市淀川区宮原一丁目1番1号 株式会

社メガチップス内

審査官 金沢 史明

最終頁に続く

(54) 【発明の名称】メモリ装置、ホスト装置、及びメモリシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

ホスト装置に接続されるメモリ装置であって、

通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生成回路を有する、第1の暗号モジュールと、

通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、

第2の暗号モジュールと、

ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、

前記第3の暗号モジュールの動作を制御する制御回路と、

を備え、

前記制御回路は、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時

データ生成回路にダミー動作を実行させる、メモリ装置。

**【請求項 2】**

前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させる、請求項1に記載のメモリ装置。

**【請求項 3】**

前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させる、請求項2に記載のメモリ装置。

**【請求項 4】**

前記ホスト装置からの不正アクセスを検出する不正アクセス検出回路をさらに備え、

前記制御回路は、前記不正アクセス検出回路が不正アクセスを検出した場合に、前記第3の暗号モジュールにダミー動作を実行させる、請求項1～3のいずれか一つに記載のメモリ装置。

**【請求項 5】**

メモリ装置が接続されるホスト装置であって、

通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生成回路を有する、第1の暗号モジュールと、

通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、第2の暗号モジュールと、

ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、

前記第3の暗号モジュールの動作を制御する制御回路と、

を備え、

前記制御回路は、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、

前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時データ生成回路にダミー動作を実行させる、ホスト装置。

**【請求項 6】**

前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させる、請求項5に記載のホスト装置。

**【請求項 7】**

前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させる、請求項6に記載のホスト装置。

**【請求項 8】**

請求項1～4のいずれか一つに記載のメモリ装置と、

請求項5～7のいずれか一つに記載のホスト装置と、

を備える、メモリシステム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

20

30

40

50

本発明は、メモリ装置、ホスト装置、及びそれらを備えるメモリシステムに関する。

【背景技術】

【0002】

ホスト装置とそれに接続されるメモリ装置とを備えるメモリシステムにおいて、両装置間で送受信されるコマンドやデータを暗号化することによってセキュリティ性を向上させたメモリシステムが実用化されている。

【0003】

現在使用されている暗号方式は、暗号学的な解析手法に対して計算量的に安全であるとされている。しかし、実際にメモリシステムに暗号モジュールを実装する場合には、消費電力や処理時間のような、実装に依存したリークが発生する。そのような動作状況を様々な物理的手段で観察することにより、秘密鍵等の秘密情報を不正に取得しようとするサイドチャネル攻撃の脅威が増している。10

【0004】

サイドチャネル攻撃の一つとして、装置の消費電力を測定することによって秘密情報を解析する電力解析攻撃がある。その中でも、測定した複数の消費電力波形に対して統計処理による解析を行う差分電力解析（DPA : Differential Power Analysis）が、特に強力な攻撃法として報告されている（下記非特許文献1参照）。

【0005】

そのため近年では、DPA攻撃に対する種々の対策回路が提案されており、例えば下記非特許文献2には、RSL（Random Switching Logic）回路及びWDDL（Wave Dynamic Differential Logic）回路が提案されている。RSL回路は、乱数を用いて論理回路の動作モードを切り替えることによって状態遷移確率の偏りをなくし、それによって暗号鍵に依存しないよう消費電力をランダム化する。WDDL回路は、プリチャージ動作を行った後、演算時のビット値の違いに起因する消費電流の相違を相補回路によって低減することにより、消費電力を均一化する。20

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Paul Kocher、他2名、"Introduction to Differential Power Analysis and related Attacks"、[online]、Cryptography Research、平成27年7月1日検索、インターネット<<http://www.cryptography.com/public/pdf/DPATechInfo.pdf>>30

【非特許文献2】Daisuke Suzuki、他2名、"Random Switching Logic: A Countermeasure against DPA based on Transition Probability"、[online]、International Association for Cryptologic Research、平成27年7月1日検索、インターネット<<http://eprint.iacr.org/2004/346.pdf>>

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、ホスト装置とメモリ装置とを備えるメモリシステムにおいて、上述したRSL回路又はWDDL回路を装置に実装する場合には、これらの回路を実装しない装置と比較して、演算時間、回路規模、及び消費電力が2～3倍以上に増大するため、コストが増大する。40

【0008】

本発明はかかる事情に鑑みて成されたものであり、DPA攻撃に対する対策を低成本で実装することが可能な、メモリ装置、ホスト装置、及びそれらを備えるメモリシステムを得ることを目的とするものである。

【課題を解決するための手段】

【0009】

本発明の第1の態様に係るメモリ装置は、ホスト装置に接続されるメモリ装置であって、通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生50

成回路を有する、第1の暗号モジュールと、通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、第2の暗号モジュールと、ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、前記第3の暗号モジュールの動作を制御する制御回路と、を備え、前記制御回路は、前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時データ生成回路にダミー動作を実行させることを特徴とするものである。

10

#### 【0010】

第1の態様に係るメモリ装置によれば、制御回路は、第1の暗号モジュール及び第2の暗号モジュールの一方が通常動作を実行する期間において、第3の暗号モジュールにダミー動作を実行させる。このように、第3の暗号モジュールにダミー動作を実行させることにより、通常動作を実行している第1又は第2の暗号モジュールが具有する消費電力特性を隠蔽することができる。その結果、DPA攻撃に対する対策を低コストで実装することが可能となる。

20

また、第1の態様に係るメモリ装置によれば、制御回路は、第1の一時データ生成回路のみが通常動作を実行する期間においては第2のストリームデータ生成回路にダミー動作を実行させ、第1のストリームデータ生成回路のみが通常動作を実行する期間においては第2の一時データ生成回路にダミー動作を実行させる。これにより、メモリ装置全体の消費電力を均一化できるため、DPA攻撃による消費電力特性の解析を困難化することが可能となる。

#### 【0011】

本発明の第2の態様に係るメモリ装置は、第1の態様に係るメモリ装置において特に、前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させることを特徴とするものである。

30

#### 【0012】

第2の態様に係るメモリ装置によれば、制御回路は、第2の暗号モジュールが通常動作を実行し第1の暗号モジュールが通常動作を実行しない期間において、第1の暗号モジュールにダミー動作を実行させる。このように、第2の暗号モジュールのみが通常動作を実行する期間において第1の暗号モジュールをダミー動作させることにより、第2の暗号モジュールが具有する消費電力特性をさらに隠蔽することができる。

#### 【0013】

本発明の第3の態様に係るメモリ装置は、第2の態様に係るメモリ装置において特に、前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させることを特徴とするものである。

40

#### 【0014】

第3の態様に係るメモリ装置によれば、制御回路は、第1の暗号モジュール及び第2の暗号モジュールの双方が同時に通常動作を実行する期間において、第3の暗号モジュールにダミー動作を実行させる。このように、第1の暗号モジュール及び第2の暗号モジュールの双方が通常動作を同時に実行する期間において第3の暗号モジュールをダミー動作させることにより、第1の暗号モジュール及び第2の暗号モジュールが具有する消費電力特

50

性をさらに隠蔽することができる。

#### 【0023】

本発明の第4の態様に係るメモリ装置は、第1～第3のいずれか一つの態様に係るメモリ装置において特に、前記ホスト装置からの不正アクセスを検出する不正アクセス検出回路をさらに備え、前記制御回路は、前記不正アクセス検出回路が不正アクセスを検出した場合に、前記第3の暗号モジュールにダミー動作を実行させることを特徴とするものである。

#### 【0024】

第4の態様に係るメモリ装置によれば、制御回路は、不正アクセス検出回路が不正アクセスを検出した場合に、第3の暗号モジュールにダミー動作を実行させる。従って、システムの可用性を確保できるとともに、不正アクセスを検出しない場合にダミー動作を実行させることに起因する消費電力の増大を回避することが可能となる。10

#### 【0025】

本発明の第5の態様に係るホスト装置は、メモリ装置が接続されるホスト装置であって、通常動作として入力データに基づいて第1の一時データを生成する第1の一時データ生成回路を有する、第1の暗号モジュールと、通常動作として前記第1の一時データ生成回路によって生成された第1の一時データに基づいて第1のストリームデータを生成する第1のストリームデータ生成回路を有する、第2の暗号モジュールと、ダミー動作としてダミーの入力データに基づいて第2の一時データを生成する第2の一時データ生成回路と、ダミー動作として前記第2の一時データ生成回路によって生成された第2の一時データに基づいて第2のストリームデータを生成する第2のストリームデータ生成回路とを有する、第3の暗号モジュールと、前記第3の暗号モジュールの動作を制御する制御回路と、を備え、前記制御回路は、前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のうち前記第1の一時データ生成回路のみが通常動作を実行する期間において、前記第2のストリームデータ生成回路にダミー動作を実行させ、前記第1の一時データ生成回路及び前記第1のストリームデータ生成回路のみが通常動作を実行する期間において、前記第2の一時データ生成回路にダミー動作を実行させることを特徴とするものである。20

#### 【0026】

第5の態様に係るホスト装置によれば、制御回路は、第1の暗号モジュール及び第2の暗号モジュールの一方が通常動作を実行する期間において、第3の暗号モジュールにダミー動作を実行させる。このように、第3の暗号モジュールにダミー動作を実行させることにより、通常動作を実行している第1又は第2の暗号モジュールが具有する消費電力特性を隠蔽することができる。その結果、DPA攻撃に対する対策を低コストで実装することが可能となる。

また、第5の態様に係るホスト装置によれば、制御回路は、第1の一時データ生成回路のみが通常動作を実行する期間においては第2のストリームデータ生成回路にダミー動作を実行させ、第1のストリームデータ生成回路のみが通常動作を実行する期間においては第2の一時データ生成回路にダミー動作を実行させる。これにより、ホスト装置全体の消費電力を均一化できるため、DPA攻撃による消費電力特性の解析を困難化することが可能となる。40

#### 【0027】

本発明の第6の態様に係るホスト装置は、第5の態様に係るホスト装置において特に、前記制御回路はさらに、前記第2の暗号モジュールが通常動作を実行し前記第1の暗号モジュールが通常動作を実行しない期間において、前記第1の暗号モジュールにダミー動作を実行させることを特徴とするものである。50

**【 0 0 2 8 】**

第6の態様に係るホスト装置によれば、制御回路は、第2の暗号モジュールが通常動作を実行し第1の暗号モジュールが通常動作を実行しない期間において、第1の暗号モジュールにダミー動作を実行させる。このように、第2の暗号モジュールのみが通常動作を実行する期間において第1の暗号モジュールをダミー動作させることにより、第2の暗号モジュールが具有する消費電力特性をさらに隠蔽することができる。

**【 0 0 2 9 】**

本発明の第7の態様に係るホスト装置は、第6の態様に係るホスト装置において特に、前記制御回路はさらに、前記第1の暗号モジュール及び前記第2の暗号モジュールの双方が同時に通常動作を実行する期間において、前記第3の暗号モジュールにダミー動作を実行させることを特徴とするものである。 10

**【 0 0 3 0 】**

第7の態様に係るホスト装置によれば、制御回路は、第1の暗号モジュール及び第2の暗号モジュールの双方が同時に通常動作を実行する期間において、第3の暗号モジュールにダミー動作を実行させる。このように、第1の暗号モジュール及び第2の暗号モジュールの双方が通常動作を同時に実行する期間において第3の暗号モジュールをダミー動作させることにより、第1の暗号モジュール及び第2の暗号モジュールが具有する消費電力特性をさらに隠蔽することができる。 20

**【 0 0 3 9 】**

本発明の第8の態様に係るメモリシステムは、第1～第4のいずれか一つの態様に係るメモリ装置と、第5～第7のいずれか一つの態様に係るホスト装置と、を備えることを特徴とするものである。

**【 0 0 4 0 】**

第8の態様に係るメモリシステムによれば、メモリ装置及びホスト装置の双方においてDPA攻撃に対する対策がそれぞれ実装されているため、メモリシステム全体としてDPA攻撃に対する耐性を高めることが可能となる。 30

**【発明の効果】****【 0 0 4 1 】**

本発明によれば、DPA攻撃に対する対策を低コストで実装することが可能となる。

**【図面の簡単な説明】****【 0 0 4 2 】**

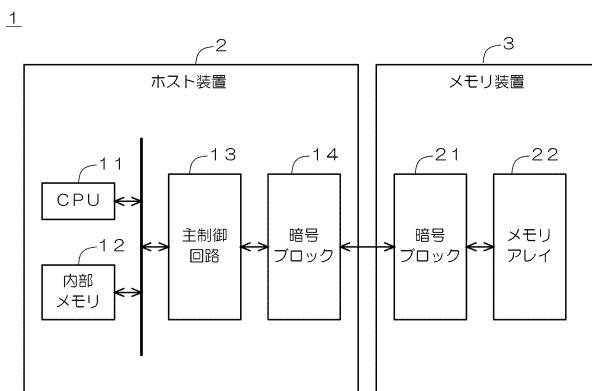

【図1】本発明の実施の形態に係るメモリシステムの構成を示す図である。

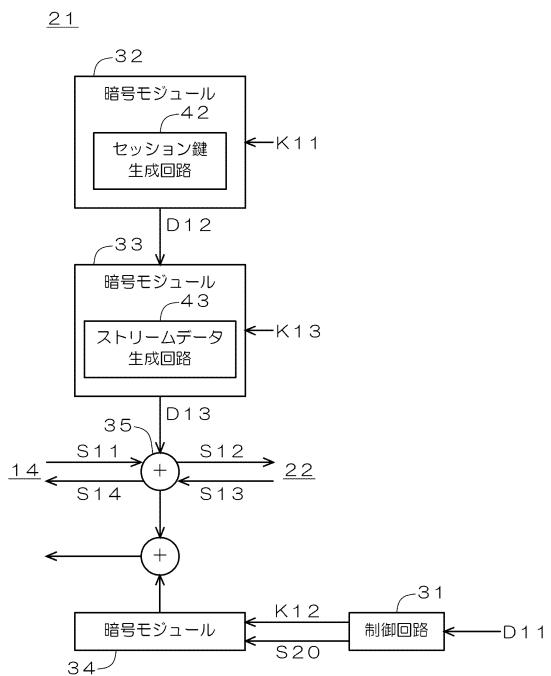

【図2】メモリ装置の暗号ブロックの構成を示す図である。

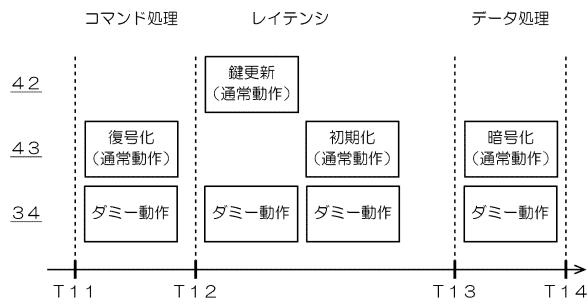

【図3】セッション鍵生成回路、ストリームデータ生成回路、及び暗号モジュールの処理内容を示すタイミングチャートである。 40

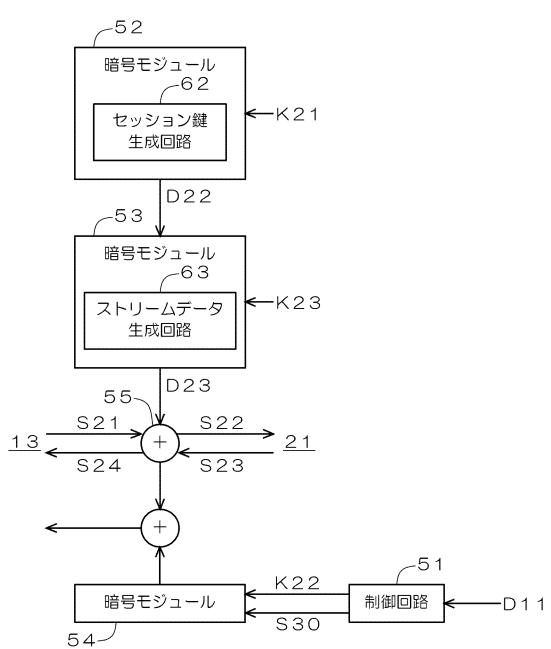

【図4】ホスト装置の暗号ブロックの構成を示す図である。

【図5】セッション鍵生成回路、ストリームデータ生成回路、及び暗号モジュールの処理内容を示すタイミングチャートである。

【図6】メモリ装置の暗号ブロックの構成を示す図である。

【図7】メモリ装置の暗号ブロックの構成を示す図である。

【図8】セッション鍵生成回路及びストリームデータ生成回路の処理内容を示すタイミングチャートである。

【図9】セッション鍵生成回路、ストリームデータ生成回路、及び暗号モジュールの処理内容を示すタイミングチャートである。 50

**【発明を実施するための形態】**

**【0043】**

以下、本発明の実施の形態について、図面を用いて詳細に説明する。なお、異なる図面において同一の符号を付した要素は、同一又は相応する要素を示すものとする。

**【0044】**

図1は、本発明の実施の形態に係るメモリシステム1の構成を簡略化して示す図である。図1に示すようにメモリシステム1は、ホスト装置2と、ホスト装置2に着脱自在に接続される半導体メモリ等のメモリ装置3とを備えて構成されている。

**【0045】**

ホスト装置2は、CPU11、内部メモリ12、主制御回路13、及び暗号ブロック14を有している。メモリ装置3は、暗号ブロック14と同様の暗号ブロック21と、コンテンツデータ等の任意のデータが格納されたメモリアレイ22とを有している。暗号ブロック14, 21は、ホスト装置2とメモリ装置3との間で送受信されるコマンドやデータに対して、暗号化処理及び復号化処理を実行する。

**【0046】**

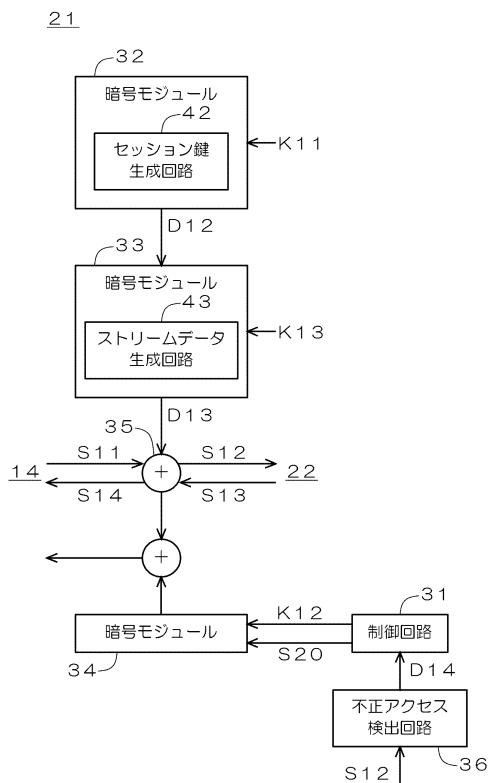

図2は、メモリ装置3の暗号ブロック21の構成を示す図である。図2に示すように暗号ブロック21は、制御回路31、暗号モジュール32～34、及び演算回路35を有している。暗号モジュール32は、セッション鍵生成回路42を有している。セッション鍵生成回路42は、一時データ生成回路として機能し、入力データとしての鍵情報（秘密鍵K11）に基づいて、一時データとしてのセッション鍵D12を生成する。暗号モジュール33は、ストリームデータ生成回路43を有している。ストリームデータ生成回路43は、暗号処理回路として機能し、鍵情報（秘密鍵K13）と、セッション鍵生成回路42から入力されたセッション鍵D12とに基づいて、ストリーム暗号のためのストリームデータD13を生成する。演算回路35は、ホスト装置2から受信した暗号化コマンドS11と、ストリームデータ生成回路43から入力されたストリームデータD13との排他的論理和を演算することにより、非暗号のコマンドS12を復元する。また、演算回路35は、メモリアレイ22から読み出された非暗号のデータS13と、ストリームデータ生成回路43から入力されたストリームデータD13との排他的論理和を演算することにより、暗号化データS14を生成する。

**【0047】**

暗号モジュール34は、暗号モジュール32, 33とは異なる暗号アルゴリズムの暗号モジュールであり、コマンドやデータの暗号化及び復号化には寄与しないダミー動作を実行する。暗号モジュール34には、制御回路31から制御信号S20と鍵情報（ダミー鍵K12）とが入力される。ダミー鍵K12は、固定値であっても良いし、乱数生成器を用いた変動値であっても良い。あるいは、ダミー鍵K12は秘密鍵K11又は秘密鍵K13と同一であっても良い。なお、暗号モジュール34は、暗号モジュール32又は暗号モジュール33と同一の暗号アルゴリズムの暗号モジュールであっても良く、その場合には、ダミー鍵K12として秘密鍵K11, K13とは異なる鍵が使用される。

**【0048】**

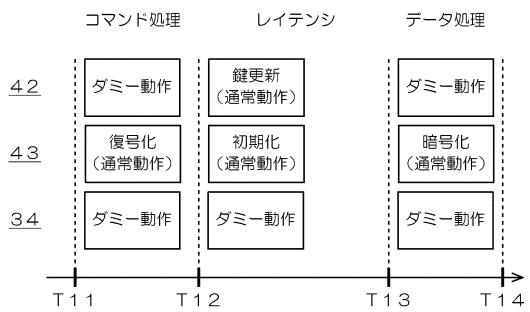

図3は、セッション鍵生成回路42、ストリームデータ生成回路43、及び暗号モジュール34の処理内容を示すタイミングチャートである。

**【0049】**

コマンド処理期間（時刻T11～T12）において、ストリームデータ生成回路43は、コマンド又はデータの暗号化又は復号化を実行するための通常動作として、ストリームデータD13の生成処理を行い、これにより暗号化コマンドS11の復号化が実行される。また、コマンド処理期間において、セッション鍵生成回路42は動作せず、暗号モジュール34はストリームデータ生成回路43の動作期間に同期してダミー動作を実行する。

**【0050】**

レイテンシ期間（時刻T12～T13）において、まずセッション鍵生成回路42は、通常動作としてセッション鍵D12の更新処理を行う。次にストリームデータ生成回路4

10

20

30

40

50

3は、通常動作として、更新後のセッション鍵D12を用いて初期化処理を行う。また、

レイテンシ期間において、暗号モジュール34はセッション鍵生成回路42及びストリームデータ生成回路43の各動作期間に同期してダミー動作を実行する。

#### 【0051】

メモリアレイ22からのデータの読み出しが完了した後のデータ処理期間（時刻T13～T14）において、ストリームデータ生成回路43は、通常動作としてストリームデータD13の生成処理を行い、これにより非暗号のデータS13の暗号化が実行される。また、データ処理期間において、セッション鍵生成回路42は動作せず、暗号モジュール34はストリームデータ生成回路43の動作期間に同期してダミー動作を実行する。

#### 【0052】

以下、メモリアレイ22に格納されているデータをメモリ装置3からホスト装置2に読み出す処理を例にとり、メモリ装置3の動作を詳細に説明する。

#### 【0053】

メモリシステム1が起動されると、制御回路31は、メモリアレイ22の所定場所に格納されているDPA制御情報D11（ON又はOFFのフラグ情報）を読み出す。制御回路31は、DPA制御情報D11がONに設定されている場合には以下に述べるDPA対策処理を実行し、OFFに設定されている場合には実行しない。本実施の形態の例では、DPA制御情報D11はONに設定されているものとする。なお、DPA制御情報D11は、ホスト装置2から発行されるコマンドの一部に格納されていても良く、この場合には、DPA対策処理の実行の要否をホスト装置2によって簡易に切り替えることが可能となる。

#### 【0054】

次に制御回路31は、DPA対策処理として暗号モジュール34のダミー動作を実行するため、制御信号S20及びダミー鍵K12を暗号モジュール34に入力する。

#### 【0055】

次にホスト装置2は、CPU11が発行した読み出しコマンドを暗号ブロック14によって暗号化することにより、暗号化コマンドS11をメモリ装置3に送信する。

#### 【0056】

次にコマンド処理期間（時刻T11～T12）において、ストリームデータ生成回路43は、通常動作として、セッション鍵生成回路42から入力された最新のセッション鍵D12に基づいてストリームデータD13の生成処理を行い、これにより暗号化コマンドS11の復号化が実行される。また、暗号モジュール34は、ストリームデータ生成回路43の動作期間に同期して、ダミー鍵K12に基づいてダミー動作を実行する。暗号モジュール34のダミー動作によって生成されたデータは、メモリ装置3内で廃棄しても良いし、ダミーデータとしてメモリ装置3の外部に出力しても良い。

#### 【0057】

次にレイテンシ期間（時刻T12～T13）において、まずセッション鍵生成回路42は、通常動作としてセッション鍵D12の更新処理を行うことにより、新たなセッション鍵D12を生成する。また、暗号モジュール34は、セッション鍵生成回路42の動作期間に同期してダミー動作を実行する。次にストリームデータ生成回路43は、通常動作として、更新後のセッション鍵D12を用いて初期化処理を行う。また、暗号モジュール34は、セッション鍵生成回路42の動作期間に同期してダミー動作を実行する。次に、上述した暗号化コマンドS11の復号化によって復元された非暗号のコマンドS12に基づいて、メモリアレイ22から所望のデータS13が読み出される。

#### 【0058】

次にデータ処理期間（時刻T13～T14）において、ストリームデータ生成回路43は、通常動作として、セッション鍵生成回路42から入力された更新後のセッション鍵D12に基づいてストリームデータD13の生成処理を行い、これにより非暗号のデータS13の暗号化が実行される。暗号化データS14は、メモリ装置3からホスト装置2に送信される。また、暗号モジュール34は、ストリームデータ生成回路43の動作期間に同

10

20

30

40

50

期してダミー動作を実行する。

**【0059】**

このように本実施の形態に係るメモリ装置3によれば、制御回路31は、暗号モジュール32（第1の暗号モジュール）及び暗号モジュール33（第2の暗号モジュール）の一方が通常動作を実行する期間において、暗号モジュール34（第3の暗号モジュール）にダミー動作を実行させる。このように、暗号モジュール34にダミー動作を実行させることにより、通常動作を実行している暗号モジュール32又は暗号モジュール33が具有する消費電力特性を隠蔽することができる。その結果、DPA攻撃に対する対策を低コストで実装することが可能となる。

**【0060】**

また、ダミー鍵K12をあえて固定値とし、何らかの鍵データの生成処理が実行されていることを攻撃者に予見させることにより、解析によってダミー鍵K12を特定するという無駄な作業を攻撃者に行わせる効果が期待できる。その結果、秘密鍵K11，K13を長期間保護することが可能となる。また、ダミー鍵K12を固定値とすることにより、ダミー動作に伴う暗号モジュール34の消費電力を均一化することが可能となる。

10

**【0061】**

また、ダミー鍵K12を変動値とすることにより、ダミー鍵K12が変動する度に暗号モジュール34の消費電力も変動するため、メモリ装置3全体の消費電力を変動させることができる。その結果、DPA攻撃による消費電力特性の解析を困難化することが可能となる。

20

**【0062】**

また、入力データとして秘密鍵K11（鍵情報）を入力することにより、セッション鍵生成回路42は、一時データとしてセッション鍵D12を生成することが可能となる。

**【0063】**

<第1の変形例>

上記実施の形態では、DPA対策をメモリ装置3に実装する例について説明したが、DPA対策をホスト装置2に実装しても良い。

**【0064】**

図4は、ホスト装置2の暗号ブロック14の構成を示す図である。図4に示すように暗号ブロック14は、制御回路51、暗号モジュール52～54、及び演算回路55を有している。暗号モジュール52は、セッション鍵生成回路62を有している。セッション鍵生成回路62は、一時データ生成回路として機能し、入力データとしての鍵情報（秘密鍵K21）に基づいて、一時データとしてのセッション鍵D22を生成する。暗号モジュール53は、ストリームデータ生成回路63を有している。ストリームデータ生成回路63は、暗号処理回路として機能し、鍵情報（秘密鍵K23）と、セッション鍵生成回路62から入力されたセッション鍵D22とに基づいて、ストリーム暗号のためのストリームデータD23を生成する。演算回路55は、メモリ装置3から受信した暗号化データS23と、ストリームデータ生成回路63から入力されたストリームデータD23との排他的論理和を演算することにより、非暗号のデータS24を復元する。また、演算回路55は、主制御回路13から入力された非暗号のコマンドS21と、ストリームデータ生成回路63から入力されたストリームデータD23との排他的論理和を演算することにより、暗号化コマンドS22を生成する。

30

**【0065】**

暗号モジュール54は、暗号モジュール52，53とは異なる暗号アルゴリズムの暗号モジュールであり、コマンドやデータの暗号化及び復号化には寄与しないダミー動作を実行する。暗号モジュール54には、制御回路51から制御信号S30と鍵情報（ダミー鍵K22）とが入力される。ダミー鍵K22は、固定値であっても良いし、乱数生成器を用いた変動値であっても良い。あるいは、ダミー鍵K22は秘密鍵K21又は秘密鍵K23と同一であっても良い。なお、暗号モジュール54は、暗号モジュール52又は暗号モジュール53と同一の暗号アルゴリズムの暗号モジュールであっても良く、その場合には、

40

50

ダミー鍵 K 2 2 として秘密鍵 K 2 1 , K 2 3 とは異なる鍵が使用される。

**【 0 0 6 6 】**

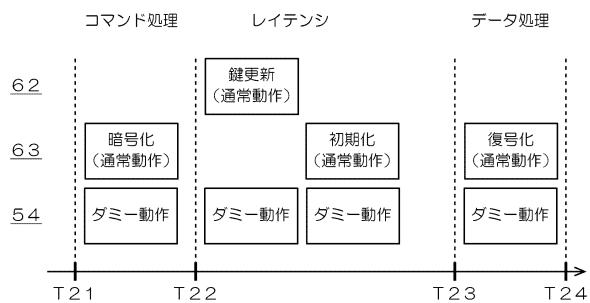

図 5 は、セッション鍵生成回路 6 2 、ストリームデータ生成回路 6 3 、及び暗号モジュール 5 4 の処理内容を示すタイミングチャートである。

**【 0 0 6 7 】**

コマンド処理期間（時刻 T 2 1 ~ T 2 2 ）において、ストリームデータ生成回路 6 3 は、コマンド又はデータの暗号化又は復号化を実行するための通常動作として、ストリームデータ D 2 3 の生成処理を行い、これにより非暗号のコマンド S 2 1 の暗号化が実行される。また、コマンド処理期間において、セッション鍵生成回路 6 2 は動作せず、暗号モジュール 5 4 はストリームデータ生成回路 6 3 の動作期間に同期してダミー動作を実行する。

10

**【 0 0 6 8 】**

レイテンシ期間（時刻 T 2 2 ~ T 2 3 ）において、まずセッション鍵生成回路 6 2 は、通常動作としてセッション鍵 D 2 2 の更新処理を行う。次にストリームデータ生成回路 6 3 は、通常動作として、更新後のセッション鍵 D 2 2 を用いて初期化処理を行う。また、レイテンシ期間において、暗号モジュール 5 4 はセッション鍵生成回路 6 2 及びストリームデータ生成回路 6 3 の各動作期間に同期してダミー動作を実行する。

**【 0 0 6 9 】**

データ処理期間（時刻 T 2 3 ~ T 2 4 ）において、ストリームデータ生成回路 6 3 は、通常動作としてストリームデータ D 2 3 の生成処理を行い、これにより暗号化データ S 2 3 の復号化が実行される。また、データ処理期間において、セッション鍵生成回路 6 2 は動作せず、暗号モジュール 5 4 はストリームデータ生成回路 6 3 の動作期間に同期してダミー動作を実行する。

20

**【 0 0 7 0 】**

以下、メモリアレイ 2 2 に格納されているデータをメモリ装置 3 からホスト装置 2 に読み出す処理を例にとり、ホスト装置 2 の動作を詳細に説明する。

**【 0 0 7 1 】**

メモリシステム 1 が起動されると、制御回路 5 1 は、メモリアレイ 2 2 の所定場所に格納されている D P A 制御情報 D 1 1 を読み出す。制御回路 5 1 は、D P A 制御情報 D 1 1 が O N に設定されている場合には以下に述べる D P A 対策処理を実行し、O F F に設定されている場合には実行しない。本変形例では、D P A 制御情報 D 1 1 は O N に設定されているものとする。

30

**【 0 0 7 2 】**

次に C P U 1 1 は、非暗号の読み出しコマンド S 2 1 を発行する。コマンド S 2 1 は、主制御回路 1 3 を介して暗号ブロック 1 4 に入力される。

**【 0 0 7 3 】**

次にコマンド処理期間（時刻 T 2 1 ~ T 2 2 ）において、ストリームデータ生成回路 6 3 は、通常動作として、セッション鍵生成回路 6 2 から入力された最新のセッション鍵 D 2 2 に基づいてストリームデータ D 2 3 の生成処理を行い、これにより非暗号のコマンド S 2 1 の暗号化が実行される。また、暗号モジュール 5 4 は、ストリームデータ生成回路 6 3 の動作期間に同期して、ダミー鍵 K 2 2 に基づいてダミー動作を実行する。暗号モジュール 5 4 のダミー動作によって生成されたデータは、ホスト装置 2 内で廃棄しても良いし、ダミーデータとしてホスト装置 2 の外部に出力しても良い。

40

**【 0 0 7 4 】**

次にレイテンシ期間（時刻 T 2 2 ~ T 2 3 ）において、まずセッション鍵生成回路 6 2 は、通常動作としてセッション鍵 D 2 2 の更新処理を行うことにより、新たなセッション鍵 D 2 2 を生成する。また、暗号モジュール 5 4 は、セッション鍵生成回路 6 2 の動作期間に同期してダミー動作を実行する。次にストリームデータ生成回路 6 3 は、通常動作として、更新後のセッション鍵 D 2 2 を用いて初期化処理を行う。また、暗号モジュール 5 4 は、セッション鍵生成回路 6 2 の動作期間に同期してダミー動作を実行する。

50

**【 0 0 7 5 】**

次にデータ処理期間（時刻 T 2 3 ~ T 2 4）において、ストリームデータ生成回路 6 3 は、通常動作として、セッション鍵生成回路 6 2 から入力された更新後のセッション鍵 D 2 2 に基づいてストリームデータ D 2 3 の生成処理を行い、これにより暗号化データ S 2 3 の復号化が実行される。復号化されたデータ S 2 4 は、主制御回路 1 3 を介して C P U 1 1 に入力される。

**【 0 0 7 6 】**

このように本変形例に係るホスト装置 2 によれば、制御回路 5 1 は、暗号モジュール 5 2（第 1 の暗号モジュール）及び暗号モジュール 5 3（第 2 の暗号モジュール）の一方が通常動作を実行する期間において、暗号モジュール 5 4（第 3 の暗号モジュール）にダミー動作を実行させる。このように、暗号モジュール 5 4 にダミー動作を実行させることにより、通常動作を実行している暗号モジュール 5 2 又は暗号モジュール 5 3 が具有する消費電力特性を隠蔽することができる。その結果、D P A 攻撃に対する対策を低成本で実装することが可能となる。10

**【 0 0 7 7 】**

また、ダミー鍵 K 2 2 をあえて固定値とし、何らかの鍵データの生成処理が実行されていることを攻撃者に予見させることにより、解析によってダミー鍵 K 2 2 を特定するという無駄な作業を攻撃者に行わせる効果が期待できる。その結果、秘密鍵 K 2 1, K 2 3 を長期間保護することが可能となる。また、ダミー鍵 K 2 2 を固定値とすることにより、ダミー動作に伴う暗号モジュール 5 4 の消費電力を均一化することが可能となる。20

**【 0 0 7 8 】**

また、ダミー鍵 K 2 2 を変動値とすることにより、ダミー鍵 K 2 2 が変動する度に暗号モジュール 5 4 の消費電力も変動するため、ホスト装置 2 全体の消費電力を変動させることができる。その結果、D P A 攻撃による消費電力特性の解析を困難化することが可能となる。

**【 0 0 7 9 】**

また、入力データとして秘密鍵 K 2 1（鍵情報）を入力することにより、セッション鍵生成回路 6 2 は、一時データとしてセッション鍵 D 2 2 を生成することが可能となる。

**【 0 0 8 0 】**

< 第 2 の変形例 >

上記実施の形態では、D P A 制御情報 D 1 1 に基づいて D P A 対策処理の実行の要否が判定されたが、ホスト装置 2 からメモリ装置 3 への不正アクセスがあったことを条件として、D P A 対策処理を実行しても良い。30

**【 0 0 8 1 】**

図 6 は、メモリ装置 3 の暗号ブロック 2 1 の構成を示す図である。図 2 に示した構成に対して不正アクセス検出回路 3 6 が追加されている。不正アクセス検出回路 3 6 には、復号化によって復元された非暗号のコマンド S 1 2 が、演算回路 3 5 から入力される。

**【 0 0 8 2 】**

不正アクセス検出回路 3 6 は、例えば、所定のアクセス禁止領域へのアクセス要求、メモリアレイ 2 2 のデータ容量を超えるアクセス要求、コマンド I D が定義されていない未定義コマンドによるアクセス要求、及び、規定のコマンドシーケンス以外のシーケンスによるアクセス要求等をホスト装置 2 から受けた場合に、そのアクセスを不正アクセスとして検出し、不正アクセス検出信号 D 1 4 を制御回路 3 1 に入力する。40

**【 0 0 8 3 】**

制御回路 3 1 は、不正アクセス検出信号 D 1 4 が入力されたことを実行条件として、上記実施の形態で説明した D P A 対策処理を実行する。

**【 0 0 8 4 】**

このように本変形例に係るメモリ装置 3 によれば、制御回路 3 1 は、不正アクセス検出回路 3 6 が不正アクセスを検出した場合に、D P A 対策処理を実行する。従って、メモリシステム 1 の可用性を確保できるとともに、不正アクセスを検出しない場合にダミー動作50

を実行させることに起因する消費電力の増大を回避することが可能となる。

**【0085】**

<第3の変形例>

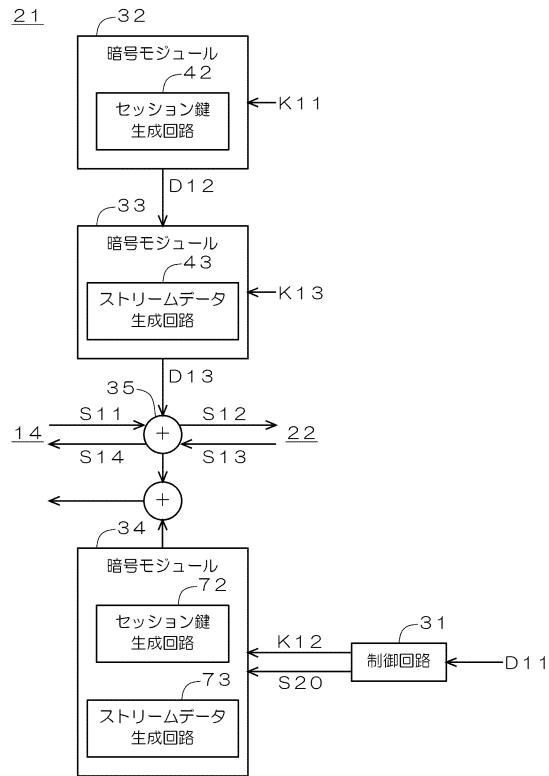

図7は、メモリ装置3の暗号ブロック21の構成を示す図である。図7に示すように暗号ブロック21は、制御回路31、暗号モジュール32～34、及び演算回路35を有している。暗号モジュール34は、セッション鍵生成回路42(第1の一時データ生成回路)と同様のセッション鍵生成回路72(第2の一時データ生成回路)と、ストリームデータ生成回路43(第1の暗号処理回路)と同様のストリームデータ生成回路73(第2の暗号処理回路)とを有している。

**【0086】**

10

図8は、セッション鍵生成回路42, 72及びストリームデータ生成回路43, 73の処理内容を示すタイミングチャートである。

**【0087】**

コマンド処理期間(時刻T11～T12)において、ストリームデータ生成回路43は、通常動作としてストリームデータD13の生成処理を行い、これにより暗号化コマンドS11の復号化が実行される。この時、セッション鍵生成回路42及びストリームデータ生成回路73は動作せず、セッション鍵生成回路72はストリームデータ生成回路43の動作期間に同期してダミー動作を実行する。

**【0088】**

20

レイテンシ期間(時刻T12～T13)において、まずセッション鍵生成回路42は、通常動作としてセッション鍵D12の更新処理を行う。この時、ストリームデータ生成回路43及びセッション鍵生成回路72は動作せず、ストリームデータ生成回路73はセッション鍵生成回路42の動作期間に同期してダミー動作を実行する。次にストリームデータ生成回路43は、通常動作として、更新後のセッション鍵D12を用いて初期化処理を行う。この時、セッション鍵生成回路42及びストリームデータ生成回路73は動作せず、セッション鍵生成回路72はストリームデータ生成回路43の動作期間に同期してダミー動作を実行する。

**【0089】**

30

データ処理期間(時刻T13～T14)において、ストリームデータ生成回路43は、通常動作としてストリームデータD13の生成処理を行い、これにより非暗号のデータS13の暗号化が実行される。この時、セッション鍵生成回路42及びストリームデータ生成回路73は動作せず、セッション鍵生成回路72はストリームデータ生成回路43の動作期間に同期してダミー動作を実行する。

**【0090】**

このように本変形例に係るメモリ装置3によれば、制御回路31は、セッション鍵生成回路42のみが通常動作を実行する期間においてはストリームデータ生成回路73にダミー動作を実行させ、ストリームデータ生成回路43のみが通常動作を実行する期間においてはセッション鍵生成回路72にダミー動作を実行させる。これにより、メモリ装置3全体の消費電力を均一化できるため、DPA攻撃による消費電力特性の解析を困難化することが可能となる。

40

**【0091】**

なお、以上の説明では本変形例をメモリ装置3に適用する例について説明したが、本変形例はホスト装置2にも適用することが可能であり、同様の効果を得ることができる。

**【0092】**

<第4の変形例>

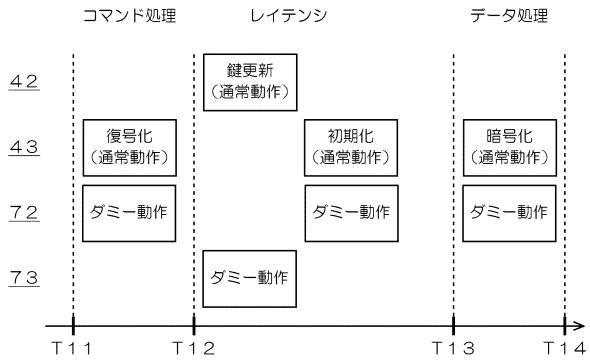

図9は、セッション鍵生成回路42、ストリームデータ生成回路43、及び暗号モジュール34の処理内容を示すタイミングチャートである。

**【0093】**

50

コマンド処理期間(時刻T11～T12)において、ストリームデータ生成回路43は、通常動作としてストリームデータD13の生成処理を行い、これにより暗号化コマンド

S 1 1 の復号化が実行される。この時、セッション鍵生成回路 4 2 及び暗号モジュール 3 4 は、ストリームデータ生成回路 4 3 の動作期間に同期してダミー動作を実行する。

#### 【 0 0 9 4 】

制御回路 3 1 は、セッション鍵生成回路 4 2 のダミー動作を実行するために、セッション鍵生成回路 4 2 の現在の設定内容を示す状態遷移情報を暗号モジュール 3 2 から読み出し、制御回路 3 1 が内部に有する保持回路に当該状態遷移情報を保持する。また、制御回路 3 1 は、秘密鍵 K 1 1 に代えて固定値又は変動値のダミー鍵をセッション鍵生成回路 4 2 に入力する。セッション鍵生成回路 4 2 は、当該ダミー鍵に基づいてダミーのセッション鍵 D 1 2 を生成する。

#### 【 0 0 9 5 】

次にレイテンシ期間（時刻 T 1 2 ~ T 1 3）において、制御回路 3 1 は、保持回路が保持している状態遷移情報をセッション鍵生成回路 4 2 に書き戻す。これにより、セッション鍵生成回路 4 2 の設定内容は、ダミー動作を実行する前の状態に再設定される。また、制御回路 3 1 は、ダミー鍵に代えて秘密鍵 K 1 1 をセッション鍵生成回路 4 2 に入力する。セッション鍵生成回路 4 2 は、通常動作としてセッション鍵 D 1 2 の更新処理を行うことにより、次回に使用する新たなセッション鍵 D 1 2 を生成する。それと同時にストリームデータ生成回路 4 3 は、通常動作として、現在入力されている更新前のセッション鍵 D 1 2 を用いて初期化処理を行う。この時、暗号モジュール 3 4 は、セッション鍵生成回路 4 2 及びストリームデータ生成回路 4 3 の動作期間に同期してダミー動作を実行する。

#### 【 0 0 9 6 】

次にデータ処理期間（時刻 T 1 3 ~ T 1 4）において、ストリームデータ生成回路 4 3 は、通常動作としてストリームデータ D 1 3 の生成処理を行い、これにより非暗号のデータ S 1 3 の暗号化が実行される。この時、セッション鍵生成回路 4 2 及び暗号モジュール 3 4 は、ストリームデータ生成回路 4 3 の動作期間に同期してダミー動作を実行する。

#### 【 0 0 9 7 】

このように本変形例に係るメモリ装置 3 によれば、制御回路 3 1 は、暗号モジュール 3 3 が通常動作を実行し暗号モジュール 3 2 が通常動作を実行しない期間（コマンド処理期間及びデータ処理期間）において、暗号モジュール 3 2 , 3 4 にダミー動作を実行させる。このように、暗号モジュール 3 3 のみが通常動作を実行する期間において暗号モジュール 3 2 , 3 4 をダミー動作させることにより、暗号モジュール 3 3 が具有する消費電力特性をさらに隠蔽することができる。

#### 【 0 0 9 8 】

また、制御回路 3 1 は、暗号モジュール 3 2 , 3 3 の双方が同時に通常動作を実行する期間（レイテンシ期間）において、暗号モジュール 3 4 にダミー動作を実行させる。このように、暗号モジュール 3 2 , 3 3 の双方が通常動作を同時に実行する期間において暗号モジュール 3 4 をダミー動作させることにより、暗号モジュール 3 2 , 3 3 が具有する消費電力特性をさらに隠蔽することができる。

#### 【 0 0 9 9 】

なお、以上の説明では本変形例をメモリ装置 3 に適用する例について説明したが、本変形例はホスト装置 2 にも適用することが可能であり、同様の効果を得ることができる。

#### 【 符号の説明 】

##### 【 0 1 0 0 】

- 1 メモリシステム

- 2 ホスト装置

- 3 メモリ装置

- 1 4 , 2 1 暗号ブロック

- 3 1 , 5 1 制御回路

- 3 2 ~ 3 4 , 5 2 ~ 5 4 暗号モジュール

- 3 6 不正アクセス検出回路

- 4 2 , 6 2 , 7 2 セッション鍵生成回路

10

20

30

40

50

## 4 3 , 6 3 , 7 3 ストリームデータ生成回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2015-026892(JP,A)

特表2004-516706(JP,A)

特開2003-018143(JP,A)

特開2013-143653(JP,A)

米国特許第09735953(US,B1)

特開2007-195132(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 9/10

G06F 21/55

G06F 21/75

H04L 9/16