US 20050156273A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2005/0156273 A1 Trivedi

# Jul. 21, 2005 (43) **Pub. Date:**

### (54) MEMORY DEVICES

(76) Inventor: Jigish G. Trivedi, Boise, ID (US)

Correspondence Address: WELLS ST. JOHN P.S. 601 W. FIRST AVENUE, SUITE 1300 SPOKANE, WA 99201 (US)

- 11/079,974 (21) Appl. No.:

- (22) Filed: Mar. 14, 2005

# **Related U.S. Application Data**

(60) Continuation of application No. 10/222,305, filed on Aug. 15, 2002, now Pat. No. 6,867,497, which is a division of application No. 09/976,635, filed on Oct. 12, 2001.

**Publication Classification**

(51) Int. Cl.<sup>7</sup> ..... H01L 21/76; H01L 29/00; H01L 23/48

#

ABSTRACT (57)

A method of forming a local interconnect includes forming an isolation trench within a semiconductor substrate. A first trench isolation material is deposited to within the trench. First isolation material is removed effective to form a line trench into a desired local interconnect. Conductive material is formed therewithin. A second isolation material is deposited over the first isolation material, over the conductive material within the isolation trench and within the line trench. At least some first and second isolation material is removed in at least one common removing step. Integrated circuitry includes a substrate comprising trench isolation material. A local interconnect line is received within a trench formed within the isolation material. The local interconnect includes at least two different conductive materials. One of the conductive materials lines the trench. Another of the conductive materials is received within a conductive trench formed by the one. Other implementations are disclosed.

IE II III III

# TECHNICAL FIELD

**[0001]** This invention relates to methods of forming conductive lines, and to integrated circuitry.

#### BACKGROUND OF THE INVENTION

**[0002]** The reduction in memory cell and other circuit size implemented in high density dynamic random access memories (DRAMs), static random access memories (SRAMs), logic and other circuitry is a continuing goal in semiconductor fabrication. Implementing electric circuits involves connecting isolated devices through specific electric paths. When fabricating silicon and other semiconductive materials into integrated circuits, conductor devices built into semiconductive substrates need to be isolated from one another. Such isolation typically occurs in the form of LOCOS grown field oxide, and more recently in isolation trench and refill field isolation regions.

**[0003]** Conductive lines, for example transistor gate lines, are formed over substrates. Some lines run globally over large areas of the substrate. Others are much shorter and associated with very small portions of the integrated circuitry. This invention was principally motivated in making processing and structural improvements involving local interconnects.

#### SUMMARY

[0004] The invention includes methods of forming conductive lines, and integrated circuitry. In but one implementation, a method of forming a local interconnect includes forming an isolation trench within a semiconductor substrate. A first trench isolation material is deposited over the semiconductor substrate and to within the isolation trench. First trench isolation material is removed effective to form a line trench within the isolation material into a desired local interconnect configuration. Conductive material is formed within the line trench. A second trench isolation material is deposited over the first trench isolation material, over the conductive material within the isolation trench and within the line trench. At least some first and second trench isolation material is removed from the substrate in at least one common removing step.

**[0005]** In one implementation, a method of forming a local interconnect includes providing a bulk semiconductor substrate having a first conductivity type background region, an adjacent second conductivity type background region and a boundary extending therebetween. An isolation trench is formed within the bulk semiconductor substrate over and along the boundary. A trench isolation material is deposited over the bulk semiconductor substrate and to within the isolation trench. Trench isolation material into a desired local interconnect configuration. Conductive material is formed to within the line trench.

**[0006]** In one implementation, integrated circuitry includes a semiconductor substrate comprising trench isolation material. A local interconnect line is received within a trench formed within the trench isolation material. The local interconnect line includes at least two different conductive materials. One of the conductive materials lines the

trench. Another of the conductive materials is received within a conductive trench formed by the one.

[0007] Other implementations and aspects are contemplated.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0008]** Preferred embodiments of the invention are described below with reference to the following accompanying drawings.

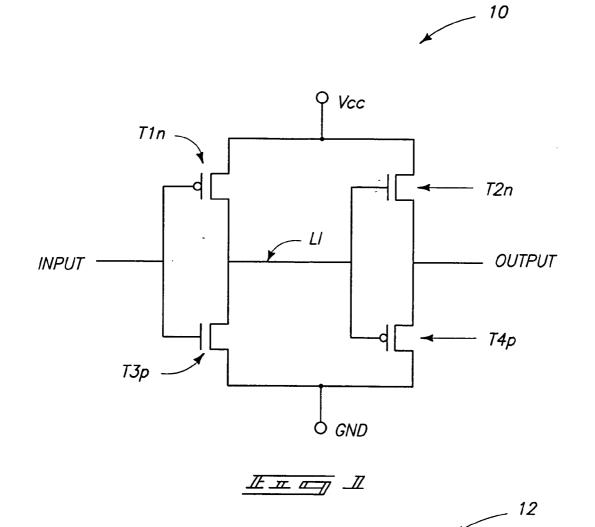

[0009] FIG. 1 is a schematic of exemplary integrated circuitry.

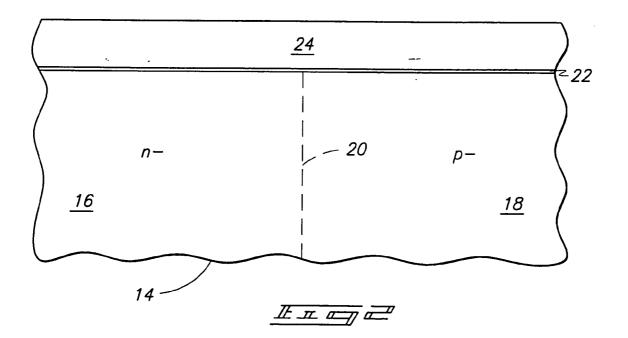

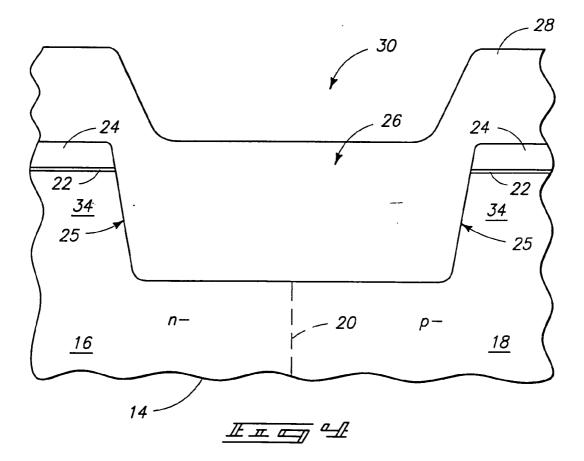

**[0010] FIG. 2** is a diagrammatic sectional view of a semiconductor wafer fragment in process in accordance with an aspect of the invention.

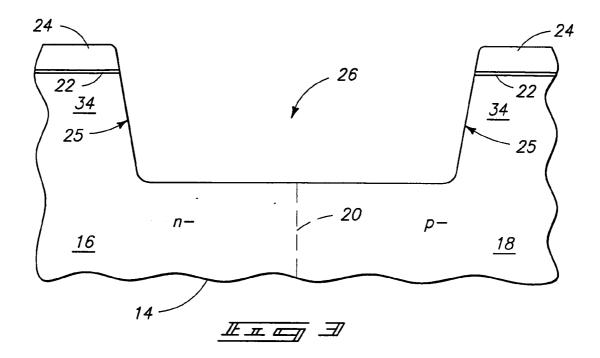

[0011] FIG. 3 is a view of the FIG. 2 wafer fragment at a processing step subsequent to that shown by FIG. 2.

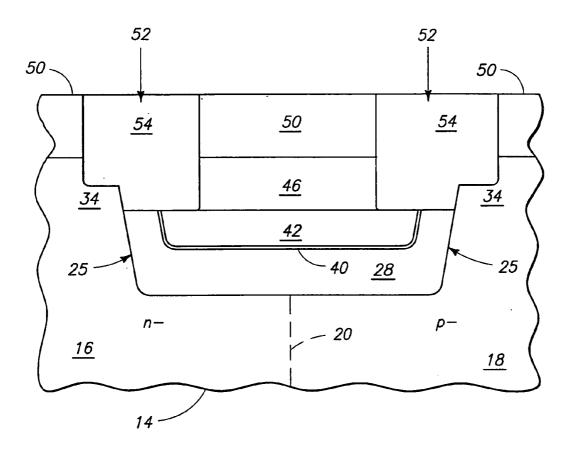

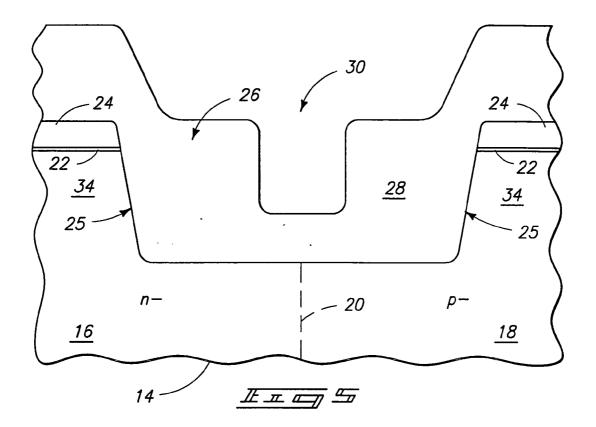

[0012] FIG. 4 is a view of the FIG. 3 wafer fragment at a processing step subsequent to that shown by FIG. 3.

[0013] FIG. 5 is a view of the FIG. 4 wafer fragment at a processing step subsequent to that shown by FIG. 4.

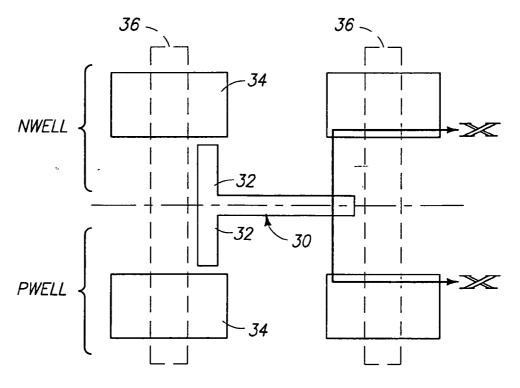

[0014] FIG. 6 is a top plan view of a larger portion of the wafer fragment in process, the above fragmentary views being taken through line X-X in FIG. 6.

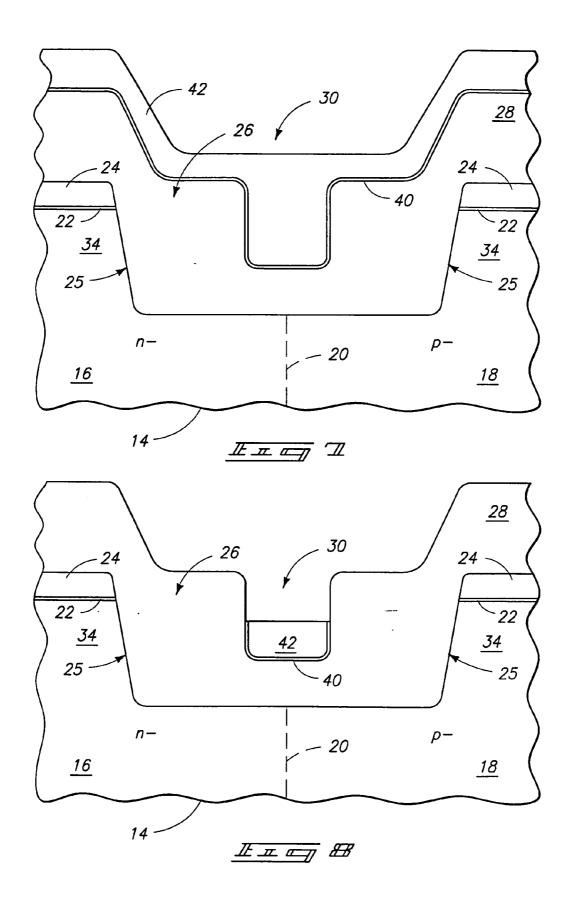

[0015] FIG. 7 is a view of the FIG. 5 wafer fragment at a processing step subsequent to that shown by FIG. 5.

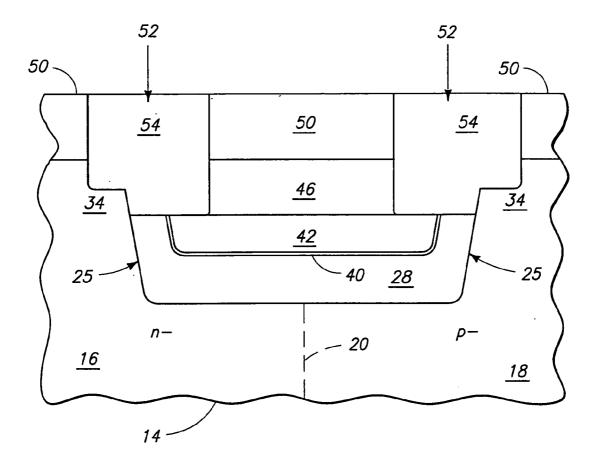

**[0016] FIG. 8** is a view of the **FIG. 7** wafer fragment at a processing step subsequent to that shown by **FIG. 7**.

[0017] FIG. 9 is a view of the FIG. 8 wafer fragment at a processing step subsequent to that shown by FIG. 8.

[0018] FIG. 10 is a view of the FIG. 9 wafer fragment at a processing step subsequent to that shown by FIG. 9.

[0019] FIG. 11 is a top plan view like FIG. 6, but shown at a processing step subsequent to that of FIGS. 6 and 10.

[0020] FIG. 12 is a view of a portion of the FIG. 11 wafer fragment as taken through line 12-12 in FIG. 11.

[0021] FIG. 13 is a view of the FIG. 12 wafer fragment at a processing step subsequent to that shown by FIG. 12.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

**[0022]** This disclosure of the invention is submitted in furtherance of the constitutional purposes of the U.S. Patent Laws "to promote the progress of science and useful arts" (Article 1, Section 8).

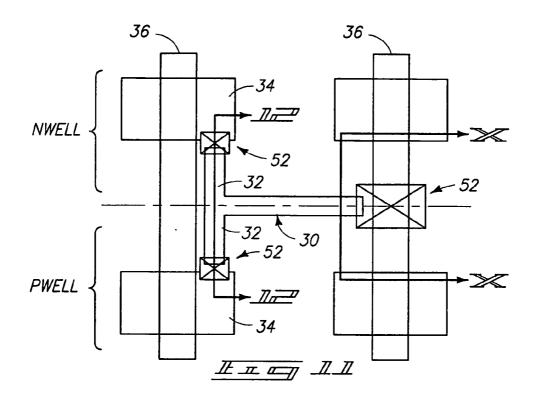

**[0023]** The invention contemplates methods of forming local interconnects, and any integrated circuitry involving a local interconnect line, in accordance with the literal wording of the claims. The invention is described with respect to but one exemplary integrated circuit shown in FIG. 1. Such depicts a cross-coupled inverter circuitry 10 comprising n-type transistors T1n and T2n, and p-type transistors T3p and T4p. A local interconnect LI interconnects the gates of T2n and T4p with source/drain regions of T1n and T3p.

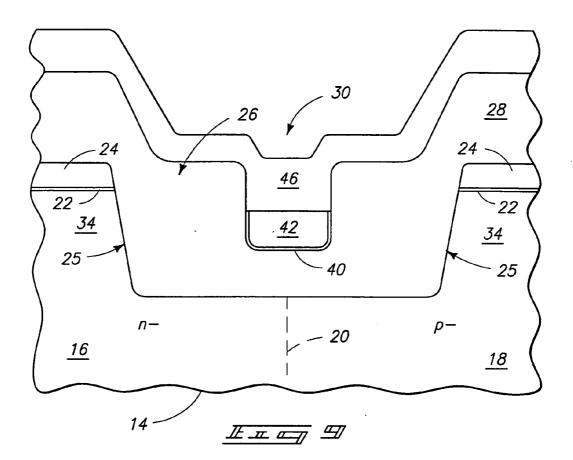

[0024] Referring to FIG. 2, a semiconductor wafer fragment is indicated generally with reference 12. Such comprises a bulk semiconductor substrate having a first conductivity-type background region 16 adjacent a second conductivity-type background region 18, and a boundary 20 extending therebetween. An exemplary preferred material for bulk substrate 14 is monocrystalline, for example monocrystalline silicon, with region 16 being shown lightly background doped with "n" type impurity and region 18 being lightly background doped with "p" type impurity. In the context of this document, the term "semiconductor substrate" or "semiconductive substrate" is defined to mean any construction comprising semiconductive material, including, but not limited to, bulk semiconductive materials such as a semiconductive wafer (either alone or in assemblies comprising other materials thereon), and semiconductive material layers (either alone or in assemblies comprising other materials). The term "substrate" refers to any supporting structure, including, but not limited to, the semiconductive substrates described above. Also in the context of this document, the terms "layer" and "material" encompass both the singular and the plural unless otherwise indicated. A pad oxide layer 22 is formed over bulk substrate 14. An exemplary thickness is 100 Angstroms. A masking layer 24 is formed over layer 22. An exemplary material is silicon nitride deposited to an exemplary thickness of 900 Angstroms.

[0025] Referring to FIG. 3, an isolation trench 26 is formed within bulk semiconductor substrate material 14, which is laterally centered and extends along p-type/n-type boundary 20. Such will be utilized to form interwell isolation, with an exemplary open width of depicted trench 26 being about 0.5 micron. An exemplary depth within substrate material 14 is 3000 Angstroms. Such provides but one example of forming an isolation trench within a semiconductor substrate. Further in the depicted and preferred embodiment, the isolation trench is formed in bulk substrate material, although the invention is in no way so limited. For purposes of the continuing discussion, isolation trench 26 can be considered as having opposing longitudinal sidewalls 25 in the depicted cross-section. Further in the depicted embodiment, isolation trench 26 is formed to be laterally centered over boundary 20.

[0026] Referring to FIG. 4, a first trench isolation material 28 is deposited over substrate 14 and within isolation trench 26. A preferred method of forming layer 28 is by high density plasma chemical vapor deposition. Sidewalls 25 of trench 26 are preferably thermally oxidized (not shown) before or after deposition of material 28.

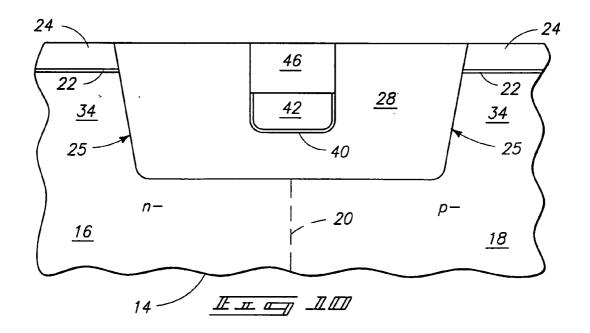

[0027] Referring to FIGS. 5 and 6, exemplary active areas 34 can be seen. First trench isolation material 28 is removed effective to form a line trench 30 within the isolation material into a desired local interconnect configuration. Such removing preferably comprises photolithography and chemical etching, and forms at least a portion of line trench 30 to be laterally centered within isolation trench 26 between sidewalls 25, and laterally centered over boundary 20. In the preferred embodiment, FIG. 6 depicts that line trench 30 includes extensions 32 which do not extend to an edge of the trench isolation material proximate active area substrate material/regions 34. Accordingly at this point in the process in the preferred embodiment, local interconnect trench 30 does not extend to connect with the illustrated active areas. FIG. 6 also depicts exemplary transistor gate outlines 36, which would typically not be formed at this point in the preferred embodiment process. Regardless, it can be seen that the far right illustrated edge of local interconnect trench 30 is also spaced from, and therefore does not connect with, the right illustrated transistor gate outline 36, in this preferred embodiment.

[0028] Conductive material is formed within trench 30 to form at least a portion of the local interconnect being formed. FIG. 7 illustrates but one exemplary embodiment wherein a first conductive material 40 is formed, preferably by depositing, to within trench 30 to form a conductive lining therewithin. In one preferred embodiment, layer 40 is formed of an oxidation resistant material. Exemplary materials include tungsten suicide and nitrogen-rich titanium nitride. In such preferred embodiment, such thereby forms an oxidation resistant lining within line trench 30. In an alternate considered embodiment, the oxidation resistant liner material might be insulative as opposed to conductive. An exemplary insulative oxidation resistant liner material is silicon nitride. A second conductive material 42. different from first conductive material 40, is deposited to within line trench 30 on (in contact with) conductive lining 40. Exemplary materials for layer 42 include tungsten and doped polysilicon. Of course, a singe conductive material could be utilized or more than two conductive materials utilized.

[0029] Referring to FIG. 8, conductive materials 40/42 are recessed within line trench 30 after their deposition. An exemplary preferred process for doing so would be one or more suitable timed chemical etching(s). Such provides but a few preferred examples of forming conductive materials to within line trench 30.

[0030] Referring to FIG. 9, a second trench isolation material 46 is deposited over first trench isolation material 28, over recessed conductive material 40/42 within isolation trench 26, and within line trench 3Q. Second trench isolation material 46 might be the same composition as first trench isolation material 28, or be of different composition. More preferably, such are the same material, with high density plasma deposited oxide being the preferred example. In the illustrated and preferred embodiment, second trench isolation material 46 is formed on (in contact with) conductive materials 40/42.

[0031] Referring to FIG. 10, at least some first trench isolation material 28 and at least some second trench isolation material 46 are removed from the substrate in at least one common removing step. A preferred process includes chemical mechanical polishing (CMP). In the depicted preferred embodiment, such polishing is shown conducted effective to substantially stop on nitride masking layer 24. Of course, polishing could also be continued to remove more material, for example polishing through nitride layer 24 and pad oxide layer 22. Further by way of example only, nitride layer 24 and pad oxide layer 22 might be selectively chemically etched in processing subsequent to that depicted by FIG. 10.

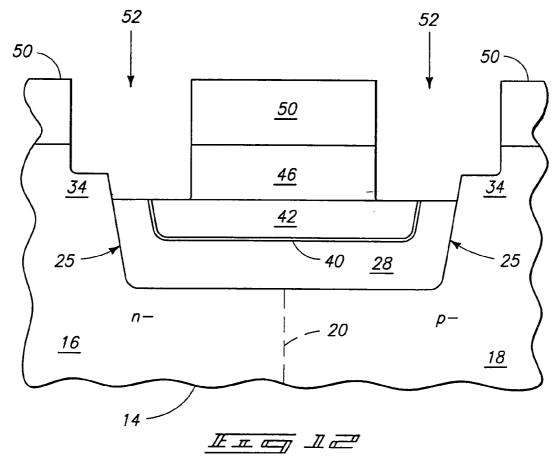

[0032] Referring to FIGS. 11 and 12, an insulative material 50 is formed over trench isolation material 28/46 and over conductive material 40/42. Exemplary materials for layer 50 include undoped and doped oxides, for example borophosphosilicate glass, phosphosilicate glass, and other doped and undoped silicon dioxides. Further at this point in the process, gate lines 36 have been fabricated prior to deposition of layer 50, and layers 24 and 22 have been removed. Contact openings 52 are etched into insulative material 50 to bridge over and between active area substrate material 34 and conductive material 40/42 within line trench 30.

[0033] Referring to FIG. 13, a conductor is formed within contact openings 52 which electrically connects the conductive material with the active area substrate material, and with the far right illustrated gate 52 as shown in FIG. 6. Such thereby effectively extends the conductive local interconnect line to electrically connect with the depicted source/drain regions and transistor gate line.

**[0034]** The invention also contemplates integrated circuitry comprising a local interconnect line independent of any method of fabrication.

**[0035]** The invention may have particular application in the formation of local interconnects in the periphery of SRAM circuitry. Processing and circuitry in accordance with the invention can serve to provide an extra level of interconnect, thereby freeing up space for higher level interconnects at upper levels of the fabrication. By embedding an extra level of interconnect in trench isolation areas, tighter metallization and interconnect density might be achievable.

**[0036]** In compliance with the statute, the invention has been described in language more or less specific as to structural and methodical features. It is to be understood, however, that the invention is not limited to the specific features shown and described, since the means herein disclosed comprise preferred forms of putting the invention into effect. The invention is, therefore, claimed in any of its forms or modifications within the proper scope of the appended claims appropriately interpreted in accordance with the doctrine of equivalents.

- 1-48. (canceled)

- **49**. A memory device comprising:

- first and second transistors formed within a semiconductor substrate, the semiconductor substrate comprising trench isolation material between the first and second transistors, the trench isolation material comprising first and second opposing sidewalls in at least one cross section;

- a trench formed within the trench isolation material; and

- a local interconnect line received within the trench and electrically connecting the a source/drain region of the first transistor with a gate of the second transistor.

**50**. The device of claim 49 wherein the first transistor, the second transistor, and the local interconnect line are components of an SRAM device.

**51**. The device of claim 50 wherein the local interconnect line electrically connects two gates of the SRAM device with source drain regions of two transistors.

**52.** The device of claim 49 further comprising insulative material received within the trench and over the local interconnect line.

**53.** The device of claim 49 wherein the local interconnect line comprises at least two different conductive materials, a first conductive material lining the trench and a second conductive material being received on the first conductive material.

**54**. The device of claim 53 further comprising insulative material received over the local interconnect line, a conductive trench being formed in the first conductive material, wherein the second conductive material is received within the conductive trench.

**55**. The device of claim 49 wherein the substrate further comprises:

a first conductivity type background region; and

a second conductivity type background region adjacent the first conductivity type background region, wherein the first sidewall extends along the first conductivity type background region, and the second sidewall extends along the second conductivity type background region.

**56**. The device of claim 55 wherein the first transistor is formed within the first conductivity type background region and the second transistor is formed within the second conductivity type background region.

**57**. The device of claim 55 wherein the local interconnect line is laterally centered between the first and second opposing sidewalls in the at least one cross section.

**58**. The device of claim 55 further comprising a boundary extending between the first and second conductivity type background regions, wherein the local interconnect line is received along the boundary.

**59**. A memory device comprising:

- a substrate comprising:

- a first conductivity type background region;

- an adjacent second conductivity type background region; and

- a boundary extending therebetween;

- a first transistor formed within the first conductivity type background region;

- a second transistor formed within the second conductivity type background region;

- trench isolation material received along the boundary and between the first and second transistors;

- a trench formed within the trench isolation material and received along the boundary; and

- a local interconnect line received within the trench, the line electrically connecting the first transistor with the second transistor.

**60**. The device of claim 59 wherein the trench isolation material comprises opposing outer sidewalls in at least one cross section, one of the sidewalls extending along at least the first region, the local interconnect line being laterally centered between the opposing outer sidewalls in the at least one cross section.

**61**. The device of claim 59 wherein the first transistor, the second transistor, and the local interconnect line are components of an SRAM device.

**62**. The device of claim 59 further comprising insulative material received within the trench and over the local interconnect line.

**63**. The device of claim 59 wherein the local interconnect line is received along the boundary.

**64**. The device of claim 59 wherein the local interconnect line comprises at least two different conductive materials, a first conductive material of the two different conductive

materials lining the trench and a second conductive material of the two different conductive materials being received on the first conductive material.

65. The device of claim 64 further comprising insulative

material received over the local interconnect line.

66. A memory device comprising:

- at least first and second pairs of transistors formed within a substrate, the first pair being electrically connected to one another by a first conductive line and the second pair being electrically connected to one another by a second conductive line, the substrate comprising trench isolation material between the first and second conductive lines;

- a trench formed within the trench isolation material; and

- a local interconnect line received within the trench and electrically connecting the first conductive line with the second conductive line.

**67**. The memory device of claim 66 wherein the local interconnect line comprises at least first and second conduc-

tive portions, the first conductive portion lining the trench and comprising a conductive trench, and the second conductive portion being received within the trench.

**68**. The memory device of claim 66 wherein the substrate further comprises at least first and second conductivity type background regions, one of the first pair of transistors being formed within the first conductivity type background region and the other of the first pair of transistors being formed with the second type background region.

**69**. The memory device of claim 68 wherein the first conductivity type background region comprises n-type conductivity material and the second type background region comprises p-type conductivity material.

**70**. The memory device of claim 68 wherein the substrate further comprises a boundary between the first and second regions, the local interconnect line being received over the boundary.

\* \* \* \* \*