(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7175551号**

**(P7175551)**

(45)発行日 令和4年11月21日(2022.11.21)

(24)登録日 令和4年11月11日(2022.11.11)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3225(2016.01) | F I | G 0 9 G | 3/3225       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 2 4 B |

| G 0 9 F | 9/30 (2006.01)  |     | G 0 9 G | 3/20 6 9 1 D |

| G 0 9 F | 9/00 (2006.01)  |     | G 0 9 G | 3/20 6 4 2 A |

| G 0 6 F | 3/041(2006.01)  |     | G 0 9 G | 3/20 6 8 0 H |

請求項の数 17 (全24頁) 最終頁に続く

(21)出願番号 特願2017-58348(P2017-58348)

(22)出願日 平成29年3月24日(2017.3.24)

(65)公開番号 特開2018-159885(P2018-159885)

A)

(43)公開日 平成30年10月11日(2018.10.11)

審査請求日 令和2年3月18日(2020.3.18)

前置審査

(73)特許権者 502161508

シナブティクス インコーポレイテッド

アメリカ合衆国, 95131 カリフォルニア州, サンノゼ, マッケイ ドラ

イブ 1109

(74)代理人 100205350

弁理士 狩野 芳正

(74)代理人 100117617

弁理士 中尾 圭策

(72)発明者 高橋 盛毅

東京都中野区中野4丁目10番2号 シ

ナブティクス・ジャパン合同会社内

橋本 直明

審査官

最終頁に続く

(54)【発明の名称】 電流駆動表示パネル及びパネル表示装置

**(57)【特許請求の範囲】****【請求項1】**

センスラインと、

第1スキャンラインと、第2スキャンラインと、第3スキャンラインと、

タッチ検出対応画素回路を含む複数の画素回路と

を備える表示パネルであって、

前記タッチ検出対応画素回路が、

データ電圧に対応する電圧を保持する保持キャパシタと、

前記保持キャパシタに接続された保持ノードと、

前記保持ノードと接地ラインとの間に接続され、前記タッチ検出対応画素回路の近傍

における物体の前記表示パネルへの接触に応じて変動する容量を有する検出キャパシタと、

電流駆動素子と、

ゲートが前記保持ノードに接続され、前記データ電圧に応じて前記電流駆動素子に電

流を供給し、前記検出キャパシタの容量に応じたセンス電流を前記センスラインに供給す

るように構成された駆動トランジスタと、

リセットトランジスタと、

を備えており、

前記保持キャパシタが前記保持ノードと前記第2スキャンラインの間に接続され、

10

20

前記リセットトランジスタが、前記第3スキャンラインの電位に応じて、所定の第1電位に固定された第1電源ラインと前記保持ノードとを電気的に接続するように構成された表示パネル。

**【請求項2】**

前記複数の画素回路は、複数の行に配置されており、

前記タッチ検出対応画素回路は、前記複数の行の第1行に位置している、

請求項1に記載の表示パネル。

**【請求項3】**

前記第1スキャンラインは、前記第1行に位置する前記画素回路にデータ電圧を書き込むときに前記第1行を選択する電位にされ、

10

前記第2スキャンラインは、前記複数の行のうち、前記第1行に隣接し、且つ、前記第1行の画素回路よりも早くデータ電圧が書き込まれる第2行に位置する前記画素回路にデータ電圧を書き込むときに前記第2行を選択する電位にされ、

前記第3スキャンラインは、前記複数の行のうち、前記第2行に隣接し、且つ、前記第2行の画素回路よりも早くデータ電圧が書き込まれる第3行に位置する前記画素回路にデータ電圧を書き込むときに前記第3行を選択する電位にされる

請求項2に記載の表示パネル。

**【請求項4】**

更に、

第1エミッションラインと、

第2エミッションラインと、

データラインと

20

を備え、

前記駆動トランジスタのゲートが前記保持ノードに接続され、

前記タッチ検出対応画素回路が、更に、

前記第1スキャンラインの電位に応じて、前記データラインを前記駆動トランジスタのソースに電気的に接続するように構成された第1選択トランジスタと、

所定の第2電位に固定された第2電源ラインを前記駆動トランジスタのソースに電気的に接続するように構成された第2選択トランジスタと、

前記第1エミッションラインの電位に応じて、前記駆動トランジスタのドレインを前記電流駆動素子に電気的に接続するように構成された第3選択トランジスタと、

30

前記第2スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記センスラインに電気的に接続するように構成された第4選択トランジスタとを備える

請求項2に記載の表示パネル。

**【請求項5】**

前記タッチ検出対応画素回路が、更に、前記第1スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記駆動トランジスタのゲートに電気的に接続するように構成された閾値補償トランジスタを備える

請求項4に記載の表示パネル。

40

**【請求項6】**

更に、

エミッションラインと、

データラインと

を備え、

前記タッチ検出対応画素回路が、更に、

前記保持ノードと前記駆動トランジスタのゲートとの間に接続された閾値補償キャパシタと、

前記第1スキャンラインの電位に応じて、前記データラインを前記保持ノードに電気的に接続するように構成された第1選択トランジスタと、

50

前記エミッションラインの電位に応じて、前記駆動トランジスタのドレインを前記電流駆動素子に電気的に接続するように構成された第2選択トランジスタと、

前記第2スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記センスラインに電気的に接続するように構成された第3選択トランジスタと、

前記第3スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記駆動トランジスタのゲートに電気的に接続するように構成された閾値補償トランジスタとを備える

請求項2に記載の表示パネル。

**【請求項7】**

前記検出キャパシタが、

第1電極と、

第2電極と、

前記第1電極と前記第2電極の間に設けられた絶縁層とを備え、

前記検出キャパシタは、その少なくとも一部分において、前記第1電極と前記第2電極の間の距離が、前記検出キャパシタの近傍において当該表示パネルに作用する圧力に依存して変化するように構成されている

請求項1に記載の表示パネル。

**【請求項8】**

前記絶縁層が、弾性を有する有機絶縁体で形成されている

請求項7に記載の表示パネル。

**【請求項9】**

データ電圧を生成し、センス電流を受け取るように構成された表示ドライバと、

センスラインと、第1スキャンラインと、第2スキャンラインと、第3スキャンラインと、タッチ検出対応画素回路を含む複数の画素回路とを備える表示パネルとを備え、

前記タッチ検出対応画素回路が、

前記データ電圧に対応する電圧を保持する保持キャパシタと、

前記保持キャパシタに接続された保持ノードと、

前記保持ノードと接地ラインとの間に接続され、前記タッチ検出対応画素回路の近傍における物体の前記表示パネルへの接触に応じて変動する容量を有する検出キャパシタと、電流駆動素子と、

ゲートが前記保持ノードに接続され、前記データ電圧に応じて前記電流駆動素子に電流を供給し、前記検出キャパシタの容量に応じたセンス電流を前記センスラインに供給するように構成された駆動トランジスタと、

リセットトランジスタと、

を備え、

前記保持キャパシタが前記保持ノードと前記第2スキャンラインの間に接続され、前記リセットトランジスタが、前記第3スキャンラインの電位に応じて、所定の第1電位に固定された第1電源ラインと前記保持ノードとを電気的に接続するように構成された

パネル表示装置。

**【請求項10】**

前記複数の画素回路は、複数の行に配置されており、

前記タッチ検出対応画素回路は、前記複数の行の第1行に位置している、

請求項9に記載のパネル表示装置。

**【請求項11】**

前記第1スキャンラインは、前記第1行に位置する前記画素回路にデータ電圧を書き込むときに前記第1行を選択する電位にされ、

前記第2スキャンラインは、前記複数の行のうち、前記第1行に隣接し、且つ、前記第1行の画素回路よりも早くデータ電圧が書き込まれる第2行に位置する前記画素回路にデ

10

20

30

40

50

データ電圧を書き込むときに前記第2行を選択する電位にされ、

前記第3スキャンラインは、前記複数の行のうち、前記第2行に隣接し、且つ、前記第2行の画素回路よりも早くデータ電圧が書き込まれる第3行に位置する前記画素回路にデータ電圧を書き込むときに前記第3行を選択する電位にされる

請求項10に記載のパネル表示装置。

**【請求項12】**

前記表示パネルが、更に、

第1エミッションラインと、

第2エミッションラインと、

データラインと

を備え、

前記駆動トランジスタのゲートが前記保持ノードに接続され、

前記タッチ検出対応画素回路が、更に、

前記第1スキャンラインの電位に応じて、前記データラインを前記駆動トランジスタのソースに電気的に接続するように構成された第1選択トランジスタと、

所定の第2電位に固定された第2電源ラインを前記駆動トランジスタのソースに電気的に接続するように構成された第2選択トランジスタと、

前記第1エミッションラインの電位に応じて、前記駆動トランジスタのドレインを前記電流駆動素子に電気的に接続するように構成された第3選択トランジスタと、

前記第2スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記センスラインに電気的に接続するように構成された第4選択トランジスタ

とを備える

請求項10に記載のパネル表示装置。

**【請求項13】**

前記タッチ検出対応画素回路が、更に、前記第1スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記駆動トランジスタのゲートに電気的に接続するように構成された閾値補償トランジスタを備える

請求項12に記載のパネル表示装置。

**【請求項14】**

前記表示パネルが、更に、

エミッションラインと、

データライン

とを具備し、

前記タッチ検出対応画素回路が、更に、

前記保持ノードと前記駆動トランジスタのゲートとの間に接続された閾値補償キャパシタと、

前記第1スキャンラインの電位に応じて、前記データラインを前記保持ノードに電気的に接続するように構成された第1選択トランジスタと、

前記エミッションラインの電位に応じて、前記駆動トランジスタのドレインを前記電流駆動素子に電気的に接続するように構成された第2選択トランジスタと、

前記第2スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記センスラインに電気的に接続するように構成された第3選択トランジスタと、

前記第3スキャンラインの電位に応じて、前記駆動トランジスタのドレインを前記駆動トランジスタのゲートに電気的に接続するように構成された閾値補償トランジスタとを備える

請求項10に記載の表示パネル。

**【請求項15】**

前記検出キャパシタが、

第1電極と、

第2電極と、

10

20

30

40

50

前記第1電極と前記第2電極の間に設けられた絶縁層

とを備え、

前記検出キャパシタは、その少なくとも一部分において、前記第1電極と前記第2電極の間の距離が、前記検出キャパシタの近傍において当該表示パネルに作用する圧力に依存して変化するように構成され、

前記表示ドライバは、前記センス電流に基づいて前記表示パネルに作用する圧力を検出するように構成された

請求項9に記載のパネル表示装置。

**【請求項16】**

前記絶縁層が、弾性を有する有機絶縁体で形成されている

10

請求項15に記載のパネル表示装置。

**【請求項17】**

表示パネルの画素回路の、ゲートが保持ノードに接続されている駆動トランジスタを用いて、前記画素回路の、前記保持ノードに接続されている保持キャパシタに保持されている電圧に応じて前記画素回路の電流駆動素子に駆動電流を供給すること、

前記駆動トランジスタを用いて、前記保持ノードと接地ラインとの間に接続された検出キャパシタの容量に応じてセンスラインにセンス電流を供給すること、

前記画素回路に集積化されているリセットトランジスタによって、前記駆動トランジスタが前記駆動トランジスタのゲートとドレインとが電気的に接続された状態にある間に前記保持ノードを所定電位に設定することと、

20

を含み、

前記容量が、前記画素回路の近傍における物体の前記表示パネルとの接触に応じて変化し、

閾値電圧補償キャパシタが、前記保持ノードと前記駆動トランジスタの前記ゲートとの間に接続され、

前記駆動電流と前記センス電流とが、前記閾値電圧補償キャパシタに保持されている電圧に依存する

方法。

**【発明の詳細な説明】**

**【技術分野】**

30

**【0001】**

本発明は、電流駆動表示パネル及びパネル表示装置に関し、特に、電流駆動素子を画素回路に用いる電流駆動表示パネルに対するタッチ検出(touch sensing)に関する。

**【背景技術】**

**【0002】**

近年のパネル表示装置は、しばしば、表示パネルへの物体(例えば、人体の指)の接触を検出するタッチ検出(touch sensing)に対応するように構成される。タッチ検出に対応した表示パネルは、単独で入出力装置として使用可能であり、ユーザフレンドリ性の向上に寄与する。なお、本明細書でいう「タッチ検出」は、表示パネルに物体が接触した位置の検出を含んでおり、加えて、接触する圧力の検出を含んでいてもよい。

40

**【0003】**

特に携帯端末に用いられるパネル表示装置について、パネル表示装置が占める体積の減少が求められている。このような要求を満たすため、液晶表示パネルについては、容量性負荷のみが接続された共通電極(「対向電極」とも呼ばれる)をタッチ検出のための検出電極として用いる技術が提案されている。共通電極をタッチ検出のための検出電極として用いることで、液晶表示パネルの外部にタッチパネルを設けることなくタッチ検出を行うことができる。

**【0004】**

一方で、例えばOLED(organic light emitting diode)表示パネルのような電流駆動素子を画素回路に用いる表示パネル(以下、「電流駆動表示パネル」という。)には

50

、容量性負荷のみが接続された共通電極は存在しないため、このような手法によってタッチ検出を行うことはできない。このような背景から、発明者は、電流駆動表示パネル（例えば、OLED表示パネル）にタッチ検出のための検出素子を集積化する技術について検討している。

#### 【0005】

電流駆動表示パネルにタッチ検出のための検出素子を集積化する技術を検討する上で発明者が認識した課題の一つは、タッチ検出のために追加される回路素子（例えば、薄膜トランジスタ）及び配線の数の低減である。追加の回路素子及び配線の数を低減することは、設計や製造プロセスの容易化に寄与する。このように、タッチ検出のために追加される回路素子及び配線の数の低減には、技術的なニーズが存在する。

10

#### 【0006】

なお、米国特許第8,427,435号及びTakahashi et al. "Embedded Liquid Crystal Capacitive Touch Screen Technology for Large Size LCD applications", SID Symposium Digest, pp. 563-566, 2009は、検出キャパシタ(sensor capacitor)を含むタッチセンサを液晶表示パネルに組み込む技術を開示している。

#### 【0007】

また、Park et al. "High-Speed AMOLED Pixel Circuit and Driving Scheme", SID Symposium Digest, pp. 806-809は、OLED表示パネルの画素回路の構成を開示している。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

#### 【文献】米国特許第8,427,435号

#### 【非特許文献】

#### 【0009】

【文献】Takahashi et al. "Embedded Liquid Crystal Capacitive Touch Screen Technology for Large Size LCD applications", SID Symposium Digest, pp. 563-566, 2009

Park et al. "High-Speed AMOLED Pixel Circuit and Driving Scheme", SID Symposium Digest, pp. 806-809

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

従って、本発明の目的の一つは、タッチ検出のために追加される回路素子及び配線が低減された電流駆動表示パネルを提供することにある。本発明の他の目的及び新規な特徴は、以下の開示から当業者には理解されるであろう。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一の観点では、電流駆動表示パネルが、複数の画素回路と、センスラインとを具備する。複数の画素回路は、タッチ検出対応画素回路を含む。タッチ検出対応画素回路は、電流駆動素子と、駆動トランジスタと、データ電圧に対応する電圧を保持する保持キャパシタと、検出キャパシタとを備えている。検出キャパシタは、検出キャパシタの容量が、タッチ検出対応画素回路の近傍における物体の電流駆動表示パネルへの接触に応じて変動するように構成されている。タッチ検出対応画素回路は、駆動トランジスタが、データ電圧に応じて電流駆動素子に電流を供給すると共に、駆動トランジスタが、検出キャパシタの容量に応じたセンス電流をセンスラインに供給するように構成されている。

40

#### 【0012】

本発明の他の観点では、パネル表示装置が、上記の電流駆動表示パネルと、電流駆動表示パネルにデータ電圧を供給し、電流駆動表示パネルからセンス電流を受け取るタッチコントローラ内蔵表示ドライバを備えている。

50

**【発明の効果】****【0013】**

本発明によれば、タッチ検出のために追加される回路素子及び配線が低減された電流駆動表示パネルが提供される。

**【図面の簡単な説明】****【0014】**

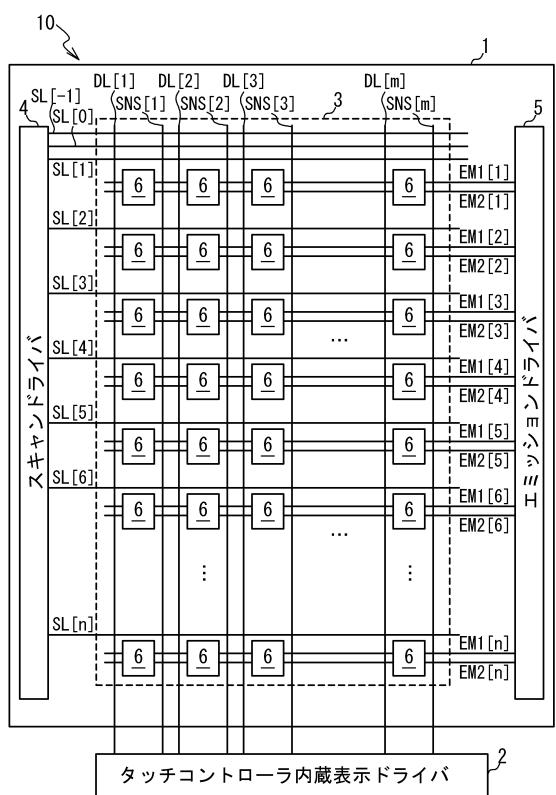

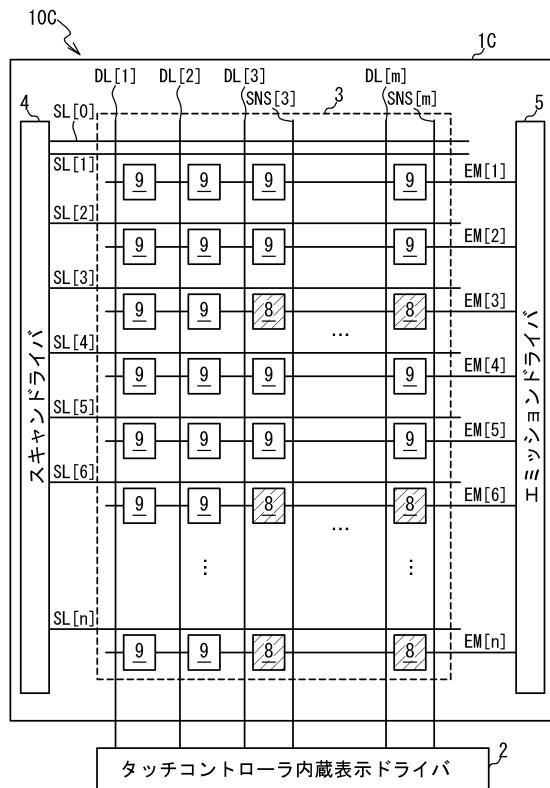

**【図1】**第1の実施形態のパネル表示装置の構成を示すブロック図である。

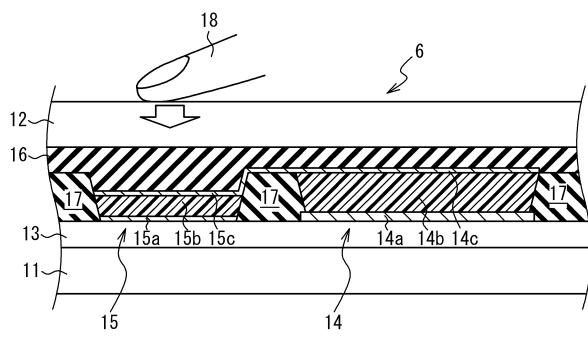

**【図2】**第1の実施形態におけるOLED表示パネルの画素回路の構造を概略的に示す断面図である。

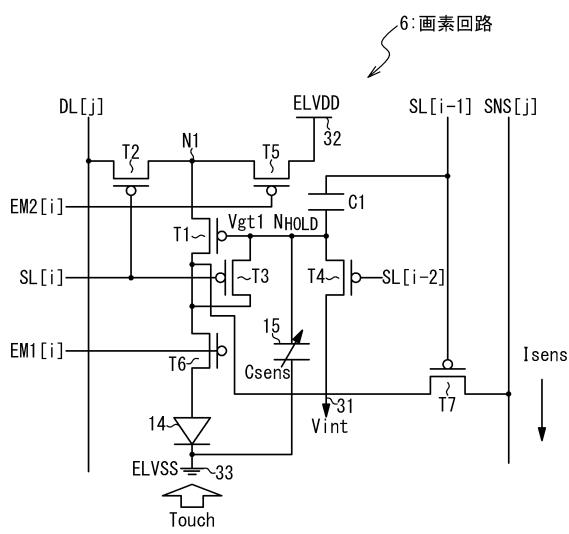

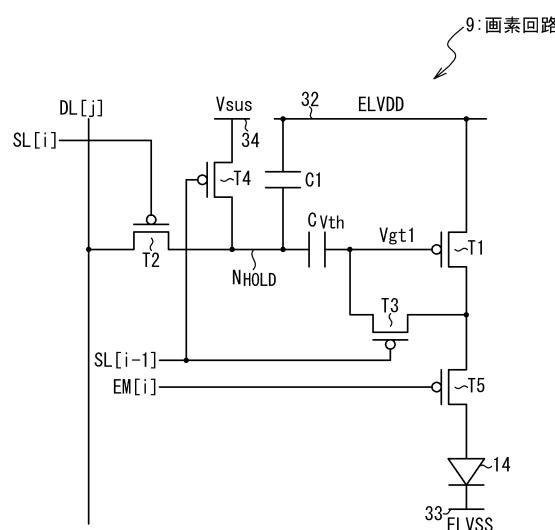

**【図3】**第1の実施形態における画素回路の回路構成を示す回路図である。

10

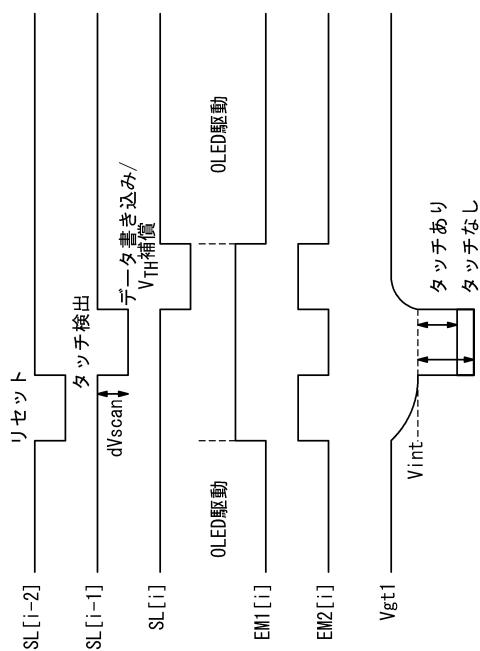

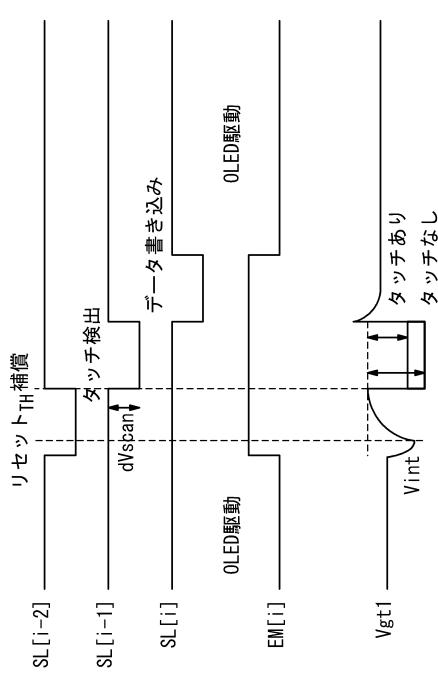

**【図4】**図3に図示されている画素回路の動作を示すタイミングチャートである。

**【図5】**第1の実施形態の変形例におけるパネル表示装置の構成を示すブロック図である。

**【図6】**図5のパネル表示装置における、検出キャパシタを含まない画素回路の回路構成を示す回路図である。

**【図7】**第2の実施形態のパネル表示装置の構成を示すブロック図である。

**【図8】**第2の実施形態における画素回路の回路構成を示す回路図である。

**【図9】**図3に図示されている画素回路の動作を示すタイミングチャートである。

**【図10】**第2の実施形態の変形例におけるパネル表示装置の構成を示すブロック図である。

**【図11】**図10のパネル表示装置における、検出キャパシタを含まない画素回路の回路構成を示す回路図である。

20

**【発明を実施するための形態】****【0015】**

以下、添付図面を参照しながら、本発明の好適な実施形態を説明する。

**【0016】****(第1の実施形態)**

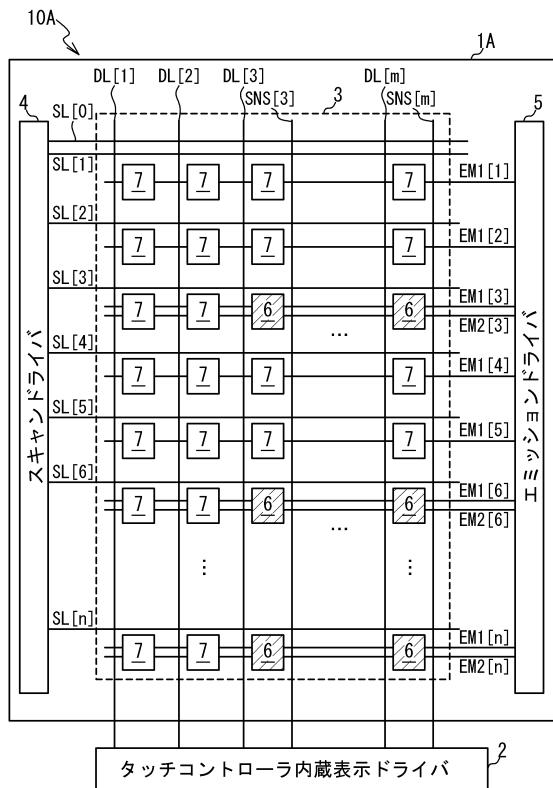

図1は、第1の実施形態のパネル表示装置10の構成を示すブロック図である。パネル表示装置10は、OLED表示パネル1と、タッチコントローラ内蔵表示ドライバ2とを備えている。タッチコントローラ内蔵表示ドライバ2は、OLED表示パネル1を駆動すると共に、OLED表示パネル1についてのタッチ検出を行う機能を有している。

30

**【0017】**

本実施形態では、OLED表示パネル1は、電圧プログラミング法に対応した電流駆動表示パネルとして構成されている。OLED表示パネル1は、表示領域3とスキャンドライバ4とエミッションドライバ5とを備えている。表示領域3には、行列に配置された画素回路6と、スキャンラインSL[-1]～SL[n]と、第1エミッショングラインEM1[1]～EM1[n]と、第2エミッショングラインEM2[1]～EM2[n]と、データラインDL[1]～DL[m]と、センスラインSNS[1]～SNS[m]とが配置される。スキャンドライバ4は、スキャンラインSL[-1]～SL[n]を駆動し、エミッションドライバ5は、第1エミッショングラインEM1[1]～EM1[n]と、第2エミッショングラインEM2[1]～EM2[n]とを駆動する。スキャンドライバ4とエミッションドライバ5とは、例えば、SOG技術(system on glass)を用いてOLED表示パネル1に集積化されてもよい。

40

**【0018】**

各画素回路6は、OLED素子を用いて赤色(R)、緑色(G)、青色(B)のいずれかの色を表示するように構成されている。一実施形態では、各画素回路6は、赤色(R)、緑色(G)、青色(B)のいずれかの光を発光するOLED素子を含んでいてもよい。他の実施形態では、各画素回路6が、白色の光を発光するOLED素子を含んでおり、赤色、緑色、青色のカラーフィルタを用いて赤色、緑色、青色のいずれかの色を表示するように構成されてもよい。赤色を表示するOLED素子を含む画素回路6は、R副画素として用いられる。同様に、緑色を表示するOLED素子を含む画素回路6は、G副画素とし

50

て用いられ、青色を表示するOLED素子を含む画素回路6は、B副画素として用いられる。加えて、各画素回路6は、タッチ検出に対応するように構成されており、タッチ検出に用いられる検出キャパシタを含んでいる。

#### 【0019】

図2は、OLED表示パネル1の各画素回路6の構造を概略的に示す断面図である。OLED表示パネル1は、下側ガラス基板11と、上側ガラス基板12とを備えている。下側ガラス基板11と上側ガラス基板12との間に、回路形成層13と、OLED素子14と、検出キャパシタ15と、パッシベーション層16とが形成されている。回路形成層13には、各画素回路6の薄膜トランジスタ、スキャンラインSL[-1]~SL[n]、第1エミッションラインEM1[1]~EM1[n]、第2エミッションラインEM2[1]~EM2[n]、データラインDL[1]~DL[m]、センスラインSNS[1]~SNS[m]、及び、これらを被覆するパッシベーション層が集積化される。OLED素子14と検出キャパシタ15とは、回路形成層13の上面に形成されている。OLED素子14は、アノード14aと、発光層14bと、カソード14cとを備えている。検出キャパシタ15は、下部電極15aと絶縁層15bと上部電極15cとを備えている。なお、図2には、カソード14cと上部電極15cとが接続されている構造が図示されているが、カソード14cと上部電極15cとは、分離されていてもよい。OLED素子14と検出キャパシタ15のそれぞれは、スペーサ17によって他のOLED素子14及び検出キャパシタ15から分離されている。パッシベーション層16は、OLED素子14と検出キャパシタ15とを被覆するように形成されている。

10

#### 【0020】

検出キャパシタ15は、タッチ検出のためのセンス信号の生成に用いられる。上側ガラス基板12が、検出キャパシタ15の近傍の位置で、物体、例えば、人体の指18によって押されると、検出キャパシタ15が微小に変形して、検出キャパシタ15の少なくとも一部分において下部電極15aと上部電極15cとの距離が変化する。下部電極15aと上部電極15cとの距離が変化すると、検出キャパシタ15の容量が変化する。この検出キャパシタ15の容量の変化は、検出キャパシタ15の近傍においてOLED表示パネル1に作用する圧力に依存している。後に詳細に説明するように、各画素回路6は、検出キャパシタ15の容量の変化に応じた電流レベルを有するセンス電流Isensを生成するように構成される。検出キャパシタ15が変形しやすいように、絶縁層15bは、例えば、弾性を有する有機絶縁体で形成されることが好ましい。

20

#### 【0021】

図1を再度に参照して、スキャンラインSL[-1]~SL[n]と、第1エミッションラインEM1[1]~EM1[n]と、第2エミッションラインEM2[1]~EM2[n]とは、OLED表示パネル1の水平方向(画素回路6の行の方向)に延伸するよう設けられている。スキャンラインSL[-1]~SL[n]は、リセットする画素回路6の行の選択、センス信号を得る画素回路6の行の選択、及び、データ電圧を書き込むべき画素回路6の行の選択のために用いられる。また、第1エミッションラインEM1[1]~EM1[n]と第2エミッションラインEM2[1]~EM2[n]とは、OLED素子14の発光を許可する画素回路6の行を選択するために用いられる。なお、図1に図示されている構成では、OLED表示パネル1が、画素回路6の行のそれぞれに対応するスキャンラインSL[1]~SL[n]に加え、2本の追加のスキャンラインSL[-1]、SL[0]を有している。該2本の追加のスキャンラインSL[-1]、SL[0]は、上から2行の画素回路6について、リセットする画素回路6の行の選択、及び、センス信号を得る画素回路6の行の選択を行うために用いられる。

30

#### 【0022】

データラインDL[1]~DL[m]、センスラインSNS[1]~SNS[m]とは、垂直方向(画素回路6の列の方向)に延伸するよう設けられている。データラインDL[1]~DL[m]は、各画素回路6にデータ電圧を供給するために用いられる。センスラインSNS[1]~SNS[m]は、後述のように、タッチ検出において各画素回路

40

50

6において生成されるセンス電流  $I_{\text{sens}}$  を、各画素回路 6 から出力するために用いられる。

#### 【0023】

タッチコントローラ内蔵表示ドライバ 2 は、外部から（例えば、アプリケーションプロセッサから）供給される画像データに応答してデータライン  $DL[1] \sim DL[m]$  にデータ電圧を供給し、これにより、データライン  $DL[1] \sim DL[m]$  を介して各画素回路 6 にデータ電圧を書き込む。加えて、タッチコントローラ内蔵表示ドライバ 2 は、各画素回路 6 から得られたセンス電流  $I_{\text{sens}}$  の電流レベルを検出してタッチ検出を行う機能も有している。タッチコントローラ内蔵表示ドライバ 2 は、タッチ検出の結果を示すタッチ検出データを出力する。一実施形態では、タッチコントローラ内蔵表示ドライバ 2 は、表面実装技術を用いて OLED 表示パネル 1 の上に搭載されてもよい。10

#### 【0024】

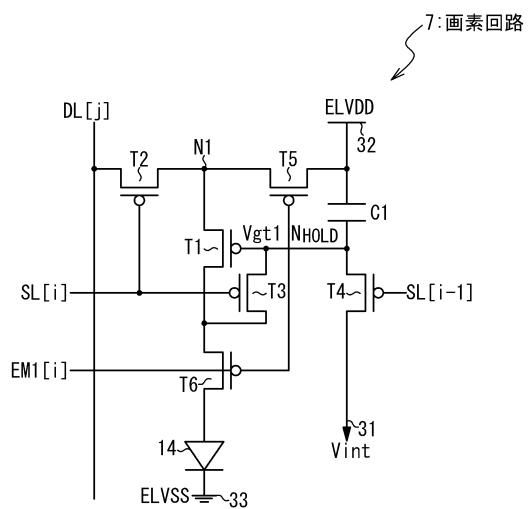

図 3 は、第 1 の実施形態における画素回路 6 の回路構成を示す回路図である。なお、図 3 は、 $i$  行目、 $j$  列目に位置している画素回路 6 の構成を図示しているが、他の画素回路 6 の構成も、図 3 に図示されている構成と同一である。ここで、スキャンライン  $SL[i]$  は、 $i$  行目に位置している画素回路 6 にデータ電圧を書き込む水平同期期間において活性化されるスキャンラインである。同様に、スキャンライン  $SL[i-1]$  は、 $i-1$  行目に位置している画素回路 6 にデータ電圧を書き込む水平同期期間において活性化されるスキャンラインであり、スキャンライン  $SL[i-2]$  は、 $i-2$  行目に位置している画素回路 6 にデータ電圧を書き込む水平同期期間において活性化されるスキャンラインである。20

#### 【0025】

第 1 の実施形態では、各画素回路 6 が、上述の OLED 素子 14、検出キャパシタ 15 に加え、駆動トランジスタ T 1 と、選択トランジスタ T 2 と、閾値補償トランジスタ T 3 と、リセットトランジスタ T 4 と、選択トランジスタ T 5、T 6、T 7 と、保持キャパシタ C 1 を備えている。本実施形態では、駆動トランジスタ T 1 と、選択トランジスタ T 2 と、閾値補償トランジスタ T 3 と、リセットトランジスタ T 4 と、選択トランジスタ T 5、T 6、T 7 は、いずれも、P 型の MOS トランジスタとして構成される。

#### 【0026】

駆動トランジスタ T 1 は、各画素回路 6 に書き込まれたデータ電圧に応じた駆動電流を生成し、生成した駆動電流を OLED 素子 14 に供給する。駆動トランジスタ T 1 は、そのソースがノード N 1 に接続され、ゲートが保持ノード N<sub>HOLD</sub> に接続されている。30

#### 【0027】

選択トランジスタ T 2 は、データ電圧を書き込む画素回路 6 を選択するために用いられる。選択トランジスタ T 2 は、ソースがデータライン  $DL[j]$  に接続され、ドレインがノード N 1 に接続され、ゲートがスキャンライン  $SL[i]$  に接続されている。選択トランジスタ T 2 は、スキャンライン  $SL[i]$  の電位に応じて、データライン  $DL[j]$  とノード N 1（即ち、駆動トランジスタ T 1 のソース）とを電気的に接続する。

#### 【0028】

閾値補償トランジスタ T 3 は、ソースが駆動トランジスタ T 1 のドレインに接続され、ドレインが駆動トランジスタ T 1 のゲートに接続され、ゲートがスキャンライン  $SL[i]$  に接続されている。閾値補償トランジスタ T 3 は、スキャンライン  $SL[i]$  の電位に応じて、駆動トランジスタ T 1 のドレインとゲートとを電気的に接続する。40

#### 【0029】

リセットトランジスタ T 4 は、スキャンライン  $SL[i-2]$  の電位に応じて保持ノード N<sub>HOLD</sub> と内部電源ライン 31 とを電気的に接続することで保持キャパシタ C 1 及び検出キャパシタ 15 をリセットするために用いられる。本実施形態では、リセットトランジスタ T 4 は、ソースが保持ノード N<sub>HOLD</sub> に接続され、ドレインが内部電源ライン 31 に接続され、ゲートがスキャンライン  $SL[i-2]$  に接続されている。ここで、内部電源ライン 31 は、電位  $V_{int}$  に固定された電源ラインである。50

**【 0 0 3 0 】**

選択トランジスタ T 5、T 6 は、O L E D 素子 1 4 を発光させる画素回路 6 を選択するために用いられる。詳細には、選択トランジスタ T 5 は、ソースが電源ライン 3 2 に接続され、ドレインがノード N 1 に接続され、ゲートが第 2 エミッショナーライン E M 2 [ i ] に接続されている。ここで、電源ライン 3 2 は、O L E D 素子 1 4 を駆動に用いられる電源電圧 E L V D D が供給される電源ラインである。選択トランジスタ T 5 は、第 2 エミッショナーライン E M 2 [ i ] の電位に応じて、電源ライン 3 2 とノード N 1 ( 即ち、駆動トランジスタ T 1 のソース ) とを電気的に接続する。また、選択トランジスタ T 6 は、ソースが駆動トランジスタ T 1 のドレインに接続され、ドレインが O L E D 素子 1 4 のアノードに接続され、ゲートが第 1 エミッショナーライン E M 1 [ i ] に接続されている。選択トランジスタ T 6 は、第 1 エミッショナーライン E M 1 [ i ] の電位に応じて、駆動トランジスタ T 1 のドレインと O L E D 素子 1 4 のアノードとを電気的に接続するように構成されている。

**【 0 0 3 1 】**

選択トランジスタ T 7 は、センス電流 I s e n s を取得する画素回路 6 を選択するために用いられる。選択トランジスタ T 7 は、ソースが駆動トランジスタ T 1 のドレインに接続され、ドレインがセンスライン S N S [ j ] に接続され、ゲートがスキャンライン S L [ i - 1 ] に接続されている。選択トランジスタ T 7 は、スキャンライン S L [ i - 1 ] の電位に応じて、駆動トランジスタ T 1 のドレインとセンスライン S N S [ j ] とを電気的に接続するように構成されている。

**【 0 0 3 2 】**

保持キャパシタ C 1 は、当該画素回路 6 に対応する副画素の階調 ( 即ち、O L E D 素子 1 4 が発光すべき輝度 ) に対応するデータ電圧を保持する。保持キャパシタ C 1 は、保持ノード N H O L D とスキャンライン S L [ i - 1 ] との間に接続されている。

**【 0 0 3 3 】**

O L E D 素子 1 4 は、アノードが選択トランジスタ T 6 のドレインに接続され、カソードが接地ライン 3 3 に接続されている。ここで、接地ライン 3 3 は、接地電位 E L V S S に固定されている電源ラインである。

**【 0 0 3 4 】**

検出キャパシタ 1 5 は、上述のように、タッチ検出のためのセンス信号の生成に用いられる。検出キャパシタ 1 5 は、保持ノード N H O L D と接地ライン 3 3 との間に接続されている。

**【 0 0 3 5 】**

図 3 に図示されている画素回路 6 は、いわゆる 6 T 1 C 型画素回路 ( 上記の非特許文献 2 参照 ) に、選択トランジスタ T 7 、第 2 エミッショナーライン E M 2 、検出キャパシタ 1 5 、及び、センスライン S N S を追加した構成であることに留意されたい。図 3 に図示されている構成では、O L E D 素子 1 4 を駆動するために用いられる回路素子及び配線が、タッチ検出のためのセンス信号の生成にも用いられ、これにより、タッチ検出のために画素回路 6 に追加される回路素子及び配線を低減することができる。

**【 0 0 3 6 】**

詳細には、まず、O L E D 素子 1 4 にデータ電圧に応じた駆動電流を供給する駆動トランジスタ T 1 が、検出キャパシタ 1 5 の容量に応じてタッチ検出に用いられるセンス電流 I s e n s を生成する增幅トランジスタとしても用いられる。

**【 0 0 3 7 】**

また、保持キャパシタ C 1 をリセットするために用いられるリセットトランジスタ T 4 が、検出キャパシタ 1 5 をリセットするためにも用いられる。詳細には、図 3 に図示されている画素回路 6 では、保持ノード N H O L D ( 即ち、駆動トランジスタ T 1 のゲート ) に保持キャパシタ C 1 の一端と検出キャパシタ 1 5 の一端が接続されており、且つ、リセットトランジスタ T 4 が、保持ノード N H O L D と内部電源ライン 3 1 とをスキャンライン S L [ i - 2 ] の電位に応じて電気的に接続する。このような構成によれば、一つのリセッ

トランジスタ T 4 によって保持キャパシタ C 1 と検出キャパシタ C 5 の両方をリセットできる。

#### 【 0 0 3 8 】

更に、データ電圧を保持する保持キャパシタ C 1 が、センス電流 I\_sens の生成においてリファレンスキャパシタとして使用される。

#### 【 0 0 3 9 】

このように、本実施形態の画素回路 6 の構成によれば、回路素子を OLE D 素子 14 の駆動とタッチ検出に用いられるセンス電流 I\_sens の生成に兼用することで、タッチ検出のために追加される回路素子及び配線を低減することができる。

#### 【 0 0 4 0 】

図 4 は、図 3 に図示されている画素回路 6 ( i 行 j 列に位置する画素回路 6 ) の動作を示すタイミングチャートである。なお、本実施形態では、スキャンライン SL [ i - 2 ] ~ [ i ] 、第 1 エミッショングライン EM1 [ i ] 及び第 2 エミッショングライン EM2 [ i ] は、いずれも、ローアクティブ ( low-active ) である。初期状態において、スキャンライン SL [ i - 2 ] 、 SL [ i - 1 ] 、 SL [ i ] は、いずれも、非活性化され ( deactivated ) 、第 1 エミッショングライン EM1 [ i ] 、第 2 エミッショングライン EM2 [ i ] は、いずれも、活性化されている ( activated ) ものとする。

#### 【 0 0 4 1 】

図 3 に図示されている画素回路 6 の動作は、リセット動作、タッチ検出動作、データ書き込み動作、及び、OLE D 素子 14 の駆動動作を含んでいる。

#### 【 0 0 4 2 】

リセット動作では、スキャンライン SL [ i - 2 ] が活性化され、更に、第 1 エミッショングライン EM1 [ i ] 、第 2 エミッショングライン EM2 [ i ] が非活性化される。ここで、スキャンライン SL [ i - 2 ] は、 i - 2 行目の画素回路 6 にデータ電圧を書き込む際に活性化されるスキャンラインであることに留意されたい。これにより、リセットトランジスタ T 4 がオンされ、保持ノード N\_HOLD の電位、即ち、駆動トランジスタ T 1 のゲート電位 Vgt 1 が、電位 Vinet にリセットされる。

#### 【 0 0 4 3 】

リセット動作に続いてタッチ検出動作が行われる。タッチ検出動作では、スキャンライン SL [ i - 2 ] が非活性化されると共にスキャンライン SL [ i - 1 ] が活性化される。上述のように、スキャンライン SL [ i - 1 ] はローアクティブであり、且つ、保持ノード N\_HOLD は、保持キャパシタ C 1 を介してスキャンライン SL [ i - 1 ] に接続されているから、保持ノード N\_HOLD の電位、即ち、駆動トランジスタ T 1 のゲート電位 Vgt 1 は、スキャンライン SL [ i - 1 ] のプルダウンによって低下する。

#### 【 0 0 4 4 】

ここで、スキャンライン SL [ i - 1 ] が活性化されたときの駆動トランジスタ T 1 のゲート電位 Vgt 1 の変化量 dV\_sens は、検出キャパシタ C 5 の容量 C\_sens に依存しており、下記式で表される：

#### 【 数 1 】

$$dV_{sens} = \frac{dV_{scan} \times C1}{(C_{sens} + C1)} \quad \cdots (1)$$

ここで、 dV\_scan は、スキャンライン SL [ i - 1 ] が活性化されたとき ( 即ち、スキャンライン SL [ i - 1 ] がプルダウンされたとき ) のスキャンライン SL [ i - 1 ]

10

20

30

40

50

の電位の変化量である。スキャンラインSL[i - 1]が活性化されたときの駆動トランジスタT1のゲート電位Vgt1は、検出キャパシタ15の容量Cseensに依存することになる。

#### 【0045】

検出キャパシタ15の容量Cseensは、当該画素回路6の近傍におけるOLED表示パネル1への物体、例えば、人体の指の接触の有無に依存するから、結果として、駆動トランジスタT1のゲート電位Vgt1は、OLED表示パネル1への物体の接触の有無に依存することになる。当該画素回路6の近傍においてOLED表示パネル1に物体が接触していると、検出キャパシタ15の絶縁層15bの厚みが薄くなり、検出キャパシタ15の容量Cseensが増加する。検出キャパシタ15の容量Cseensが増加すると、図4の凡例「タッチあり」に示されているように、ゲート電位Vgt1の変化dVseensが相対的に小さくなる。逆に、当該画素回路6の近傍においてOLED表示パネル1に物体が接触していない場合には、検出キャパシタ15の容量Cseensが減少し、図4の凡例「タッチなし」に示されているように、ゲート電位Vgt1の変化dVseensが相対的に大きくなる。10

#### 【0046】

スキャンラインSL[i - 1]の活性化に同期して、第2エミッショナーラインEM2[i]は活性化される。これにより、電源ライン32から選択トランジスタT5、駆動トランジスタT1及び選択トランジスタT7を介してセンスラインSNS[j]にセンス電流Iseensを流す電流パスが形成される。センス電流Iseensは、駆動トランジスタT1のゲート電位Vgt1に依存しているので、画素回路6から得られるセンス電流Iseensは、当該画素回路6の近傍におけるOLED表示パネル1への物体、例えば、人体の指の接触の有無に依存することになる。よって、タッチコントローラ内蔵表示ドライバ2によってセンス電流Iseensを検出することで、各画素回路6の近傍におけるOLED表示パネル1への物体の接触の有無を検出することができる。20

#### 【0047】

検出キャパシタ15の容量Cseensは、検出キャパシタ15に作用する圧力、即ち、検出キャパシタ15の近傍においてOLED表示パネル1に作用する圧力に依存するので、センス電流Iseensを検出することにより、物体がOLED表示パネル1に接触して作用する圧力を検出することも可能である。例えば、物体がOLED表示パネル1に接触する圧力が増大すると、検出キャパシタ15の絶縁層15bの厚みが薄くなり、検出キャパシタ15の容量Cseensが増加する。上記から理解されるように、センス電流Iseensは、検出キャパシタ15の容量Cseensに応じた電流レベルを有しているので、センス電流Iseensを検出することで、物体がOLED表示パネル1に接触して作用する圧力を検出することができる。30

#### 【0048】

単にOLED表示パネル1への物体の接触の有無を検出するか、加えて物体がOLED表示パネル1に作用する圧力を検出するかは、本実施形態のOLED表示パネル1の応用に応じて決めてよい。

#### 【0049】

タッチ検出動作に続いてデータ書き込み動作が行われる。データ書き込み動作では、第2エミッショナーラインEM2[i]及びスキャンラインSL[i - 1]が非活性化されると共にスキャンラインSL[i]が活性化される。このとき、データラインDL[j]には、当該画素回路6に書き込むべきデータ電圧が供給される。スキャンラインSL[i]の活性化により、選択トランジスタT2、駆動トランジスタT1及び閾値補償トランジスタT3を介してデータラインDL[j]を保持ノードNHOLDに接続する経路が形成され、データ電圧が保持キャパシタC1に書き込まれる。このとき、駆動トランジスタT1及び閾値補償トランジスタT3を介して保持キャパシタC1にデータ電圧が書き込まれることにより、データ電圧のみならず駆動トランジスタT1の閾値電圧VTHに依存した電圧が保持キャパシタC1に書き込まれ、これにより、閾値電圧補償が実現される。なお、閾40

値電圧補償を行わない場合には、閾値補償トランジスタT3を設ける必要は無い。

#### 【0050】

データ書き込み動作に続いてOLED素子14の駆動動作が行われる。OLED素子14の駆動動作では、第1エミッショナーラインEM1[i]及び第2エミッショナーラインEM2[i]の両方が活性化される。これにより、電源ライン32から選択トランジスタT5、駆動トランジスタT1、選択トランジスタT6及びOLED素子14を介して接地ライン33に到達する電流バスが形成され、OLED素子14が駆動される。OLED素子14を流れる電流は、駆動トランジスタT1のゲート電位Vgt1、即ち、保持キャパシタC1に保持される電圧に依存するので、結果として、当該画素回路6に書き込まれたデータ電圧に応じた輝度でOLED素子14は発光する。

10

#### 【0051】

以上に説明されているように、本実施形態のOLED表示パネル1では、タッチ検出に用いられる検出キャパシタ15が画素回路6に組み込まれる。このとき、OLED素子14を駆動するために用いられる回路素子及び配線が、タッチ検出のためのセンス電流Isensの生成にも用いられ、これにより、タッチ検出のために画素回路6に追加される回路素子及び配線を低減することができる。

#### 【0052】

上記では、全ての画素回路6が検出キャパシタ15を含むOLED表示パネル1が記述されているが、全ての画素回路6が検出キャパシタ15を含んでいなくてもよい。タッチ検出の感度、分解能その他の要求に対応できるような必要な割合の画素回路6が、検出キャパシタ15を含んでいてもよい。

20

#### 【0053】

図5は、このような構成のOLED表示パネル1Aを含むパネル表示装置10Aの構成を示すブロック図である。図5の構成では、表示領域3に、検出キャパシタ15を含む画素回路6と検出キャパシタ15を含まない画素回路7が、行列に配置されている。図5の構成では、3行3列の画素回路が配置された画素回路アレイが、表示領域3に行列に配置されている。各画素回路アレイにおいて、右下端の画素回路が検出キャパシタ15を含む画素回路6であり、残りが検出キャパシタ15を含まない画素回路7である。即ち、検出キャパシタ15を含む画素回路6は、3行3列の画素回路アレイのうちの下端の行に位置している。

30

#### 【0054】

図6は、検出キャパシタ15を含まない画素回路7の構成の一例を示す回路図である。なお、図6には、i行j列に位置する画素回路7の構成が図示されている。本実施形態では、画素回路7は、いわゆる6T1C型画素回路として構成される。画素回路7は、図3に図示されている画素回路6と類似した構成を有しているが、下記の点で相違している。第1に画素回路7については、選択トランジスタT7、及び、検出キャパシタ15が設けられていない。更に、スキャンラインSL[i-2]、第2エミッショナーラインEM2及びセンスラインSNSは、検出キャパシタ15を含まない画素回路7には接続されない。また、リセットトランジスタT4のゲートは、(スキャンラインSL[i-2]ではなく)スキャンラインSL[i-1]に接続されている。更に、保持キャパシタC1は、電源電圧ELVDDが供給される電源ライン32と保持ノードN<sub>HOLD</sub>との間に接続されている。

40

#### 【0055】

図4に図示されている動作は、このような画素回路7についてもOLED素子14を正しく駆動できるものであることに留意されたい。

#### 【0056】

なお、図6に図示されている画素回路7の構成から理解されるように、画素回路7の配置によっては、図1の構成において表示領域3に配置されているライン(スキャンラインSL、第1エミッショナーラインEM1、第2エミッショナーラインEM2、センスラインSNS)のうち、不必要的ラインは設けられなくてもよい。検出キャパシタ15を含まない

50

画素回路 7 のみが配置されている画素回路の行については、第 2 エミッショナーライン E M 2 が設けられる必要がなく、画素回路 7 のみが配置されている画素回路の列については、センスライン S N S が設けられる必要がない。また、検出キャパシタ 1 5 を含まない画素回路 7 のみが、最上端の画素回路の行に設けられている場合には、スキャンライン S L [ - 1 ] は設けられる必要がない。

#### 【 0 0 5 7 】

図 5 に図示されている O L E D 表示パネル 1 A の構成では、検出キャパシタ 1 5 を含む画素回路 6 が配置されている画素回路の行について第 2 エミッショナーライン E M 2 が設けられ、残りの行については第 2 エミッショナーライン E M 2 が設けられていない。また、更に、検出キャパシタ 1 5 を含む画素回路 6 が配置されている画素回路の列についてセンスライン S N S が設けられ、残りの列についてはセンスライン S N S が設けられていない。更に、スキャンライン S L [ - 1 ] は設けられていない。

#### 【 0 0 5 8 】

上記に説明されているのは、画素回路 6、7 に含まれる駆動トランジスタ T 1、選択トランジスタ T 2、閾値補償トランジスタ T 3、リセットトランジスタ T 4 及び選択トランジスタ T 5、T 6、T 7 が、いずれも、P 型の M O S トランジスタとして構成される実施形態であるが、これらのトランジスタとして、N 型の M O S トランジスタが用いられてもよい。この場合、電源ライン 3 2 が接地される一方で、接地ライン 3 3 の代わりに電源電圧 E L V D D が供給される電源ラインが用いられる。また、O L E D 素子 1 4 は、カソードが選択トランジスタ T 6 のドレインに接続され、アノードが、電源電圧 E L V D D が供給される該電源ラインに接続される。更に、スキャンライン S L [ i - 2 ] ~ [ i ]、第 1 エミッショナーライン E M 1 [ i ] 及び第 2 エミッショナーライン E M 2 [ i ] は、いずれも、ハイアクティブ (high-active) の信号線として動作される。

#### 【 0 0 5 9 】

##### ( 第 2 の実施形態 )

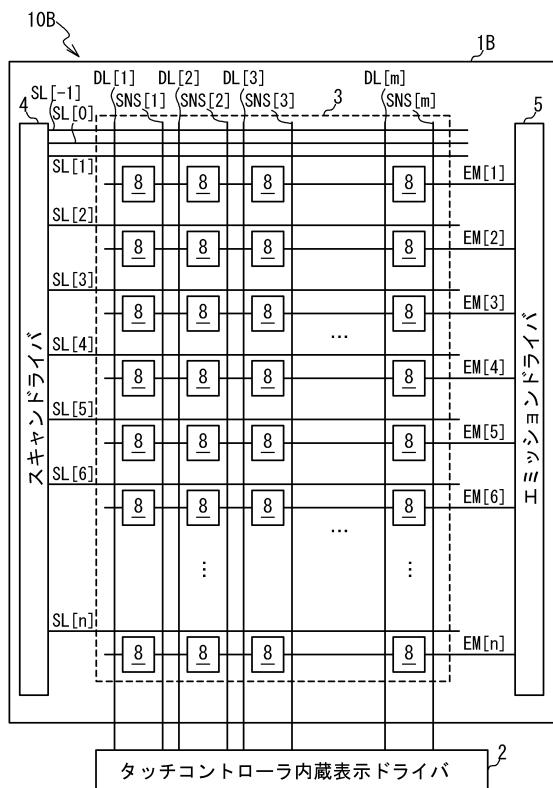

図 7 は、第 2 の実施形態のパネル表示装置 1 0 B の構成を示すブロック図である。パネル表示装置 1 0 B は、O L E D 表示パネル 1 B と、タッチコントローラ内蔵表示ドライバ 2 とを備えている。タッチコントローラ内蔵表示ドライバ 2 は、O L E D 表示パネル 1 B を駆動すると共に、O L E D 表示パネル 1 B についてのタッチ検出を行う機能を有している。

#### 【 0 0 6 0 】

第 2 の実施形態のパネル表示装置 1 0 B は、第 1 の実施形態のパネル表示装置 1 0 と類似した構成を有しているが、下記の点で相違している。第 1 に、第 2 の実施形態のパネル表示装置 1 0 B では、第 1 の実施形態で用いられる画素回路 6、7 と異なる構成の画素回路 8 が O L E D 表示パネル 1 B に配置されている。また、第 1 の実施形態のパネル表示装置 1 0 では、各画素回路 6 に 2 本のエミッショナーライン ( 第 1 エミッショナーライン E M 1 、第 2 エミッショナーライン E M 2 ) が接続されているが、第 2 の実施形態では、各画素回路 8 に 1 本のエミッショナーライン E M が接続されている。エミッションドライバ 5 は、エミッショナーライン E M [ 1 ] ~ E M [ n ] を駆動する。

#### 【 0 0 6 1 】

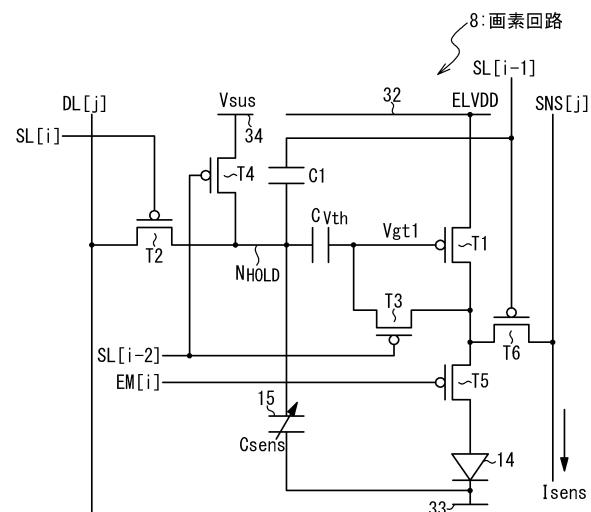

図 8 は、第 2 の実施形態における画素回路 8 の構成を示す回路図である。なお、図 8 は、i 行目、j 列目に位置している画素回路 8 の構成を図示しているが、他の画素回路 8 の構成も、図 8 に図示されている構成と同一である。

#### 【 0 0 6 2 】

第 2 の実施形態では、各画素回路 8 が、上述の O L E D 素子 1 4 、検出キャパシタ 1 5 に加え、駆動トランジスタ T 1 と、選択トランジスタ T 2 と、閾値補償トランジスタ T 3 と、リセットトランジスタ T 4 と、選択トランジスタ T 5 、T 6 と、保持キャパシタ C 1 と、閾値補償キャパシタ C v t h とを備えている。本実施形態では、駆動トランジスタ T 1 と、選択トランジスタ T 2 と、閾値補償トランジスタ T 3 と、リセットトランジスタ T 4 と、選択トランジスタ T 5 、T 6 は、いずれも、P 型の M O S トランジスタとして構成さ

10

20

30

40

50

れる。

#### 【0063】

駆動トランジスタT1は、各画素回路8に書き込まれたデータ電圧に応じた駆動電流を生成し、生成した駆動電流をOLED素子14に供給する。駆動トランジスタT1は、そのソースが電源ライン32に接続され、ゲートが保持ノードN<sub>HOLD</sub>に接続されている。ここで、電源ライン32は、OLED素子14を駆動に用いられる電源電圧E<sub>LVDD</sub>が供給される電源ラインである。

#### 【0064】

選択トランジスタT2は、データ電圧を書き込む画素回路8を選択するために用いられる。選択トランジスタT2は、ソースがデータラインDL[j]に接続され、ドレインが保持ノードN<sub>HOLD</sub>に接続され、ゲートがスキャンラインSL[i]に接続されている。

10

#### 【0065】

閾値補償トランジスタT3は、ソースが駆動トランジスタT1のドレインに接続され、ドレインが駆動トランジスタT1のゲートに接続され、ゲートがスキャンラインSL[i-2]に接続されている。

#### 【0066】

リセットトランジスタT4は、スキャンラインSL[i-2]の電位に応じて保持ノードN<sub>HOLD</sub>と内部電源ライン34とを電気的に接続することで保持キャパシタC1、閾値補償キャパシタC<sub>Vth</sub>及び検出キャパシタ15をリセットするために用いられる。本実施形態では、リセットトランジスタT4は、ソースが内部電源ライン34に接続され、ドレインが保持ノードN<sub>HOLD</sub>に接続され、ゲートがスキャンラインSL[i-2]に接続されている。ここで、内部電源ライン34は、電位V<sub>sus</sub>に固定された電源ラインである。

20

#### 【0067】

選択トランジスタT5は、OLED素子14を発光させる画素回路8を選択するために用いられる。選択トランジスタT5は、ソースが駆動トランジスタT1のドレインに接続され、ドレインがOLED素子14のアノードに接続され、ゲートがエミッഷョンラインEM[i]に接続されている。

#### 【0068】

選択トランジスタT6は、センス電流I<sub>sens</sub>を取得する画素回路8を選択するために用いられる。選択トランジスタT6は、ソースが駆動トランジスタT1のドレインに接続され、ドレインがセンスラインSNS[j]に接続され、ゲートがスキャンラインSL[i-1]に接続されている。

30

#### 【0069】

保持キャパシタC1は、当該画素回路8に対応する階調（即ち、OLED素子14が発光すべき輝度）に対応するデータ電圧を保持する。保持キャパシタC1は、保持ノードN<sub>HOLD</sub>とスキャンラインSL[i-1]との間に接続されている。

#### 【0070】

閾値補償キャパシタC<sub>Vth</sub>は、駆動トランジスタT1の閾値電圧に対応する電圧を保持する。閾値補償キャパシタC<sub>Vth</sub>は、駆動トランジスタT1のゲートと保持ノードN<sub>HOLD</sub>との間に接続されている。

40

#### 【0071】

OLED素子14は、アノードが選択トランジスタT5のドレインに接続され、カソードが接地ライン33に接続されている。ここで、接地ライン33は、接地電位E<sub>LVSS</sub>に固定される電源ラインである。

#### 【0072】

検出キャパシタ15は、上述のように、タッチ検出のためのセンス信号の生成に用いられる。検出キャパシタ15は、保持ノードN<sub>HOLD</sub>と接地ライン33との間に接続されている。

#### 【0073】

図8に図示されている画素回路8は、いわゆる5T2C型画素回路（上記の非特許文献

50

2 参照) に、選択トランジスタ T 6 、検出キャパシタ 15 、及び、センスライン SNS を追加した構成であることに留意されたい。図 8 に図示されている構成では、OLED 素子 14 を駆動するために用いられる回路素子及び配線が、タッチ検出のためのセンス信号の生成にも用いられ、これにより、タッチ検出のために画素回路 8 に追加される回路素子及び配線を低減することができる。

#### 【 0 0 7 4 】

詳細には、まず、OLED 素子 14 にデータ電圧に応じた駆動電流を供給する駆動トランジスタ T 1 が、検出キャパシタ 15 の容量に応じてタッチ検出に用いられるセンス電流 I\_sens を生成する増幅トランジスタとしても用いられる。

#### 【 0 0 7 5 】

また、保持キャパシタ C 1 及び閾値補償キャパシタ C\_Vth をリセットするために用いられるリセットトランジスタ T 4 が、検出キャパシタ 15 をリセットするためにも用いられる。詳細には、図 8 に図示されている画素回路 8 では、保持ノード N\_HOLD に保持キャパシタ C 1 の一端と閾値補償キャパシタ C\_Vth の一端と検出キャパシタ 15 の一端が接続されており、且つ、リセットトランジスタ T 4 が、保持ノード N\_HOLD と内部電源ライン 34 とをスキャンライン SL [ i - 2 ] の電位に応じて電気的に接続する。このような構成によれば、一つのリセットトランジスタ T 4 によって、保持キャパシタ C 1 及び閾値補償キャパシタ C\_Vth のみならず、検出キャパシタ 15 をリセットできる。

#### 【 0 0 7 6 】

更に、保持キャパシタ C 1 が、センス電流 I\_sens の生成においてリファレンスキャパシタとして使用される。

#### 【 0 0 7 7 】

このように、本実施形態の画素回路 8 の構成によれば、回路素子を OLED 素子 14 の駆動とタッチ検出に用いられるセンス電流 I\_sens の生成に兼用することで、タッチ検出のために追加される回路素子及び配線を低減することができる。

#### 【 0 0 7 8 】

なお、閾値補償を行わないのであれば、閾値補償トランジスタ T 3 及び閾値補償キャパシタ C\_Vth は設けられる必要はない。この場合、駆動トランジスタ T 1 のゲートは、直接、保持ノード N\_HOLD に接続される。

#### 【 0 0 7 9 】

図 9 は、図 8 に図示されている画素回路 8 ( i 行 j 列に位置する画素回路 8 ) の動作を示すタイミングチャートである。なお、本実施形態では、スキャンライン SL [ i - 2 ] ~ [ i ] 及びエミッションライン EM [ i ] は、いずれも、ローアクティブ ( low-active ) である。初期状態において、スキャンライン SL [ i - 2 ] 、 SL [ i - 1 ] 、 SL [ i ] は、いずれも、非活性化され ( deactivated ) 、エミッションライン EM [ i ] は、活性化されている ( activated ) ものとする。

#### 【 0 0 8 0 】

図 9 に図示されている画素回路 8 の動作は、リセット動作、閾値補償動作、タッチ検出動作、データ書き込み動作、及び、OLED 素子 14 の駆動動作を含んでいる。

#### 【 0 0 8 1 】

リセット動作では、スキャンライン SL [ i - 2 ] が活性化される。ここで、スキャンライン SL [ i - 2 ] は、 i - 2 行目の画素回路 6 にデータ電圧を書き込む際に活性化されるスキャンラインであることに留意されたい。これにより、リセットトランジスタ T 4 がオンされ、保持ノード N\_HOLD の電位が、電位 V\_sus にリセットされる。このとき、閾値補償キャパシタ C\_Vth を介して保持ノード N\_HOLD に接続されている駆動トランジスタ T 1 のゲート電位 V\_gt1 も、保持ノード N\_HOLD の電位の変動に応じて変動する。電位 V\_sus は、各画素回路 8 にデータ書き込みが許容されるデータ電圧よりも低く、駆動トランジスタ T 1 のゲート電位 V\_gt1 が低下して駆動トランジスタ T 1 はオン状態になる。

#### 【 0 0 8 2 】

10

20

30

40

50

リセット動作に続いて、閾値補償動作が行われる。閾値補償動作では、スキャンライン S L [ i - 2 ] が活性化された状態のまま、エミッションライン E M [ i ] が非活性化される。エミッションライン E M [ i ] が非活性化された瞬間は、駆動トランジスタ T 1 はオン状態であり、且つ、閾値補償トランジスタ T 3 もオン状態であるので、駆動トランジスタ T 1 のゲートが、電源電圧 E L V D D が供給されている電源ライン 3 2 に電気的に接続され、駆動トランジスタ T 1 のゲートの電位が上昇する。このとき、駆動トランジスタ T 1 のゲートの電位が電源電圧 E L V D D よりも駆動トランジスタ T 1 の閾値電圧の絶対値だけ低い電位まで上昇すると駆動トランジスタ T 1 はオフされる。この結果、閾値補償キャパシタ C v t h には、駆動トランジスタ T 1 の閾値電圧に対応した電圧が保持される。

## 【0083】

10

閾値補償動作に続いてタッチ検出動作が行われる。タッチ検出動作では、スキャンライン S L [ i - 2 ] が非活性化されると共にスキャンライン S L [ i - 1 ] が活性化される。上述のように、スキャンライン S L [ i - 1 ] はローアクティブであり、且つ、保持ノード N H O L D は、保持キャパシタ C 1 を介してスキャンライン S L [ i - 1 ] に接続されているから、保持ノード N H O L D の電位は、スキャンライン S L [ i - 1 ] のプルダウンによって低下する。この結果、駆動トランジスタ T 1 のゲートは、閾値補償キャパシタ C v t h を介して保持ノード N H O L D に接続されているから、駆動トランジスタ T 1 のゲート電位 V g t 1 もスキャンライン S L [ i - 1 ] のプルダウンによって低下する。

## 【0084】

20

ここで、スキャンライン S L [ i - 1 ] が活性化されたときの駆動トランジスタ T 1 のゲート電位 V g t 1 の変化量 d V s e n s は、検出キャパシタ 1 5 の容量 C s e n s に依存している。第 1 の実施形態と同様に、駆動トランジスタ T 1 のゲート電位 V g t 1 の変化量 d V s e n s は、下記式(2)で表される：

## 【数2】

$$dV_{sens} = \frac{dV_{scan} \times C1}{(Csens + C1)} \cdots (2)$$

30

ここで、d V s c a n は、スキャンライン S L [ i - 1 ] が活性化されたときのスキャンライン S L [ i - 1 ] の電位の変化量である。スキャンライン S L [ i - 1 ] が活性化されたときの駆動トランジスタ T 1 のゲート電位 V g t 1 は、検出キャパシタ 1 5 の容量 C s e n s に依存することになる。

## 【0085】

40

第 1 の実施形態において説明したように、検出キャパシタ 1 5 の容量 C s e n s は、当該画素回路 8 の近傍における O L E D 表示パネル 1 B への物体、例えば、人体の指の接触の有無に依存するから、結果として、駆動トランジスタ T 1 のゲート電位 V g t 1 は、O L E D 表示パネル 1 B への物体の接触の有無に依存することになる。当該画素回路 6 の近傍において O L E D 表示パネル 1 B に物体が接触していると、検出キャパシタ 1 5 の容量 C s e n s が増加する。検出キャパシタ 1 5 の容量 C s e n s が増加し、図 9 の凡例「タッチあり」に示されているように、ゲート電位 V g t 1 の変化 d V s e n s が相対的に小さくなる。逆に、当該画素回路 6 の近傍において O L E D 表示パネル 1 B に物体が接触していない場合には、検出キャパシタ 1 5 の容量 C s e n s が減少し、図 9 の凡例「タッチなし」に示されているように、ゲート電位 V g t 1 の変化 d V s e n s が相対的に大きくなる。

50

**【 0 0 8 6 】**

加えて、スキャンラインSL [ i - 1 ] の活性化に応答して選択トランジスタT6がオン状態になるので、電源ライン32から駆動トランジスタT1及び選択トランジスタT6を介してセンスラインSNS [ j ] にセンス電流I<sub>sens</sub>を流す電流パスが形成される。センス電流I<sub>sens</sub>は、駆動トランジスタT1のゲート電位V<sub>gt1</sub>に依存しているので、画素回路8から得られるセンス電流I<sub>sens</sub>は、当該画素回路8の近傍におけるOLED表示パネル1Bへの物体、例えば、人体の指の接触の有無に依存することになる。よって、タッチコントローラ内蔵表示ドライバ2によってセンス電流I<sub>sens</sub>を検出することで、各画素回路8の近傍におけるOLED表示パネル1Bへの物体の接触の有無を検出することができる。

10

**【 0 0 8 7 】**

第1の実施形態と同様に、検出キャパシタ15の容量C<sub>sens</sub>は、検出キャパシタ15に作用する圧力に依存するので、センス電流I<sub>sens</sub>を検出することにより、物体がOLED表示パネル1Bに接触する圧力を検出することも可能である。物体がOLED表示パネル1Bに接触する圧力が増大すると、検出キャパシタ15の絶縁層15bの厚みが薄くなり、検出キャパシタ15の容量C<sub>sens</sub>が増加する。上記から理解されるように、センス電流I<sub>sens</sub>は、検出キャパシタ15の容量C<sub>sens</sub>に応じた電流レベルを有しているので、センス電流I<sub>sens</sub>を検出することで、物体がOLED表示パネル1Bに接触する圧力を検出することができる。

20

**【 0 0 8 8 】**

単にOLED表示パネル1Bへの物体の接触の有無を検出するか、加えて物体がOLED表示パネル1Bに接触する圧力を検出するかは、本実施形態のOLED表示パネル1の応用に応じて決めてよい。

**【 0 0 8 9 】**

なお、第2の実施形態におけるOLED表示パネル1Bでは、タッチ検出動作の前に閾値補償動作が行われるため、タッチ検出動作において、駆動トランジスタT1の閾値電圧の変動の影響が小さくできることに留意されたい。

**【 0 0 9 0 】**

タッチ検出動作に続いてデータ書き込み動作が行われる。データ書き込み動作では、スキャンラインSL [ i - 1 ] が非活性化されると共にスキャンラインSL [ i ] が活性化される。このとき、データラインDL [ j ] には、当該画素回路8に書き込むべきデータ電圧が供給される。スキャンラインSL [ i ] の活性化により、選択トランジスタT2を介してデータラインDL [ j ] を保持ノードN<sub>HOLD</sub>に接続する経路が形成され、データ電圧が保持キャパシタC1に書き込まれる。

30

**【 0 0 9 1 】**

データ書き込み動作に続いてOLED素子14の駆動動作が行われる。OLED素子14の駆動動作では、エミッショナーラインEM [ i ] が活性化される。これにより、電源ライン32から駆動トランジスタT1、選択トランジスタT5及びOLED素子14を介して接地ライン33に到達する電流パスが形成され、OLED素子14が駆動される。OLED素子14を流れる電流は、駆動トランジスタT1のゲート電位V<sub>gt1</sub>に依存し、駆動トランジスタT1のゲート電位V<sub>gt1</sub>は、保持キャパシタC1及び閾値補償キャパシタC<sub>Vth</sub>に保持される電圧に依存するので、結果として、当該画素回路8に書き込まれたデータ電圧に応じた輝度でOLED素子14は発光する。

40

**【 0 0 9 2 】**

以上に説明されているように、本実施形態のOLED表示パネル1Bでは、タッチ検出に用いられる検出キャパシタ15が画素回路8に組み込まれる。このとき、OLED素子14を駆動するために用いられる回路素子及び配線が、タッチ検出のためのセンス電流I<sub>sens</sub>の生成にも用いられ、これにより、タッチ検出のために画素回路8に追加される回路素子及び配線を低減することができる。

**【 0 0 9 3 】**

50

上記では、全ての画素回路 8 が検出キャパシタ 15 を含む O L E D 表示パネル 1 B が記述されているが、全ての画素回路 8 が検出キャパシタ 15 を含んでいなくてもよい。タッチ検出の感度、分解能その他の要求に対応できるような必要な割合の画素回路 8 が、検出キャパシタ 15 を含んでいてもよい。

#### 【 0 0 9 4 】

図 10 は、このような構成の O L E D 表示パネル 1 C を含むパネル表示装置 10 C の構成を示すブロック図である。図 10 の構成では、表示領域 3 に、検出キャパシタ 15 を含む画素回路 8 と検出キャパシタ 15 を含まない画素回路 9 が、行列に配置されている。図 10 の構成では、3 行 3 列の画素回路が配置された画素回路アレイが、表示領域 3 に行列に配置されている。各画素回路アレイにおいて、右下端の画素回路が検出キャパシタ 15 を含む画素回路 8 であり、残りが検出キャパシタ 15 を含まない画素回路 9 である。即ち、検出キャパシタ 15 を含む画素回路 8 は、3 行 3 列の画素回路アレイのうちの下端の行に位置している。10

#### 【 0 0 9 5 】

図 11 は、検出キャパシタ 15 を含まない画素回路 9 の構成の一例を示す回路図である。図 11 には、 $i$  行  $j$  列に位置する画素回路 9 の構成が図示されている。本実施形態では、画素回路 9 は、いわゆる 5 T 2 C 型画素回路として構成される。画素回路 9 は、図 8 に図示されている画素回路 8 と類似した構成を有しているが、下記の点で相違している。第 1 に、画素回路 9 については、選択トランジスタ T 6 、及び、検出キャパシタ 15 が設けられていない。更に、スキャンライン S L [  $i - 2$  ] 及びセンスライン S N S は、検出キャパシタ 15 を含まない画素回路 9 には接続されない。また、リセットトランジスタ T 4 のゲートは、(スキャンライン S L [  $i - 2$  ] ではなく) スキャンライン S L [  $i - 1$  ] に接続されている。更に、保持キャパシタ C 1 は、電源電圧 E L V D D が供給される電源ライン 3 2 と保持ノード N H O L D との間に接続されている。20

#### 【 0 0 9 6 】

図 9 に図示されている動作は、このような画素回路 9 についても O L E D 素子 1 4 を正しく駆動できるものであることに留意されたい。

#### 【 0 0 9 7 】

なお、図 11 に図示されている画素回路 9 の構成から理解されるように、画素回路 9 の配置によっては、図 7 の構成において表示領域 3 に配置されているライン(スキャンライン S L 、エミッഷョンライン E M 、センスライン S N S )のうち、不必要的ラインは設けられなくてもよい。検出キャパシタ 15 を含まない画素回路 9 のみが配置されている画素回路の列については、センスライン S N S が設けられる必要がない。また、検出キャパシタ 15 を含まない画素回路 9 のみが、最上端の画素回路の行に設けられている場合には、スキャンライン S L [ - 1 ] は設けられる必要がない。図 10 に図示されている O L E D 表示パネル 1 C の構成では、検出キャパシタ 15 を含む画素回路 8 が配置されている画素回路の列についてセンスライン S N S が設けられ、残りの列についてはセンスライン S N S が設けられていない。更に、スキャンライン S L [ - 1 ] は設けられていない。30

#### 【 0 0 9 8 】

上記に説明されているのは、画素回路 8 、 9 に含まれる駆動トランジスタ T 1 、選択トランジスタ T 2 、閾値補償トランジスタ T 3 、リセットトランジスタ T 4 及び選択トランジスタ T 5 、 T 6 が、いずれも、P 型の M O S ドレインとして構成される実施形態であるが、これらのトランジスタとして、N 型の M O S ドレインが用いられてもよい。この場合、電源ライン 3 2 が接地される一方で、接地ライン 3 3 の代わりに電源電圧 E L V D D が供給される電源ラインが用いられる。また、O L E D 素子 1 4 は、カソードが選択トランジスタ T 6 のドレインに接続され、アノードが、電源電圧 E L V D D が供給される該電源ラインに接続される。更に、スキャンライン S L [  $i - 2$  ] ~ [  $i$  ] 、エミッഷョンライン E M [  $i$  ] は、いずれも、ハイアクティブ( high-active )の信号線として動作される。40

#### 【 0 0 9 9 】

10

20

30

40

50

以上には、本発明の実施形態が具体的に記述されているが、本発明は、上記の実施形態に限定されない。本発明が種々の変更と共に実施され得ることは、当業者には理解されよう。

### 【0100】

例えば、上記では、OLED素子14が各画素回路(6～9)に集積化されたOLED表示パネル1の実施形態が記述されているが、本発明は、他の電流駆動素子(例えば、無機材料で形成されたLED素子)がOLED素子14の代わりに各画素回路(6～9)に集積化された電流駆動表示パネルにも適用可能である。

### 【符号の説明】

#### 【0101】

- 1、1A、1B、1C：OLED表示パネル

- 2 : タッチコントローラ内蔵表示ドライバ

- 3 : 表示領域

- 4 : スキャンドライバ

- 5 : エミッションドライバ

- 6、7、8、9 : 画素回路

- 10、10A、10B、10C : パネル表示装置

- 11 : 下側ガラス基板

- 12 : 上側ガラス基板

- 13 : 回路形成層

- 14 : OLED素子

- 14a : アノード

- 14b : 発光層

- 14c : カソード

- 15 : 検出キャパシタ

- 15a : 下部電極

- 15b : 絶縁層

- 15c : 上部電極

- 16 : パッシベーション層

- 17 : スペーサ

- 18 : 指

- 31 : 内部電源ライン

- 32 : 電源ライン

- 33 : 接地ライン

- 34 : 内部電源ライン

- C1 : 保持キャパシタ

- $C_{Vth}$  : 閾値補償キャパシタ

- D<sub>L</sub> : データライン

- E<sub>M</sub>、E<sub>M1</sub>、E<sub>M2</sub> : エミッショナーライン

- S<sub>L</sub> : スキャンライン

- S<sub>N</sub>S : センスライン

- T<sub>1</sub> : 駆動トランジスタ

- T<sub>2</sub> : 選択トランジスタ

- T<sub>3</sub> : 閾値補償トランジスタ

- T<sub>4</sub> : リセットトランジスタ

- T<sub>5</sub>、T<sub>6</sub>、T<sub>7</sub> : 選択トランジスタ

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9】

【図 10】

【図 11】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

**G 0 6 F** 3/044(2006.01)

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 F | 9/30  | 3 3 8   |

| G 0 9 F | 9/30  | 3 4 9 Z |

| G 0 9 F | 9/00  | 3 6 6 A |

| G 0 6 F | 3/041 | 4 1 2   |

| G 0 6 F | 3/044 | 1 4 0   |

| G 0 6 F | 3/041 | 5 1 2   |

## (56)参考文献

米国特許出願公開第 2 0 1 5 / 0 0 0 2 4 1 4 ( U S , A 1 )

特開 2 0 1 1 - 0 0 8 7 7 5 ( J P , A )

特開 2 0 1 0 - 0 8 5 5 2 6 ( J P , A )

特開 2 0 1 1 - 0 8 5 6 8 0 ( J P , A )

中国特許出願公開第 1 0 3 3 5 4 0 7 9 ( C N , A )

特表 2 0 1 6 - 5 3 1 3 2 2 ( J P , A )

## (58)調査した分野

(Int.Cl. , D B 名)

|         |             |

|---------|-------------|

| G 0 9 G | 3 / 3 2 2 5 |

| G 0 9 G | 3 / 2 0     |

| G 0 9 F | 9 / 3 0     |

| G 0 9 F | 9 / 0 0     |

| G 0 6 F | 3 / 0 4 1   |

| G 0 6 F | 3 / 0 4 4   |