(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

20 May 2010 (20.05.2010)(10) International Publication Number

**WO 2010/056118 A1****(51) International Patent Classification:***G06F 1/32 (2006.01)***(21) International Application Number:**

PCT/NL2009/050682

**(22) International Filing Date:**

12 November 2009 (12.1 1.2009)

**(25) Filing Language:**

English

**(26) Publication Language:**

English

**(30) Priority Data:**

61/133,916 12 November 2008 (12.1 1.2008) US

**(71) Applicant** (for all designated States except US): AN-AGEAR B.V. [NIVNL]; Sluiskeshoeven 10, NL-5244 GM Rosmalen (NL).**(72) Inventor; and****(75) Inventor/Applicant** (for US only): KAMP, Petrus, Jor-hannes, Maria [NL/NL]; Sluiskeshoeven 10, NL-5244 GM Rosmalen (NL).**(74) Agents:** ALGEMEEN OCTROOI- EN MERKEN BUREAU BV et al; Postbus 645, NL-5600 AP Eindhoven (NL).**(81) Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

**(84) Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).**Published:**

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

**(54) Title:** POWER SUPPLY MANAGEMENT CONTROLLER INTEGRATED CIRCUIT, POWER MANAGEMENT CIRCUIT FOR ELECTRICALLY POWERED SYSTEMS, AND METHOD OF MANAGING POWER TO SUCH SYSTEMS**(57) Abstract:** The present invention provides a power supply management controller integrated circuit for managing power supply to one or more system units of a system, said integrated circuit comprising power supply means for powering said system units, a power supply control unit for controlling said powering of said system units, a wake-up timer unit, and means for acknowledging an active or passive state of said system, wherein said power supply control unit is arranged for cooperating with said means for acknowledging said state of said system for enabling said power supply control unit to cease powering of said system units for de-activation of said system during said passive state of said system, and for enabling said power supply control unit to maintain powering of said system units during an active state of said system, and wherein said power supply control unit is arranged for cooperating with said wake-up timer unit for periodically powering said system units during said passive state of said system for enabling activation of said system.

Title:

Power supply management controller integrated circuit, power management circuit for electrically powered systems, and method of managing power to such systems

5

Field of the invention

The present invention is directed to a power supply management controller integrated circuit for managing power supply to one or more system units of a system, a power management circuit for electrically powered systems using such an integrated circuit, and to a method of managing power supply to such a system.

10

Background of the invention

With the continuing shrink of silicon device sizes, the processing speed of digital signal processors and micro controllers keeps on growing. However the current consumption is rising too. In many electronic systems high processing speed is only needed during short periods of operation. The rest of the time such systems are in a sleep mode or standby mode at a very low activity level. However the systems cannot be fully shut off as they must be able to resume full operation in a very short period of time. In particular as a result of high leakage currents typical for silicon devices there is still significant supply current being drawn by the systems in sleep mode or standby mode. It will be appreciated that this is not desired from the point of view of energy conservation. Moreover, due to this inefficient use of available energy, many of these type of applications must be powered by mains voltage or a by a durable, large capacity power source that enables operation over a sufficiently long period of time. Battery operation is often not possible, or results in the application being large and bulky, and as therefore difficult to handle or install.

15

20

25

Summary of the invention

The present invention is directed to resolving the above mentioned problem, and providing a power management controller which is small, fast, reliable and accurate.

30

To this end, the present invention provides a power supply management controller integrated circuit for managing power supply to one or more system units of a system, said integrated circuit comprising power supply means for

powering said system units, a power supply control unit for controlling said powering of said system units, a wake-up timer unit, and means for acknowledging an active or passive state of said system, wherein said power supply control unit is arranged for cooperating with said means for acknowledging said state of said system for enabling said power supply control unit to cease powering of said system units for de-activation of said system during said passive state of said system, and for enabling said power supply control unit to maintain powering of said system units during an active state of said system, and wherein said power supply control unit is arranged for cooperating with said wake-up timer unit for periodically powering said system units during said passive state of said system for enabling activation of said system.

The integrated circuit of the present invention enables complete shut down of the one or more system units in the system, or the complete system as a whole (dependent on the application).

The integrated circuit takes over all critical system functions when the system is in the de-activated state, and is able to wake-up the full system in a fast and time accurate way. This allows the use of fast signal processors in battery operated equipment or in equipment operated from an unreliable energy source.

In particular, since the integrated circuit of the present invention periodically powers the system units during the de-activated state of the system, power supply management controller integrated circuit of the present invention makes it possible for the system to wake-up as soon as activation of the system is required for processing data or other functions.

The means for acknowledging an active or passive state of the system may be integrated in the power supply control unit of the integrated circuit. In particular, the power supply control unit may be able to detect the active or passive state of the system based on voltage difference, amount of current being drawn, or the temperature of the system units being monitored. Moreover, the means for acknowledging an active or passive state of said system may be connected to a sensor signal input for receiving sensor signals from a sensor unit. Such a sensor unit may for example be at least one element of a group comprising an internal sensor unit of said integrated circuit, a micro-electro-mechanical systems (MEMS) based sensor such as a pressure sensor implemented on said integrated circuit, an external sensor unit, a voltage level sensor, a current sensor or a temperature

sensor. It should be appreciated, however, that other types of sensor units may be used as well, e.g. dependent on the application.

The terms 'active', 'passive', 'de-activated' and 'activated' are to be interpreted as follows. The active or passive state of the system refers to the presence or absence of a requirement for the system to perform its functions, i.e. data processing, interaction between system units or performing specific tasks of the system. A passive state thus refers to a state wherein the system is activated, but without performing any required activity (e.g. a wait-state or idle state). De-activation or activation refers to the power supply management controller integrated circuit switching off power to the system units under control, and taking over the system critical functions (e.g. providing a clock signal). In this respect, activation and wake-up both refer to the system being powered on by the integrated circuit of the invention, after a period of de-activation. De-activation turns the system to a de-activated or standby mode by cutting off power to the system units under control, and taking over critical system functions by the integrated circuit.

According to another embodiment of the invention, said integrated circuit further comprises a clock unit for providing a clock signal for said wake-up timer unit. A clock unit enables accurate operation of the wake-up timer, and makes the integrated circuit self-supporting in that it does not have to rely on an external clock circuit. Moreover, the accurate clock unit of this embodiment provides a clock signal that can be used by external units, such as system units that rely on an accurate clock signal even during a de-activated state of the system.

The clock unit may be operatively connected to an oscillator unit. Such an oscillator unit may comprise any of a group comprising a crystal oscillator or a controlled oscillator. In case a controlled oscillator is present in the clock unit, this oscillator comprises tuning means arranged for periodically tuning said controlled oscillator according to a duty cycle, and wherein said tuning means are arranged for adapting said duty cycle dependent on a tuning signal which is indicative of an environmental parameter. Accurate tuning of the oscillator may be achieved by means of a suitable combination of a phase locked loop, a delay locked loop, and/or a frequency locked loop in a manner known to the skilled person.

A special feature of this embodiment is that tuning is performed periodically according to a variable duty cycle. The tuning cycle is made dependent

on parameters that may influence the oscillation frequency. Such parameters include, amongst others, the temperature of the oscillator or the rate of change of this temperature. The present embodiment is designed to perform tuning more intensively (by amending the duty cycle within which tuning is performed) or less intensively 5 dependent on the need for tuning.

As mentioned, the clock unit may comprise a crystal oscillator. In particular, this may be a low power high frequency oscillator with the following characteristics: very low current consumption, fast start-up time, programmable power modes. The high frequency oscillator may provide a clean reference clock to 10 system units, such as radio devices and/or high speed data converters in a system.

The start-up time of a crystal oscillator is generally interpreted as the duration of time required for the oscillator circuit to generate a stable and desired oscillation signal from the time of power-on. In a preferred embodiment, the fast start-up time and programmable power modes are based on precision control of the 15 amplitude of oscillation. In this embodiment, a low-power mode of the crystal oscillator is achieved by reducing the oscillation amplitude to a low level, while in high-power mode the amplitude is increased for providing a strong clock reference signal. Transition from the low-power mode to the high-power mode can be performed relatively fast. This principle is used for providing the short start-up time and fast start-up. In this embodiment, start-up is thus performed by switching the 20 oscillator from a low-power to a high-power mode, instead of switching the oscillator from no power to power-on. Moreover, since the low-power and high-power levels are programmable (the amplitude is programmable), the start-up time can be influenced by selecting/optimizing suitable power levels.

According to another embodiment of the invention, integrated circuit 25 may comprise a transducer interface for enabling said integrated circuit to be operatively connected to an (external) transducer. This enables connection of transducers to monitor specific system parameters which cannot be monitored with the on-chip provided transducers (e.g. gas or pressure). Such parameters may be 30 indicative for a need to 'wake-up' the system from a de-activated state as facilitated by the power supply management controller integrated circuit of the present invention. In relation to this, it is noted that apart from periodic powering of the one or more system units during said de-activated state of said system for enabling

activation of said system, the power supply control unit may be arranged to wake-up the system on detection of a voltage level or temperature within the system which exceeds or drops below a certain preprogrammed threshold. In that case, in order to control such a parameter, the system may require to take action immediately (e.g. by regulating a voltage, switching on a ventilation unit or other cooling means, or the like).

According to another embodiment, said integrated circuit comprises a communication interface for reading or writing data to said integrated circuit. The integrated circuit may be arranged for programming of operation parameters of said circuit, using the communication interface. The communication interface may comprise a serial or parallel digital input or output, for writing or reading said data. Communication may of course also take place in a different suitable way.

The term power supply means, as used herein, should be interpreted to include a power supply input, such as an input voltage connector, which enables the integrated circuit to be connected to an external power source, such as a battery, mains voltage adapter or transformer unit, an alternative suitable AC or DC power source, or an energy harvesting device (i.e. for deriving energy from external sources, such as solar power, thermal energy, wind energy, salinity gradients, and kinetic energy). Integrated circuit according to any of the previous claims, wherein said power supply means comprise an input voltage connector for receiving power from an external power source.

According to a second aspect of the invention, there is provided a power supply management circuit comprising an integrated circuit as described above.

According to a third aspect of the invention, there is provided a method of managing power supply to one or more system units of a system, wherein said system units are powered by power supply means, and wherein said powering of said units is controlled by a power supply control unit, said method comprising a step of: acknowledging an active or passive state of said system; said power supply control unit managing said supply by ceasing powering of said system units for deactivation of said system during said passive state of said system, and maintaining powering of said system units during an active state of said system, and said power supply control unit periodically powering said system units during said passive state

of said system for enabling activation of said system.

Brief description of the drawings

The present invention will be further elucidated through description

5 of an embodiment thereof, with reference to the enclosed drawing, wherein:

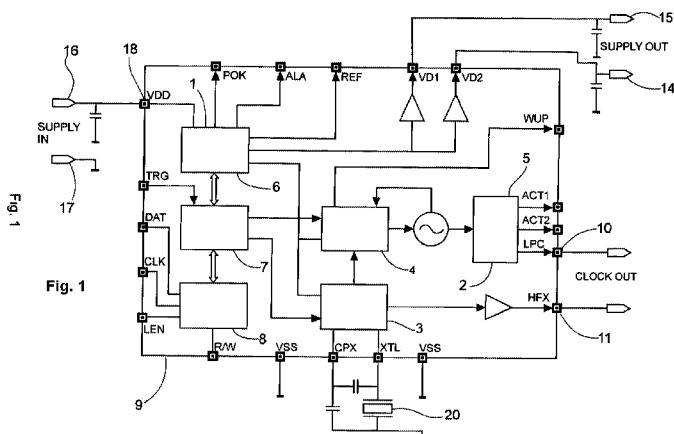

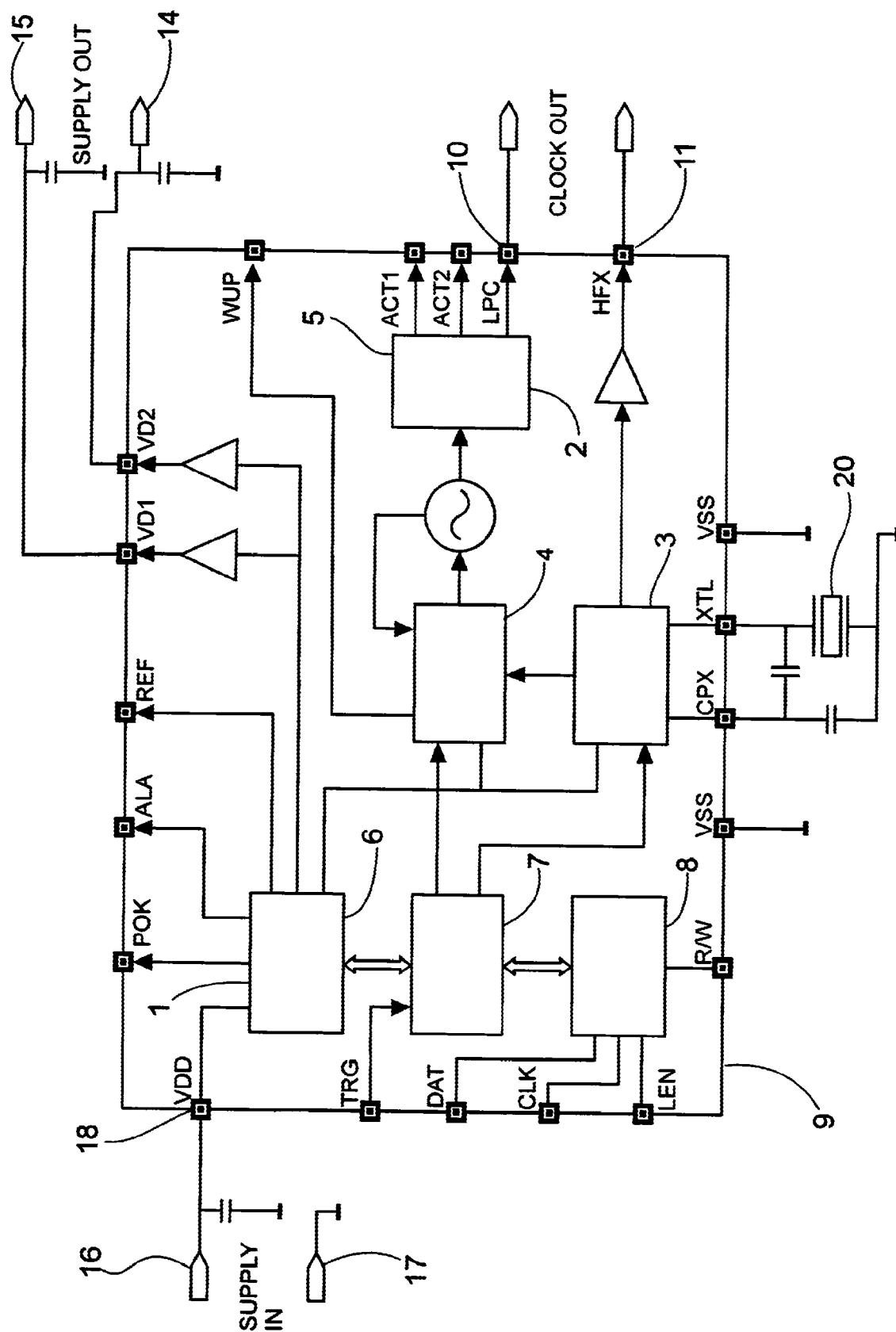

fig. 1 is a schematic layout of an integrated circuit according to an

embodiment of the present invention.

Detailed description of the drawing

10 The invention is directed to a largely analog integrated device (also referred to as power supply management controller integrated circuit) that enables complete shut down of other devices in a system (e.g. devices characterized by high leakage current). The integrated circuit takes over all critical system functions in standby or de-activated mode and is able to wake-up the full system in a fast and

15 time accurate way. This will allow the use of fast signal processors in battery operated equipment or in equipment operated from an unreliable energy source.

20 The key function of the Integrated circuit is to be the system reference for supply (voltage) and time (clock signals) as well as being a monitor of the system's operating conditions. The integrated circuit has ultra low current consumption and therefore never has to be switched off in practice. The integrated circuit has one or more of the functions listed below. How the functions interact is shown in the block diagram.

25 Figure 1 illustrates the layout of an integrated circuit 9 in accordance with an embodiment of the present invention. In figure 1, the integrated circuit 9 comprises a power supply voltage regulator or power supply control unit 1, a real time clock 2, a high frequency oscillator 3, a controlled oscillator 4, programmable timers 5 (in this embodiment integrated with real time clock 2), temperature and/or voltage monitors 6 (in this embodiment integrated with the power supply control unit 1), a transducer interface 7, and serial digital interface 8.

30 Power supply control unit 1, comprising one or more voltage regulators, creates the supply voltage for other system parts. This supply voltage is provided through outputs VD1 and VD2 of the integrated circuit, being connected to output terminals 14 and 15 in figure 1. The regulators in the control unit 1 can be

shut-off and their output can be disabled to fully shut down connected system parts. A power-on reset circuit is part of the power management system and produces a logic signal (pok) when the supply voltage has reached a predefined and stable level. Although any suitable power source may be applied, in the present embodiment, the integrated circuit 9 receives its power via supply voltage inputs 16 and 17, through input 18 (VDD) of the integrated circuit 9.

The real time clock 2 can either be based on a crystal oscillator 3 or a Controlled Oscillator (CO) 4, or both. High frequency oscillator 3 comprises a crystal based oscillator with the following special characteristics: very low current consumption, fast start-up, programmable power modes. The high frequency oscillator provides a clean reference clock to, for example radio devices (not shown) and/or high speed data converters (not shown) in the system. This (reference) clock signal is provided to the system units via outputs 10 and 11 (CLOCK out) of the integrated circuit.

The fast start-up time and programmable power modes are based on precision control of the amplitude of oscillation. A low-power mode of the crystal oscillator is achieved by reducing the oscillation amplitude to a low level, while in high-power mode the amplitude is increased for providing a strong clock reference signal. Transition from the low-power mode to the high-power mode can be performed relatively fast. This principle is used for providing the short start-up time and fast start-up. In this embodiment, start-up is thus performed by switching the oscillator 3 from a low-power to a high-power mode.

Controlled oscillator 4 is a low frequency oscillator which is periodically tuned by a low power but high frequency crystal oscillator 3. Under duty cycle control. The tuning is performed using a combination of a Phase Locked Loop (PLL), a Frequency Locked Loop (FLL) and a Delay Locked Loop (DLL). The tuning is performed according to a duty cycle. The controlled oscillator uses adaptive duty cycle control for the timing of the tuning of the oscillator. The duty cycle depends on the rate of change of environmental factors, such as temperature.

Programmable timers 5 are used to wake-up system parts at a pre-programmed time. The timers are controlled based on the clock signal provided by the clock unit 2. A wake-up timer unit causes providing a trigger signal to the power supply control unit at the end of a count-down cycle for temporarily powering the

system units, such as to enable the system to be activated if required. If the system is required to activate from a de-activated state, this may either be detected within the power supply control unit 1, or alternatively the system may provide an indication signal to the integrated circuit.

5 One of the timers 5 is a watchdog counter which resets the system if it has detected that the system has unintentionally entered a locked-up mode. The watchdog counter is a digitally implemented pulse counter which is preset and counts down to zero. When the zero count is reached a logic signal is generated which can be used to reset or restart (part of) the system. The counter is periodically preset by 10 the system to prevent that the zero count will be reached during normal operation. If zero count is reached then this means that normal system operation is not possible anymore (e.g. due to a software bug or other system failure) an a reset is necessary.

15 The temperature and voltage monitors 6 are monitor circuits that create trigger signals (e.g. wake up signals) to other parts of the system in case certain pre-programmed thresholds have been exceeded.

The transducer interface 7 allows the connection of transducers to the integrated circuit for monitoring specific system parameters which cannot be monitored with the on-chip provided transducers (e.g. gas or pressure).

20 Serial digital interface enables communication with the integrated circuit during normal system operation. It can be used to write settings to or read parameters form the device. It can also be used to provide programming data to the integrated circuit for programming its operational parameters.

## CLAIMS

1. Power supply management controller integrated circuit for managing power supply to one or more system units of a system, said integrated circuit comprising power supply means for powering said system units, a power supply control unit for controlling said powering of said system units, a wake-up timer unit, and means for acknowledging an active or passive state of said system,

5 wherein said power supply control unit is arranged for cooperating with said means for acknowledging said state of said system for enabling said power supply control unit to cease powering of said system units for de-activation of said system during said passive state of said system, and for enabling said power supply control unit to maintain powering of said system units during an active state of said system, and

10 15 wherein said power supply control unit is arranged for cooperating with said wake-up timer unit for periodically powering said system units during said passive state of said system for enabling activation of said system.

2. Integrated circuit according to claim 1, wherein said means for acknowledging said state of said system are comprised by or integrated within said power supply control unit.

20 3. Integrated circuit according to claim 2, wherein for acknowledging said state of said system, said power supply control unit is arranged for detecting current or current variations of a supply current provided to said system units.

4. Integrated circuit according to any of the previous claims, wherein 25 said means for acknowledging an active or passive state of said system are connected to an sensor signal input for receiving sensor signals from a sensor unit.

5. Integrated circuit according to claim 4, wherein said sensor unit comprises at least one element of a group comprising an internal sensor unit of said integrated circuit, a micro-electro-mechanical systems (MEMS) based sensor such as a pressure sensor implemented on said integrated circuit, an external sensor unit, a 30 voltage level sensor, a current sensor or a temperature sensor.

6. Integrated circuit according to any of the previous claims, further comprising a clock unit for providing a clock signal for said wake-up timer unit.

7. Integrated circuit according to claim 6, wherein said clock unit is

operatively connected to an oscillator unit, said oscillator unit being at least one of a group comprising a crystal oscillator or a controlled oscillator.

8. Integrated circuit according to claim 7, wherein said oscillator unit is a controlled oscillator, and wherein said oscillator comprises tuning means arranged for periodically tuning said controlled oscillator according to a duty cycle, and wherein said tuning means are arranged for adapting said duty cycle dependent on a tuning signal which is indicative of an environmental parameter.

9. Integrated circuit according to claim 8, said tuning means further comprising means for providing said tuning signal being indicative for at least one of a group comprising temperature, rate of change of temperature.

10. Integrated circuit according to any of the previous claims, further comprising a transducer interface for enabling said integrated circuit to be operatively connected to a transducer.

11. Integrated circuit according to any of the previous claims, further comprising a communication interface for reading or writing data to said integrated circuit.

12. Integrated circuit according to claim 11, said integrated circuit being arranged for programming of operation parameters of said circuit.

13. Integrated circuit according to any of the previous claims, wherein said power supply means comprise an input voltage connector for receiving power from an external power source.

14. Power management circuit for an electrically powered system, said power management circuit comprising a power supply management controller integrated circuit according to any of the previous claims.

25 15. Method of managing power supply to one or more system units of a system, wherein said system units are powered by power supply means, and wherein said powering of said units is controlled by a power supply control unit, said method comprising a step of:

acknowledging an active or passive state of said system;

30 said power supply control unit managing said supply by ceasing powering of said system units for de-activation of said system during said passive state of said system, and maintaining powering of said system units during an active state of said system, and

said power supply control unit periodically powering said system units during said passive state of said system for enabling activation of said system.

Fig. 1

# INTERNATIONAL SEARCH REPORT

International application No

PCT/NL2009/050682

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. G06F1/32

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                      | Relevant to claim No |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| X         | US 2005/168438 A1 (CASEBOLT MARK W [US] ET AL) 4 August 2005 (2005-08-04)<br>paragraphs [0040], [0041], [0072] - [0094]; figures 1,8<br>-----                                                                                           | 1-15                 |

| X         | US 4 698 748 A (JUZSWIK DAVID L [US] ET AL) 6 October 1987 (1987-10-06)<br>column 1, line 53 - column 3, line 35;<br>column 6, line 15 - column 8, line 36;<br>column 25, line 49 - column 28, line 8;<br>figures 2,3a, 3b, 13<br>----- | 1-12,14,<br>15       |

| X         | US 5 167 024 A (SMITH R STEVEN [US] ET AL) 24 November 1992 (1992-11-24)<br>the whole document<br>-----<br>-/-                                                                                                                          | 1-3,6-15             |

Further documents are listed in the continuation of Box C

See patent family annex

\* Special categories of cited documents

- 'A' document defining the general state of the art which is not considered to be of particular relevance

- 'E' earlier document but published on or after the international filing date

- 'L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- 'O' document referring to an oral disclosure, use, exhibition or other means

- 'P' document published prior to the international filing date but later than the priority date claimed

'T' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

'X' document of particular relevance, the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

'Y' document of particular relevance, the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

& document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

8 March 2010

16/03/2010

Name and mailing address of the ISA/

European Patent Office, P B 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel (+31-70) 340-2040,

Fax (+31-70) 340-3016

Authorized officer

Alonso Nogueiro, M

**INTERNATIONAL SEARCH REPORT**International application No

PCT/NL2009/050682**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                     | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2004/148533 A1 (NICHOLAS KEN [US])<br>29 July 2004 (2004-07-29)<br>the whole document<br>-----      | 1-15                  |

| X         | US 5 990 868 A (FREDERICK JOHN W [US])<br>23 November 1999 (1999-11-23)<br>the whole document<br>----- | 1,11                  |

**INTERNATIONAL SEARCH REPORT**

## Information on patent family members

International application No

**PCT/NL2009/050682**

| Patent document cited in search report | Publication date | Patent family member(s) |                                              | Publication date                                                                                           |                                                                                                                    |

|----------------------------------------|------------------|-------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| US 2005168438                          | A1               | 04-08-2005              | NONE                                         |                                                                                                            |                                                                                                                    |

| US 4698748                             | A                | 06-10-1987              | CA<br>DE<br>DE<br>EP<br>ES<br>JP<br>JP<br>JP | 1229875 A1<br>3486192 D1<br>3486192 T2<br>0140814 A2<br>8507710 A1<br>1781504 C<br>4069465 B<br>60143050 A | 01-12--1987<br>09-09--1993<br>18-11--1993<br>08-05--1985<br>16-12-1985<br>13-08--1993<br>06-11--1992<br>29-07-1985 |

| US 5167024                             | A                | 24-11-1992              | NONE                                         |                                                                                                            |                                                                                                                    |

| us 2004148533                          | A1               | 29-07-2004              | NONE                                         |                                                                                                            |                                                                                                                    |

| us 5990868                             | A                | 23-11-1999              | NONE                                         |                                                                                                            |                                                                                                                    |