1. 一种存储装置，包括：

行电路；

列电路；以及

单元阵列，

其中，所述单元阵列位于进行电源门控的电源定域中，

所述单元阵列包括：

存储单元；

第一备份电路；

字线；

包括第一位线和第二位线的位线对；

第一电源线；以及

第二电源线，

所述行电路驱动所述字线，

所述列电路驱动所述位线对，

所述存储单元包括：

包括第一节点及第二节点的双稳态电路；

控制所述第一节点与所述第一位线之间的导通状态的第一转移晶体管；以及

控制所述第二节点与所述第二位线之间的导通状态的第二转移晶体管，

所述第一转移晶体管的栅电极及所述第二转移晶体管的栅电极电连接于所述字线，

所述第一电源线及所述第二电源线电连接于所述双稳态电路，所述第一备份电路电连接于所述第一节点及所述第二节点，

所述第一备份电路层叠在形成有所述存储单元的区域上，

第一至第五布线层包括在所述存储装置中，

所述双稳态电路中的晶体管的栅电极、所述第一转移晶体管的所述栅电极及所述第二转移晶体管的所述栅电极位于所述第一布线层中，所述第二至第五布线层层叠在所述存储单元与所述第一备份电路之间，

所述第二电源线位于所述第一布线层上的所述第二布线层中，所述位线对位于所述第二布线层上的所述第三布线层中，

所述字线位于所述第三布线层上的所述第四布线层中，

所述第一电源线位于所述第四布线层上的所述第五布线层中，所述位线对、所述第一电源线和所述第二电源线在列方向上延伸，并且

所述字线对于所述存储单元中的每一个具有两个弯曲部。

2. 根据权利要求1所述的存储装置，

其中所述第一备份电路包括：

第一保持节点；

第二保持节点；

电连接于所述第一保持节点的第一电容器；

电连接于所述第二保持节点的第二电容器；

第一晶体管；以及

第二晶体管，

所述第一晶体管控制所述第一保持节点与所述第一节点之间的导通状态，

所述第二晶体管控制所述第二保持节点与所述第二节点之间的导通状态，

电源管理单元控制所述第一晶体管的开启/关闭和所述第二晶体管的开启/关闭，

并且所述第一晶体管的沟道形成区域及所述第二晶体管的沟道形成区域都包含金属氧化物。

3. 根据权利要求1所述的存储装置，

其中代替所述第一备份电路包括第二备份电路，

并且所述第二备份电路只电连接于所述第一节点和所述第二节点中的所述第一节点。

4. 根据权利要求3所述的存储装置，

其中所述第二备份电路包括第三保持节点、电连接于所述第三保持节点的第三电容器及第三晶体管，

所述第三晶体管控制所述第一节点与所述第三保持节点之间的导通状态，

并且所述第三晶体管的沟道形成区域包含金属氧化物。

5. 一种包括权利要求1所述的存储装置的半导体装置，

其中，所述半导体装置包括：

处理器核心；以及

所述存储装置与所述处理器核心之间的数据传送给用总线。

6. 一种包括芯片的电子构件，其中权利要求1所述的存储装置安装在所述芯片上，

其中，所述电子构件包括引线，

并且，所述引线电连接于所述芯片。

7. 一种包括权利要求6所述的电子构件的电子装置，

其中，所述电子装置包括显示部、触摸传感器、麦克风、扬声器、操作键和外壳中的至少一个。

8. 一种存储装置，包括：

行电路；

列电路；以及

单元阵列，

其中，所述单元阵列位于进行电源门控的电源定域中，

所述单元阵列包括：

存储单元；

第一备份电路；

字线；

包括第一位线和第二位线的位线对；

第一电源线；以及

第二电源线，

所述行电路驱动所述字线，

所述列电路驱动所述位线对，

所述存储单元包括：

包括第一节点及第二节点的双稳态电路；

控制所述第一节点与所述第一线之间的导通状态的第一转移晶体管；以及

控制所述第二节点与所述第二线之间的导通状态的第二转移晶体管，

所述第一转移晶体管的栅电极及所述第二转移晶体管的栅电极电连接于所述字线，

所述第一电源线及所述第二电源线电连接于所述双稳态电路，所述第一备份电路电连接于所述第一节点及所述第二节点，

所述第一备份电路层叠在形成有所述存储单元的区域上，

第一至第五布线层包括在所述存储装置中，

所述双稳态电路中的晶体管的栅电极、所述第一转移晶体管的所述栅电极及所述第二转移晶体管的所述栅电极位于所述第一布线层中，所述第二布线层及所述第三布线层层叠在所述存储单元与所述第一备份电路之间，

所述第四布线层及所述第五布线层层叠在所述第一备份电路上，所述字线及所述第一电源线位于所述第五布线层中，

所述位线位于所述第三布线层中，

并且，所述第二电源线位于所述第二布线层中。

9. 根据权利要求8所述的存储装置，

其中所述第一备份电路包括：

第一保持节点；

第二保持节点；

电连接于所述第一保持节点的第一电容器；

电连接于所述第二保持节点的第二电容器；

第一晶体管；以及

第二晶体管，

所述第一晶体管控制所述第一保持节点与所述第一节点之间的导通状态，

所述第二晶体管控制所述第二保持节点与所述第二节点之间的导通状态，

电源管理单元控制所述第一晶体管的开启/关闭和所述第二晶体管的开启/关闭，

并且所述第一晶体管的沟道形成区域及所述第二晶体管的沟道形成区域都包含金属氧化物。

10. 根据权利要求8所述的存储装置，

其中代替所述第一备份电路包括第二备份电路，

并且所述第二备份电路只电连接于所述第一节点和所述第二节点中的所述第一节点。

11. 根据权利要求10所述的存储装置，

其中所述第二备份电路包括第三保持节点、电连接于所述第三保持节点的第三电容器及第三晶体管，

所述第三晶体管控制所述第一节点与所述第三保持节点之间的导通状态，

并且所述第三晶体管的沟道形成区域包含金属氧化物。

12. 一种包括权利要求8所述的存储装置的半导体装置，

其中，所述半导体装置包括：

处理器核心；以及

所述存储装置与所述处理器核心之间的数据传送给总线。

13. 一种包括芯片的电子构件，其中权利要求8所述的存储装置安装在所述芯片上，

其中，所述电子构件包括引线，

并且，所述引线电连接于所述芯片。

14. 一种包括权利要求13所述的电子构件的电子装置，

其中，所述电子装置包括显示部、触摸传感器、麦克风、扬声器、操作键和外壳中的至少一个。

## 存储装置、半导体装置、电子构件以及电子装置

### 技术领域

[0001] 本发明的说明书、附图以及权利要求书(以下称为“本说明书等”)涉及一种半导体装置及其工作方法等。注意,本发明的一个实施方式不局限于所例示的技术领域。

[0002] 在本说明书等中,半导体装置是指利用半导体特性的装置以及包括半导体元件(晶体管、二极管、光电二极管等)的电路及包括该电路的装置等。另外,半导体装置是指能够利用半导体特性而工作的所有装置。例如,集成电路、具备集成电路的芯片或在其封装中容纳有芯片的电子构件是半导体装置的一个例子。另外,存储装置、显示装置、发光装置、照明装置、电子构件以及电子装置等有时本身是半导体装置,或者有时包括半导体装置。

### 背景技术

[0003] (1)电子装置的低功耗化受到重视。因此,CPU等集成电路(IC)的低功耗化成为电路设计上的重要课题。IC的功耗大致可分为工作时的功耗(动态功率)及不工作时(待机时)的功耗(静态功率)这两种功耗。当为了实现高性能化而提高工作频率时,动态功率增大。静态功率的大部分是因晶体管的泄漏电流而被消耗的功率。作为泄漏电流,有亚阈值泄漏电流、栅极隧道泄漏电流、栅极诱导漏极泄漏(GIDL)电流、结隧穿泄漏电流。这些泄漏电流随着晶体管的微型化的进展而增大,因此,在使IC高性能化或高集成化时,功耗的增大会成为很大的问题。

[0004] 为了减少半导体装置的功耗,通过利用电源门控或时钟门控来停止不需要工作的电路。在电源门控中电源供应停止,由此有削减待机功率的效果。为了在CPU中进行电源门控,需要将寄存器或高速缓冲存储器的存储数据备份于非易失性存储器中。

[0005] 已知其沟道形成区由金属氧化物形成的晶体管(以下,有时称为“氧化物半导体晶体管”或“OS晶体管”)。已提出了一种备份电路,其中通过利用OS晶体管的关态电流极小的特性,在停止电源时也能够保持数据。例如,专利文献1、2及非专利文献1、2提出了具备使用OS晶体管的备份电路的静态随机存取存储器(SRAM)。

[0006] (2)为了SRAM的存储单元的微型化,提出了各种存储单元的布局(例如,专利文献3)。

[0007] [参考文献]

[0008] [专利文献]

[0009] [专利文献1]日本专利申请公开第2015-195075号公报

[0010] [专利文献2]日本专利申请公开第2016-139450号公报

[0011] [专利文献3]日本专利申请公开第2001-28401号公报

[0012] [非专利文献]

[0013] [非专利文献1]T.Ishizu et al., “SRAM with C-Axis Aligned Crystalline Oxide Semiconductor:Power Leakage Reduction Technique for Microprocessor Caches,” Int.Memory Workshop, 2014, pp.103-106.

[0014] [非专利文献2]H.Tamura et al., “Embedded SRAM and Cortex-M0 Core Using

a 60-nm Crystalline Oxide Semiconductor,” IEEE Micro, 2014, Vol. 34, No. 6, pp. 42-53.

## 发明内容

[0015] 本发明的一个实施方式的目的之一是提供一种能够进行电源门控的存储装置且减小存储单元的面积开销。

[0016] 注意,多个目的的记载不互相妨碍彼此的存在。本发明的一个实施方式并不一定必须实现所有上述目的。上述列举的目的以外的目的是从本说明书等的记载自然得知的,而有可能成为本发明的一个实施方式的目的。

[0017] 本发明的一个实施方式是一种存储装置,该存储装置包括单元阵列、用来驱动单元阵列的行电路及列电路。单元阵列包括第一电源线、第二电源线、字线、位线对、存储单元及备份电路。单元阵列设置在能够进行电源门控的电源定域中。在单元阵列的电源门控序列中,存储单元的数据备份在备份电路中。备份电路层叠在存储单元的形成区域上。备份电路与存储单元之间设置有多个布线层。第一电源线、第二电源线、字线及位线对设置在彼此不同的布线层中。

[0018] 在本说明书等中,有时为了表示顺序而附记“第一”、“第二”、“第三”等序数词。另外,有时为了避免构成要素的混淆而附记序数词。该序数词不限定构成要素的个数,并且不限定顺序。例如,可以将“第一”调换为“第二”或“第三”来说明本发明的一个实施方式。

[0019] 在本说明书等中,当记载为“X与Y连接”时,表示如下情况:X与Y电连接的情况;X与Y在功能上连接的情况;以及X与Y直接连接的情况。因此,不局限于如附图或文中所示的连接关系等预定的连接关系,其他的连接关系也包括在附图或文中所记载的范围内。X和Y都是对象物(例如,装置、元件、电路、布线、电极、端子、导电膜、层等)。

[0020] 晶体管包括栅极、源极以及漏极这三个端子。栅极被用作控制晶体管的开关状态的控制端子。在用作源极或漏极的两个输入输出端子中,根据晶体管的类型或者供应到各输入输出端子的电位电平将一个端子用作源极而将另一个端子用作漏极。因此,在本说明书等中,“源极”和“漏极”可以互相调换。另外,在本说明书等中,有时将栅极以外的两个端子称为第一端子及第二端子。

[0021] 电压大多是指某个电位与标准电位(例如,接地电位(GND)或源极电位)之间的电位差。由此,可以将电压换称为电位。电位是相对性的。因此,即使记载为“GND”,也并不一定是指0V的。

[0022] 节点可以根据电路结构或装置结构等换称为端子、布线、电极、导电层、导电体或杂质区域等。另外,端子、布线等也可以换称为节点。

[0023] 在本说明书等中,“膜”和“层”可以根据情形或状况相互调换。例如,有时可以将“导电层”调换为“导电膜”。例如,有时可以将“绝缘膜”调换为“绝缘层”。

[0024] 在本说明书等中,金属氧化物是指广义上的金属的氧化物。金属氧化物被分类为氧化物绝缘体、氧化物导电体(包括透明氧化物导电体)和氧化物半导体(Oxide Semiconductor,也可以简称为OS)等。例如,有时将用于晶体管的沟道形成区域中的金属氧化物称为氧化物半导体。

[0025] 在本说明书等中,在没有特别说明的情况下,可以将包含氮的金属氧化物用于晶

体管的沟道形成区域。此外,也可以将包含氮的金属氧化物称为金属氧氮化物。

[0026] 本发明的一个实施方式可以提供一种能够进行电源门控的存储装置,并且可以减小存储单元的面积开销。

[0027] 多个效果的记载并不妨碍其他效果的存在。此外,本发明的一个实施方式并不需要具有所有上述效果。在本发明的一个实施方式中,上述之外的目的、效果及新颖的特征可从本说明书中的描述及附图自然得知。

## 附图说明

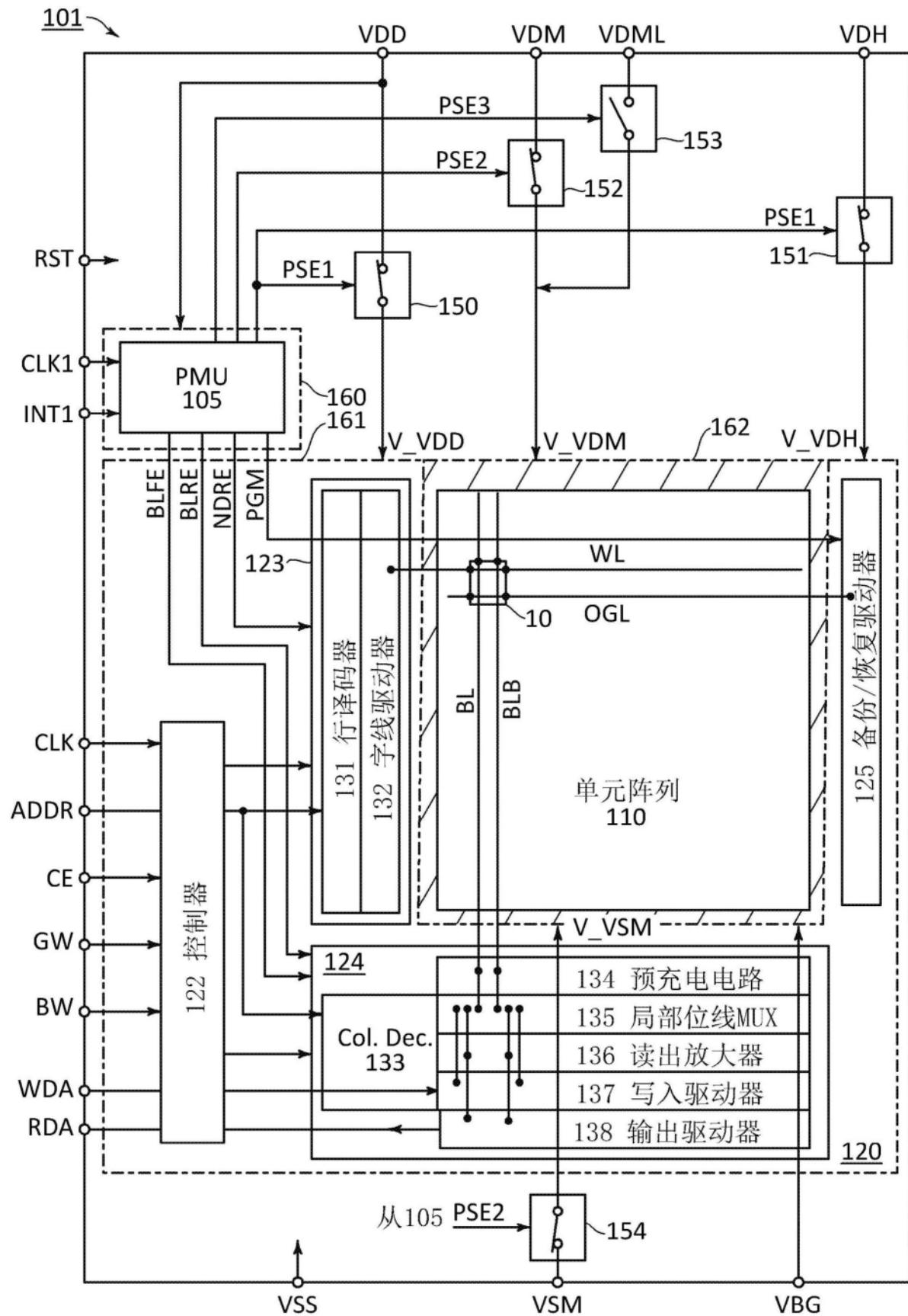

[0028] 图1是示出存储装置的结构实例的方框图。

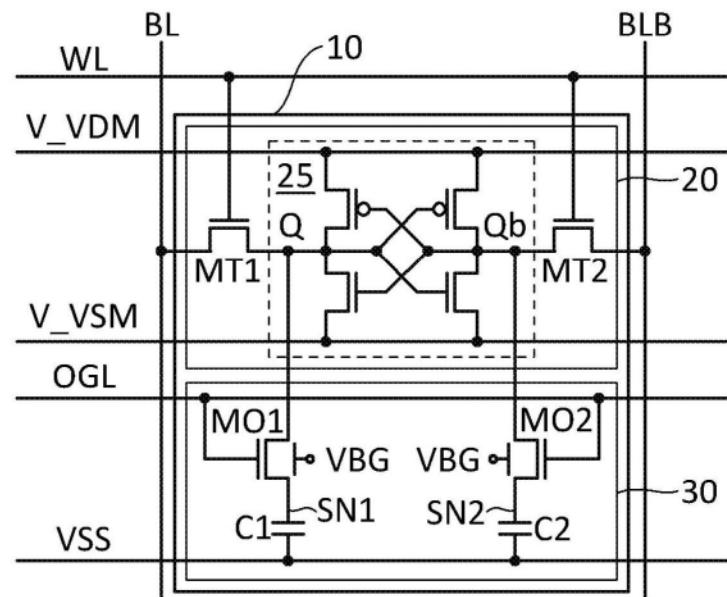

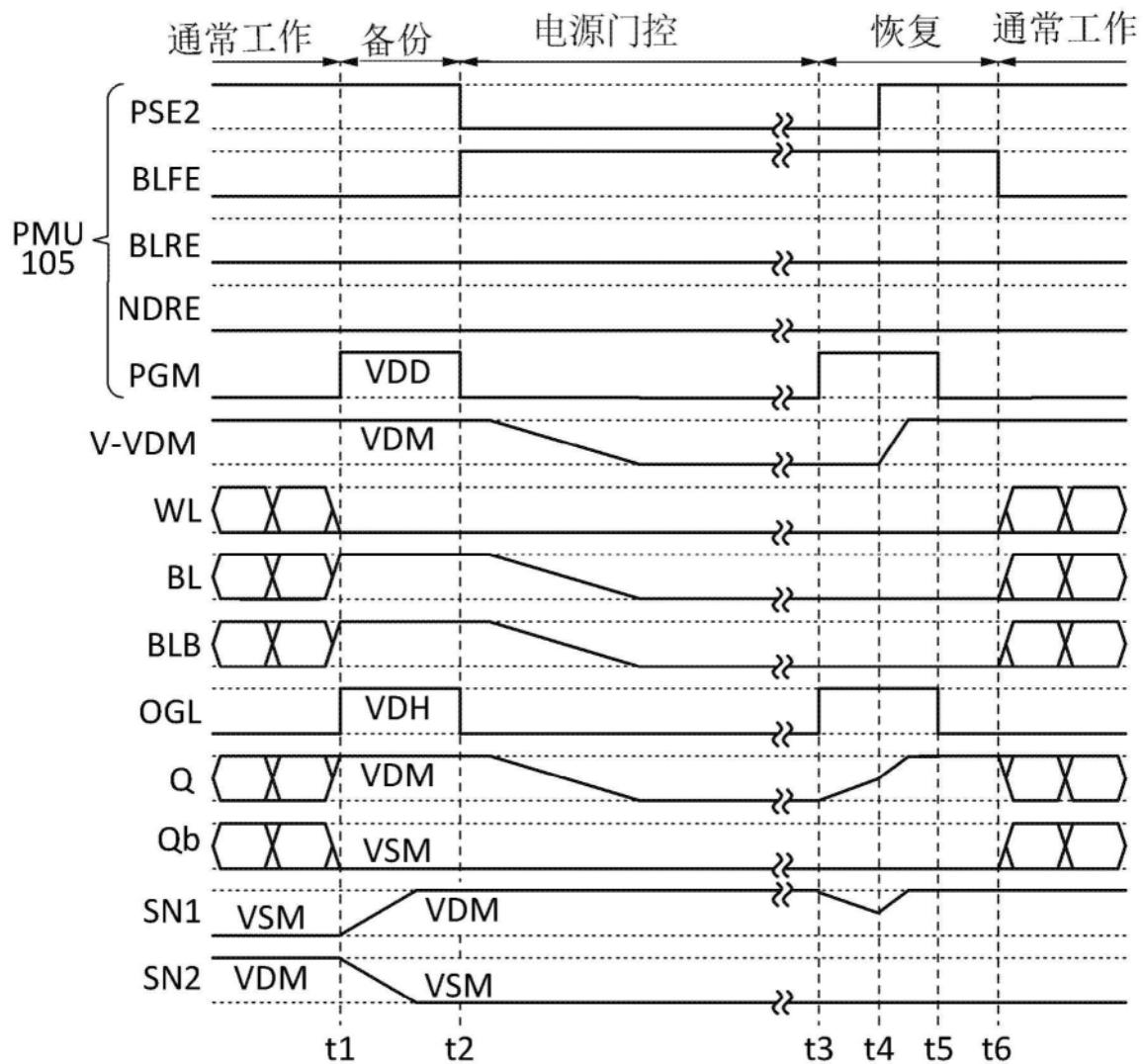

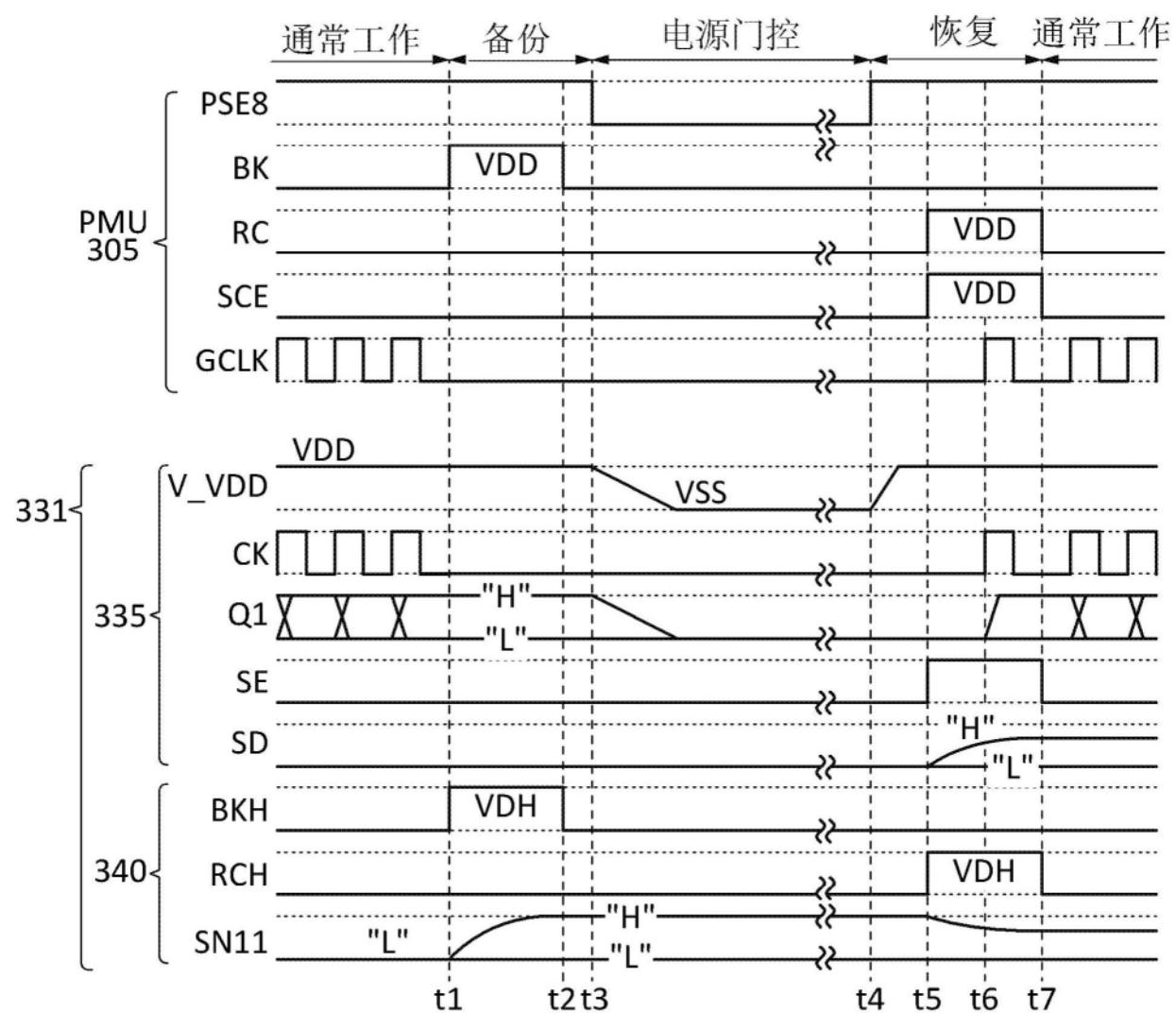

[0029] 图2A是示出单元的结构实例的电路图,图2B是示出存储装置的工作实例的时序图。

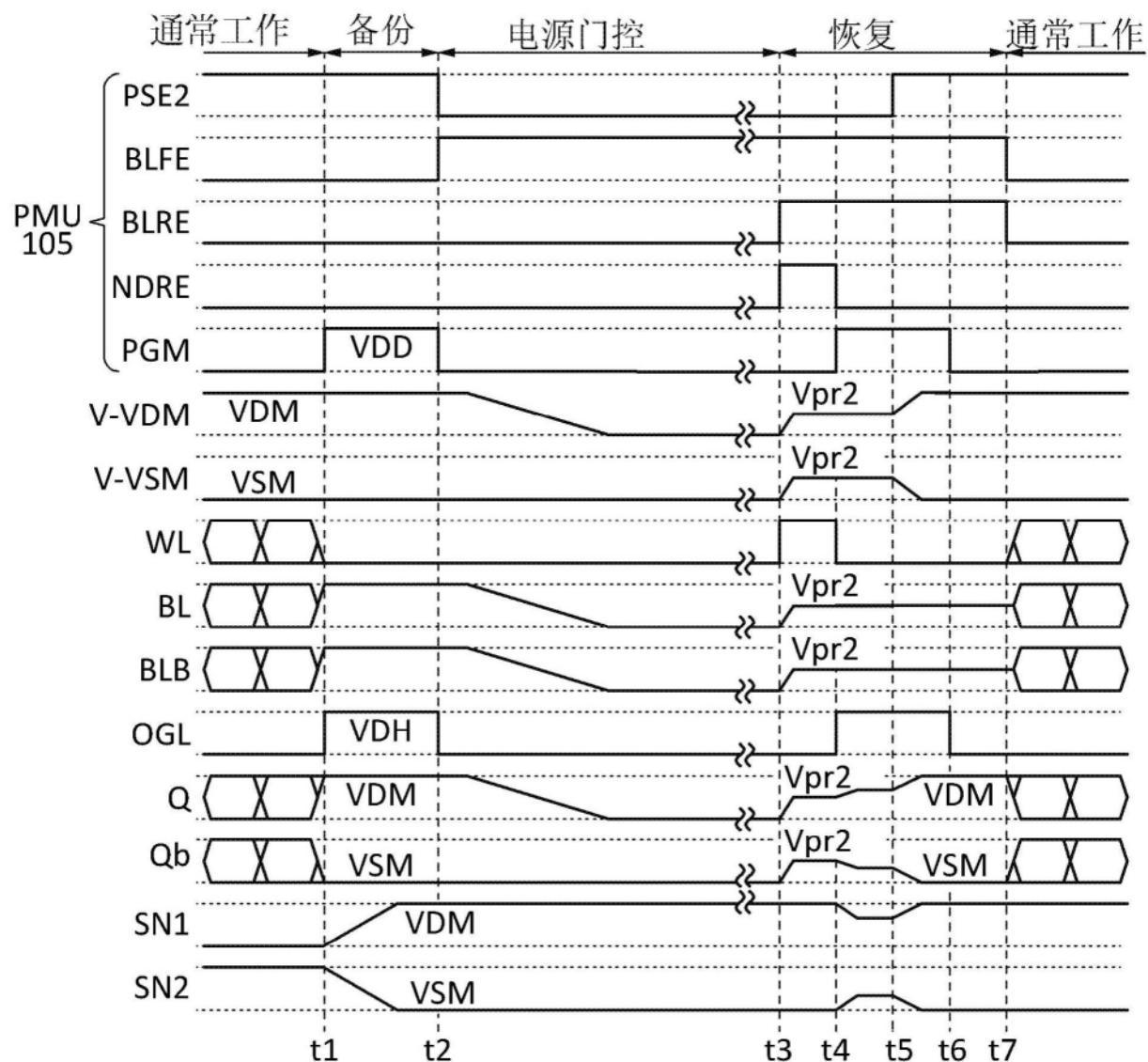

[0030] 图3是示出列电路的结构实例的电路图。

[0031] 图4是存储装置的状态迁移图。

[0032] 图5A是示出单元的结构实例的电路图,图5B是示出存储装置的工作实例的时序图。

[0033] 图6A是示出单元的结构实例的电路图,图6B是示出存储装置的工作实例的时序图。

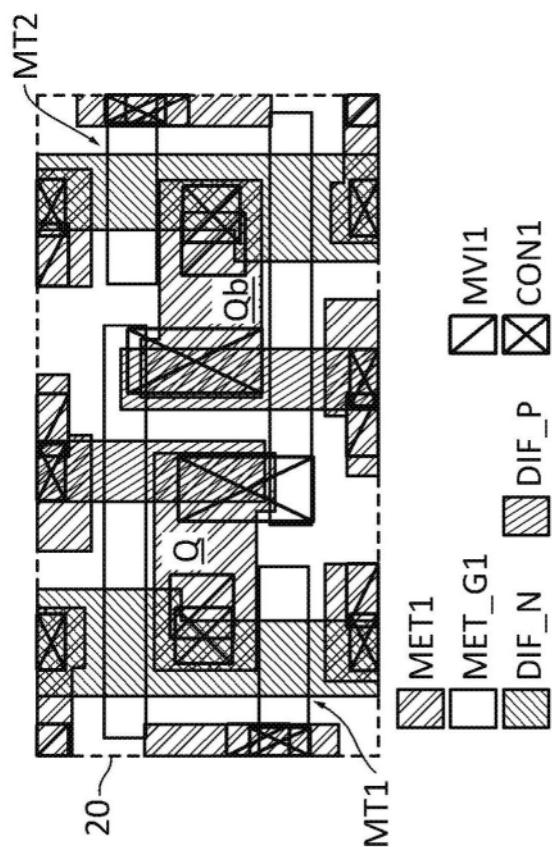

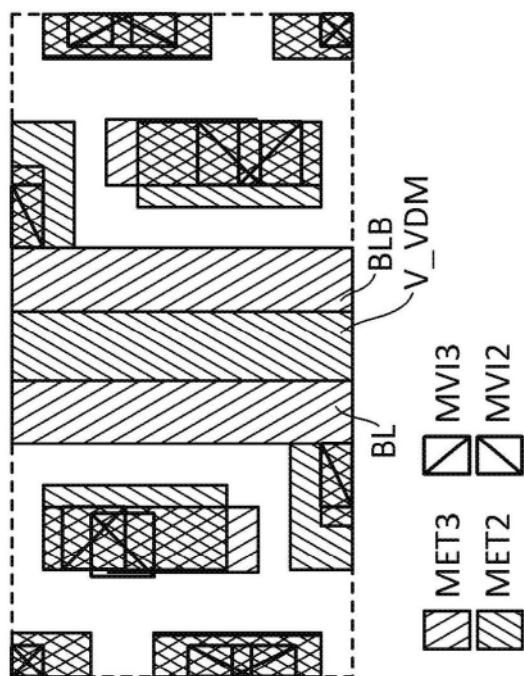

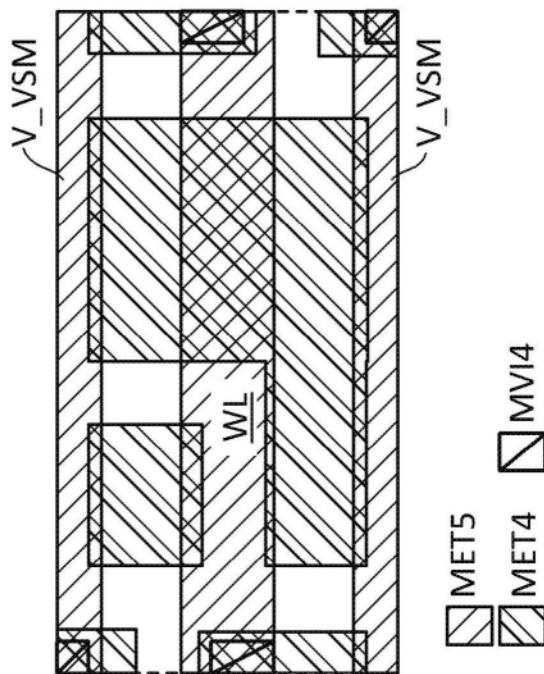

[0034] 图7A至图7D示出单元的布局实例。

[0035] 图8A至图8D示出单元的布局实例。

[0036] 图9A至图9D示出单元的布局实例。

[0037] 图10A至图10D示出单元的布局实例。

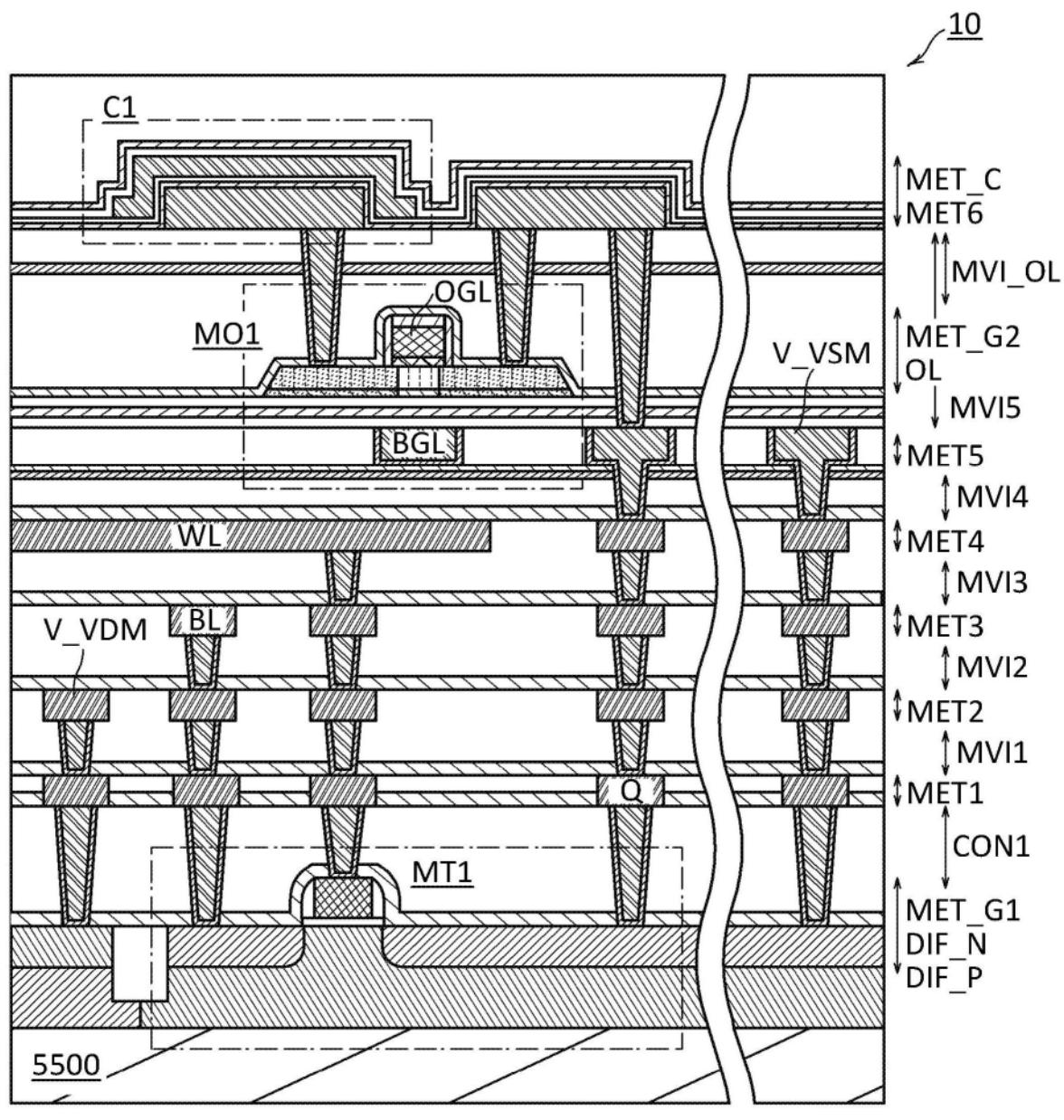

[0038] 图11是示出单元的叠层结构实例的截面图。

[0039] 图12是示出单元的叠层结构实例的截面图。

[0040] 图13是示出CPU的结构实例的方框图。

[0041] 图14是示出触发器的结构实例的电路图。

[0042] 图15是示出触发器的工作实例的时序图。

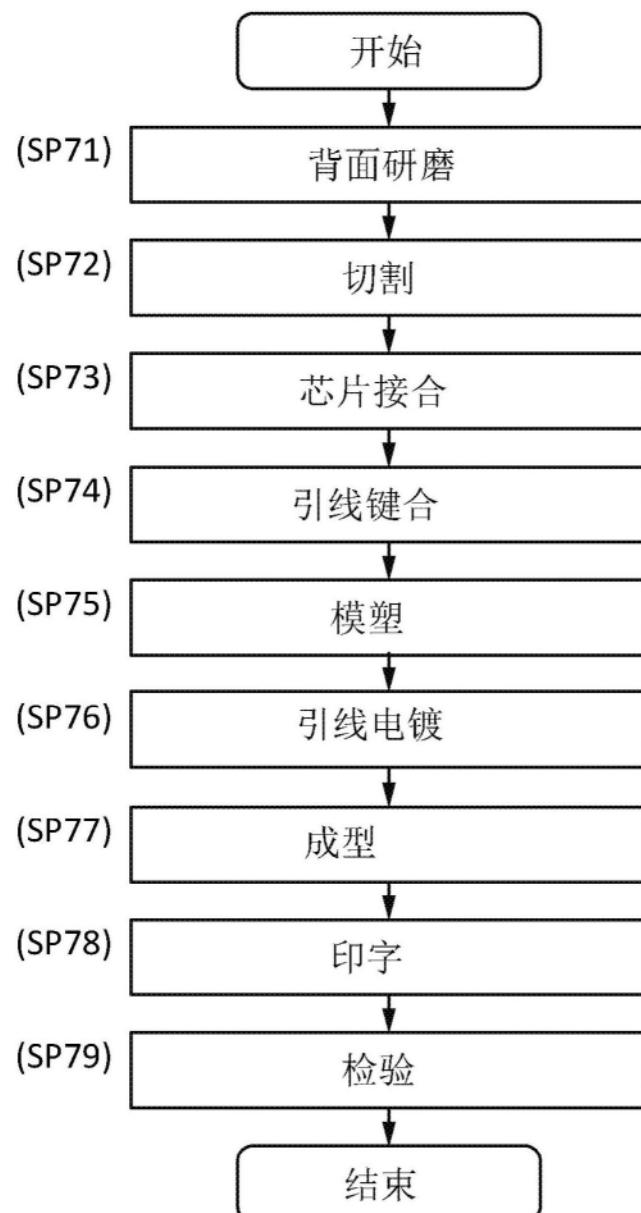

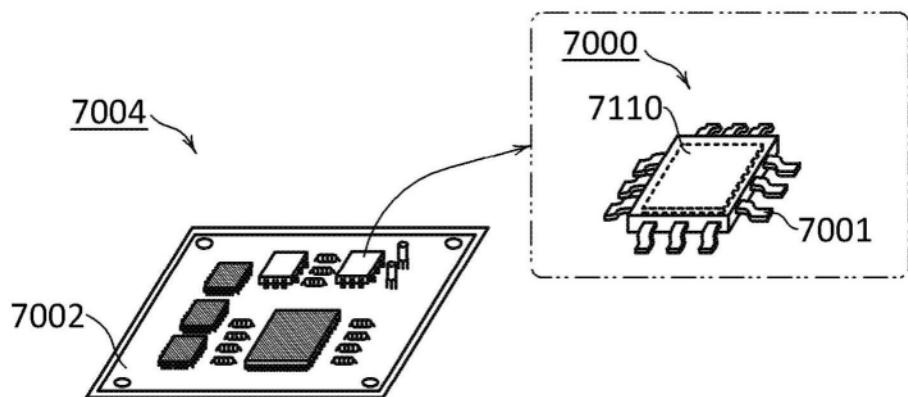

[0043] 图16A是示出电子构件的制造方法实例的流程图,图16B是示出电子构件的结构实例的立体示意图。

[0044] 图17A至图17F示出电子装置的结构实例。

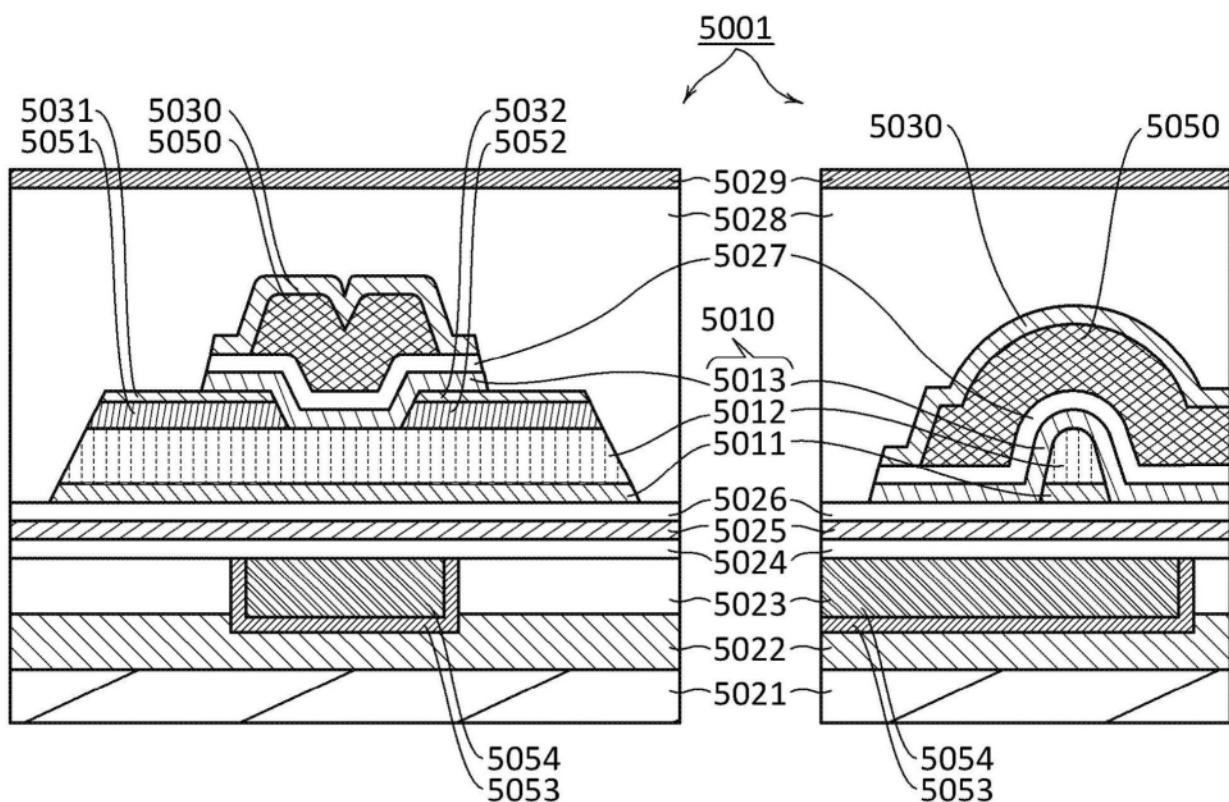

[0045] 图18A和图18B是示出OS晶体管的结构实例的截面图。

[0046] 图19A和图19B是示出OS晶体管的结构实例的截面图。

## 具体实施方式

[0047] 以下说明本发明的实施方式。注意,本发明的一个实施方式不局限于以下说明,所属技术领域的普通技术人员可以很容易地理解一个事实,就是本发明在不脱离其宗旨及其范围的条件下,其方式及详细内容可以被变换为各种各样的形式。因此,本发明的一个实施方式不应该被解释为仅局限在以下所示的实施方式所记载的内容中。

[0048] 下面所示的多个实施方式可以适当地组合。另外,在一个实施方式中示出多个结构例子(包括制造方法例子、工作方法例子等)的情况下,可以适当地组合该结构例子,并且

可以适当地组合其他实施方式所记载的一个或多个结构例子。

[0049] 在附图中,有时使用同一附图标记表示同一构成要素、具有相同功能的构成要素、由同一材料构成的构成要素或者同时形成的构成要素等,并且有时省略重复说明。

[0050] 在附图中,为便于清楚地说明,有时夸大表示大小、层的厚度及区域等。因此,本发明的一个实施方式并不一定限定于上述尺寸。在附图中,示意性地示出理想的例子,而不局限于附图所示的形状或数值等。例如,可以包括因噪声或定时偏差等所引起的信号、电压或电流的不均匀等。

[0051] 在本说明书中,为了方便起见,有时使用“上”、“上方”、“下”、“下方”等表示配置的词句以参照附图说明构成要素的位置关系。另外,构成要素的位置关系根据描述各构成要素的方向适当地变化。因此,不局限于本说明书中所说明的词句,根据情况可以适当地改换词句。

[0052] [实施方式1]

[0053] 在本实施方式中,作为存储装置的一个例子,说明能够进行电源门控的SRAM。

[0054] 《存储装置101》

[0055] 图1是示出存储装置的结构实例的功能方框图。图1所示的存储装置101包括电源管理单元(PMU)105、单元阵列110、外围电路120及功率开关150至154。

[0056] 存储装置101读出单元阵列110的数据并向单元阵列110写入数据。在图1中,数据RDA是读出数据,数据WDA是写入数据。向存储装置101输入时钟信号CLK1、CLK、地址信号ADDR及信号RST、INT1、CE、GW、BW。信号RST是复位信号,并被输入到PMU105和外围电路120。信号INT1是中断信号。信号CE是芯片使能信号,信号GW是全局写入使能信号,信号BW是字节写入使能信号。

[0057] 向存储装置101输入电压VDD、VDH、VDM、VDML、VSS、VSM、VBG。电压VDD、VDM、VDML、VDH为高电平电源电压。电压VSS、VSM为低电平电源电压,例如是GND(接地电位)或0V。

[0058] 单元阵列110包括单元10、字线WL、位线BL、BLB及布线OGL。位线BL、BLB也可以称为局部位线。有时由设置在同一列上的位线BL和位线BLB构成的布线对称为位线对BL及BLB。

[0059] 外围电路120包括控制器122、行电路123、列电路124及备份/恢复驱动器125。

[0060] 控制器122具有如下功能:对信号CE、GW、BW进行逻辑运算而决定工作模式的功能;生成用来执行所决定的工作模式的对行电路123和列电路124的控制信号的功能。另外,也可以在控制器122中设置暂时储存地址信号ADDR、信号CE、GW、BW及数据RDA、WDA的寄存器。

[0061] 行电路123包括行译码器131和字线驱动器132。行译码器131对地址信号ADDR进行译码,生成字线驱动器132的控制信号。字线驱动器132选择地址信号ADDR所指定的行的字线WL。

[0062] 列电路124包括列译码器133、预充电电路134、局部位线复用器(MUX)135、读出放大器136、写入驱动器137及输出驱动器138。列电路124对地址信号ADDR所指定的列的位线BL、BLB进行数据的写入及读出。关于列电路124的电路结构,将在后面描述。

[0063] 在存储装置101中,根据需要可以适当地取舍各电路、各信号及各电压。另外,也可以追加其他电路或其他信号。此外,存储装置101的输入信号及输出信号的结构(例如,位宽)根据存储装置101的工作模式及单元阵列110的结构等设定。

[0064] 〈电源定域〉

[0065] 存储装置101包括多个电源定域。图1的例子中设置有电源定域160、161及162。对电源定域160不进行电源门控。对电源定域161、162进行电源门控。电压VSS不通过功率开关而被输入到各电源定域160、161及162。

[0066] 电源定域160中设置有PMU105。不通过功率开关而向电源定域160输入电压VDD。

[0067] 电源定域161中设置有外围电路120和虚拟电压线V\_VDD、V\_VDH。功率开关150控制向虚拟电压线V\_VDD(以下,称为V\_VDD线)供应电压VDD。功率开关151控制向虚拟电压线V\_VDH(以下,称为V\_VDH线)供应电压VDH。在备份/恢复驱动器125中使用电压VDH。

[0068] 电源定域162中设置有单元阵列110和虚拟电压线V\_VDM、V\_VSM。功率开关152控制向虚拟电压线V\_VDM(以下,称为V\_VDM线)输入电压VDM,功率开关153控制向V\_VDM线输入电压VDML。电压VDML低于电压VDM。功率开关154控制向虚拟电压线V\_VSM(以下,称为V\_VSM线)输入电压VSM。不通过功率开关而向电源定域162输入电压VBG。

[0069] 〈PMU〉

[0070] PMU105在低功耗模式中控制存储装置101。向PMU105输入时钟信号CLK1和信号INT1。信号INT1是中断信号。可以向PMU105输入多种中断信号。PMU105根据信号CLK1、INT1生成信号PSE1、PSE2、PSE3、BLFE、BLRE、NDRE及PGM。

[0071] 信号PSE1、PSE2及PSE3是功率开关使能信号。信号PSE1控制功率开关150、151的开启/关闭,信号PSE2控制功率开关152、154的开启/关闭,信号PSE3控制功率开关153的开启/关闭。在此,在信号PSE1为“H”(高电平)时功率开关150处于开启状态,在信号PSE1为“L”(低电平)时功率开关150处于关闭状态。其他功率开关也是同样的。

[0072] 信号NDRE、BLFE、BLRE及PGM是在低功耗模式中使用的控制信号。信号NDRE是节点复位使能信号,并控制单元10的节点Q、Qb的复位工作。信号NDRE被输入到行电路123。行电路123根据信号NDRE选择单元阵列110的所有字线WL。信号BLFE、BLRE被输入到列电路124。信号BLFE是位线浮动使能信号,并控制使位线对BL及BLB成为浮动状态的工作。信号BLRE是位线复位使能信号,并控制位线对BL及BLB的复位工作。

[0073] 信号PGM被输入到备份/恢复驱动器125。备份/恢复驱动器125根据信号PGM选择单元阵列110的所有布线OGL。例如,备份/恢复驱动器125对信号PGM进行电平移位而生成布线OGL的选择信号。选择信号的高电平电压为VDH。电压VDH高于电压VDD。在选择信号的高电平电压为VDD的情况下,不需要设置功率开关151。

[0074] 〈单元10〉

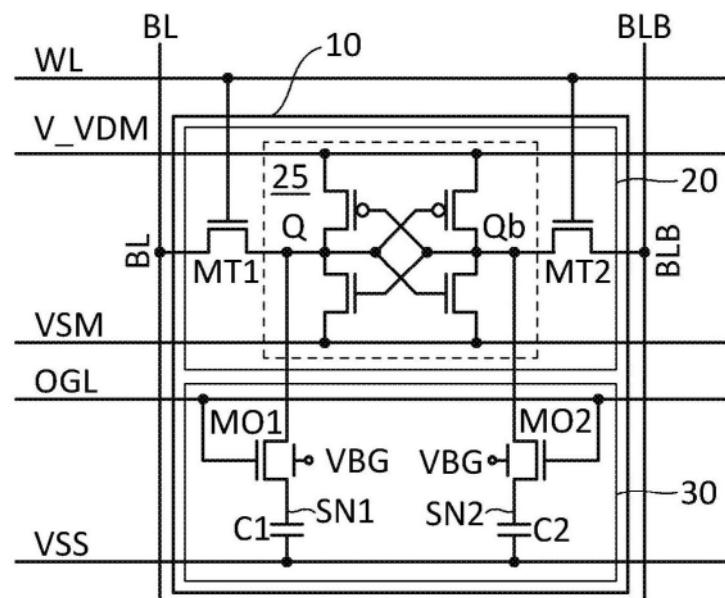

[0075] 图2A示出单元10的电路结构实例。单元10包括存储单元20和备份电路30。存储单元20具有与标准的6晶体管(6T)SRAM单元相同的电路结构,由双稳态电路25和晶体管MT1、MT2构成。双稳态电路25电连接于V\_VDM线和V\_VSM线。

[0076] 在图2A的例子中,双稳态电路25是由两个CMOS反相器电路构成的锁存电路。节点Q、Qb是CMOS反相器电路的输入端子和输出端子的连接部,且是互补数据的保持节点。在节点Q、Qb分别成为“H”、“L”或者“L”、“H”时,双稳态电路25成为稳定状态。晶体管MT1、MT2为转移晶体管。晶体管MT1控制位线BL与节点Q之间的导通状态,晶体管MT2控制位线BLB与节点Qb之间的导通状态。

[0077] 备份电路30是用来备份存储单元20的数据的电路。通过在各单元10中设置备份电路30,能够进行电源定域162的电源门控。

[0078] 备份电路30电连接于供应电压VSS的电压线(以下,称为VSS线)、供应电压VBG的电压线(以下,称为VBG线)。备份电路30由两个1晶体管1电容器(1T1C)型DRAM单元构成。备份电路30包括节点SN1、SN2、晶体管M01、M02及电容器C1、C2。节点SN1、SN2分别是用来保持节点Q、Qb的数据的保持节点。电容器C1、C2分别是用来保持节点SN1、SN2的电压的存储电容器。晶体管M01控制节点Q与节点SN1之间的导通状态,晶体管M02控制节点Qb与节点SN2之间的导通状态。

[0079] 为了使备份电路30长时间保持数据,作为晶体管M01、M02选择关态电流极小的晶体管。作为晶体管M01、M02优选使用OS晶体管。通过作为晶体管M01、M02使用OS晶体管,可以抑制电荷从电容器C1、C2泄漏,由此备份电路30可以长时间保持数据。也就是说,备份电路30可以被用作非易失性存储电路。

[0080] 由于金属氧化物的带隙为2.5eV以上,因此OS晶体管的因热激发所引起的泄漏电流小,并且如上所述关态电流极小。可以将以沟道宽度标准化的OS晶体管的关态电流降低至几yA/ $\mu$ m以上且几zA/ $\mu$ m以下左右。作为应用于沟道形成区域的金属氧化物,有Zn氧化物、Zn-Sn氧化物、Ga-Sn氧化物、In-Ga氧化物、In-Zn氧化物及In-M-Zn氧化物(M是Ti、Ga、Y、Zr、La、Ce、Nd、Sn或Hf)等。此外,包含铟和锌的氧化物也可以还包含选自铝、镓、钇、铜、钒、铍、硼、硅、钛、铁、镍、锗、锆、钼、铈、钕、钽、钨和镁等中的一种或多种。

[0081] 通过作为晶体管M01、M02使用OS晶体管,可以将备份电路30层叠于包括Si晶体管的存储单元20上,由此可以抑制设置备份电路30时的单元10的面积开销。

[0082] 晶体管M01、M02包括背栅极,背栅极电连接于VBG线。例如,电压VBG为使晶体管M01、M02的阈值电压向正一侧漂移的电压。此外,可以使备份/恢复驱动器125具有根据备份电路30的工作而能够改变输入到VBG线的电压的功能。晶体管M01、M02可以为不包括背栅极的OS晶体管。

[0083] 〈列电路〉

[0084] 参照图3说明列电路124的电路结构实例。

[0085] (预充电电路134)

[0086] 预充电电路134包括预充电电路51、52。预充电电路51、52被信号PRCH1、PRCH2控制。预充电电路51将位线对BL及BLB预充电到电压Vpr1,预充电电路52将位线对BL及BLB预充电到电压Vpr2。预充电电路51、52被用作使位线对BL及BLB的电压平滑化的均衡器。

[0087] 预充电电路51是用来在通常工作模式和待机模式中对位线对BL及BLB进行预充电的电路。此外,预充电电路52是用来在恢复状态及备份状态下对位线对BL及BLB进行预充电的电路。电压Vpr2是恢复用预充电电压,且是备份用预充电电压。

[0088] (读出放大器136)

[0089] 向读出放大器136输入信号PRCH3、SNS。读出放大器136包括局部位线对LRBL及LRBLB、预充电电路53、读出放大器55、复位-置位(RS)锁存电路56、反相器电路57、58及晶体管MP3、MP4。

[0090] 局部位线对LRBL及LRBLB都是局部读出位线。对多个位线对BL及BLB设置有一个局部位线对LRBL及LRBLB。在此,对四个位线对BL及BLB设置有一个局部位线对LRBL及LRBLB。

[0091] 预充电电路53根据信号PRCH3将局部位线对LRBL及LRBLB预充电到电压Vpr1。预充电电路53被用作使位线对LRBL及LRBLB的电压平滑化的均衡器。

[0092] 读出放大器55通过使局部位线对LRBL及LRBLB的电压差增大而检测从单元10读出的数据。读出放大器55包括晶体管MN3和锁存电路55a并电连接于VSS线、V\_VDD线。锁存电路55a由两个反相器电路构成。节点QS、QSb是锁存电路55a的保持节点,电连接于RS锁存电路56的输入。读出放大器55所检测的数据被RS锁存电路56保持。RS锁存电路56由两个NAND电路构成。RS锁存电路56所保持的数据LATOB、LAT0被输入到反相器电路57、58。反相器电路57的输出(数据D0)和反相器电路58的输出(数据DOB)被输入到输出驱动器138。

[0093] 晶体管MP3、MP4控制局部位线对LRBL及LRBLB与读出放大器55之间的导通状态以及局部位线对LRBL及LRBLB与RS锁存电路56之间的导通状态。信号SNS控制晶体管MP3、MP4的开启/关闭。信号SNS还控制晶体管MN3的开启/关闭。信号SNS为用来使读出放大器55处于活动状态的读出放大器使能信号。在读出放大器55处于活动状态时,读出放大器55与局部位线对LRBL及LRBLB之间处于非导通状态。

[0094] (写入驱动器137)

[0095] 写入驱动器137是用来向局部位线对LWBL及LWBLB写入数据的电路。写入驱动器137包括反相器电路59。

[0096] 局部位线对LWBL及LWBLB都是局部写入位线。对多个位线对BL及BLB设置有一个局部位线对LWBL及LWBLB。在此,对四个位线对BL及BLB设置有一个局部位线对LWBL及LWBLB。

[0097] 数据DIN是写入数据。数据DIN被输入到局部位线LWBL和反相器电路59。反相器电路59的输出(数据DINB)被输入到局部位线LWBLB。

[0098] (局部位线MUX135)

[0099] 局部位线MUX135包括MUX135r和MUX135w并被输入信号RDE[3:0]和WTE[15:0]。信号RDE[3:0]为读出使能信号,信号WTE[15:0]为写入使能信号。

[0100] MUX135r选择读出数据的列的位线对BL及BLB。被MUX135r选择的多个位线对BL及BLB分别与不同的局部位线对LRBL及LRBLB电连接。

[0101] MUX135r由晶体管MP1、MP2构成。向晶体管MP1、MP2输入信号RDE[3:0]中的任何一位。晶体管MP1、MP2被用作控制位线对BL及BLB与局部位线对LRBL及LRBLB之间的导通状态的开关。

[0102] MUX135w选择写入数据的列的位线对BL及BLB。被MUX135w选择的多个位线对BL及BLB分别与不同的局部位线对LWBL及LWBLB电连接。MUX135w由晶体管MN1、MN2构成。向晶体管MN1、MN2输入信号WDE[15:0]中的任何一位。晶体管MN1、MN2被用作控制位线对BL及BLB与局部位线对LWBL及LWBLB之间的导通状态的开关。

[0103] 列电路124的电路结构不局限于图3所示的电路结构。可以根据输入信号、输入电压等适当地改变。在图3的例子中,预充电电路52由三个n沟道型晶体管构成,但是有时由三个p沟道型晶体管构成。

[0104] 《工作模式》

[0105] 接着,说明存储装置101的工作模式。表1示出存储装置101的真值表。在此,信号BW的位宽为4位,数据WDA、RDA的位宽为32位。

[0106] [表1]

[0107]

| 工作模式      | RST | CE | GW | BW[0] | BW[1] | BW[2] | BW[3] | BLFE | PSE1 | PSE2 | PSE3 |

|-----------|-----|----|----|-------|-------|-------|-------|------|------|------|------|

| 复位        | L   | X  | X  | X     | X     | X     | X     | L    | H    | H    | L    |

| 待机        | H   | L  | X  | X     | X     | X     | X     | L    | H    | H    | L    |

| 全字写入      | H   | H  | H  | H     | H     | H     | H     | L    | H    | H    | L    |

| 半字写入      | H   | H  | H  | H     | H     | L     | L     | L    | H    | H    | L    |

| 字节 0 写入   | H   | H  | H  | H     | L     | L     | L     | L    | H    | H    | L    |

| 读出        | H   | H  | L  | L     | L     | L     | L     | L    | H    | H    | L    |

| 位线浮动      | H   | L  | X  | X     | X     | X     | X     | H    | H    | H    | L    |

| 休眠        | H   | L  | X  | X     | X     | X     | X     | H    | H    | L    | H    |

| 单元阵列定域 PG | H   | L  | X  | X     | X     | X     | X     | H    | H    | L    | L    |

| 全定域 PG    | L   | L  | X  | X     | X     | X     | X     | L    | L    | L    | L    |

[0108] PG:电源门控

[0109] 在字节0写入模式中,进行写入分配于信号BW[0]的1字节(8位)的数据的工作。例如,在字节0写入模式中,写入数据WDA[7:0]。在字节写入工作中,BW[1]、BW[2]及BW[3]为“H”时的写入数据分别是WDA[15:8]、WDA[23:16]及WDA[31:24]。

[0110] 〈低功耗模式〉

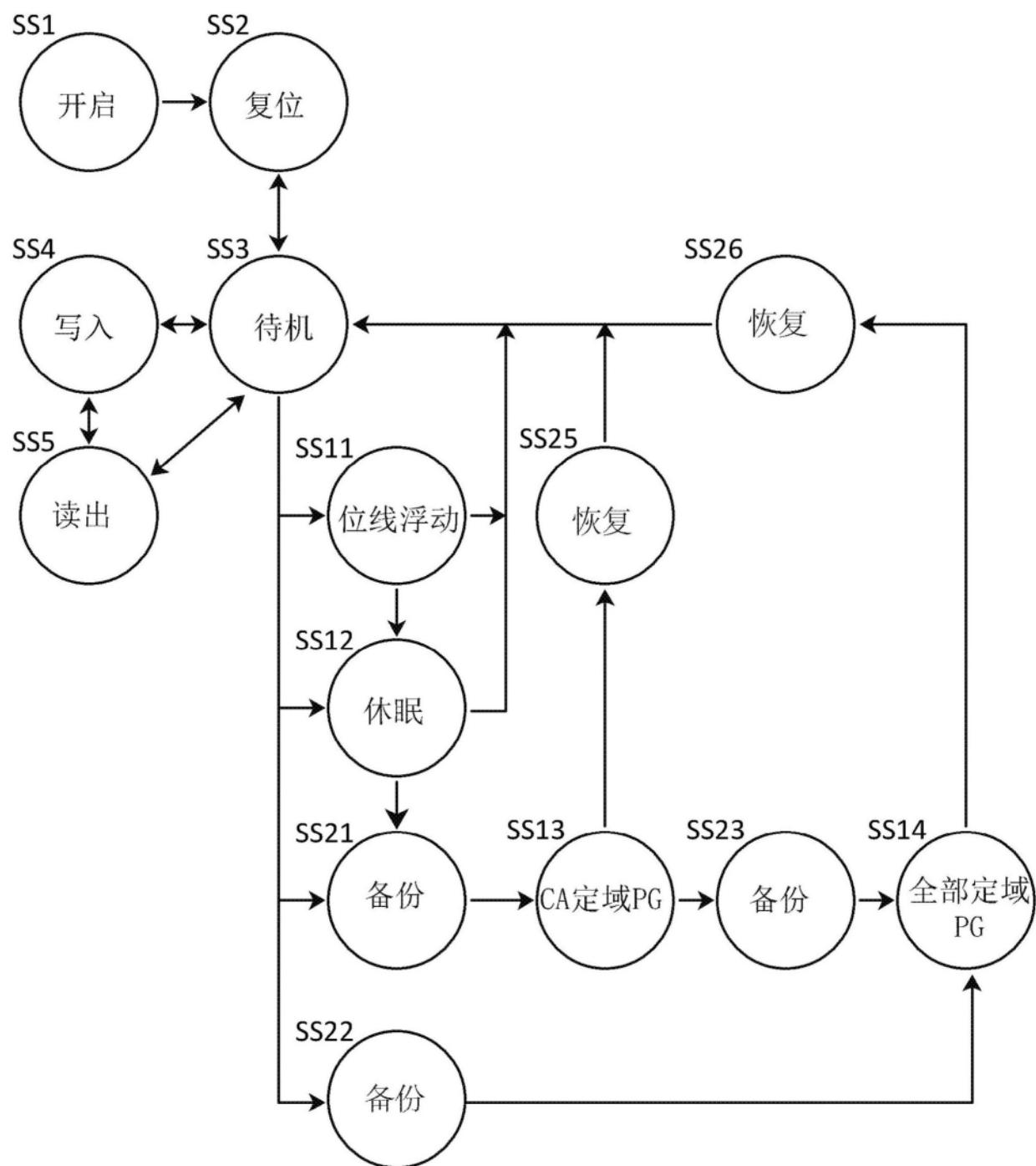

[0111] 图4示出存储装置101的状态迁移图。作为存储装置101的状态,有电源开启状态SS1、复位状态SS2、待机状态SS3、写入状态SS4、读出状态SS5、位线浮动状态SS11、休眠状态SS12、单元阵列(CA)定域电源门控(PG)状态SS13、全部定域PG状态SS14、备份状态SS21至SS23及恢复状态SS25、SS26。如表1的真值表所示,存储装置101的状态根据外部信号及内部信号迁移,在各状态下执行对应的工作模式。

[0112] 存储装置101具有四种低功耗模式:(1)位线浮动模式;(2)休眠模式;(3)单元阵列定域PG模式;(4)全部定域PG模式。PMU105管理低功耗状态下的存储装置101的工作模式。PMU105从这些低功耗模式选择一个工作模式,使存储装置101执行所指定的工作序列。

[0113] (位线浮动模式)

[0114] 在待机状态下,将位线对BL及BLB升压到预充电电压(Vpr1)。在位线浮动模式中,使位线对BL及BLB成为浮动状态。存储单元20的数据不消失。

[0115] (休眠模式)

[0116] 在待机状态下,向电源定域162供应电压VDM。在休眠模式中,向电源定域162供应低于电压VDM的电压VDM。电压VDM是存储单元20的数据不消失的程度的电压。使位线对BL及BLB成为浮动状态。

[0117] (单元阵列定域PG模式)

[0118] 使功率开关152、153关闭,停止向电源定域162供应电压VDM、VSM。使位线对BL及BLB成为浮动状态。存储单元20的数据消失。

[0119] (全部定域PG模式)

[0120] 全部定域PG模式是指对能够进行电源门控的全部定域进行电源门控的模式。使功率开关150、151关闭,停止向电源定域161供应电压VDD、VDH。使功率开关152、154关闭,停止向电源定域162供应电压VDM、VSM。存储单元20的数据消失。

[0121] 四个低功耗模式中的能够获得功耗降低效果的损益平衡时间(BET:break-even-time)彼此不同,并满足BET\_b1f1<BET\_s1p<BET\_pgca<BET\_pgall。BET\_b1f1、BET\_s1p、BET\_pgca及BET\_pgall分别是位线浮动模式、休眠模式、单元阵列定域PG模式及全部定域PG模式的BET。通过具有BET不同的多个低功耗模式,可以高效地降低存储装置101的功耗。

[0122] 〈电源门控序列〉

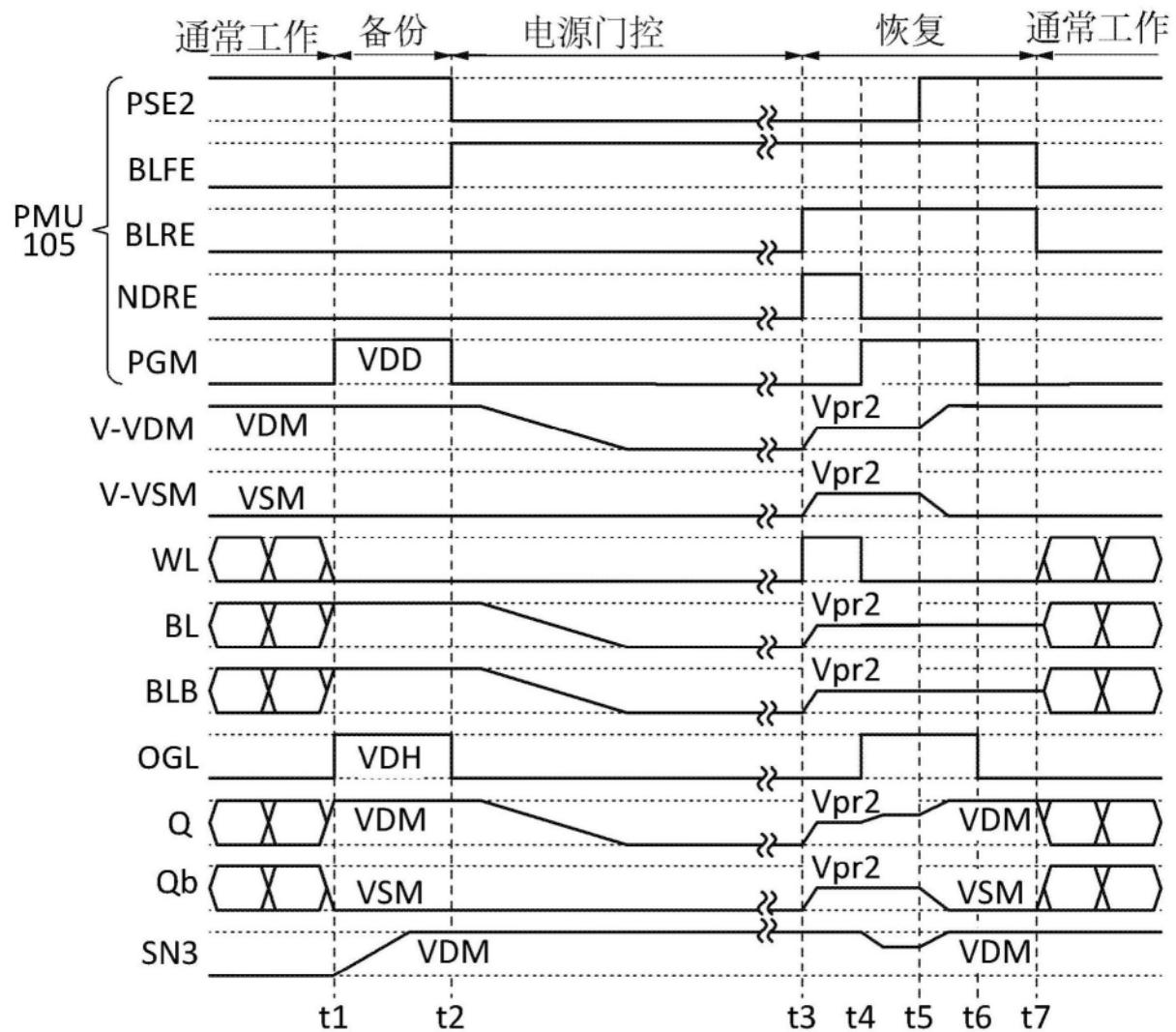

[0123] 因为各单元10中设置有备份电路30,所以能够进行电源定域162的电源门控。图2B示出电源定域162的电源门控序列的一个例子。在图2B中,t1和t2等表示时间。

[0124] (通常工作)

[0125] 在t1之前,存储装置101处于通常工作状态(写入状态或读出状态)。存储装置101进行与单端口SRAM同样的通常工作。在信号NDRE为“L”的期间,行电路123根据控制器122的控制信号进行工作。在信号BLFE、BLRE为“L”的期间,列电路124根据控制器122的控制信号进行工作。功率开关150至152处于开启状态,功率开关153处于关闭状态。

[0126] (备份)

[0127] 在t1,“H”的信号PGM被输入到备份/恢复驱动器125,由此开始备份工作。在此,t1的节点Q、Qb分别处于“H”、“L”,节点SN1、SN2分别处于“L”、“H”。由于所有布线OGL成为“H”,所以备份电路30的晶体管M01、M02成为开启状态。节点SN1的电压从VSM升压到VDM,节点SN2的电压从VDM下降到VSM。t2的信号PGM成为“L”,由此结束备份工作。t1的节点Q、Qb的数据分别被写入到节点SN1、SN2。

[0128] (电源门控)

[0129] 在t2,PMU105使信号PSE2成为“L”,使功率开关152、154关闭,由此开始电源定域162的电源门控。V\_VDM线的电压从VDM下降到VSM。当V\_VDM线与V\_VSM线之间的电压差下降时,存储单元20成为非活动状态。存储单元20的数据消失,但是备份电路30保持数据。

[0130] 在此,在电源定域162不被供应电源时,使位线对BL及BLB处于浮动状态。由此,PMU105以使信号PSE2成为“L”的时序使信号BLFE成为“H”。

[0131] 在t1之后,无论信号BLFE的逻辑如何,局部位线MUX135的晶体管MN1、MN2、MP1及MP2也处于关闭状态。通过向列电路124输入“H”的信号BLFE,预充电电路51、52成为关闭状态,因此单元阵列110的所有位线对BL及BLB成为浮动状态。

[0132] (恢复)

[0133] 恢复工作是指根据备份电路30所保持的数据对存储单元20的数据进行恢复的工作。在恢复工作中,双稳态电路25被用作检测节点Q、Qb的数据的读出放大器。

[0134] 首先,进行节点Q、Qb的复位工作。在t3,PMU105使信号BLRE、NDRE成为“H”。

[0135] 列电路124根据“H”的信号BLFE、BLRE对所有位线对BL及BLB进行预充电工作。具体而言,使预充电电路51关闭,使预充电电路52开启。因为局部位线MUX135的晶体管MN1、MN2、MP1及MP2处于关闭状态,将所有位线对BL及BLB预充电到电压Vpr2。

[0136] 行电路123根据“H”的信号NDRE选择所有字线WL。将V\_VDM线和V\_VSM线预充电到电

压Vpr2,将节点Q、Qb的电压固定为Vpr2。

[0137] 在t4,PMU105使信号PGM成为“H”,由此晶体管M01、M02成为开启状态。电容器C1的电荷分配于节点Q和节点SN1,电容器C2的电荷分配于节点Qb和节点SN2,在节点Q与节点Qb之间产生电压差。

[0138] 在t5,使功率开关152、154开启,再次开始向电源定域162输入电压VDM、VSM。当双稳态电路25成为活动状态时,增大节点Q与节点Qb之间的电压差。最终,节点Q、SN1的电压成为VDM,节点Qb、SN2的电压成为VSM。也就是说,节点Q、Qb的状态恢复到t1的状态,即“H”、“L”。在t6,PMU105使信号PGM成为“L”,在t7,使信号BLFE、BLRE成为“L”。在t7,结束恢复工作。

[0139] 下面,说明存储装置的其他结构实例。

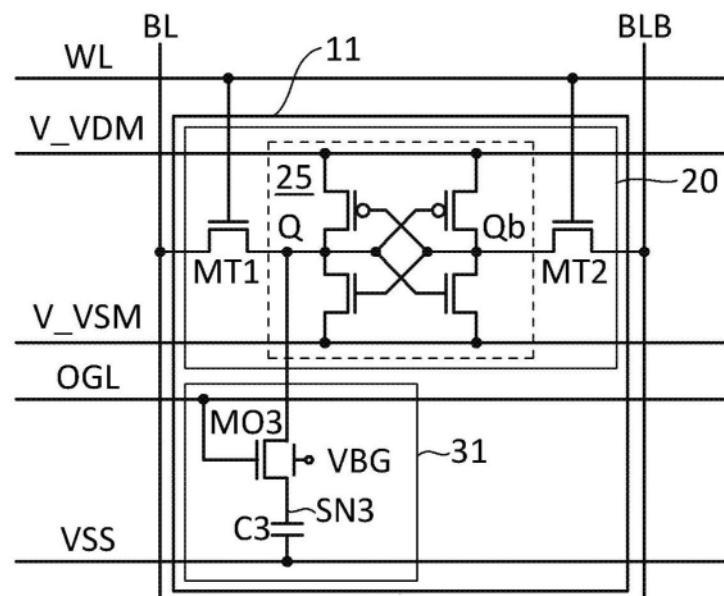

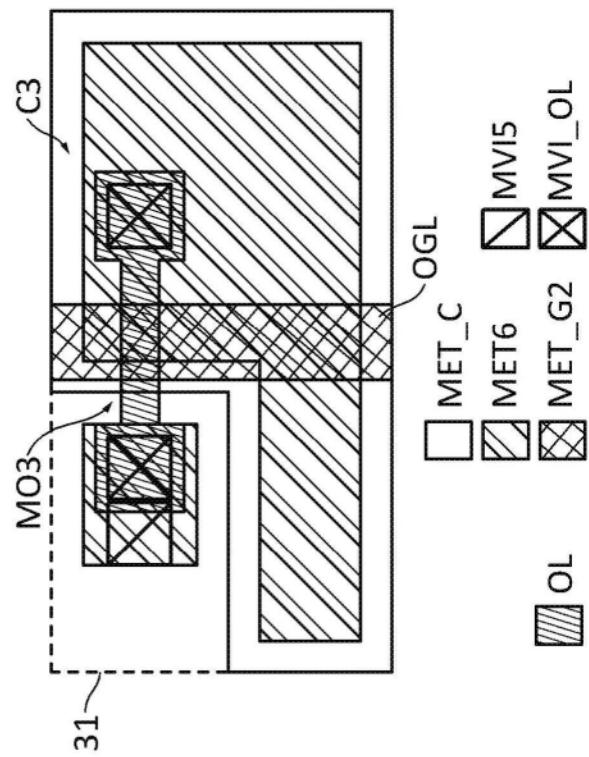

[0140] 图5A示出单元的其他的电路结构实例。图5A所示的单元11包括存储单元20及备份电路31。

[0141] 备份电路31由一个1T1C型DRAM单元构成。备份电路31包括节点SN3、晶体管M03及电容器C3。与晶体管M01、M02同样,晶体管M03是包括背栅极的OS晶体管。晶体管M03的背栅极电连接于VBG线。晶体管M03也可以是不包括背栅极的OS晶体管。

[0142] 可以由单元11构成单元阵列110。图5B示出该结构实例中的电源定域162的电源门控序列的一个例子。图5B所示的电源门控序列与上述电源门控序列同样,因此图5B的说明可以援用图2B的说明。

[0143] 虽然备份电路31只对节点Q的数据进行备份,但是可以利用节点SN3的保持数据对节点Q、Qb的数据进行恢复。这是因为预先将节点Q、Qb的电压预充电到Vpr2的缘故,由此可以使用一个电容器C3的电荷在节点Q与节点Qb之间产生电位差。

[0144] 在使用单元10构成单元阵列110的情况下,可以采用在存储装置101中不设置功率开关154的结构。此时,不通过功率开关而向电源定域162输入电压VSM。单元10的双稳态电路与供应电压VSM的电源线(VSM线)电连接(参照图6A)。

[0145] 图6B示出该结构实例中的电源定域162的电源门控序列的一个例子。图6B的说明可以援用图2B的说明。图6B的电源门控序列的与图2B的电源门控序列不同之处在于:在恢复工作中不进行节点Q、Qb的预充电。

[0146] 单元10、11具有标准的6T型SRAM单元与备份电路电连接的电路结构。当使用单元10时,发生如下问题:由于将备份电路安装于SRAM单元而存储单元20的面积开销增加。使用单元11的情况也发生相同的问题。下面,说明可以使面积开销成为0的单元10、11的布局实例。

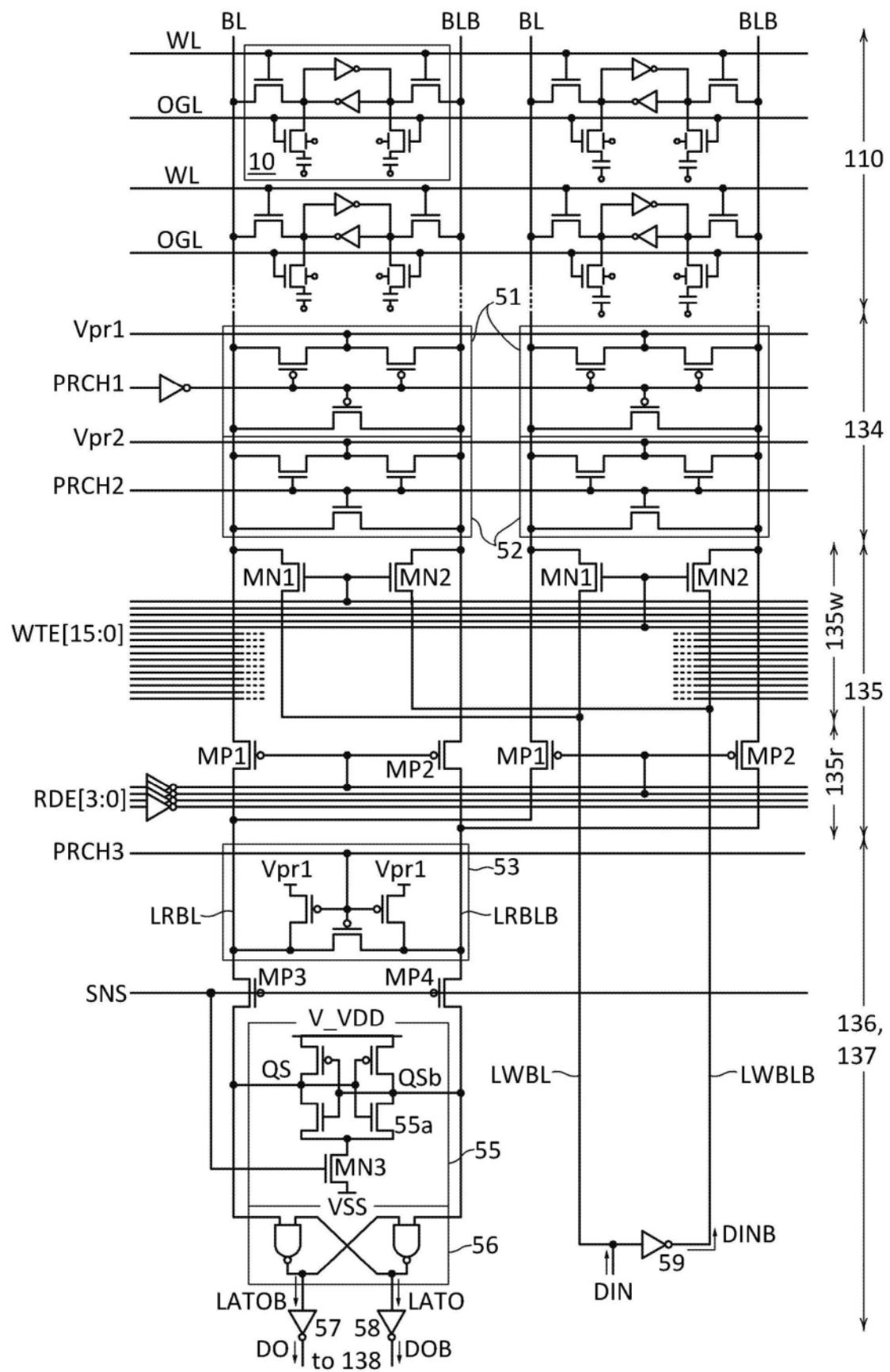

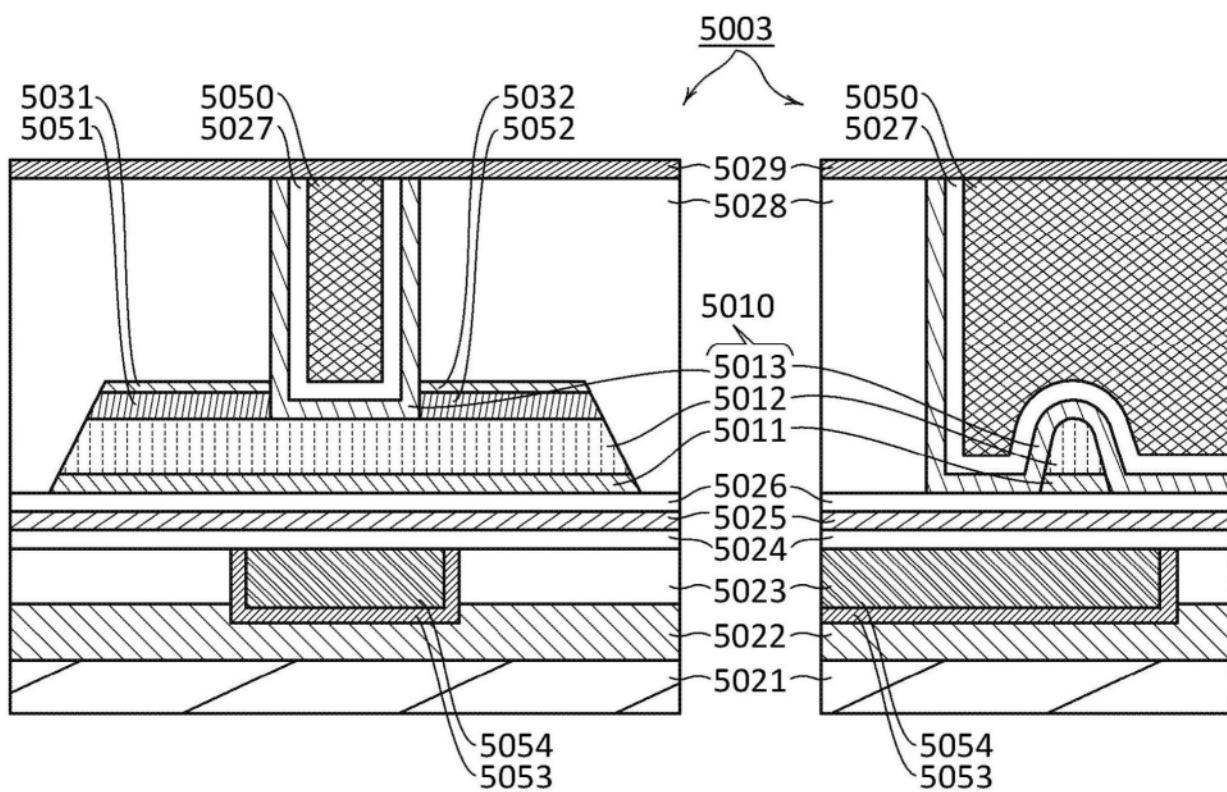

[0147] 《布局实例1》

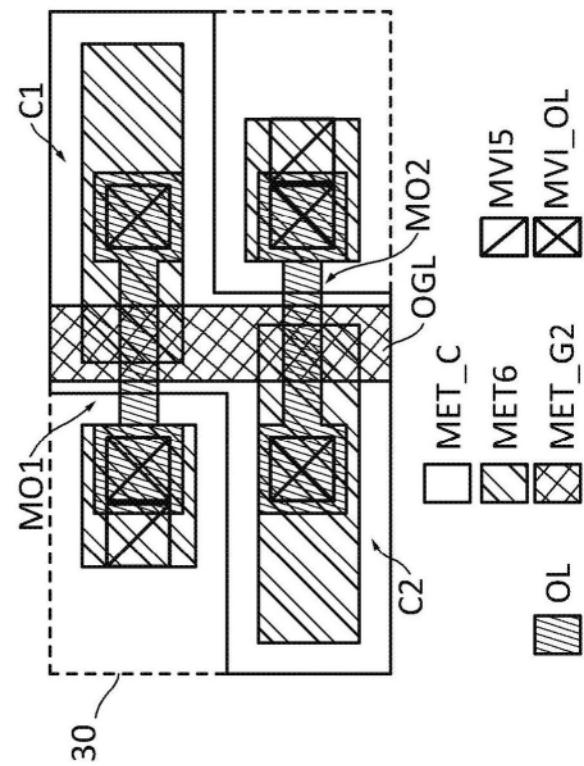

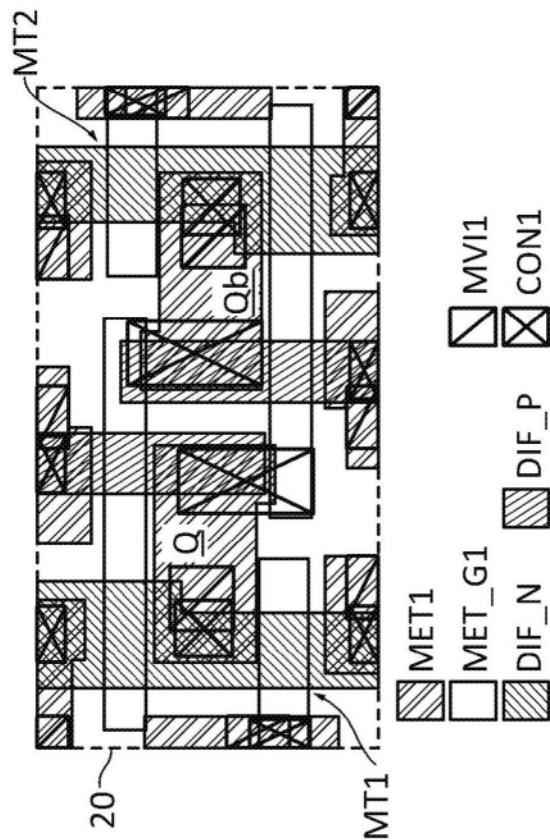

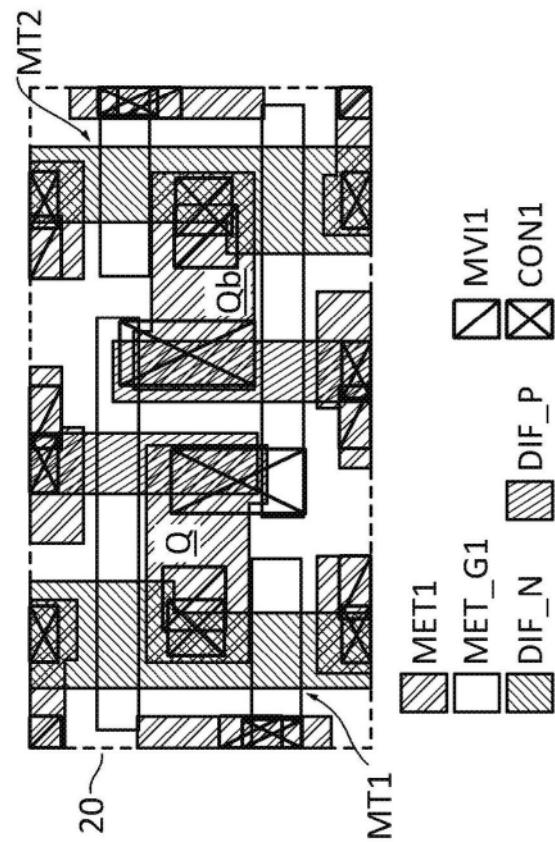

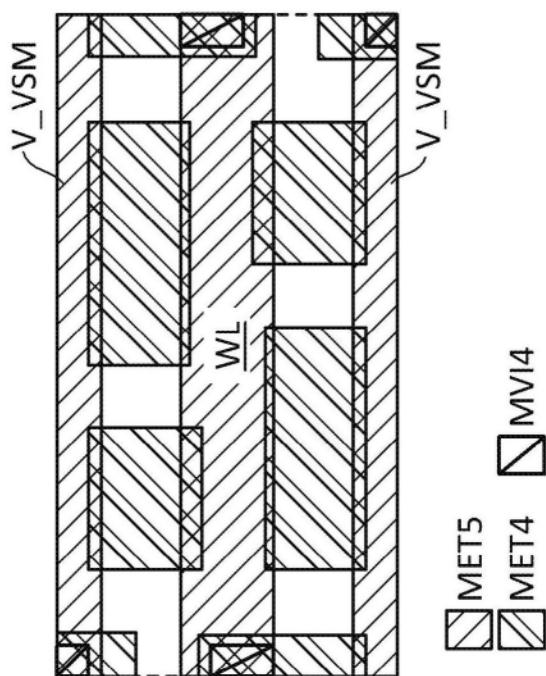

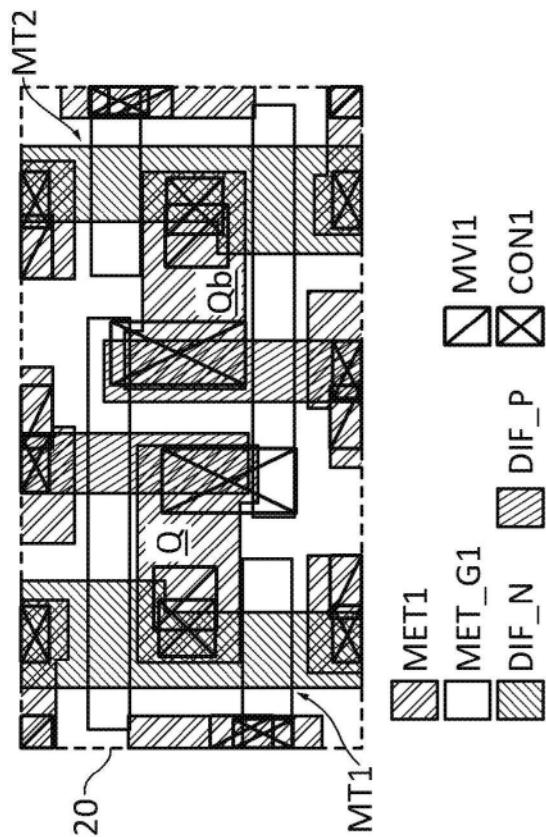

[0148] 参照图7A至图7D说明单元10的布局实例。单元10具有将备份电路30层叠在存储单元20上而成的3D结构。图7A是存储单元20的布局图,图7D是备份电路30的布局图。图7B是位线BL、BLB和V\_VDM线的布局图,图7C是字线WL、VSS线的布局图。依次层叠图7A到图7D的层。

[0149] 在图7A中,扩散层DIF\_N是n型扩散层,扩散层DIF\_P表示p型扩散层。布线层MET\_G1是设置有存储单元20的Si晶体管的栅电极的层。布线层MET1位于布线层MET\_G1的上方,并设置有Si晶体管的源电极及漏电极。导通孔CON1中形成有使扩散层DIF\_N、DIF\_P与布线层MET1、MET\_G1之间电连接的插头。

[0150] 布线层MET1上依次层叠布线层MET2到布线层MET5。导通孔MVI1形成在布线层MET1与布线层MET2之间,导通孔MVI2形成在布线层MET2与布线层MET3之间,导通孔MVI3形成在布线层MET3与布线层MET4之间,导通孔MVI4形成在布线层MET4与布线层MET5之间。导通孔MVI1至MVI4中都设置有插头。

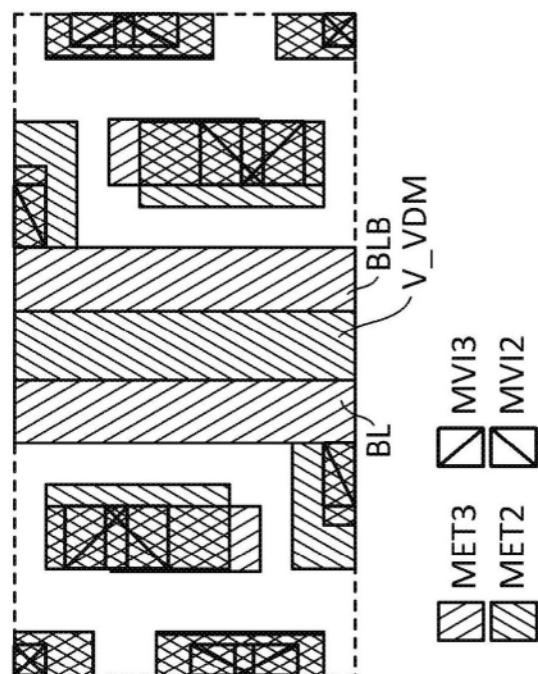

[0151] 如图7B所示,V\_VDM线设置在布线层MET2中,位线对BL及BLB设置在布线层MET3中。如图7C所示,字线WL设置在布线层MET4中,V\_VSM线(或VSM线)和布线BGL设置在布线层MET5中。

[0152] 参照图7D说明备份电路30的布局实例。布线层MET5上层叠有层OL。布线层MET\_G2、MET6及MET\_C层叠在层OL上。导通孔MVI5中设置有使布线层MET5与布线层MET6之间电连接的插头,导通孔MVI\_OL中设置有使层OL与布线层MET6之间电连接的插头。

[0153] 层OL中设置有晶体管M01、M02(晶体管M01、M02都是OS晶体管)的活性层。布线层MET\_G2中设置有布线OGL。布线层MET6中设置有晶体管M01、M02的源电极及漏电极。电容器C1、C2的两个电极中的一个设置在布线层MET6中,另一个设置在布线层MET\_C中。

[0154] 在布局实例1中,V\_VDM线、V\_VSM线及布线BGL、OGL与位线BL、BLB同样地在列方向上延伸。字线WL在各存储单元20中包括两个弯曲部。

[0155] (叠层结构)

[0156] 图11示出单元10的叠层结构实例。图11示出晶体管MT1、M01、电容器C1作为典型的构成要素。注意,图11是用来说明单元10的叠层结构实例的截面图,而不是沿着特定的切断线切断图7A至图7D的布局图的截面图。

[0157] 单元10制造在单晶硅片5500上。晶体管M01的结构与后述的OS晶体管5004(参照图19B)同样。如上所述,V\_VDM线设置在布线层MET2中,V\_VSM线设置在布线层MET5中。位线BL设置在布线层MET3中,字线WL设置在布线层MET4中。

[0158] 在单元10中,因为备份电路31的元件数少于存储单元20,所以容易使备份电路31的面积小于存储单元20的面积。然而,当为了将备份电路31电连接于节点Q、Qb而改变存储单元20的布局时,面积增加的问题明显化。以专利文献3为例说明该问题。

[0159] 为了减少SRAM的每位单价,有面积的缩小、面积效率的提高的需求。因此,SRAM的单元阵列中以极高的密度配置有字线、位线对及电源线。例如,在专利文献3的图1和图2所示的SRAM单元的布局MC中,第二层中的金属布线层中设置有字线WD,第三层中的金属布线层中设置有位线对BL1及BL2和电源线Vss1、Vcc1及Vss2。为了连接专利文献3的SRAM单元与备份电路30需要改变布局MC,这导致SRAM单元的面积增加。

[0160] 针对于此,在本实施方式的布局实例中,通过将字线WL、位线对BL及BLB、V\_VDM线及V\_VSM线设置在不同的布线层中,即使将备份电路30安装在存储单元20中也可以使存储单元20的面积开销成为0。

[0161] 图7A至图7D是根据技术节点65nm的设计规则而设计的布局实例。存储单元20的面积为 $134.20F^2$  ( $0.567\mu\text{m}^2 = 0.54\mu\text{m} \times 1.05\mu\text{m}$ )。F为最小加工尺寸。在利用使布线的宽度、布线间的距离等最优化的尺寸进行设计的情况下,存储单元20的面积为 $124.26F^2$  ( $0.525\mu\text{m}^2 = 0.50\mu\text{m} \times 1.05\mu\text{m}$ )。本实施方式的布局实例的存储单元20的面积比最优化的布局大8%。

[0162] 图7A所示的存储单元20的行方向的长度比最优化的布局长 $0.04\mu\text{m}$ ,以设置制造工序的余地。因此,通过改善制造工序,可以使面积开销成为0。

[0163] 在以下所示的布局实例2至4中,存储单元20的布局及面积与布局实例1相同。

[0164] 《布局实例2》

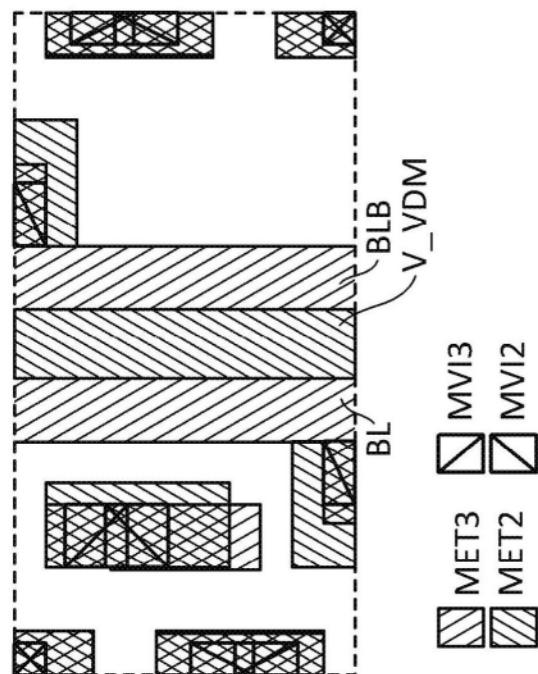

[0165] 可以与单元10同样地设计单元11。图8A至图8D示出单元11的布局实例。图8A至图8D的说明援用图7A至图7D的说明。

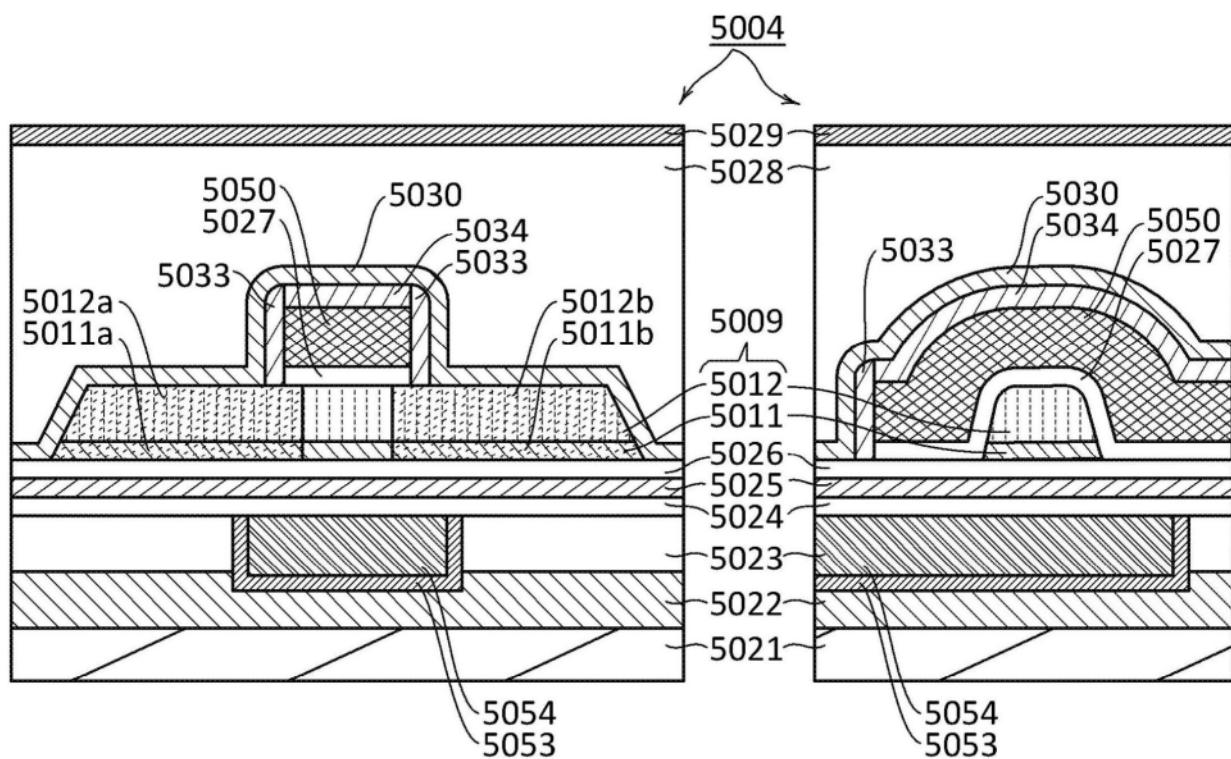

[0166] 《布局实例3》

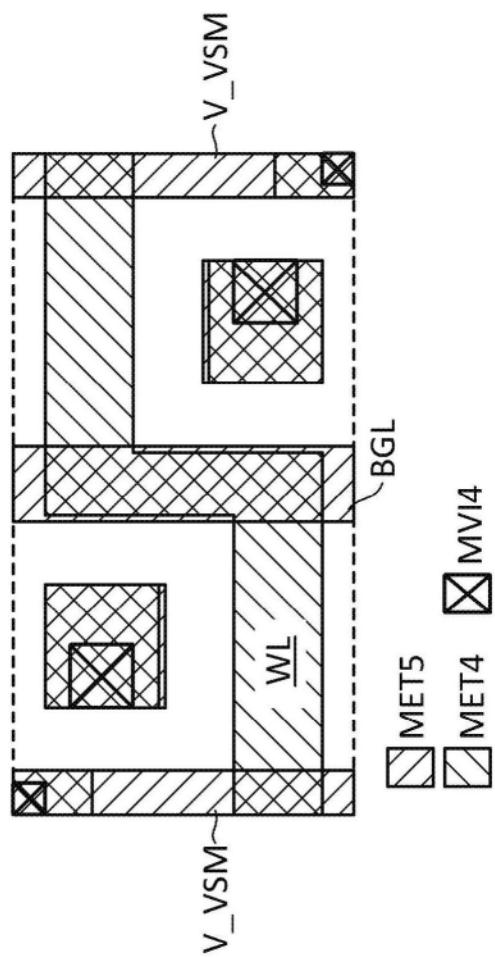

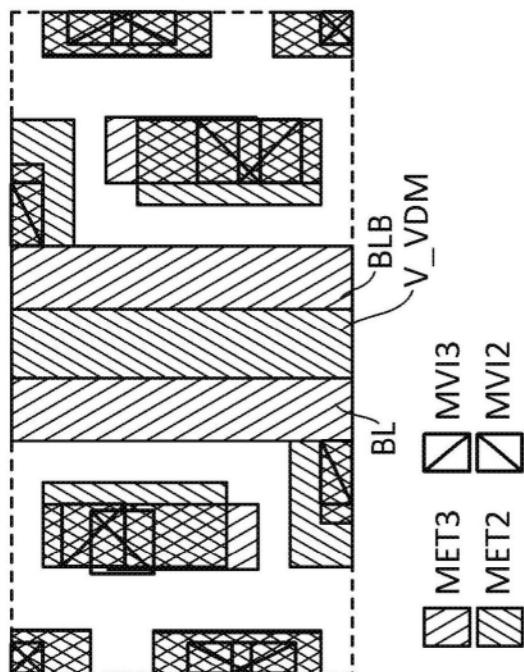

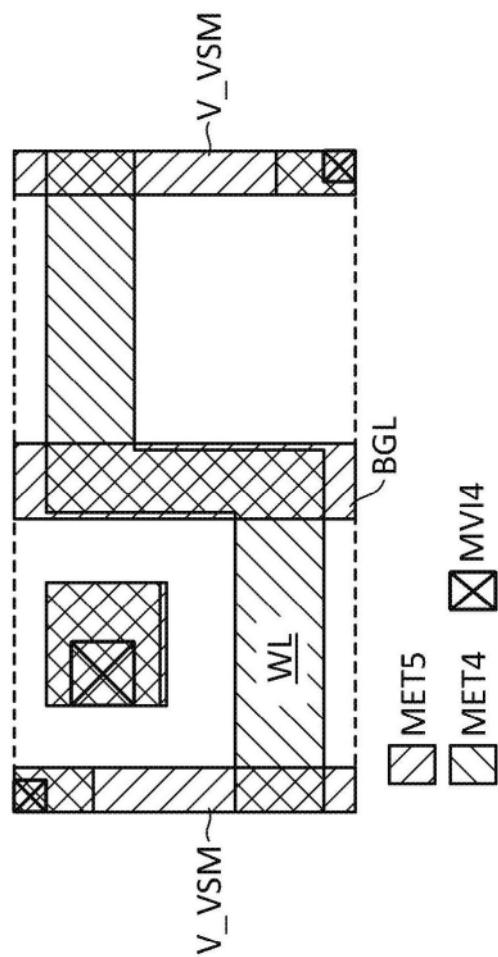

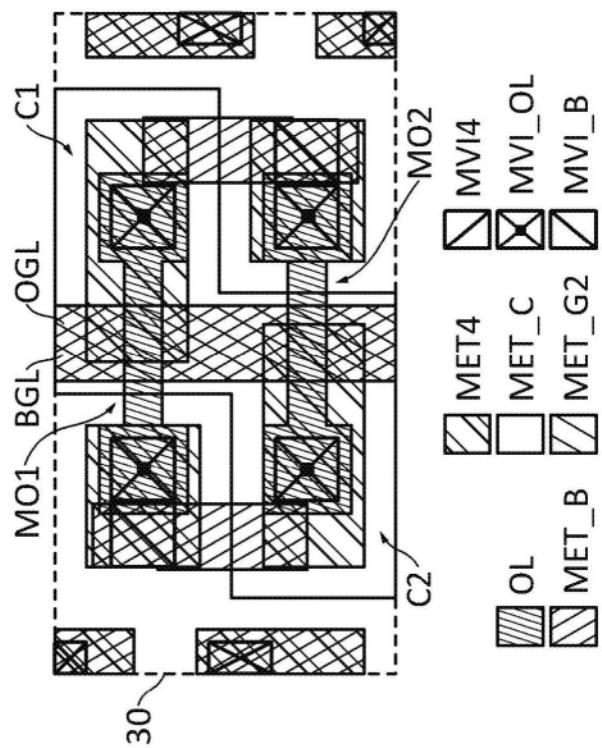

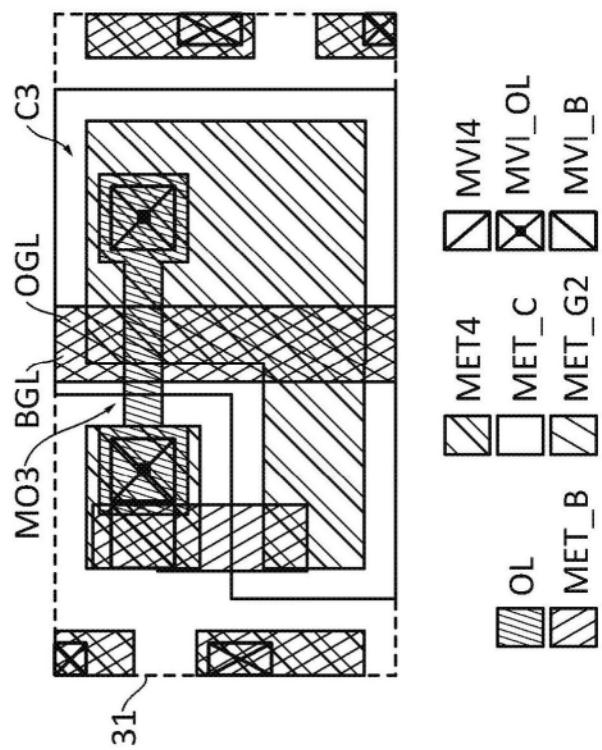

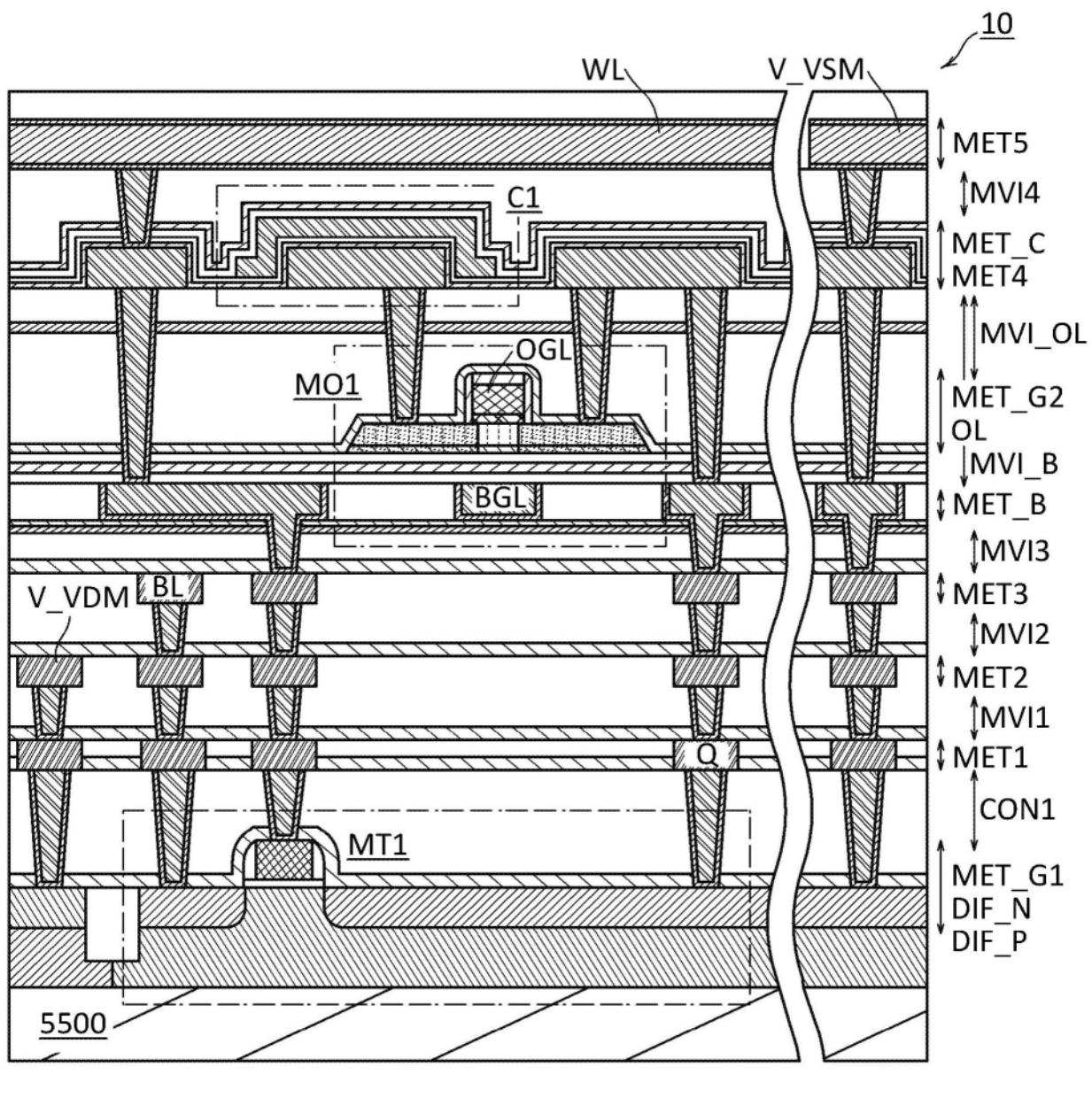

[0167] 在布局实例1中,字线WL、位线对BL及BLB、V\_VDM线及V\_VSM线设置在存储单元20与备份电路30之间。可以将这些布线中的一个或多个设置在备份电路30的上方的布线层中。图9A至图9D示出这样的布局实例。图12示出对应于布局实例3的单元10的叠层结构实例。

[0168] 在布局实例3中,布线层MET1至MET3设置在布线层MET\_G1与层OL之间。布线层MET4设置在布线层MET\_G2与布线层MET\_C之间。布线层MET5层叠在布线层MET\_C上。

[0169] 图9A是与图7A相同的存储单元20的布局图。图9B是与图7B相同的位线BL、BLB和V\_VDM线的布局图。

[0170] 图9C是备份电路30的布局图。布线层MET3与层OL之间设置有布线层MET\_B。导通孔MVI3中设置有使布线层MET3与布线层MET\_B电连接的插头。布线层MET\_B中设置有布线BGL,布线层MET\_G2中设置有布线OGL。布线层MET4中设置有晶体管M01、M02的源电极及漏电极。电容器C1、C2的两个电极中的一个设置在布线层MET4中,另一个设置在布线层MET\_C中。导通孔MVI\_B中设置有使布线层MET\_B与布线层MET4电连接的插头,导通孔MVI\_OL中设置有使层OL与布线层MET4电连接的插头。

[0171] 当晶体管M01、M02不包括背栅极时,不需要形成布线层MET\_B、导通孔MVI\_B。在此情况下,导通孔MVI3中设置有使布线层MET3与布线层MET4电连接的插头。

[0172] 图9D是字线WL和V\_VSM线的布局图。字线WL和V\_VSM线设置在布线层MET5中。

[0173] 布局实例3的与布局实例1相同之处在于:位线对BL及BLB、V\_VDM线设置在存储单元20与备份电路30之间;设置有位线对BL及BLB的布线层中不设置有字线WL、V\_VDM线及V\_VSM线。

[0174] 布局实例3的与布局实例1不同之处在于:字线WL与V\_VSM线层叠在备份电路30上且设置在同一布线层中;字线WL不包括弯曲部;V\_VSM线与字线WL同样地在行方向上延伸。

[0175] 《布局实例4》

[0176] 可以与布局实例3的单元10同样地设计单元11。图10A至图10D示出单元11的布局实例。图10A至图10D的说明援用图9A至图9D的说明。

[0177] 本实施方式的存储装置可以被用作各种电子构件及电子装置中的存储装置。本实施方式的存储装置除了两种电源门控模式之外还具有其BET比电源门控模式短的多个低功耗模式,由此可以高效地降低安装有本实施方式的存储装置的电子构件及电子装置的功耗。

[0178] 为了减少存储装置的每位单价,有存储单元的面积的缩小、面积效率的提高的需求。通过使用本实施方式,可以提供能够进行备份的存储装置,而不使存储单元的面积增加。因此,根据本实施方式,可以提供低功耗且低成本的大容量存储装置。

[0179] [实施方式2]

[0180] 实施方式1的存储装置典型为可代替SRAM的存储装置。例如,可以在微控制单元(MCU)、FPGA、CPU及GPU等各种处理器中组装实施方式1的存储装置代替SRAM。此外,也可以

将实施方式1的存储装置组装于无线IC、显示控制器IC、源极驱动器IC及影像用译码器IC等各种IC中。在本实施方式中,作为一个例子,说明在一个芯片上安装有处理器核心和高速缓冲存储器的处理器。

[0181] 《处理器》

[0182] 图13是示出处理器的结构实例的方框图。图13所示的处理器300包括PMU305、总线306、高速缓冲存储器320、CPU核心330、备份/恢复驱动器311及功率开关390至394、398、399。

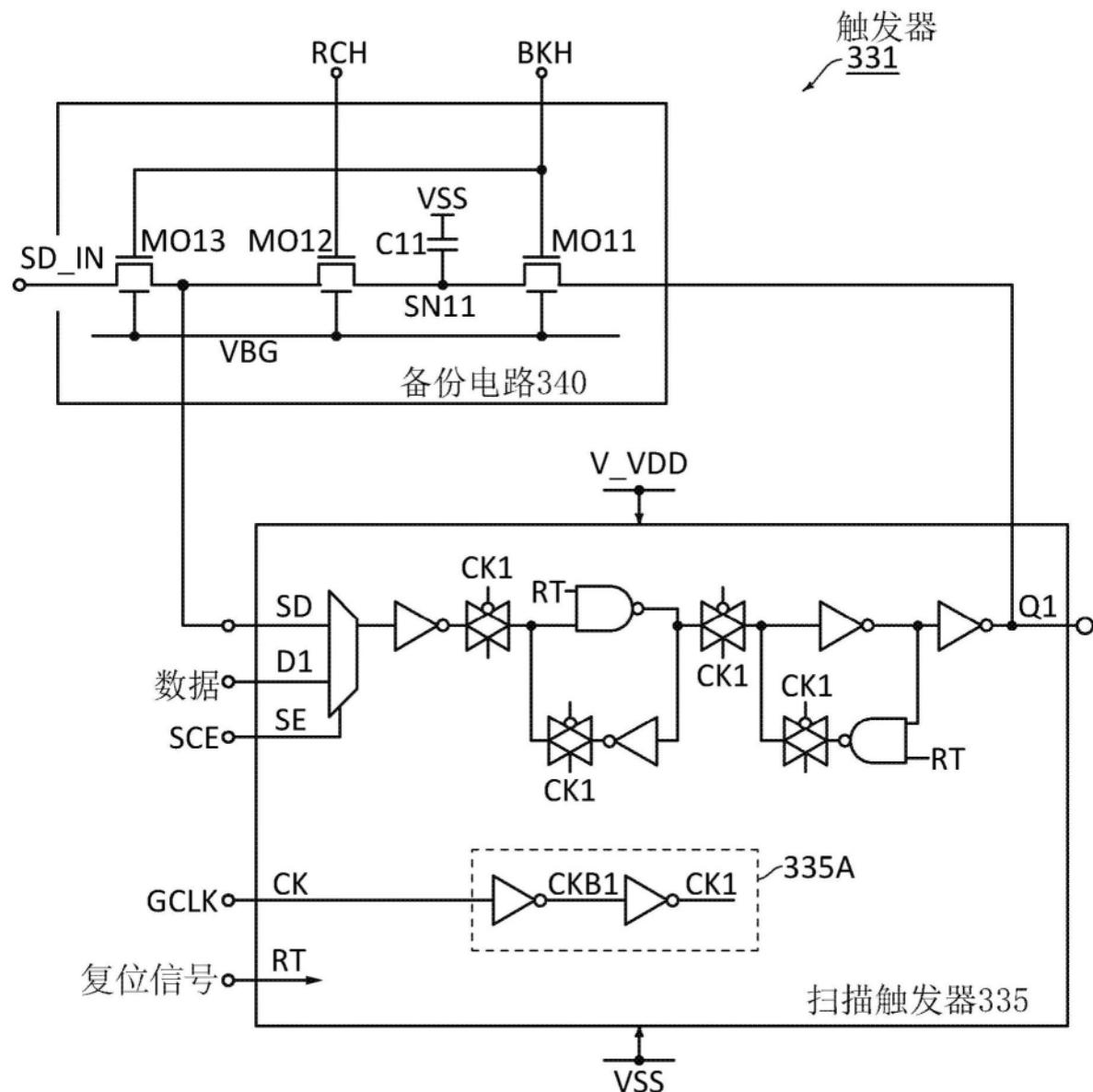

[0183] CPU核心330与高速缓冲存储器320之间的数据及信号传送通过总线306进行。CPU核心330包括触发器331和组合电路332。例如,触发器331包括在寄存器中。通过在触发器331中设置备份电路,能够进行CPU核心330的电源门控。

[0184] 在此,将图1的存储装置101用作高速缓冲存储器320。当然,可以将存储装置100用作高速缓冲存储器320。

[0185] 高速缓冲存储器320包括单元阵列321和外围电路322。外围电路322包括控制器324、备份/恢复驱动器325、行电路326及列电路327。功率开关390至394对应于存储装置101的功率开关150至154。PMU305具有与存储装置101的PMU105同样的功能并生成信号PSE1至PSE3、PGM、BLFE、BLRE及NDRE。

[0186] PMU305使用从外部输入的时钟信号CLK2生成时钟信号GCLK。时钟信号GCLK被输入到高速缓冲存储器320和CPU核心330。PMU305生成信号PSE8、SCE、BK及RC。信号PSE8、BK及RC是对于CPU核心330的电源门控控制信号。

[0187] 信号PSE8是控制功率开关398、399的开启/关闭的功率开关使能信号。功率开关398控制向CPU核心330的电压VDD供应,功率开关399控制向备份/恢复驱动器311的电压VDH供应。

[0188] 信号SCE是扫描使能信号,并输入到触发器331。

[0189] 备份/恢复驱动器311根据信号BK、RC控制触发器331的备份电路。信号BK为备份信号,信号RC为恢复信号。备份/恢复驱动器311对信号BK、RC进行电平移位以生成信号BKH、RCH。信号BKH、RCH被输入到触发器331的备份电路。电压VDH是信号BKH、RCH的高电平电压。

[0190] PMU305根据从外部输入的中断信号INT2、CPU核心330所发出的SLEEP信号生成时钟信号GCLK及各种控制信号。例如,可以将SLEEP信号用作使CPU核心330转移到电源门控模式的触发信号。

[0191] 《触发器331》

[0192] 图14示出触发器331的电路结构实例。触发器331包括扫描触发器335、备份电路340。

[0193] 电压VDD、VSS通过CPU核心330内的V\_VDD线和VSS线输入到扫描触发器335。扫描触发器335包括节点D1、Q1、SD、SE、RT、CK和时钟缓冲器电路335A。

[0194] 节点D1是数据输入节点,节点Q1是数据输出节点,节点SD是扫描测试数据的输入节点。节点SE是信号SCE的输入节点。节点CK是时钟信号GCLK的输入节点。时钟信号GCLK被输入到时钟缓冲器电路335A。扫描触发器335的模拟开关分别电连接于时钟缓冲器电路335A的节点CK1、CKB1。节点RT是复位信号的输入节点。

[0195] 扫描触发器335的电路结构不局限于图14所示的电路结构。可以使用在标准的电

路库中准备的扫描触发器。

[0196] 〈备份电路340〉

[0197] 备份电路340包括节点SD\_IN、SN11、晶体管M011至M013及电容器C11。

[0198] 节点SD\_IN是扫描测试数据的输入节点，并电连接于其他扫描触发器335的节点Q1。节点SN11是备份电路340的保持节点。电容器C11电连接于VSS线及节点SN11。

[0199] 晶体管M011控制节点Q1与节点SN11之间的导通状态。晶体管M012控制节点SN11与节点SD之间的导通状态。晶体管M013控制节点SD\_IN与节点SD之间的导通状态。晶体管M011、M013的开启/关闭被信号BKH控制，晶体管M012的开启/关闭被信号RCH控制。

[0200] 与晶体管M01同样，晶体管M011至M013为包括背栅极的OS晶体管。晶体管M011至M013的背栅极电连接于CPU核心330内的VBG线。优选的是，晶体管M011、M012至少为OS晶体管。由于OS晶体管的关态电流极小的特征，因此可以抑制节点SN11的电压下降，在保持数据时几乎不耗电，所以备份电路340可以长时间保持数据，即具有非易失性。因此，在CPU核心330处于电源门控状态的期间，备份电路340可以保持数据。

[0201] 《CPU核心330的低功耗模式》

[0202] CPU核心330可以被设定为时钟门控模式、电源门控模式作为低功耗模式。PMU305根据信号INT2、SLEEP信号选择CPU核心330的低功耗模式。通过使PMU305停止信号GCLK的生成，可以使CPU核心330的状态成为时钟门控状态。

[0203] 在使CPU核心330从通常工作状态转移到电源门控状态时将触发器331的数据备份到备份电路340。在使CPU核心330从电源门控状态恢复到通常工作状态时进行将备份电路340的数据再次写入到触发器331的恢复工作。下面，参照图15说明CPU核心330的电源门控序列的一个例子。

[0204] (通常工作)

[0205] 在t1之前，触发器331进行通常工作。PMU305输出“L”的信号SCE、BK及RC。在此，在t1，备份电路340的节点SN11为“L”。由于节点SE为“L”，扫描触发器335储存节点D1的数据。

[0206] (备份)

[0207] 在t1，PMU305停止时钟信号GCLK，使信号BK成为“H”。晶体管M011成为开启状态，扫描触发器335的节点Q1的数据写入到备份电路340的节点SN11。若扫描触发器335的节点Q1为“L”，节点SN11则保持“L”，若节点Q1为“H”，节点SN11则成为“H”。

[0208] 在t2，PMU305使信号BK成为“L”，在t3，PMU305使信号PSE8成为“L”。在t3，CPU核心330的状态转移到电源门控状态。可以使信号BK下降的时序使信号PSE8下降。

[0209] (电源门控)

[0210] 在信号PSE8成为“L”时，功率开关398、399成为关闭状态。因为V\_VDD线的电压下降，节点Q1的数据消失。节点SN11保持t1的节点Q1的数据。

[0211] (恢复)

[0212] 在t4，PMU305使信号PSE8成为“H”，因此CPU核心330从电源门控状态转移到恢复状态。开始V\_VDD线的充电。在V\_VDD线的电压为VDD的状态下(t5)，PMU305使信号RC、SCE成为“H”。

[0213] 因为信号RCH成为“H”，所以晶体管M012成为开启状态，电容器C11的电荷分配于节点SN11和节点SD。若节点SN11是“H”，节点SD的电压则上升。因为节点SE是“H”，节点SD的数

据被写入到扫描触发器335的输入侧锁存电路。在t6,向节点CK输入时钟信号GCLK,输入侧锁存电路的数据被写入到节点Q1。也就是说,节点SN11的数据被写入到节点Q1。

[0214] 在t7,PMU305使信号SCE、RC成为“L”,由此结束恢复状态。

[0215] 由于本实施方式的处理器的处理器核心及存储装置中都设置有备份电路,所以可以高效地降低处理器整体的功耗。

[0216] [实施方式3]

[0217] 在本实施方式中,作为半导体装置的一个例子,对IC芯片、电子构件及电子装置等进行说明。

[0218] 《电子构件的制造方法例子》

[0219] 图16A是示出电子构件的制造方法例子的流程图。电子构件也被称为半导体封装或IC用封装等。

[0220] 通过组装工序(后工序),在印刷电路板上集成多个能够装卸的构件,可以形成包括晶体管的半导体装置。在前工序中,在半导体晶片(例如,硅片)上形成本发明的一个实施方式的半导体装置等。后工序可以通过进行图16A所示的各工序完成。

[0221] 在后工序中,首先,进行对半导体晶片的背面(没有形成半导体装置等的面)进行研磨的背面研磨工序(步骤SP71)。该步骤的目的是通过研磨减薄半导体晶片,实现电子构件的小型化。在步骤SP71之后,进行将半导体晶片分为多个芯片的切割工序(步骤SP72)。在切割工序中,通过沿着分离线切割半导体晶片,从半导体晶片切割出芯片。

[0222] 进行拾取分离后的芯片并将其接合于引线框架上的芯片接合工序(步骤SP73)。芯片接合工序中的芯片与引线框架的接合方法可以选择适合产品的方法,例如,使用树脂或胶带进行接合的方法。另外,也可以将芯片接合于插入物衬底上,而不接合于引线框架。

[0223] 接着,进行将引线框架的引线与芯片上的电极通过金属细线电连接的引线键合工序(步骤SP74)。作为金属细线可以使用银线或金线等。引线键合例如可以使用球键合或楔键合进行。对引线键合后的芯片7110进行由环氧树脂等密封的模塑工序(步骤SP75)。

[0224] 接着,进行对引线框架的引线进行电镀处理的引线电镀处理(步骤SP76)。进行对引线进行切断及成型加工的成型工序(步骤SP77)。进行对封装表面实施印字处理的印字工序(步骤SP78)。然后,通过进行检验外观形状的优劣或工作故障的有无等的检验工序(步骤SP79)完成电子构件。

[0225] 图16B是完成的电子构件的立体示意图。电子构件根据端子取出方向或端子的形状具有多个不同规格和名称。在图16B中,作为电子构件的一个例子,示出四侧引脚扁平封装(QFP)。

[0226] 图16B所示的电子构件7000包括引线7001及芯片7110。在芯片7110中设置有本实施方式的存储装置或安装有该存储装置的处理器。

[0227] 电子构件7000可以包括多个芯片7110。电子构件7000例如安装于印刷电路板7002上。通过组合多个这样的电子构件7000并使其在印刷电路板7002上彼此电连接,完成安装有电子构件的电路板(电路板7004)。电路板7004用于电子装置等。

[0228] 由于电子构件7000安装有低功耗的存储装置,所以通过将电子构件7000组装于电子装置,可以降低电子装置的功耗。接着,说明具备上述电子构件的电子装置。

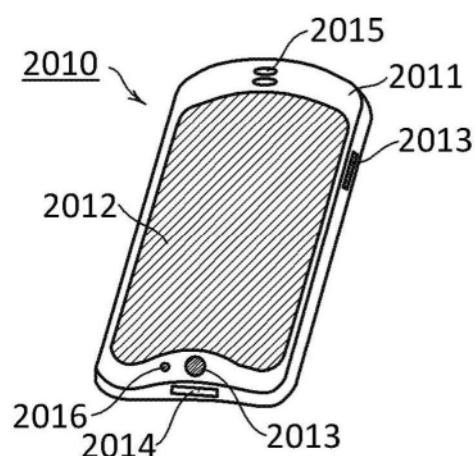

[0229] 图17A所示的信息终端2010除了安装在外壳2011中的显示部2012以外还包括操作

按钮2013、外部连接端口2014、扬声器2015、麦克风2016。在此，显示部2012的显示区域是弯曲的。信息终端2010是用电池驱动的便携式信息终端，可以被用作平板信息终端或智能手机。信息终端2010具有电话、电子邮件、笔记本、上网、音乐播放等功能。通过用手指等触摸显示部2012可以输入信息。通过用手指等触摸显示部2012，可以进行打电话、输入文字、显示部2012的屏面切换工作等各种操作。还可以通过从麦克风2016输入声音，进行信息终端2010的操作。通过按操作按钮2013，可以进行电源的开启/关闭工作、显示部2012的屏面切换工作等各种操作。

[0230] 图17B所示的笔记本型PC2050包括外壳2051、显示部2052、键盘2053、指向装置2054。通过显示部2052的触摸操作，可以操作笔记本型PC2050。

[0231] 图17C所示的摄像机2070包括外壳2071、显示部2072、外壳2073、操作键2074、透镜2075、连接部2076。显示部2072设置在外壳2071中，操作键2074及透镜2075设置在外壳2073中。外壳2071和外壳2073由连接部2076连接，由连接部2076可以改变外壳2071和外壳2073之间的角度。可以采用根据连接部2076处的外壳2071和外壳2073之间的角度切换显示部2072的图像的结构。通过显示部2072的触摸操作，可以进行录像的开始及停止的操作、放大倍率的调整、摄像范围的改变等各种操作。

[0232] 图17D所示的便携式游戏机2110包括外壳2111、显示部2112、扬声器2113、LED灯2114、操作键按钮2115、连接端子2116、照相机2117、麦克风2118及记录介质读取部2119。

[0233] 图17E所示的电冷藏冷冻箱2150包括外壳2151、冷藏室门2152及冷冻室门2153等。

[0234] 图17F所示的汽车2170包括车体2171、车轮2172、仪表盘2173及灯2174等。

[0235] [实施方式4]

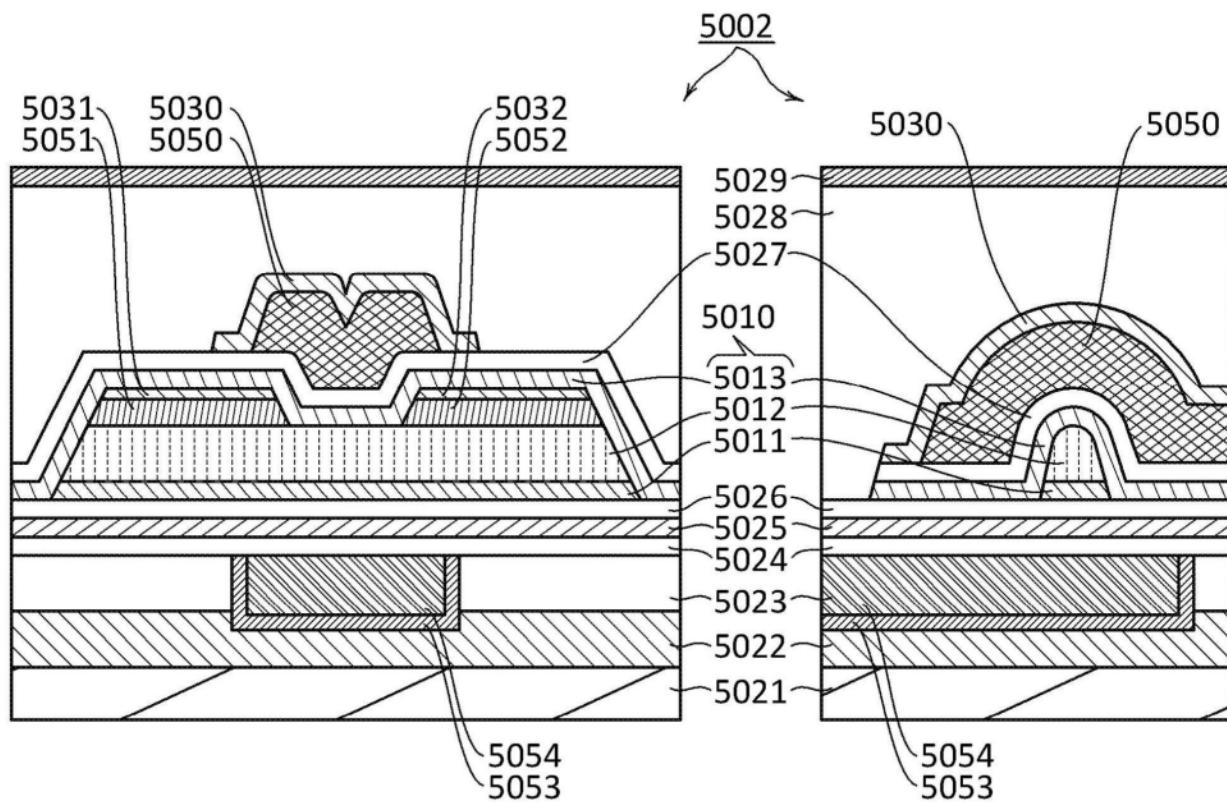

[0236] 参照图18A至图19B说明OS晶体管的结构实例。图18A至图19B的左侧示出OS晶体管的沟道长度方向的截面结构，右侧示出OS晶体管的沟道宽度方向的截面结构。

[0237] 《OS晶体管的结构实例1》

[0238] 图18A所示的OS晶体管5001形成在绝缘表面上。在此，OS晶体管5001形成在绝缘层5021上。OS晶体管5001被绝缘层5028及5029覆盖。OS晶体管5001包括绝缘层5022至5027、5030至5032、金属氧化物层5011至5013以及导电层5050至5054。

[0239] 附图中的绝缘层、金属氧化物层、导电层等可以为单层或叠层。在制造这些层时，可以使用溅射法、分子束外延(MBE)法、脉冲激光烧蚀(PLA)法、化学气相沉积(CVD)法、原子层沉积(ALD)法等各种沉积方法。CVD法包括等离子体增强CVD法、热CVD法及有机金属CVD法等。

[0240] 将金属氧化物层5011至5013总称为氧化物层5010。如图18A所示，氧化物层5010包括依次层叠有金属氧化物层5011、金属氧化物层5012及金属氧化物层5013的部分。在OS晶体管5001处于导通状态时，沟道主要形成在氧化物层5010的金属氧化物层5012中。

[0241] OS晶体管5001的栅电极由导电层5050构成，用作源电极或漏电极的一对电极由导电层5051、5052构成。导电层5050至5052被作为阻挡层的绝缘层5030至5032覆盖。OS晶体管5001的背栅电极由导电层5053和导电层5054的叠层构成。OS晶体管5001也可以不包括背栅电极。后述的OS晶体管5002也是同样的。

[0242] 栅极(前栅极)一侧的栅极绝缘层由绝缘层5027构成，背栅极一侧的栅极绝缘层由绝缘层5024至5026的叠层构成。绝缘层5028是层间绝缘层。绝缘层5029是阻挡层。

[0243] 金属氧化物层5013覆盖包括金属氧化物层5011、5012以及导电层5051、5052的叠层体。绝缘层5027覆盖金属氧化物层5013。导电层5051、5052具有隔着金属氧化物层5013及绝缘层5027与导电层5050重叠的区域。

[0244] 在作为备份电路30的晶体管M01、M02使用OS晶体管5001的情况下,电容器C1、C2的两个电极中的一个可以使用与导电层5050同一层的导电层形成,其中另一个可以使用导电层5052形成。备份电路31也是同样的。

[0245] 作为用于导电层5050至5054的导电材料,例如有如下材料:以掺杂有磷等杂质元素的多晶硅为代表的半导体;镍硅化物等硅化物;钼、钛、钽、钨、铝、铜、铬、钕、钪等金属或以上述金属为成分的金属氮化物(氮化钽、氮化钛、氮化钼、氮化钨)等。此外,也可以使用铟锡氧化物、包含氧化钨的铟氧化物、包含氧化钨的铟锌氧化物、包含氧化钛的铟氧化物、包含氧化钛的铟锡氧化物、铟锌氧化物、添加有氧化硅的铟锡氧化物等导电材料。

[0246] 例如,导电层5050为氮化钽或钽的单层。或者,在导电层5050为两层结构或三层结构时,可以采用如下组合:铝、钛;氮化钛、钛;氮化钛、钽;氮化钽、钽;氮化钨、钽;钛、铝、钛;氮化钛、铝、钛;氮化钛、铝、氮化钛。其中前者设置在绝缘层5027一侧。

[0247] 导电层5051及导电层5052具有相同的层结构。例如,在导电层5051为单层时,可以使用铝、钛、铬、镍、铜、钇、锆、钼、银、钽或钨等的金属或以这些金属为主要成分的合金。在导电层5051为两层结构或三层结构时,可以采用如下组合:钛、铝;钽、铝;钽、铜;铜-镁-铝合金、铜;钛、铜;钛或氮化钛、铝或铜、钛或氮化钛;钼或氮化钼、铝或铜、钼或氮化钼。其中前者设置在绝缘层5027一侧。

[0248] 例如,优选的是,导电层5053为对氢具有阻挡性的导电层(例如,氮化钽层),导电层5054为其导电率比导电层5053高的导电层(例如,钽层)。通过采用该结构,导电层5053和导电层5054的叠层具有布线的功能以及抑制氢扩散到氧化物层5010的功能。

[0249] 作为用于绝缘层5021至5032的绝缘材料,例如有如下材料:氮化铝、氧化铝、氮氧化铝、氧氮化铝、氧化镁、氮化硅、氧化硅、氮氧化硅、氧氮化硅、氧化镓、氧化锗、氧化钇、氧化锆、氧化镧、氧化钕、氧化铪、氧化钽、硅酸铝等。绝缘层5021至5032由包括这些绝缘材料的单层或叠层构成。构成绝缘层5021至5032的层可以包含多种绝缘材料。

[0250] 在本说明书等中,氧氮化物是指氧含量大于氮含量的化合物,氮氧化物是指氮含量大于氧含量的化合物。

[0251] 在OS晶体管5001中,氧化物层5010优选被对氧和氢具有阻挡性的绝缘层(以下称为阻挡层)包围。通过采用该结构,可以抑制氧从氧化物层5010释放出并可以抑制氢侵入到氧化物层5010,由此可以提高OS晶体管5001的可靠性及电特性。

[0252] 例如,绝缘层5029被用作阻挡层,绝缘层5021、5022、5024中的至少一个被用作阻挡层。阻挡层可以使用氧化铝、氧氮化铝、氧化镓、氧氮化镓、氧化钇、氧氮化钇、氧化铪、氧氮化铪、氮化硅等的材料形成。另外,还可以在氧化物层5010和导电层5050之间设置阻挡层。或者,也可以设置对氧和氢具有阻挡性的金属氧化物层作为金属氧化物层5013。

[0253] 绝缘层5030优选为防止导电层5050的氧化的阻挡层。当绝缘层5030对氧具有阻挡性时,可以抑制从绝缘层5028等脱离的氧使导电层5050氧化。例如,作为绝缘层5030可以使用氧化铝等金属氧化物。

[0254] 示出绝缘层5021至5032的结构例子。在该例子中,绝缘层5021、5022、5025、5029、

5030至5032都被用作阻挡层。绝缘层5026至5028是包含过剩氧的氧化物层。绝缘层5021是氮化硅层,绝缘层5022是氧化铝层,绝缘层5023是氧氮化硅层。背栅极一侧的栅极绝缘层(5024至5026)是氧化硅、氧化铝和氧化硅的叠层。前栅极一侧的栅极绝缘层(5027)是氧氮化硅层。层间绝缘层(5028)是氧化硅层。绝缘层5029、5030至5032是氧化铝层。

[0255] 图18A示出氧化物层5010为三层结构的例子,但是不局限于此。氧化物层5010例如可以为没有金属氧化物层5011或金属氧化物层5013的两层结构,也可以由金属氧化物层5011和金属氧化物层5012中的任一个层构成。另外,氧化物层5010也可以由四层以上的金属氧化物层构成。

[0256] 《OS晶体管的结构实例2》

[0257] 图18B所示的OS晶体管5002是OS晶体管5001的变形例子。在OS晶体管5002中,金属氧化物层5011与金属氧化物层5012的叠层的顶面及侧面被金属氧化物层5013与绝缘层5027的叠层覆盖。因此,在OS晶体管5002中,不需要必须设置绝缘层5031、5032。

[0258] 《OS晶体管的结构实例3》

[0259] 图19A所示的OS晶体管5003是OS晶体管5001的变形例子。两者的主要不同之处是栅电极的结构。

[0260] 在形成于绝缘层5028中的开口中设置有金属氧化物层5013、绝缘层5027及导电层5050。也就是说,通过利用绝缘层5028的开口以自对准的方式形成栅电极。因此,在OS晶体管5003中,栅电极(5050)不具有隔着栅极绝缘层(5027)与源电极及漏电极(5051、5052)重叠的区域。由此,可以降低栅极-源极之间的寄生容量及栅极-漏极之间的寄生电容,从而可以提高频率特性。此外,由于可以利用绝缘层5028的开口控制栅电极的宽度,所以能够容易地制造沟道长度短的OS晶体管。

[0261] 《OS晶体管的结构实例4》

[0262] 图19B所示的OS晶体管5004的与OS晶体管5001不同之处是栅电极、氧化物层的结构。

[0263] OS晶体管5004的栅电极(5050)被绝缘层5033、5034覆盖。OS晶体管5004包括由金属氧化物层5011和金属氧化物层5012构成的氧化物层5009。金属氧化物层5011中设置有低电阻区域5011a、5011b,金属氧化物层5012中设置有低电阻区域5012a、5012b,而代替导电层5051、5052。通过向氧化物层5009选择性地添加杂质元素(例如,氢、氮),可以形成低电阻区域5011a、5011b、5012a及5012b。

[0264] 当向金属氧化物层添加杂质元素时,氧空位形成在添加杂质元素的区域中,杂质元素侵入氧空位而载流子密度增高,由此添加区域被低电阻化。

[0265] OS晶体管的沟道形成区域优选为CAC-OS (cloud-aligned composite metal oxide semiconductor)。

[0266] CAC-OS在材料的一部分中具有导电性的功能,在材料的另一部分中具有绝缘性的功能,作为材料的整体具有半导体的功能。在将CAC-OS用于晶体管的活性层的情况下,导电性的功能是使被用作载流子的电子(或空穴)流过的功能,绝缘性的功能是不使被用作载流子的电子流过的功能。通过导电性的功能和绝缘性的功能的互补作用,可以使CAC-OS具有开关功能(开启/关闭的功能)。通过在CAC-OS中使各功能分离,可以最大限度地提高各功能。

[0267] CAC-OS包括导电性区域及绝缘性区域。导电性区域具有上述导电性的功能,绝缘性区域具有上述绝缘性的功能。在材料中,导电性区域和绝缘性区域有时以纳米粒子级分离。另外,导电性区域和绝缘性区域有时在材料中不均匀地分布。有时导电性区域被观察为其边缘模糊且以云状连接。

[0268] 在CAC-OS中,有时导电性区域及绝缘性区域以0.5nm以上且10nm以下,优选为0.5nm以上且3nm以下的尺寸分散在材料中。

[0269] 此外,CAC-OS由具有不同带隙的成分构成。例如,CAC-OS由具有起因于绝缘性区域的宽隙的成分及具有起因于导电性区域的窄隙的成分构成。在该结构中,当使载流子流过时,载流子主要在具有窄隙的成分中流过。此外,具有窄隙的成分与具有宽隙的成分互补作用,与具有窄隙的成分联动地在具有宽隙的成分中载流子流过。因此,通过将上述CAC-OS用于晶体管的沟道形成区域,可以实现具有高电流驱动力及高场效应迁移率的OS晶体管。

[0270] 此外,金属氧化物半导体根据其结晶性被分为单晶金属氧化物半导体和非单晶金属氧化物半导体。作为非单晶金属氧化物半导体,有CAAC-OS (*c-axis-aligned crystalline metal oxide semiconductor*)、多晶金属氧化物半导体、nc-OS (*nanocrystalline metal oxide semiconductor*) 及a-like OS (*amorphous-like metal oxide semiconductor*)等。

[0271] OS晶体管的沟道形成区域优选包括CAAC-OS、nc-OS等具有结晶部的金属氧化物。

[0272] CAAC-OS具有c轴取向性,其多个纳米晶在a-b面方向上连结而结晶结构具有畸变。畸变是指在多个纳米晶连结的区域中晶格排列一致的区域与其他晶格排列一致的区域之间的晶格排列的方向变化的部分。

[0273] 虽然纳米晶基本上是六角形,但是并不局限于正六角形,有不是正六角形的情况。此外,在畸变中有时具有五角形或七角形等晶格排列。在CAAC-OS的畸变附近观察不到明确的晶界。即,可知通过使晶格排列畸变,可抑制晶界的形成。这可能是由于CAAC-OS可容许因如下原因而发生的畸变:在a-b面方向上的氧原子排列的低密度或因金属元素被取代而使原子间的键合距离产生变化等。

[0274] CAAC-OS有具有层状结晶结构(也称为层状结构)的倾向,在该层状结晶结构中层叠有包含铟及氧的层(下面称为In层)和包含元素M、锌及氧的层(下面称为(M,Zn)层)。铟和元素M彼此可以取代,在用铟取代(M,Zn)层中的元素M的情况下,也可以将该层表示为(In,M,Zn)层。另外,在用元素M取代In层中的铟的情况下,也可以将该层表示为(In,M)层。

[0275] 在nc-OS中,微小的区域(例如1nm以上且10nm以下的区域,特别是1nm以上且3nm以下的区域)中的原子排列具有周期性。nc-OS在不同的纳米晶之间观察不到结晶取向的规律性。因此,在膜整体中观察不到取向性。所以,有时nc-OS在某些分析方法中与a-like OS或非晶氧化物半导体没有差别。

[0276] a-like OS是具有介于nc-OS与非晶金属氧化物半导体之间的结构的金属氧化物半导体。a-like OS包含空洞或低密度区域。a-like OS的结晶性比nc-OS及CAAC-OS的结晶性低。

[0277] 在本说明书等中,CAC表示金属氧化物半导体的功能或材料,CAAC表示金属氧化物半导体的结晶结构。

[0278] 符号说明

[0279] 10、11:单元,20、25:双稳态电路,30、31:备份电路,51、52、53:预充电电路,55:读出放大器,55a:锁存电路,56:RS锁存电路,57、58、59:反相器电路,101:存储装置,105:电源管理单元(PMU),110、120:外围电路,122:控制器,123:行电路,124:列电路,125:备份/恢复驱动器,131:行译码器,132:字线驱动器,133:列译码器,134:预充电电路,135:局部位线复用器(MUX),135r、135w:MUX,136:读出放大器,137:写入驱动器,138:输出驱动器,150、151、152、153、154:功率开关,160、161、162:电源定域,300:处理器,305:PMU,306:总线,311:备份/恢复驱动器,320:高速缓冲存储器,321:单元阵列,322:外围电路,324:控制器,325:备份/恢复驱动器,326:行电路,327:列电路,330:CPU核心,331:触发器,332:高速缓冲存储器,335:扫描触发器,335A:时钟缓冲器电路,340:备份电路,390、391、392、393、394、398、399:功率开关,2010:信息终端,2011:外壳,2012:显示部,2013:操作按钮,2014:外部连接端口,2015:扬声器,2016:麦克风,2051:外壳,2052:显示部,2053:键盘,2054:指向装置,2070:摄像机,2071:外壳,2072:显示部,2073:外壳,2074:操作键,2075:透镜,2076:连接部,2110:便携式游戏机,2111:外壳,2112:显示部,2113:扬声器,2114:LED灯,2115:操作键按钮,2116:连接端子,2117:照相机,2118:麦克风,2119:记录介质读取部,2150:电冷藏冷冻箱,2151:外壳,2152:冷藏室门,2153:冷冻室门,2170:汽车,2171:车体,2172:车轮,2173:仪表盘,2174:灯,5001、5002、5003、5004:OS晶体管,5009、5010:氧化物层,5011、5012、5013:金属氧化物层,5021、5022、5023、5024、5025、5026、5027、5028、5029、5030、5031、5032、5033、5034:绝缘层,5050、5051、5052、5053、5054:导电层,5500:单晶硅片,7000:电子构件,7001:引线,7002:印刷电路板,7004:电路板,7110:芯片,BL、BLB:位线,LRBL、LRBLB、LWBL、LWBLB:局部位线,WL:字线,BGL、OGL:布线,V\_VDD、V\_VDH、V\_VDM、V\_VSM:虚拟电压线,Q、Qb、QS、QSb、SN1、SN2、SN3、SN11、D1、Q1、SD、SD\_IN、SE、CK、CK1、CKB1、RT:节点,MN1、MN2、MN3、MP1、MP2、MP3、MP4、M01、M02、M03、M011、M012、M013、MT1、MT2:晶体管,C1、C2、C3、C11:电容器,DIF\_N、DIF\_P:扩散层,OL:层,MET1、MET2、MET3、MET4、MET5、MET6、MET\_G1、MET\_G2、MET\_B、MET\_C:布线层,CON1、MVI1、MVI2、MVI3、MVI4、MVI5、MVI\_OL、MVI\_B:导通孔

[0280] 本申请基于2017年1月13日提交到日本专利局的日本专利申请No.2017-003830,通过引用将其完整内容并入在此。

图1

图2A

图2B

图3

图4

图5A

图5B

图6A

图7A

图7B

图7C

图7D

图8A

图8B

图8C

图8D

图9A

图9B

图9C

图9D

图10A

图10B

图10C

图10D

图11

金属氧化物层

绝缘层

导电层

图12

图13

图14

图15

图16A

图16B

图17A

图17B

图17C

图17D

图17E

图17F

图18A

图18B

图19A

图19B