(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5716012号

(P5716012)

(45) 発行日 平成27年5月13日(2015.5.13)

(24) 登録日 平成27年3月20日(2015.3.20)

|              |           |            |       |

|--------------|-----------|------------|-------|

| (51) Int.Cl. | F 1       |            |       |

| H01L 27/105  | (2006.01) | H01L 27/10 | 4 4 8 |

| H01L 45/00   | (2006.01) | H01L 45/00 | Z     |

| H01L 49/00   | (2006.01) | H01L 49/00 | Z     |

請求項の数 22 (全 36 頁)

|               |                               |           |                                                                 |

|---------------|-------------------------------|-----------|-----------------------------------------------------------------|

| (21) 出願番号     | 特願2012-504904 (P2012-504904)  | (73) 特許権者 | 511225435<br>インターモレキュラー、インコーポレーテッド                              |

| (86) (22) 出願日 | 平成22年4月9日(2010.4.9)           |           | アメリカ合衆国、カリフォルニア州 95<br>134, サンノゼ, 2865 ザンカーロード                  |

| (65) 公表番号     | 特表2012-523711 (P2012-523711A) | (74) 代理人  | 100114775<br>弁理士 高岡 亮一                                          |

| (43) 公表日      | 平成24年10月4日(2012.10.4)         | (74) 代理人  | 100121511<br>弁理士 小田 直                                           |

| (86) 國際出願番号   | PCT/US2010/030619             | (72) 発明者  | クセ, ロナルド, ジョン<br>アメリカ合衆国、カリフォルニア州 95<br>134, サンノゼ, 2865 ザンカーロード |

| (87) 國際公開番号   | W02010/118380                 |           |                                                                 |

| (87) 國際公開日    | 平成22年10月14日(2010.10.14)       |           |                                                                 |

| 審査請求日         | 平成25年4月5日(2013.4.5)           |           |                                                                 |

| (31) 優先権主張番号  | 12/608, 934                   |           |                                                                 |

| (32) 優先日      | 平成21年10月29日(2009.10.29)       |           |                                                                 |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                 |

| (31) 優先権主張番号  | 12/705, 474                   |           |                                                                 |

| (32) 優先日      | 平成22年2月12日(2010.2.12)         |           |                                                                 |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                 |

最終頁に続く

(54) 【発明の名称】スイッチング特性を改善した抵抗スイッチングメモリ素子

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電極および第2の電極と、

ハフニウム酸化物を含み、第1の厚さを有する、前記第1の電極と前記第2の電極との間のスイッチング層と、

前記スイッチング層と前記第2の電極との間のカップリング層であって、酸化アルミニウムおよび酸化ジルコニウムから構成されるグループから選択される材料を含む前記カップリング層であり、前記第1の厚さの25パーセント未満であって0パーセントよりも大きい第2の厚さを有する前記カップリング層と

を備え、

前記第1の厚さは、20オングストロームと100オングストロームとの間であることを特徴とする抵抗スイッチングメモリ素子。

## 【請求項 2】

前記第1の電極は、不純物添加シリコンであり、前記メモリ素子は、前記第2の電極にて、共通の電気的基準に関する負のリセット電圧と、前記共通の電気的基準に関する正のセット電圧とを受信するように構成されることを特徴とする請求項1に記載のメモリ素子。

## 【請求項 3】

前記スイッチング層は、 $HfO_{1-x_2}$ と $HfO_{1-x_7}$ との間の元素組成を有するハフニウム酸化物原料を含むことを特徴とする請求項1に記載のメモリ素子。

**【請求項 4】**

前記第1の電極は、n型ポリシリコンであることを特徴とする請求項3に記載のメモリ素子。

**【請求項 5】**

前記第1の電極および前記第2の電極のうちの少なくとも1つは、前記スイッチング層と同一の最も一般的な酸化状態を有することを特徴とする請求項1に記載のメモリ素子。

**【請求項 6】**

前記第1の電極と前記スイッチング層との間の界面層であって、10未満の厚さを有する前記界面層をさらに備えることを特徴とする請求項1に記載のメモリ素子。

**【請求項 7】**

前記第2の電極の仕事関数は、前記第1の電極の仕事関数より高く、前記第1の電極は、共通の電気的基準に関する負電圧を有する形成電圧パルスを受信するように構成されることを特徴とする請求項1に記載のメモリ素子。

**【請求項 8】**

第1の電極および第2の電極と、

前記第1の電極と前記第2の電極との間のスイッチング層であって、前記スイッチング層は4電子ボルト(eV)を超える第1のバンドギャップを有する第1の金属酸化物を含み、第1の厚さを有する前記スイッチング層と、

前記スイッチング層と前記第2の電極との間のカップリング層であって、前記第1のバンドギャップ以上の第2のバンドギャップを有する第2の金属酸化物を含む前記カップリング層であり、前記第1の厚さの25パーセント未満であって0パーセントよりも大きい第2の厚さを有する前記カップリング層と、

を備え、

前記第1の電極は、不純物添加シリコンと、窒化チタンとから構成されるグループから選択され、

前記第2の電極は、モリブデン窒化物と、酸化モリブデンと、窒化チタンと、タングステンと、タンタル窒化物と、モリブデン窒化物と、酸化モリブデンと、白金と、ルテニウムと、ニッケルと、イリジウムと、酸化イリジウムと、酸化ルテニウムとから構成されるグループから選択されることを特徴とする抵抗スイッチングメモリ素子。

**【請求項 9】**

前記第1の金属酸化物は、正規組成の60～95%である酸素濃度を有することを特徴とする請求項8に記載のメモリ素子。

**【請求項 10】**

前記第1の金属酸化物の第1の金属は、前記第2の金属酸化物の第2の金属の第2の最も一般的な酸化状態とは異なる第1の最も一般的な酸化状態を有することを特徴とする請求項8に記載のメモリ素子。

**【請求項 11】**

前記第1の金属酸化物の第1の金属および前記第2の金属酸化物の第2の金属は、同一の最も一般的な酸化状態を有することを特徴とする請求項8に記載のメモリ素子。

**【請求項 12】**

前記第2の金属酸化物の第2の金属は、前記第1の金属酸化物の第1の金属の第1の最も一般的な酸化状態以下である第2の最も一般的な酸化状態を有することを特徴とする請求項8に記載のメモリ素子。

**【請求項 13】**

前記第1の金属酸化物は、ハフニウム酸化物と、タンタルオキサイドと、酸化アルミニウムと、酸化ジルコニアムと、酸化ランタンと、酸化セリウムと、イットリウム酸化物とから構成されるグループから選択され、

前記第2の金属酸化物は、酸化ジルコニアムと、酸化アルミニウムとから構成されるグループから選択されること

を特徴とする請求項8に記載のメモリ素子。

10

20

30

40

50

**【請求項 14】**

前記第1の電極は、不純物添加シリコンを含み、前記第1の電極と前記スイッチング層との間の界面層であって、酸化シリコンを含み10未満の厚さを有する前記界面層をさらに含むことを特徴とする請求項8に記載のメモリ素子。

**【請求項 15】**

前記第1の電極は、チタンケイ化物と、コバルトケイ化物と、ニッケルケイ化物と、パラジウムケイ化物と、白金ケイ化物とから構成されるグループから選択されたケイ化物を含むことを特徴とする請求項8に記載のメモリ素子。

**【請求項 16】**

基板上に第1の電極を堆積させるステップと、

原子層堆積(ALD)を用いて、前記第1の電極の表面に金属酸化物を含むスイッチング層を堆積させるステップであって、

摂氏40度を超えた状態かつ摂氏50度を超えない状態で前駆物質を保持するステップと、

前記前駆物質を基板に導入するステップと、

摂氏10度未満かつ摂氏0度より高い状態で酸素源を保持するステップと、

前記酸素源を基板に導入するステップとをさらに含む前記スイッチング層を堆積する前記ステップと、

前記スイッチング層の表面に第2の電極を堆積させるステップと

を含むことを特徴とする抵抗スイッチングメモリ素子を形成する方法。 20

**【請求項 17】**

前記酸素源は、水蒸気と、イソプロピルアルコール(IPA)と、エタノールとのうちの少なくとも1つであることを特徴とする請求項16に記載の方法。

**【請求項 18】**

前記金属酸化物は、ハフニウム酸化物と、タンタルオキサイドと、酸化アルミニウムと、イットリウム酸化物と、酸化ジルコニウムとから構成されるグループから選択されることを特徴とする請求項16に記載の方法。

**【請求項 19】**

前記金属酸化物は、正規組成の60~95パーセントである酸素濃度を有することを特徴とする請求項16に記載の方法。 30

**【請求項 20】**

前記ALDのための堆積温度は、摂氏250度未満であることを特徴とする請求項16に記載の方法。

**【請求項 21】**

物理気相堆積(PVD)を用いて前記第1の電極の表面に物理気相堆積層を堆積させることをさらに含み、前記スイッチング層は、前記PVD層上に堆積され、前記PVD層は、前記スイッチング層と同一の材料を含むことを特徴とする請求項16に記載の方法。

**【請求項 22】**

前記スイッチング層の表面にカップリング層を堆積させるステップであって、前記カップリング層は前記スイッチング層の厚さの25パーセント未満である厚さを有するステップをさらに含むことを特徴とする請求項16に記載の方法。 40

**【発明の詳細な説明】****【技術分野】****【0001】**

(関連出願に対する相互参照)

本出願は、「不純物添加シリコン電極を含む抵抗スイッチングメモリ素子」と題され、2009年4月10日に出願された米国仮出願番号第61/168,534号、「不純物添加シリコン電極を含む抵抗スイッチングメモリ素子」と題され、2009年10月29日に出願された米国ユーティリティ出願番号第12/608,934号、「スイッチング特性を改善した抵抗スイッチングメモリ素子」と題され、2009年10月30日に出願

された米国ユーティリティ出願番号第12/610,236号、および「スイッチング特性を改善した抵抗スイッチングメモリ素子」と題され、2010年2月12日に出願された米国ユーティリティ出願番号第12/705,474号に対する優先権を主張し、すべての文献は参考文献として本明細書に援用される。

#### 【0002】

本発明は、半導体メモリに概して関する。より具体的には、スイッチング特性を改善した抵抗スイッチングメモリ素子が記載される。

#### 【背景技術】

#### 【0003】

不揮発性メモリは、無電源の時でもそれらのコンテンツを保存する半導体メモリである。不揮発性メモリは、永続的なストレージを必要とする汎用コンピュータシステム、組込システムおよび他の電子装置と同様に、デジタルカメラ、携帯電話および音楽プレーヤーなどの電子装置におけるストレージとして用いられる。不揮発性半導体メモリは、リムーバブルかつ携帯メモリカード、または他のメモリモジュールの形式をとることができ、他の型の回路またはデバイスに組み込むことができ、または他の所望の形式をとることができる。不揮発性半導体メモリは、小サイズかつ永続性を有しており、可動部品を有しておらず、かつ動作するための電力をほとんど必要としない、というそれらの有利性のため、より普及するようになっている。

#### 【0004】

フラッシュメモリは、様々なデバイスにおいて用いられる不揮発性メモリの一般的な形式である。フラッシュメモリは、長時間にわたるアクセス回数、消去回数および書き込み回数に帰着することができるアーキテクチャを用いる。電子装置の動作速度およびユーザのストレージ要求は、急速に増大しているフラッシュメモリは、不揮発性メモリのニーズに不十分であることを多くの事例で証明している。加えて、不揮発性メモリの速度が現在揮発性メモリを用いるRAMおよび他のアプリケーションのための要求を満たすために高められるならば、(ランダムアクセスメモリ(RAM)などの)揮発性メモリが、場合によっては不揮発性メモリと置き換わることができる。

#### 【0005】

抵抗スイッチングメモリは、第1の比抵抗値からセット電圧のアプリケーション上の第2の比抵抗値に変化する、および、第2の比抵抗値からリセット電圧のアプリケーション上の第1の比抵抗値へ戻るように変化する抵抗スイッチング材料(例えば金属酸化膜)を含むメモリである。既存の抵抗スイッチングメモリは、いくつかのアプリケーションに適さないスイッチング特性(例えばセット電圧、リセット電圧および形成電圧、保持)を有している。

#### 【0006】

したがって、必要とされるものは、改善されたスイッチング特性を有する抵抗スイッチングメモリ素子である。

#### 【0007】

本発明の様々な実施形態は、以下の詳細な説明および添付の図面において開示される。

#### 【図面の簡単な説明】

#### 【0008】

【図1】抵抗スイッチングメモリ素子のメモリアレイを図示する。

【図2A】抵抗スイッチング材料および選択素子を含むメモリ素子を図示する。

【図2B】1つの実施形態によるメモリ素子の一部の拡大図である。

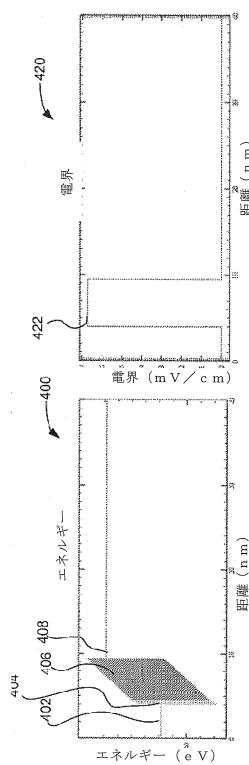

【図3】バンド図であって、界面層があるメモリ素子(図3)および界面層がないメモリ素子(図4)におけるエネルギー準位を図示する。

【図4】バンド図であって、界面層があるメモリ素子(図3)および界面層がないメモリ素子(図4)におけるエネルギー準位を図示する。

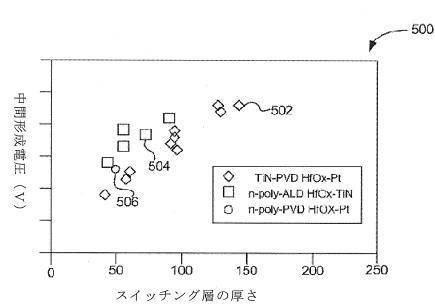

【図5】界面層の存在上の形成電圧の依存関係を図示するグラフである。

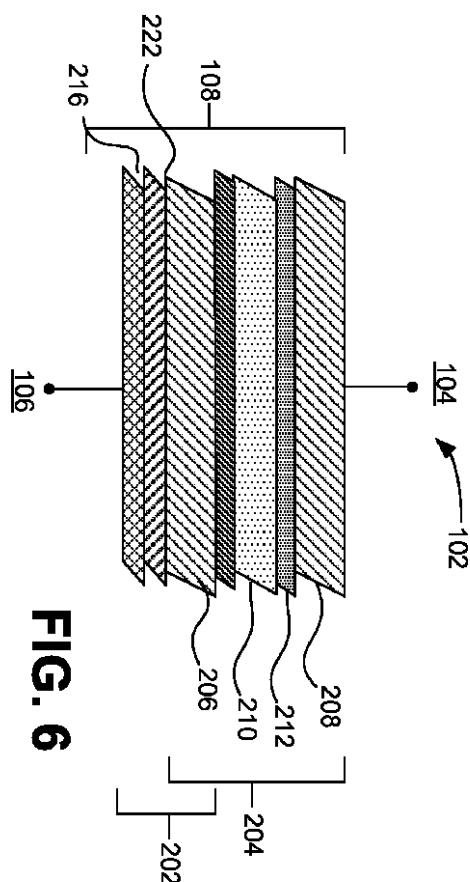

【図6】電極を、選択素子として用いられるダイオードと共有するメモリ素子を図示する

10

20

30

40

50

。

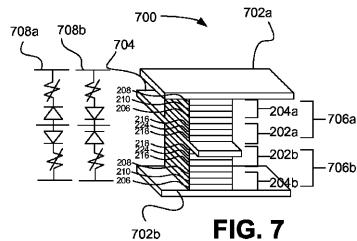

【図7】本明細書に記載されるメモリ素子を用いる3次元メモリアレイの一部を図示する。

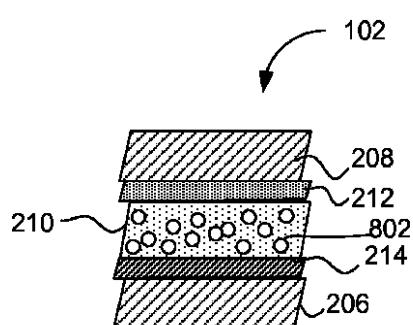

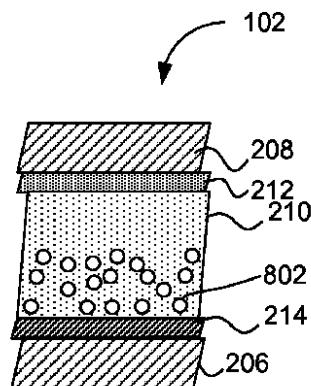

【図8A】メモリ素子、および界面層を用いるメモリ素子内での酸素空孔（欠陥）の生成および処置を図示する。

【図8B】メモリ素子、および界面層を用いるメモリ素子内での酸素空孔（欠陥）の生成および処置を図示する。

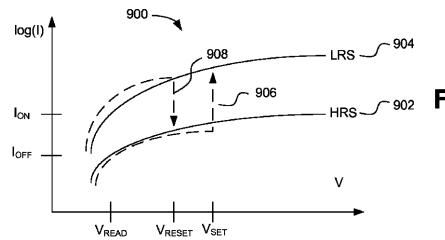

【図9】メモリ素子のための電流（I）対電圧（V）のプロットの対数である。

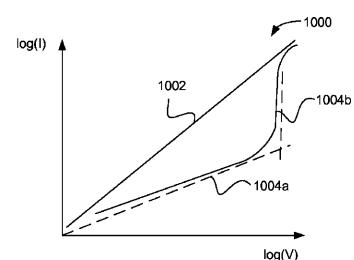

【図10】抵抗状態変化を実証するメモリ素子のための電流（I）対電圧（V）のプロットである。

10

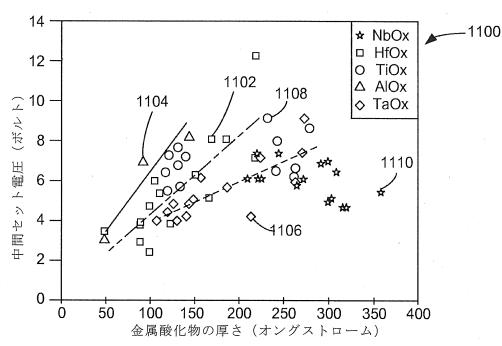

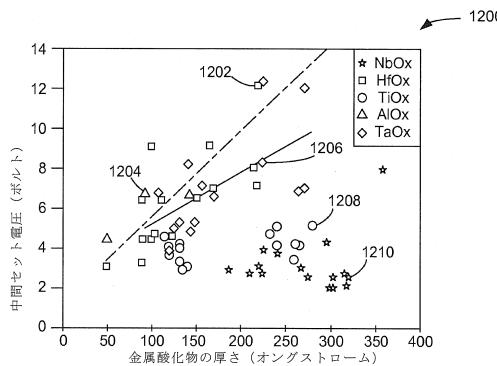

【図11】金属酸化物層の厚さと、本明細書に記載されるメモリ素子において用いられるいくつかの材料（金属酸化物）のための帰着するセット電圧、リセット電圧およびオン／オフ電流比との間の関係を示すグラフである。

【図12】金属酸化物層の厚さと、本明細書に記載されるメモリ素子において用いられるいくつかの材料（金属酸化物）のための帰着するセット電圧、リセット電圧およびオン／オフ電流比との間の関係を示すグラフである。

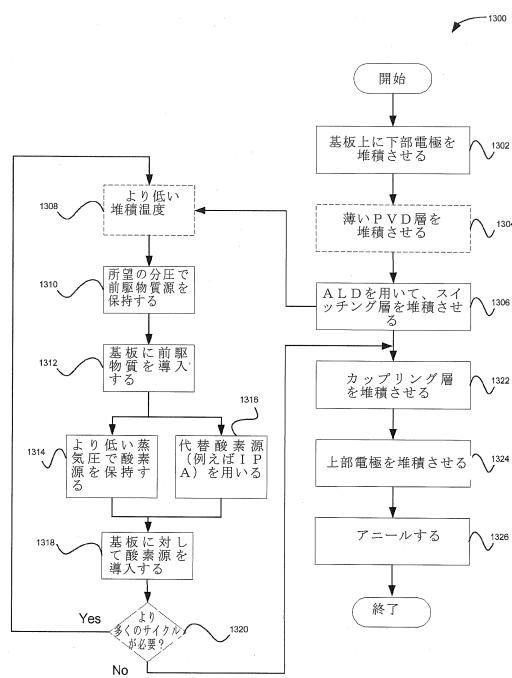

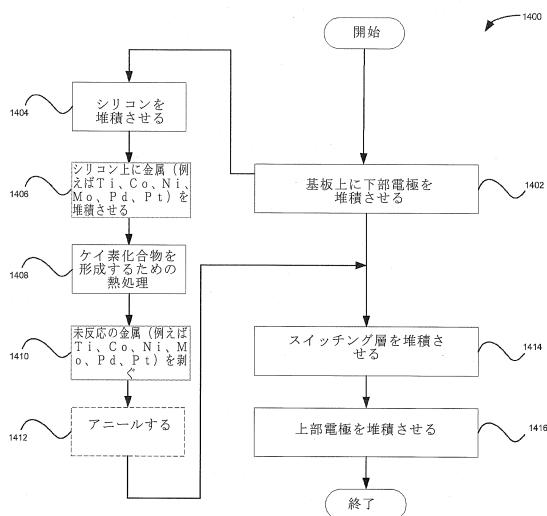

【図13】界面層を制御するためのプロセスを記載するフローチャートである。

【図14】界面層を制御するためのプロセスを記載するフローチャートである。

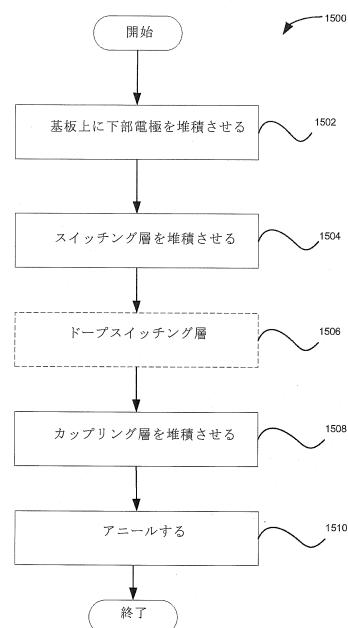

【図15】様々な実施形態による、メモリ素子を形成するプロセスを記載するフローチャートである。

20

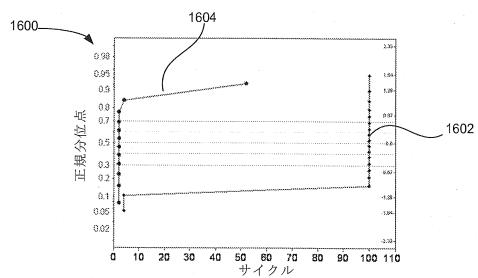

【図16A】抵抗スイッチングメモリ素子の低い仕事関数の電極が負電圧セットパルスおよび正電圧リセットパルスを受信するときの高サイクル収率を示すグラフである。

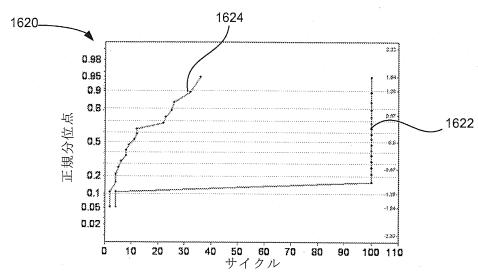

【図16B】抵抗スイッチングメモリ素子の2つの電極が、0.1 eVを超える1.0 eV未満の異なる仕事関数を有するときの高サイクル収率を示すグラフである。

#### 【発明を実施するための形態】

##### 【0009】

1つ以上の実施形態の詳細な説明は、添付する図に沿って以下に提供される。詳細な説明は、このような実施形態に関して提供されるが、任意の特定の例には限定されない。その範囲は特許請求の範囲によってのみ限定され、多数の代替手段、変更および等価物が含まれる。多数の特定の詳細は、充分な理解を与えるために以下の説明において述べられる。これらの詳細は、例示の目的で提供され、記載される技術は、これらの特定の詳細のいくつかまたはすべてを伴わないで、特許請求の範囲に従って実施されてもよい。明瞭さの目的のために、実施形態に関する技術分野において知られている技術的な材料は、説明を不明瞭にすることを必要に回避するために詳細に記載されていない。

30

##### 【0010】

様々な実施形態によると、抵抗スイッチングメモリ素子が本明細書に記載される。メモリ素子は、概して、少なくとも1つの絶縁層が2つの導電性電極に囲まれる金属・絶縁体・金属（MIM）構造を有する。本明細書に記載されるいくつかの実施形態は、4.0 eVを超えるバンドギャップを有するスイッチング材料（例えばハフニウム酸化物（HfO<sub>2</sub>）、バンドギャップ = 5.7 eV、厚さ～20～100）のスイッチング層と、いくつかの材料（例えばZrO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、TiO<sub>2</sub>、Ti/TiO<sub>2</sub>など）の1つになりえるカップリング層とを囲む異材質（例えば、1つの電極は不純物添加シリコンであり、1つは窒化チタンである）の電極を含むメモリ素子である。いくつかの実施形態において、カップリング層は、スイッチング層（例えば、酸化ジルコニア（ZrO<sub>2</sub>）でバンドギャップ = 5.8 eV；または酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）でバンドギャップ = 8.4 eV）より高いバンドギャップを有する。カップリング層は、スイッチング層の厚さの25パーセント未満である厚さを有しており、カップリング層を含むメモリ素子は、改善されたスイッチング特性（例えば、より低いセット電圧、リセット電圧および形成電圧、より優れた保持）を示している。

40

##### 【0011】

10

20

30

40

50

他の実施形態において、金属分に富む金属酸化物スイッチング層および金属分に富むスイッチング層を形成するための技術が記載される。金属分に富むスイッチング層は、（スイッチング特性を改善するために処理されることがある）増大する欠陥数（例えば酸素空孔）を含む。金属分に富むスイッチング層は、例えば、原子層堆積（ALD）プロセス中に導入されるオキシダントの量を削減することにより、堆積することができる。さらなる実施形態において、電極とその上に堆積したスイッチング層との間の界面層のサイズ（粒度）を除去または制御するための技術が記載される。

## I . スイッチング操作

### 【0012】

メモリ素子の金属酸化物スイッチング層の欠陥によって、本明細書に記載されるメモリ素子の抵抗性のスイッチングが引き起こされると考えられている。一般に、欠陥は、溶着金属酸化物において形成され、または既に存在し、既存の欠陥は、追加工程によって増強される場合がある。例えば、PVD法（PVD）プロセスおよび原子層堆積（ALD）プロセスは、いくつかの欠陥または傷を有する場合がある層を堆積する。欠陥は、金属酸化物の構造において、電荷の変化という形式をとってもよい。すなわち、いくつかの電荷キャリアが構造に不在であっても（すなわち空孔）よいし、付加的な電荷キャリアが存在しても（すなわち格子間）よいし、または1つの素子が別のものを置換すること（すなわち置換型）ができる。

10

### 【0013】

欠陥は、金属酸化物の大部分において、および／または、金属酸化物と隣接している層との界面にて、電気的にアクティブな欠陥（トラップとしても知られている）であると考えられる。トラップは、セット電圧の印加（高抵抗状態から低抵抗状態にスイッチするために）によって満たされることができ、リセット電圧の印加（低抵抗状態から高抵抗状態にスイッチするために）によって空にされることができると考えられている。トラップは、沈着状態の金属酸化物において本来的になりえる（すなわち、金属酸化物の形成から存在している）し、またはドーピングおよび他のプロセスにより生成および／または増強されることができる。ドーピングは、スイッチング層と相互に拡散する隣接する「ドーピング」層を用いて、注入を用いて、または他の技術を用いて、実行することができる。

20

### 【0014】

スイッチング層の欠陥は、セット電圧の印加に際して伝導性の浸透経路を形成すると考えられている。浸透経路は、リセット電圧の印加に際して除去されるとさらに考えられている。例えば、ハフニウム酸化被膜は、浸透経路を生成し、かつハフニウム酸化被膜の導電率を変更するために用いることができるトラップを形成してもよい酸素空孔またはハフニウム空孔、または酸素格子間原子またはハフニウム格子間原子を含んでもよい。

30

### 【0015】

抵抗スイッチングメモリ素子のスイッチング特性は、金属酸化物内の欠陥を制御することにより調整することができる。スイッチング特性は、動作電圧（例えばセット電圧、リセット電圧および形成電圧）、動作電流（例えばオン電流およびオフ電流）およびデータリテンションを含む。欠陥制御は、スイッチング層内の型、密度、エネルギー準位および空間分布によって達成される。その後、これらの欠陥は、それらが満たされる（不動態化される／補償される）か、満たされない（補償されない）かに基づいて、電流フローを変調する。別層を追加すること、スイッチング層の形成を制御すること、注入すること、応力を制御すること、ある熱処理は、すべて欠陥特性を制御するために用いられる。さらに、欠陥は流動性である必要はない。例えば、カップリング層212（図2Aを参照）および界面層214（図2Aおよび図8A～図8Bを参照）は、位置、深さ、密度、および／または欠陥の型を制御するために用いることができ、技術は、増大した欠陥数を有するスイッチング層を形成するために用いることができる。

40

### 【0016】

加えて、金属酸化物スイッチング層は、任意の位相（例えば、結晶で・無定形の）または多重の位相の混合物を有する場合がある。無定形の位相の金属酸化物は、比抵抗値（そ

50

れは、いくつかの実施形態においてメモリ素子への潜在的損害を低減するためにデバイスの使用可能な電流を低下させることができる)を高めてもよい。

## I I . メモリ構造

### A . メモリアレイ

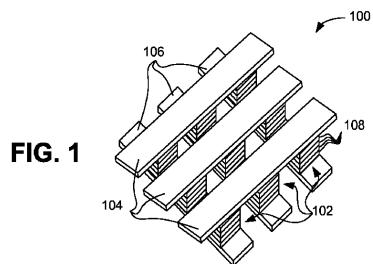

#### 【0017】

図1は、抵抗スイッチングメモリ素子102のメモリアレイ100を図示する。メモリアレイ100は、メモリデバイスまたは他の集積回路の一部であってもよい。メモリアレイ100は、ポテンシャルメモリ構成の例であるが、他のいくつかの構成が可能であることは理解される。

#### 【0018】

読み出し書き込み回路は、信号線104および直交の信号線106を用いて、メモリ素子102に接続されてもよい。信号線104および信号線106などの信号線は、時にワード線とビット線とも呼ばれ、アレイ100の素子102にデータを読み書きするために用いられる。個別のメモリ素子102またはグループのメモリ素子102は、信号線104および106の適合するセットを用いて扱われることができる。メモリ素子102は、以下にさらに詳細に記載されるように、材料の1つ以上の層108から形成されてもよい。さらに、示されたメモリ素子102は、マルチレイヤ3Dメモリアレイを構成するために、垂直の方式で積層されることができる(図7を参照)。

#### 【0019】

任意の好適な読み出し書き込み回路およびアレイレイアウトスキームは、素子102などの抵抗スイッチングメモリ素子から非揮発性メモリ装置を構成するために用いられてもよい。例えば、水平線104および垂直線106は、抵抗スイッチングメモリ素子102の末端に直接接続されてもよい。これは単に例示である。

#### 【0020】

所望であれば、他の電気装置が、各々のメモリ素子102に関連づけられてもよい(すなわち、層108の1つ以上であってもよい)(例えば図2Aを参照)。これらの装置(それらは時に選択素子とも呼ばれる)は、例えば、ダイオード、PINダイオード、シリコンダイオード、シリコンPINダイオード、トランジスタ、ショットキーダイオードなどを含んでもよい。選択素子は、メモリ素子102において任意の好適な位置に直列に接続されてもよい。

### B . メモリ素子

#### 1 . MIM構造

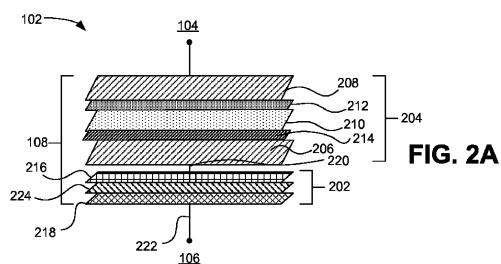

#### 【0021】

図2Aおよび図2Bは、抵抗スイッチング材料および選択素子(ダイオード202)を含むメモリ素子102を図示する。図2Bは、1つの実施形態によるメモリ素子102の一部の拡大図である。メモリ素子102は、金属・絶縁体・金属(MIM)型スタック204を含む(いくつかの実施形態において、金属層の1つ以上は不純物添加シリコンなどの伝導性の半導体材料になりえる)。スタック204は、2つの電極206および208、および1つの抵抗スイッチング層210(例えば絶縁体または金属酸化物)を含む。電極206および208は、金属、金属炭化物、金属酸化物または金属窒化物(例えばPt、Ru、RuO<sub>2</sub>、Ir、IrO<sub>2</sub>、TiN、W、TaN、MoN、MoO<sub>x</sub>、WN、TiAl合金、Ni、WO<sub>x</sub>、Al、不純物添加Al、Cu、HfC、HfN、NbN、TaC、TaSiN、Ti、VC、VN、ZrN、など)でありえるし、または不純物添加シリコン(例えばp型またはn型不純物添加ポリシリコン)でありえる。抵抗スイッチング層210、は金属酸化物または他のスイッチング材料でありえる。いくつかの実施形態において、抵抗スイッチング層210は、HfO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、Al<sub>2</sub>O<sub>3</sub>、Y<sub>2</sub>O<sub>3</sub>、CeO<sub>2</sub>、La<sub>2</sub>O<sub>3</sub>およびZrO<sub>2</sub>などの高バンドギャップ(すなわち4電子ボルト(eV s)を超えるバンドギャップ)材料である。より高い移動性を有するイオンを含んでいるかもしれない、CeO<sub>2</sub>はいくつかの実施形態のためには有用かもしれない。さらなる実施形態において、ZnO<sub>x</sub>、CuO<sub>x</sub>およびそれらの不定比・不純物添加変形

10

20

30

40

50

体などの半導体の金属酸化物（p型またはn型）は、有用なスイッチング特性を有すると考えられているので、 $ZnO_x$ 、 $CuO_x$ およびそれらの不定比・不純物添加変形体などの半導体の金属酸化物（p型またはn型）は、これらの酸化物は用いられることができる。他の実施形態において、 $Hf_xM_yO_2$ （ここで、 $M = Al$ 、 $Zr$ 、 $Ti$ 、 $La$ または $Sr$ である）などの三元金属酸化物も、スイッチング層210として用いることができる。

#### a. スイッチング層

##### 【0022】

スイッチング層210は、任意の所望厚さを有することができるが、いくつかの実施形態において、10 ~ 100 の間、20 ~ 60 の間、または約50 でありえる。

10

スイッチング層210は、任意の所望の技術を用いて堆積することができるが、本明細書に記載されるいくつかの実施形態においては、ALD、またはALDとPVDとの組み合わせを用いて堆積される。他の実施形態において、スイッチング層210は、減圧CVD（LPCVD）、プラズマ強化CVD（PECVD）、プラズマ強化ALD（PEALD）、液相成長プロセス、およびエピタクシープロセスを用いて堆積することができる。PEALDプロセスは、いくつかの実施形態において、欠陥を制御し、かつスイッチング電圧および形成電圧を改善するために用いられる考えられている。

##### 【0023】

スイッチング層210は、加えて、スイッチング層210の元素組成が化学量的であるとは言えない（例えば $HfO_{1.7}$ に対して $HfO_2$ ）。スイッチング層210は、酸素の欠損がある（それは酸素空孔欠陥として明らかになる）場合がある。付加的な欠陥は、メモリ素子102の、低減され予測可能なスイッチング電圧および形成電圧に結びつく場合がある。金属分に富むスイッチング層210を堆積させるための技術は、図13に記載される。

#### b. カップリング層

##### 【0024】

スタック204は、また、カップリング層212（それは $ZrO_2$ 、 $TiO_2$ または $Al_2O_3$ などの別の金属酸化物であってもよい）、または金属Tiなどの金属層、またはTiと酸化チタン（ $TiO_2$ ）を含む層を、含むことができる。他の実施形態において、カップリング層212は、隣接電極208の堆積に際して、またはアニーリングに際して、部分的にまたは全面的に酸化する金属層として堆積することができる。カップリング層212は、例えば、電極208の近くに欠陥を生成することにより、電極208でスイッチングを促進することができる。例えば、カップリング層がTiなどの金属であるならば、（短時間熱酸化または真空アニールなどの）アニール中に、カップリング層212は、隣接した金属酸化物スイッチング層210からの酸素を誘引する場合があり、それによって、カップリング層212を酸化させながら、スイッチング層210に酸素空孔を生成する。

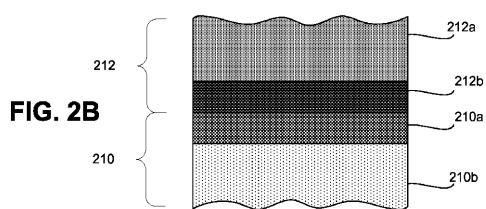

##### 【0025】

例えば、図2Bに示されるように、メモリ素子102は、堆積されたままの実質的に金属チタン（または別の金属）であるカップリング層212と、金属酸化物（例えば $HfO_2$ ）であるスイッチング層とを、含む。メモリ素子102がアニールされた後、または電極208の堆積の結果、金属のカップリング層212は、異なる特性（例えば異なる酸素濃度）を有する複数の部分を有するカップリング層212およびスイッチング層210に帰着するスイッチング層210からの酸素を誘引する場合がある。例えば、カップリング層212の第1の部分212aは、実質的に金属（例えば実質的に金属チタン）である。その一方でスイッチング層210に接している第2の部分212bは、実質的に金属酸化物（例えば酸化チタン）である。同時に、スイッチング特性を調整するために用いることができる酸素空孔を残して、金属酸化物における酸素がカップリング層212の第2の部分212bに移行しているので、カップリング層210に接しているスイッチング層210の第1の部分210aは、酸素欠損である。スイッチング層210の第2の部分210

40

50

bは、第1の部分210bより高い酸素濃度を有する。言いかえれば、第1の部分210aは、第2の部分（例えばHfO<sub>1.6~2.0</sub>）より金属分に富む（例えばHfO<sub>1.2~1.5</sub>）。部分210a、210b、212aおよび212bは、単に例示であり、スイッチング層210およびカップリング層212の各々は、酸素の異なる濃度を有するいくつかの部分を有していてもよく、または、酸素濃度は、層210および212の厚さを通じて次第に変化させられてもよいことは、理解される。さらに、カップリング層212の酸化の量、およびスイッチング層210の酸素の低減は、アニールのパラメータ（例えば、RTOのための期間や酸素濃度）を変化させることにより調整することができる。

#### 【0026】

カップリング層212は、抵抗スイッチング層210より薄くすることができ、例えば10、カップリング層212は、抵抗スイッチング層210の厚さの25%未満である厚さ、または抵抗スイッチング層210の厚さの10%未満である厚さを有することができる。例えば、抵抗スイッチング層210は、20~60の層にすることができ、界面層212は、5~10の層にすることができる。

#### 【0027】

いくつかの実施形態において、カップリング層212は、スイッチング層210のバンドギャップとほぼ等しいか、それ以上のバンドギャップを有する。カップリング層212のより高いバンドギャップは、スイッチング層210からのリークを低減することにより、メモリ素子102の記憶力を改善することを支援することができる。加えて、カップリング層212は、（スイッチングを支援することができる）電極208の近く（カップリング層とスイッチング層210との間の界面で（またはその近く）、および/または、電極208とカップリング層212との間の界面で（またはその近く）を含む）に欠陥を生成することができる。カップリング層212は、スイッチング層210の欠陥へのアクセスを提供することができるほど十分に薄い。

#### 【0028】

いくつかの実施形態において、カップリング層212は堆積されたままの金属チタン（いくつかの実施形態においてアニール中に少なくとも部分的に酸化チタンになることができる）である。チタンカップリング層212は、隣接電極208の実効仕事関数（（例えばリークを低減することにより）スイッチング特性を変更するために用いることができる）を変化させることができる。

#### c. 界面層

#### 【0029】

スタック204は、電極206とスイッチング層210との間の界面層214をさらに含んでもよい。界面層214は、スイッチング層210の堆積の結果、およびその堆積中に、例えば、処理の間の熱酸化の結果、形成される電極206の材料の酸化物になりえる。界面層214は、いくつかの実施形態において、スイッチング層210（例えば図8A~図8Bを参照）の欠陥を変更することができる。他の実施形態において、形成電圧を低減する、またはスイッチングを可能にするための界面層214を除去することは望ましいかもしれない。いくつかの実施形態において、界面層214は、満たされるトラップを可能にするスイッチング層210に効果的な電子注入を妨げる場合があり、それによって形成電圧を高め、またはその一帯で著しい電位降下を引き起こし、スイッチング層210において高電界を生成し、スイッチングを防止すると考えられている。サイズを制御し、界面層214を除去するための技術は、図13および図14に記載される。

#### 【0030】

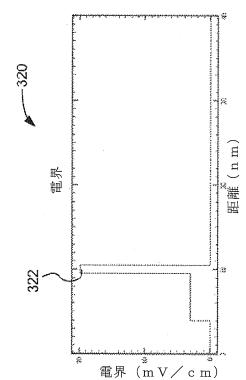

図3および図4は、界面層214があるメモリ素子（図3）、および界面層がないメモリ素子（図4）におけるエネルギー準位を図示するバンド図300および400である。バンド図300および400の各々のために、メモリ素子102のある領域内の電界の強度を図示する、対応する電界図320および340がある。

#### 【0031】

バンド図300において、メモリ素子は、窒化チタン電極302、酸化ジルコニウムカ

10

20

30

40

50

ツプリング層 304、ハフニウム酸化物スイッチング層 306、酸化シリコン界面層 308、および n 型ポリシリコン電極 310 を有する。ここで用いられる材料は、実例であり、他の材料（例えば金属チタン、または酸化ジルコニウムの代わりに Ti / TiO<sub>2</sub>）を用いることができるることは理解される。バンド図 400において、メモリ素子は、窒化チタン電極 402、酸化ジルコニウムカッピング層 404、ハフニウム酸化物スイッチング層 406、および n 型ポリシリコン電極 408 を有する。電界図 320 に示されるように、電界は、界面層 314 における大量 322 によって低減される。増大されたスイッチング電圧は、界面層 214 における電界の低減を克服するために必要かもしれない。界面層 214 が十分に厚いならば、全体の電界は、界面層 214（それはスイッチングをすべて防いでもよい）に対して失われてもよい。あるいは、電界図 420 において示されるように、界面層 214 を伴わないメモリ素子において、電界は、スイッチング層 210（それは、スイッチング電圧を低減することができ、より予測可能なスイッチングに結びつくことができる）において含むメモリ素子 102 の全体にわたって平等に低減される（422）。但し、図 8A および図 8B に関して記載されるように、スイッチング層 210 における欠陥数を高めるために、調整される厚さの界面層 214 を保存することは望ましいかもしれない。

#### 【0032】

図 5 は、界面層 214 の存在上の形成電圧の依存関係を図示するグラフ 500 である。以下の 3 つのセットのメモリ素子が準備された。

#### 【0033】

菱形 502 によって表わされるメモリ素子の第 1 のセットは、窒化チタン電極 206、PVD を堆積させたハフニウム酸化物スイッチング層 210、およびカッピング層 212 のない白金電極 208 を含む。

#### 【0034】

正方形 504 によって表わされるメモリ素子の第 2 のセットは n 型ポリシリコン電極 206、ALD - 堆積されたハフニウム酸化物スイッチング層 210、およびカッピング層 212 のない窒化チタン電極 208 を含む。

#### 【0035】

円形 506 によって表わされるメモリ素子の第 3 のセットは、n 型ポリシリコン電極 206、PVD を堆積させたハフニウム酸化物スイッチング層 210、およびカッピング層 212 のない白金電極 208 を含む。

#### 【0036】

見て分かるように、同一の厚さを有するスイッチング層のために、窒化チタン上の PVD ハフニウム酸化物を含む素子 502 は、最低値の形成電圧を有し、ポリシリコン上の PVD ハフニウム酸化物を含む素子 506 は、次に最低値の形成電圧を有し、ポリシリコンの上の ALD ハフニウム酸化物を有する素子 504 は、最高値の形成電圧を有する。見て分かるように、同一の厚さを有するスイッチング層のために、窒化チタン上の PVD ハフニウム酸化物を含む素子 502 は、最低値の形成電圧を有し、ポリシリコン上の PVD ハフニウム酸化物を含む素子 506 は、次に最低値の形成電圧を有し、ポリシリコンの上の ALD ハフニウム酸化物を有する素子 504 は、最高値の形成電圧を有する。ALD プロセスは、場合によっては、増大された形成電圧に結びつく、より高い加工温度（PVD のいくつかの事例として、室温に対して 200 以上）のため、より厚い界面層 214 を少なくとも部分的に形成する可能性があると考えられている。加えて、ポリシリコン電極（例えば、素子 502 および 506）上で生成された酸化シリコン界面層 214 は、窒化チタンなどの金属を含む電極上で生成された酸化物よりは伝導性でない。したがって、界面層 214 を低減および / または制御するための（特にシリコンベースの電極のための）技術は、形成電圧を改善するために用いられることができる。

#### 【0037】

ALD プロセスは、より厚い界面層 214 を形成し、かつ高められた形成電圧を有するメモリ素子に帰着する可能性があるかもしれないが、他の理由（例えば、より共形な層を

10

20

30

40

50

形成するために)のために、PVD処理にわたってALD処理を用いることは望ましいかもしれない。また、図13は、ALD処理を用いて界面層214を低減または除去するプロセスを記載する。加えて、図8Aおよび図8Bに関して記載されるように、スイッチング層210(それは図13のプロセスを用いても形成することができる)における欠陥数を高めるために、調整された厚さの界面層214(例えば10以下)を保存することは望ましいかもしれない。

#### 【0038】

界面層214を有することが望ましいならば、MIMスタック204の層の堆積の順序は、重要かもしれない。界面層214はスイッチング層210の堆積中に形成されるので、スイッチング層210は、界面層214が形成されるべき電極上に形成される(例えば、酸化シリコン界面層214が所望されるならば、ポリシリコン層上に形成される)ことができる。一例として、および図7においてさらに論じられるように、3次元メモリアレイを形成する場合、他の素子の配向が逆にされるべきである場合でさえ、同一の配向のメモリ素子を常に形成すること(例えば常に下部の1つの電極)が必要かもしれない。他の実施形態において、但し、メモリ素子102の後堆積アニールを用いることにより、メモリ素子102が逆順に堆積される場合、界面層214は生成することができる。

#### d. 電極

#### 【0039】

電極206および208は、異材質にすることができる。いくつかの実施形態において、電極は、0.1~1電子ボルト(eV)、または0.4~0.6eVなどによる、異なる仕事関数を有する。例えば、電極208は、4.5~4.6eVの仕事関数を有するTiNにすることができる。その一方で、電極206は、約4.1~4.15eVの仕事関数を有するn型ポリシリコンにすることができる。他の電極物質は、p型ポリシリコン(4.9~5.3eV)、遷移金属、遷移金属合金、遷移金属窒化物、遷移金属炭化物、白金(5.7eV)、タンゲステン(4.5~4.6eV)、タンタル窒化物(4.7~4.8eV)、酸化モリブデン(約5.1eV)、モリブデン窒化物(4.0~5.0eV)、イリジウム(4.6~5.3eV)、酸化イリジウム(約4.2eV)、ルテニウム(約4.7eV)および酸化ルテニウム(約5.0eV)を含む。他の電位電極は、チタン/アルミニウム合金(4.1~4.3eV)、ニッケル(約5.0eV)、タンゲステン窒化物(約4.3~5.0eV)、酸化タンゲステン(5.5~5.7eV)、アルミニウム(4.2~4.3eV)、銅またはシリコン添加アルミニウム(4.1~4.4eV)、銅(約4.5eV)、炭化ハフニウム(4.8~4.9eV)、ハフニウム窒化物(4.7~4.8eV)、窒化ニオブ(約4.95eV)、炭化タンタル(約5.1eV)、タンタル窒化シリコン(約4.4eV)、チタン(4.1~4.4eV)、バナジウム炭化物(約5.15eV)、窒化バナジウム(約5.15eV)および窒化ジルコニア(約4.6eV)を含む。本明細書に記載されるいくつかの実施形態にとって、他の構成も可能であるが、仕事関数の高い電極は、リセット動作中に(共通の基準電位と比較して測定されるように)正パルスを受信する。他の実施形態において、仕事関数の高い電極は、リセット動作中に負パルスを受信する。いくつかの実施形態において、セット電圧およびリセット電圧に共通の電気的基準に関する異極性がある場合には、メモリ素子102は、二極性のスイッチングを用いる。また、いくつかの実施形態において、セット電圧およびリセット電圧に同一の極性がある場合には、メモリ素子102は、単極のスイッチングを用いる。他の実施形態において、リークを低減し、かつより多くの安定した金属酸化物/電極界面を生成するために、電極の仕事関数を一般に高めることは望ましい。

#### 2. 選択素子

#### 【0040】

ダイオード202は、メモリアレイ100(図1を参照)のいくつかのメモリ素子102などのいくつかのメモリ素子中からアクセスするためのメモリ素子を選択するために用いることができる選択素子である。ダイオード202は、電流がメモリ素子102を通じて一方向にのみ流れるように、電流の流れを制御する。

10

20

30

40

50

## 【0041】

ダイオード202は、半導体材料の2つ以上の層を含んでもよい。ダイオードは、一般にp n接合であり、不純物添加シリコン層216および218は、p n接合を形成することができる。例えば、不純物添加シリコン層216は、p型層になりえるし、不純物添加シリコン層218は、n型層になりえる。その結果、ダイオード202のノード220は、アノードであり、第1の電極206に接続される。この一例において、ダイオード202のノード222は、カソードであり、信号線106（それは、例えばビット線またはワード線であってもよいし、ビット線またはワード線に接続されてもよい）に接続される。例えば、ノード220および222は、必ずしもメモリ素子102における物理的特徴でないし、例えば、電極206は不純物添加シリコン層216と直接接触してもよい。他の実施形態において、低抵抗性フィルムなどの1つ以上の付加的層が、電極206と不純物添加シリコン層216との間に追加される。10

## 【0042】

いくつかの実施形態において、不純物添加シリコン層216は、n型層であり、不純物添加シリコン層218は、p型層である。また、ノード220は、ダイオード202のカソードであり、ノード222は、ダイオード202のアノードである。任意の絶縁層224は、PINまたはNIPダイオード202を生成するために、不純物添加シリコン層216と218との間におくことができる。いくつかの実施形態において、絶縁層224、および不純物添加シリコン層216および218の1つは、同層から形成される。例えば、シリコン層は、堆積されることができるし、層の一部は、不純物添加シリコン層216または218を形成するためにドープされることができる。そして、層の残りの部分は、絶縁層224である。20

## 【0043】

他の実施形態において、メモリ素子102の1つの電極は、不純物添加シリコン（例えばp型またはn型ポリシリコン）（それは、またダイオード202の一部として作用することもできる）になりえる。図6は、選択素子として用いられるダイオード202と電極とを共有するメモリ素子102を図示する。ダイオード202が不純物添加シリコンの2層から構成され、不純物添加シリコンの層がメモリ素子202の電極として用いることができるので、不純物添加シリコン（例えばn型ポリシリコンの層）の単一層は、メモリ素子102の電極として、およびダイオード202の層として、役立つことができる。ダイオード202とメモリ素子102との間の不純物添加シリコン層を共有することによって、2層、1つの不純物添加シリコン層、およびダイオード202とメモリ素子102との間のカップリング層、およびそれらの関連づけられる処理ステップは、省かれることができる。30

## 3. 極性のスイッチング

## 【0044】

信号線（例えば信号線104）は「第2」の電極208に接続され、信号線は、第2の電極208にスイッチング電圧を提供するように構成される。いくつかの実施形態において、第2の電極208は、第1の電極206より高い仕事関数を有しているし、信号線104は、共通の電気的基準に関する負のセット電圧、および共通の電気的基準に関する正のリセット電圧を提供するように構成される。実施形態は、白金またはルテニウムなどの低い仕事関数の第1の電極206（例えば窒化チタン）および高い仕事関数の第2の電極を用いるものを含んでもよい例えば、共通の電気的基準は、接地されてもよい（すなわち0V）し、セット電圧は、その後、負電圧（例えば-2V）になり、リセット電圧は、正電圧（例えば2V）になるだろう。但し、共通の電気的基準は、+2Vまたは-2Vなどの、任意の電圧になりえる。40

## 【0045】

他の実施形態において、第2の電極208は、また、第1の電極206より高い仕事関数を有しており、信号線104は、共通の電気的基準に関する正のセット電圧および負のリセット電圧を提供するように構成される。例えば、不純物添加シリコンの第1の電極250

06（例えばn型ポリシリコン）および高い仕事関数の第2の電極208（例えば窒化チタン）を有するメモリ素子において、リセット電圧は、第2の電極208において負である可能性がある。例えば、図16Aおよび図16Bを参照されたい。

#### 【0046】

いくつかの実施形態において、メモリ素子の1つのスイッチング電圧（例えばリセット電圧）は、共通の電気的基準に関する第1の極性（例えば正極性）を有することができるし、別のスイッチング電圧（例えばセット電圧）は、メモリ素子が二極性スイッチングを用いるように、共通の電気的基準に関する負極性を有することができます。他の実施形態において、スイッチング電圧は、共通の基準に関する同一の極性を有しており、単極性スイッチングと呼ばれる。いくつかの実施形態において、メモリアレイの他の素子（例えば選択素子）のある構成との互換性を提供するために、単極性スイッチングを用いることは望ましいかもしれない。加えて、スイッチング電圧は、限られた期間（例えば1ミリ秒未満、50マイクロ秒未満、1マイクロ秒未満、50ナノ秒未満、など）を有する電圧パルス（例えば矩形波パルス）にすることができる。10

#### 4. 形成電圧の極性

#### 【0047】

より低い動作電圧は、抵抗スイッチングメモリ素子がメモリアレイにおいて関連づけられる装置（例えばダイオード）を保護するために望ましい。形成電圧は、多くの場合、最高値の振幅動作電圧であり、したがって、形成電圧の低減は、装置の操作性および信頼性を改善するための重要な目的である。形成電圧極性は、いくつかの実施形態において、形成電圧振幅に影響を与えることが示されている。20

#### 【0048】

一例において、メモリ素子は、接地するために接続された高い仕事関数の電極、および形成電圧パルスを受信する低い仕事関数の電極を準備された。第1の例は、n型ポリシリコン電極、ハフニウム酸化物スイッチング層、および窒化チタン電極を含んだ。この例において、窒化チタン電極（すなわち高い仕事関数の電極）は、接地され、正負の形成電圧パルスは、n型ポリシリコン電極に適用された。ネガティブパルスは、約-8Vの中間の形成電圧を有し、その一方で、プラスパルスは、約+13Vの中間の形成電圧を有した。第2の例において、メモリ素子は、窒化チタン電極、ハフニウム酸化物スイッチング層、および白金電極を有するように準備された。高い仕事関数の電極（ここでは白金電極）は、接地され、低い仕事関数の電極（窒化チタン電極）は、形成電圧パルスを受信した。この例において、負パルスの中間の形成電圧は、-4.4Vであり、その一方で、正パルスを用いる中間の形成電圧は、6.4Vであった。30

#### 【0049】

上述の例は、低い仕事関数の電極にて印加された負の形成電圧が、いくつかの実施形態において形成電圧の振幅を低減することができることを実証することを示す。低い仕事関数の電極からの電子注入は、正極性の形成電圧と比較して、負極性の形成電圧の振幅を低減することができると考えられている。

#### 【0050】

加えて、メモリ素子における電極の仕事関数の間の差分が大きくなればなるほど、形成電圧の振幅は小さくなることは、いくつかの実施形態のために実証されている。例えば、n型ポリシリコン電極、ハフニウム酸化物スイッチング層、および窒化チタン電極を有するメモリ素子において、仕事関数の差分は、約0.5eVであり、中間の形成電圧は、-7Vである。n型ポリシリコン電極、ハフニウム酸化物スイッチング層、および白金電極を有する別のメモリ素子は、1.6eVの仕事関数の差分および-5.5Vの中間の形成電圧を有する。したがって、いくつかの実施形態において、例示のように、仕事関数の差分を1.6eVに高めることは必要ではないかもしれないが、形成電圧を低減するために電極間の仕事関数の差分を高めることは望ましいかもしれない。40

#### 5. 他の特性

#### 【0051】

メモリの記憶力を支援するために、抵抗スイッチング層 210 として低リーケ材料を有していることは望ましいかもしれない。例えば、層 210 は、メモリ素子のオフ状態（例えば高抵抗状態）において、金属酸化物の 20 オングストロームの厚さ当たり 0.5 ボルト (V) で測定されたスクエア・センチメートル ( / cm<sup>2</sup>) 当たり 40 アンペア未満のリーケ電流密度を有する材料であってもよい。

## 6. 3D メモリ構造

### 【0052】

図 7 は、本明細書に記載されたメモリ素子 102 を用いる 3 次元メモリ 700 アレイの一部を図示する。アレイ 700 は、2 つのワード線 702a および 702b、および共有されるビット線 704 を含む。2 つの MIM スタック 204a および 204b、およびダイオード 202a および 204b が、アレイ 700 において示される。メモリセル 706a は、MIM スタック 204a およびダイオード 202a を含み、メモリセル 706b は、MIM スタック 204b およびダイオード 202b を含む。

10

### 【0053】

2 つのメモリセル 706a および 706b が、同一の共有されるビット線 704 を用いることができるよう、メモリアレイ 700 は構成される。ここに示されるように、MIM スタック 204a および 204b は、両方とも、同一の順序で、それらの個々層（すなわち電極 206 および 208、およびスイッチング層 210）を組み込む。言いかえれば、MIM スタック 204a および 204b の両方のために、電極 206 は、第 1 に形成され、スイッチング層 210 は、電極 206 の上に形成され、電極 208 は、スイッチング層 210 の上に形成される。上述のように、MIM スタック 204 の層の堆積の順序は、界面層 214 を生成するために同一である必要があるかもしれない。しかしながら、いくつかの実施形態において、堆積の順序は、逆にすることができるし、界面層 214 は、電極堆積またはアニーリングなどの次工程の結果として生成された。

20

### 【0054】

一方、ダイオード 202a および 202b は、互いにミラーである。言いかえれば、ダイオード 202a は、底部の上に層 216 を有し、ダイオード 202b は、底部の上に層 218 を有する。例えば、層 216 は、n 型層であってもよいし、層 218 は、p 型層であってもよい。この構成を用いて、ダイオード 202a および 202b は、反対方向にバイアスをかけられる（それは、双方が同一共有されるビット線 704 を用いるようにメモリセル 706 を可能にする）。回路図 708a および 708b において示されるように、ダイオードは、任意の所望された配向を有することができるし、配向は、3 次元メモリアレイの構成に基づいて異なってもよい。

30

## 7. 界面層および酸素空孔

### 【0055】

図 8A および 8B は、メモリ素子 102 と、界面層 214 を用いるメモリ素子 102 内での酸素空孔（欠陥）の生成および処置とを図示する。界面層 214 は、メモリ素子 102 において他の層の処理中に生成することができる酸化物層である。例えば、スイッチング層 210 の堆積は、界面層 214 を生成するために温度（例えば 200 以上）での処理を含んでもよい。例えば、電極 206 が不純物添加シリコン（例えばポリシリコン）であるならば、スイッチング層 210 の堆積（例えば、PVD または ALD を用いて）は、酸化シリコン界面層 214 を生成することができる温度を含んでもよい。界面層 214 は、いくつかの実施形態において省くことができるが、他の実施形態において、界面層 214 は、リーケ特性の改善によりスイッチング層 210 の記憶力を改善するために、かつスイッチング層 210 の欠陥（例えば酸素空孔）を調整するために保持することができる。界面層 214 が保持されるいくつかの実施形態において、界面層 214 は、スイッチング層 210 の欠陥を電極 206 に対して見えるようにする（すなわち、界面層 214 は、スイッチング層 210 の欠陥へのアクセスを提供する）ために、かつスイッチング電圧上の界面層 214 の効果を低減するために相対的に薄くても（例えば、10 以下）よい。

40

### 【0056】

一例において、下部電極 206 は、ポリシリコンである。シリコンは、特に、加熱された場合に酸素を誘引することが知られており、金属分に富む金属酸化物スイッチング層を近くに生成するスイッチング層 210 において酸素空孔 802 を残しながら、金属酸化物スイッチング層 210 から酸素を取り出すことができる。理論によって束縛されるものではないが、これらの酸素空孔 802 は、このようなトラップを満たし空にするために、プログラミング電圧の印加で電流フローを調整するトラップとして役立つことができる。酸素空孔 802 は、流動性である必要はない。いくつかの実施形態において、界面層 214 の存在は、酸素（それは、処理条件に依存して、スイッチング層 210 の両面に、またはスイッチング層 210 を通じて付加的な酸素空孔を生成することができる）を誘引する金属のまたは部分的に金属のカップリング層 212 の存在と組み合わせることができる。

10

### 【0057】

薄いまたはゼロの中間の層の厚さの界面層 214 は、スイッチング層 210 において酸素空孔 802 の密度を調整するために用いることができる。例えば、より薄い界面層 214（例えば 5 に対して 10）は、酸素空孔 802 密度を高めることができる。加えて、スイッチング層 210 の厚さは、トラップ（例えば酸素空孔 802）がスイッチング層 210 を通じて、より立体的に等しくなるように、最適化することができる。例えば、図 8A は、界面層 214 の近くで濃縮された酸素空孔 802 を有する、より厚いスイッチング層 210 を示す。その一方で、図 8B は、酸素空孔 802 のより均衡のとれた分布を有する、より薄いスイッチング層 210 を示す。例えば、同一の材料を用いている 2 つのメモリ素子において、図 8A のスイッチング層 210 は、50 であってもよい。その一方で、図 8B のスイッチング層 210 の厚さは、25 である。スイッチング層 210 内の酸素空孔 802 の分布は、用いられる材料、界面層 214 の厚さ、用いられるプロセス（例えば、用いられるアニールの温度）などを含むいくつかの要因に依存される場合がある。図 8A および 8B は、酸素空孔の分布の 2 つのみの例であり、様々な他の構成が可能であることは理解される。

20

### I I I . メモリ操作

#### 【0058】

読み出し動作中に、メモリ素子 102 の状態は、信号線 104 および 106 の適合するセットに対して検知電圧（すなわち「読み出し」電圧  $V_{READ}$ ）を印加することにより検知することができる。その履歴によって、このように対処されるメモリ素子は、高抵抗状態または低抵抗状態のいずれであってもよい。したがって、メモリ素子の抵抗は、メモリ素子によって格納されているデジタルデータが何であるかを判定する。メモリ素子が低抵抗を有しているならば、例えば、メモリ素子は、論理 1（すなわち「1」のビット）を含むと言ってもよい。一方、メモリ素子が高抵抗値を有しているならば、メモリ素子は、論理 0（すなわち「0」のビット）を含むと言ってもよい。書き込み動作中に、メモリ素子の状態は、信号線 104 および 106 の適合するセットに対する好適な書き込み信号の印加によって変化させることができる。

30

#### 【0059】

図 9 は、メモリ素子 102 のための電流 (I) 対電圧 (V) プロット 900 の対数である。図 9 は、メモリ素子 102 のコンテンツを変化させるためのセット動作およびリセット動作を図示する。最初に、メモリ素子 102 は、高抵抗状態（「HRS」、例えば、論理 0 を格納）にあってもよい。この状態において、電流対メモリ素子 102 の電圧特性は、実線 HRS (902) によって表わされる。メモリ素子 102 の高抵抗状態は、信号線 104 および 106 を用いて、読み出し書き込み回路によって検知することができる。例えば、読み出し書き込み回路は、メモリ素子 102 に対して、読み出された電圧  $V_{READ}$  を適用し、メモリ素子 102 を介して流れる「オフ」電流  $I_{OFF}$  の帰着を検知することができる。メモリ素子 102 において論理 1 を格納することが所望される場合、メモリ素子 102 は、その低抵抗状態に置かれることができる。これは、信号線 104 および 106 にわたってセット電圧  $V_{SET}$  を適用するために読み出し書き込み回路を用いることにより達成されてもよい。破線 906 によって示されるように、メモリ素子 102 に対し

40

50

て  $V_{SET}$  を適用すると、メモリ素子 102 は、その低抵抗状態に切り替えられる。この領域において、メモリ素子 102 は、セット電圧  $V_{SET}$  の解除に続いて、メモリ素子 102 が低抵抗曲線 LRS (904) により特徴づけられるように変化される。さらに以下で記載されるように、メモリ素子 102 の抵抗状態への変化は、金属酸化物材料において、トラップを満たすためであってもよい（すなわち、「トラップ媒介」であってもよい）。 $V_{SET}$  と  $V_{RESET}$  は、「スイッチング電圧」と一般に指称されることができる。

#### 【0060】

メモリ素子 102 の低抵抗状態は、読み出し書き込み回路を用いて検知することができる。読み出された電圧  $V_{READ}$  が抵抗スイッチングメモリ素子 102 に対して適用された場合、読み出し書き込み回路は、メモリ素子 102 がその低抵抗状態にあることを示し、相対的に高い「オン」電流値  $I_{ON}$  を検知するだろう。メモリ素子 102 において論理 0 を格納することが所望される場合、メモリ素子は、メモリ素子 102 に対してリセット電圧  $V_{RESET}$  を適用することにより、その高抵抗状態にもう一度置かれることができる。読み出し書き込み回路がメモリ素子 102 に対して  $V_{RESET}$  を適用する場合、破線 908 によって示されるように、メモリ素子 102 は、その高抵抗状態 HRS に入る。リセット電圧  $V_{RESET}$  がメモリ素子 102 から解除された場合、メモリ素子 102 は、もう一度高抵抗値線 HRS (904) により特徴づけられるだろう。電圧パルスは、メモリ素子 102 のプログラミングにおいて用いることができる。例えば、1ミリ秒、10マイクロ秒、5マイクロ秒、500ナノ秒などの正方形パルスは、メモリ素子 102 を切り替えるために用いることができる。いくつかの実施形態において、メモリ素子 102 を切り替えるための所要時間の量に依存するパルスの長さを調整することは望ましいかもしれない。

#### 【0061】

形成電圧  $V_{FORM}$  は、使用するためのメモリ素子 102 を準備するために、メモリ素子 102 に対して印加された電圧である。本明細書に記載されるいくつかのメモリ素子は、セット電圧またはリセット電圧以上の電圧の印加を含む形成イベント (forming event) を必要としてもよい。メモリ素子 102 が最初に切り替わるとすぐに、セット電圧およびリセット電圧は、メモリ素子 102 の抵抗状態を変化させるために用いることができる。

#### 【0062】

抵抗スイッチングメモリ素子 102 の双安定抵抗は、メモリ素子 102 がデジタルデータを格納するために好適にする。電圧  $V_{SET}$  および  $V_{RESET}$  の印加がない状態で格納されたデータにおいては変化されないので、素子 102 などの素子から形成されたメモリは、不揮発性である。

#### 【0063】

図 10 は、抵抗状態変化を実証するメモリ素子 102 のための電流 (I) 対電圧 (V) のプロット 1000 である。プロット 1000 は、X 軸に沿ったメモリ素子 102 に対して適用された電圧ランプと、y 軸に沿った派生電流とを示す。ランプ電圧が印加される場合、線 1002 は、オーム性材料の応答を表わす。セットまたはリセットが生じる離散的な電圧がないので、オーム性応答は望ましくない。

#### 【0064】

一般に、グラフ 1004 のような、より急激な応答が所望される。グラフ 1004 は、オーム性応答 1004a から開始し、その後、急激な上向き 1004b に曲げる。グラフ 1004 は、メモリ素子 102 が HRS (902) から LRS (904) に切り替わるセット動作を表わしてもよい。

#### 【0065】

理論によって束縛されるものではないが、不金属の浸透経路は、セット動作中に形成され、リセット動作中に壊される。例えば、セット動作中に、メモリ素子 102 は、低抵抗状態に対して切り替わる。トラップを満たすことにより形成される浸透経路は、金属酸化物の導電率を高め、それによって、比抵抗値を低減する（すなわち、変化させる）。符号

10

20

30

40

50

404 b によって表わされる電圧は、セット電圧である。セット電圧においては、トラップが満たされ、金属酸化物の比抵抗値が減少するにつれて、電流において大規模なジャンプがある。

## I V . 材料

### 【 0 0 6 6 】

様々な金属酸化物は、本明細書に記載されるメモリ素子 102 のスイッチング層 210 として用いることができる。いくつかの実施形態において、メモリ素子 102 は、バルクスイッチングプロパティを示し、拡大縮小可能である。言い換えれば、欠陥は、スイッチング層 210 のバルクを通じて分散され、スイッチング電圧（すなわち、 $V_{SET}$  および  $V_{RESET}$ ）は、金属酸化物の厚さが増大または減少するのに伴って、増大または減少する考えられている。他の実施形態において、メモリ素子 102 は、界面を媒介としたスイッチング動作を示す。他の実施形態は、バルクと界面を媒介としたスイッチングプロパティ（それは、層界面でなお欠陥動作を示しながら拡大縮小可能であってもよい）の組み合わせを示してもよい。10

### A . スイッチング層のための高バンドギャップの材料

### 【 0 0 6 7 】

図 11 および図 12 は、本明細書に記載されるメモリ素子において用いられる、金属酸化物層の厚さと帰着するセット電圧との間の関係、リセット電圧、およびいくつかの材料（金属酸化物）のためのオン / オフ電流比を示すグラフである。これらのグラフは、2つの電極を含むメモリ素子、および中間に（すなわちカップリング層 212 なしで）配置された金属酸化物の単一層の特性を図示し、ある材料がバルクスイッチングプロパティを示すことを表示する。図 11 において見て分かるように、ハフニウム酸化物 1102、酸化アルミニウム 1104 またはタンタルオキサイド 1106 を含むメモリ素子にとって、セット電圧は、厚さとともに（すなわち、厚さに依存して）増加し、いくつかの実施形態において、およびこれらの材料のために、セット電圧は、メモリ素子における金属酸化物層の厚さの 100 オンゲストローム（）当たり少なくとも 1 ボルト（V）である。いくつかの実施形態において、100 の金属酸化物層の厚さの増加は、セット電圧を少なくとも 1 V 増加させる。同様に、図 12 において示されるように、ハフニウム酸化物 1202、酸化アルミニウム 1204、またはタンタルオキサイド 1206 のためのリセット電圧は、また、厚さに依存する。直線関係が金属酸化物のバルクの全体にわたる浸透経路の形成を示すので、したがって、これらのデータは、これらの材料のためのバルクに制御されるセット / リセット機構を支援する。言い換えれば、より厚い材料のために、より多くの電圧がトラップを満たすために必要とする。2030

### 【 0 0 6 8 】

酸化チタン ( $TiO_2$ 、3.0 eV) および酸化ニオブ ( $Nb_2O_5$ 、3.4 eV) が 4 eV 未満のバンドギャップを有する一方、ハフニウム酸化物 ( $HfO_2$ 、5.7 電子ボルト (eV))、酸化アルミニウム ( $Al_2O_3$ 、8.4 eV) およびタンタルオキサイド ( $Ta_2O_5$ 、4.6 eV) はすべて、4 eV を超えるバンドギャップを有する。本明細書に記載される様々な実施形態により用いることができる他の高バンドギャップの金属酸化物は、イットリウム酸化物 ( $Y_2O_3$ 、6.0 eV)、酸化ジルコニウム ( $ZrO_2$ 、5.8 eV)、酸化ランタン ( $La_2O_3$ 、4.3 eV) および酸化セリウム ( $CeO_2$ 、5.5 eV) を含む（表 1 も参照）。図 11 および図 12 において示されるように、酸化チタン 1108 および酸化ニオブ 1110 のためのセット電圧、および酸化チタン 1208 および酸化ニオブ 1210 のためのリセット電圧は、厚さとともにには増加しない。したがって、高バンドギャップ（すなわち 4 eV を超えるバンドギャップ）の金属酸化物は、バルクを媒介としたスイッチングおよび拡大縮小可能なセット電圧およびリセット電圧を示す。表 1 は、スイッチング層 210 として用いることができる高バンドギャップの材料を概説する。40

【表1】

| 材料                             | バンドギャップ |

|--------------------------------|---------|

| HfO <sub>2</sub>               | 5.7 eV  |

| Al <sub>2</sub> O <sub>3</sub> | 8.4 eV  |

| Ta <sub>2</sub> O <sub>5</sub> | 4.6 eV  |

| Y <sub>2</sub> O <sub>3</sub>  | 6.0 eV  |

| ZrO <sub>2</sub>               | 5.8 eV  |

| CeO <sub>2</sub>               | 5.5 eV  |

| La <sub>2</sub> O <sub>3</sub> | 4.3 eV  |

10

## B. カッピング層材料

## 【0069】

カッピング層212は、スイッチング層210の材料を補完するために選択される金属、金属酸化物、または金属／金属酸化物材料となることができる。例えば、カッピング層212は、スイッチング層210のバンドギャップを補完するために選択されてもよい。いくつかの実施形態において、カッピング層212は、ほぼスイッチング層210のバンドギャップ以上であるバンドギャップを有する。理論によって束縛されるものではないが、これは、リーク特性の改善によりメモリ素子102の記憶力を改善する場合がある。図3および図4のバンド図300および400で示されるように、酸化ジルコニアウムカッピング層212は、スイッチング層210のバンドギャップより高いバンドギャップを有する。高バンドギャップのカッピング層212は、スイッチング層210から電極208へのリークを低減することにより、記憶力を促進することができる。

20

## 【0070】

他の例において、カッピング層212は、スイッチング層210より低いバンドギャップを有することができる（例えば、カッピング層212は、酸化チタン（バンドギャップ = 3.5 eV）になりえる）。別の例において、カッピング層212は、チタン／酸化チタン層になりえる（図2Bを参照）。

## 【0071】

30

いくつかの例において、スイッチング層210は、ハフニウム酸化物（バンドギャップ = 5.7 eV）であり、第1の厚さ（例えば20～100）を有している。その後、カッピング層は、第1の厚さの25パーセント未満である第2の厚さを有する、酸化ジルコニアウム（ZrO<sub>2</sub>、バンドギャップ = 5.8 eV）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>、バンドギャップ = 8.7 eV）、酸化チタン、チタン／酸化チタンなど（表3を参照）の層のいずれかでありえる。例えば、カッピング層は、1～10の間（または、5または8）の厚さであることができる。

## 【0072】

それは、カッピング材が、スイッチング層210を通じて（例えば、HfAlO<sub>x</sub>層よりむしろ、ハフニウム酸化物スイッチング層210および酸化アルミニウムカッピング層212を用いて）分散されたというよりむしろ、カッピング材が離散的なカッピング層212にある場合、スイッチング動作がより優れているいくつかの材料系のために示されている（表3を参照）。カッピング層212とスイッチング層210の間の界面で生成された欠陥は、スイッチング特性を改善する場合があると考えられている。

40

## 【0073】

いくつかの実施形態において、カッピング層212は、スイッチング層210にドープするために用いることができる。ドーピングは、異原子価または等原子価のいずれかでありえる。異原子価ドーピングにおいて、ドーピング種は、ドープされた層とは異なる原子価を有する。例えば、スイッチング層210は、ハフニウム酸化物でありえるし、カッピング層212は、酸化アルミニウムでありえる。ハフニウム酸化物の典型的な欠陥種

50

は、 $Hf^{+4}$ であり、酸化アルミニウムの典型的な欠陥種は、 $Al^{+3}$ である。 $Al^{+3}$ イオンは、ハフニウム酸化物層においてハフニウム $^{+4}$ イオンにとって代わり、それによって、欠陥とトラップとを生成する。いくつかの実施形態において、ドーピングは等原子価であり、カッピング層212（例えば酸化ジルコニウム）は、スイッチング層210の金属と同一の最も一般的な酸化状態（例えば $+4$ ）を有する金属を有してもよい。これらのケースにおいて、異なる酸化状態（例えば $Zr^{+3}$ ）を有する他の種がスイッチング層210内に拡散する場合、異原子価ドーピングが、なお生じてもよい。

### C. 電極

#### 【0074】

様々な電極は、メモリ素子102として用いられることができる。いくつかの実施形態は、異材質からなる電極206および208を用いるメモリ素子102を記載する。例えば、電極206および208は、（いくつかのシステムにおける二極性スイッチングを容易にできると考えられている）異なる仕事関数（例えば、0.4eVと0.6eVとの間で異なる、または0.1eVと1.0eVとの間で異なる）を有するために選択される材料を有することができる。

10

#### 【0075】

電極206および208として用いることができる材料は、不純物添加シリコン（例えば、p型またはn型シリコン）、窒化チタン、タンタル窒化物、タングステン、タングステン窒化物、モリブデン窒化物、酸化モリブデン、白金、ルテニウム、酸化ルテニウム、イリジウム、および酸化イリジウムを含む。他の材料は、以上に、および表2に、記載される。電極「ペア」は、他のペアリングも可能であるが、n型ポリシリコンおよび窒化チタン；窒化チタン、タングステン窒化物またはタンタル窒化物および白金、ルテニウム、酸化ルテニウム、イリジウム、酸化イリジウム、モリブデン窒化物、または酸化モリブデンを含んでもよい。他の電極は、金属ケイ化物（図14を参照）および無電解に堆積された電極（例えば無電解ニッケル）を含む。これらの電極は、酸化シリコン界面層214を除去し、したがって、形成電圧を低減するために用いることができる。

20

#### 【0076】

いくつかの実施形態において、電極206および208は、スイッチング層210に等原子価でドープするために選択することができる。言いかえれば、電極206および208の少なくとも1つは、スイッチング層210の最も一般的な酸化状態または原子価と同一の最も一般的な酸化状態または原子価を有する。いくつかのメモリ素子102において、等原子価ドーピングは、スイッチング層210において深トラップを生成することができると考えられている。例えば、電極206は、不純物添加シリコン（+4の原子価）でありえるし、スイッチング層210は、ハフニウム（+4の原子価）酸化物でありえる。他の実施形態において、電極206または208は、窒化チタン（チタンは+4の原子価を有する）、白金（+4の原子価）などを含むことができる。シリコンは、より大きな抵抗変化およびより高いオン／オフ電流比を生成するために用いることができる深トラップを生成して、ハフニウム酸化物に等原子価にドープする。異原子価ドーピングは、いくつかの事例において、ドナーとアクセプタ（それらは、浅いトラップであり、抵抗状態において大きな差分を示さない抵抗性変化メモリに帰着してもよい）を生成してもよい。

30

### D. 材料系

#### 【0077】

表2は、本明細書に記載されるメモリ素子102のための可能な材料系のリストを含む。ある組み合わせが表2に記載されるが、様々な他の構成は、本明細書に記載されたメモリ素子102の範囲内で可能である。例えば、他の電極物質（例えば、モリブデン窒化物またはモリブデン窒化物）またはスイッチング材料は、用いられることができる。

40

【表2】

|   | 電極206                                | 電極214                  | スイッチング層210                                                                                                                                                   | スイッチング層212                                                                                                                                 | 電極208                                   |

|---|--------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1 | n型ポリシリコン<br>p型ポリシリコン                 | 0-10A SiO <sub>x</sub> | HfO <sub>x</sub> 30-100A<br>or ~50A                                                                                                                          | TiO <sub>x</sub> {1-15A or<br>5A or 8A},<br>AlO <sub>x</sub> {1-15A or<br>5A or 8A},<br>ZrO <sub>x</sub> {1-15A or<br>5A or 8A} or<br>None | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

| 2 | n型ポリシリコン<br>p型ポリシリコン                 | 0-10A SiO <sub>x</sub> | Hf <sub>x</sub> M <sub>y</sub> O <sub>z</sub> 30-<br>100A or ~50A<br>where M = Al,<br>Zr, Ti, La, Sr                                                         | TiO <sub>x</sub> {1-15A or<br>5A or 8A},<br>AlO <sub>x</sub> {1-15A or<br>5A or 8A},<br>ZrO <sub>x</sub> {1-15A or<br>5A or 8A} or<br>None | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

| 3 | n型ポリシリコン<br>p型ポリシリコン                 | 0-10A SiO <sub>x</sub> | HfO <sub>x</sub> , CeO <sub>x</sub> ,<br>AlO <sub>x</sub> , TaO <sub>x</sub> ,<br>Y <sub>x</sub> , ZrO <sub>x</sub> ,<br>ZnO <sub>x</sub> , CuO <sub>x</sub> | Ti, TiO <sub>x</sub> or<br>None                                                                                                            | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

| 4 | TiN, TaN, W, WN,<br>Ni, Cu, Al, TiAl | None                   | HfO <sub>x</sub> 30-100A<br>or ~50A                                                                                                                          | Ti, TiO <sub>x</sub> or<br>None                                                                                                            | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

| 5 | TiN, TaN, W, WN,<br>Ni, Cu, Al, TiAl | None                   | Hf <sub>x</sub> M <sub>y</sub> O <sub>z</sub> 30-<br>100A or ~50A<br>where M = Al,<br>Zr, Ti, La, Sr                                                         | Ti, TiO <sub>x</sub> or<br>None                                                                                                            | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

| 6 | TiN, TaN, W, WN,<br>Ni, Cu, Al, TiAl | None                   | HfO <sub>x</sub> , CeO <sub>x</sub> ,<br>AlO <sub>x</sub> , TaO <sub>x</sub> ,<br>Y <sub>x</sub> , ZrO <sub>x</sub> ,<br>ZnO <sub>x</sub> , CuO <sub>x</sub> | Ti, TiO <sub>x</sub> or<br>None                                                                                                            | TiN, TaN, W,<br>WN, Ni, Cu, Al,<br>TiAl |

## V. 処理

## 【0078】

図13および図14は、界面層214の制御された堆積のためのプロセス1300および1400を記載するフローチャートである。プロセス1300は、金属分に富むスイッチング層210を生成し、かつスイッチング層210の欠陥の量を増加させるために導入された酸素の量を低減するALDプロセスを用いるスイッチング層210の堆積を記載する。加えて、プロセス1300は、界面層214の所望の厚さを取得するために、処理パラメータを選択することにより界面層214のサイズを調整するために用いることができる。プロセス1400は、界面層214を著しく低減または除去するケイ化物電極206の堆積を記載する。

## 【0079】

原子層堆積(ALD)は、様々な半導体処理動作中に原子スケール膜厚制御により共形層を堆積るために用いられるプロセスである。金属酸化物を堆積させるために、ALDは、2つの試薬(金属前駆体および酸素源(例えばオキシダント))の使用を含む多重ステップの自己制御式のプロセスである。一般に、第1の試薬は、基板を含んでいる処理室に導入され、基板の表面上に吸着する。第1の試薬の超過分は、除去および/または排出される。その後、第2の試薬は、チャンバに導入され、堆積反応を介して堆積させた層を形成するために吸着層で反応する。堆積反応は、反応が一旦終了するという点で自己制御式であり、最初に吸着層は、第2の試薬での反応によって使い果たされる。第2の試薬の超過分は、除去および/または排出される。前述のステップは、1つの堆積またはALD「サイクル」を構成する。そのプロセスは、全体の堆積膜厚さを判定する複数のサイクルで、次の層を形成するために繰り返される。

## 【0080】

図13に戻って、プロセス1300は、動作1302において、基板上に下部電極を堆積させることから開始する。下部電極(例えば電極206)は、以上に記載された電極物質の1つであってもよい。但し、1つの実施形態において、下部電極は、スイッチング層

10

20

30

40

50

210の堆積中に二酸化けい素の界面層214を形成してもよいポリシリコン電極である。他の実施形態において、下部電極は、スイッチング層210の堆積中にも酸化することができる金属電極である。

#### 【0081】

動作1304において、薄いPVD金属酸化物層は、状況に応じて基板上に堆積させる。薄いPVD金属酸化物層は、PVD堆積プロセスが界面層214の成長を促進しないことが示されているので、界面層214を除去するために用いられることがある（例えば図5を参照）。一旦、薄い（例えば10未満）PVD金属酸化物層が堆積されれば、動作1306において、ALDプロセスは実行されることができる。

#### 【0082】

動作1306において、スイッチング層210は、ALDを用いて堆積される。動作1304は、ALDプロセスのいくつかのサイクルを記載するいくつかの構成要素動作1308～1320を含む。これらの動作のいくつかは、任意に、または異なる順序で完了してもよい。

#### 【0083】

動作1308において、ALDプロセスの堆積温度は、状況に応じて低下させる。例えば、堆積温度は、加熱される基板台座の温度（すなわち台座温度）を低下させることにより低下させてよい。いくつかの例において、堆積温度または台座温度は、250以下、200以下、175以下などであってもよい。より低い温度は、スイッチング層210において電気的欠陥の濃度を変更して、酸化中に表面種の変換平衡を変動させてよい。加えて、低減された堆積温度は、熱酸化のレートを低減することにより、界面層214を低減または除去することができる。例えば、シリコン電極206を用いる場合、200未満にALD堆積温度を低減するために、任意の界面層214を実質的に低減してもよい。

#### 【0084】

動作1310において、前駆物質源は、所望の圧力で保持される。所望の蒸気圧は、前駆物質源の温度を制御することにより達成することができる。前駆物質源は、ALD堆積チャンバの外側にあり、したがって、堆積チャンバの温度以外の異なる温度で保持されることがある。所望の温度および圧力は、用いられる前駆物質に依存する。例えば、ハフニウム酸化物を堆積させるためにテトラキス（ジメチルアミノ）ハフニウム（TDMAH）を用いる場合、前駆物質源は、30～100、または40～50に保持することができる。いくつかの実施形態において、前駆物質源の温度は、前駆物質の分圧を増加させるために、増加させることができ、それは、チャンバの金属前駆体の濃度を増加させることにより、より金属分に富むスイッチング層を生成することもできる。動作1312において、前駆物質は、ALDプロセスを開始するために下部電極を含む基板に導入される。

#### 【0085】

動作1314および動作1316は、金属酸化物を形成するために用いられる酸素源の処理を記載する。メモリ素子102の特性に依存して、動作1314および動作1316のいずれか一方またはその両方は、界面層214の厚さを制御するために用いられることがある。酸素源は、オゾン、酸素、水蒸気、イソプロピルアルコール（IPA）、エタノールまたは他のアルコール、または他のALD酸素源でありえる。いくつかの構成のために、ALDプロセスにおいて酸素源として水蒸気を用いることは、スイッチング特性を改善したメモリ素子に起因している。

#### 【0086】

動作1314において、酸素源が水またはイソプロピルアルコールなどの液体または固体である場合、より少ない酸素を有するスイッチング層210を生成するための典型である、より低い蒸気圧で保持される。オキシダントの分圧は、その蒸気圧を低減する源温度を低減することにより低減することができる。分圧は、また、アルゴンなどの不活性ガスによりオキシダントを薄めることにより低減することができる。酸素とオゾンなどのいくつかのオキシダントは、それらの源ではガスであり、したがって、それらの分圧は、源温

10

20

30

40

50

度を変化させることでは操作することができない。酸化の度合いを低減する第3の方法は、オキシダント自体の選択を通じてである。例えば、水蒸気があまり酸化していなくて、IPAとエタノールもあまり酸化していない一方で、オゾンと酸素は、より酸化している（すなわち、より多くの酸素を有する層をより迅速に生成する）という傾向がある。薄膜において酸素の量を低減する一方で、チャンバの酸素源の量の限定は、なお薄膜が自己制御式であることを可能にする。金属原子に付着された反応しない配位子は、後堆積処理を通じて、部分的にまたはほとんど全面的に除去することができる。その後、酸素欠損の薄膜は、酸素空孔（それはメモリ素子102のスイッチングを制御するために用いることができる欠陥である）を有するだろう。

## 【0087】

10

例え、金属分に富むハフニウム酸化物スイッチング層210を堆積させるために、水蒸気は、酸素源として用いられることができ、水蒸気源は、0～10などの低温度に維持することができる。低温度は、ALDサイクル当たりの酸化の量を効果的に低減し、酸素源の蒸気圧を低減する。この技術を用いて形成されたハフニウム酸化膜は、 $HfO_{1.2} \sim HfO_{1.9}$ 、または $HfO_{1.7}$ の元素組成において帰着することができる。一般に、酸素濃度は、化学量論的組成の60～95%に低減することができる（すなわち、酸素の量は、化学量的な金属酸化物（例え $HfO_{1.2} \sim HfO_{1.9}$ ）の60～95%である）。IPAまたはエタノールは、酸素を供給するために用いることができるが、同一の温度で、水蒸気より少ない酸素または以上に記載された他の酸素源を供給するだろう。したがって、スイッチング層210において酸素の量を低減するためにIPAとエタノールにより同様の温度低減を用いることができるが、IPAまたはエタノールは、室温源を用いて、金属分に富む薄膜を堆積させることができてもよい。

## 【0088】

20

動作1318において、金属酸化物のALD層を生成するために、酸素源は基板に導入される。単一のALDサイクルは、厚さが例え0.5のである薄膜を堆積させてもよい。また、多重のサイクルは、所望の厚さのスイッチング層210を構築するために典型的には必要とされる。動作1320において、より多くのサイクルが必要とされるならば、プロセス1300は、動作1308に戻る。これ以上のサイクルが必要とされないならば、プロセス1300は、動作1322に続く。

## 【0089】

30

動作1322において、カップリング層が堆積される。カップリング層212は、スイッチング層の厚さの例え25パーセント未満の薄層でありえる。カップリング層212は、ALD、PVDなどの任意の堆積方法を用いて堆積させることができる。動作1324において、上部電極（例え電極208）が堆積される。

## 【0090】

動作1326において、メモリ素子がアニールされる。アニーリングは、ALDプロセスの低い堆積温度のため、薄膜において存在するかもしれない反応しない前駆物質配位子を除去することができる。一例において、真空アニール、酸化アニールなどの他のアニールを用いることもできるが、素子は、水素／アルゴン混合液（例え2～10%の水素、90～98%のアルゴン）を用いてアニールされる。

## 【0091】

40

図14に戻って、プロセス1400は、メモリ素子102で使用される下部電極206の形成を記載する。プロセス1400は、そのように所望されるならば、界面層214を除去するために用いることができるケイ化物電極の堆積を記載する。いくつかの実施形態において、ケイ化物電極は、スイッチング層210の堆積中に界面層214を形成しない。プロセス1400は、いくつかの実施形態において、プロセス1300と共に用いられることができる。例え、プロセス1400の動作1402～1412は、プロセス1300の動作1302に代用することができる。

## 【0092】

動作1402において、下部電極（例え電極206）は基板上に堆積される。下部電

50

極は、動作 1404～1412 に従って堆積される金属ケイ化物（例えば、チタン、コバルト、ニッケル、パラジウム、白金ケイ化物）である。

#### 【0093】

動作 1404において、シリコンは、基板上に堆積される。動作 1406において、チタン、コバルト、ニッケル、モリブデン、パラジウムまたは白金などの金属は、シリコン上に堆積される。動作 1408において、熱処理は、金属をシリコンに相互に拡散することにより、ケイ化物層を形成するために実行される。動作 1410において、任意の反応しない金属は、電極から剥がれ、動作 1412において、電極は、電極の比抵抗値を低下させるために状況に応じてアニールされることができる。

#### 【0094】

ケイ化物電極が堆積させた後、動作 1414において、スイッチング層は、（例えば、プロセス 1300において記載されていた技術を用いて）電極上に堆積され、動作 1416において、上部電極（例えば電極 208）は、スイッチング層上に堆積される。ケイ化物電極は、酸化物層の形成に抵抗し、したがって、界面層 214 を形成しない。いくつかの実施形態において、界面層 214 を保持することは望ましいかもしれないが、他において、界面層 214 を除去することのほうが望ましく、プロセス 1400 は、そのようにするための代替技術である。

#### 【0095】

図 15 は、様々な実施形態によってメモリ素子を形成するプロセス 1500 を記載するフローチャートである。プロセス 1500 は、そのように所望するならば、動作 1300 において記載されていたプロセスと共に用いられることができる。

#### 【0096】

動作 1502において、下部電極は、基板上に堆積される。下部電極は、例えば n 型ポリシリコンまたは本明細書に記載される他の材料でありえる。動作 1504において、スイッチング層 210 は、下部電極上に堆積される。スイッチング層 210 は、例えば HfO<sub>x</sub>、CuO<sub>x</sub>、ZnO<sub>x</sub>、CeO<sub>x</sub>などの以上に記載された材料のいずれかでありえる。スイッチング層 210 は、ALD または PEALD などの適合する堆積技術を用いて堆積されることができる。

#### 【0097】

動作 1506において、スイッチング層 210 は状況に応じてドープされる。例えば、スイッチング層 210 は、p 型のスイッチング層（例えば、p 型の ZnO<sub>x</sub> または CuO<sub>x</sub> 層）を生成するためにドープされてもよい。動作 1508において、金属または部分的に金属（例えば、Ti または Ti / TiO<sub>x</sub>）または金属酸化物（例えば、ZrO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>）などのカップリング層は、スイッチング層上に堆積される。

#### 【0098】

動作 1210において、メモリ素子は、例えば、短時間熱酸化（RTO）、水素 / アルゴン混合液、真空アニールなどを用いてアニールされる。アニーリングは、いくつかの実施形態（例えば図 2B を参照）において、金属酸化物スイッチング層 210 からカップリング層 212 に酸素を移行させることができる。

### V I . 代表的なデータ

#### A . スイッチング特性

#### 【0099】

表 3 は、本明細書に記載された実施形態を用いて形成されたメモリ素子、および比較としての他のメモリ素子のための様々なスイッチングメトリクスを含む。

#### 【0100】

HfO<sub>x</sub> / TiO<sub>2</sub> は、n 型ポリシリコン電極 206、250 で堆積させた 50 の厚さのハフニウム酸化物スイッチング層 210、250 で堆積させた 8 の酸化チタンカップリング層 212、および窒化チタン電極 208 を含むメモリ素子を指す。

#### 【0101】

HfO<sub>x</sub> / Al<sub>2</sub>O<sub>3</sub> は、n 型ポリシリコン電極 206、250 で堆積させた 50

10

20

30

40

50

の厚さのハフニウム酸化物スイッチング層 210、250 で堆積させた 8 の酸化アルミニウムカップリング層 212、および窒化チタン電極 208 を含むメモリ素子を指す。

#### 【0102】

$HfO_x/ZrO_2$  は、n 型ポリシリコン電極 206、250 で堆積させた 50 の厚さのハフニウム酸化物スイッチング層 210、250 で堆積させた 8 の酸化ジルコニウムカップリング層 212、および窒化チタン電極 208 を含むメモリ素子を指す。

#### 【0103】

$HfAl_xO_y$  は、n 型ポリシリコン電極 206、250 で堆積させた 58 のアルミニウムがドープされたハフニウム酸化物スイッチング層 210、および窒化チタン電極 208 を含むメモリ素子を指す。

10

#### 【0104】

すべてのデータは二極性スイッチングのためのものであり、収率は、確実に切り替えるメモリ素子の与えられたサンプルにおけるパーセンテージを指す。電極 208 は、接地され、パルスは、電極 206 で適用される。見て分かるように、 $HfO_x/Al_2O_3$  および  $HfO_x/ZrO_2$  メモリ素子内の高バンドギャップのカップリング層は、改善された形成電圧またはリセット電圧、および改善されたサイクル収率を示す。

#### 【0105】

$HfAl_xO_y$  および  $HfO_x/Al_2O_3$  メモリ素子は、同一の厚さおよび同一の材料成分を有している。但し、 $HfO_xZAl_2O_3$  メモリ素子がバルクハフニウム酸化物層および小さな酸化アルミニウムカップリング層を有する一方、 $HfAl_xO_y$  メモリ素子は、アルミニウムがドープされ、ハフニウム酸化物層を通じて分散されたアルミニウムを有する。 $HfO_x/Al_2O_3$  のためのスイッチング特性は、改善されたスイッチングがカップリング層 212 とスイッチング層 210 との間の界面で形成された欠陥ためであるかもしれないことを示唆して、より優れている。

20

### B. 界面層

#### 【0106】

プロセス 1300において記載された技術は、界面層 214 を実質的に除去したメモリ素子 102 を堆積させるために用いられた。酸化アルミニウムは、トリメチルアルミニウムおよび水蒸気を用いて堆積された。気相における水蒸気の量は、水蒸気源の温度を 1 ~ 5 に低下させることにより制限された。この技術を用いると、界面層 214 の厚さは、1.1 ナノメートルから約 0 に減った（水源が室温に維持された場合）。いくつかの実施形態において、界面層 214 の除去は、形成電圧を低減してもよい。

30

#### 【0107】

図 16A は、低仕事関数電極が負電圧セットパルスおよび正電圧リセットパルスを受信する場合の、高サイクル収率を示すグラフ 1600 である。メモリ素子構成は、n 型ポリシリコン電極 206、原子層堆積 (ALD) - 堆積されたハフニウム酸化物スイッチング層 210、ALD - 堆積された酸化チタンカップリング層 212、および物理気相堆積 (PVD) - 堆積された窒化チタン電極 208 を含む。プロット 1602 は、低い仕事関数の電極（ここでは n 型ポリシリコン電極）が、共通の電気的基準に関する負電圧セットパルスおよび正電圧リセットパルスを受信するメモリ素子を示す。共通の電気的基準は、接地、+2V などの任意の電圧でありえる。その電圧が電極にて顕著ならば、電極は電圧を受信すると言われている。例えば、電圧パルスが他の場所で発信したとしても、ポリシリコン電極 206 は、正のリセット電圧を参照してもよい。

40

#### 【0108】

プロット 1602 において見て分かるように、低い仕事関数の電極が負電圧セットパルスを受信するメモリ素子の約 85% は、100 サイクルまで存続する。対照的に、プロット 1604 は、低い仕事関数の電極が正電圧セットパルスおよび負電圧リセットパルスを受信するメモリ素子を示す。見て分かるように、これらのメモリ素子はどれも、過去の 60 のサイクルまで残存しないし、ほとんどは、10 サイクルまで残存しない。そして、本明細書に記載されたメモリ素子を用いるとき、低い仕事関数の電極は、負電圧セットパル

50

スおよび正電圧リセットパルスを受信するべきであることを推測することができる。

#### 【0109】

図16Bは、2つの電極が0.1eVと1.0eVとの間で異なる仕事関数を有する場合の高サイクル収率を示すグラフ1620である。0.1eVを超える1.0eV未満により異なる仕事関数を有する電極206および208を含むメモリ素子は、1.0eVを超えることにより異なる仕事関数を有する電極を含むメモリ素子と比較して、高サイクル収率を示す。グラフ1620は、プロット1622および1624によって表わされる、2つのメモリ素子構成のためのサイクル収率を示す。プロット1622によって表わされる構成は、n型ポリシリコン電極206、ハフニウム酸化物スイッチング層210、酸化チタンカッピング層212、および窒化チタン電極208を含む。窒化チタンが約4.5～4.6eVの仕事関数を有する一方、n型ポリシリコンは、約4.1eVの仕事関数を有しており、約0.4～0.5eVの差分を与えていた。プロット524によって表わされる構成は、n型ポリシリコン電極402、ハフニウム酸化物スイッチング層406、酸化チタン層418、および白金電極404を含む。白金が約5.7eVの仕事関数を有する一方、n型ポリシリコンは、約4.1eVの仕事関数を有しており、約1.6eVの差分を与えていた。見て分かるように、プロット524が低値サイクル収率を示している一方、プロット522は高サイクル収率を示しており、1.0eV未満の仕事関数の差分を有する場合に本明細書に記載されたメモリ素子において用いられる電極がより効果的であることを示している。10

#### D、カッピング層の厚さおよびスイッチング収率

20

#### 【0110】

サイクル収率は、高バンドギャップの材料（すなわち4eVを超えるバンドギャップによる材料）の増加された厚さおよびカッピング層で改善されることが示された。表4は、低い仕事関数の電極がセットパルス中に正の場合に二極性スイッチングを用いて評価された、いくつかのメモリ素子のためのサイクル収率を表している。各々の構成のために18の素子がテストされ、各メモリ素子は、金属酸化物スイッチング層の下で、n型ポリシリコン電極およびカッピング層の上の窒化チタン電極を含む。見て分かるように、他の組み合わせ（例えば70のハフニウム酸化物層）も容認できる結果を示しているが、最高値のサイクル収率は、50の厚さのハフニウム酸化物層および5の厚さの酸化チタン層を含むメモリ素子のためのものである。30

#### 【表4】

| 金属酸化物スイッチング層     |     | カッピング層           |      | サイクル<br>収率 |

|------------------|-----|------------------|------|------------|

| 材料               | 厚さ  | 材料               | 厚さ   |            |

| HfO <sub>2</sub> | 20Å | None             | None | 29.3%      |

| HfO <sub>2</sub> | 50Å | None             | None | 32.2%      |

| HfO <sub>2</sub> | 70Å | None             | None | 51.7%      |

| HfO <sub>2</sub> | 30Å | TiO <sub>2</sub> | 5Å   | 35.1%      |

| HfO <sub>2</sub> | 50Å | TiO <sub>2</sub> | 5Å   | 89.3%      |

40

#### 【0111】

金属酸化物層の厚さが金属酸化物層とカッピング層との全体の厚さの80%を超えていたメモリ素子は、改善されたサイクル収率を示すことができる。例えば、50のハフニウム酸化物層および5の酸化チタン層を含むメモリ素子は、厚さによる80%以上のハフニウム酸化物を含み、高サイクル収率を示す。対照的に、30のハフニウム酸化物層および5の酸化チタン層を含むメモリ素子は、厚さによる80%未満のハフニウム酸化物を含み、低スイッチング収率を示す。したがって、高バンドギャップ（すなわち4eVを超える）材料の存在は、改善されたスイッチング特性に結びつく。

#### 【0112】

50

加えて、他のメモリ素子設計は、不純物添加ポリシリコンの下部電極、ポリシリコン電極に隣接した 5 の酸化チタン層、および酸化チタン層と窒化チタンの上部電極との間の 50 のハフニウム酸化物層を有する M I S 型スタックを含む。この設計は、メモリ素子内の金属酸化物層の配置が装置耐久生存に影響を与える場合があることを例証し、 33 . 3 % ( 100 サイクルが残存する 18 個の装置のうち 6 個 ) のサイクル収率を示した。

#### 【 0113 】

他の高バンドギャップの材料（例えば TaO<sub>x</sub>、AlO<sub>x</sub>、LaO<sub>x</sub>、ZrO<sub>x</sub>、YO<sub>x</sub>）は、上記の表のハフニウム酸化物を代用または補足することができ、好結果を示す。例えば、ハフニウム酸化物層は、酸化アルミニウム層、酸化ランタン層、ハフニウム酸化アルミニウム層、またはハフニウム酸化ランタン層と置き換わることができる。

10

#### VII. 代表的な実施形態

##### 【 0114 】

1つの実施形態によれば、抵抗スイッチングメモリ素子は、第 1 の電極および第 2 の電極と、ハフニウム酸化物を含み、第 1 の厚さを有する、前記第 1 の電極と前記第 2 の電極との間のスイッチング層と、前記スイッチング層と前記第 2 の電極との間のカップリング層であって、酸化アルミニウムおよび酸化ジルコニアから構成されるグループから選択される材料を含む前記カップリング層であり、前記第 1 の厚さの 25 パーセント未満である第 2 の厚さを有する前記カップリング層とを備えることを規定される。

##### 【 0115 】

1つのさらなる実施形態によれば、前記メモリ素子の前記第 1 の電極は、不純物添加シリコンであり、前記メモリ素子は、前記第 2 の電極にて、共通の電気的基準に関する負のリセット電圧と前記共通の電気的基準に関する正のセット電圧とを受信するように構成される。

20

##### 【 0116 】

1つのさらなる実施形態によれば、前記メモリ素子の前記第 1 の電極は、第 1 の材料を含み、前記第 2 の電極は、第 2 の材料を含み、前記第 1 の材料は前記第 2 の材料とは異なる。

##### 【 0117 】

1つのさらなる実施形態によれば、前記第 1 の電極の前記第 1 の材料は、不純物添加シリコンであり、前記第 2 の電極の前記第 2 の材料は、窒化チタンである。

30

##### 【 0118 】

1つのさらなる実施形態によれば、前記メモリ素子の前記第 1 の厚さは、 20 ~ 100 オンゲストロームである。

##### 【 0119 】

1つのさらなる実施形態によれば、前記メモリ素子の前記スイッチング層は、 HfO<sub>1</sub><sub>.2</sub> と HfO<sub>1</sub><sub>.7</sub> との間の元素組成を有するハフニウム酸化物原料を含む。

##### 【 0120 】

1つのさらなる実施形態によれば、前記第 1 の電極の前記第 1 の材料は、 n 型ポリシリコンである。

##### 【 0121 】

1つのさらなる実施形態によれば、前記メモリ素子の前記第 1 の電極および前記第 2 の電極の少なくとも 1 つは、前記スイッチング層に同一の最も一般的な酸化状態を有する。

40

##### 【 0122 】

1つのさらなる実施形態によれば、前記メモリ素子は、前記第 1 の電極と前記スイッチング層との間の界面層であって、 10 未満の厚さを有する前記界面層をさらに備える。

##### 【 0123 】

1つのさらなる実施形態によれば、前記メモリ素子の前記界面層は、酸化シリコンを含む。

##### 【 0124 】

1つのさらなる実施形態によれば、前記メモリ素子の前記第 2 の電極の仕事関数は、前

50

記第1の電極の仕事関数より高く、前記第1の電極は、共通の電気的基準に関する負電圧を有する形成電圧パルスを受信するように構成される。

【0125】

別の実施形態によれば、抵抗スイッチングメモリ素子は、第1の電極および第2の電極と、前記第1の電極と前記第2の電極との間のスイッチング層であって、前記スイッチング層は4電子ボルト(eV)を超える第1のバンドギャップを有する第1の金属酸化物を含み、第1の厚さを有する前記スイッチング層と、前記スイッチング層と前記第2の電極との間のカップリング層であって、前記第1のバンドギャップ以上の第2のバンドギャップを有する第2の金属酸化物を含む前記カップリング層であり、前記第1の厚さの25パーセント未満である前記第2の厚さを有する前記カップリング層とを備えることを規定される。

10

【0126】

1つのさらなる実施形態によれば、前記メモリ素子の前記第1の金属酸化物は、正規組成の60~95%である酸素濃度を有する。

【0127】

1つのさらなる実施形態によれば、前記メモリ素子の前記第1の電極は、不純物添加シリコンと、窒化チタンとから構成されるグループから選択され、前記第2の電極は、モリブデン窒化物と、酸化モリブデンと、窒化チタンと、タンゲステンと、タンタル窒化物と、モリブデン窒化物と、酸化モリブデンと、白金と、ルテニウムと、ニッケルと、イリジウムと、酸化イリジウムと、酸化ルテニウムとから構成されるグループから選択される。

20

【0128】

1つのさらなる実施形態によれば、前記スイッチング層の前記第1の厚さは、20と100との間である。

【0129】

1つのさらなる実施形態によれば、前記第1の金属酸化物の第1の金属は、前記第2の金属酸化物の前記第2の金属の第2の最も一般的な酸化状態とは異なる第1の最も一般的な酸化状態を有する。

【0130】

1つのさらなる実施形態によれば、前記第1の金属酸化物の前記第1の金属および前記第2の金属酸化物の前記第2の金属は、同一の最も一般的な酸化状態を有する。

30

【0131】

1つのさらなる実施形態によれば、前記第2の金属酸化物の第2の金属は、前記第1の金属酸化物の第1の金属の第1の最も一般的な酸化状態以下である第2の最も一般的な酸化状態を有する。

【0132】

1つのさらなる実施形態によれば、前記第1の金属酸化物は、ハフニウム酸化物であり、前記第2の金属酸化物は、酸化ジルコニアムと酸化アルミニウムとから構成されるグループから選択される。

【0133】

1つのさらなる実施形態によれば、前記第1の金属酸化物は、ハフニウム酸化物と、タンタルオキサイドと、酸化アルミニウムと、酸化ジルコニアムと、イットリウム酸化物とから構成されるグループから選択され、前記第2の金属酸化物は、酸化ジルコニアムと、酸化アルミニウムとから構成されるグループから選択される。

40

【0134】

1つのさらなる実施形態によれば、前記第1の電極は、不純物添加シリコンを含み、前記第1の電極と前記スイッチング層との間の界面層であって、酸化シリコンを含み10未満の厚さを有する前記界面層をさらに含む。

【0135】

1つのさらなる実施形態によれば、前記第1の電極は、チタンケイ化物と、コバルトケイ化物と、ニッケルケイ化物と、パラジウムケイ化物と、白金ケイ化物とから構成される

50

グループから選択されたケイ化物を含む。

**【 0 1 3 6 】**

1つのさらなる実施形態によれば、前記メモリ素子は、3次元メモリアレイの一部である。

**【 0 1 3 7 】**

別の実施形態によれば、抵抗スイッチングメモリ素子を形成する方法は、

基板上に第1の電極を堆積させるステップと、

原子層堆積（ALD）を用いて、前記第1の電極の表面に金属酸化物を含むスイッチング層を堆積させるステップであって、

摂氏40度を超えた状態で前駆物質を保持するステップと、

前記前駆物質を基板に導入するステップと、

摂氏10度未満で酸素源を保持するステップと、

前記酸素源を基板に導入するステップとをさらに含む前記スイッチング層を堆積する

前記ステップと、

前記スイッチング層の表面に第2の電極を堆積させるステップとを含むことを規定される。

**【 0 1 3 8 】**

1つのさらなる実施形態によれば、前記酸素源は、水蒸気と、イソプロピルアルコール（IPA）と、エタノールとのうちの少なくとも1つである。

**【 0 1 3 9 】**

1つのさらなる実施形態によれば、前記金属酸化物は、ハフニウム酸化物と、タンタルオキサイドと、酸化アルミニウムと、イットリウム酸化物と、酸化ジルコニウムとから構成されるグループから選択される。

**【 0 1 4 0 】**

1つのさらなる実施形態によれば、前記金属酸化物は、正規組成の60～95パーセントである酸素濃度を有している。

**【 0 1 4 1 】**

1つのさらなる実施形態によれば、前記金属酸化物は、ハフニウム酸化物であり、HfO<sub>1.2</sub>とHfO<sub>1.7</sub>との間に元素組成を有する。

**【 0 1 4 2 】**

1つのさらなる実施形態によれば、前記ALDのための堆積温度は、摂氏250度未満である。

**【 0 1 4 3 】**

1つのさらなる実施形態によれば、前記ALDのための堆積温度は、摂氏約200度である。

**【 0 1 4 4 】**

1つのさらなる実施形態によれば、前記方法は、前記第2の電極を堆積させた後に前記メモリ素子をアニールするステップを含む。

**【 0 1 4 5 】**

1つのさらなる実施形態によれば、前記方法は、物理気相堆積（PVD）を用いて、前記第1の電極の表面に物理気相堆積層を堆積させるステップをさらに含み、前記スイッチング層は、前記PVD層上に堆積され、前記PVD層は、前記スイッチング層と同一の材料を含む。

**【 0 1 4 6 】**

1つのさらなる実施形態によれば、前記方法は、前記スイッチング層の表面にカップリング層を堆積させるステップであって、前記カップリング層は前記スイッチング層の厚さの25パーセント未満である厚さを有するステップをさらに含む。

**【 0 1 4 7 】**

1つのさらなる実施形態によれば、前記カップリング層のバンドギャップは、前記スイッチング層のバンドギャップより大きい。

10

20

30

40

50

## 【0148】

1つのさらなる実施形態によれば、前記カップリング層は、酸化アルミニウムと酸化ジルコニウムとから構成されるグループから選択される。

## 【0149】

別の実施形態によれば、抵抗スイッチングメモリ素子を形成する方法は、基板上に第1の電極を堆積させるステップと、前記第1の電極の表面にスイッチング層を堆積させるステップであって、前記スイッチング層は、第1の厚さを有し、4電子ボルト(eV)を超えている第1のバンドギャップを有しているステップと、前記スイッチング層の表面にカップリング層を堆積させるステップであって、前記カップリング層は、前記第1の厚さの25パーセント未満である第2の厚さと、前記第1のバンドギャップ以上である第2のバンドギャップとを有するステップと、前記カップリング層の表面に第2の電極を堆積させるステップとを含むことを規定される。 10

## 【0150】

1つのさらなる実施形態によれば、前記第1の電極は、不純物添加シリコンであり、スイッチング層を堆積させるステップは、前記第1の電極と前記スイッチング層との間の酸化シリコンを含む界面層を形成するステップであって、前記界面層が10未満の厚さを有するステップを含む。

## 【0151】

1つのさらなる実施形態によれば、前記スイッチング層は、ハフニウム酸化物と、タンタルオキサイドと、酸化アルミニウムと、イットリウム酸化物と、酸化ジルコニウムとから構成されるグループから選択される。 20

## 【0152】

1つのさらなる実施形態によれば、前記カップリング層は、酸化ジルコニウムと、酸化アルミニウムとから構成されるグループから選択される。

## 【0153】

1つのさらなる実施形態によれば、前記スイッチング層を堆積させるステップは、摂氏40度を超えた状態で前駆物質を保持し、前記前駆物質を前記基板に導入し、摂氏10度未満で酸素源を保持し、酸素源を前記基板に導入するステップを含む、原子層堆積(ALD)を用いるステップを含む。 30

## 【0154】

1つのさらなる実施形態によれば、前記スイッチング層を堆積させるステップは、正規組成の60~95パーセントである酸素濃度を有する金属酸化物を堆積させるステップを含む。

## 【0155】

1つのさらなる実施形態によれば、前記方法は、前記メモリ素子をアニールするステップを含む。

## 【0156】

1つのさらなる実施形態によれば、前記酸素源は、水蒸気と、イソプロピルアルコールと、エタノールとのうちの少なくとも1つである。 40

## 【0157】

別の実施形態によれば、抵抗スイッチングメモリ素子は、第1の電極および第2の電極と、ハフニウム酸化物を含み、第1の厚さを有する、前記第1の電極と前記第2の電極との間のスイッチング層と、前記スイッチング層と前記第2の電極との間のカップリング層であって、部分的に金属チタンと部分的に酸化チタンとを含み、前記第1の厚さの25パーセント未満である第2の厚さを有する材料を含む前記カップリング層とを備えることを規定される。

## 【0158】

1つのさらなる実施形態によれば、前記第1の電極は、不純物添加シリコンであり、前記メモリ素子は、前記第2の電極にて、共通の電気的基準に関する負のリセット電圧と、前記共通の電気的基準に関する正のセット電圧とを受信するように構成される。 50

**【0159】**

1つのさらなる実施形態によれば、前記第1の厚さは、20～100オングストロームである。

**【0160】**

1つのさらなる実施形態によれば、前記スイッチング層は、 $HfO_{1.2}$ と $HfO_{1.7}$ との間の元素組成を有するハフニウム酸化物原料を含む。

**【0161】**

1つのさらなる実施形態によれば、前記第1の材料は、n型ポリシリコンである。

**【0162】**

1つのさらなる実施形態によれば、前記メモリ素子は、前記第1の電極と前記スイッチング層との間の界面層であって、10未満の厚さを有する前記界面層を備える。 10

**【0163】**

1つのさらなる実施形態によれば、前記第1の金属酸化物は、正規組成の60～95%である酸素濃度を有する。

**【0164】**

1つのさらなる実施形態によれば、前記メモリ素子の前記第1の電極は、不純物添加シリコンと、窒化チタンとから構成されるグループから選択され、前記第2の電極は、モリブデン窒化物と、酸化モリブデンと、窒化チタンと、タンゲステンと、タンタル窒化物と、モリブデン窒化物と、酸化モリブデンと、白金と、ルテニウムと、ニッケルと、イリジウムと、酸化イリジウムと、チタン／アルミニウム合金と、酸化ルテニウムとから構成されるグループから選択される。 20

**【0165】**

1つのさらなる実施形態によれば、前記第1の電極は、不純物添加シリコンを含み、前記第1の電極と前記スイッチング層との間の界面層であって、酸化シリコンを含み10未満の厚さを有する前記界面層をさらに含む。

**【0166】**

別の実施形態によれば、抵抗スイッチングメモリ素子は、不純物添加シリコンを含む第1の電極と、遷移金属と、遷移金属合金と、遷移金属窒化物と、遷移金属炭化物とから構成されるグループから選択される材料を含む第2の電極と、前記第1の電極と前記第2の電極との間のスイッチング層であって、ハフニウム酸化物と、酸化ジルコニアと、酸化チタンと、酸化セリウムと、酸化亜鉛と、酸化ランタンと、酸化銅とから構成されるグループから選択される金属酸化物を含む前記スイッチング層と、前記抵抗スイッチング金属酸化物と前記第2の電極との間のカップリング層とを備えることを規定され、前記カップリング層は、少なくとも部分的にチタン金属を含む。 30

**【0167】**

1つのさらなる実施形態によれば、前記カップリング層は、チタン金属を実質的に含む第1の部分と、酸化チタンを実質的に含む第2の部分とを含む。

**【0168】**

1つのさらなる実施形態によれば、前記カップリング層の第2の部分は、前記スイッチング層に接しており、前記スイッチング層は、酸素欠損の金属酸化物を含む前記カップリング層の前記第2の部分に接する第1の部分と、前記スイッチング層の前記第1の部分より大きな酸素濃度を有する金属酸化物を含む第2の部分とを含む。 40

**【0169】**

別の実施形態によれば、抵抗スイッチングメモリ素子を形成する方法は、基板上に第1の電極を堆積させるステップと、前記第1の電極上の金属酸化物を含むスイッチング層を堆積させるステップと、前記スイッチング層上のチタン金属を含むカップリング層を堆積させるステップと、前記カップリング層上に第2の電極を堆積させるステップと、前記メモリ素子をアニールするステップと、前記カップリング層の少なくとも一部に酸化チタンを形成させ、前記スイッチング層の少なくとも一部に酸素欠損を持たせるステップとを含むことを規定される。 50

**【 0 1 7 0 】**

1つのさらなる実施形態によれば、前記スイッチング層は、酸化セリウムと、ハフニウム酸化物と、酸化アルミニウムと、タンタルオキサイドと、イットリウム酸化物と、酸化ジルコニウムとから構成されるグループから選択された金属酸化物である。

**【 0 1 7 1 】**

1つのさらなる実施形態によれば、前記スイッチング層は、p型の酸化亜鉛と、p型の酸化銅とから構成されるグループから選択された金属酸化物である。

**【 0 1 7 2 】**

1つのさらなる実施形態によれば、前記方法は、前記第1の電極上に前記スイッチング層を堆積させるステップと、p型の金属酸化物スイッチング層を形成するために前記スイッチング層をドープするステップとをさらに含む。10

**【 0 1 7 3 】**

1つのさらなる実施形態によれば、前記スイッチング層を堆積させるステップは、原子層堆積（ALD）およびプラズマ強化ALD（PEALD）のうちの少なくとも1つを用いるステップを含む。

**【 0 1 7 4 】**

1つのさらなる実施形態によれば、前記スイッチング層を堆積させるステップは、水蒸気と、イソプロピルアルコール（IPA）と、エタノールとのうちの少なくとも1つである酸素源を用いるステップを含む。

**【 0 1 7 5 】**

1つのさらなる実施形態によれば、前記ALDのための堆積温度は、摂氏250度未満である。20

**【 0 1 7 6 】**

1つのさらなる実施形態によれば、前記方法は、前記スイッチング層の厚さの25パーセント未満である厚さを有する前記カップリング層を堆積させるステップをさらに含む。

**【 0 1 7 7 】**

前述の例は、理解の明瞭さの目的のためにかなり詳細に記載されているが、本発明は、提供される詳細な記述に限定されない。本発明を実行する多くの別な方法がある。開示された例は、例示であって、限定的ではない。

【図1】

FIG. 1

【図3】

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図4】

【図5】

(△) 王蟲導通中

◇ TiN-PVD HfOx-PT

□ n-poly-ALD HfOx-TiN

○ n-poly-PVD HfOx-PT

【 四 6 】

【図 8 B】

**FIG. 8B**

【図9】

**FIG. 9**

【 図 7 】

**FIG. 7**

【図 8 A】

FIG. 8A

【図10】

【图 1-1】

【図12】

【図13】

【図14】

【図15】

【図 1 6 A】

【図 1 6 B】

---

フロントページの続き

(31)優先権主張番号 12/610,236

(32)優先日 平成21年10月30日(2009.10.30)

(33)優先権主張国 米国(US)

(31)優先権主張番号 61/168,534

(32)優先日 平成21年4月10日(2009.4.10)

(33)優先権主張国 米国(US)

(72)発明者 フタク , プラシャント

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

(72)発明者 チヤン , トニー

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

(72)発明者 ミラー , マイケル

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

(72)発明者 トン , ジンホン

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

(72)発明者 ウー , ウエン

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

(72)発明者 ハシム , イムラン

アメリカ合衆国 , カリフォルニア州 95134 , サンノゼ , 2865 ザンカー ロード

審査官 小山 満

(56)参考文献 特開2010-016381(JP, A)

国際公開第2010/038423(WO, A1)

国際公開第2010/073897(WO, A1)

国際公開第2009/015297(WO, A1)

特開2007-311798(JP, A)

(58)調査した分野(Int.Cl. , DB名)

H01L 27/105

H01L 45/00

H01L 49/00