(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7613569号**

**(P7613569)**

(45)発行日 令和7年1月15日(2025.1.15)

(24)登録日 令和7年1月6日(2025.1.6)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| H 10 D | 12/00 (2025.01) | F I | H 01 L | 29/78 | 6 5 5 F |

| H 10 D | 30/66 (2025.01) |     | H 01 L | 29/78 | 6 5 2 H |

| H 10 D | 84/80 (2025.01) |     | H 01 L | 29/78 | 6 5 2 D |

| H 10 D | 62/10 (2025.01) |     | H 01 L | 29/78 | 6 5 2 J |

H 01 L 29/78 6 5 2 M

請求項の数 12 (全21頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2023-520756(P2023-520756) |

| (86)(22)出願日       | 令和3年12月8日(2021.12.8)        |

| (86)国際出願番号        | PCT/JP2021/045100           |

| (87)国際公開番号        | WO2022/239284               |

| (87)国際公開日         | 令和4年11月17日(2022.11.17)      |

| 審査請求日             | 令和5年4月28日(2023.4.28)        |

| (31)優先権主張番号       | 特願2021-80620(P2021-80620)   |

| (32)優先日           | 令和3年5月11日(2021.5.11)        |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |

|          |                                             |

|----------|---------------------------------------------|

| (73)特許権者 | 000005234<br>富士電機株式会社<br>神奈川県川崎市川崎区田辺新田1番1号 |

| (74)代理人  | 110000877<br>弁理士法人 R Y U K A 国際特許事務所        |

| (72)発明者  | 伊倉 巧裕<br>神奈川県川崎市川崎区田辺新田1番1号                 |

| (72)発明者  | 富士電機株式会社内<br>野口 晴司<br>神奈川県川崎市川崎区田辺新田1番1号    |

| (72)発明者  | 富士電機株式会社内<br>桜井 洋輔<br>神奈川県川崎市川崎区田辺新田1番1号    |

| (72)発明者  | 富士電機株式会社内<br>浜崎 竜太郎                         |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

トランジスタ部およびダイオード部を有する活性部と、

前記活性部の外周に設けられた耐圧構造部と

を備え、

前記トランジスタ部は、

半導体基板に設けられた第1導電型のドリフト領域と、

前記ドリフト領域の上方に設けられた第2導電型のベース領域と、

前記半導体基板のおもて面から前記ドリフト領域まで延伸するトレンチ部と、

前記トレンチ部の下端に設けられた第2導電型のトレンチボトム部と

を有し、

前記ダイオード部は、上面視において、前記耐圧構造部に近接するトランジスタ部と、

前記耐圧構造部との間に設けられ、

前記トランジスタ部は複数の前記トレンチ部を有し、

前記トレンチボトム部は、隣接する前記トレンチ部の一方から他方まで延伸して設けられ

れている

半導体装置。

**【請求項2】**

前記ダイオード部の少なくとも一部から前記耐圧構造部にわたって、前記半導体基板に

設けられた第2導電型のウェル領域をさらに備え、

上面視において、前記トレンチボトム部のトレンチ配列方向における端部は、前記ウェル領域のトレンチ配列方向における端部から離間している

請求項1に記載の半導体装置。

**【請求項 3】**

前記トレンチボトム部は、電気的に浮遊している

請求項1または2に記載の半導体装置。

**【請求項 4】**

前記トレンチボトム部のドーピング濃度は、前記ドリフト領域のドーピング濃度よりも大きく、前記ベース領域のドーピング濃度よりも小さい

請求項1から3の何れか一項に記載の半導体装置。

10

**【請求項 5】**

前記トレンチボトム部のドーピング濃度は、 $1 \times 10^{12} \text{ cm}^{-3}$ 以上、 $1 \times 10^{13} \text{ cm}^{-3}$ 以下である

請求項4に記載の半導体装置。

**【請求項 6】**

前記トレンチボトム部は前記ダイオード部に設けられていない

請求項1から5の何れか一項に記載の半導体装置。

**【請求項 7】**

前記耐圧構造部において、前記半導体基板の裏面側に第1導電型のカソード領域をさらに備える

20

請求項1から6の何れか一項に記載の半導体装置。

**【請求項 8】**

前記活性部において、前記半導体基板の上方に設けられたエミッタ電極と、

前記ダイオード部の少なくとも一部から前記耐圧構造部にわたって、前記半導体基板に設けられた第2導電型のウェル領域と

をさらに備え、

前記ダイオード部において、前記ウェル領域は前記エミッタ電極から離間している

請求項1から7の何れか一項に記載の半導体装置。

**【請求項 9】**

前記半導体基板のおもて面において、前記ウェル領域を覆う層間絶縁膜をさらに備え、

30

前記ダイオード部において、前記層間絶縁膜は、上面視において、前記ウェル領域よりも $10 \mu\text{m}$ 以上 $30 \mu\text{m}$ 以下、前記半導体基板の内側に延伸している

請求項8に記載の半導体装置。

**【請求項 10】**

前記トランジスタ部は、前記トレンチボトム部の上方に設けられた第1導電型の蓄積領域をさらに有し、

前記蓄積領域は、前記ダイオード部には設けられていない

請求項1から9の何れか一項に記載の半導体装置。

**【請求項 11】**

前記トランジスタ部および前記ダイオード部は、前記ドリフト領域の上方に設けられた第1導電型の蓄積領域をさらに有する

40

請求項1から9の何れか一項に記載の半導体装置。

**【請求項 12】**

前記蓄積領域と前記トレンチボトム部との間に前記ドリフト領域をさらに備える

請求項10または11に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置に関する。

**【背景技術】**

50

**【 0 0 0 2 】**

特許文献 1 には、 I G B T セルの少なくとも一部が、第 2 の導電型の電気的に浮遊するバリア領域を含むことが記載されている。

**[ 先行技術文献 ]****[ 特許文献 ]**

[ 特許文献 1 ] 特開 2 0 1 9 - 9 1 8 9 2 号公報

**[ 解決しようとする課題 ]****【 0 0 0 3 】**

このようなバリア領域が半導体基板に設けられたウェル領域と接していると、ターンオフ特性が低下する。

10

**[ 一般的開示 ]****【 0 0 0 4 】**

本発明の第 1 の態様においては、半導体装置を提供する。半導体装置は、トランジスタ部およびダイオード部を有する活性部と、活性部の外周に設けられた耐圧構造部とを備え、トランジスタ部は、半導体基板に設けられた第 1 導電型のドリフト領域と、ドリフト領域の上方に設けられた第 2 導電型のベース領域と、半導体基板のおもて面からドリフト領域まで延伸するトレチ部と、トレチ部の下端に設けられた第 2 導電型のトレチボトム部とを有し、ダイオード部は、上面視において、耐圧構造部に近接するトランジスタ部と、耐圧構造部との間に設けられる。

**【 0 0 0 5 】**

20

トレチボトム部は、電気的に浮遊していてよい。

**【 0 0 0 6 】**

トレチボトム部のドーピング濃度は、ドリフト領域のドーピング濃度よりも大きく、ベース領域のドーピング濃度よりも小さくてよい。

**【 0 0 0 7 】**

トレチボトム部のドーピング濃度は、 $1 E 1 2 \text{ cm}^{-3}$  以上、 $1 E 1 3 \text{ cm}^{-3}$  以下であってよい。

**【 0 0 0 8 】**

トレチボトム部はダイオード部に設けられていなくてよい。

**【 0 0 0 9 】**

30

半導体装置は、耐圧構造部において、半導体基板の裏面側に第 1 導電型のカソード領域をさらに備えてよい。

**【 0 0 1 0 】**

半導体装置は、活性部において、半導体基板の上方に設けられたエミッタ電極と、ダイオード部の少なくとも一部から耐圧構造部にわたって、半導体基板に設けられた第 2 導電型のウェル領域とをさらに備え、ダイオード部において、ウェル領域はエミッタ電極から離間していてよい。

**【 0 0 1 1 】**

半導体装置は、半導体基板のおもて面において、ウェル領域を覆う層間絶縁膜をさらに備え、ダイオード部において、層間絶縁膜は、上面視において、ウェル領域よりも $1 0 \mu \text{m}$  以上 $3 0 \mu \text{m}$  以下、半導体基板の内側に延伸していてよい。

40

**【 0 0 1 2 】**

トランジスタ部は、トレチボトム部の上方に設けられた第 1 導電型の蓄積領域をさらに有し、蓄積領域は、ダイオード部には設けられていなくてよい。

**【 0 0 1 3 】**

トランジスタ部およびダイオード部は、ドリフト領域の上方に設けられた第 1 導電型の蓄積領域をさらに有してよい。

**【 0 0 1 4 】**

半導体装置は、蓄積領域とトレチボトム部との間にドリフト領域をさらに備えてよい。

**【 0 0 1 5 】**

50

なお、上記の発明の概要は、本発明の特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。

**【図面の簡単な説明】**

**【0016】**

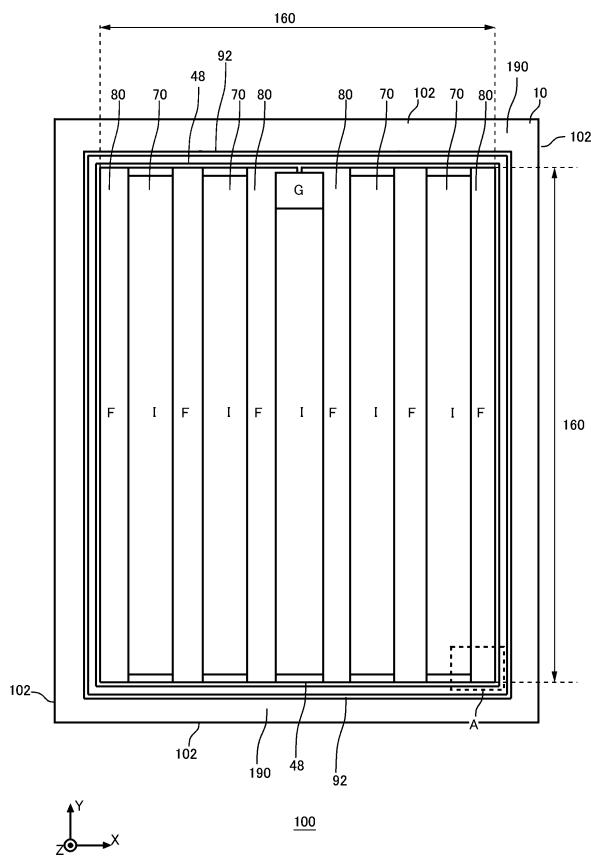

【図1】本実施形態に係る半導体装置100の上面の一例を示す図である。

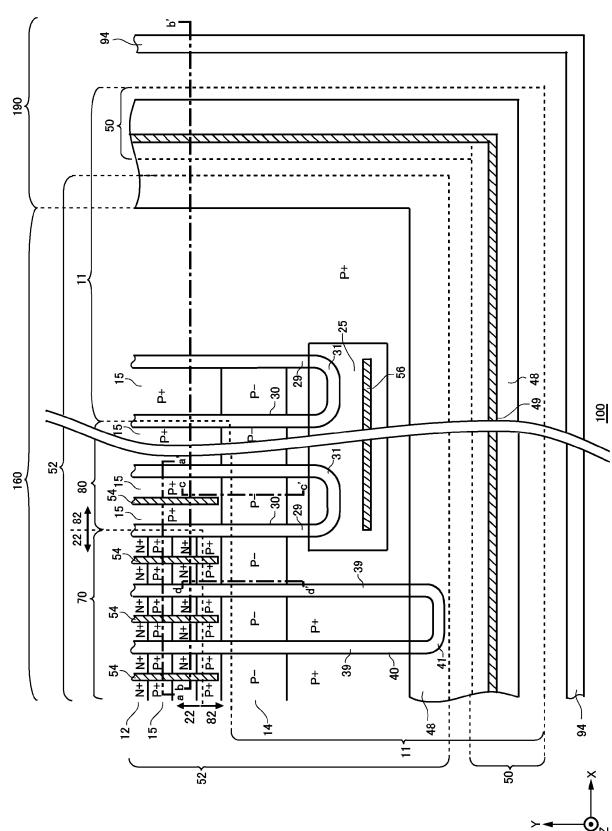

【図2A】半導体装置100の上面の一例を示す拡大図である。

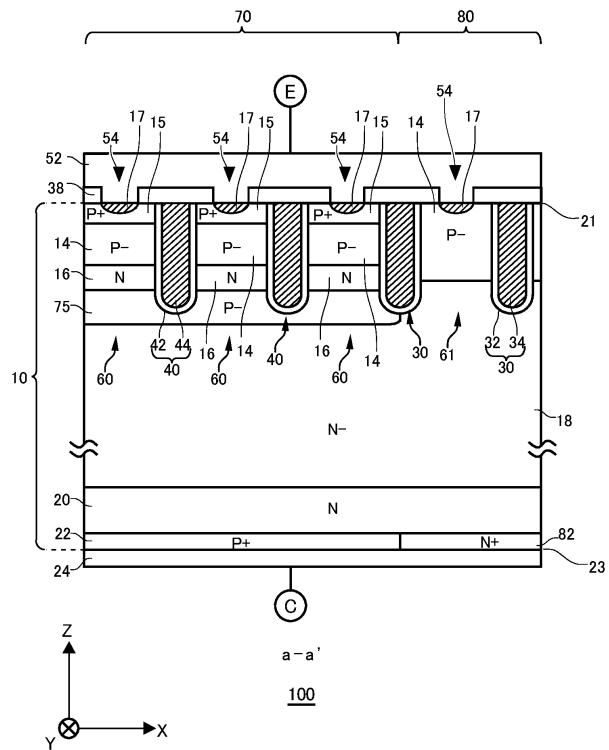

【図2B】図2Aにおけるa-a'断面を示す図である。

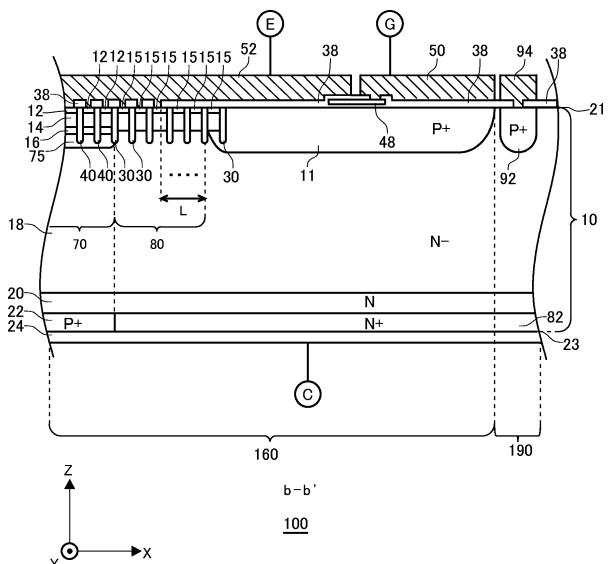

【図2C】図2Aにおけるb-b'断面を示す図である。

【図2D】図2Aにおけるc-c'断面を示す図である。

【図2E】図2Aにおけるd-d'断面を示す図である。

【図2F】図2Aにおけるa-a'断面の別例を示す図である。

【図2G】図2Aにおけるa-a'断面の別例を示す図である。

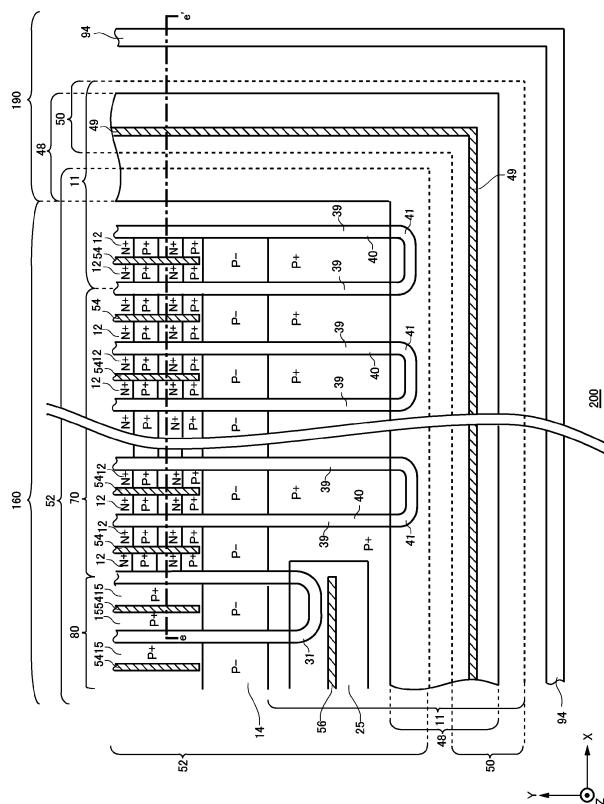

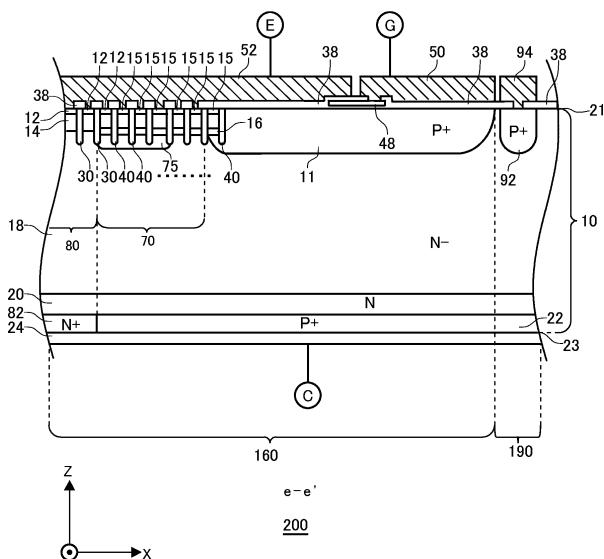

【図3A】比較例に係る半導体装置200の上面の一例を示す拡大図である。

【図3B】図3Aにおけるe-e'断面を示す図である。

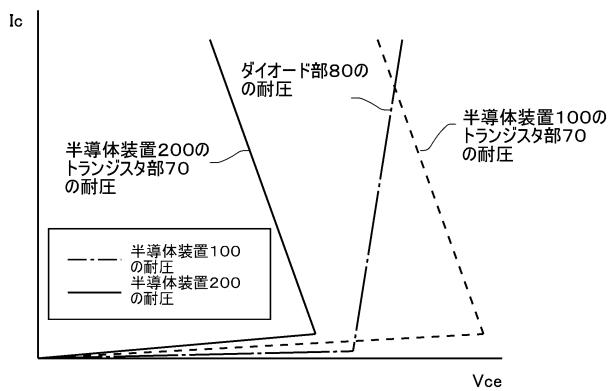

【図4】半導体装置100および半導体装置200の耐圧波形を示すグラフである。

**【発明を実施するための形態】**

**【0017】**

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

**【0018】**

本明細書においては半導体基板の深さ方向と平行な方向における一方の側を「上」または「おもて」、他方の側を「下」または「裏」と称する。基板、層またはその他の部材の2つの主面のうち、一方の面をおもて面、他方の面を裏面と称する。「上」、「下」の方向は、重力方向または半導体装置の実装時における方向に限定されない。

**【0019】**

本明細書では、X軸、Y軸およびZ軸の直交座標軸を用いて技術的事項を説明する場合がある。直交座標軸は、構成要素の相対位置を特定するに過ぎず、特定の方向を限定するものではない。例えば、Z軸は地面に対する高さ方向を限定して示すものではない。なお、+Z軸方向と-Z軸方向とは互いに逆向きの方向である。正負を記載せず、Z軸方向と記載した場合、+Z軸および-Z軸に平行な方向を意味する。

**【0020】**

本明細書では、半導体基板のおもて面および裏面に平行な直交軸をX軸およびY軸とする。また、半導体基板のおもて面および裏面と垂直な軸をZ軸とする。本明細書では、Z軸の方向を深さ方向と称する場合がある。また、本明細書では、X軸およびY軸を含めて、半導体基板のおもて面および裏面に平行な方向を、水平方向と称する場合がある。

**【0021】**

本明細書において「同一」または「等しい」のように称した場合、製造ばらつき等に起因する誤差を有する場合も含んでよい。当該誤差は、例えば10%以内である。

**【0022】**

本明細書においては、不純物がドーピングされたドーピング領域の導電型をP型またはN型として説明している。本明細書においては、不純物とは、特にN型のドナーまたはP型のアクセプタの何れかを意味する場合があり、ドーパントと記載する場合がある。本明細書においては、ドーピングとは、半導体基板にドナーまたはアクセプタを導入し、N型の導電型を示す半導体またはP型の導電型を示す半導体とすることを意味する。

**【0023】**

本明細書においては、ドーピング濃度とは、熱平衡状態におけるドナーの濃度またはアクセプタの濃度を意味する。本明細書においては、ネット・ドーピング濃度とは、ドナー濃度を正イオンの濃度とし、アクセプタ濃度を負イオンの濃度として、電荷の極性を含めて足し合わせた正味の濃度を意味する。一例として、ドナー濃度をN<sub>D</sub>、アクセプタ濃度

10

20

30

40

50

を  $N_A$  とすると、任意の位置における正味のネット・ドーピング濃度は  $N_D - N_A$  となる。

#### 【0024】

ドナーは、半導体に電子を供給する機能を有している。アクセプタは、半導体から電子を受け取る機能を有している。ドナーおよびアクセプタは、不純物自体には限定されない。例えば、半導体中に存在する空孔 (V)、酸素 (O) および水素 (H) が結合した VOH 欠陥は、電子を供給するドナーとして機能する。

#### 【0025】

本明細書において P+ 型または N+ 型と記載した場合、P 型または N 型よりもドーピング濃度が高いことを意味し、P- 型または N- 型と記載した場合、P 型または N 型よりもドーピング濃度が低いことを意味する。また、本明細書において P++ 型または N++ 型と記載した場合には、P+ 型または N+ 型よりもドーピング濃度が高いことを意味する。

10

#### 【0026】

本明細書において化学濃度とは、電気的な活性化の状態によらずに測定される不純物の濃度を指す。化学濃度は、例えば二次イオン質量分析法 (SIMS) により計測できる。上述したネット・ドーピング濃度は、電圧 - 容量測定法 (CV 法) により測定できる。また、拡がり抵抗測定法 (SR 法) により計測されるキャリア濃度を、ネット・ドーピング濃度としてよい。CV 法または SR 法により計測されるキャリア濃度は、熱平衡状態における値としてよい。また、N 型の領域においては、ドナー濃度がアクセプタ濃度よりも十分大きいので、当該領域におけるキャリア濃度を、ドナー濃度としてもよい。同様に、P 型の領域においては、当該領域におけるキャリア濃度を、アクセプタ濃度としてもよい。

20

#### 【0027】

また、ドナー、アクセプタまたはネット・ドーピングの濃度分布がピークを有する場合、当該ピーク値を当該領域におけるドナー、アクセプタまたはネット・ドーピングの濃度としてよい。ドナー、アクセプタまたはネット・ドーピングの濃度がほぼ均一な場合等においては、当該領域におけるドナー、アクセプタまたはネット・ドーピングの濃度の平均値をドナー、アクセプタまたはネット・ドーピングの濃度としてよい。

#### 【0028】

SR 法により計測されるキャリア濃度が、ドナーまたはアクセプタの濃度より低くてもよい。拡がり抵抗を測定する際に電流が流れる範囲において、半導体基板のキャリア移動度が結晶状態の値よりも低い場合がある。キャリア移動度の低下は、格子欠陥等による結晶構造の乱れ (ディスオーダー) により、キャリアが散乱されることで生じる。

30

#### 【0029】

CV 法または SR 法により計測されるキャリア濃度から算出したドナーまたはアクセプタの濃度は、ドナーまたはアクセプタを示す元素の化学濃度よりも低くてよい。一例として、シリコンの半導体においてドナーとなるリンまたはヒ素のドナー濃度、あるいはアクセプタとなるボロン (ホウ素) のアクセプタ濃度は、これらの化学濃度の 99 % 程度である。一方、シリコンの半導体においてドナーとなる水素のドナー濃度は、水素の化学濃度の 0.1 % から 10 % 程度である。

#### 【0030】

図 1 は、本実施形態に係る半導体装置 100 の上面の一例を示す図である。図 1 においては、各部材を半導体基板 10 のおもて面に投影した位置を示している。図 1 においては、半導体装置 100 の一部の部材だけを示しており、一部の部材は省略している。

40

#### 【0031】

半導体装置 100 は、半導体基板 10 を備えている。半導体基板 10 は、上面視において端辺 102 を有する。本明細書で単に上面視と称した場合、半導体基板 10 のおもて面側から見ることを意味している。本例の半導体基板 10 は、上面視において互いに向かい合う 2 組の端辺 102 を有する。図 1 においては、X 軸および Y 軸は、何れかの端辺 102 と平行である。また Z 軸は、半導体基板 10 のおもて面と垂直である。

#### 【0032】

半導体基板 10 には活性部 160 が設けられている。活性部 160 は、半導体装置 10

50

0が動作した場合に半導体基板10のおもて面と裏面との間で、深さ方向に主電流が流れる領域である。活性部160の上方にはエミッタ電極が設けられているが、図1では省略している。

#### 【0033】

活性部160には、IGBT等のトランジスタ素子を含むトランジスタ部70と、還流ダイオード(FWD)等のダイオード素子を含むダイオード部80の少なくとも一方が設けられている。図1の例では、トランジスタ部70およびダイオード部80は、半導体基板10のおもて面における所定の配列方向(本例ではX軸方向)に沿って、交互に配置されている。

#### 【0034】

図1においては、トランジスタ部70が配置される領域には記号「I」を付し、ダイオード部80が配置される領域には記号「F」を付している。本明細書では、上面視において配列方向と垂直な方向を延伸方向(図1ではY軸方向)と称する場合がある。トランジスタ部70およびダイオード部80は、それぞれ延伸方向に長手を有してよい。つまり、トランジスタ部70のY軸方向における長さは、X軸方向における幅よりも大きい。同様に、ダイオード部80のY軸方向における長さは、X軸方向における幅よりも大きい。トランジスタ部70およびダイオード部80の延伸方向と、後述する各トレンチ部の長手方向とは同一であってよい。

10

#### 【0035】

トランジスタ部70は、半導体基板10の裏面と接する領域に、P+型のコレクタ領域を有する。ダイオード部80は、半導体基板10の裏面と接する領域に、N+型のカソード領域を有する。本明細書では、コレクタ領域が設けられた領域を、トランジスタ部70と称する。つまりトランジスタ部70は、上面視においてコレクタ領域と重なる領域である。

20

#### 【0036】

半導体基板10の裏面には、コレクタ領域以外の領域には、N+型のカソード領域が設けられてよい。本明細書では、トランジスタ部70を後述するゲートランナーまでY軸方向に延長した延長領域の下面にはカソード領域が設けられている。本明細書では、延長領域はダイオード部80に含まれる。また、トランジスタ部70は、半導体基板10のおもて面側に、N型のエミッタ領域、P型のベース領域、ゲート導電部およびゲート絶縁膜を有するゲート構造が周期的に配置されている。

30

#### 【0037】

半導体装置100は、半導体基板10の上方に1つ以上のパッドを有してよい。一例として、図1に示す半導体装置100はゲートパッドGを有するが、これは例示に過ぎない。半導体装置100は、アノードパッド、カソードパッドおよび電流検出パッド等のパッドを有してもよい。各パッドは、端辺102の近傍に配置されている。端辺102の近傍とは、上面視における端辺102と、エミッタ電極との間の領域を指す。半導体装置100の実装時において、各パッドは、ワイヤ等の配線を介して外部の回路に接続されてよい。

#### 【0038】

ゲートパッドGには、ゲート電位が印加される。ゲートパッドGは、活性部160のゲートトレンチ部の導電部と電気的に接続される。半導体装置100は、ゲートパッドGとゲートトレンチ部とを電気的に接続するゲートランナー48を備える。

40

#### 【0039】

ゲートランナー48は、上面視において活性部160と半導体基板10の端辺102との間に配置されている。本例のゲートランナー48は、上面視において活性部160を囲んでいる。上面視においてゲートランナー48に囲まれた領域を活性部160としてもよい。

#### 【0040】

ゲートランナー48は、半導体基板10の上方に配置されている。本例のゲートランナー48は、不純物がドープされたポリシリコン等で形成されてよい。ゲートランナー48

50

は、ゲートトレーニング部の内部にゲート絶縁膜を介して設けられたゲート導電部と電気的に接続する。

#### 【0041】

本例の半導体装置100は、活性部160の外周に設けられた耐圧構造部190を備える。本例の耐圧構造部190は、ゲートランナー48と端辺102との間に配置されている。耐圧構造部190は、半導体基板10のおもて面側の電界集中を緩和する。

#### 【0042】

耐圧構造部190は、ガードリング92を有してよい。ガードリング92は、半導体基板10のおもて面と接するP型の領域である。なお、本例の耐圧構造部190は複数のガードリング92を有するが、図1では省略して1つのガードリング92のみが示されている。複数のガードリング92を設けることで、活性部160の上面側における空乏層を外側に伸ばすことができ、半導体装置100の耐圧を向上できる。耐圧構造部190は、活性部160を囲んで環状に設けられたフィールドプレートおよびリサーフのうちの少なくとも一つを更に備えていてもよい。

10

#### 【0043】

また、半導体装置100は、ポリシリコン等で形成されたPN接合ダイオードである不図示の温度センス部や、活性部160に設けられたトランジスタ部と同様な動作をする不図示の電流検出部を備えてもよい。

#### 【0044】

図2Aは、半導体装置100の上面の一例を示す拡大図である。図2Aは、図1に示す領域A、すなわち、活性部160と耐圧構造部190との境界近傍を示す。半導体装置100は、IGBT等のトランジスタ素子を含むトランジスタ部70と、還流ダイオード(FWD)等のダイオード素子を含むダイオード部80とを有する半導体基板を備える。

20

#### 【0045】

本例のトランジスタ部70およびダイオード部80は、配列方向(本例ではX軸方向)に沿って交互に配置されている。ダイオード部80は、上面視において、耐圧構造部190に近接するトランジスタ部70と、耐圧構造部190との間に設けられる。つまり、活性部160の最も外側にはダイオード部80が配置されている。なお、本明細書では、単に「内側」と「外側」と称した場合、半導体装置100の中心に向かう方向が内側、離れる方向が外側を指す。

30

#### 【0046】

本例の半導体装置100は、半導体基板のおもて面側に設けられたゲートトレーニング部40、ダミートレーニング部30、ウェル領域11、エミッタ領域12、ベース領域14およびコンタクト領域15を備える。ゲートトレーニング部40およびダミートレーニング部30は、それぞれがトレーニング部の一例である。

#### 【0047】

また、本例の半導体装置100は、半導体基板のおもて面の上方に設けられたゲート金属層50およびエミッタ電極52を備える。ゲート金属層50およびエミッタ電極52は、互いに分離して設けられる。ゲート金属層50とエミッタ電極52とは、電気的に絶縁される。

40

#### 【0048】

エミッタ電極52およびゲート金属層50と、半導体基板のおもて面との間には層間絶縁膜が設けられるが、図2Aでは省略している。本例の層間絶縁膜には、コンタクトホール49、54および56が、当該層間絶縁膜を貫通して設けられる。図2Aにおいては、それぞれのコンタクトホールに斜線のハッチングを付している。

#### 【0049】

エミッタ電極52は、ゲートトレーニング部40、ダミートレーニング部30、ウェル領域11、エミッタ領域12、ベース領域14およびコンタクト領域15の上方に設けられる。エミッタ電極52は、コンタクトホール54によって、半導体基板のおもて面におけるエミッタ領域12、ベース領域14およびコンタクト領域15と電気的に接続する。

50

**【 0 0 5 0 】**

また、エミッタ電極 5 2 は、コンタクトホール 5 6 によってダミートレンチ部 3 0 内のダミー導電部と接続される。エミッタ電極 5 2 とダミー導電部との間には、不純物がドープされたポリシリコン等の、導電性を有する材料で形成された接続部 2 5 が設けられてよい。接続部 2 5 は、層間絶縁膜およびダミートレンチ部 3 0 のダミー絶縁膜等の絶縁膜を介して半導体基板のおもて面に設けられる。

**【 0 0 5 1 】**

ゲート金属層 5 0 は、コンタクトホール 4 9 によってゲートランナー 4 8 と電気的に接続する。ゲートランナー 4 8 は、不純物がドープされたポリシリコン等で形成されてよい。ゲートランナー 4 8 は、半導体基板のおもて面において、ゲートトレンチ部 4 0 内のゲート導電部に接続する。ゲートランナー 4 8 は、ダミートレンチ部 3 0 内のダミー導電部およびエミッタ電極 5 2 には電気的に接続しない。

10

**【 0 0 5 2 】**

ゲートランナー 4 8 とエミッタ電極 5 2 とは層間絶縁膜および酸化膜などの絶縁物により電気的に分離される。本例のゲートランナー 4 8 は、コンタクトホール 4 9 の下方から、ゲートトレンチ部 4 0 の先端部まで設けられる。ゲートトレンチ部 4 0 の先端部においてゲート導電部は半導体基板のおもて面に露出しており、ゲートランナー 4 8 と接続する。

**【 0 0 5 3 】**

エミッタ電極 5 2 およびゲート金属層 5 0 は、金属を含む導電性材料で形成される。例えば、アルミニウムまたはアルミニウムを主成分とした合金（例えば、アルミニウム・シリコン合金等）で形成される。各電極は、アルミニウム等で形成された領域の下層にチタンやチタン化合物等で形成されたバリアメタルを有してよい。

20

**【 0 0 5 4 】**

各電極は、コンタクトホール内においてタングステン等で形成されたプラグを有してもよい。プラグは、半導体基板に接する側にバリアメタルを有し、バリアメタルに接するようにタングステンを埋め込み、タングステン上にアルミニウム等で形成されてよい。

**【 0 0 5 5 】**

なおプラグは、コンタクト領域 1 5 またはベース領域 1 4 に接するコンタクトホールに設けられる。また、プラグのコンタクトホールの下には P + + 型のプラグ領域を形成し、コンタクト領域 1 5 よりドーピング濃度が高い。これは、バリアメタルとコンタクト領域 1 5 との接触抵抗を改善することができる。また、プラグ領域の深さは約 0 . 1  $\mu\text{m}$  以下であり、コンタクト領域 1 5 の深さと比べて 10 % 以下と小さい領域を持つ。

30

**【 0 0 5 6 】**

プラグ領域は以下の特徴をもつ。トランジスタ部 7 0 の動作において、接触抵抗改善によりラッチアップ耐量が向上する。一方、ダイオード部 8 0 の動作においては、プラグ領域がない場合はバリアメタルとベース領域 1 4 との接触抵抗が高く、導通損失、スイッチング損失が上昇するが、プラグ領域を設けることにより、導通損失、スイッチング損失の上昇を抑制することができる。

**【 0 0 5 7 】**

ウェル領域 1 1 は、ゲートランナー 4 8 と重なって、活性部 1 6 0 の外周を延伸し、上面視で環状に設けられている。ウェル領域 1 1 は、ゲートランナー 4 8 と重ならない範囲にも、所定の幅で延伸し、上面視で環状に設けられている。本例のウェル領域 1 1 は、コンタクトホール 5 4 の Y 軸方向の端から、ゲートランナー 4 8 側に離れて設けられている。ウェル領域 1 1 は、ベース領域 1 4 よりもドーピング濃度の高い第 2 導電型の領域である。ゲートランナー 4 8 は、ウェル領域 1 1 と電気的に絶縁される。

40

**【 0 0 5 8 】**

本例のベース領域 1 4 は P - 型であり、ウェル領域 1 1 は P + 型である。また、ウェル領域 1 1 は、半導体基板のおもて面から、ベース領域 1 4 の下端よりも深い位置まで形成されている。ベース領域 1 4 は、トランジスタ部 7 0 およびダイオード部 8 0 において、ウェル領域 1 1 に接して設けられている。よって、ウェル領域 1 1 はエミッタ電極 5 2 と

50

電気的に接続される。

**【 0 0 5 9 】**

トランジスタ部 7 0 およびダイオード部 8 0 のそれぞれは、配列方向に複数配列されたトレンチ部を有する。本例のトランジスタ部 7 0 には、配列方向に沿って 1 以上のゲートトレンチ部 4 0 が設けられている。本例のダイオード部 8 0 には、複数のダミートレンチ部 3 0 が、配列方向に沿って設けられている。本例のダイオード部 8 0 には、ゲートトレンチ部 4 0 が設けられていない。

**【 0 0 6 0 】**

本例のゲートトレンチ部 4 0 は、配列方向と垂直な延伸方向に沿って延伸する 2 つの直線部分 3 9 ( 延伸方向に沿って直線状であるトレンチの部分 ) と、 2 つの直線部分 3 9 を接続する先端部 4 1 を有してよい。

10

**【 0 0 6 1 】**

先端部 4 1 の少なくとも一部は、上面視において曲線状に設けられてよい。2 つの直線部分 3 9 の Y 軸方向における端部同士を先端部 4 1 がゲートランナー 4 8 と接続することで、ゲートトレンチ部 4 0 へのゲート電極として機能する。一方、先端部 4 1 を曲線状にすることにより直線部分 3 9 で完結するよりも、端部における電界集中を緩和できる。

**【 0 0 6 2 】**

他の例においては、トランジスタ部 7 0 は、配列方向に沿って 1 以上のゲートトレンチ部 4 0 と 1 以上のダミートレンチ部 3 0 とが交互に設けられてもよい。トランジスタ部 7 0 において、ダミートレンチ部 3 0 はゲートトレンチ部 4 0 のそれぞれの直線部分 3 9 の間に設けられる。それぞれの直線部分 3 9 の間には、1 本のダミートレンチ部 3 0 が設けられてよく、複数本のダミートレンチ部 3 0 が設けられていてもよい。

20

**【 0 0 6 3 】**

またそれぞれの直線部分 3 9 の間には、ダミートレンチ部 3 0 が設けられなくてよく、ゲートトレンチ部 4 0 が設けられてもよい。このような構造により、エミッタ領域 1 2 からの電子電流を増大することができるため、オン電圧が低減する。

**【 0 0 6 4 】**

ダミートレンチ部 3 0 は、延伸方向に延伸する直線形状を有してよく、ゲートトレンチ部 4 0 と同様に、直線部分 2 9 と先端部 3 1 とを有していてもよい。図 2 A に示した半導体装置 1 0 0 は、先端部 3 1 を有するダミートレンチ部 3 0 のみが配列されているが、他の例においては、半導体装置 1 0 0 は、先端部 3 1 を有さない直線形状のダミートレンチ部 3 0 を含んでもよい。

30

**【 0 0 6 5 】**

ウェル領域 1 1 の拡散深さは、ゲートトレンチ部 4 0 およびダミートレンチ部 3 0 の深さよりも深くてよい。ゲートトレンチ部 4 0 およびダミートレンチ部 3 0 の Y 軸方向の端部は、上面視においてウェル領域 1 1 に設けられる。つまり、各トレンチ部の Y 軸方向の端部において、各トレンチ部の深さ方向の底部は、ウェル領域 1 1 に覆われている。また、X 軸方向の端部に設けられるトレンチ部は、ウェル領域 1 1 に覆われてもよい。これにより、各トレンチ部の当該底部における電界集中を緩和できる。

**【 0 0 6 6 】**

配列方向において各トレンチ部の間には、メサ部が設けられている。メサ部は、半導体基板の内部において、トレンチ部に挟まれた領域を指す。一例としてメサ部の深さ位置は、半導体基板のおもて面からトレンチ部の下端までである。

40

**【 0 0 6 7 】**

本例のメサ部は、X 軸方向において隣接するトレンチ部に挟まれ、半導体基板のおもて面においてトレンチに沿って延伸方向 ( Y 軸方向 ) に延伸して設けられている。図 2 B で後述するように、本例では、トランジスタ部 7 0 にはメサ部 6 0 が設けられ、ダイオード部 8 0 にはメサ部 6 1 が設けられている。本明細書において単にメサ部と称した場合、メサ部 6 0 およびメサ部 6 1 のそれぞれを指している。

**【 0 0 6 8 】**

50

それぞれのメサ部には、ベース領域 14 が設けられる。それぞれのメサ部には、上面視においてベース領域 14 に挟まれた領域に、第 1 導電型のエミッタ領域 12 および第 2 導電型のコンタクト領域 15 の少なくとも一方が設けられてよい。本例のエミッタ領域 12 は N+ 型であり、コンタクト領域 15 は P+ 型である。エミッタ領域 12 およびコンタクト領域 15 は、深さ方向において、ベース領域 14 と半導体基板のおもて面との間に設けられてよい。

#### 【0069】

トランジスタ部 70 のメサ部は、半導体基板のおもて面に露出したエミッタ領域 12 を有する。エミッタ領域 12 は、ゲートトレンチ部 40 に接して設けられている。ゲートトレンチ部 40 に接するメサ部には、半導体基板のおもて面に露出したコンタクト領域 15 が設けられている。10

#### 【0070】

メサ部におけるコンタクト領域 15 およびエミッタ領域 12 のそれぞれは、X 軸方向における一方のトレンチ部から、他方のトレンチ部まで設けられる。一例として、メサ部のコンタクト領域 15 およびエミッタ領域 12 は、トレンチ部の延伸方向 (Y 軸方向) に沿って交互に配置されている。20

#### 【0071】

他の例においては、メサ部のコンタクト領域 15 およびエミッタ領域 12 は、トレンチ部の延伸方向 (Y 軸方向) に沿ってストライプ状に設けられていてよい。例えばトレンチ部に接する領域にエミッタ領域 12 が設けられ、エミッタ領域 12 に挟まれた領域にコンタクト領域 15 が設けられる。20

#### 【0072】

ダイオード部 80 のメサ部には、エミッタ領域 12 が設けられていない。ダイオード部 80 のメサ部の上面には、ベース領域 14 が設けられてよい。ベース領域 14 は、ダイオード部 80 のメサ部全体に配置されてよい。

#### 【0073】

それぞれのメサ部の上方には、コンタクトホール 54 が設けられている。コンタクトホール 54 は、その延伸方向 (Y 軸方向) においてベース領域 14 に挟まれた領域に配置されている。本例のコンタクトホール 54 は、コンタクト領域 15、ベース領域 14 およびエミッタ領域 12 の各領域の上方に設けられる。コンタクトホール 54 は、メサ部の配列方向 (X 軸方向) における中央に配置されてよい。30

#### 【0074】

ダイオード部 80 において、半導体基板の裏面と隣接する領域には、N+ 型のカソード領域 82 が設けられる。半導体基板の裏面において、カソード領域 82 が設けられていない領域には、P+ 型のコレクタ領域 22 が設けられてよい。図 2A においては、カソード領域 82 およびコレクタ領域 22 の境界を点線で示している。耐圧構造部 190 においても、半導体基板の裏面側に N+ 型のカソード領域 82 が設けられてよい。

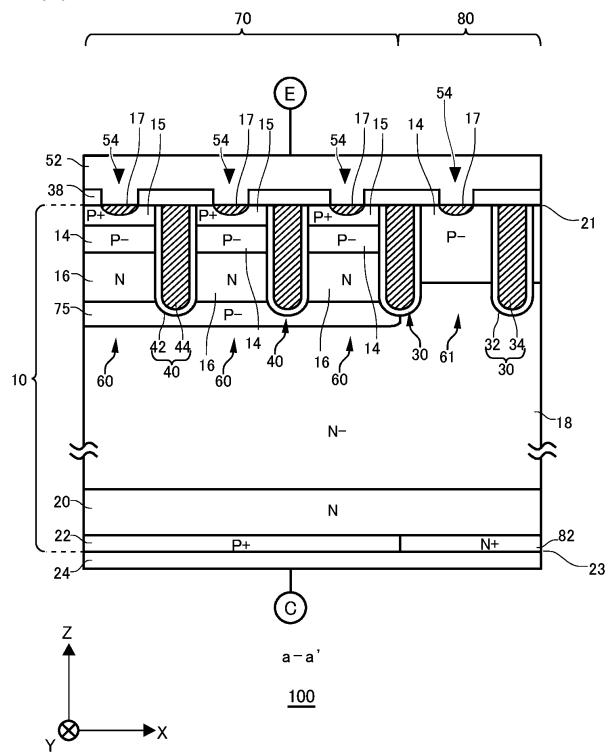

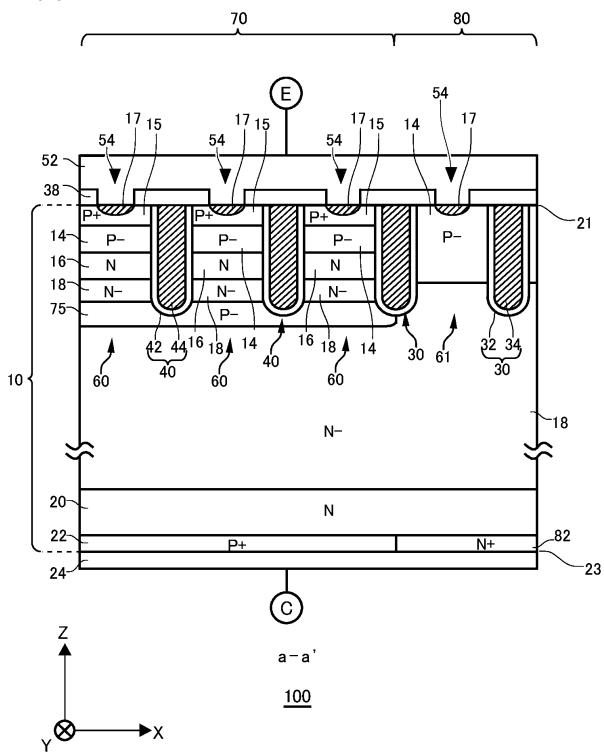

#### 【0075】

図 2B は、図 2A における a-a' 断面を示す図である。a-a' 断面は、コンタクト領域 15、ベース領域 14、並びにゲートトレンチ部 40 およびダミートレンチ部 30 を通る XZ 面である。本例の半導体装置 100 は、a-a' 断面において、半導体基板 10、層間絶縁膜 38、エミッタ電極 52 およびコレクタ電極 24 を有する。40

#### 【0076】

層間絶縁膜 38 は、半導体基板 10 のおもて面 21 に設けられている。層間絶縁膜 38 は、ボロンまたはリン等の不純物が添加されたシリケートガラス等の絶縁膜である。層間絶縁膜 38 はおもて面 21 に接していてよく、層間絶縁膜 38 とおもて面 21 との間に酸化膜等の他の膜が設けられていてよい。層間絶縁膜 38 には、図 2A において説明したコンタクトホール 54 が設けられている。

#### 【0077】

エミッタ電極 52 は、半導体基板 10 のおもて面 21 および層間絶縁膜 38 の上面に設

10

20

30

40

50

けられる。エミッタ電極 5 2 は、層間絶縁膜 3 8 のコンタクトホール 5 4 によって、おもて面 2 1 と電気的に接続する。コンタクトホール 5 4 の内部には、タングステン (W) 等のプラグ領域 1 7 が設けられていてよい。コレクタ電極 2 4 は、半導体基板 1 0 の裏面 2 3 に設けられる。エミッタ電極 5 2 およびコレクタ電極 2 4 は、金属を含む材料またはそれらの積層膜で形成される。

#### 【 0 0 7 8 】

半導体基板 1 0 は、シリコン基板であってよく、炭化シリコン基板であってよく、窒化ガリウム等の窒化物半導体基板等であってもよい。本例の半導体基板 1 0 はシリコン基板である。

#### 【 0 0 7 9 】

半導体基板 1 0 は、第 1 導電型のドリフト領域 1 8 を有する。本例のドリフト領域 1 8 は、N - 型である。ドリフト領域 1 8 は、半導体基板 1 0 において他のドーピング領域が設けられずに残存した領域であってよい。

#### 【 0 0 8 0 】

トランジスタ部 7 0 において、ドリフト領域 1 8 の上方には、Z 軸方向に一つ以上の蓄積領域 1 6 が設けられてよい。蓄積領域 1 6 は、ドリフト領域 1 8 と同じドーパントが、ドリフト領域 1 8 よりも高濃度に蓄積した領域である。蓄積領域 1 6 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。

#### 【 0 0 8 1 】

本例の蓄積領域 1 6 は、N 型である。蓄積領域 1 6 は、トランジスタ部 7 0 において、ベース領域 1 4 と後述するトレニチボトム部 7 5 との間に設けられていてよい。蓄積領域 1 6 は、トランジスタ部 7 0 のみに設けられていてもよく、トランジスタ部 7 0 およびダイオード部 8 0 の両方に設けられていてもよい。蓄積領域 1 6 を設けることで、キャリアの注入促進効果 (IE 効果) を高めて、オン電圧を低減できる。

#### 【 0 0 8 2 】

トランジスタ部 7 0 において、ベース領域 1 4 の上方には、おもて面 2 1 に接してエミッタ領域 1 2 が設けられる。エミッタ領域 1 2 は、ゲートトレニチ部 4 0 と接して設けられる。エミッタ領域 1 2 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。エミッタ領域 1 2 のドーパントは、一例としてヒ素 (As) 、リン (P) 、アンチモン (Sb) 等である。

#### 【 0 0 8 3 】

ダイオード部 8 0 には、おもて面 2 1 に露出したベース領域 1 4 が設けられる。ダイオード部 8 0 のベース領域 1 4 は、アノードとして動作する。

#### 【 0 0 8 4 】

ドリフト領域 1 8 の下方には、第 1 導電型のバッファ領域 2 0 が設けられてよい。本例のバッファ領域 2 0 は、N 型である。バッファ領域 2 0 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。バッファ領域 2 0 は、ベース領域 1 4 の下面側から広がる空乏層が、コレクタ領域 2 2 およびカソード領域 8 2 に到達することを防ぐフィールドストップ層として機能してよい。

#### 【 0 0 8 5 】

トランジスタ部 7 0 において、バッファ領域 2 0 の下方にはコレクタ領域 2 2 が設けられる。コレクタ領域 2 2 は、裏面 2 3 においてカソード領域 8 2 と接して設けられていてよい。

#### 【 0 0 8 6 】

ダイオード部 8 0 において、バッファ領域 2 0 の下方にはカソード領域 8 2 が設けられる。カソード領域 8 2 は、トランジスタ部 7 0 のコレクタ領域 2 2 と同じ深さに設けられてよい。ダイオード部 8 0 は、トランジスタ部 7 0 がターンオフする時に、逆方向に導通する還流電流を流す還流ダイオード (FWD) として機能してよい。

#### 【 0 0 8 7 】

半導体基板 1 0 には、ゲートトレニチ部 4 0 およびダミートレンチ部 3 0 が設けられる

10

20

30

40

50

。ゲートトレーニング部 40 およびダミートレーニング部 30 は、おもて面 21 からベース領域 14 および蓄積領域 16 を貫通して、ドリフト領域 18 に到達するように設けられる。トレーニング部がドーピング領域を貫通するとは、ドーピング領域を形成してからトレーニング部を形成する順序で製造したものに限定されない。トレーニング部を形成した後に、トレーニング部の間にドーピング領域を形成したものも、トレーニング部がドーピング領域を貫通しているものに含まれる。

#### 【0088】

ゲートトレーニング部 40 は、おもて面 21 に設けられたゲートトレーニング、ゲート絶縁膜 42 およびゲート導電部 44 を有する。ゲート絶縁膜 42 は、ゲートトレーニングの内壁を覆って設けられる。ゲート絶縁膜 42 は、酸化膜または窒化膜で形成してよい。ゲート導電部 44 は、ゲートトレーニングの内部においてゲート絶縁膜 42 よりも内側を埋め込むように設けられる。ゲート導電部 44 の上面は、おもて面 21 と同じ XY 平面内にあってよい。ゲート絶縁膜 42 は、ゲート導電部 44 と半導体基板 10 とを絶縁する。ゲート導電部 44 は、不純物がドープされたポリシリコン等で形成される。

10

#### 【0089】

ゲート導電部 44 は、深さ方向においてベース領域 14 よりも長く設けられてよい。ゲートトレーニング部 40 は、おもて面 21 において層間絶縁膜 38 により覆われる。ゲート導電部 44 に所定の電圧が印加されると、ベース領域 14 のうちゲートトレーニングに接する界面の表層に、電子の反転層によるチャネルが形成される。

20

#### 【0090】

ダミートレーニング部 30 は、XZ 断面においてゲートトレーニング部 40 と同一の構造を有してよい。ダミートレーニング部 30 は、おもて面 21 に設けられたダミートレーニング、ダミー絶縁膜 32 およびダミー導電部 34 を有する。ダミー絶縁膜 32 は、ダミートレーニングの内壁を覆って設けられる。ダミー絶縁膜 32 は、酸化膜または窒化膜で形成してよい。ダミー導電部 34 は、ダミートレーニングの内部においてダミー絶縁膜 32 よりも内側を埋め込むように設けられる。ダミー導電部 34 の上面は、おもて面 21 と同じ XY 平面内にあってよい。ダミー絶縁膜 32 は、ダミー導電部 34 と半導体基板 10 とを絶縁する。ダミー導電部 34 は、ゲート導電部 44 と同一の材料で形成されてよい。

#### 【0091】

本例のゲートトレーニング部 40 およびダミートレーニング部 30 は、おもて面 21 において層間絶縁膜 38 により覆われている。なお、ダミートレーニング部 30 およびゲートトレーニング部 40 の底部は、下側に凸の曲面状（断面においては曲線状）であってよい。

30

#### 【0092】

トランジスタ部 70 は、トレーニング部の下端に設けられた P 型のトレーニングボトム部 75 を有する。本例のトレーニングボトム部 75 は、蓄積領域 16 より下方に設けられている。半導体基板 10 の深さ方向において、トレーニングボトム部 75 の下端は、ゲートトレーニング部 40 の底部より下方に位置してよい。換言すると、トレーニングボトム部 75 は、ゲートトレーニング部 40 の底部を覆っていてよい。

#### 【0093】

トレーニングボトム部 75 のドーピング濃度は、ドリフト領域 18 のドーピング濃度よりも大きく、ベース領域 14 のドーピング濃度よりも小さい。トレーニングボトム部 75 のドーピング濃度は、 $1 \times 10^{12} \text{ cm}^{-3}$  以上、 $1 \times 10^{13} \text{ cm}^{-3}$  以下である。

40

#### 【0094】

図 2B では、トレーニングボトム部 75 の X 軸方向正側（ダイオード部 80 側）の端部は、カソード領域 82 およびコレクタ領域 22 の境界と一致しているが、これよりもダイオード部 80 側に延伸していくてもよく、トランジスタ部 70 内に後退していくてもよい。

#### 【0095】

トレーニングボトム部 75 は、電気的に浮遊するフローティング層であってよい。本明細書において、フローティング層とは、エミッタ電極 52 等のいずれの電極とも電気的に接続されていない層をいう。トレーニングボトム部 75 を設けることにより、トランジスタ部 70

50

のターンオン特性が向上する。また、トレンチボトム部 75 を設けることにより、ゲートトレンチ部 40 の底部における電界集中を緩和し、アバランシェ耐量を向上させる。

#### 【0096】

図 2 C は、図 2 A における b - b' 断面を示す図である。b - b' 断面は、活性部 160 および耐圧構造部 190 の境界近傍において、エミッタ領域 12、コンタクト領域 15、ベース領域 14、並びにゲートトレンチ部 40 およびダミートレンチ部 30 を通る XZ 面である。

#### 【0097】

本例のダイオード部 80 は、上面視において、耐圧構造部 190 に近接するトランジスタ部 70 と、耐圧構造部 190 との間に設けられる。つまり、活性部 160 の最も耐圧構造部 190 側にはダイオード部 80 が配置されている。10

#### 【0098】

上述したように、本例のトランジスタ部 70 はトレンチボトム部 75 を有する。活性部 160 の最も外側にトランジスタ部 70 を設ける場合、トランジスタ部 70 の一部にトレンチボトム部 75 を設けず、エミッタ電極 52 と電気的に接続されたウェル領域 11 からトレンチボトム部 75 を離間させる必要がある。例えば、トランジスタ部 70 において、耐圧構造部 190 側の端部から一定の範囲にトレンチボトム部 75 を設けない場合、トレンチボトム部 75 の減少量に応じてターンオン特性が低下する。

#### 【0099】

本例では、活性部 160 の最も外側にダイオード部 80 を配置することにより、トランジスタ部 70 の全体にトレンチボトム部 75 を設けることができるので、ターンオン特性を向上させることができる。20

#### 【0100】

また、トランジスタ部 70 の全体にトレンチボトム部 75 を設けることにより、トランジスタ部 70 の耐圧が向上する。これにより、半導体装置 100 全体の耐圧が向上し、ラッチアップ耐量が向上する。

#### 【0101】

本例のダイオード部 80 では、ウェル領域 11 はエミッタ電極 52 から離間している。本例では、層間絶縁膜 38 をウェル領域 11 とエミッタ電極 52 との間に設けることにより、ウェル領域 11 およびエミッタ電極 52 を絶縁することができる。30

#### 【0102】

層間絶縁膜 38 は、上面視において、耐圧構造部 190 から、活性部 160 の最も外側に設けられたダイオード部 80 の一部にわたって延伸している。図 2 C において、層間絶縁膜 38 の端部とウェル領域 11 の端部との間の距離 L は、10 μm 以上 30 μm 以下であってよい。

#### 【0103】

ウェル領域 11 の端部には、半導体装置 100 の逆回復時に電流が集中しやすい。そこで、ダイオード部 80 におけるエミッタ電極 52 とのコンタクトをウェル領域 11 の端部から離間することにより、逆回復耐量を向上させることができる。

#### 【0104】

トランジスタ部 70 は、ベース領域 14 とトレンチボトム部 75 との間に N 型の蓄積領域 16 を有する。蓄積領域 16 は、トランジスタ部 70 のみに設けられ、ダイオード部 80 には設けられなくてよい。40

#### 【0105】

あるいは、蓄積領域 16 は、トランジスタ部 70 およびダイオード部 80 の両方に設けられてもよい。蓄積領域 16 を設けることで、キャリアの注入促進効果 (IE 効果) を高めて、オン電圧を低減できる。

#### 【0106】

耐圧構造部 190 において、半導体基板 10 の裏面 23 側には、N 型のカソード領域 82 が設けられてよい。つまり、ダイオード部 80 から耐圧構造部 190 にわたって、半導

10

20

30

40

50

体基板 10 の裏面 23 側にはカソード領域 82 が連続的に活性部 160 の外周を囲むように設けられてよい。

#### 【0107】

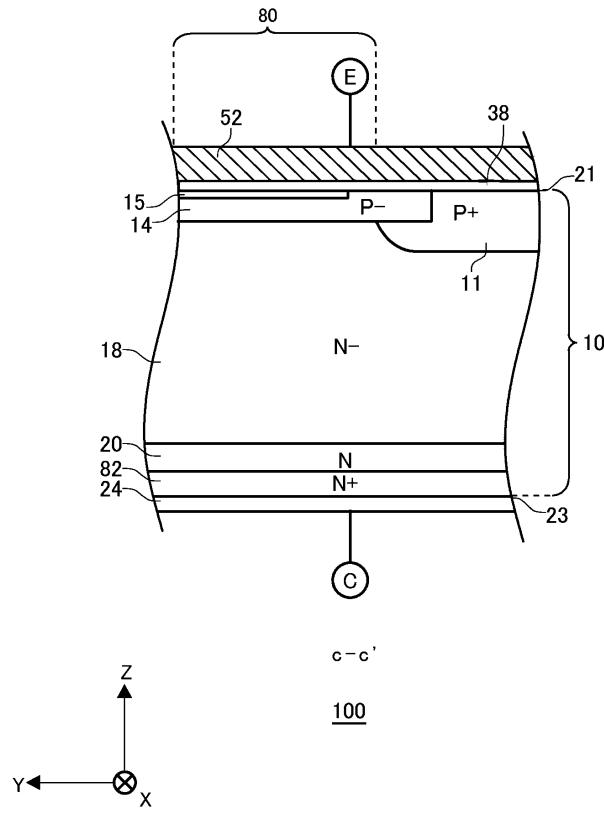

図 2 D は、図 2 A における c - c' 断面を示す図である。c - c' 断面は、活性部 160 の Y 軸負側端部近傍において、ダイオード部 80 に設けられたベース領域 14 およびコンタクト領域 15 を通る YZ 面である。

#### 【0108】

本例では、活性部 160 の最も外側にダイオード部 80 が設けられている。ダイオード部 80 では、半導体基板 10 のおもて面 21 にコンタクト領域 15 が設けられている。また、ダイオード部 80 では、コンタクト領域 15 の Y 軸方向外側に、ベース領域 14 が半導体基板 10 のおもて面 21 に露出している。つまり、上面視において、ダイオード部 80 では、Y 軸方向において、コンタクト領域 15 がベース領域 14 に挟まれている。

10

#### 【0109】

活性部 160 の Y 軸負側端部近傍には、ウェル領域 11 が設けられている。ウェル領域 11 の拡散深さは、ベース領域 14 より深い。ウェル領域 11 は、ベース領域 14 の底部を部分的に覆うように Y 軸方向に延伸してよい。

#### 【0110】

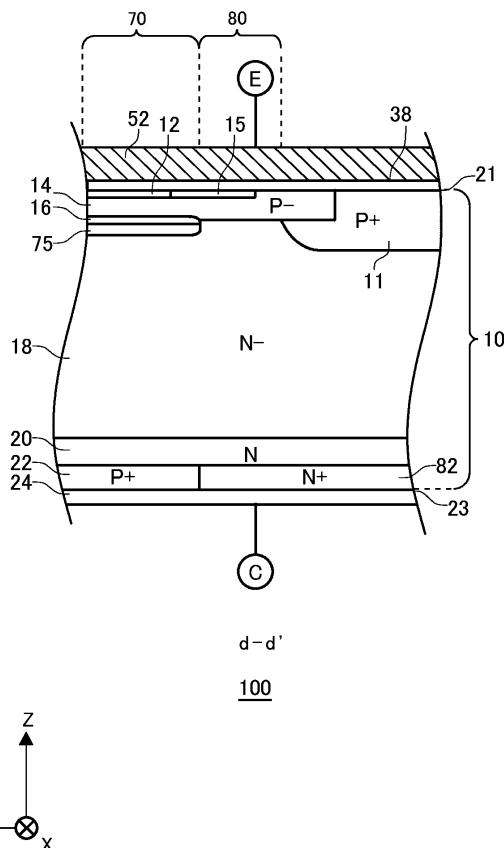

図 2 E は、図 2 A における d - d' 断面を示す図である。d - d' 断面は、活性部 160 の Y 軸負側端部近傍において、トランジスタ部 70 に設けられたエミッタ領域 12、ベース領域 14 およびコンタクト領域 15 を通る YZ 面である。また、d - d' 断面は、トランジスタ部 70 を Y 軸方向に延長した延長領域を通る。延長領域の下面にはカソード領域が設けられている。つまり、上面視において、トランジスタ部 70 は、Y 軸方向においてダイオード部 80 に挟まれている。

20

#### 【0111】

トランジスタ部 70 では、半導体基板 10 のおもて面 21 に、エミッタ領域 12 およびコンタクト領域 15 が設けられている。また、トランジスタ部 70 では、コンタクト領域 15 の Y 軸方向外側に、ベース領域 14 が半導体基板 10 のおもて面 21 に露出している。つまり、上面視において、トランジスタ部 70 では、Y 軸方向において、エミッタ領域 12 およびコンタクト領域 15 がベース領域 14 に挟まれている。

#### 【0112】

トランジスタ部 70 において、ドリフト領域 18 の上方に、蓄積領域 16 およびトレントボトム部 75 が設けられている。トレントボトム部 75 は、蓄積領域 16 より下方に設けられている。トレントボトム部 75 は、蓄積領域 16 の下面と接して設けられてよい。

30

#### 【0113】

図 2 F は、図 2 A における a - a' 断面の別例を示す図である。a - a' 断面は、図 2 B と同様にコンタクト領域 15、ベース領域 14、並びにゲートトレントボトム部 40 およびダミートレンチ部 30 を通る XZ 面である。本例の半導体装置 100 は、a - a' 断面において、半導体基板 10、層間絶縁膜 38、エミッタ電極 52 およびコレクタ電極 24 を有する。

#### 【0114】

トランジスタ部 70 のトレントボトム部の下端に設けられたトレントボトム部 75 は、半導体基板 10 の深さ方向において、蓄積領域 16 より厚さが薄いことが図 2 B と異なる。

40

#### 【0115】

本例のトレントボトム部 75 の下端は、ゲートトレントボトム部 40 の底部より下方に位置し、ゲートトレントボトム部 40 の底部を覆っている。トレントボトム部 75 は、電気的に浮遊するフローティング層であってよい。

#### 【0116】

図 2 F では、トレントボトム部 75 の X 軸方向正側（ダイオード部 80 側）の端部は、カソード領域 82 およびコレクタ領域 22 の境界と一致しているが、これよりもダイオード部 80 側に延伸していくてもよく、トランジスタ部 70 内に後退していくてもよい。本例は、図 2 B と同様な効果を得ることができる。

50

**【 0 1 1 7 】**

図 2 G は、図 2 A における a - a' 断面の別例を示す図である。a - a' 断面は、図 2 B と同様にコンタクト領域 15、ベース領域 14、並びにゲートトレンチ部 40 およびダミートレンチ部 30 を通る XZ 面である。本例の半導体装置 100 は、a - a' 断面において、半導体基板 10、層間絶縁膜 38、エミッタ電極 52 およびコレクタ電極 24 を有する。

**【 0 1 1 8 】**

トレンチボトム部 75 は、蓄積領域 16 と離間して、すなわち、蓄積領域 16 とトレンチボトム部 75 との間にドリフト領域 18 が介在するように設けられている点が図 2 B、図 2 F と異なる。

**【 0 1 1 9 】**

トレンチボトム部 75 は半導体基板 10 の深さ方向において、蓄積領域 16、または、蓄積領域 16 とトレンチボトム部 75 との間のドリフト領域 18 より厚さが薄くてもよい。

**【 0 1 2 0 】**

図 2 G では、トレンチボトム部 75 の X 軸方向正側（ダイオード部 80 側）の端部は、カソード領域 82 およびコレクタ領域 22 の境界と一致しているが、これよりもダイオード部 80 側に延伸していてもよく、トランジスタ部 70 内に後退していてもよい。本例は、図 2 B と同様な効果を得ることができる。

**【 0 1 2 1 】**

図 3 A は、比較例に係る半導体装置 200 の上面の一例を示す拡大図である。図 3 A は、図 2 A と同様に、図 1 に示す領域 A、すなわち、活性部 160 と耐圧構造部 190 との境界近傍を示す。半導体装置 200 において、半導体装置 100 と共通する部材については同じ符号が付されている。

20

**【 0 1 2 2 】**

半導体装置 200 のトランジスタ部 70 は、上面視において、耐圧構造部 190 に近接するダイオード部 80 と、耐圧構造部 190 との間に設けられる。つまり、図 2 A と異なり、活性部 160 の最も外側にはトランジスタ部 70 が配置されている。また、ウェル領域 11 の上方には、コンタクトホール 54 が設けられている。したがって、ウェル領域 11 は、図示しないエミッタ電極 52 と電気的に接続されている。

**【 0 1 2 3 】**

図 3 B は、図 3 A における e - e' 断面を示す図である。e - e' 断面は、エミッタ領域 12、コンタクト領域 15、ベース領域 14、並びにゲートトレンチ部 40 およびダミートレンチ部 30 を通る XZ 面である。

30

**【 0 1 2 4 】**

上述したように、半導体装置 200 において、活性部 160 の最も外側にはトランジスタ部 70 が配置されている。また、耐圧構造部 190 において、半導体基板 10 の裏面 23 側には、P 型のコレクタ領域 22 が設けられている。つまり、トランジスタ部 70 から耐圧構造部 190 にわたって、半導体基板 10 の裏面 23 側にはコレクタ領域 22 が連続的に設けられている。

**【 0 1 2 5 】**

半導体装置 200 のトランジスタ部 70 は、トレンチボトム部 75 を有する。ただし、活性部 160 の最も外側に設けられたトランジスタ部 70 全体にトレンチボトム部 75 を設けると、トレンチボトム部 75 がウェル領域 11 と接触する。ウェル領域 11 は、エミッタ電極 52 と電気的に接続されているので、トレンチボトム部 75 はエミッタ電位に固定され、電流を流すことができない。

40

**【 0 1 2 6 】**

そのため、活性部 160 の最も外側に設けられたトランジスタ部 70 において、耐圧構造部 190 側には、トレンチボトム部 75 が設けられていない。これにより、エミッタ電極 52 と電気的に接続されたウェル領域 11 からトレンチボトム部 75 を離間させている。したがって、半導体装置 200 は、半導体装置 100 よりもトレンチボトム部 75 が小さいため、その差分に応じてターンオン特性が低下する。また、半導体装置 200 の耐圧

50

も半導体装置 100 より低くなり、ラッチアップ耐量が低下する。

#### 【0127】

図 4 は、半導体装置 100 および半導体装置 200 の耐圧波形を示すグラフである。一般に、デバイスの耐圧は、電流が集中しやすいトレンチ部底部の耐圧によって決まる。IGBT は負性抵抗を有するので、電流  $I_c$  が増大するほど電圧  $V_{ce}$  が減少し、トレンチ部底部のような同じ場所に電流が集中する。一方で、FWD は、電流  $I_c$  が増大すると電圧も増大するため、電流が一か所に集中しない。

#### 【0128】

IGBT の耐圧は FWD の耐圧より低いので、RC-IGBT の耐圧は、FWD の耐圧によって決まる。IGBT は内在する寄生サイリスタの影響で、電流集中によりアバランシェが発生するとラッチアップのおそれがある。一方で、FWD には寄生サイリスタが内在しないので、電流集中によりアバランシェが発生してもラッチアップのおそれがない。

10

#### 【0129】

図 4 において、実線は半導体装置 200 のトランジスタ部 70 の耐圧波形を示し、一点鎖線はダイオード部 80 の耐圧波形を示す。半導体装置 200 において、トランジスタ部 70 の耐圧はダイオード部 80 の耐圧より低いので、半導体装置 200 の耐圧は、トランジスタ部 70 の耐圧によって決まる。

#### 【0130】

一方で、半導体装置 100 のトランジスタ部 70 は、半導体装置 200 のトランジスタ部 70 と異なり、トレンチボトム部 75 が全体に設けられているので、その差分に応じて半導体装置 200 のトランジスタ部 70 よりも耐圧が上昇する。破線は、半導体装置 100 のトランジスタ部 70 の耐圧波形を示す。半導体装置 100 のトランジスタ部 70 の耐圧波形は、半導体装置 200 のトランジスタ部 70 の耐圧波形を耐圧の上昇分だけ右側に平行移動している。

20

#### 【0131】

半導体装置 100 のダイオード部 80 にはトレンチボトム部 75 が設けられていないので、半導体装置 100 のダイオード部 80 の耐圧は半導体装置 200 と同じである。図 4 に示すように、半導体装置 100 において、トランジスタ部 70 の耐圧がダイオード部 80 の耐圧よりも高くなつたことにより、半導体装置 100 の耐圧は、ダイオード部 80 の耐圧によって決まる。

30

#### 【0132】

半導体装置 100 の耐圧波形は、図 4 の一点鎖線、すなわちダイオード部 80 の耐圧波形に従う。これに対し、半導体装置 200 の耐圧波形は、図 4 の実線、すなわちトランジスタ部 70 の耐圧波形に従う。このように、半導体装置 100 の耐圧は半導体装置 200 の耐圧よりも高くなり、また、ダイオード部 80 ではアバランシェが発生してもラッチアップのおそれがないので、アバランシェ耐量が向上する。

#### 【0133】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、請求の範囲の記載から明らかである。

40

#### 【0134】

請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるの限り、任意の順序で実現しうることに留意すべきである。請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

#### 【符号の説明】

#### 【0135】

50

10 . . . 半導体基板、11 . . . ウェル領域、12 . . . エミッタ領域、14 . . . ベース領域、15 . . . コンタクト領域、16 . . . 蓄積領域、17 . . . プラグ領域、18 . . . ドリフト領域、20 . . . バッファ領域、21 . . . おもて面、22 . . . コレクタ領域、23 . . . 裏面、24 . . . コレクタ電極、25 . . . 接続部、29 . . . 直線部分、30 . . . ダミートレンチ部、31 . . . 先端部、32 . . . ダミー絶縁膜、34 . . . ダミー導電部、38 . . . 層間絶縁膜、39 . . . 直線部分、40 . . . ゲートトレンチ部、41 . . . 先端部、42 . . . ゲート絶縁膜、44 . . . ゲート導電部、48 . . . ゲートランナー、49 . . . コンタクトホール、50 . . . ゲート金属層、52 . . . エミッタ電極、54 . . . コンタクトホール、56 . . . コンタクトホール、60 . . . メサ部、61 . . . メサ部、70 . . . トランジスタ部、75 . . . トレンチボトム部、80 . . . ダイオード部、82 . . . カソード領域、92 . . . ガードリング、100 . . . 半導体装置、102 . . . 端辺、160 . . . 活性部、190 . . . 耐圧構造部、200 . . . 半導体装置

10

〔 叴 面 〕

〔 1 〕

【 2 A 】

20

30

40

50

【図2B】

【図2C】

【図2D】

【図2E】

【図 2 F】

【図 2 G】

10

20

30

40

【図 3 A】

【図 3 B】

50

【図 4】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

| F I                  |

|----------------------|

| H 01 L 29/78 6 5 3 A |

| H 01 L 29/78 6 5 2 Q |

| H 01 L 29/78 6 5 5 B |

| H 01 L 29/78 6 5 5 D |

| H 01 L 29/78 6 5 7 D |

| H 01 L 29/78 6 5 2 P |

| H 01 L 29/06 3 0 1 V |

| H 01 L 29/06 3 0 1 G |

神奈川県川崎市川崎区田辺新田1番1号 富士電機株式会社内

審査官 志津木 康

(56)参考文献

特開2021-028930 (JP, A)

特開2005-142243 (JP, A)

特開2019-161126 (JP, A)

特開2020-115596 (JP, A)

特開2016-162855 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 21/8234

H 01 L 27/06

H 01 L 29/06

H 01 L 21/336

H 01 L 29/78

H 01 L 29/12

H 01 L 29/739

H 01 L 29/861

H 01 L 29/868