(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-341465

(P2004-341465A)

(43) 公開日 平成16年12月2日(2004.12.2)

(51) Int.C1.<sup>7</sup>

**G02F** 1/1368

**G02F** 1/1339

**G02F** 1/1343

**G02F** 1/1345

**H01L** 21/3205

F 1

G02F 1/1368

G02F 1/1339 500

G02F 1/1343

G02F 1/1345

H01L 29/78 612C

テーマコード(参考)

2H089

2H092

5FO33

5F110

審査請求 未請求 請求項の数 71 書面 (全 65 頁) 最終頁に続く

(21) 出願番号

特願2003-185823 (P2003-185823)

(22) 出願日

平成15年5月14日 (2003.5.14)

(71) 出願人

591129195

大林精工株式会社

愛知県豊川市諏訪4丁目295番地

(72) 発明者

広田直人

愛知県豊川市諏訪4丁目295

F ターム(参考) 2H089 LA09 NA05 NA14 QA10 QA15

QA16 TA02 TA09 TA12 TA13

2H092 GA14 GA20 GA24 GA29 GA32

GA40 GA60 GA64 JA24 JA34

JA37 JA41 JA46 JA47 JA48

JB04 JB52 JB56 JB57 JB61

KA18 MA13 MA14 MA17 NA01

NA07 PA02 PA03 PA08 PA09

PA12

最終頁に続く

(54) 【発明の名称】高品質液晶表示装置とその製造方法

## (57) 【要約】

【目的】横電界方式のアクティブマトリックス型液晶表示装置で、カラーシフトや階調反転がなく、クロストークが発生しにくく、かつ高開口率を実現でき、明るいコントラストの高い画像を得る。

【構成】横電界方式アクティブマトリックス型液晶パネルに関して、誘電率が3.3以下の透明な絶縁物で映像信号配線を被覆し、この細長い絶縁体バンプの上に、透明導電体を用いて映像信号配線をシールドするための共通電極を形成した。

【選択図】図69

## 【特許請求の範囲】

## 【請求項 1】

横電界方式アクティブマトリックス液晶表示装置に関して、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの上に、映像信号配線をシールドするための共通電極を映像信号配線をおおうように形成したことを特徴とする液晶表示装置。

## 【請求項 2】

横電界方式アクティブマトリックス液晶表示装置に関して、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に映像信号配線をシールドするための共通電極が映像信号配線をはさみこむように形成されていることを特徴とする液晶表示装置。 10

## 【請求項 3】

請求項 1, 2 において、映像信号配線の上に、映像信号配線をつつみこむように形成された細長い絶縁体のバンプが、液晶セルを組み立てる時に液晶セルギャップを決定するスペーサーの役割をはたしていることを特徴とする液晶表示装置

## 【請求項 4】

横電界方式アクティブマトリックス液晶表示装置に関して、ハーフトーン露光方法を用いて、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプと液晶セルのセルギャップを決定するスペーサーを、ホトリソグラフィーを用いて同時に形成し、前記細長い絶縁体のバンプの上に映像信号配線をシールドするための共通電極を映像信号配線をおおうように形成したことを特徴とする液晶表示装置。 20

## 【請求項 5】

横電界方式アクティブマトリックス液晶表示装置に関して、ハーフトーン露光方法を用いて、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプと、液晶セルのセルギャップを決定するスペーサーを、ホトリソグラフィーを用いて、同時に形成し、この細長い絶縁体のバンプの両側の側壁に映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成したことを特徴とする液晶表示装置

## 【請求項 6】

請求項 1, 2, 3, 4, 5 において映像信号配線をシールドするための前記シールド共通電極が、酸化インジウム  $In_2O_3$  または酸化亜鉛  $ZnO$  を主体とする金属酸化物透明導電体または、窒化チタン ( $TiN_x$ ) または、酸窒化チタン ( $TiO_xN_y$ ) または窒化チタンシリサイド ( $TiSi_xN_y$ ) またはチタンシリサイド ( $TiSi_x$ ) などのチタン金属化合物からなり可視光透過率が 20 % 以上あることを特徴とする液晶表示装置 30

## 【請求項 7】

請求項 1, 2, 3, 4, 5 において、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体バンプの断面形状が、半円形または、半だ円形、または双曲線形または放物曲線形のようになるままであり、バンプのテーパー角度が 30 度以下であることを特徴とする液晶表示装置

## 【請求項 8】

請求項 1, 2, 3, 4, 5 において、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体バンプが、映像信号配線と走査線が交差している領域には、形成されていないことを特徴とする液晶表示装置。 40

## 【請求項 9】

請求項 4, 5 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの頂点付近の領域は、共通電極によって被覆されておらずスペーサーを形成している誘電体が露出していることを特徴とする液晶表示装置

## 【請求項 10】

請求項 4, 5 において細長い絶縁体バンプの高さと、液晶セルのセルギャップを決定するスペーサーの高さの差  $h_2$  が 0.2 ミクロンメーターから 2.0 ミクロンメーターの範囲にあることを特徴とする液晶表示装置 50

**【請求項 1 1】**

請求項 4, 5 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの密度が  $1 \text{ mm}^2$  あたり 1 個から 75 個の範囲にあることを特徴とする液晶表示装置

**【請求項 1 2】**

請求項 4, 5 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの面積が  $1 \text{ mm}^2$  あたりにつき 200 平方ミクロンメーターから 2000 平方ミクロンメーターの範囲にあることを特徴とする液晶表示装置

**【請求項 1 3】**

横電界方式アクティブマトリックス液晶表示装置に関して、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの上に映像信号配線の電界をシールドするために共通電極を形成し、かつ走査線の上にも同様に走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を走査線をはさみこむように形成したことを特徴とする液晶表示装置。 10

**【請求項 1 4】**

横電界方式アクティブマトリックス液晶表示装置に関して、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体バンプの両側の側壁に映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成し、かつ走査線の上にも同様に、走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を走査線をはさみこむように形成したことを特徴とする液晶表示装置 20

**【請求項 1 5】**

請求項 1 3, 請求項 1 4 において、映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体のバンプが、液晶セルを組み立てる時に、液晶セルギャップを決定するスペーサーの役割をはたしていることを特徴とする液晶表示装置。

**【請求項 1 6】**

横電界方式アクティブマトリックス液晶表示装置に関して、ハーフトーン露光方法を用いて、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプと、液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの上に映像信号配線をシールドするための共通電極を、映像信号配線をおおうように形成し、かつ走査線の上にも同様にハーフトーン露光法を用いて走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に、走査線の電界をシールドするための共通電極を、走査線をはさみこむように形成したことを特徴とする液晶表示装置 30

**【請求項 1 7】**

横電界方式アクティブマトリックス液晶表示装置に関して、ハーフトーン露光方法を用いて、映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプと液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの両側の側壁に、映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成し、かつ走査線の上にも、同様に、ハーフトーン露光法を用いて、走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を走査線をはさみこむように形成したことを特徴とする液晶表示装置 40

**【請求項 1 8】**

請求項 1 3, 1 4, 1 5, 1 6, 1 7 において映像信号配線と走査線の電界をシールドするための前記シールド共通電極が、酸化インジウム  $\text{In}_2\text{O}_3$  または酸化亜鉛  $\text{ZnO}$  を主体とする金属酸化物透明導電体または、窒化チタン ( $\text{TiN}_x$ ) または、酸窒化チタン ( $\text{TiO}_x\text{N}_y$ ) または、窒化チタンシリサイド ( $\text{TiSi}_x\text{N}_y$ ) またはチタンシリサイ 50

ド (Ti<sub>5</sub>Si<sub>3</sub>) などのチタン金属化合物からなり可視光透過率が 20 % 以上あることを特徴とする液晶表示装置

【請求項 19】

請求項 13, 14, 15, 16, 17 において映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体バンプの断面形状が、半円形または半だ円形、または、双曲線形または、放物線形のようにまるまっており、バンプのテー<sup>10</sup>パー角度が 30 度以下であることを特徴とする液晶表示装置。

【請求項 20】

請求項 13, 14, 15, 16, 17 において映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体バンプが、映像信号配線と走査線とが交差している領域には、形成されていないことを特徴とする液晶表示装置

【請求項 21】

請求項 16, 17 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの頂点付近の領域は、映像信号配線の電界をシールドするための共通電極によって被覆されておらずスペーサーを形成している誘電体が露出していることを特徴とする液晶表示装置。

【請求項 22】

請求項 16, 17 において細長い絶縁体バンプの高さと、液晶セルのセルギャップを決定するスペーサーの高さの差  $h_2$  が 0.2 ミクロンメーターから 2.0 ミクロンメーターの範囲にあることを特徴とする液晶表示装置

【請求項 23】

請求項 16, 17 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの密度が  $1 \text{ mm}^2$  あたり 1 個から 75 個の範囲にあることを特徴とする液晶表示装置

【請求項 24】

請求項 16, 17 においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの面積が  $1 \text{ mm}^2$  あたりにつき 200 平方ミクロンメーターから 2000 平方ミクロンメーターの範囲にあることを特徴とする液晶表示装置

【請求項 25】

請求項 1, 2, 3, 4, 5, 13, 14, 15, 16, 17 において映像信号配線を左右上下からはさみこむように、ゲート絶縁膜やパッシベーション膜をかいして上層と下層に共通電極を配置し、下層の共通電極は、光を透過させない金属電極からなり上層の共通電極は光を透過する透明電極で構成されており、かつ上層の共通電極の方が下層の共通電極よりも電極幅がひろく、液晶駆動電極側にはみでている構造を特徴とする液晶表示装置

【請求項 26】

請求項 1, 2, 3, 4, 5, 13, 14, 15, 16, 17 において、映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極と画素内の共通電極とが、1 画素内で液晶の配向方向に対して 0 度をのぞく 0 度から 30 度の角度の範囲で 1 回以上屈曲している構造を特徴とする液晶表示装置

【請求項 27】

請求項 1, 2, 3, 4, 5, 13, 14, 15, 16, 17 において、映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体の両方がともに直線状に配置されていて、この絶縁体に沿うように形成されたシールド共通電極と画素内の液晶駆動電極と、画素内の共通電極とが、1 画素内で液晶の配向方向に対して 0 度をのぞく 0 度から 30 度の角度の範囲で 1 回以上屈曲している構造を特徴とする液晶表示装置。

【請求項 28】

請求項 1, 2, 3, 4, 5, 13, 14, 15, 16, 17 において映像信号配線と、映

10

20

30

40

50

像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極のみが、1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

【請求項 29】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

10

【請求項 30】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲しておりかつカラーフィルター層と遮光膜（ブラックマスク）とが映像信号配線の形状とほぼ同様に液晶の配向方向に対して1画素内で、0度をのぞく0度から30度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

20

【請求項 31】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極と画素内の共通電極とが、1画素内で液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

30

【請求項 32】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体とが、ともに直線状に配置されていて、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、1画素内で液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

【請求項 33】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極のみが、1画素内で液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

40

【請求項 34】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

【請求項 35】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲しており、かつカラーフィルター層と遮光膜（ブラックマスク）とが映像信号配線の形状とほぼ同様に液晶の配向方向に対して1画素内で、0度をのぞく0度から30度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

50

ク)とが、映像信号配線の形状とほぼ同様に液晶の配向方向に対して1画素内で90度をのぞく60度から120度の角度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

【請求項36】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線に沿って映像信号配線を被覆している絶縁体バンプの比誘電率が、3.3以下でかつ絶縁体バンプの高さ $h_1$ が1.5ミクロンメーターから5.0ミクロンメーターの範囲にあり、かつ映像信号配線のエッジから絶縁体バンプのエッジまでの距離 $L_1$ を3.0ミクロンメーターから6.0ミクロンメーターの範囲にあることを特徴とする液晶表示装置

【請求項37】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線を被覆する絶縁体バンプのエッジから絶縁体バンプをつつみこんでいるシールド共通電極のエッジまでの距離 $L_2$ が0.5ミクロンメーターから10.0ミクロンメーターの範囲にあることを特徴とする液晶表示装置

【請求項38】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線を被覆する絶縁体バンプの原料となるモノマーまたはオリゴマーが、ベンゾシクロブテン構造を1個以上有するものまたはその誘導体であることまたは、フルオレン骨格を1個以上有するものまたはその誘導体であることを特徴とする液晶表示装置

【請求項39】

請求項1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線を被覆する細長い絶縁体バンプを形成する時に、同時に、有効画素領域全体をとりかこみ、液晶セルのメインシールが形成される領域と同じ位置に、メインシールが大気の圧力や液晶の圧力により破断されることを防止するための閉ループ状のバリアーバンプスペーサーを1本以上形成したことを特徴とする液晶表示装置

【請求項40】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1) 走査線のパターンニング(走査線形成)

- 2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

【請求項41】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

- 2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極の形成

【請求項42】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1) 走査線形成

- 2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

10

20

30

40

50

- 3 ) 映像信号配線と液晶駆動電極の同時形成

- 4 ) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

【請求項 4 3】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1 ) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

- 2 ) 薄膜トランジスタのエッティングストッパーのチャネル部パターン形成

- 3 ) 映像信号配線と液晶駆動電極の同時形成

- 4 ) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6 ) 映像信号配線シールド用透明共通電極の形成

10

【請求項 4 4】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1 ) 走査線形成

- 2 ) 映像信号配線と、液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーン露光技術)

- 3 ) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 5 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

20

【請求項 4 5】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

- 1 ) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

- 2 ) 映像信号配線と液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーン露光技術)

- 3 ) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 5 ) 映像信号配線シールド用透明共通電極の形成

30

【請求項 4 6】

請求項 1 , 2 , 3 , 4 , 5 , 13 , 14 , 15 , 16 , 17 において、映像信号配線をつつみこむように形成された細長い絶縁体に沿うように形成されたシールド共通電極が有効表示画素領域全体にわたって互いに連結されており、映像信号電圧の中心電圧付近の電位に設定されていることを特徴とする液晶表示装置

40

【請求項 4 7】

請求項 1 , 2 , 3 , 4 , 5 , 13 , 14 , 15 , 16 , 17 において、1画素内で、液晶分子を駆動するために必要な電極が、薄膜トランジスタ素子に連結されている1本の液晶駆動電極と1画素の左右両側に存在している映像信号配線をシールドするための下層共通電極と映像信号配線を被覆している細長い絶縁体に沿って形成されているシールド用上層共通電極の3種類の電極から構成されており、画素内部の共通電極が1本も存在していないことを特徴とする液晶表示装置

【請求項 4 8】

横電界方式アクティブマトリックス液晶表示装置に関して、不透明な金属材料または金属シリサイドまたは金属窒化物から形成されている画素内の共通電極や、映像信号配線をシ

50

ールドするための下層共通電極や液晶駆動電極の膜厚のうち1番厚い膜厚と液晶セルギャップの両方を合計した膜厚のネガレジストを塗布した後、ホトスペーサー形成用のホトマスクを用いてスペーサーを形成する部分に紫外線を照射して完全露光した後、アクティブマトリックス基板の裏面から紫外線を有効画素領域全面に照射してから現像することでアクティブマトリックス基板側の凹凸の平坦化とホトリソスペーサーの形成を同時に起こなったことを特徴とする液晶表示装置

【請求項 4 9】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線 (Gate 電極) と画素内共通電極と映像信号配線シールド用下層共通電極の 10 同時形成

2 ) 薄膜トランジスタのシリコン素子分離 (シリコン island 化)

3 ) 映像信号配線と液晶駆動電極の同時形成

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

6 ) ホトスペーサー形成と有効画素領域の平坦化 (ハーフトーン裏面露光技術)

【請求項 5 0】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線 (Gate 電極) と画素内共通電極と映像信号配線シールド用下層共通電極の 20 同時形成

2 ) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

3 ) 映像信号配線と液晶駆動電極の同時形成

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

6 ) ホトスペーサー形成と有効画素領域の平坦化 (ハーフトーン裏面露光技術)

【請求項 5 1】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線 (Gate 電極) と画素内共通電極と映像信号配線シールド用下層共通電極の 30 同時形成

2 ) 薄膜トランジスタのシリコン素子分離 (シリコン island 化)

3 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と映像信号配線端子部の同時形成

5 ) ホトスペーサー形成と有効画素領域の平坦化 (ハーフトーン裏面露光技術)

【請求項 5 2】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線 (Gate 電極) と画素内共通電極と映像信号配線シールド用下層共通電極の 40 同時形成

2 ) 薄膜トランジスタのシリコン素子分離 (シリコン island 化) と端子部と静電気対策用保護回路形成のためのコンタクトホールの同時形成 (ハーフトーン露光技術 - - - - 1st & 2nd 2回露光)

3 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と映像信号配線端子部の同時形成

4 ) ホトスペーサー形成と有効画素領域の平坦化 (ハーフトーン裏面露光技術)

【請求項 5 3】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線 ( Gate 電極 ) と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 映像信号配線と液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成 ( ハーフトーン露光技術 )

3 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

5 ) ホトスペーサー形成と有効画素領域の平坦化 ( ハーフトーン裏面露光技術 )

【請求項 5 4】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置 10

1 ) 走査線 ( Gate 電極 ) と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

( P - Si N<sub>x</sub> \ a - Si i 層 \ n<sup>+</sup> a - Si 層はシャドーフレームを用いるマスキング d e p o プロセス使用 )

2 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と薄膜トランジスタのシリコン素子分離の同時形成 ( ハーフトーン露光技術 )

3 ) ホトスペーサー形成と有効画素領域の平坦化 ( ハーフトーン裏面露光技術 )

【請求項 5 5】

横電界方式アクティブマトリックス液晶表示装置の製造工程で用いられるハーフトーン裏面露光装置に関して、紫外線用石英ファイバーケーブルや紫外線 LED をインライン状にたばねて配置し、横電界方式アクティブマトリックス液晶表示基板の有効画素領域のみに、紫外線を走査露光できるようにしたことを特徴とする横電界方式アクティブマトリックス液晶表示装置用ハーフトーン裏面走査露光装置 20

【請求項 5 6】

請求項 4 8 , 4 9 , 5 0 , 5 1 , 5 2 , 5 3 , 5 4 に記載されているハーフトーン裏面露光プロセスで用いられる露光装置に関して、ホトスペーサー形成用のホトマスクを用いてスペーサーを形成する部分に紫外線を照射して完全露光した後、アクティブマトリックス基板の裏面から紫外線を有効画素領域全面に走査露光する。次に現像した後アクティブマトリックス基板側の有効画素領域内の凹凸の度合いと、スペーサーの高さを白色干渉計を用いて計測し、計測値に応じてネガ型ホトレジストのコーティング膜厚とハーフトーン裏面露光光量をフィードバック制御できるようにしたことを特徴とするハーフトーン裏面走査露光装置 30

【請求項 5 7】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) レーザーを用いてガラス基板内部にアライメントマークを形成する。

2 ) 異なる種類の金属または金属化合物または合金を 2 層以上堆積する。 ( ただしレーザーで形成したアライメントマーク部には堆積しない。 )

3 ) ポジレジストを全面に塗布した後、通常ホトマスクを用いるアンダー露光方法による 1 次ハーフトーン露光をおこない、 Gate Bus と Common Bus を露光する。次に 2 次露光で Gate Bus と Common Bus と映像信号配線シールド用共通電極と画素内共通電極とを通常露光する。

4 ) 現像後、 1 次の Dry エッチング法または Wet エッチング法を用いて堆積した金属のエッチングをおこなう。次にハーフトーン露光領域のポジレジストを酸素プラズマアッシング法などを用いて除去した後、 2 次の Dry エッチング法または Wet エッチング法を用いてハーフトーン露光領域の不必要な金属層をエッチングする。

上記 1 次 , 2 次のエッチング工程により Gate Bus と Common Bus と映像信号配線シールド用共通電極と画素内共通電極とを形成する。

5 ) Gate 絶縁膜とノンドープ薄膜半導体層 ( i 層 a - Si ) と n<sup>+</sup> a - Si 層 ( オームニックコンタクト層 ) を堆積した後、通常ホトマスクを用いるアンダー露光方法による 1

10

20

30

40

50

次ハーフトーン露光をおこない a - Si i s l a n d を露光する。次に 2 次露光で G a t e 端子接続部と静電気対策用保護回路部にコンタクトホールを通常露光する。

6 ) 現像後、1 次の D r y エッチング法を用いて G a t e 絶縁膜とノンドープ薄膜半導体層 ( i 層 a - Si ) と n<sup>+</sup> a - Si 層 ( オーミックコンタクト層 ) をエッチングして G a t e 端子接続部と静電気対策用保護回路部のコンタクトホールを形成する。次にハーフトーン露光領域のポジレジストを酸素プラズマアッシング法などを用いて除去した後、2 次の D r y エッチング法を用いてハーフトーン露光領域の不必要的ノンドープ薄膜半導体層 ( i 層 a - Si ) と n<sup>+</sup> a - Si 層 ( オーミックコンタクト層 ) をエッチングする。上記 1 次、2 次のエッチング工程により a - Si i s l a n d と G a t e 端子接続部と静電気対策用保護回路部のコンタクトホールを形成する。

7 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と G a t e 端子の同時形成 ( 通常ホトマスクを用いるハーフトーン露光工程を適用する。 )

【請求項 5 8】

アクティブマトリックス表示装置の薄膜トランジスタ素子の製造工程で用いられる露光装置に関して、目標とする薄膜トランジスタのチャネル長の約半分のチャネル長でソース電極とドレイン電極を形成した通常ホトマスクを用いて、1 次のハーフトーン露光 ( 不完全露光 ) をおこなった後、目標とする薄膜トランジスタのチャネル長の約半分程度、アクティブマトリックス基板を水平方向にシフトさせてから再度 2 次のハーフトーン露光 ( 不完全露光 ) をおこなうことのできる機能を有する露光装置。

【請求項 5 9】

アクティブマトリックス表示装置の薄膜トランジスタ素子の製造工程に関して、目標とする薄膜トランジスタ素子のチャネル長の約半分のチャネル長でソース電極とドレイン電極を形成した通常ホトマスクを用いて、1 次のハーフトーン露光 ( 不完全露光 - - - - アンダー露光 ) をおこなった後、目標とする薄膜トランジスタのチャネル長の約半分程度アクティブマトリックス基板を水平方向にシフトさせてから、再度 2 次のハーフトーン露光 ( 不完全露光 - - - - アンダー露光 ) をおこなった後、ポジレジストを現像し、薄膜トランジスタ素子のチャネル部分のポジレジスト膜厚を薄くしたことを特徴とする薄膜トランジスタ素子の製造方法。

【請求項 6 0】

請求項 5 9 に記載されたハーフトーンシフト露光技術を用いて、薄膜トランジスタのシリコン素子分離と映像信号配線 ( ソース電極 ) とドレイン電極 ( 液晶駆動電極または透明画素電極に連結されている電極 ) の形成を同時におこなったことを特徴とするアクティブマトリックス表示装置

【請求項 6 1】

請求項 5 9 に記載されたハーフトーンシフト露光技術を用いて、アクティブマトリックス基板の製造工程が下記の工程でおこなわれることを特徴とする液晶表示装置

1 ) 走査線 ( G a t e 電極 ) と共通電極の同時形成

2 ) 映像信号配線とドレイン電極と薄膜トランジスタのシリコン素子分離の同時形成 ( ハーフトーンシフト露光技術 )

3 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路と透明画素電極の同時形成

【請求項 6 2】

請求項 5 9 に記載されたハーフトーンシフト露光技術を用いてアクティブマトリックス基板の製造工程が下記の工程でおこなわれることを特徴とする横電界方式液晶表示装置

1 ) 走査線 ( G a t e 電極 ) と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

( P - S i N<sub>x</sub> \ a - Si i 層 \ n<sup>+</sup> a - Si 層はシャドーフレームを用いるマスキング d e p o プロセス使用 )

10

20

30

40

50

2) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーンシフト露光技術)

3) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【請求項 6 3】

請求項 3, 4, 5, 15, 16, 17 で用いられているスペーサーバンプが、アクティブマトリックス基板と対向するカラーフィルター基板を真空中でかさねあわせて液晶Cell 1を形成する時に大気圧の応力により 0.1 ミクロンから 0.5 ミクロンの範囲で均一に弾性変形する物性を有することを特徴とする液晶表示装置

【請求項 6 4】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置 10

1) 走査線形成

2) 薄膜トランジスタのシリコン素子分離(シリコン island 化)

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

【請求項 6 5】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置 20

1) 走査線と映像信号配線シールド用下層共通電極の同時形成

2) 薄膜トランジスタのシリコン素子分離(シリコン island 化)

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

【請求項 6 6】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置 30

1) 走査線形成

2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

【請求項 6 7】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置 40

1) 走査線と映像信号配線シールド用下層共通電極の同時形成

2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

50

6 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

【請求項 6 8】

横電界方式アクティブマトリックス液晶表示装置に関して、アクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線形成

2 ) 映像信号配線（ソース電極）とドレイン電極と薄膜トランジスタのシリコン素子分離の同時形成（ハーフトーン露光技術）

3 ) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成（ハーフトーン露光技術）

4 ) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

10

【請求項 6 9】

横電界方式アクティブマトリックス液晶表示装置に関してアクティブマトリックス基板の製造工程が下記の工程にしたがっておこなわれることを特徴とする液晶表示装置

1 ) 走査線と映像信号配線シールド用下層共通電極の同時形成

2 ) 映像信号配線（ソース電極）とドレイン電極と薄膜トランジスタのシリコン素子分離の同時形成（ハーフトーン露光技術）

3 ) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成（ハーフトーン露光技術）

4 ) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

20

【請求項 7 0】

請求項 1 , 2 , 3 , 4 , 5 , 13 , 14 , 15 , 16 , 17 において、1画素内で液晶分子を駆動するために必要な電極が、薄膜トランジスタ素子に連結されている1本の液晶駆動電極と1画素の左右両側に存在する映像信号配線をシールドするための下層共通電極と映像信号配線を被覆している細長い絶縁体バンプに沿って形成されているシールド用上層共通電極の3種類の電極から構成されており、画素内部の共通電極が1本も存在していない構造でかつ、上記3種類の電極と映像信号配線と、映像信号配線を被覆している細長い絶縁体バンプとが1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲しており、かつカラーフィルター層と遮光膜（ブラックマスク）とが映像信号配線の形状とほぼ同様に、液晶の配向方向に対して1画素内で0度をのぞく0度から30度の範囲で1回以上屈曲していることを特徴とする液晶表示装置

30

【請求項 7 1】

請求項 1 , 2 , 3 , 4 , 5 , 13 , 14 , 15 , 16 , 17 において、1画素内で液晶分子を駆動するために必要な電極が、薄膜トランジスタ素子に連結されている1本の液晶駆動電極と1画素の左右両側に存在する映像信号配線をシールドするための下層共通電極と映像信号配線を被覆している細長い絶縁体バンプに沿って形成されているシールド用上層共通電極の3種類の電極から構成されており、画素内部の共通電極が1本も存在していない構造で、かつ上記3種類の電極と映像信号配線と、映像信号配線を被覆している細長い絶縁体バンプとが1画素内で液晶の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲しており、かつカラーフィルター層と遮光膜（ブラックマスク）とが映像信号配線の形状とほぼ同様に液晶の配向方向に対して1画素内で90度をのぞく60度から120度の範囲で1回以上屈曲していることを特徴とする液晶表示装置。

40

【発明の詳細な説明】

【0001】

【産業上の利用分野】

本発明は高開口率・広視野角・高画質・低コストの大画面アクティブマトリックス型表示

50

装置に関する。

【0002】

【従来の技術】

液晶に印加する電界の方向を基板の界面にほぼ平行な方向とする横電界方式液晶表示装置は、視野角が広く、大画面液晶表示の本命とされ、特開平10-55000, 特開平10-325961, 特開平11-24104, 特開平10-55001, 特開平10-170939, 特開平11-52420など数多くの提案と改良がなされてきて、縦方向クロストークの問題はほぼ解決された。

【0003】横電界方式液晶表示装置のコントラストを改善するためにホトリソスペーサーの提案も特開2000-199904, 特開2000-19527などをはじめ多くの液晶パネルメーカーから提案され、実用化されている。これらのほとんどがカラーフィルター基板側にホトリソグラフィー技術を用いてスペーサーを形成している。特開2000-19527や特開2000-199904では、映像信号配線の電界を基板の水平方向ではなく、基板の垂直な方向に向けることで垂直クロストークを低減することを考えている。このために、ホトリソスペーサーの比誘電率を液晶の比誘電率よりも大きくしていた。特開2000-19526も同様にホトリソスペーサーの比誘電率を液晶の比誘電率よりも大きくしていた。

【0004】特開2001-209053では、縦電界方式のホトリソスペーサーに関して、液晶の比誘電率よりも小さい比誘電率の誘電体を用いて映像信号配線に沿って映像信号配線を被覆することで、映像信号配線の波形のなまり（歪み）を低減している。この特許では液晶セルの組み立てに、液晶セル内部を真空にしてから、注入口から大気圧を利用して液晶を注入する方法を用いていた。この液晶注入方法では、大型液晶パネルを生産する時に一度に数百セルを同時に処理するバッチ方式を採用していた。

【0005】特開2002-258321や特開2002-323706では、横電界方式の画素開口率を向上させかつ映像信号配線の信号遅延を防止するために、液晶の比誘電率よりも小さい比誘電率の誘電体を用いて映像信号配線に沿って映像信号配線を被覆しこの誘電体の上に透明な導電体を映像信号配線に沿って配置している。

【0006】

【発明が解決しようとする課題】

従来の横電界方式液晶パネルでは、映像信号配線の電界の影響をシールドするために、映像信号配線の左右両側に共通電極を配置している。縦方向クロストークを完全に解決するためには、この構造だけでは、共通電極の電極幅を映像信号配線よりも約1.5倍以上大きくしなければならず、画素の開口率が低下してしまうことをさけられなかった。

【0007】カラーフィルター側の遮光膜（ブラックマスク）を導電体薄膜（クロム酸化物層とクロム金属薄膜層）で形成しこの電位を共通電極電位に設定し、映像信号配線と同じ方向に細長くのびるホトリソスペーサーを液晶よりも誘電率の大きな絶縁物で形成することで、映像信号配線の電気力線をホトリソスペーサーに集束させ、垂直方向のクロストークを低減することは可能である。しかしこの方法では、誘電率を大きくするため、遮光膜（ブラックマスク）と映像信号配線間の容量が大きくなってしまい映像信号配線の信号波形が遅延し歪んでしまい、大型液晶パネルには適していない。

【0008】特開平11-24104にあるように映像信号配線上にパッシベーション膜を形成し、その上に映像信号配線にそうようにシールド電極を配置することで映像信号配線をほぼ完全にシールドすることができる。しかしこの構造では保護膜（パッシベーション膜）の厚みが0.3ミクロンメートルから1ミクロンメートル程度と薄いことと、保護膜は酸化シリコン膜や窒化シリコン膜の場合には比誘電率は4~6と大きいために、シールド電極と映像信号配線間の容量が大きくなってしまい映像信号配線の信号波形が、遅延し、歪んでしまい、大型液晶パネルには適していない。

【0009】特開2001-209053では、映像信号配線とカラーフィルター側の共通電極の容量を低減するために比誘電率の小さな誘電体を用いて映像信号配線をつつみこむように細長くホトリソスペーサーを形成している。しかしこの特許では液晶セルへの液

晶注入が従来の注入口から液晶を注入する方法を用いており、細長いホトリソスペーサーは、液晶注入速度をいちじるしく低下させる作用をもっているため、生産効率は非常に悪くなってしまう。

【0010】特開2002-258321や特開2002-323706では、画素開口率を向上させかつ映像信号配線の信号遅延を防止するために、液晶の比誘電率よりも小さい誘電体を用いて映像信号配線に沿って映像信号配線を被覆し、この誘電体の上に透明な導電体を映像信号配線に沿って配置している。しかしこの構造では、液晶セルを形成するときに必要なスペーサーを同時に形成することができないため、もう一回ホトリソ工程を用いてホトリソスペーサーを形成しなければならない。そのためにプロセスが複雑になりコストアップをさけることができない。

【0011】特開2002-258321で開示されている技術だけでは、光ぬけの少ないコントラストの高い横電界方式液晶パネルを作ることはできない。映像信号配線に沿って映像信号配線を被覆している誘電率の小さな誘電体のバンプのテーパー角が40度以上大きい場合には、従来のラビング布を用いるラビング処理では、ラビング布の毛先きの運動方向がバンプのテーパー部分で横すべりしたり、バンプの傾斜面にラビング布の毛先きがあたらなかつたりするため、配向不良の領域が発生してしまう。

バンプのテーパー部分の近傍にこの配向不良の領域が多発するため、光ぬけが発生し、コントラストを悪化させる。

【0012】本発明は、上記の問題を解決するものであり、その目的は、開口率を大幅に改善し、透過率を向上し、明るいコントラストの高い大型カラー液晶表示装置を安価に歩留り良く製造できるようにすることである。

### 【0013】

【課題を解決するための手段】前記課題を解決し、上記目的を達成するために、本発明では、下記の手段を用いる。

【0014】〔手段1〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、映像信号配線に沿って映像信号配線をつつみこむように細長い絶縁体のバンプを形成する。その後、この細長い絶縁体バンプの上に、映像信号配線と細長い絶縁体バンプを被覆し、かつ映像信号配線の電界をシールドするための共通電極を映像信号配線にそうように形成した。

【0015】〔手段2〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、映像信号配線に沿って、映像信号配線をつつみこむように細長い絶縁体のバンプを形成する。その後、この細長い絶縁体バンプの側壁の両側に映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成した。

【0016】〔手段3〕手段1, 2に記載した映像信号配線をつつみこむように形成された細長い絶縁体のバンプが液晶セルを組み立てる時に、液晶セルギャップを決定するスペーサーの役割をはたすようにした。

【0017】〔手段4〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、ハーフトーン露光技術を用いて、映像信号配線をつつみこむように細長い絶縁体のバンプと液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの上に映像信号配線の電界をシールドするための共通電極を映像信号配線をおおうように形成した。

【0018】〔手段5〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、ハーフトーン露光技術を用いて、映像信号配線をつつみこむように細長い絶縁体のバンプと液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの両側の側壁に映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成した。

【0019】〔手段6〕手段1, 2, 3, 4, 5において、映像信号配線をシールドするための共通電極に、酸化インジウムIn<sub>2</sub>O<sub>3</sub>または酸化亜鉛ZnOを主体とする金属酸化物透明導電体または窒化チタン(TiN<sub>x</sub>)または、酸窒化チタン(TiO<sub>x</sub>N<sub>y</sub>)または、窒化チタンシリサイド(TiSiN<sub>y</sub>)またはチタンシリサイド(TiSi<sub>x</sub>)な

どのチタン金属化合物からなり可視光透過率が20%以上ある薄膜透明導電体を用いた。

【0020】〔手段7〕手段1, 2, 3, 4, 5において、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体バンプの断面形状が半円形または、半だ円形、または双曲線形または放物曲線形のようにまるまるっており、バンプのテーパー角度が30度以下であるようにテーパー角をできるだけ小さくした。

【0021】〔手段8〕手段1, 2, 3, 4, 5において映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体バンプが、映像信号配線と走査線が交差している領域には存在しないようにした。

【0022】〔手段9〕手段4, 5においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの頂点付近の領域は、共通電極によって被覆されておらずスペーサーの材料である誘電体がじかに露出しているようにした。 10

【0023】〔手段10〕手段4, 5において、細長い絶縁体バンプの高さと、液晶セルのセルギャップを決定するスペーサーの高さの差 $h_2$ が0.2ミクロンメーターから2.0ミクロンメーターの範囲にあるようにした。

【0024】〔手段11〕手段4, 5においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの密度が、 $1 \text{ mm}^2$ あたり1個から75個の範囲にあるように均一に配置した。

【0025】〔手段12〕手段4, 5においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの面積が $1 \text{ mm}^2$ あたり200平方ミクロンメタから2000平方ミクロンメーターの範囲にあるようにした。 20

【0026】〔手段13〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの上に映像信号配線の電界をシールドするために共通電極を映像信号配線に沿うように形成し、かつ走査線の上にも同様に走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を、走査線をはさみこむように形成した。 30

【0027】〔手段14〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、映像信号配線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体バンプの両側の側壁に映像信号配線をシールドするための共通電極を映像信号配線をはさみこむように形成し、かつ走査線の上にも同様に走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を走査線をはさみこむように形成した。 30

【0028】〔手段15〕手段13, 14に記載された、映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体のバンプが液晶セルを組み立てる時に、液晶セルギャップを決定するスペーサーの役割をはたすようにした。

【0029】〔手段16〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、ハーフトーン露光方法を用いて、映像信号配線をつつみこむように細長い絶縁体のバンプと、液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの上に映像信号配線をシールドするための共通電極を映像信号配線をおおうように形成し、かつ走査線の上にも、同様にハーフトーン露光方法を用いて走査線をつつみこむように細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に、走査線の電界をシールドするための共通電極を走査線をはさみこむように形成した。 40

【0030】〔手段17〕横電界方式アクティブマトリックス基板上の映像信号配線の上に、ハーフトーン露光方法を用いて、映像信号配線をつつみこむように細長い絶縁体のバンプと、液晶セルギャップを決定するスペーサーを同時に形成し、この細長い絶縁体のバンプの両側の側壁に、映像信号配線の電界をシールドするための共通電極を映像信号配線をはさみこむように形成し、かつ、走査線の上にも同様に、ハーフトーン露光方法を用いて走査線をつつみこむように、細長い絶縁体のバンプを形成し、この細長い絶縁体のバンプの両側の側壁に走査線の電界をシールドするための共通電極を走査線をはさみこむように形成した。 50

【0031】〔手段18〕手段13, 14, 15, 16, 17において、映像信号配線と走査線の電界をシールドするための共通電極に酸化インジウム $In_2O_3$ または酸化亜鉛を主体とする金属酸化物透明導電体または窒化チタン( $TiN_x$ )または、酸窒化チタン( $TiO_xN_y$ )または窒化チタンシリサイド( $TiSi_xN_y$ )またはチタンシリサイド( $TiSi_x$ )などのチタン金属化合物からなり、可視光透過率が20%以上ある薄膜透明導電体を用いた。

【0032】〔手段19〕手段13, 14, 15, 16, 17において、映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体バンプの断面形状が、半円形または、半だ円形、または、双曲線形または放物線形のようにまるまっており、バンプのテーパー角度が30度以下であるように、テーパー角度をできるだけ小さくした。10

【0033】〔手段20〕手段13, 14, 15, 16, 17において、映像信号配線と走査線の上に映像信号配線と走査線をつつみこむように形成された細長い絶縁体バンプが、映像信号配線と走査線が交差している領域には、存在しないようにした。

【0034】〔手段21〕手段16, 17において、ハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの頂点付近の領域は、映像信号配線の電界をシールドするための共通電極によって被覆されておらず、スペーサーを形成している誘電体が直接露出しているようにした。

【0035】〔手段22〕手段16, 17において、細長い絶縁体バンプの高さと、液晶セルのセルギャップを決定するスペーサーの高さの差 $h_2$ が0.2ミクロンメーターから2.0ミクロンメーターの範囲にあるようにした。20

【0036】〔手段23〕手段16, 17においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの密度が、 $1\text{ mm}^2$ あたり1個から75個の範囲にあるようにした。

【0037】〔手段24〕手段16, 17においてハーフトーン露光方法を用いて細長い絶縁体バンプと同時に形成されたスペーサーの面積が $1\text{ mm}^2$ あたりにつき200平方ミクロンメーターから2000平方ミクロンメーターの範囲にあるようにした。

【0038】〔手段25〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線を左右上下からはさみこむように、ゲート絶縁膜やパッシベーション膜をかいして上層と下層に共通電極を配置し、下層の共通電極は、光を透過させない金属電極からなり、上層の共通電極は可視光を透過する透明電極で構成されており、かつ上層の共通電極の方が下層の共通電極よりも電極幅がひろく、液晶駆動電極側にはみ出している構造とした。30

【0039】〔手段26〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極とがともに直線状に配置されていて、画素内の液晶駆動電極と画素内の共通電極とが、1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造とした。

【0040】〔手段27〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体の両方がともに直線状に配置されていて、この絶縁体に沿うように形成されたシールド共通電極と画素内の液晶駆動電極と画素内の共通電極とが、1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造とした。40

【0041】〔手段28〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極のみが、1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲してい50

る構造とした。

【0042】〔手段29〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造とした。

【0043】〔手段30〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造とした。

10

【0044】〔手段31〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線と映像信号配線の上に、映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極と画素内の共通電極とが、1画素内で液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲している構造とした。

【0045】〔手段32〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体とが、ともに直線状に配置されていて、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、1画素内で液晶分子の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲している構造とした。

【0046】〔手段33〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内共通電極とが、ともに直線状に配置されていて、画素内の液晶駆動電極のみが、1画素内で液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲している構造とした。

30

【0047】〔手段34〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で液晶の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲している構造とした。

【0048】〔手段35〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線と、映像信号配線の上に映像信号配線をつつみこむように形成された細長い絶縁体と、この細長い絶縁体に沿うように形成されたシールド共通電極と、画素内の液晶駆動電極と、画素内の共通電極とが、ともに1画素内で、液晶分子の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲しており、かつカラーフィルター層と遮光膜(ブラックマスク)とが、映像信号配線の形状とほぼ同様に液晶分子の配向方向に対して1画素内で90度をのぞく60度から120度の角度の範囲で1回以上屈曲している構造とした。

40

【0049】〔手段36〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線に沿って映像信号配線を被覆している絶縁体バンプの比誘電率が3.3以下でかつ絶縁体バンプの高さ $h_1$ が1.5ミクロンメーターから5.0ミクロンメーターの範囲にあり、かつ映像信号配線のエッジから絶縁体のバンプのエッジまでの距離 $L_1$ を3.0ミクロンメーターから6.0ミクロンメーターの範囲にある構造とした。

50

【0050】〔手段37〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線を被覆している絶縁体のバンパのエッジから絶縁体バンプをつつみこんでいるシールド共通電極のエッジまでの距離 $L_2$ が0.5ミクロンメーターから10.0ミクロンメーターの範囲にある構造とした。

【0051】〔手段38〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線を被覆している絶縁体バンプの原料となるモノマーまたはオリゴマーがベンゾシクロブテン構造を1個以上有するものまたはその誘導体であることまたはフルオレン骨格を1個以上有するものまたは、その誘導体からなるものを用いた。

【0052】〔手段39〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、映像信号配線を被覆する細長い絶縁体バンプを形成する時に、同時に、有効画素領域全体をとりかこみ液晶セルのメインシールが形成される領域と同じ位置に、メインシールが、大気の圧力や液晶の圧力により破断されることを防止するための閉ループ状のバリアーバンプスペーサーを1本以上形成した。

【0053】〔手段40〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線のパターンニング(走査線形成)

- 2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

【0054】〔手段41〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

- 2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極の形成

【0055】〔手段42〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線形成

- 2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

【0056】〔手段43〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

- 2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

- 3) 映像信号配線と液晶駆動電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

- 5) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極の形成

【0057】〔手段44〕横電界方式アクティブマトリックス液晶表示装置のアクティブ

10

20

30

40

50

マトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1 ) 走査線形成

2 ) 映像信号配線と液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成 (ハーフトーン露光技術)

3 ) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成 (ハーフトーン露光技術)

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 映像信号配線シールド用透明共通電極と画素内透明共通電極の同時形成

【0058】〔手段45〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。 10

1 ) 走査線と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成 2 ) 映像信号配線と液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成 (ハーフトーン露光技術)

3 ) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成 (ハーフトーン露光技術)

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 映像信号配線シールド用透明共通電極の形成

【0059】〔手段46〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において映像信号配線をつつみこむように形成された細長い絶縁体に沿うように形成されたシールド共通電極が有効表示画素領域全体にわたって互いに連結されており、映像信号電圧の中心電圧付近の電位に設定した。 20

【0060】〔手段47〕手段1, 2, 3, 4, 5, 13, 14, 15, 16, 17において、1画素内で液晶分子を駆動するために必要な電極が、薄膜トランジスタ素子に連結されている1本の液晶駆動電極と、1画素の左右両側に存在している映像信号配線をシールドするための下層共通電極と、映像信号配線を被覆している細長い絶縁体に沿って形成されているシールド用上層共通電極の3種類の電極から構成されており、画素内部の共通電極が1本も存在していない構成とした。

【0061】〔手段48〕横電界方式アクティブマトリックス液晶表示装置に関して、不透明な金属材料または金属シリサイドまたは、金属窒化物から形成されている画素内の共通電極や、映像信号配線をシールドするための下層共通電極や、液晶駆動電極の膜厚のうち1番厚い膜厚と液晶セルギャップの両方を合計した膜厚のネガレジストを塗布した後、ホトスペーサー形成用のホトマスクを用いてスペーサーを形成する部分に紫外線を照射して完全露光した後、アクティブマトリックス基板の裏面から紫外線を有効画素領域全面に照射してから現像することで、アクティブマトリックス基板側の凹凸の平坦化とホトリソスペーサーの形成を同時におこなうようにした。 30

【0062】〔手段49〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1 ) 走査線 (Gate電極) と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 薄膜トランジスタのシリコン素子分離 (シリコンisland化) 40

3 ) 映像信号配線と液晶駆動電極の同時形成

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

6 ) ホトスペーサー形成と有効画素領域の平坦化 (ハーフトーン裏面露光技術)

【0063】〔手段50〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1 ) 走査線 (Gate電極) と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 薄膜トランジスタのエッティングストッパーのチャネル部パターン形成

3 ) 映像信号配線と液晶駆動電極の同時形成 50

4 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

5 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

6 ) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【0064】〔手段51〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1 ) 走査線( Gate電極)と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

3 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と映像信号配線端子部の同時形成 10

5 ) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【0065】〔手段52〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1 ) 走査線( Gate電極)と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 薄膜トランジスタのシリコン素子分離(シリコンisland化)と端子部と静電気対策用保護回路形成のためのコンタクトホールの同時形成(ハーフトーン露光技術-----1st&2nd 2回露光)

【0066】〔手段53〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。 20

1 ) 走査線( Gate電極)と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成

2 ) 映像信号配線と液晶駆動電極と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーン露光技術)

3 ) 端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4 ) 走査線端子部と映像信号配線端子部と静電気対策用保護回路の同時形成

5 ) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【0067】〔手段54〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。 30

1 ) 走査線( Gate電極)と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成( P-SiN<sub>x</sub>\a-Si i層\ n<sup>+</sup>a-Si層はシャドーフレームを用いるマスキングdepoプロセスを使用)

2 ) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーン露光技術)

3 ) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【0068】〔手段55〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の有効画素領域の平坦化処理工程で用いられるハーフトーン裏面露光装置に関して、紫外線用石英ファイバーケーブルや紫外線LEDをインライン状にたばねて配置し、横電界方式アクティブマトリックス液晶表示基板の有効画素領域のみに、紫外線を裏面側から走査露光できるようにした。 40

【0069】〔手段56〕手段48, 49, 50, 51, 52, 53, 54に記載されているハーフトーン裏面露光プロセスに関して、ホトスペーサー形成用のホトマスクを用いてスペーサーを形成する部分に紫外線を照射して完全露光した後、アクティブマトリックス基板の裏面から紫外線を有効画素領域全面に走査露光する。次に現像した後、アクティブマトリックス基板側の有効画素領域内の基板表面の凹凸の度合いと、スペーサーの高さを白色干渉計を用いて計測し、計測値に応じてネガ型ホトレジストのコーティング膜厚とハーフトーン裏面走査露光量をフィードバック制御できるようにした。

【0070】〔手段57〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。 50

- 1) レーザーを用いてガラス基板内部にアライメントマークを形成する。

- 2) 異なる種類の金属または金属化合物または合金を2層以上堆積する。(ただしリーザーで形成したアライメントマーク部には堆積しない。)

- 3) ポジレジストを全面に塗布した後、通常ホトマスクを用いるアンダー露光方法による1次ハーフトーン露光をおこない、Gate Bus ラインとCommon Bus ラインを露光する。次に2次露光でGate Bus ラインとCommon Bus ラインと映像信号配線シールド用共通電極と画素内共通電極とを通常露光する。

- 4) 現像後、1次のDryエッチング法または、Wetエッチング法を用いて堆積した金属のエッチングをおこなう。次にハーフトーン露光領域のポジレジストを酸素プラズマアッティング法などを用いて除去した後、2次のDryエッチング法またはWetエッチング法を用いてハーフトーン露光領域の不必要的金属層をエッチングする。

上記1次、2次のエッチング工程によりGate Bus とCommon Bus と、映像信号配線シールド用共通電極と画素内共通電極とを形成する。

5) Gate 絶縁膜とノンドープ薄膜半導体層( $i$ 層a-Si)と $n^+ a - Si$ 層(オーミックコンタクト層)を堆積した後、ポジ型ホトレジストをコートして、通常ホトマスクを用いるアンダー露光方法による1次ハーフトーン露光をおこないa-Si islandを露光する。

次に2次露光でGate 端子接続部と静電気対策用保護回路部にコンタクトホールを通常露光する。

6) 現像後1次のDryエッチング法を用いてGate 絶縁膜とノンドープ薄膜半導体層( $i$ 層a-Si)と $n^+ a - Si$ 層(オーミックコンタクト層)をエッチングしてGate 端子接続部と静電気対策用保護回路部のコンタクトホールを形成する。次にハーフトーン露光領域のポジレジストを酸素プラズマアッティング法などを用いて除去した後、2次のDryエッチング法を用いてハーフトーン露光領域の不必要的ノンドープ薄膜半導体層( $i$ 層a-Si)と $n^+ a - Si$ 層(オーミックコンタクト層)をエッチングする。上記1次、2次のエッチング工程によりa-Si islandとGate 端子接続部と静電気対策用保護回路部のコンタクトホールを形成する。

7) 映像信号配線と液晶駆動電極と静電気対策用保護回路とGate 端子の同時形成(通常ホトマスクを用いるハーフトーン露光工程を適用する。)

【0071】〔手段58〕アクティブマトリックス表示装置の薄膜トランジスタ素子の製造工程で用いられる露光装置に関して、目標とする薄膜トランジスタのチャネル長の約半分のチャネル長でソース電極とドレイン電極を形成した通常ホトマスクを用いて、1次のハーフトーン露光(不完全露光)をおこなった後、目標とする薄膜トランジスタのチャネル長の約半分程度、アクティブマトリックス基板を水平方方向にシフトさせてから再度2次のハーフトーン露光(不完全露光)をおこなうことのできる機能を露光装置に付加した。

【0072】〔手段59〕アクティブマトリックス表示装置の薄膜トランジスタ素子の製造工程に関して、目標とする薄膜トランジスタ素子のチャネル長の約半分のチャネル長でソース電極とドレイン電極を形成した通常ホトマスクを用いて、1次のハーフトーン露光(不完全露光- - -アンダー露光)をおこなった後、目標とする薄膜トランジスタのチャネル長の約半分程度アクティブマトリックス基板を水平方向にシフトさせてから再度2次のハーフトーン露光(不完全露光- - -アンダー露光)をおこなった後、ポジレジストを現像し、薄膜トランジスタ素子のチャネル部分のポジレジストの膜厚を目標とするチャネル長の長さだけ薄くした。

【0073】〔手段60〕手段59に記載されたハーフトーンシフト露光技術を用いて、薄膜トランジスタのシリコン素子分離と映像信号配線(ソース電極)とドレイン電極(液晶駆動電極または透明画素電極に連結されている電極)の形成を同時におこなった。

【0074】〔手段61〕手段59に記載されたハーフトーンシフト露光技術を用いて、アクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線(Gate 電極)と共通電極の同時形成

10

20

30

40

50

2) 映像信号配線(ソース電極)とドレイン電極と薄薄トランジスタのシリコン素子分離の同時形成(ハーフトーンシフト露光技術)

3) 走査線端子部と映像信号配線端子部と静電気対策用保護回路形成のためのコンタクトホール形成

4) 走査線端子部と映像信号配線端子部と静電気対策用保護回路と透明画素電極の同時形成

【0075】〔手段62〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程に手段59で記述されているハーフトーン・シフト露光技術を用い、下記の工程にしたがっておこなうようにした。

1) 走査線(Gate電極)と画素内共通電極と映像信号配線シールド用下層共通電極の同時形成(P-SiNx\a-Si i層\n+a-Si層、はシャドーフレームを用いるマスキングdepoプロセス使用) 10

2) 映像信号配線と液晶駆動電極と静電気対策用保護回路と走査線端子部と薄膜トランジスタのシリコン素子分離の同時形成(ハーフトーン・シフト露光技術)

3) ホトスペーサー形成と有効画素領域の平坦化(ハーフトーン裏面露光技術)

【0076】〔手段63〕手段3, 4, 5, 15, 16, 17で用いられているスペーサーバンプが、アクティブマトリックス基板と対向するカラーフィルター基板を真空中でかさねあわせて液晶Cellを形成する時に、大気圧の応力により0.1ミクロンメートルから0.5ミクロンメートルの範囲で有効画素領域全面にわたって、均一に弾性変形するような特性を持つようにした。 20

【0077】〔手段64〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1) 走査線形成

2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極の同時形成 30

【0078】〔手段65〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1) 走査線と映像信号配線シールド用下層共通電極の同時形成

2) 薄膜トランジスタのシリコン素子分離(シリコンisland化)

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成 40

【0079】〔手段66〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

1) 走査線形成

2) 薄膜トランジスタのエッティングストッパーのチャネル部パターン形成

3) 映像信号配線(ソース電極)とドレイン電極の同時形成

4) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成(ハーフトーン露光技術)

5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成 50

【0080】〔手段67〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線と映像信号配線シールド用下層共通電極の同時形成

- 2) 薄膜トランジスタのエッチングストッパーのチャネル部パターン形成

- 3) 映像信号配線（ソース電極）とドレイン電極の同時形成

- 4) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成（ハーフトーン露光技術）

- 5) 端子部とドレイン電極部と静電気対策用保護回路のためのコンタクトホール形成

- 6) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

10

【0081】〔手段68〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線形成

- 2) 映像信号配線（ソース電極）とドレイン電極と薄膜トランジスタのシリコン素子分離の同時形成（ハーフトーン露光技術）

- 3) 映像信号配線被覆用スペーサーバンプの形成または映像信号配線被覆用バンプとスペーサーの同時形成（ハーフトーン露光技術）

- 4) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

- 5) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成

20

【0082】〔手段69〕横電界方式アクティブマトリックス液晶表示装置のアクティブマトリックス基板の製造工程を下記の工程にしたがっておこなうようにした。

- 1) 走査線と映像信号配線シールド用下層共通電極の同時形成

- 2) 映像信号配線（ソース電極）とドレイン電極と薄膜トランジスタのシリコン素子分離の同時形成（ハーフトーン露光技術）

- 3) 映像信号配線被覆用スペーサーバンプの形成または、映像信号配線被覆用バンプとスペーサーの同時形成（ハーフトーン露光技術）

- 4) 端子部とドレイン電極部と静電気対策用保護回路形成のためのコンタクトホール形成

- 5) 映像信号配線シールド用透明共通電極と画素内透明共通電極と液晶駆動電極との同時形成。

30

【0083】〔手段70〕手段47で用いられている構造でかつ映像信号配線と映像信号配線を被覆している細長い絶縁体バンプと映像信号配線の電界をシールドするためのシールド用上層共通電極とシールド用下層共通電極と、1本の液晶駆動電極とが、1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲しており、かつ対向するカラーフィルター基板のカラーフィルター層と遮光膜（ブラックマスク）とが、映像信号配線の形状とほぼ同様に、液晶の配向方向に対して1画素内で0度をのぞく0度から30度の範囲で1回以上屈曲しているようにした。

【0084】〔手段71〕手段47で用いられている構造でかつ映像信号配線と映像信号配線を被覆している細長い絶縁体バンプと映像信号配線の電界をシールドするためのシールド用上層共通電極とシールド用下層共通電極と、1本の液晶駆動電極とが、1画素内で液晶分子の配向方向に対して90度をのぞく60度から120度の角度の範囲で1回以上屈曲しており、かつ対向するカラーフィルター基板のカラーフィルター層と遮光膜（ブラックマスク）とが、映像信号配線の形状とほぼ同様に、液晶の配向方向に対して90度をのぞく60度から120度の範囲で1回以上屈曲しているようにした。

40

#### 【0085】

【作用】手段1，2，3，4，5により映像信号配線の電界をシールドするためのシールド共通電極の幅を大幅にせまくすることができ、開口率を大幅に向上することができるようになる。特に手段3，4，5を用いることで映像信号配線被覆バンプとスペーサーを併用したり、映像信号配線被覆バンプとスペーサーをハーフトーン露光技術を用いて同時に形成することで、工程を大幅に短縮することができる。特開2002-258321や特

50

開 2 0 0 2 - 3 2 3 7 0 6 では、カラーフィルター基板にホトスペーサーを形成しなければならず工程の増加をおさえることができない。特に液晶セルギャップが 3 ミクロンメーター以下になってきた時、本発明の映像信号配線被覆バンプとスペーサーを併用する方式は非常にプロセスが簡単になり低コスト化を実現できる。

【 0 0 8 6 】手段 2 , 5 により映像信号配線とシールド共通電極の間で形成される容量を最少にすることができるので、液晶表示装置が超大型化 ( 4 0 インチ以上 ) しても映像信号波形の歪を最少限におさえながら、開口率を最大に向上することができる。特に液晶セルギャップが 2 . 5 ミクロン以下になってきた時に手段 2 , と 5 は、映像信号波形の歪を低減する有効な方法となる。

【 0 0 8 7 】手段 6 , 1 8 を用いることで映像信号配線被覆バンプとシールド共通電極との密着性が向上し膜はがれが発生しなくなり、歩留りを向上することができる。さらにシールド共通電極の材質を透光性の材料にすることでシールド共通電極の領域からも液晶駆動した時に光を透過させることができるので実効的な透過率を向上することができ明るく、コントラストの高い表示装置を作ることができる。

【 0 0 8 8 】手段 7 , 1 9 を用いることでラビング配向処理時のラビング布の毛先きの運動がなめらかになり配向不良の発生を防止することができる。特開 2 0 0 2 - 2 5 8 3 2 1 や特開 2 0 0 2 - 3 2 3 7 0 6 に記載してある構造では、アクティブマトリックス基板の凹凸部のテーカー角度が 3 0 度以下になっていないため、従来のラビング配向処理方法を用いた配向方法では凹凸部のテーカー領域でラビング布の毛先きの運動がなめらかでなくなり、ラビング布の毛先きが接触しない領域が発生し、配向不良をひきおこす。このため配向不良の部分で黒表示時に光がもれる現象が発生し、コントラストをいちじるしく低下させてしまう。本発明では、映像信号配線を被覆しているバンプのテーカー角度を 3 0 度以下に制御しているため配向不良の領域はまったくないので、黒表示時の光もれがないためコントラストの高い画像を得ることができる。

【 0 0 8 9 】手段 4 , 5 , 8 , 1 0 , 1 1 , 1 2 , 1 6 , 1 7 , 2 0 , 2 3 , 2 4 により液晶セルを組み立てる時に、液晶滴下真空合着アライメント装置を用いると液晶が液晶セル内部にスムーズにひろがりやすくなり、残留気泡の問題も生じにくくなる。従来の液晶セルを大気中で組み立ててから個々のセルに分断してから真空中で液晶を注入する方法は、本発明の構造の液晶セルには適していない。従来の液晶注入法では時間が長くなってしまい生産効率が非常に悪くなってしまう。液晶滴下真空合着アライメント装置が量産ラインに導入されはじめたので本発明のような構造でも問題なく生産できるのである。

【 0 0 9 0 】手段 9 , 2 1 により液晶滴下真空はりあわせ工程での合着アライメント動作時に、アクティブマトリックス基板とカラーフィルター基板とが接触した時に、シールド共通電極の膜はがれが発生しなくなり、配向膜のダメージが最少におさえられる。

【 0 0 9 1 】手段 1 3 , 1 4 , 1 5 , 1 6 , 1 7 を用いることでシールド共通電極と走査線の間で形成される容量を低減することができるので、液晶表示装置が超大型化 ( 4 0 インチ以上 ) しても走査線の走査信号波形の歪を最少限におさえながら、開口率を最大に向上することができる。特に手段 1 4 , 1 7 を用いることで映像信号配線と走査線の両方の信号波形の歪を最少限におさえてかつ開口率を最大限に向上することが可能となる。

【 0 0 9 2 】手段 2 5 により、映像信号配線を絶縁膜をかいして上層と下層からシールド共通電極により立体的にシールドすることでシールド効果を高めることができ、シールド電極の幅をせばめても縦方向クロストークは発生しなくなり、開口率を最大に拡大することができる。上層シールド共通電極の方がシールド効果が大きいので上層シールド共通電極の幅を下層シールド共通電極の幅よりも広げることで最も効率の良いシールドと高開口率を得ることができる。

【 0 0 9 3 】手段 2 6 , 2 7 , 2 8 , 2 9 , 3 0 により正の誘電率異方性液晶分子を 1 画素内で異なる 2 方向 ( 左回りと右回り ) に回転駆動させることができ可能となり、広視野角化を実現することができる。さらにカラーシフト現象も大幅に低減することができ液晶 T V に適した画像品質を得ることができる。本発明の構造により、横電界方式液晶モードで、広視野角、高開口率、低コスト、高コントラスト、高速応答を実現できる。

10

20

30

40

50

【0094】手段31, 32, 33, 34, 35により負の誘電率異方性液晶分子を1画素内で異なる2方向(左回りと右回り)に回転駆動することが可能となり、広視野角化を実現することができる。

【0095】手段36, 37, 38により横電界方式液晶表示装置のセルギャップが3.0ミクロンメーター以下になってもシールド共通電極と映像信号配線との間に形成される容量の増大をおさえることができるので、映像信号配線の信号波形の歪を低減できる。さらに液晶駆動電極とシールド共通電極の間で発生する電界をそれぞれの電極のエッジに集中できるので、セルギャップが3.0ミクロンメーター以下になっても液晶駆動電圧を大きくしなくても液晶分子を駆動することが可能である。

【0096】手段39により、液晶滴下真空合着アライメント工程で問題になっているメインシール破断を防止することが可能である。メインシール塗布領域にスペーサーバンプが存在するとこのスペーサーバンプが液晶のつきぬけに対して防御壁の作用をもっているからである。メインシール塗布領域に設置される閉ループ状のスペーサーバンプの幅は有効画素領域のスペーサーバンプよりも幅を大きくすると防御壁の効果はさらに大きくなる。さらに本発明を用いるとメインシール材にセルギャップを決定するガラスファイバーを混入させる必要がなくなるため、アルミニウムやアルミニウム合金を走査線や映像信号配線に用いた場合にメインシールに混入されたガラスファイバーによる配線の圧力破断の現象が完全になくなる。

【0097】手段40, 41, 42, 43, 44, 45を用いることで、映像信号配線被覆用スペーサーバンプの形成またはハーフトーン露光技術を用いて映像信号配線被覆用バンプとスペーサーを同時に形成することで工程数を削減でき、コストダウンがはかれる。従来の特開2002-258321や特開2002-323706では、ホトスペーサーを別に形成するための工程が必要となり製造コストの増加をさけることができない。

【0098】手段46を用いることで、シールド共通電極が面状に連結されインピーダンスをさげることができる。この構造によりシールド共通電極の膜厚を可能なかぎり薄くすることができる。ドット反転駆動方式の場合、シールド共通電極の膜厚は300~500オングストローム程度で十分である。本発明と手段7, 19を用いることでラビング処理時のラビング布の毛先きの運動がなめらかになり、配向不良の領域がなくなり、黒表示の光もれが完全になくなり、コントラストの良好な画像と均一な中間調表示が得られるようになる。さらに本発明のようにシールド共通電極が画素の左右だけでなく上下とも互いに連結される構造では、シールド共通電極の1部分が断線しても線欠陥にはならず画像に大きな影響があらわれにくい。そのためプロセス歩留りが大幅に向上する。

【0099】手段47, 70, 71を用いることで超高精細でかつ超高開口率、高速応答、広視野角の横電界方式液晶表示装置を実現できる。本発明の構造ならば映像信号配線のピッチが50ミクロンメーター程度になっても開口率をさげることなく液晶分子を1画素内で異なる2方向(左回りと右回り)に回転駆動させることができる。本発明の構造では、映像信号配線に対応する遮光膜(ブラックマスク)は、かならずしも必要ないが、遮光膜(ブラックマスク)とオーバーコート層に導電性をもたせることでカラーフィルター層の静電気の帶電を防止することができる。

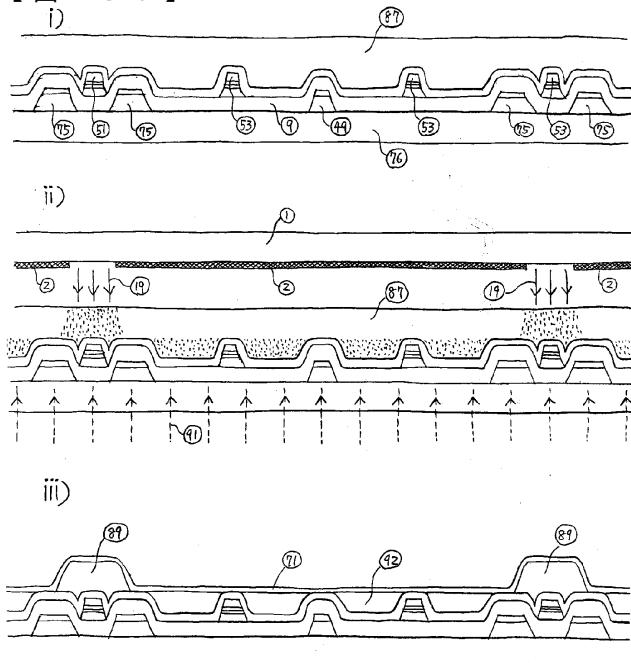

【0100】手段48を用いることで横電界方式アクティブマトリックス基板の平坦化とホトスペーサーを同時に形成することができ工程を簡略化できる。本発明の裏面側からの紫外線露光による平坦化では、液晶駆動電極や共通電極の上層に平坦化膜が残らないため、液晶を駆動するための電圧が増大することができない。さらに、液晶駆動電極や共通電極の上に平坦化膜が残らないために、有機平坦化膜の分極現象や、チャージトラップ現象が発生しない。このため残像現象が発生しない。アクティブマトリックス基板表面の凹凸がなくなっているため、ラビング配向処理でのラビング布の毛先きの運動がなめらかになり配向不良が生じない。配向不良が生じないため黒表示時の光ぬけがないので良好な黒表示を得ることができる。高コントラストで中間調表示でのムラも発生しない。

【0101】手段49, 50, 51, 52, 53, 54を用いることで、横電界方式液晶表示装置を製造する時に、アクティブマトリックス基板の平坦化とホトスペーサーを同時

10

20

30

40

50

に形成することができ、工程の短縮をおこなうことができる。特に手段 5 4 を用いるとアクティブマトリックス基板の全工程が 3 回のホトマスク工程で完成するため大幅なコストダウンをおこなうことができる。

本発明の裏面露光平坦化法を用いることで、液晶駆動電極と共に電極の上に平坦化膜が残らないため、液晶駆動電圧を増大させることができない。さらに液晶駆動電極と共に電極の上に平坦化膜が存在しないため、平坦化膜の分極現象やチャージトラップ現象が発生しない。それゆえ残像現象が発生しない。

基板の凹凸がなくなりラビング処理でのラビング布の毛先きの運動がなめらかになるため、配向不良が発生しない。

【0102】手段 5 5 , 5 6 を用いることでアクティブマトリックス基板が 2 メートル以上に拡大しても、裏面走査露光光学系を簡単に作ることができる。本発明の光学系は露光照度を調整しやすく基板サイズが拡大しても、全領域にわたり均一な露光をおこなうことができる。横電界方式液晶表示装置は液晶セルギャップに非常に敏感なため、ホトスペーサーの高さだけではなく、平坦化した領域の平坦化の度合いまで管理しないと、中間調領域でムラが発生してしまう。本発明の製造装置を用いてフィードバックをかけることで、セルギャップのバラツキのないアクティブマトリックス基板を製造することができる。

【0103】手段 5 7 を用いることで、通常ホトマスクを用いてハーフトーン露光プロセスにより映像信号配線シールド用下層共通電極と画素内共通電極とを薄膜化でき、かつ薄膜トランジスタ部のシリコン素子分離（シリコン island 化）とコンタクトホールを同時に形成することができる。ホトマスク工程をふやすことなくアクティブマトリックス基板の高性能化を実現できる。

さらに映像信号配線と液晶駆動電極を同時に形成する時に、通常ホトマスクを用いるハーフトーン露光プロセスを適用することで液晶駆動電極も 300 ~ 500 オングストローム以下に薄くすることが可能となり平坦化膜をコーティングする平坦化工程はまったく必要なくなり、製造コストを大幅に低減できる。

【0104】手段 5 8 , 5 9 , 6 0 , 6 1 , 6 2 により、同じ通常ホトマスクを用いてハーフトーンシフト露光することで、高価な透過光量変調ホトマスク（ハーフトーンホトマスク）を用いなくても、簡単にアクティブマトリックス基板のホトプロセスの工程回数を低減することが可能となる。

本発明は、横電界方式液晶表示装置だけでなくすべての他のモードの液晶表示装置にも適用できるし、アクティブマトリックス方式型有機 EL 表示装置にも適用できるので適用分野が非常に広い。

本発明のハーフトーンシフト露光装置とハーフトーンシフト露光プロセスは、大型表示装置の製造コストをさげる有力な方法である。ハーフトーンホトマスク（透過光量変調ホトマスク）を用いるハーフトーン露光法を大型基板の製造に適用する場合、ハーフトーンホトマスクの価格が非常に高価になるため大型基板に適用することができなかつたが、本発明を用いると簡単に安価な通常ホトマスクを用いてハーフトーンシフト露光することで大型基板を作れるので大型基板へのハーフトーン露光工程の適用の制限がなくなった。

【0105】手段 6 3 を用いることで低温時に液晶セル内の液晶の体積が縮少してもスペーサーバンプの高さが液晶の体積変化にあわせて変化してくれるのでセル内の気泡の発生を防止できる。特に弾性変形の範囲を大きくすることで、液晶滴下真空合着アライメント工程での大気圧による加圧工程で液晶の滴下量にあわせて液晶セル内部の体積が変化しやすくなるため、残留気泡の問題を完全に解決できる。

【0106】手段 6 4 , 6 5 , 6 6 , 6 7 , 6 8 , 6 9 を用いることで、横電界方式液晶表示装置の液晶分子の駆動に必要なすべての電極の膜厚を 300 ~ 500 オングストローム程度にすることができる。このために特別な平坦化処理が必要なくなり製造工程のコストを低減できる。液晶分子の駆動に必要なすべての電極を最後の工程で同時に形成するため各電極の材質を同一のものにすることができるため、電極の化学ポテンシャルエネルギーを同一にすることができる。これにより液晶分子を完全に交流駆動することができるようになるので、残像の問題が発生しにくくなる。

10

20

30

40

50

液晶分子の駆動に必要なすべての電極を薄膜化（500オングストローム以下）できるので、ラビング処理時のラビング布の毛先きの運動がなめらかになり配向不良が生じなくなり、黒レベル表示時の光もれが完全になくなり、高いコントラストを実現できる。

【0107】

【実施例】

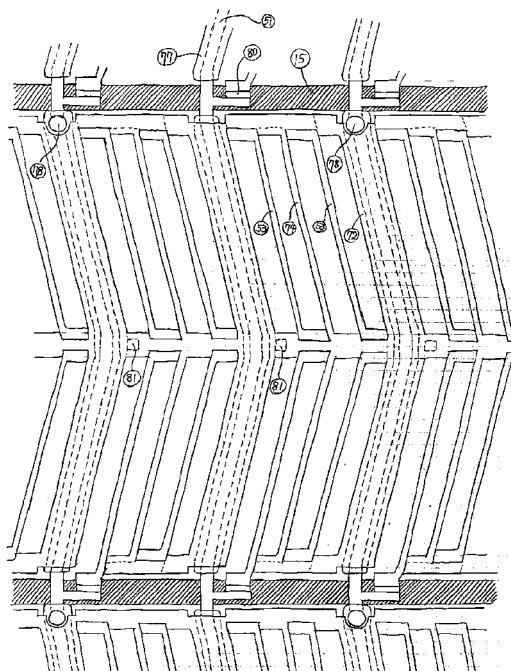

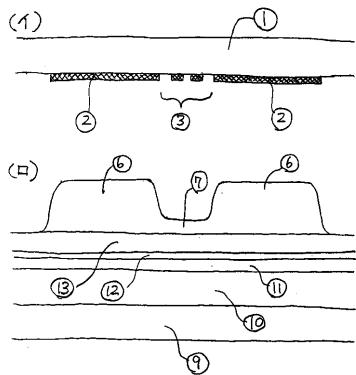

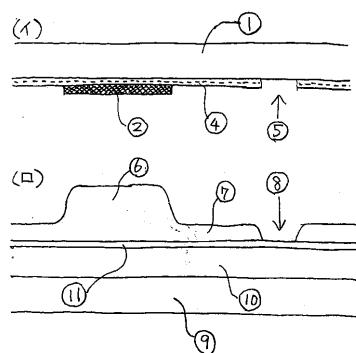

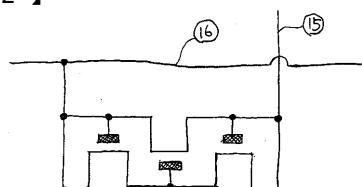

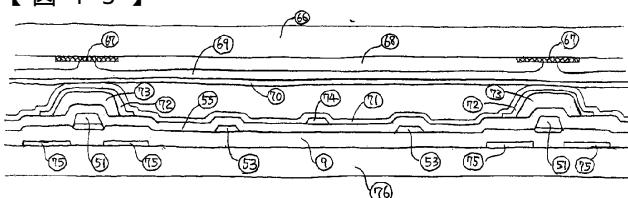

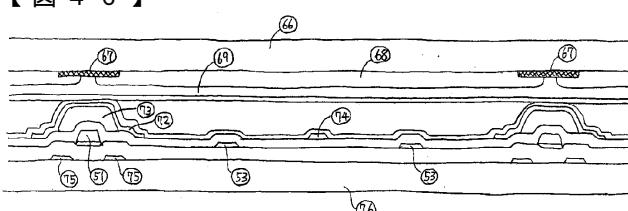

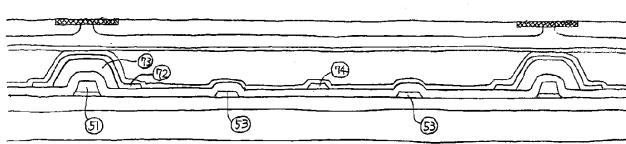

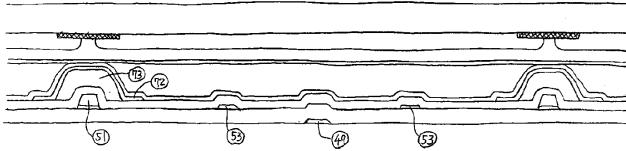

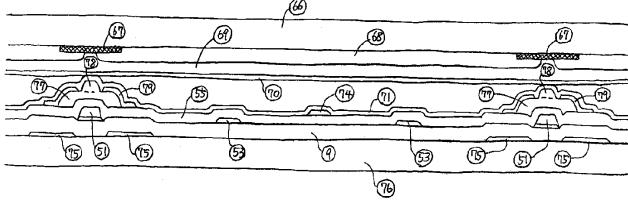

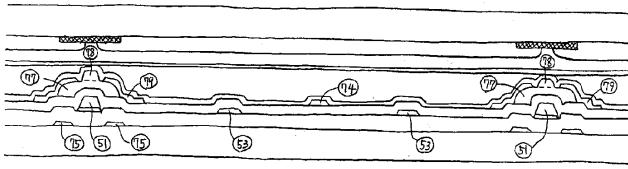

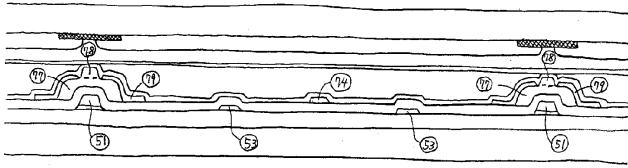

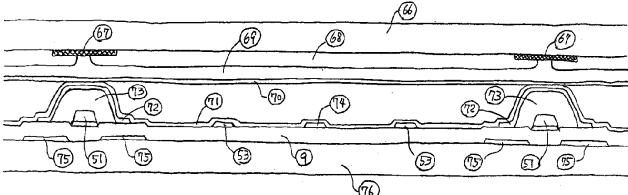

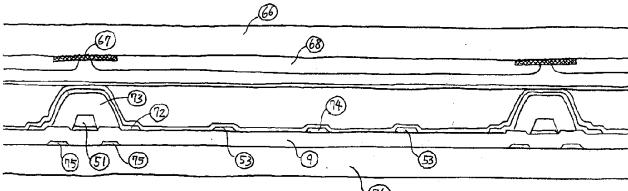

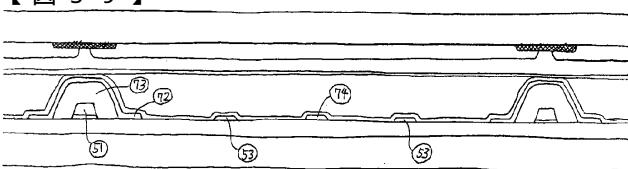

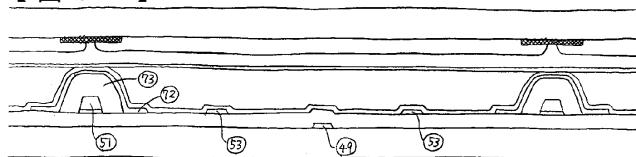

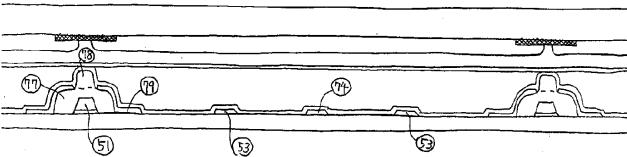

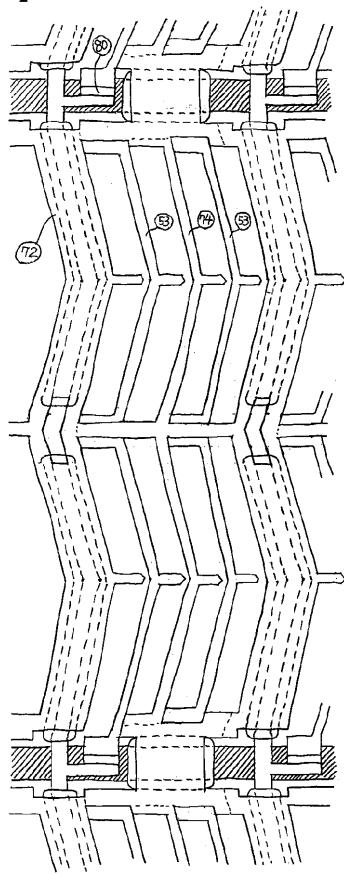

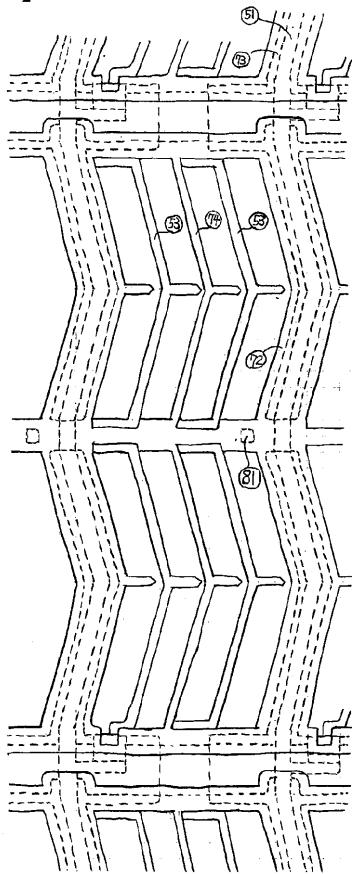

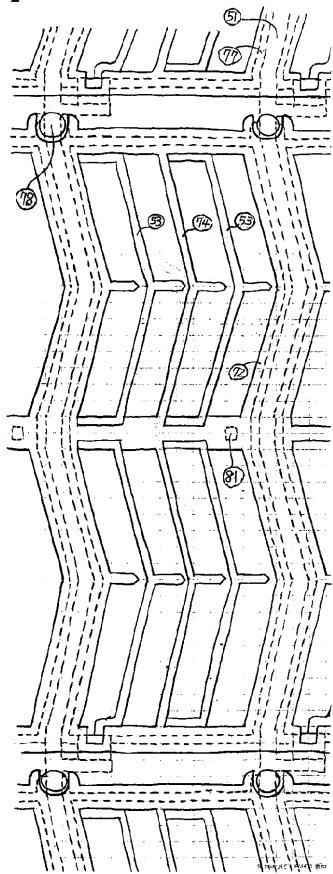

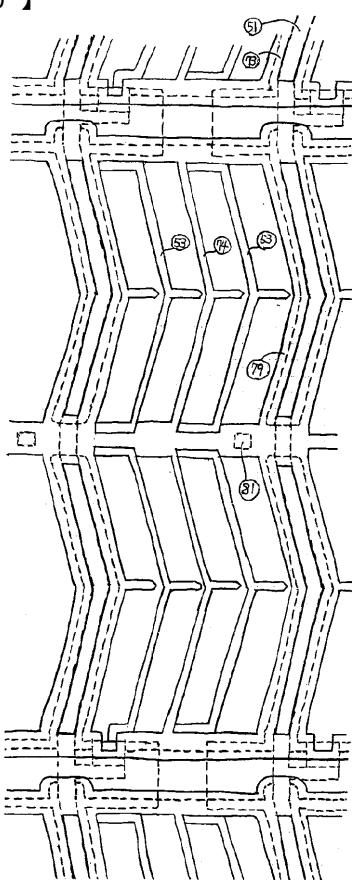

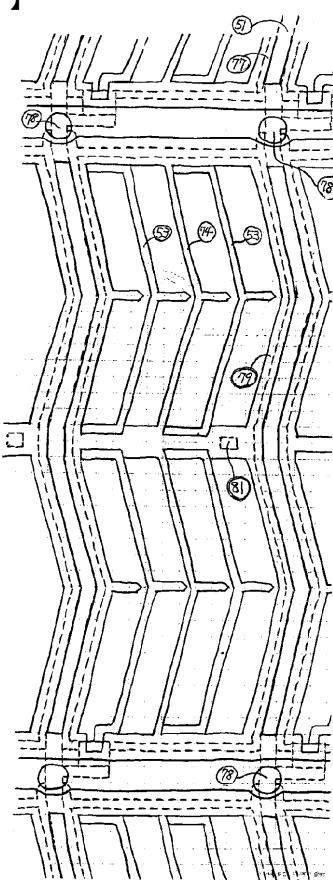

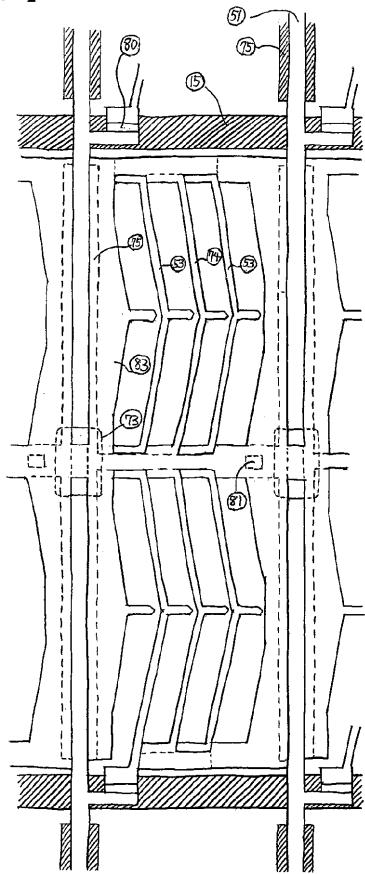

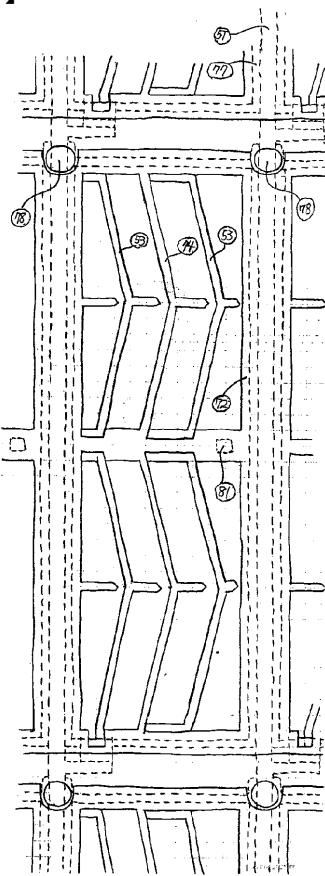

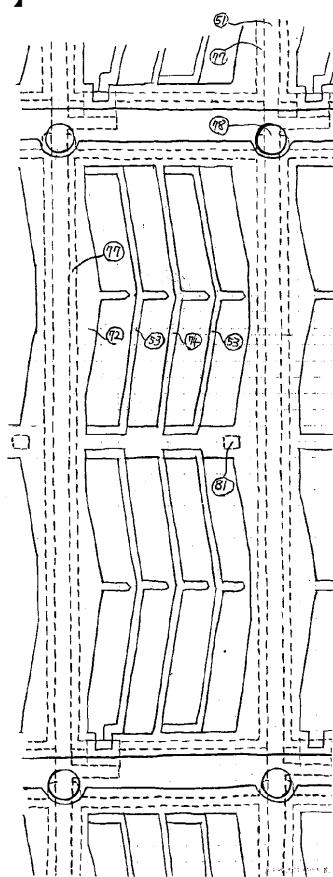

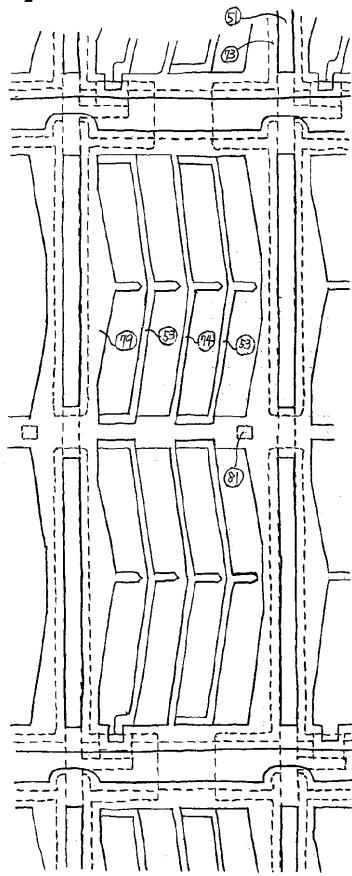

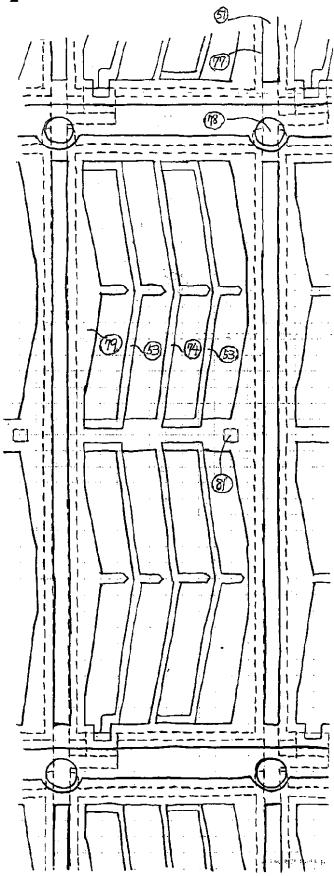

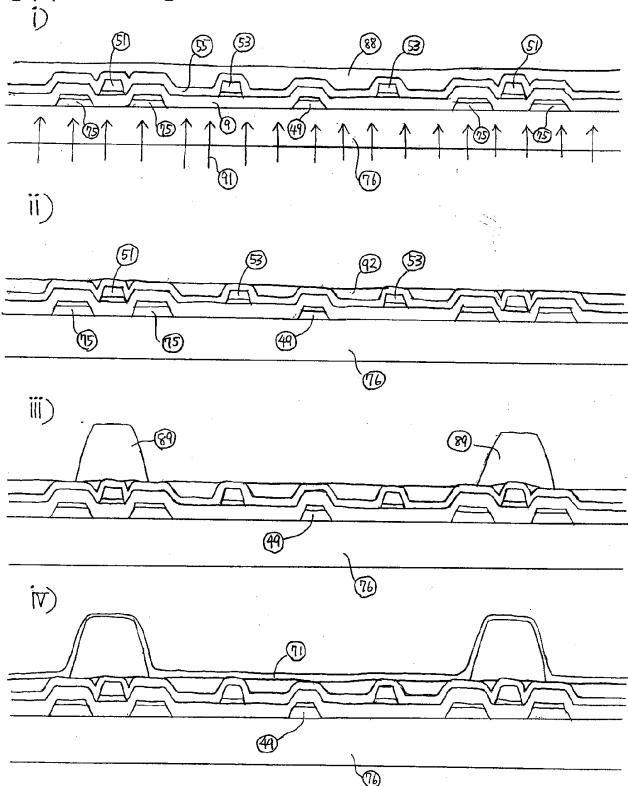

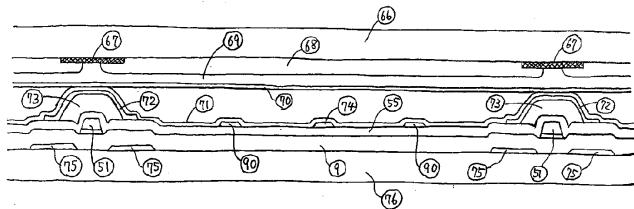

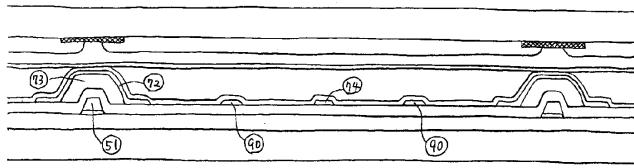

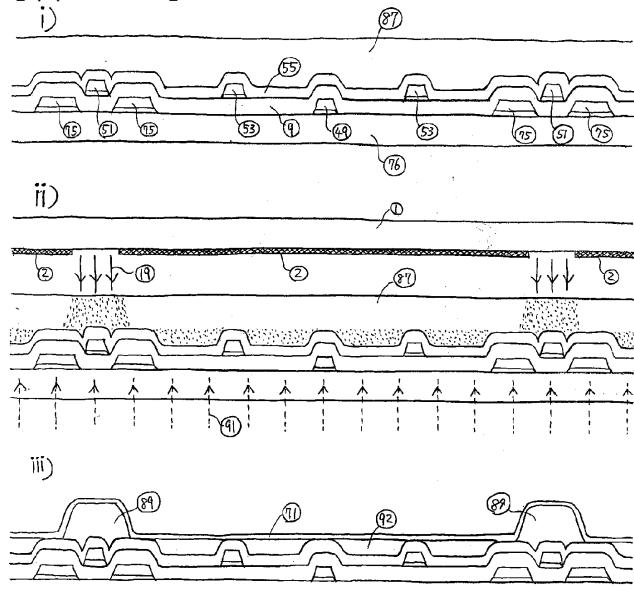

【実施例1】図45、図46、図47と図70、図72、図74、図76、図78図80が本発明の実施例1の横電界方式液晶パネルの断面図と平面図である。映像信号配線の電界をシールドするための下層共通電極75は、走査線と同じ層に同時に形成される。映像信号配線51と液晶駆動電極53は、同じ層に同時に形成されている。映像信号配線の電界をシールドするための上層シールド共通電極72と画素内共通電極74は同じ層に同時に形成される。図46では図45と異なり上層シールド共通電極72の方が下層シールド共通電極よりも電極幅が太くはみ出している構造となっている。図46の構造の方が図45の構造よりも開口率を大きくすることが可能である。

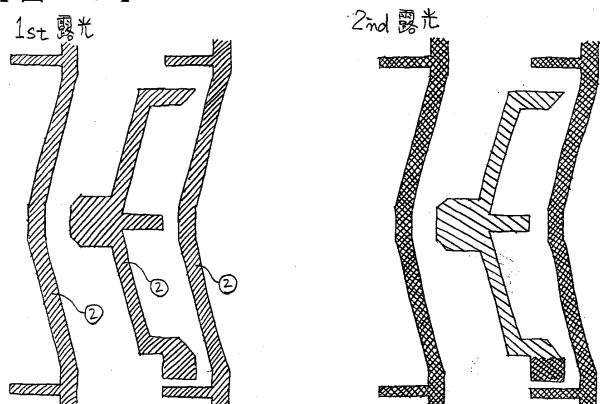

【0108】映像信号配線51と液晶駆動電極53はパッシベーション膜55によって被覆されておりこのパッシベーション膜の上に映像信号配線をおおうようにスペーサーバンプ73が形成されている。図70、図72にあるように上層シールド共通電極72がスペーサーバンプ73を完全に被覆している場合と、図76にあるようにスペーサーバンプ73の側壁の両側に上層側壁シールド共通電極79が形成されている場合とがある。スペーサーバンプの高さが3.0ミクロン以下になった場合と、液晶パネルのサイズが30インチ以上に大型化した場合図76のような上層側壁シールド共通電極79構造の方が映像信号波形の歪が生じにくい。

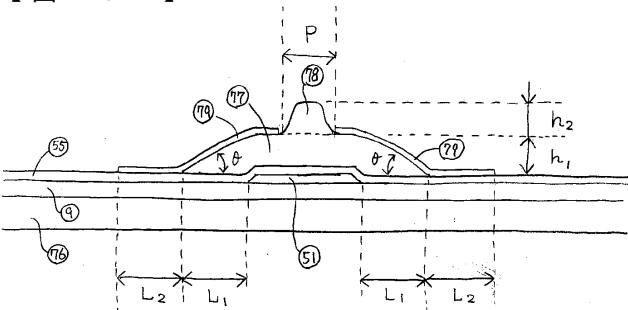

【0109】図45、図46、図47のスペーサーバンプ73は実際の断面形状は図104にあるようにゆるやかなテーパー角度を持っており、スペーサーバンプのはじから映像信号配線51のエッジまでの距離L<sub>1</sub>は最低でも3ミクロンメーター以上必要である。スペーサーバンプ73のテーパー角度は30度以下に設定した方が、ラビング配向処理時にラビング布の毛先きの運動がなめらかになり配向不良の領域が発生しなくなる。スペーサーバンプ73のはじから、上層シールド共通電極72のエッジまでの距離L<sub>2</sub>は0.5ミクロンメーター以上大きくしておく方が良い。L<sub>2</sub>が大きければ大きいほどシールド効果が大きくなります。図47のように下層シールド共通電極がない場合L<sub>2</sub>の大きさは、映像信号配線の幅と同程度の10ミクロンメーター程度あれば十分である。

【0110】本発明のスペーサーバンプ73の断面形状は、半円形または半だ円形、または双曲線形または放物線形のように上に凸状にまるまっていることが特に重要である。この形状であれば液晶滴下真空合着アライメント工程で大気圧の圧力が印加された時にたやすく変形するからである。大気圧の圧力が印加された時にスペーサーバンプ73の高さが0.1~0.5ミクロンメーターの範囲で均一に弾性変形するような材質を用いなければ、残留気泡の問題が多発します。

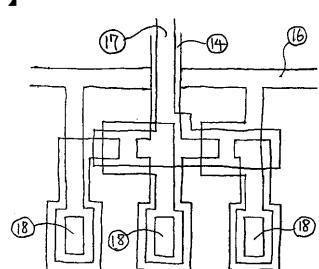

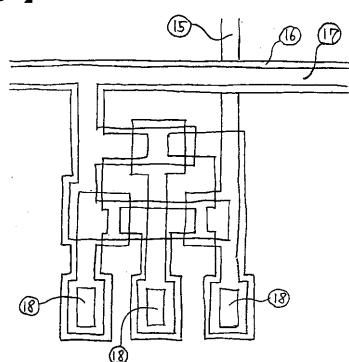

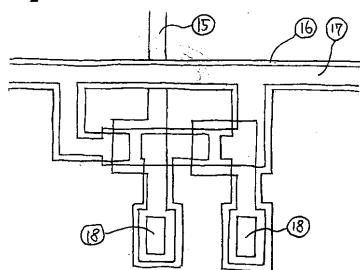

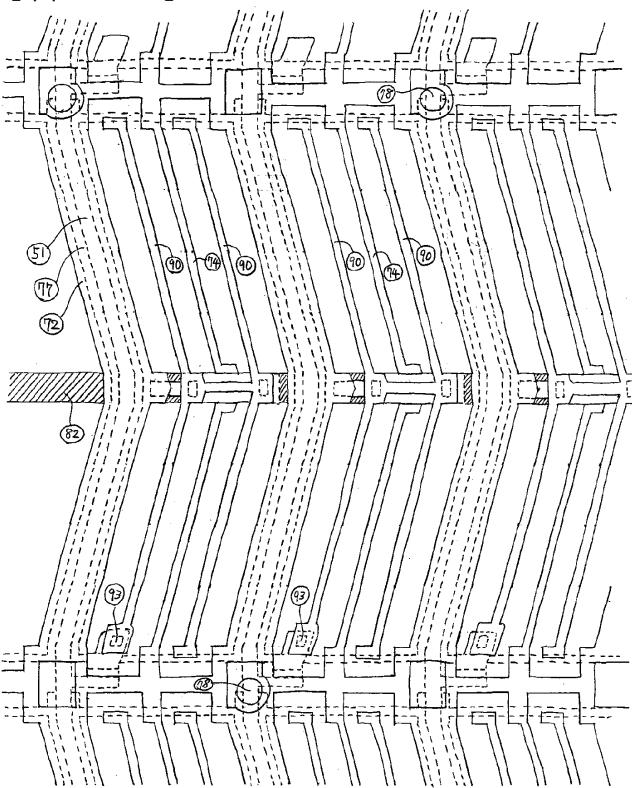

【0111】図70、図74、図76にあるように走査線15と映像信号配線51が交差する領域にスペーサーバンプ73が存在していない構造は特に重要である。スペーサーバンプ73が形成されていないこの領域を通して液晶が拡散していくからである。図78、図80では、画素の中央付近でスペーサーバンプ73が形成されていない領域がもうけられている。この構造では滴下された液晶は拡散していくが、上層シールド共通電極72と映像信号配線51の容量が大きくなるので大型液晶パネルには適さない。

【0112】図74にあるように走査線15の上にもスペーサーバンプを形成し、上層シールド共通電極72を左右の画素と上下の画素とで互いに連結しあう方式が大型液晶表示装置には適している。この方式ならばどこか断線しても2次元の網状に連結されているため致命的な線欠陥にはならないからである。

【0113】スペーサーバンプ73の比誘電率は小さければ小さいほど良いが実用的には3.3以下であれば十分に使用できる。スペーサーバンプ73の原料となるモノ

10

20

30

40

50

マーまたはオリゴマーがベンゾシクロブテン構造を1個以上有するものまたは、その誘導体か、またはフルオレン骨格を1個以上有するもの、またはその誘導体であれば比誘電3.3以下の誘電体材料を合成することができる。

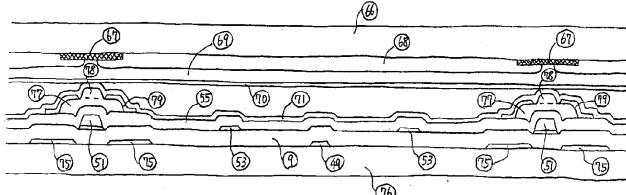

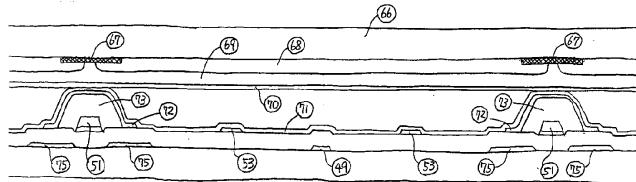

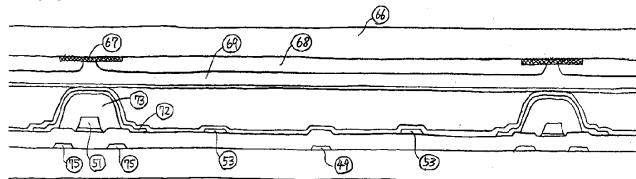

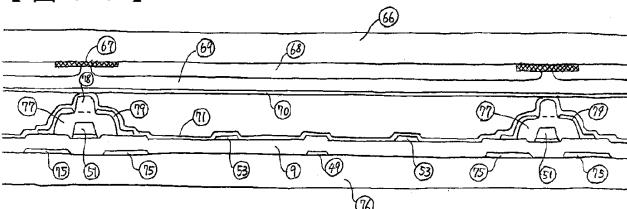

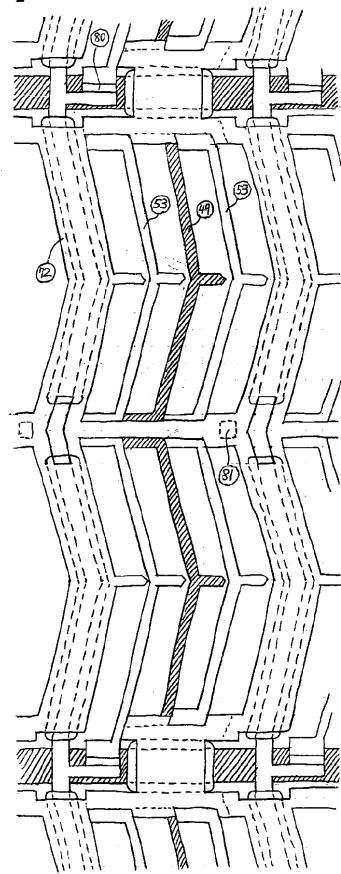

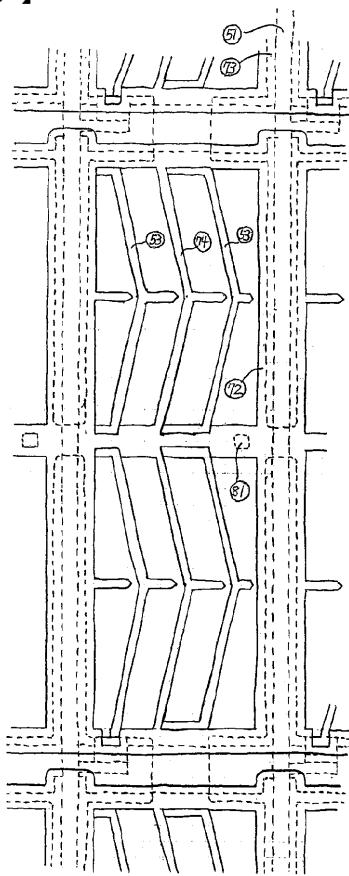

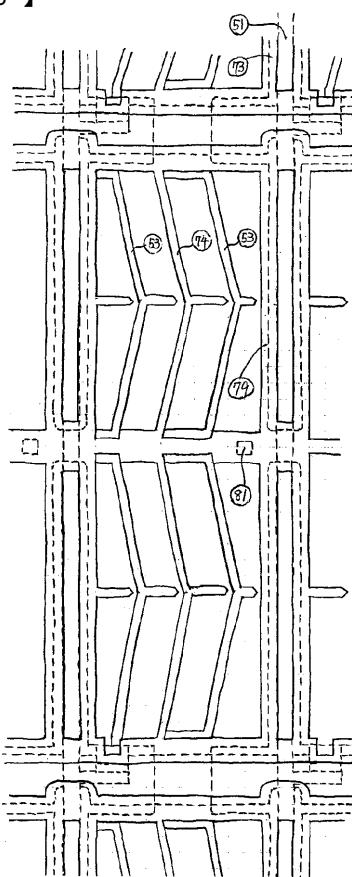

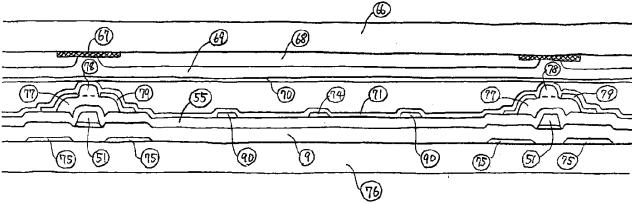

【0114】〔実施例2〕図48、図50と図71、図75が、本発明の実施例2の横電界方式液晶パネルの断面図と平面図である。映像信号配線の電界をシールドするための下層共通電極75と液晶分子を駆動するための画素内共通電極49は、走査線と同じ層に同時に形成される。映像信号配線51と液晶駆動電極53は、同じ層に同時に形成される。図49では図48と異なり上層シールド共通電極72の方が、下層シールド共通電極75よりも電極幅が太く、はみ出している構造となっている。図49の構造の方が図48の構造よりも開口率を大きくすることが可能である。本実施例2のように画素内共通電極49が、パッシベーション膜55とゲート絶縁膜9の下層に形成されている場合、液晶を駆動するための電圧が高くなる傾向にある。

【0115】本発明の構造では図71、図75にあるように液晶駆動電極53をゲート絶縁膜とパッシベーション膜をかいして上下から画素内共通電極49に連結されている下層共通電極82と上層シールド共通電極とではさみこむことができ小さな面積で大きな保持容量を形成することができ、開口率を大きくすることが可能である。

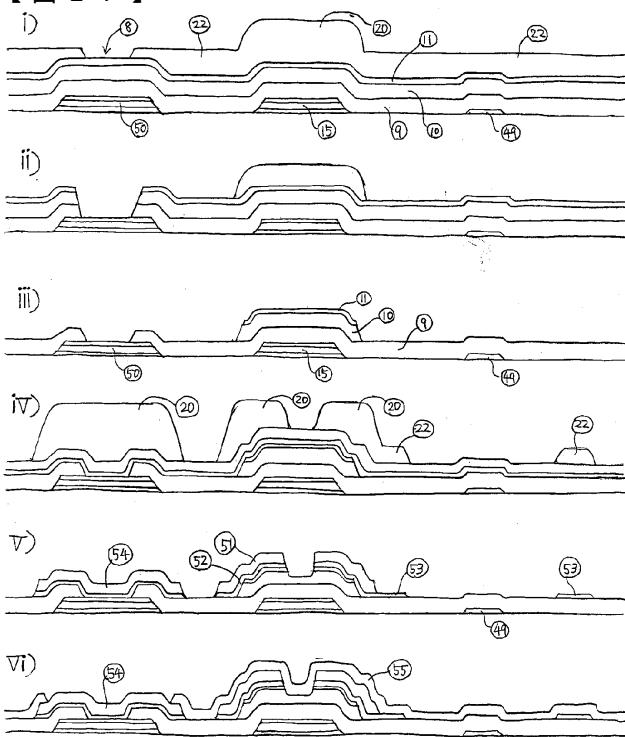

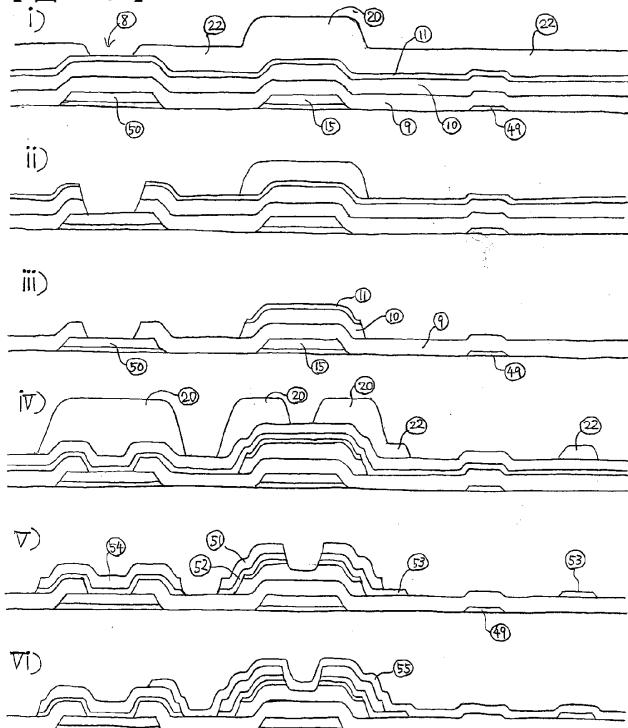

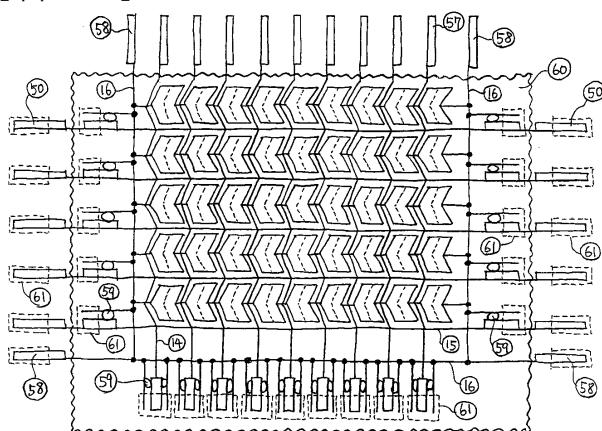

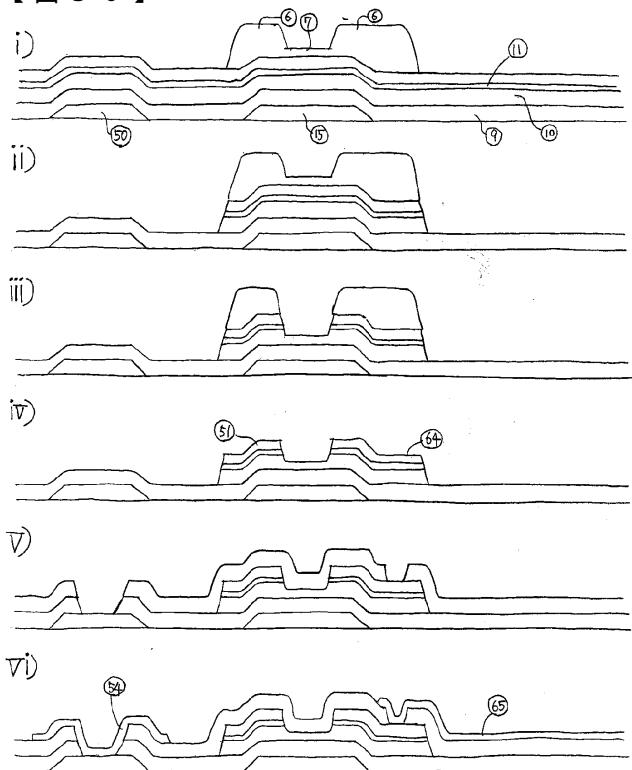

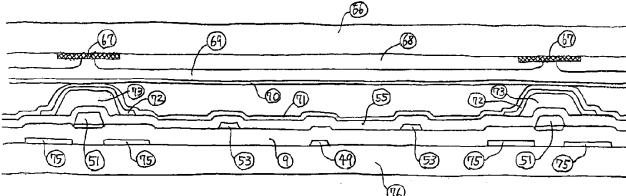

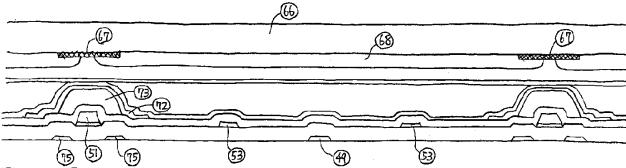

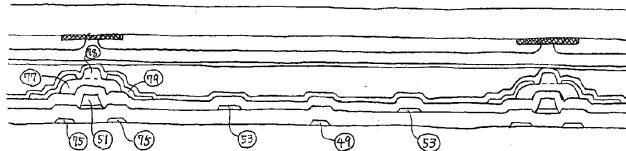

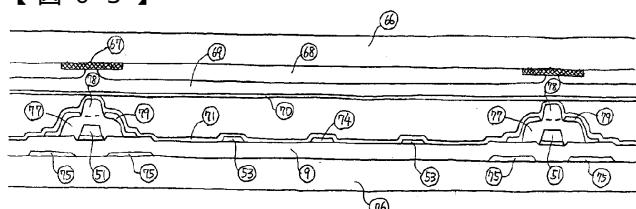

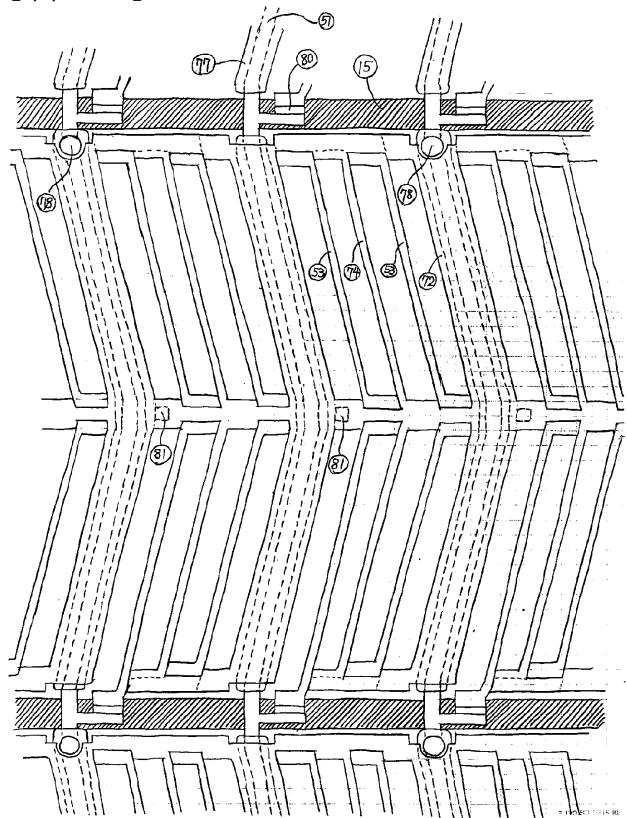

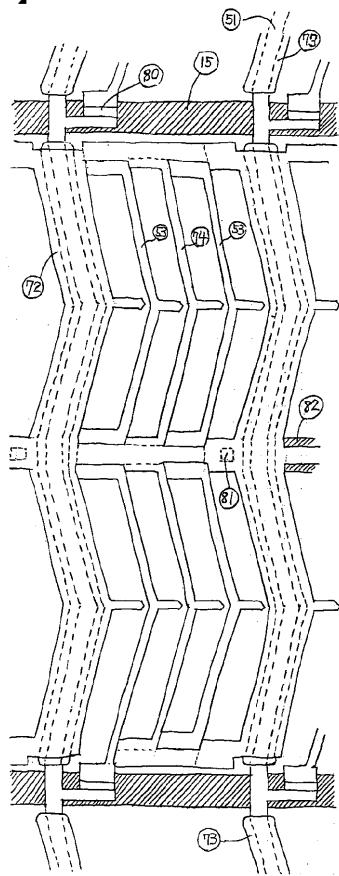

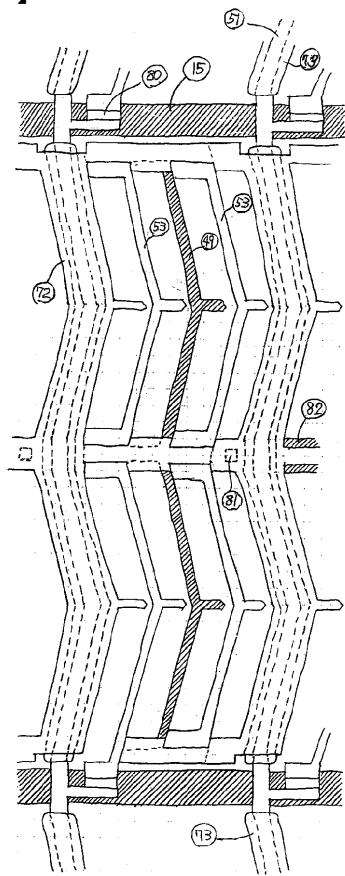

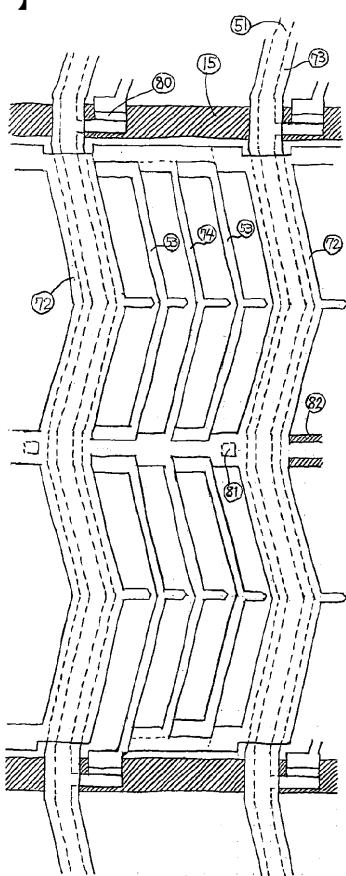

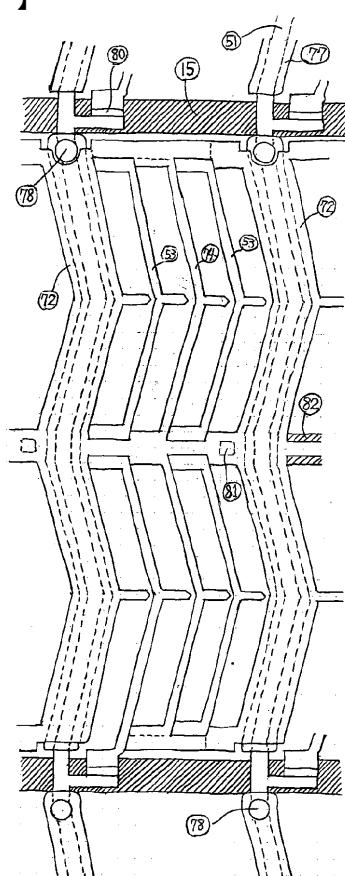

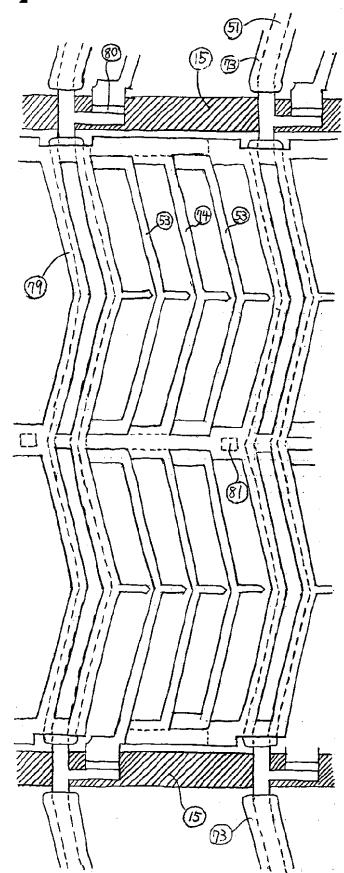

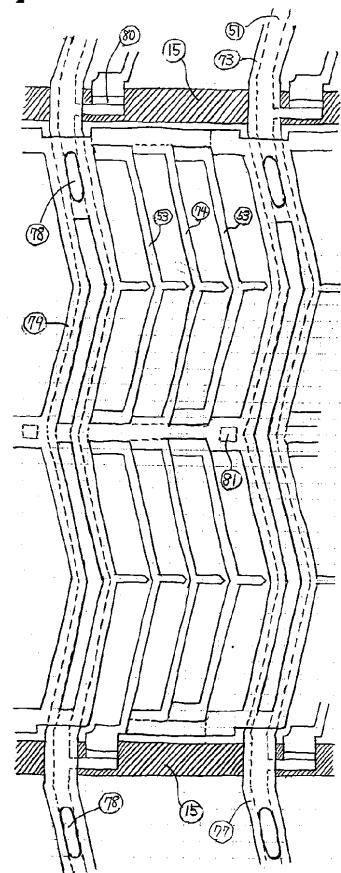

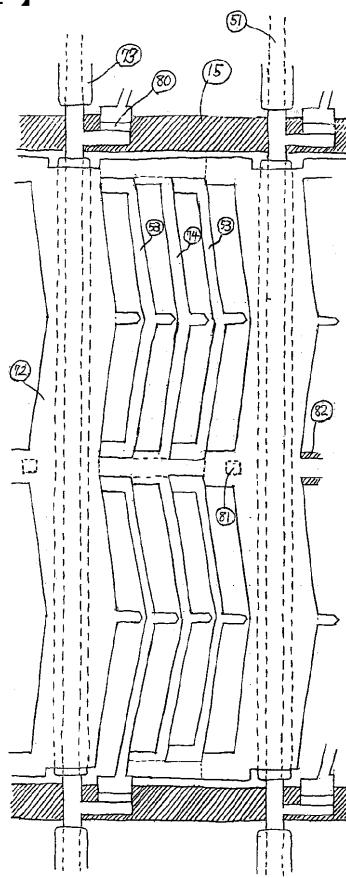

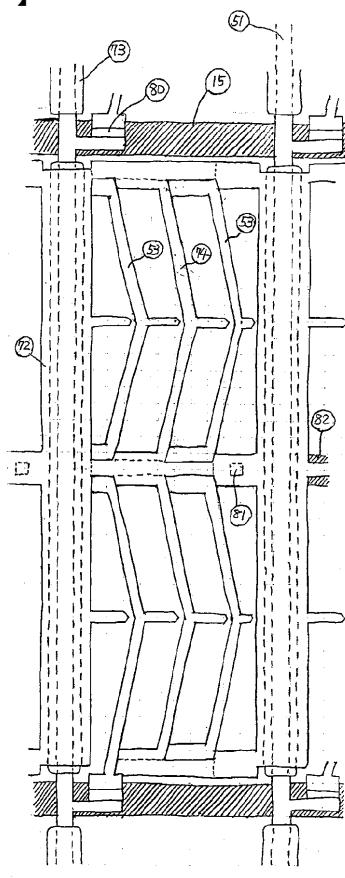

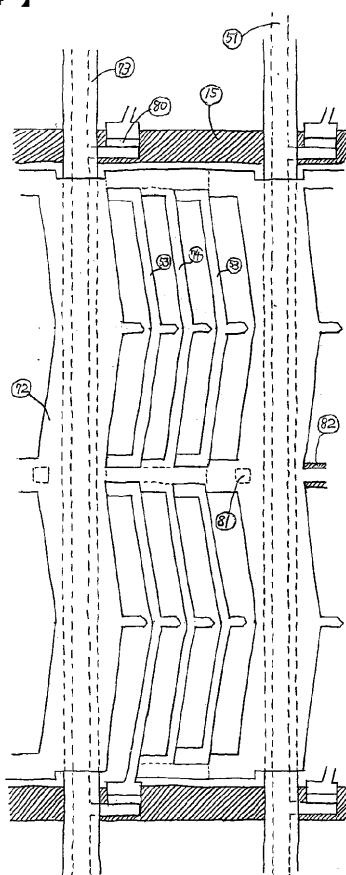

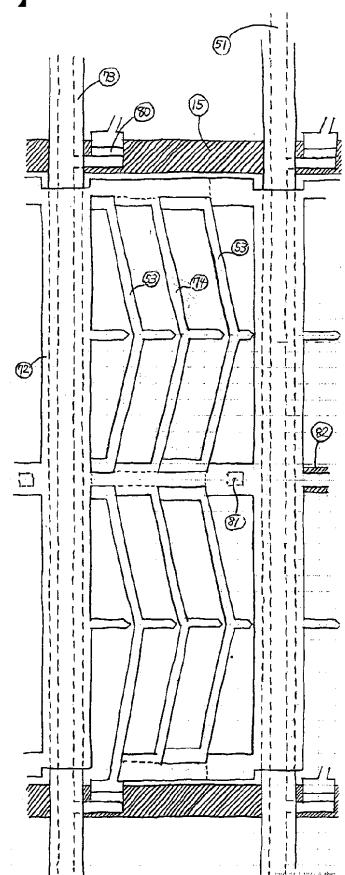

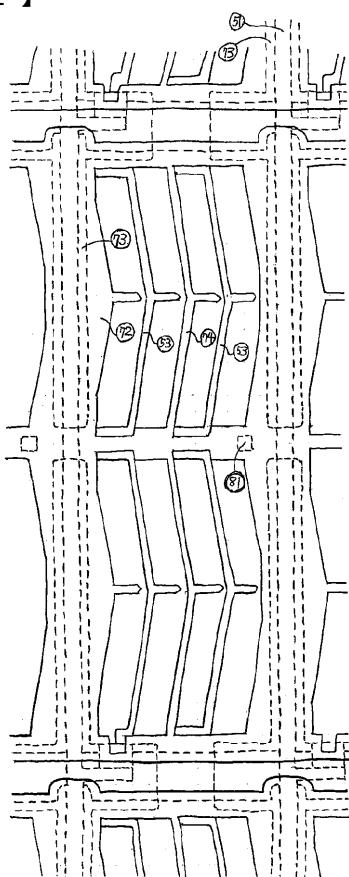

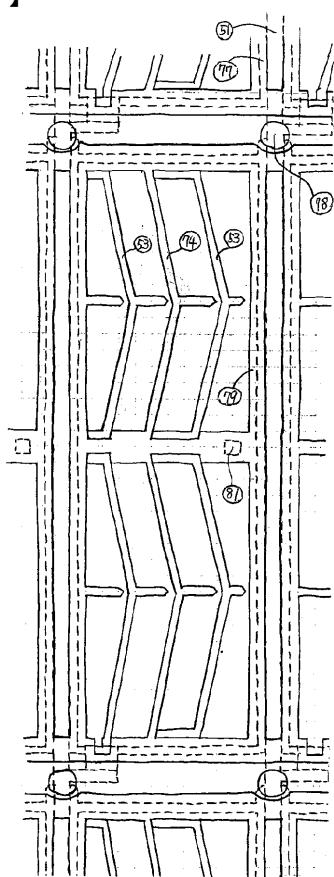

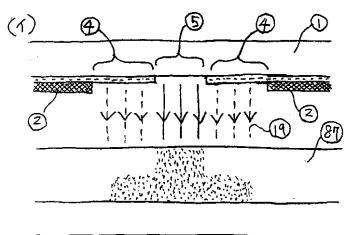

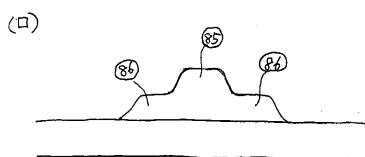

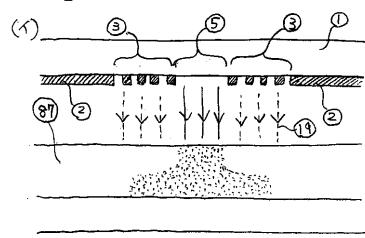

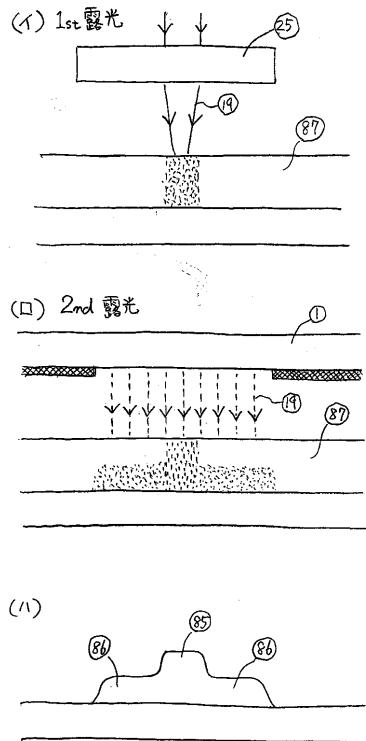

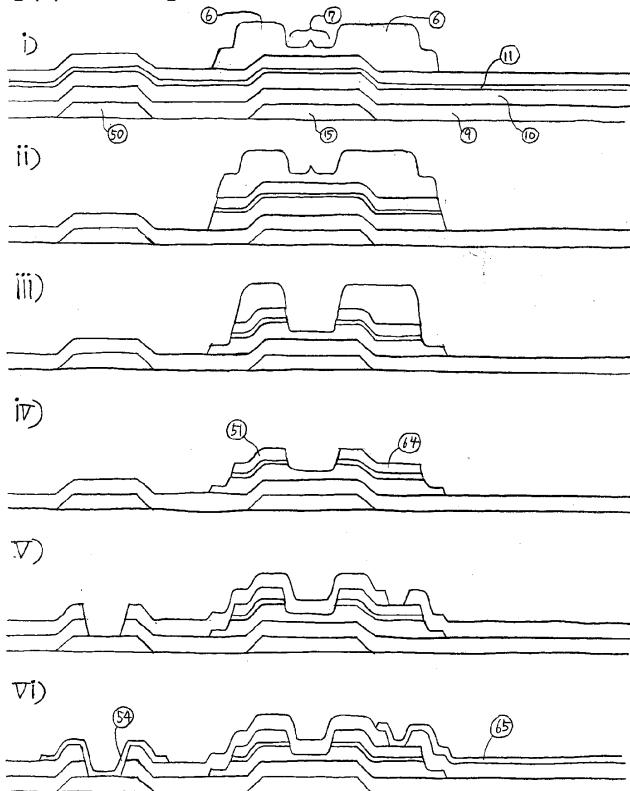

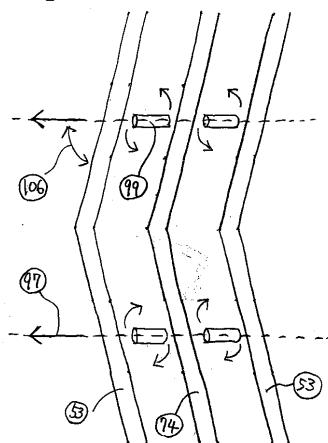

【0116】〔実施例3〕図51、図52、図53と図69、図73、図77、図79、図81が本発明の実施例3の横電界方式液晶パネルの断面図と平面図である。実施例1のスペーサーバンプ73が映像信号配線を被覆している誘電体バンプ77と液晶セルギャップを決定するスペーサー78の2つの構成体に分離されている点が異なるだけで他は実施例1とまったく同じである。

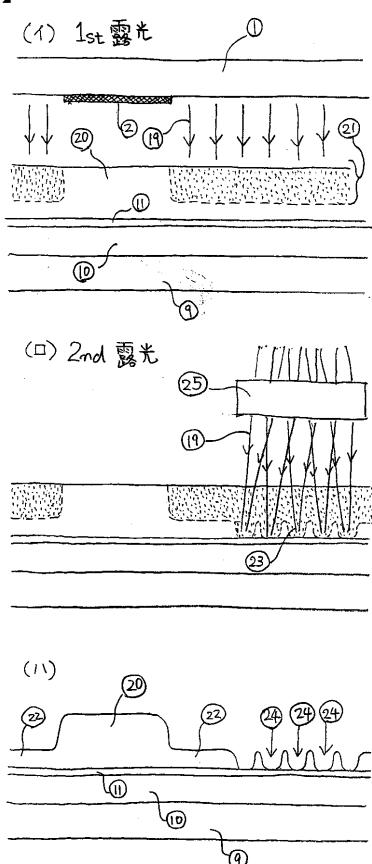

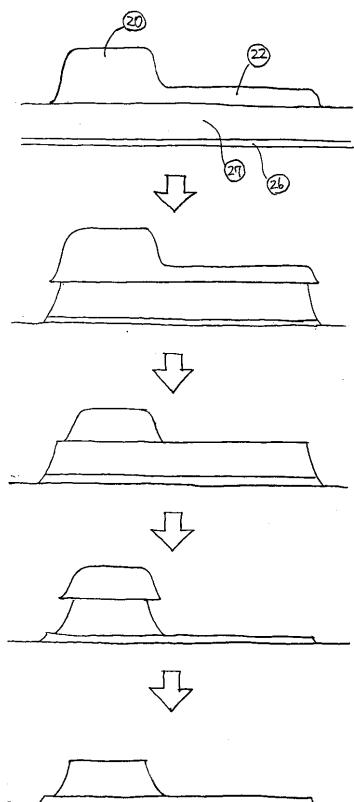

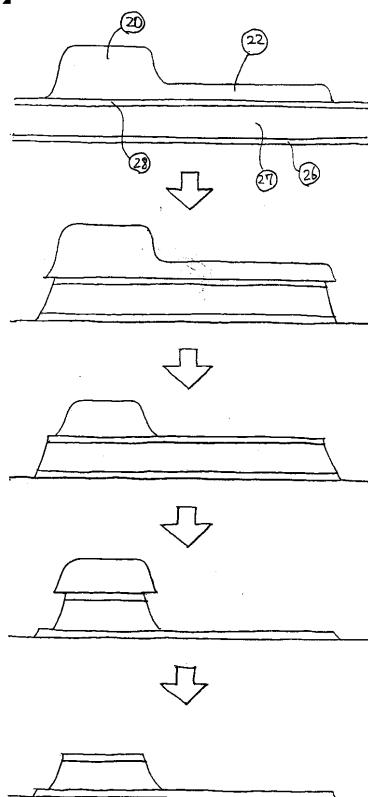

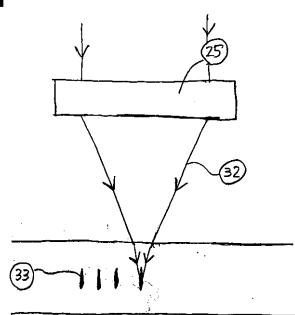

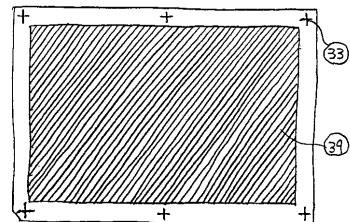

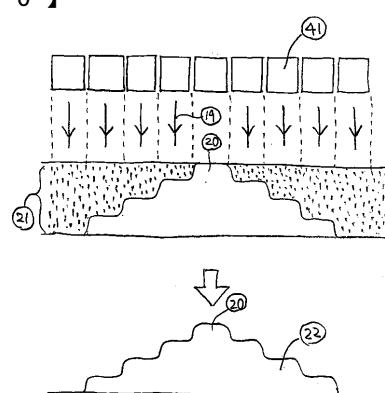

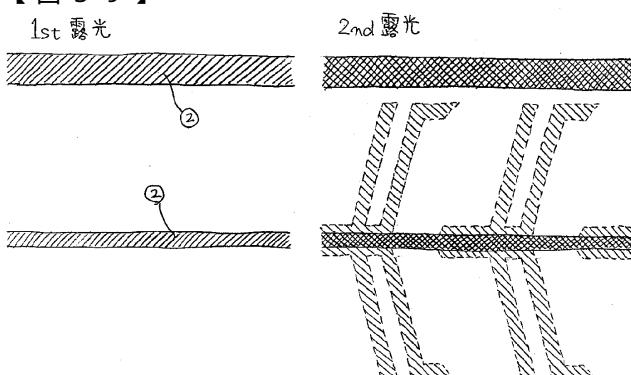

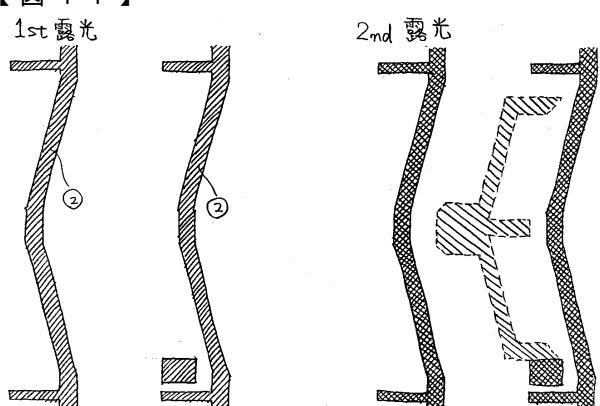

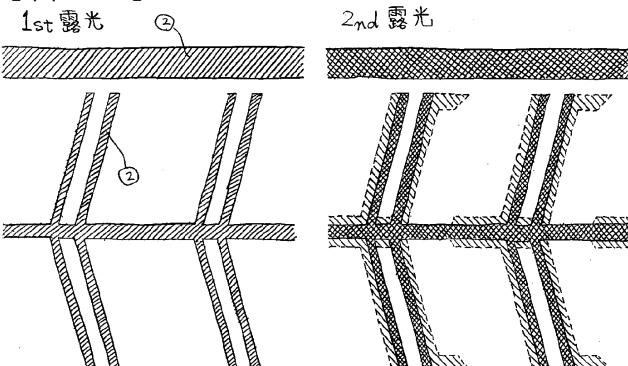

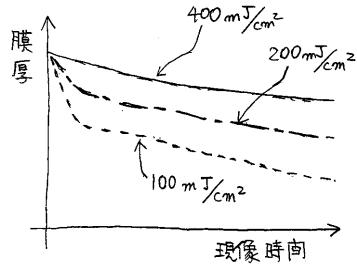

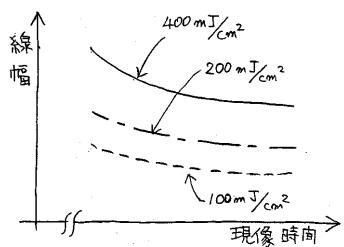

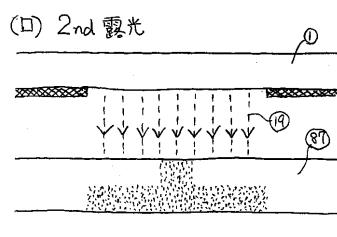

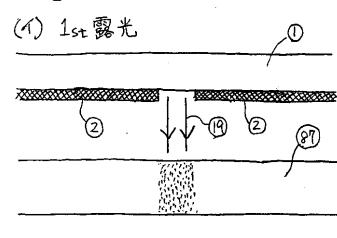

【0117】映像信号配線を被覆している誘電体バンプ77と液晶セルギャップを決定するスペーサー78を1回のホトリソ工程で同時に形成することができ本発明の特徴である。図1、図2にあるような透過光量変調ホトマスクを用いてポジ型レジストで図104の断面形状を作ることができる。図5、図6にあるような通常ホトマスクを用いてハーフ露光と追加露光の2ステップ露光法によりポジ型レジストで図104の断面形状作ることも可能である。しかしポジ型レジストでは、弾性体の特性を持たせることが非常に難しい。

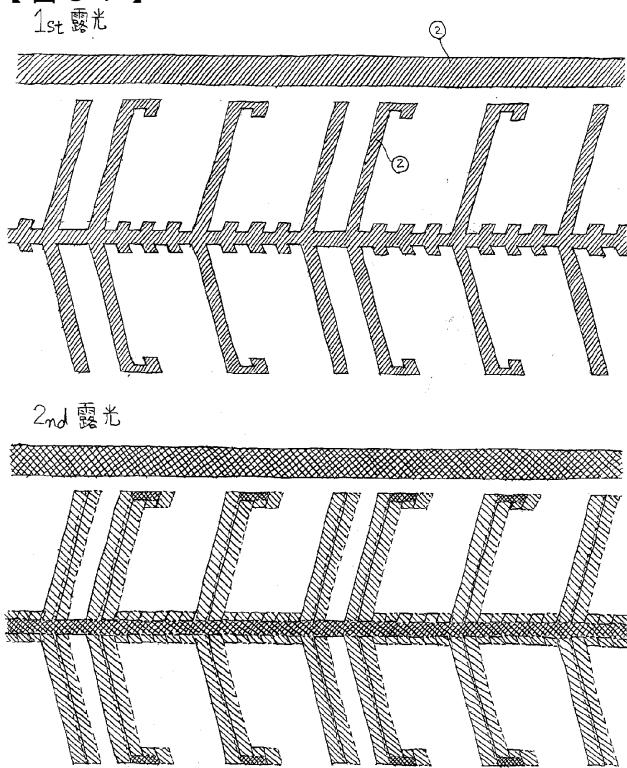

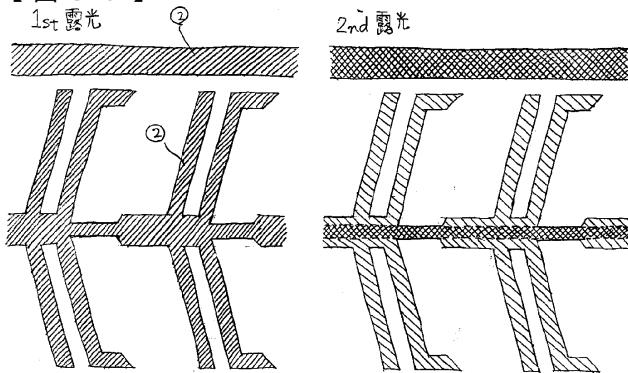

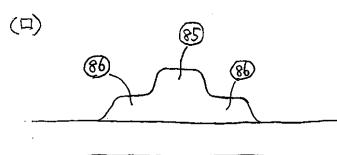

【0118】そこで弾性体の特性を持っているネガレジストを用いて図104の断面形状を1回のホトリソ工程で形成できるようにしたことが本発明の特徴である。ネガレジストで酸素障害を受けやすいタイプは、露光光量が少ない時、大気中に接している領域が大気中の酸素により光重合が阻害され反応せず、ガラス基板に接する領域が少量の紫外光で光重合が進む場合がある。図98、図99にこのタイプのネガレジストの露光光量と現像時間による膜厚と線幅の特性がしめされている。このタイプのネガレジストを用いて、図100や図101のように、透過光量変調ホトマスクを用いて露光することで図104の形状を得ることができる。別 の方法として図102や図103にあるように、部分的完全露光とハーフ露光の2ステップ露光法を用いることも可能である。この場合高価な透過光量変調ホトマスクを用いる必要はなく、安価な通常ホトマスクで図104の形状を形成することが可能である。

【0119】図104にあるように映像信号配線51を被覆しているバンプ77の厚み $h_1$ は1.5~3.5ミクロンメーターの範囲にありバンプ77の上につき出ているスペーサーの高さ $h_2$ は0.2~2.0ミクロンメーターの範囲にある。スペーサー78の形成密度は $1\text{ mm}^2$ あたり1個から75個程度であり、スペーサーの形成面積は $1\text{ mm}^2$ あたり200平方ミクロンメーターから2000平方ミクロンメーターの範囲にすると良い。スペーサーのつき出ている部分には上層シールド共通電極が存在しないことが重要である。バンプ77の上に形成されたスペーサー78は液晶滴下真空合着アライメント工程で大気圧の圧力が印加された時に0.2~0.5ミクロンメーター程度スペーサー78の高さ $h_2$ が圧縮弾性変形しなければならない。もしスペーサー78が上層シールド共通電極79によって被覆されるとスペーサー78が大気圧により圧縮弾性変形した時に上層シールド共通電極がはがれてしまう場合が発生

10

20

30

40

50

します。

【0120】上層シールド共通電極 79 は、酸化インジウム  $In_2O_3$  または酸化亜鉛  $ZnO$  を主体とする金属酸化物透明導電体または窒化チタン  $TiN_x$  または酸窒化チタン  $TiO_xN_y$  またはチタンシリサイド  $TiSi_x$  または窒化チタンシリサイド  $TiSi_xN_y$  などのチタン金属化合物からなる可視光を 20 % 以上透過する導電体が用いられる。

【0121】図 104 にあるように映像信号配線被覆バンプ 77 は、実施例 1 のスペーサーバンプ 73 と同様にエッジ部のテーパー角度 を可能なかぎり小さくすることが重要である。通常はこのテーパー角度 は 30 度以下に設定しなければならない。テーパー角を小さくすることでラビング配向処理時に、ラビング布の毛先きの運動がなめらかになり配向不良が生じなくなる。テーパー角が 45 度以上に大きくなるとテーパー部分の領域で毛先きが接触しなくなる領域が発生し配向不良となり黒表示の時この配向不良の領域から光がもれてしまいコントラストをいちじるしく低下させてしまう。

特開 2002-258321 や特開 2002-323706 に記載されている構造ではラビング布の毛先きのなめらかな運動ができないため毛先きが接触しない領域が発生して、配向不良の発生を防止できない。

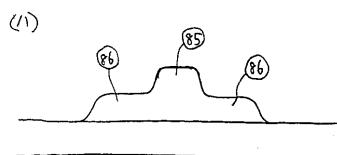

【0122】図 77 にあるようにスペーサーの形状は円形でなく、だ円形でもよい。図 79, 図 81 ではスペーサーの形状は円形になっている。本発明のように映像信号配線を被覆しているバンプ 77 の上にスペーサー 78 が形成されている場合、液晶滴下真空合着アライメント工程で液晶の拡散をさまたげるものがないので走査線 15 と映像信号配線 51 の交差部分に連続してバンプ 77 を形成することができる。図 79, 図 81 のように走査線の上にも被覆バンプ 77 を形成して網の目のようにバンプを基板上にはりめぐらせることが可能である。図 79, 図 81 のように上層シールド共通電極 72 が映像信号配線 51 や走査線とバンプ 77 をかいして完全に被覆またはオーバーラップしている場合には、カラーフィルター基板側の遮光膜は必要なくなり開口率を最大に拡大することが可能となる。

【0123】図 81 にあるように、映像信号配線 51 を被覆しているバンプ 77 と走査線を被覆しているバンプの側壁の両側に上層シールド共通電極 79 を形成する構造が、映像信号波形の歪や走査信号波形の歪を最少におさえることができ、超大型液晶表示には最も適している。

【0124】〔実施例 4〕図 54, 図 55, 図 56 は、本発明の実施例 4 の横電界方式液晶パネルの断面図である。実施例 2 のスペーサーバンプ 73 が、映像信号配線を被覆している誘電体バンプ 77 と液晶セルギャップを決定するスペーサー 78 の 2 つの構成体に分離されている点が異なるだけで他は実施例 2 とまったく同じである。

【0125】実施例 2 では映像信号配線を被覆している誘電体バンプ 73 は、セルギャップを決定するスペーサーの役割も同時にはたしているが、実施例 4 の場合には実施例 3 の場合と同様に誘電体バンプ 77 と液晶セルギャップを決定するスペーサー 78 の機能は完全に分離されている。実施例 3, 実施例 4 の場合、誘電体バンプ 77 は、走査線と映像信号配線 51 の両方を完全に被覆することができるのでバンプ 77 の両側の側壁に上層シールド共通電極 79 を形成することで走査線や映像信号配線 51 の信号波形歪を最少におさえかつ開口率を最大に拡大できる。

【0126】図 54, 図 55, 図 56 のスペーサー 78 は上層シールド共通電極によって被覆されておらず、直接誘電体がもりあがっている構造になっている。液晶滴下真空合着アライメント工程で大気圧による圧力でスペーサー 78 の高さが圧縮変形するとき共通電極の膜はがれが生じないようにするためである。

【0127】実施例 1 から実施例 4 までは映像信号配線 51 と液晶駆動電極 53 はゲート絶縁膜 9 とパッシバーション膜 55 によって完全に上下から被覆されておりシールド共通電極と画素内共通電極とは層が異なっており、パターン不良が発生しても互いにショートする確率はほとんどなく画素欠陥の不良発生率もほぼゼロに近い。

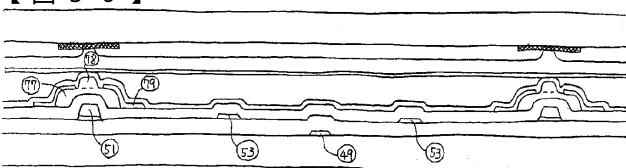

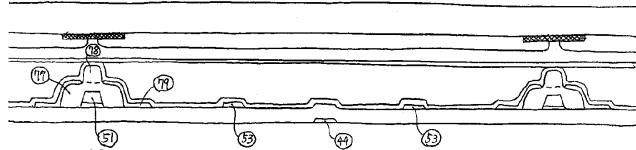

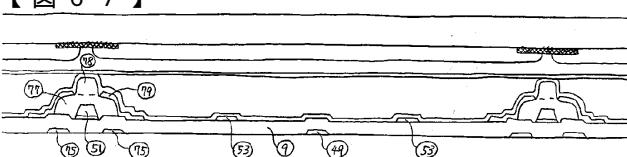

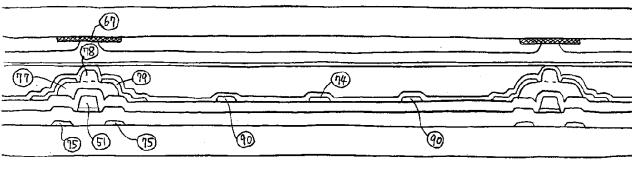

【0128】〔実施例 5〕図 57, 図 58, 図 59 は、本発明の実施例 5 の横電界方式液

10

20

30

40

50

晶パネルの断面図である。映像信号配線 51 と液晶駆動電極 53 はパッシベーション膜 55 によって被覆されていない。映像信号配線 51 のみが誘電体スペーサーバンプ 73 によって被覆されている。本発明の構造では、映像信号配線 51 と液晶駆動電極 53 は、同時に形成しても良いし、薄膜トランジスタのドレイン電極を映像信号配線 51 と同時に形成しておき、スペーサーバンプ 73 を形成した後上層シールド電極 72 と画素内共通電極 74 を形成する時に液晶駆動電極 53 を同時に同層に形成しても良い。どちらの製造方法も可能である。本発明の構造ではコンタクトホールをあけて薄膜トランジスタのドレイン電極と液晶駆動電極を接続する必要がない。

【0129】〔実施例6〕図60, 図61, 図62は、本発明の実施例6の横電界方式液晶パネルの断面図である。実施例5と同様に映像信号配線 51 と液晶駆動電極 53 は、パッシベーション膜によって被覆されていない。

10

映像信号配線 51 のみが誘電体スペーサーバンプ 73 によって被覆されている。実施例5と異なる点は画素内共通電極 49 が、下層シールド共通電極 75 と走査線と同じ層に同時に形成されている点である。そのほかは実施例5と同じである。

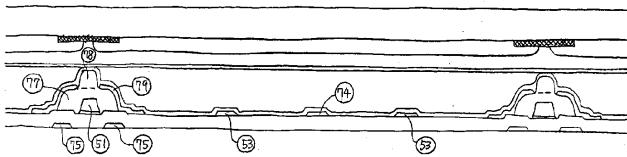

【0130】〔実施例7〕図63, 図64, 図65は本発明の実施例7の横電界方式液晶パネルの断面図である。実施例5のスペーサーバンプ 73 が映像信号配線を被覆している誘電体バンプ 77 と液晶セルギャップを決定するスペーサー 78 の2つの構成体に分離されている点が実施例5と異なるだけで他は、まったく同じである。

【0131】〔実施例8〕図66, 図67, 図68は、本発明の実施例8の横電界方式液晶パネルの断面図である。実施例6のスペーサーバンプ 73 が映像信号配線を被覆している誘電体バンプ 77 と液晶セルギャップを決定するスペーサー 78 の2つの構成体に分離されている点が実施例6と異なるだけで他はまったく同じである。

20

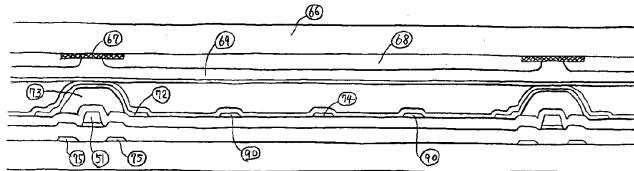

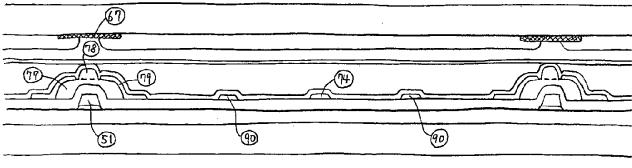

【0132】〔実施例9〕図108, 図109, 図110は本発明の実施例9の横電界方式液晶パネルの断面図である。映像信号配線 51 と液晶駆動電極 90 とはパッシベーション膜 55 をかいして異なる層に形成されている。上層シールド共通電極 72 と画素内共通電極 74 と液晶駆動電極 90 は同じ層に同時に形成される。液晶駆動電極 90 はコンタクトホールを通して薄膜トランジスタのドレイン電極に接続されている。

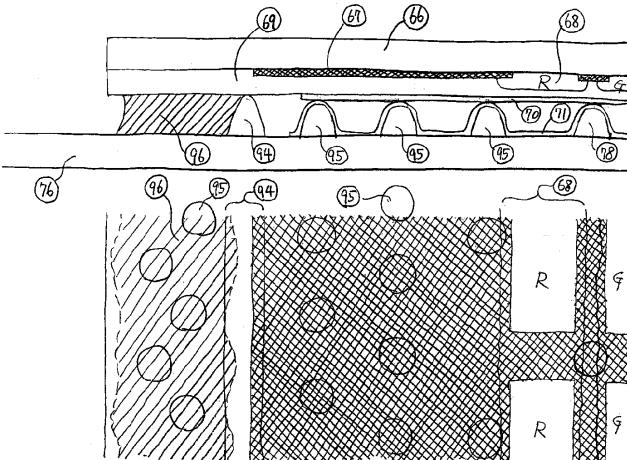

【0133】本発明の実施例9が一番表示画素領域の凹凸のレベルを平坦化することが可能である。上層シールド共通電極 72 と画素内共通電極 74 と液晶駆動電極 90 を300~500オングストロームの透明電極材料(ITOまたはIZO)を用いて同時に形成することで実質的な開口率を大幅に向上することができる。

30

横電界方式モードでは電極を3~5ミクロン程度まで細くすると電極の上の液晶分子の大部分がフリンジフィールドの効果で回転運動することができるようになり電極の領域からも光が透過することができるようになる。このフリンジフィールド効果により図109の構造が最も開口率をあげることができ、明るいコントラストの高い画像を表示できる。

【0134】図109, 図110の構造では上層シールド共通電極 72 のエッジ領域にもフリンジフィールド効果が大きくはたらき、上層シールド共通電極 72 のエッジ領域からも光を透過させることができ可能となり、開口率を向上することができる。カラーフィルター基板側の遮光膜(ブラックマスク) 67 は必ずしも必要ではない。遮光膜(ブラックマスク) 67 の幅は、誘電体スペーサーバンプ 73 の幅と同じかすこし小さい方が良い。スペーサーバンプ 73 のエッジのテーパー角は30度以下に小さく設定することがラビング配向処理時の配向不良をおさえるために重要である。

40

【0135】液晶滴下真空合着アライメント工程で液晶がすみやかに広がるように走査線と映像信号配線の交差部の領域には、スペーサーバンプは形成しない方が良い。大気圧の圧力によりスペーサーバンプ 73 が0.1~0.5ミクロンメーター程度弹性圧縮変形するような材料を選定しないと残留気泡の問題が発生する。

【0136】〔実施例10〕図111, 図112, 図113と図115が本発明の実施例10の横電界方式液晶パネルの断面図と平面図である。実施例9のスペーサーバンプ 7

50

3 が映像信号配線を被覆している誘電体バンプ 77 と液晶セルギャップを決定するスペーサー 78 の2つの構成体に分離されている点が実施例9と異なるだけで他はまったく同じである。

【0137】図115にあるように上層シールド共通電極 72 と画素内共通電極 74 と液晶駆動電極 90 は同じ層に同時に形成されている。液晶駆動電極 90 は、コンタクトホール 93 を通して薄膜トランジスタのドレイン電極に接続されている。スペーサー 78 の部分には上層シールド共通電極は存在していない。上層シールド共通電極 72 は走査配線上で上下左右に網の目状に互いに連結されている。図115では上層シールド共通電極 72 は映像信号配線 51 のほとんどを完全に被覆しているが、図81のように誘電体バンプ 77 の両側の側壁に上層シールド共通電極を形成してもよい。30インチ以上の大型液晶TVの場合には誘電体バンプ 77 の両側の側壁に上層シールド共通電極を設置する構造の方が映像信号波形の歪を低減できるのでこのましい。

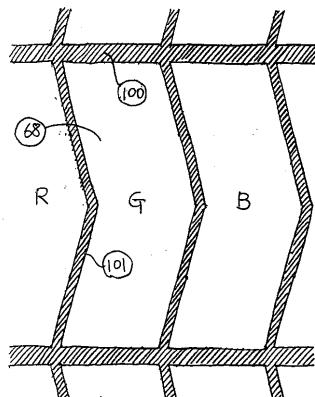

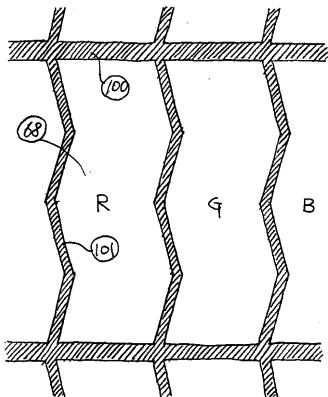

【0138】〔実施例11〕図69、図70、図71、図72、図73、図74、図75、図76、図77、図78、図79、図80、図81、図115は、本発明の実施例11の横電界方式液晶パネルの平面図である。映像信号配線と上層シールド共通電極と画素内共通電極と液晶駆動電極とが、1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造となっている。実施例11では正の誘電率異方性液晶を用いており、液晶分子の配向方向は、走査線に対してほぼ直交する方向になっている。図120にあるように液晶分子の回転運動方向は左回りと右回りの2方向になり、視野角の拡大化とカラーシフトの低減を同時におこなうことができる。

【0139】実施例11で負の誘電率異方性液晶を用い、液晶分子の配向方向を走査線に対してほぼ平行な方向にすることで、図121にあるように液晶分子の回転運動方向は左回りと右回りの2方向になり、視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合、映像信号配線と液晶駆動電極と画素内共通電極と上層共通電極は液晶分子の配向方に対して90度をのぞく60度から120度の範囲で1画素内で1回以上屈曲している構造になっている。

【0140】〔実施例12〕図82、図84、図92、図93、図94、図95は、本発明の実施例12の横電界方式液晶パネルの平面図である。映像信号配線が直線状で、上層シールド共通電極と画素内共通電極と液晶駆動電極が1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造となっている。実施例12では、正の誘電率異方性液晶を用いており、液晶分子の配向方向は、走査線に対してほぼ直交する方向になっている。図120にあるように液晶分子の回転運動方向は、左回りと右回りの2方向になり、視野角の拡大化とカラーシフトの低減を同時におこなうことができる。

【0141】実施例12で負の誘電率異方性液晶を用い、液晶分子の配向方向を走査線に対してほぼ平行な方向にすることで、図121にあるように液晶分子の回転運動方向は、左回りと右回りの2方向になり、視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合、液晶駆動電極と画素内共通電極と上層シールド共通電極は、液晶分子の配向方に対して90度をのぞく60度から120度の範囲で1画素内で1回以上屈曲している構造になっている。

【0142】〔実施例13〕図83、図85、図88、図89、図90、図91、図96、図97は、本発明の実施例13の横電界方式液晶パネルの平面図である。映像信号配線と上層シールド共通電極が直線状で、画素内共通電極と液晶駆動電極が、1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造となっている。実施例13では、正の誘電率異方性液晶を用いており、液晶分子の配向方向は、走査線に対してほぼ直交する方向になっている。図120にあるように液晶分子の回転運動方向は、左回りと右回りの2方向になり視野角の拡大化とカラーシフトの低減を同時におこなうことができる。

【0143】実施例13で負の誘電率異方性液晶を用い、液晶分子の配向方向を走査線に

10

20

30

40

50

対してほぼ平行な方向にすることで、図121にあるように液晶分子の回転運動方向は、左回りと右回りの2方向になり視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合、液晶駆動電極と画素内共通電極は、液晶分子の配向方向に対して90度をのぞく60度から120度の範囲で1画素内で1回以上屈曲している構造になっている。

【0144】〔実施例14〕映像信号配線と上層シールド共通電極と画素内共通電極が直線状で液晶駆動電極のみが、1画素内で液晶分子の配向方向に対して0度をのぞく0度から30度の角度の範囲で1回以上屈曲している構造をしていても図120にあるように液晶分子の回転運動方向は左回りと右回りの2方向になり、視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合には、正の誘電率異方性液晶を用いており、液晶分子の配向方向は、走査線に対してほぼ直交する方向になっている。10

【0145】実施例14で負の誘電率異方性液晶を用い、液晶分子の配向方向を走査線に対してほぼ平行な方向にすることで、図121にあるように液晶分子の回転運動方向は左回りと右回りの2方向になり視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合液晶駆動電極のみが、液晶分子の配向方向に対して90度をのぞく60度から120度の範囲で1画素内で1回以上屈曲している構造になっている。

【0146】〔実施例15〕実施例11で画素内共通電極が存在せず、かつ1画素内で液晶駆動電極が1本しか存在していない、かつ映像信号配線と上層シールド共通電極と1本のみの液晶駆動電極が、1画素内で液晶の配向方向に対して0度をのぞく0度から30度の角度の範囲で、1回以上屈曲している構造も図120にあるように液晶分子の回転運動方向は、左回りと右回りの2方向になる。これにより視野角の拡大化とカラーシフトの低減を同時におこなうことが可能である。この場合には、正の誘電率異方性液晶を用いており、液晶分子の配向方向は走査線に対してほぼ直交する方向になっている。実施例15は、画素ピッチが50ミクロンメーター以下の超高精細表示装置を作る時に適している。20

【0147】実施例15で負の誘電率異方性液晶を用い、液晶分子の配向方向を走査線に対してほぼ平行な方向にすることで図121にあるように液晶分子の回転運動方向は左回りと右回りの2方向になり視野角の拡大化とカラーシフトの低減を同時におこなうことができる。この場合、映像信号配線と上層シールド共通電極と1本のみの液晶駆動電極は、液晶分子の配向方向に対して90度をのぞく60度から120度の範囲で1画素内で1回以上屈曲している構造になっている。30

【0148】実施例11と実施例15で使用するカラーフィルター基板の構造は、図122や図123にあるように遮光膜（ブラックマスク）101とカラーフィルター層68が映像信号配線とほぼ同様の形状で屈曲している。本発明の場合映像信号配線を被覆しているスペーサーバンプや被覆バンプも映像信号配線とほぼ同じ形状で屈曲している。上層シールド共通電極が完全に映像信号配線を被覆している場合には、映像信号配線に対応している遮光膜はなくても光ぬけは生じないので、省略することも可能である。上層シールド共通電極が、完全に映像信号配線と走査線を被覆している場合には、遮光膜がなくても光ぬけが生じないのでカラーフィルター層だけ映像信号配線の屈曲している形状にあわせて屈曲させるだけで良い。

【0149】〔実施例16〕図119が本発明の実施例16の横電界方式液晶表示パネルの断面図と平面図である。表示領域の最外周をとりかこんでいる遮光膜（ブラックマスク）67の境界にオーバーラップする位置に閉ループ状のスペーサーバンプ94を形成している。このスペーサーバンプ94の幅は約100～500ミクロンメーター程度あれば十分である。あまり細すぎても良くない。40

図119では、閉ループ状のスペーサーバンプ94は1本だけしか存在していないが、複数本配置しても良い。メインシール96の領域には円形のスペーサーバンプ95多数配置されている。本発明の構造を採用するとメインシール96にセルギャップを決定するためのガラスファイバーを混入する必要がない。ガラスファイバーが混入しないので映像信号配線や走査線にやわらかいアルミニウム合金を用いても、配線の切断現象が発生しない。本発明の構造を採用するとメインシールが遮光膜（ブラックマスク）50

の領域に侵入しなくなりインシールを紫外線で完全に硬化することができる。メインシールからの不純物の拡散を防止できるので信頼性を向上できる。

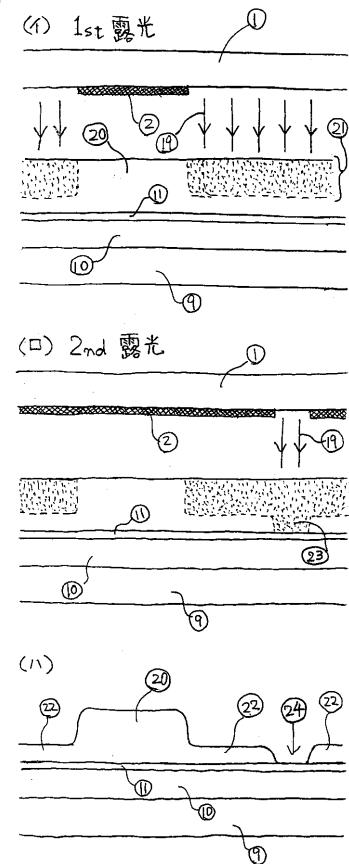

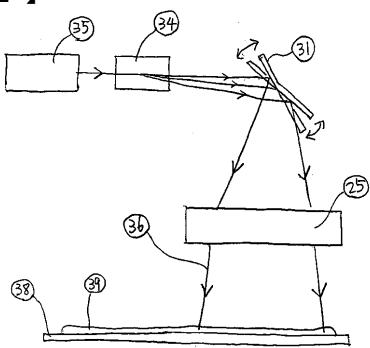

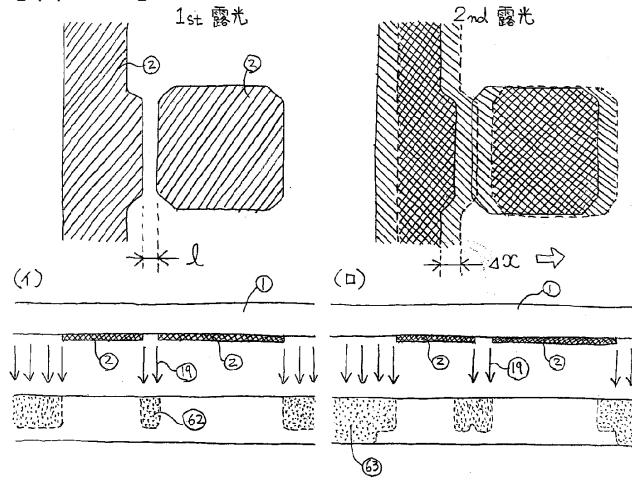

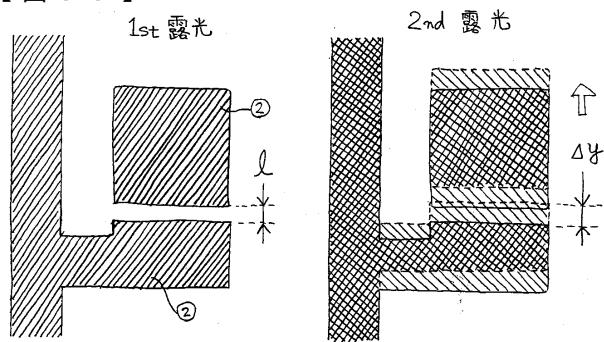

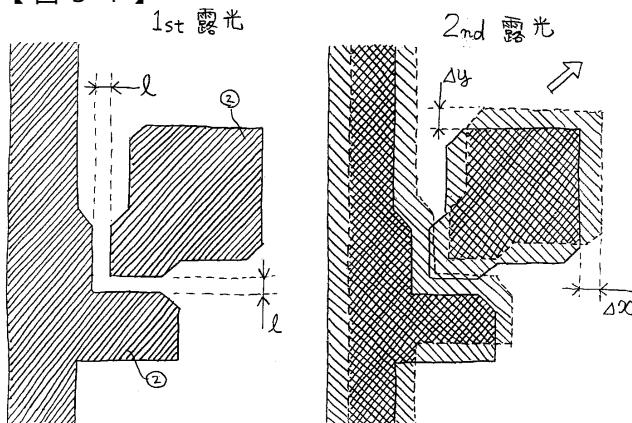

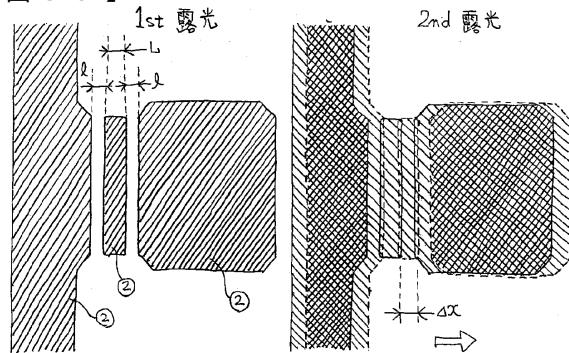

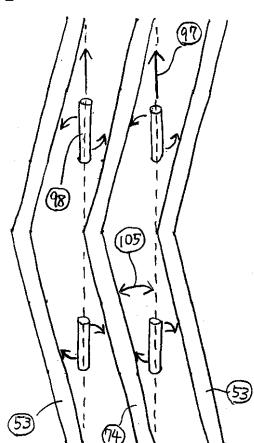

【0150】〔実施例17〕図32,図33,図34,図35,と図106が本発明の実施例17のハーフトーンシフト露光のプロセス概念図である。薄膜トランジスタのソース電極とドレイン電極を最終的に目標とするトランジスタのチャネル長の約半分の距離1だけあけてホトマスクを設計する。つまり最終的にトランジスタのチャネル長を6ミクロンメーターにしたい場合、ホトマスクでは6ミクロンの半分の3ミクロンメーターの距離をあけてソース電極とドレイン電極を作ります。この通常ホトマスクを用いてポジレジストをはじめの1回めはアンダー露光の条件で露光します。次にホトマスクか、ガラス基板のどちらかを水平方向にホトマスク上のソース電極とドレイン電極のチャネル長1だけシフトさせた後前の露光条件と同じアンダー露光の条件で再度露光します。その後現像すると、図32の(八)の断面形状をしたポジレジストを得ることができます。図33,図34もほぼ同じ発想です。

【0151】図35は、ホトマスクのソース電極とドレイン電極のあいだに1本の細長い棒状のパターンを設置している。細長い

### 棒状のパターン幅とすきまとの関係はしきい条件になつて

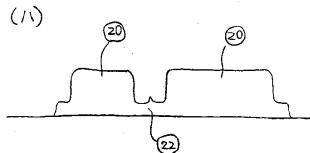

いる。アンダー露光の条件で露光するために1はしきいよりもすこしだけ大きいほうが良い。図32と同様にすきま1だけホトマスクか、ガラス基板を水平方向にシフトさせた後再度同じ条件でアンダー露光する。その後現像すると図35の(八)の断面形状のポジレジストが得られる。薄膜トランジスタのチャネル領域にあたる部分のポジレジストができるだけ平坦になるようにシフト量と露光量を調整する。完全未露光部分20の膜厚が1.5~2.5ミクロンメーターでハーフ露光領域(アンダー露光領域)22の膜厚が0.2~0.5ミクロンメーターになるようにポジレジストの塗布膜厚と露光量を調整すると良い。

【0152】図106が本発明のハーフトーンシフト露光を用いた薄膜トランジスタ素子形成のプロセス断面図である。使用するホトマスク工程は全工程で4回である。図1にある透過光量変調ホトマスクを用いてハーフトーン露光して薄膜トランジスタを製作する工程は、図36に記載されています。工程はほぼまったく同じである。本発明の場合図106にるように薄膜半導体のエッジ部分が階段状に加工されるためパッシベーションのカバーレージが従来の方式のものとくらべて良くなっている。従来の透過光量変調ホトマスクは、ホトマスク価格が高く、超大型液晶TV用には、なかなか適用しにくかったが、本発明のハーフトーンシフト露光用のホトマスクは、安価な通常ホトマスクを用いることができる。

【0153】本発明の実施例17は、液晶表示装置だけでなく、有機EL表示装置、X線ディテクター用のアクティブマトリックス基板の製造に適用することができ非常にコストダウンをはかることができる。

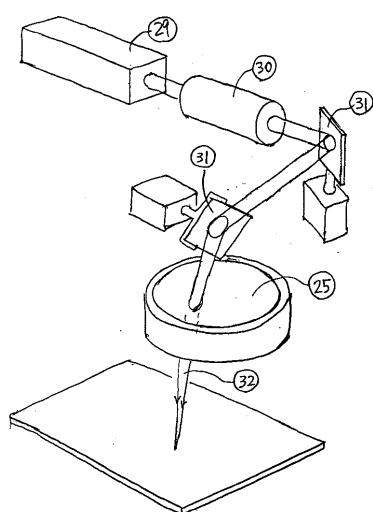

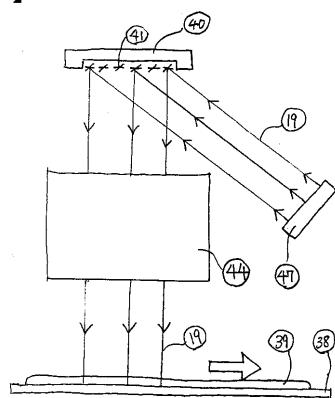

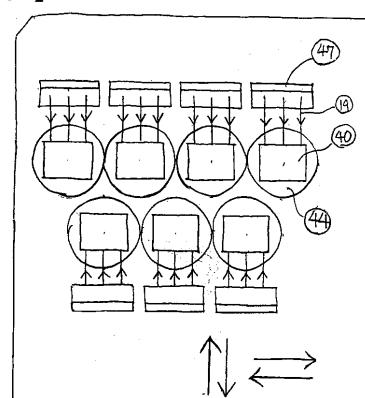

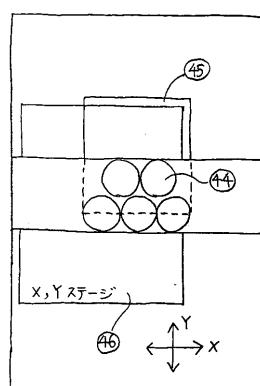

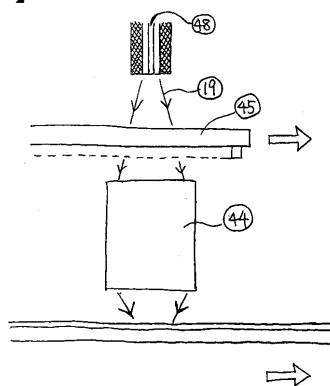

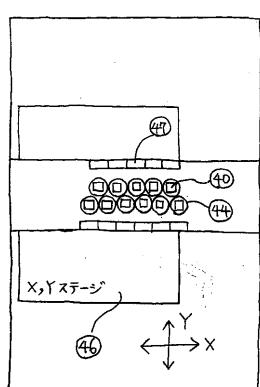

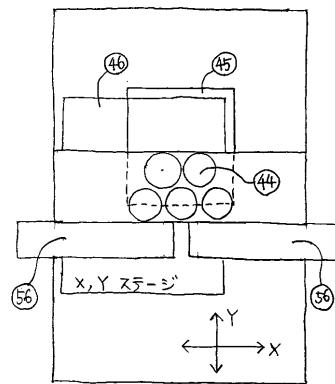

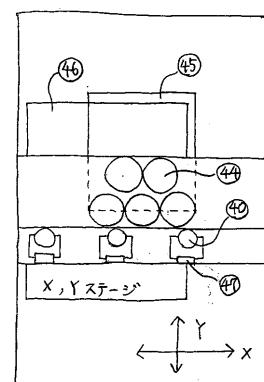

【0154】図17,図19が実施例17のハーフトーンシフト露光で使用される走査露光装置の平面図と断面図である。通常ホトマスク45をシフトさせても良いしX,Yステージをシフトさせても良い。ミラープロジェクション投影走査露光装置でもまったく同じく、ハーフトーンシフト露光をおこなうことができる。本発明のハーフトーンシフト露光法には、図17,図19にあるようなマルチレンズ走査露光装置の方がポジレジストの解像力を向上できるので適している。従来の透過光量変調ホトマスクを用いるハーフトーン露光法では解像力の弱いミラープロジェクション走査露光装置の方が適している。

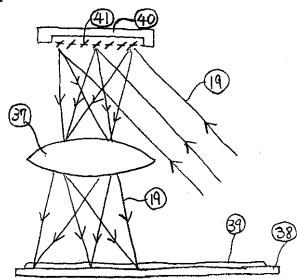

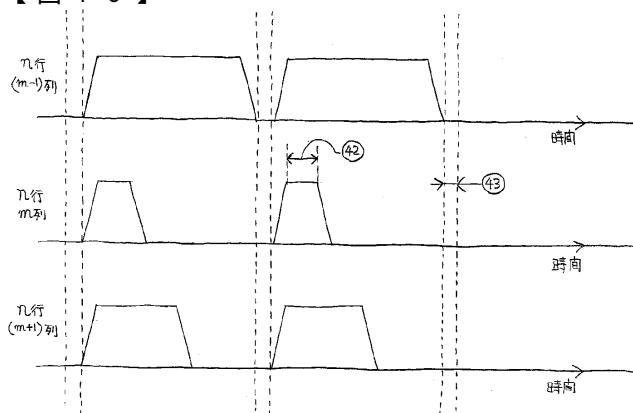

【0155】〔実施例18〕図13,図18,図14,図15,図16,図20が本発明のマイクロミラーを2次元に形成した反射ミラーデバイス40を複数個ちどり配列したホトマスクを用いない走査露光装置である。図16にるようにマイクロミラーの動作時間を1個1個別々に制御することができる。この反射ミラーデバイスを用いて紫外光をポジレジストに照射する時間を変化させることで図20にこのような多段階ハーフトーン露光をおこなうことができる。高価な透過光量変調ホトマスクを用いなくても簡単に多段

階ハーフトーン露光を大面積に走査露光することができる。

【0156】〔実施例19〕図37, 図43が実施例17のハーフトーンシフト露光を走査線と下層シールド共通電極と画素内共通電極の形成に用いた場合の通常ホトマスクのパターンの平面図とハーフトーンシフト露光した時の露光光量の分布の説明図である。まず通常ホトマスクを用いてアンダー露光(1st露光)した後走査線に平行に共通電極の幅だけシフトさせた後、再度同じ光量でアンダー露光(2nd露光)をおこなう。現像するとポジレジストが厚く残る所と薄く残る所と完全になくなる所にわかれます。この方法を用いて電極の厚みを2段階に変化させるプロセスフロー説明図が図7と図8である。選択エッチング可能な金属または合金を2層から3層に形成し、本発明のハーフトーンシフト露光をおこないポジレジストの膜厚を完全未露光領域20と不完全露光領域22の2段階に形成する点に特徴がある。エッチングとポジレジストのアッシング処理と選択エッチングを用いて電極を2段階に加工している。 10

【0157】本発明のハーフトーンシフト露光を用いる場合、はじめの1st露光と2番めの2nd露光でホトマスクを変更していない。そのために1st露光と2nd露光の位置ぎめを再度おこなう必要はなくただ単に一方向だけに一定量だけ水平移動させるだけですむので、走査線とシールド共通電極と画素内共通電極を形成する時にハーフトーンシフト露光処理用のアライメントマークをガラス基板に前もって形成しておく必要がないのでプロセス工程の短縮化と低コスト化を実現できる。

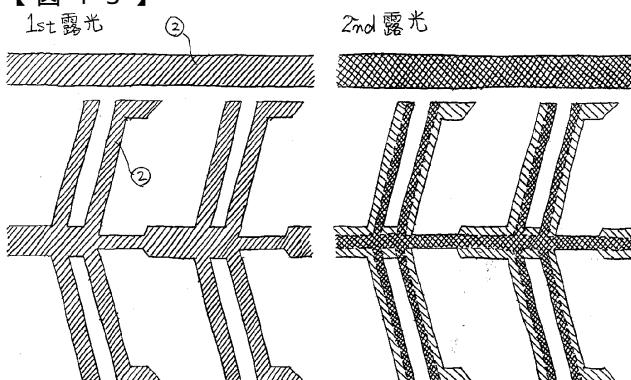

【0158】〔実施例20〕図38, 図39, 図40, 図41, 図44が通常ホトマスクを用いてハーフトーン露光を走査線とシールド共通電極に適用した時の露光光量の分布の説明図である。はじめの1st露光と2番めの2nd露光でホトマスクを変更しているために本工程では、前もってガラス基板にアライメントマークを形成しておく必要がある。図9がガラス基板に直接アライメントマークを書きこむ装置である。図10にガラス基板の内部にアライメントマークが書きこまれる原理図をしめしてある。図11がガラス基板に直接アライメントマークを書きこんだ基板である。走査線とシールド共通電極を形成するための金属をデポした領域の外にアライメントマークは形成されている。

本発明で使用するレーザーマーキングに関しては特開平11-267861に詳細に説明してある。ガラスの表面ではなくガラスの内部にアライメントマークを形成することが、歩留りを向上させるうえで特に重要です。

【0159】異なる通常ホトマスクを用いて1stアンダー露光と2ndアンダー露光をおこなった後現像すると2段階の膜厚のポジレジストパターンを得ることができる。図7, 図8に、この2段階の膜厚のポジレジストを用いてエッチングとポジレジストのアッシングと選択エッチングをすることで2段階の膜厚に金属電極を加工する方法が説明されている。この2ステップ・ハーフトーン露光法を用いて薄膜トランジスタを形成するプロセスフロー図が図27と図28である。走査線15と画素内共通電極49の同時形成と映像信号配線51と液晶駆動電極53の同時形成に本発明の2ステップハーフトーン露光法(2ステップアンダー露光法)が用いられている。 30

【0160】〔実施例21〕図27, 図28が実施例21の薄膜トランジスタ形成のためのプロセスフロー図である。図27では走査線に三層金属構造を用いている。図28では走査線に二層金属構造を用いている。図27, 図28ともに本発明の2ステップ・ハーフトーン露光法を用いて画素内共通電極49は単層金属で構成され薄膜化されている。走査線に2ステップ・ハーフトーン露光法を適用するときには、前もってガラス基板内にレーザーを用いて、アライメントマークを形成しておく必要がある。図27, 図28ともに薄膜トランジスタのシリコン素子分離(シリコンisland化)と端子部のコンタクトホールの同時形成をハーフトーン露光を用いておこなっている。図27, 図28ともに本発明の2ステップ・ハーフトーン露光法を用いて液晶駆動電極53は、単層化され薄膜化されている。 40

本実施例のように走査線と映像信号配線の2つの工程に2ステップ・ハーフトーン露光法を用いて画素内共通電極49と液晶駆動電極53の両法を薄膜化した場合、ラビング配向処理の時にラビング布の毛先きの運動がなめらかになり配向不良領域が発生しな 50

くなる。

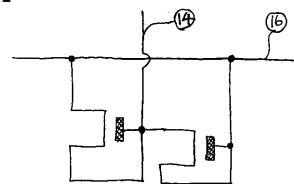

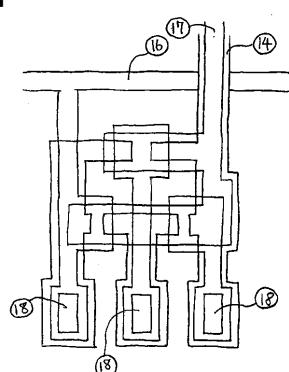

【0161】薄膜トランジスタのシリコン素子分離（シリコン *i s l a n d* 化）と端子部のコンタクトホールの同時形成をハーフトーン露光法を用いておこなう場合、図21、図22にあるような静電対策用保護回路も同時に形成されるようにしなければならない。図23、図24、図25、図26にあるようにコンタクトホール18をそろえて配置することで、コンタクトホール18の穴の大きさを最大にすることができる。この場合には、図12や図13にあるような紫外線レーザービームや紫外線LED光を用いた局所露光装置を用いてコンタクトホール18の部分だけ局所露光することが可能である。図6が局所露光装置を用いた露光プロセスの説明図である。図29、図30が、本発明の局所露光装置を内蔵した、ハーフトーン走査露光装置の平面図である。1台で通常ホトマスクを用いてハーフトーン露光と局所露光とを同時におこなうことができる。生産効率を大幅に向上できる。図31が本発明のハーフトーン露光プロセスを用いた横電界方式アクティブマトリックス基板の平面図である。局所UV露光で形成したコンタクトホール61がそろえて配置されている。

【0162】〔実施例22〕図114、図130は、本発明のハーフトーン裏面露光と通常ホトマスク露光を組みあわせて、基板の平坦化とホトリソスペーサーを同時に形成するプロセスフロー説明図である。この実施例22では、ネガレジストを用いている。ネガレジスト87を液晶セルギャップの厚みだけ塗布した後、通常ホトマスクを用いてホトスペーサーを形成する領域のみ、完全露光させる。次に図131、図132、図133、図134にあるような走査型裏面露光装置を用いてアクティブマトリックス基板の裏面側から紫外光を照射して、基板の凹凸を平坦化するのに十分なだけの厚みだけネガレジストを感光させる。現像すると、基板の平坦化とホトスペーサーが同時に形成されることになる。

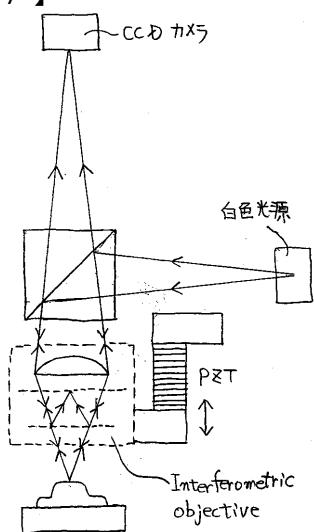

【0163】図131、図132は、実施例22で用いる走査裏面露光装置である。石英ガラスファイバーをたばにしてならべて均一な紫外線強度を得られるようにしてある。図133、図134は紫外線LEDを複数列ならべて均一な紫外線強度が得られるようになっている。図137は、アクティブマトリックス基板に形成されたホトスペーサーの高さを精密測定するための白色干渉計の光学系の説明図である。図135、図136にるように白色干渉計の測定データをもとにネガレジストコーティング膜厚とハーフトーン裏面露光光量を調整する方法を用いることで基板の凹凸の平坦化のバラツキをなくし、ホトスペーサーの高さのバラツキも低減することができる。

【0164】図107は、本発明の走査型裏面露光装置を用いて、まず最初に平坦化をおこない次にホトスペーサーを形成するプロセス説明図である。図107、図114、図130では、ホトスペーサーを形成しているが、実施例1、実施例2、実施例5、実施例6、実施例9にあるスペーサーバンプ73を形成しても良い。走査型裏面露光方法を用いて平坦化する場合には、画素内共通電極と液晶駆動電極は、光を通さない金属電極を用いなければならない。

【0165】〔実施例23〕図125は、本発明の実施例23の横電界方式アクティブマトリックス基板の製造工程の説明図である。ホトリソ工程は全工程で5回必要である。実施例21と実施例22のプロセスを用いることで、工程短縮を実現している。基板表面の平坦化処理をおこなっているためラビング配向処理時に配向不良が発生しない。黒表示時の光リークが少なく、コントラストの大きな画像が得られる。

【0166】〔実施例24〕図126は本発明の実施例24の横電界方式アクティブマトリックス基板の製造工程の説明図である。ホトリソ工程は全工程で4回必要である。実施例21と実施例22のプロセスを用いることで、工程短縮を実現している。実施例23では、基板全面にP-CVD装置を用いてP-SiNxパッシベーション膜を堆積していたが本実施例ではシャドーフレームを用いた局所成膜形成法でP-SiNxパッシベーション膜を部分的に堆積したり、インクジェットプリンターなどの塗布装置を用いて局所的に有機パッシベーション膜（BCBなど）を塗布しているため、走査線（Gate電極）や映像信号配線（Data電極）の端子部のコンタクトホールをあける工程が省略できる。

10

20

30

40

50

基板表面の平坦化処理をおこなっているため、ラビング配向不良が生じない。

【0167】〔実施例25〕図127は、本発明の実施例25の横電界方式アクティブマトリックス基板の製造工程の説明図である。ホトリソ工程は全工程で3回必要である。実施例17と実施例22のプロセスを用いることで工程短縮を実現している。本実施例では、シャドーフレームを用いた局所成膜形成法でP-SiNxパッシベーション膜を部分的に堆積したり、インクジェットプリンターなどの塗布装置を用いて局所的に有機パッシベーション膜(BCBなど)を塗布しているため、走査線(Gate電極)や映像信号配線(Data電極)の端子部のコンタクトホールをあける工程が省略できる。基板表面の平坦化処理をおこなっているため、ラビング配向不良が生じない。

【0168】

10

#### 【発明の効果】

本発明の通常ホトマスクを用いるハーフトーンシフト露光法や通常ホトマスクを用いたハーフトーン露光と局所追加露光を用いるハーフトーンミックス露光法を用いることで、横電界方式液晶表示装置を低コストで歩留り良く生産することができる。

【0169】本発明のハーフトーン裏面走査露光法とホトスペーサー形成を一回のネガレジスト工程で完了させてしまうことで低コスト化と配向不良の少ないコントラスト高い高品位画像を得ることができる。

【0170】本発明のスペーサーバンプ構造を採用することで開口率の非常に大きな横電界方式液晶表示装置を低コストで実現できる。上層シールド共通電極と画素内共通電極と液晶駆動装置とをすべて同じ電極材料でかつ同じ層に形成することで、残像の少ない開口率の大きい明るいしかも黒レベルが均一で深い黒表示が可能な高品質画像を得ることができる。本発明を用いることで低価格で高コントラストな超大型横電界方式液晶TVを実現できる。

20

#### 【図面の簡単な説明】

【図1】従来のハーフトーン露光用ホトマスクと現像後のポジレジストの断面形状

【図2】本発明のハーフトーン露光用ホトマスクと現像後のポジレジストの断面形状

【図3】従来の4ホトマスク工程フロー説明

【図4】本発明の4ホトマスク工程フロー説明

【図5】本発明の分離2重露光法と現像後のポジレジストの断面形状

【図6】本発明の分離2重露光法と現像後のポジレジストの断面形状

30

【図7】本発明の映像信号配線や共通電極を形成するためのプロセスフロー

【図8】本発明の映像信号配線や共通電極を形成するためのプロセスフロー

【図9】本発明のレーザーライメントマーキングプロセスで使用するレーザー光学装置

【図10】本発明のレーザーライメントマーキングプロセスで使用するfレンズを用いた光学系説明図

【図11】本発明で使用するレーザーライメントマーカーの位置

【図12】本発明で使用するレーザービーム走査露光光学系

【図13】本発明で使用するマイクロミラーアレイ素子を用いた紫外線投影露光方式タイマー光学系(倒立実像系)

【図14】本発明で使用するマイクロミラーアレイ素子を用いた紫外線投影露光方式マルチレンズ走査光学系(正立実像系)

40

【図15】本発明で使用するマルチレンズ走査露光光学系の平面図

【図16】本発明で使用するマイクロミラーアレイの動作の時間幅コントロールによるUV露光光量調整の説明図

【図17】本発明の分離2重露光法プロセスで用いる走査露光装置の平面図

【図18】本発明のホトマスクを用いないダイレクトハーフトーン露光法プロセスで用いる走査露光装置の平面図

【図19】本発明の分離2重露光法プロセスで用いる走査露光装置の断面図

【図20】本発明のダイレクトハーフトーン露光法による露光の原理図と現像後のホトレジストの断面形状図

50

- 【図 2 1】静電気対策用薄膜トランジスタ保護回路図

【図 2 2】静電気対策用薄膜トランジスタ保護回路図

【図 2 3】本発明の静電気対策用保護トランジスタ素子の平面図

【図 2 4】本発明の静電気対策用保護トランジスタ素子の平面図

【図 2 5】本発明の静電気対策用保護トランジスタ素子の平面図

【図 2 6】本発明の静電気対策用保護トランジスタ素子の平面図

【図 2 7】本発明の4ホトマスク工程フロー説明断面図

【図 2 8】本発明の3ホトマスク工程フロー説明断面図

【図 2 9】本発明のミックス露光法プロセスで用いる走査露光装置の平面図

【図 3 0】本発明のミックス露光法プロセスで用いる走査露光装置の平面図

【図 3 1】本発明のミックス露光法を用いて製作した横電界方式アクティブマトリックスアレイ基板の平面図

【図 3 2】本発明のハーフトーンシフト露光の原理説明図と現像後のホトレジストの断面形状

【図 3 3】本発明のハーフトーンシフト露光の原理説明図

【図 3 4】本発明のハーフトーンシフト露光の原理説明図

【図 3 5】本発明のハーフトーンシフト露光の原理説明図と現像後のホトレジストの断面形状

【図 3 6】従来のハーフトーン露光方法を用いる4ホトマスク工程のプロセス断面説明図

【図 3 7】本発明のハーフトーンシフト露光の原理説明図

【図 3 8】本発明の分離2重露光法の原理説明図

【図 3 9】本発明の分離2重露光法の原理説明図

【図 4 0】本発明の分離2重露光法の原理説明図

【図 4 1】本発明の分離2重露光法の原理説明図

【図 4 2】本発明の4ホトマスク工程フロー説明

【図 4 3】本発明の分離2重露光法の原理説明図

【図 4 4】本発明の分離2重露光法の原理説明図

【図 4 5】本発明の映像信号配線被覆スペーサーとその上に形成されたシールド電極からなる横電界方式液晶パネルの断面図。

【図 4 6】本発明の映像信号配線被覆スペーサーとその上に形成されたシールド電極からなる横電界方式液晶パネルの断面図

【図 4 7】本発明の横電界方式液晶パネルの断面図

【図 4 8】本発明の横電界方式液晶パネルの断面図

【図 4 9】本発明の横電界方式液晶パネルの断面図

【図 5 0】本発明の横電界方式液晶パネルの断面図

【図 5 1】本発明の横電界方式液晶パネルの断面図

【図 5 2】本発明の横電界方式液晶パネルの断面図

【図 5 3】本発明の横電界方式液晶パネルの断面図

【図 5 4】本発明の横電界方式液晶パネルの断面図

【図 5 5】本発明の横電界方式液晶パネルの断面図

【図 5 6】本発明の横電界方式液晶パネルの断面図

【図 5 7】本発明の横電界方式液晶パネルの断面図

【図 5 8】本発明の横電界方式液晶パネルの断面図

【図 5 9】本発明の横電界方式液晶パネルの断面図

【図 6 0】本発明の横電界方式液晶パネルの断面図

【図 6 1】本発明の横電界方式液晶パネルの断面図

【図 6 2】本発明の横電界方式液晶パネルの断面図

【図 6 3】本発明の横電界方式液晶パネルの断面図

【図 6 4】本発明の横電界方式液晶パネルの断面図

【図 6 5】本発明の横電界方式液晶パネルの断面図

10

20

30

40

50

- 【図 6 6】本発明の横電界方式液晶パネルの断面図

【図 6 7】本発明の横電界方式液晶パネルの断面図

【図 6 8】本発明の横電界方式液晶パネルの断面図

【図 6 9】本発明の横電界方式液晶表示素子の平面図

【図 7 0】本発明の横電界方式液晶表示素子の平面図

【図 7 1】本発明の横電界方式液晶表示素子の平面図

【図 7 2】本発明の横電界方式液晶表示素子の平面図

【図 7 3】本発明の横電界方式液晶表示素子の平面図

【図 7 4】本発明の横電界方式液晶表示素子の平面図

【図 7 5】本発明の横電界方式液晶表示素子の平面図

【図 7 6】本発明の横電界方式液晶表示素子の平面図

【図 7 7】本発明の横電界方式液晶表示素子の平面図

【図 7 8】本発明の横電界方式液晶表示素子の平面図

【図 7 9】本発明の横電界方式液晶表示素子の平面図

【図 8 0】本発明の横電界方式液晶表示素子の平面図

【図 8 1】本発明の横電界方式液晶表示素子の平面図

【図 8 2】本発明の横電界方式液晶表示素子の平面図

【図 8 3】本発明の横電界方式液晶表示素子の平面図

【図 8 4】本発明の横電界方式液晶表示素子の平面図

【図 8 5】本発明の横電界方式液晶表示素子の平面図

【図 8 6】本発明の横電界方式液晶表示素子の平面図

【図 8 7】本発明の横電界方式液晶表示素子の平面図

【図 8 8】本発明の横電界方式液晶表示素子の平面図

【図 8 9】本発明の横電界方式液晶表示素子の平面図

【図 9 0】本発明の横電界方式液晶表示素子の平面図

【図 9 1】本発明の横電界方式液晶表示素子の平面図

【図 9 2】本発明の横電界方式液晶表示素子の平面図

【図 9 3】本発明の横電界方式液晶表示素子の平面図

【図 9 4】本発明の横電界方式液晶表示素子の平面図

【図 9 5】本発明の横電界方式液晶表示素子の平面図

【図 9 6】本発明の横電界方式液晶表示素子の平面図

【図 9 7】本発明の横電界方式液晶表示素子の平面図

10

【図 9 8】本発明で使用するハーフトーンプロセス用ネガレジストの現像後の膜厚特性

【図 9 9】本発明で使用するハーフトーンプロセス用ネガレジストの現像後の線幅特性

【図 1 0 0】本発明のハーフトーン露光用ホトマスクと現像後のネガレジストの断面形状

【図 1 0 1】本発明のハーフトーン露光用ホトマスクと現像後のネガレジストの断面形状

【図 1 0 2】本発明の分離 2 重露光法と現像後のネガレジストの断面形状

【図 1 0 3】本発明の分離 2 重露光法と現像後のネガレジストの断面形状

【図 1 0 4】本発明の映像信号配線被覆バンプとその上に形成されたホトスペーサの拡大

20

断面図

【図 1 0 5】本発明の 4 ホトマスク工程フロー説明

【図 1 0 6】本発明のハーフトーンシフト露光方法を用いる 4 ホトマスク工程のプロセス

断面説明図

【図 1 0 7】本発明のバック露光を用いて平坦化処理した横電界方式液晶パネルのプロセス

断面説明図

【図 1 0 8】本発明の横電界方式液晶パネルの断面図

【図 1 0 9】本発明の横電界方式液晶パネルの断面図

【図 1 1 0】本発明の横電界方式液晶パネルの断面図

【図 1 1 1】本発明の横電界方式液晶パネルの断面図

【図 1 1 2】本発明の横電界方式液晶パネルの断面図

30

40

50

【図 113】本発明の横電界方式液晶パネルの断面図

【図 114】本発明のハーフトーンバック露光方法を用いて平坦化処理とホトスペーサーを同時に形成するプロセス断面説明図

【図 115】本発明の横電界方式液晶表示素子の平面図

【図 116】本発明の6ホトマスク工程フロー説明

【図 117】本発明の6ホトマスク工程フロー説明

【図 118】本発明の6ホトマスク工程フロー説明

【図 119】本発明の横電界方式液晶パネルのメインシール付近の断面図と平面図

【図 120】本発明の横電界方式液晶パネルで使用する正の誘電率異方性液晶分子の配向方向と回転方向説明図

【図 121】本発明の横電界方式液晶パネルで使用する負の誘電率異方性液晶分子の配向方向と回転方向説明図

【図 122】本発明の横電界方式液晶パネルで使用するカラーフィルターの平面図

【図 123】本発明の横電界方式液晶パネルで使用するカラーフィルターの平面図

【図 124】本発明の3ホトマスク工程フロー説明

【図 125】本発明の5ホトマスク工程フロー説明

【図 126】本発明の4ホトマスク工程フロー説明

【図 127】本発明の3ホトマスク工程フロー説明

【図 128】本発明の5ホトマスク工程フロー説明

【図 129】本発明の6ホトマスク工程フロー説明

【図 130】本発明のハーフトーンバック露光方法を用いて平坦化処理とホトスペーサーを同時に形成するプロセス断面説明図

【図 131】本発明のハーフトーンバック露光装置の断面図

【図 132】本発明のハーフトーンバック露光装置の平面図

【図 133】本発明のハーフトーンバック露光装置の断面図

【図 134】本発明のハーフトーンバック露光装置の平面図

【図 135】本発明のハーフトーンバック露光トータルシステム構成図

【図 136】本発明のハーフトーンバック露光トータルプロセスフロー

【図 137】本発明で使用する白色干渉計の光学システム断面図

【符号の説明】

1 ホトマスク用石英ガラス基板

2 ホトマスク金属 (Cr or Mo)

3 半透過ホトマスク領域 (シリットパターン領域)

4 半透過ホトマスク領域 (a-Si or TiSi<sub>x</sub> or MoSi<sub>x</sub> or Ti<sub>x</sub>)

5 完全透過領域

6 ポジレジストUV露光完全遮断領域の現像後の領域

7 ポジレジストUV露光半透過領域の現像後の領域

8 ポジレジストがUV露光され現像後に完全になくなった領域

9 ゲート絶縁膜

10 薄膜半導体層 (ノンドープ層)

11 薄膜半導体層 (ドーピング層……オーミックコンタクト層)

12 バリアーメタル層

13 低抵抗金属層

14 映像信号配線

15 走査線

16 静電気対策用画素領域周辺共通電極

17 薄膜半導体層

18 静電気対策用薄膜トランジスタ回路を作るためのコンタクトホール

19 UV光

10

20

30

40

50

|     |                                  |    |

|-----|----------------------------------|----|

| 2 0 | ポジレジスト U V 露光完全遮断領域              |    |

| 2 1 | ポジレジスト U V 露光領域                  |    |

| 2 2 | ポジレジスト U V 露光不完全露光の現像後の領域        |    |

| 2 3 | 部分的に U V 光で露光されたポジレジスト領域         |    |

| 2 4 | 部分的に U V 光で露光されポジレジストが完全になくなった領域 |    |

| 2 5 | f レンズ                            |    |

| 2 6 | 下層電極材料                           |    |

| 2 7 | 低抵抗電極材料                          |    |

| 2 8 | 上層電極材料                           |    |

| 2 9 | レーザー光源                           | 10 |

| 3 0 | ビーム整形器                           |    |

| 3 1 | ガルバノミラー                          |    |

| 3 2 | レーザー光                            |    |

| 3 3 | ガラス内部に形成されたマークパターン               |    |

| 3 4 | 超音波偏向器                           |    |

| 3 5 | U V レーザー光源                       |    |

| 3 6 | U V レーザー光                        |    |

| 3 7 | 投影レンズ                            |    |

| 3 8 | T F T 用ガラス基板                     |    |

| 3 9 | ポジレジスト                           | 20 |

| 4 0 | D M D モジュール (マイクロミラーアレイデバイス)     |    |

| 4 1 | マイクロミラー                          |    |

| 4 2 | マイクロミラーの動作時間 (on time)           |    |

| 4 3 | マイクロミラーのデータ書き換え時間                |    |

| 4 4 | マルチ投影露光レンズモジュール (正立実像系)          |    |

| 4 5 | ホトマスク                            |    |

| 4 6 | X & Y 軸可動ステージ                    |    |

| 4 7 | 紫外線光源                            |    |

| 4 8 | 石英ファイバーケーブル                      |    |

| 4 9 | 画素内共通電極 (ボトム型)                   | 30 |

| 5 0 | 走査線端子部                           |    |

| 5 1 | 映像信号配線                           |    |

| 5 2 | バリアーメタル                          |    |

| 5 3 | 液晶駆動電極 (画素電極)                    |    |

| 5 4 | 走査線端子部駆動回路接合電極                   |    |

| 5 5 | パッシベーション膜                        |    |

| 5 6 | 紫外線レーザー走査露光装置                    |    |

| 5 7 | 映像信号配線端子部                        |    |

| 5 8 | 画素周辺共通電極端子部                      |    |

| 5 9 | 静電気対策用保護回路                       | 40 |

| 6 0 | 印刷塗布されたパッシベーション膜                 |    |

| 6 1 | 部分的に U V 光で露光することで形成されたコンタクトホール  |    |

| 6 2 | 1回めのハーフトーン露光で反応したポジレジストの領域       |    |

| 6 3 | 2回めのハーフトーン露光で完全に露光されたポジレジストの領域   |    |

| 6 4 | ドレイン電極                           |    |

| 6 5 | 透明画素電極                           |    |

| 6 6 | カラーフィルター側ガラス基板                   |    |

| 6 7 | ブラックマスク (遮光膜)                    |    |

| 6 8 | カラーフィルター層                        |    |

| 6 9 | カラーフィルター側平坦化層                    | 50 |

|       |                                           |    |

|-------|-------------------------------------------|----|

| 7 0   | カラーフィルター側配向膜                              |    |

| 7 1   | TFTアレイ基板側配向膜                              |    |

| 7 2   | 映像信号配線の電界をシールドするための共通電極（トップ型）             |    |

| 7 3   | 映像信号配線を被覆しているスペーサーバンプ                     |    |

| 7 4   | 画素内共通電極（トップ型）                             |    |

| 7 5   | 映像信号配線の電界をシールドするための共通電極（ボトム型）             |    |

| 7 6   | TFTアレイ側ガラス基板                              |    |

| 7 7   | 映像信号配線を被覆しているバンプ                          |    |

| 7 8   | 映像信号配線を被覆しているバンプの上に形成されたスペーサー             |    |

| 7 9   | 被覆バンプの側壁に形成されたシールド共通電極                    | 10 |

| 8 0   | 薄膜トランジスタ素子                                |    |

| 8 1   | シールド用共通電極と下層共通電極とを接合させるためのコンタクトホール        |    |

| 8 2   | 下層共通電極                                    |    |

| 8 3   | 映像信号配線の電界をシールドするための共通電極（トップ型）             |    |

| 8 4   | 走査線を被覆しているスペーサーバンプ                        |    |

| 8 5   | ネガレジストUV完全露光の現像後の領域                       |    |

| 8 6   | ネガレジストUV不完全露光の現像後の領域                      |    |

| 8 7   | ハーフトーン露光用ネガレジスト                           |    |

| 8 8   | 平坦化用透明ネガレジスト                              |    |

| 8 9   | ホトリソスペーサー                                 | 20 |

| 9 0   | 液晶駆動電極（トップ型）                              |    |

| 9 1   | 裏面側からのUV光                                 |    |

| 9 2   | 裏面UV露光して現像後に残ったネガレジスト                     |    |

| 9 3   | 薄膜トランジスターのドレイン電極と液晶駆動電極とを接合させるためのコンタクトホール |    |

| 9 4   | ガードリング状ホトスペーサー                            |    |

| 9 5   | 円形ホトスペーサー                                 |    |

| 9 6   | 液晶Cell形成用メインシール                           |    |

| 9 7   | 液晶分子の配向方向                                 |    |

| 9 8   | 正の誘電率異方性液晶分子                              | 30 |

| 9 9   | 負の誘電率異方性液晶分子                              |    |

| 1 0 0 | 走査線を被覆する遮光膜（ブラックマスク）                      |    |

| 1 0 1 | 映像信号配線を被覆する遮光膜（ブラックマスク）                   |    |

| 1 0 2 | 搬送用コロ                                     |    |

| 1 0 3 | UVカットカバー                                  |    |

| 1 0 4 | 石英ガラスファイバー                                |    |

| 1 0 5 | 正の誘電率異方性液晶分子の配向方向と画素電極の交差角度               |    |

| 1 0 6 | 負の誘電率異方性液晶分子の配向方向と画素電極の交差角度               |    |

| 1 0 7 | 紫外線LED                                    |    |

【図1】

【図2】

【図3】

- ① Gate 電極 & 共通電極

- ② 薄膜半導体 & S/D 電極

(ハーフトーン MASK 露光)

- ③ Gate & Data 端子部と

ピクセル ドレイン部と 静電気

対策用保護トランジスタ回路

部のコンタクトホール

- ④ Gate & Data 端子部と

ピクセルの透明導電性電極

【図4】

- ① レーザー アライメントマーキング

- ② Gate 電極 & 共通電極

(ハーフトーン 露光 1st & 2nd)

- ③ 薄膜半導体 & コンタクトホール

(ハーフトーン 露光 1st & 2nd)

- ④ S/D 電極 & 液晶駆動電極

(ハーフトーン 露光 1st & 2nd)

- ⑤ Gate & Data 端子部 コンタクトホール

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図23】

【図26】

【図24】

【図25】

【図27】

【図28】

【 図 2 9 】

〔 図 3 0 〕

【 図 3 1 】

【 図 3 2 】

(八)

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

- ① Gate電極 & 共通電極

- ② 薄膜半導体 & 3次電極

(ハーフトーン・シフト露光 1st & 2nd)

- ③ Gate & Data端子部と

ピクセルドレン部と静電気対策用

保護トランジスタ回路部の

コントクトホール

- ④ Gate & Data端子部と

ピクセルの透明導電性電極

【図44】

【図43】

【図45】

【図46】

【 図 4 7 】

【 図 4 8 】

【図49】

【図50】

## 【図5-4】

### 【 図 5 5 】

### 【図 5.6】

【 図 5 1 】

【図52】

【図53】

【図57】

【 図 5 8 】

【図59】

【図 6 0】

【図 6 1】

【図 6 2】

【図 6 3】

【図 6 8】

【図 6 4】

【図 6 5】

【図 6 6】

【図 6 7】

【図 6 9】

【図70】