675873

#### **AUSTRALIA**

#### PATENTS ACT 1990

#### PATENT REQUEST: STANDARD PATENT

I/We, the Applicant(s)/Nominated Person(s) specified below, request I/We be granted a patent for the invention disclosed in the accompanying standard complete specification.

# [70,71] Applicant(s)/Nominated Person(s):

NEC Corporation, incorporated in Japan, of 7-1, Shiba 5-chome, Minato-ku, Tokyo, JAPAN

[54] Invention Title:

Power Supply Control for a Receiver

[72] Inventor(s):

Motoki Ide

[74] Address for service in Australia:

Spruson & Ferguson, Patent Attorneys

Level 33 St Martins Tower

31 Market Street

Sydney New South Wales Australia (Code SF)

Details of Basic Application(s):

[33] Country:

[32] Application Date:

280656/1993

JΡ

15 October 1993

Basic Applicant(s): NEC Corporation

DATED this FOURTEENTH day of OCTOBER 1994

NEC Corporation

By:

Registered Patent Attorney

IRN: 285092 INSTR CODE: 59060

S 050176 141094

#### Australia

#### Paterics Act 1990

#### NOTICE OF ENTITLEMENT

I, Fraser Patison Old, of Spruson & Ferguson, St Martins Tower, 31 Market Street, Sydney, New South Wales 2000, Australia, being the patent attorney for the Applicant(s)/Nominated Person(s) in respect of Application No 75832/94 state the following:-

The Appli ant(s)/Nominated Person(s) has/have entitlement from the actual inventor(s) as follows:--

The Applicant(s)/Nominated Person(s), is/are the assignee(s) of the actual inventor(s).

The Applicant(s)/Nominated Person(s) is/are the applicant(s) of the basic application(s) listed on the Patent Request. The basic application(s) listed on the Patent Request is/are the first application(s) made in a Convention Country in respect of the invention.

DATED this TENTH

day of JANUARY

1995

F P 01d

IRN: 285092

INSTR CODE: 59060

(12) PATENT ABRIDGMENT (11) Document No. AU-B-75832/94 (19) AUSTRALIAN PATENT OFFICE (10) Acceptance No. 675873

(54) Title

POWER SUPPLY CONTROL FOR A RECEIVER

International Patent Classification(s)

(51)5 H04B 001/06

(21) Application No.: 75832/94

(22) Application Date: 14.10.94

(30) Priority Data

(31) Number (32) Date (33) Country 5-280656 15.10.93 JP JAPAN

(43) Publication Date: 04.05.95

(44) Publication Date of Accepted Application: 20.02.97

(71) Applicant(s)

NEC CORPORATION

(72) Inventor(s)

MOTOKI IDE

(74) Attorney or Agent SPRUSON & FERGUSON, GPO Box 3898, SYDNEY NSW 2001

(56) Prior Art Documents

US 5381133

US 5274843

US 5381133

(57) Claim

1. A power supply control apparatus for a radio section of a receiver responsive to signals containing a preamble and multiple batches each batch containing a synchronizing signal and multiple codeword groups, said receiver being assigned to one of said groups, comprising:

means for preventing power application to said radio section at timings of synchronizing signal receptions after a detection of a first synchronizing signal; and means for turning on said radio section on detection of said first synchronizing signal, and at reception timings of the group assigned to said receiver.

# Power Supply Control for a Receiver

### BACKGROUND OF THE INVENTION

#### Field of the Invention

5

10

The present invention relates to a power supply control and, more particularly, to a power supply control for a selective calling receiver having a battery saving function.

# Description of the Related Art

In a prior art selective calling receiver, a controller supplies a battery current to a receiving portion therein only when the receiver receives a synchronizing signal and a frame assigned to its own receiver to reduce consumption of the battery. Namely, the receiving portion is turned on only at each timing of the synchronizing signal and the assigned frame and is turned off at other times.

However, since several receivers are assigned to one frame, the frame may not include a message for the receiver if the receiver turns the receiving portion on at a timing of the assigned frame. Therefore, an improved receiver is disclosed in, for example, Japanese Patent Laid-Open Application No. 115632/192? (JP 04-115632.) This receiver detects whether a message addressed to its own receiver is included or not and turns the receiving portion off immediately after determining that the addressed message is not included in the frame.

While such a receiver can reduce consumed current, since the receiver turns the receiving portion on at a timing of

each synchronizing signal, the receiver still consumes too much current and therefore the battery life is unnecessarily shortened.

# SUMMARY OF THE INVENTION

It is an object of the present invention to ameliorate one or more of the abovementioned disadvantages.

According to the invention there is disclosed a power supply control apparatus for a radio section of a receiver responsive to signals containing a preamble and multiple batches each batch containing a synchronizing signal and multiple codeword groups, said receiver being assigned to one of said groups, comprising:

means for preventing power application to said radio section at timings of synchronizing signal receptions after a detection of a first synchronizing signal; and

means for turning on said radio section on detection of said first synchronizing signal, and at reception timings of the group assigned to said receiver.

According to the invention there is further disclosed a power supply control apparatus for a receiver comprising:

first detecting means for detecting a first synchronizing signal following a preamble signal in a received signal;

first control means for generating a first timing signal at the timing of each group assigned to said receiver within said received signal, and for turning a radio section in said receiver on in response to said first timing signals and for maintaining said radio section off at reception timings of synchronizing signals after said detection of said first synchronizing signal.

According to the invention there is further disclosed a method for controlling a power supply to a radio section in a receiver, the method comprising the steps of:

detecting a first synchronizing signal followed a preamble signal in a received signal;

general. a first timing signal at the timing of groups assigned to said receiver within said received signal;

turning a radio section in said receiver on in response to said first timing signal; and

keeping said radio section off at reception timings of synchronizing signals after said detection of said first synchronizing signal.

5

10

15

20

25

According to the invention there is further disclosed a method for controlling a power supply for a receiver turning a radio section on at reception timings of necessary parts in a received signal, the method comprising the steps of:

keeping said radio section off at timings of reception of synchronizing signals after a detection of a first synchronizing signal; and

turning said radio section on, based on said detection of the first synchronizing signal, at reception timings of assigned groups included in said received signal.

In a preferred embodiment of the invention there is provided a power supply control apparatus wherein each said group contains a selective calling number, said power supply control further comprising:

means for turning off said radio section when selective calling number in the receiver's assigned group is not the same as a selective calling number assigned to said receiver.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and other objects, features and advantages of this invention will become more apparent from the following detailed description taken with the accompanying drawings in which:

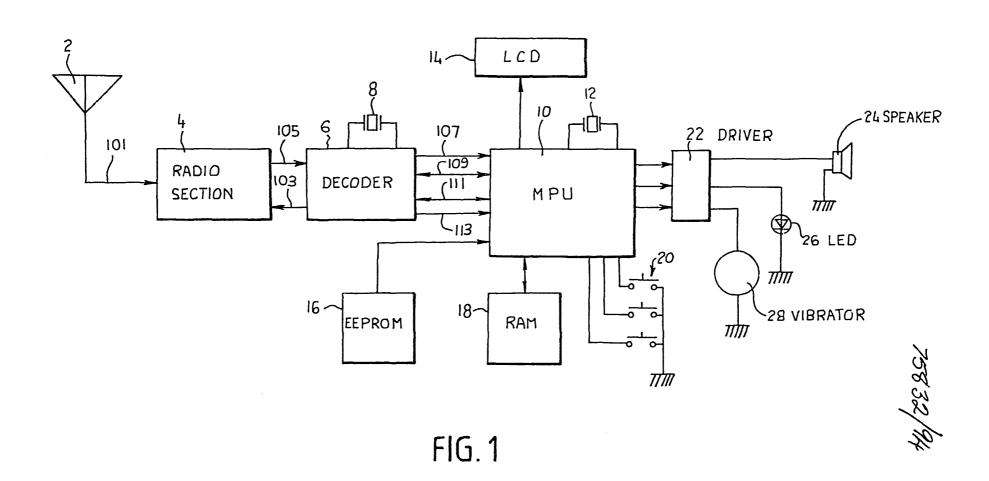

FIG. 1 is a block diagram of a preferred embodiment of a receiver of the present invention;

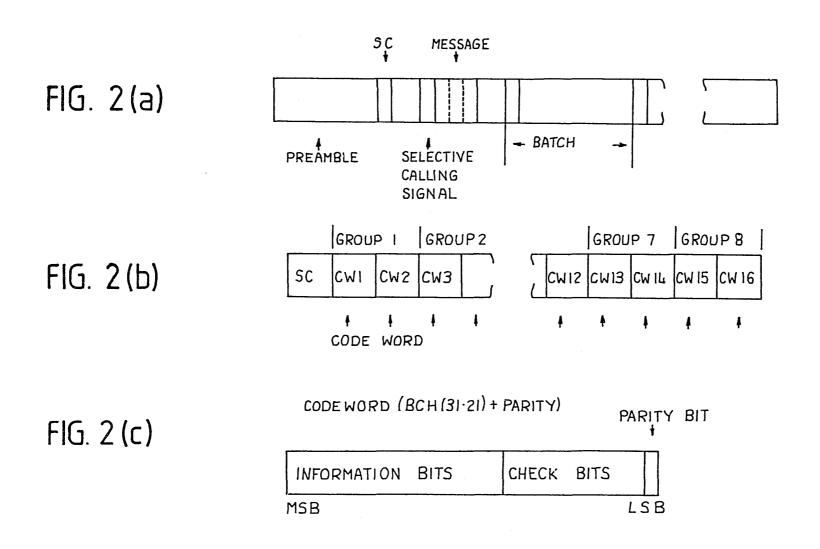

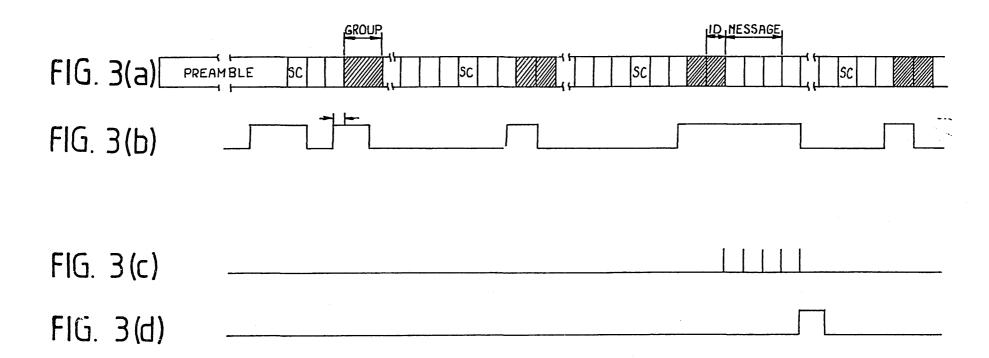

FIGs. 2(a)-2(c) illustrate a POCSAG format using in the present invention; FIGs. 3(a)-3(d) illustrate timing charts to explain a battery saving operation according to the present invention;

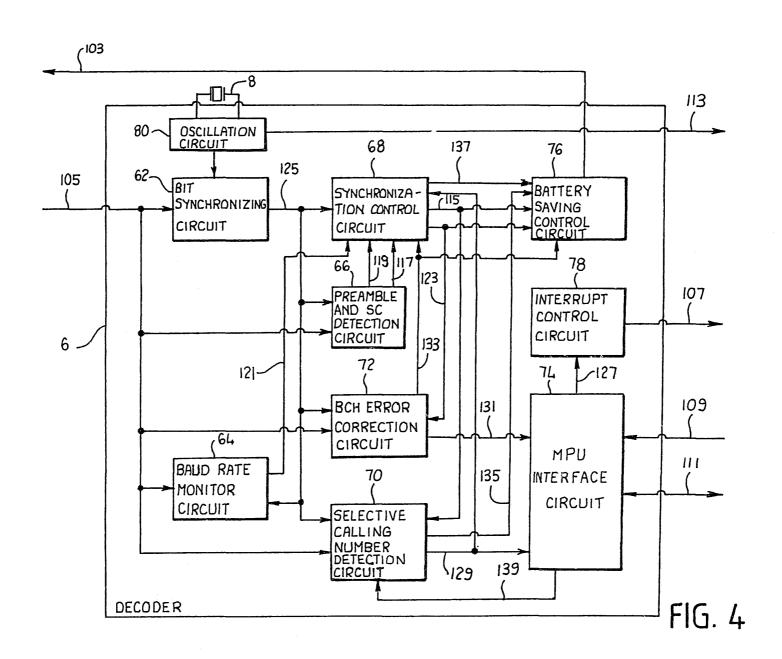

FIG. 4 is a block diagram of a preferred embodiment of the decoder shown in FIG. 1;

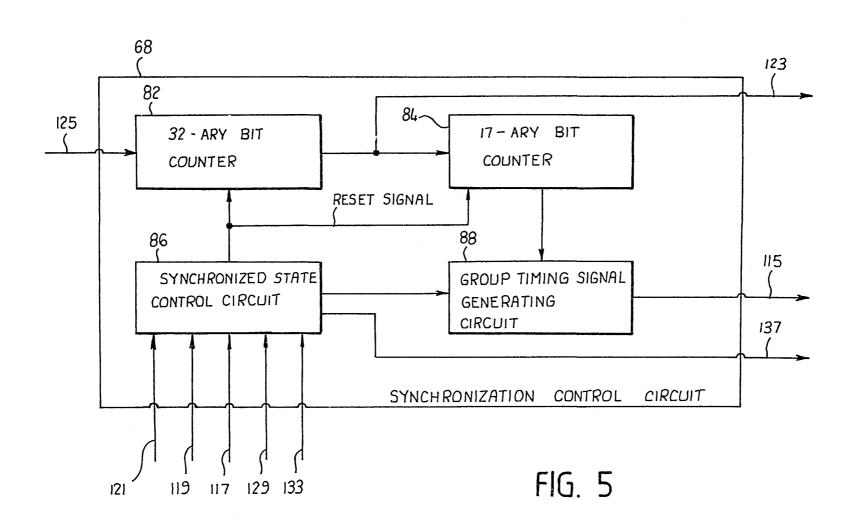

FIG. 5 is a block diagram of a preferred embodiment of the synchronization control circuit shown in FIG. 4; and

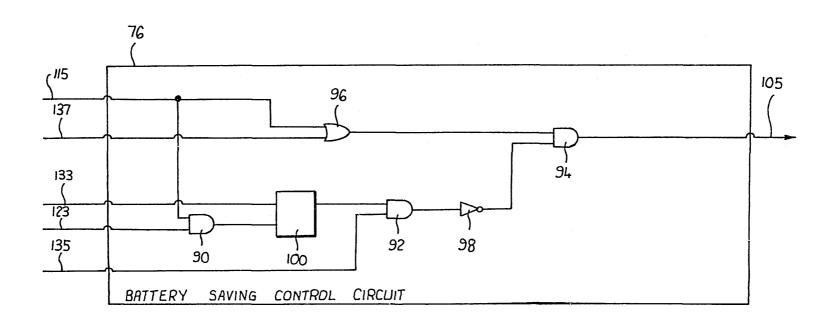

FIG. 6 is a block diagram of a preferred embodiment of the battery saving control circuit shown in FIG. 4.

10

15

20

In the drawings, the same reference numerals denote the same structural elements.

#### DESCRIPTION OF THE PREFERRED EMBODIMENT

Now a preferred embodiment of the present invention will be described in detail with reference to FIGs. 1 to 6.

FIG. 1 is a block diagram of a preferred embodiment of the A modulated signal 101 received from an present invention. antenna 2 is demodulated in a radio section 4. The radio section 4 carries out intermittent receiving operation in accordance with a battery saving control signal 103 of a decoder 6. microprocessor (referred to as MPU hereinafter) 10 reads a selective calling number or an identification number (ID) of the receiver itself set in advance in an EEPROM 16, and sends the selective calling number to the decoder 6 using an address bus The decoder 6 compares the selective calling number from the EEPROM 16 with a signal 105 demodulated in the radio section 4, and informs the MPU 10 of the detection of the selective calling number using an MPU interface, namely, an interrupt signal 107, the address bus 109 and a data bus 111, if the result of the comparison shows coincidence.

10

15

FIGS. 2(a) to 2(c) illustrate a signal format, proposed by a post office code standardization advisory group (POCSAG), which is used with the present invention. In FIG. 2(a), the POCSAG signal format is constituted of a preamble signal which is a repeat signal of "1" and "0" and which consists of 576 bits, and a plurality of batches each consisting of a synchronizing signal SC and a plurality of lines of code words including a selective

calling signal, a message signal and the like. As shown in FIG. 2(b), the batch is divided into the SC and a group of eight frames, where each group comprises two code words. Each code word has 21 bits of information, 10 check bits for check and a parity bit as shown in FIG. 2(c).

Returned to FIG. 1, after the coincidence of the selective calling number, error correction of data, such as the check bits, sent following the selective calling signal is carried out, and transfers the information bits to MPU 10 using the MPU interface for every code word.

10

15

The MPU 10 receives the detection information on the selective calling number from the decoder 6, and stores the detection information in a RAM within MPU or an external RAM 18. If thereafter signals are sent continuously from the decoder 6, the MPU 10 judges whether the signals are a piece of message information signals or the selective calling number, and the piece of the message information signals are stored in the buffer area of the RAM within MPU or within the external RAM 18 if they represent a piece of the message information signals. operation is processed by MPU 10 using an oscillator 8 as the operating clock. If the signals turn out to be the selective calling number, signal acquisition is stopped at that moment, an MPU operating clock of an oscillator 12 is actuated, and the signals accumulated so far in the buffer are processed using the MPU operating clock 12 to be converted to a message, for example, character data and the signals are stored in the message memory area within the external RAM 18.

After completion of message signal reception, MPU 10 notifies the user of the receiver of the arrival of a call by driving a speaker 24, an LED 26 or a vibrator 28 via a driver 22, and displays the contents of the received message on an LCD 14. Which one of the speaker 24, LED 26 and vibrator 28 is to be used for the notification is set before hand in the EEPROM 16, and is determined by the combination of a piece of information and the setting of a function switch 20.

5

10

15

The message stored in the RAM within MPU or in the external RAM 18 can be displayed again on the LCD 14 by means of the function switch 20.

FIGs. 3(a) to 3(d) illustrate a received signal and a timing chart of battery saving operation according to the present invention. In FIG. 3(a), hatched parts are pre-assigned groups each of which consists of two code words.

FIG. 3(b) illustrates a timing chart of the timings of the battery saving control signal 103 which carries out the message receiving operation of the radio section 4, decoder 6 and MPU 10. After the preamble signal is detected and then the synchronizing signal SC is detected, the radio section is turned on exclusively at the timings of the code words of the group which is assigned to its own receiver, preferably, is turned on before the timing of the group so as to receive the first bit of the group. Accordingly, the radio section is put to the off-state at the timings of the synchronizing signals SC that appear later. Moreover, during the reception of the code words of the group which is assigned to that receiver, the radio section is brought

to the off-state in the midst of the second code word as soon as the decoder detects that the own ID is not found.

Furthermore, when the receiver's ID is detected in the code word of the group which is assigned to the receiver, two code words are fully received by keeping the on-state as is, then MPU 10 reads the message signal from the decoder 6 at the timing of the interrupt signal 107 shown in FIG. 3(c), and stores the message signal in the buffer memory.

FIG. 3(d) illustrates the oscillation timings of the MPU operating clock of the oscillator 12. The high level in the time chart represents that the operating clock is oscillated there. With this timing, MPU 4 processes the message signal within the buffer memory using the MPU operating clock 12 as the working clock, and stores the message signal in the message memory as a character data.

10

15

Next, an example of circuiting for executing the abovementioned battery saving operation according to the present invention will be described in detail with reference to FIGs. 4 to 6.

FIG. 4 is a block diagram of preferred embodiment of the decoder 6 shown in FIG. 1. A bit synchronizing circuit 62 generates a regenerated clock 125 using reference clock from an oscillator circuit 80 and the demodulated signal 105 from the radio section 4.

A Baud rate monitor circuit 64 compares the regenerated clock 125 with the demodulated signal 105 to decide whether it is a bit rate of a POCSAG signal to be received, and outputs a bit rate detection signal 121. It is used in actuating the

operation of a search for the SC signal from the battery saving operation in a state where a POCSAG signal is not being received, and can be used for releasing the battery saving operation even for a signal other than the preamble signal.

A preamble and SC detection circuit 66 generates a detection signal 117 which detects the preamble signal by sampling the demodulated signal 105 using the regenerated clock 125. As it detects the ensuing synchronizing signal SC, it generates a synchronization detection signal 119.

10

15

Α synchronization control circuit 68 controls the establishment/releasing of synchronization. In the state where a POCSAG signal is not being received, it is engaged in the battery saving operation for preamble search mode, and outputs a continuous reception signal 137 to keep the radio section in the receiving condition by receiving the preamble detection signal 117 or the bit rate detection signal 121. The circuit synchronization control 68 is brought the synchronizing state by the synchronization detection signal 119 to resume the battery saving operation for selective calling number search mode, and receives the selective calling number at the timings of the pre-assigned group. The synchronization control circuit 68 outputs a group timing signal 115 at the preassigned group and a word timing signal 123 during the synchronization state. In addition, the circuit 68 outputs the continuous reception signal 137 for receiving the ensuing message signal by receiving a coincidence detection signal 129 from a selective calling number detection circuit 70 to be described Further, the circuit 68 counts BCH error detection of

consecutive two code words in its own group by an error checking signal 133 from a BCH error correction circuit 72 to be described later, and goes over to the preamble search mode by releasing the synchronization state when a count reaches a predetermined level.

The selective calling code detection circuit 70 sequentially collates the received selective calling number with a preassigned selective calling number 139 via an MPU interface circuit 74 from the MPU 10 at the timings of the group timing signal 115 from the synchronization control circuit 68, and outputs coincidence detection signal 129 the synchronization control circuit 68 and an MPU interface circuit 74. If non-coincidence, preferably of more than two bits, is detected, the selective calling number detection circuit 70 immediately outputs a non-coincidence detection signal 135 to a battery saving control circuit 76.

10

15

The BCH error correction circuit 72 carries out error correction of the demodulated signal 105 at the timings of the word timing signal 123 from the synchronization control circuit 68, and outputs a message signal 131 to MPU 10 via the MPU interface circuit 74. In addition, it checks the errors in the code word received in the synchronization state, and outputs an error check signal 133 to the synchronization control circuit 68.

The MPU interface circuit 74 controls the MPU interface such as address bus 109 and data bus 111, and controls signal input/output for MPU 10.

The battery saving control circuit 76 holds for the duration of one word the error checking signal 133 of the BCH error correction circuit 72 at the timings of the group timing signal

115 and the word timing signal 123 from the synchronization control circuit 68. When the battery saving control circuit 76 receives the non-coincidence detection signal 135 for the selective calling number in the second word of its own group, it immediately turns off the power supply of the radio section 4 by controlling the battery saving control signal 103 if the held contents of the BCH check in the first word on its own group shows that an error was not detected.

An interrupt control circuit 78 outputs an interrupt signal 107 to the MPU 10 based on an interrupt request signal 127 from the MPU interface circuit 74 when there arose a change in data to be sent to MPU 10 or in the operating conditions. The oscillation circuit 80 generates the reference clock 113 by an oscillator 8.

10

15

FIG. 5 is a block diagram of a preferred embodiment of the synchronization control circuit 68 shown in FIG. 3. A 32-ary bit counter 82 counts the regenerated clock 125 from the bit synchronizing circuit 62 and generates the word timing signal 123 which determines the reference timing of one word. A 17-ary word counter 84 generates a timing signal for 17 words corresponded to 1 batch length. A self group timing signal generating circuit 88 generates a group timing signal 115 at the timing of the preassigned group after a predetermined term passed from a detection of synchronizing signal and at the timing of the pre-assigned group in the following batch after a detection of the selective calling number. For example, the self group timing signal generating circuit comprises a comparison circuit. The comparison circuit compares the value of the counter 84 with a

predetermined value showing a position of the group assigned to the receiver and generates the group timing signal when the values are coincident. A synchronized state control circuit 86 controls the synchronized state using the preamble detection signal 117, the bit rate detection signal 121, the synchronizing signal detection signal 119, the error checking signal 133 and the selective calling number coincidence detection signal 129 as the actuating signals, and generates the continuous reception signal 137 and a reset signal to the 32-ary and 17-ary bit counters 82 and 84 in response to the synchronizing signal detection signal 119.

10

15

FIG. 6 is a block diagram of a preferred embodiment of the battery saving control circuit 76 shown in FIG. 3. The circuit 76 consists of AND gates 90, 92 and 94, an OR gate 96, and an inverter 98 and a latch 100 for an error check signal holding The latch 100 latches the error checking signal 133 of the BCH error correction circuit 72 at the timing of the inputting of the self group timing signal 115 from synchronization control circuit 68 and the word timing signal 123, and holds the error checking signal 133 for the duration of If the non-coincidence detection signal 135 of the selective calling signal at the second word of its own group and the latched error checking signal are input to the AND gate 92, the circuit 76 immediately turns off the power supply of the radio section 4 at the second word of its own group by controlling the battery saving control signal 103 when the self group timing signal 115 or continuous reception signal 137 is supplied to the AND gate 94 via the OR gate 96.

Therefore, according to this selective calling receiver of the present invention, after the detection of the preamble and the synchronizing signal SC in the preamble and SC detection circuit 66, the bits in the selective calling number are sequentially compared with the pre-assigned selective calling number in the selective calling code detection circuit 70 exclusively at the timings of the groups, namely, the code words assigned to the receiver itself, by the synchronization control circuit 68. The selective calling number detection circuit 70 detects immediately selective calling number non-coincidence and outputs a number non-coincidence signal when there occurred noncoincidence of bits for a number of times that exceeds a predetermined level. Moreover, selective calling number coincidence is detected and a number coincidence signal is output when non-coincidence occurred only for a number of bits smaller than the predetermined level.

10

15

In the battery saving control circuit 76, the result of the block error checking output at the completion of one block of the error correction code and received by the BCH error correction circuit 72 is held for at least the duration of one block. The power supply for the radio section 4 is controlled in response to the error non-detection output of the error check output holding means issued in the preceding block, and the non-coincidence output in the block in question.

As described hereinbefore, since, according to the present invention, the radio section is turned on only in the frames or groups which are pre-assigned to the receiver, without turning the radio section on at the timings of the synchronizing signals

after the synchronizing signal is detected once, and the power supply for the receiving circuit is turned off immediately when its own ID is not found in the code words which

constitute the receiver's frame during the reception, it is possible to enhance the battery saving efficiency in comparison to the conventional system in which power is supplied during the entirety of each synchronizing signal and the two code words of the frame to which the receiver belongs. In this way, the battery line can be prolonged by reducing the average consumed current of the receiver.

Further, it becomes possible to use a small-sized battery which shows that the present invention has an effect of contributing to the miniaturization of the selective calling receiver.

10

15

Although the embodiment has been described with respect to a case in which the modification was based on a specific arrangement, it goes without saying that the present invention is not restricted to this case. The claims defining the invention are as follows:

1. A power supply control apparatus for a radio section of a receiver responsive to signals containing a preamble and multiple batches each batch containing a synchronizing signal and multiple codeword groups, said receiver being assigned to one of said groups, comprising:

means for preventing power application to said radio section at timings of synchronizing signal receptions after a detection of a first synchronizing signal; and means for turning on said radio section on detection of said first synchronizing signal, and at reception timings of the group assigned to said receiver.

2. The power supply control apparatus as claimed in claim 1, wherein each said group contains a selective calling number, said power supply control further comprising:

means for turning off said radio section when selective calling number in the receiver's assigned group is not the same as a selective calling number assigned to said receiver.

3. A power supply control apparatus for a receiver comprising: first detecting means for detecting a first synchronizing signal following a preamble signal in a received signal;

first control means for generating a first timing signal at the timing of each group assigned to said receiver within said received signal, and for turning a radio section in said receiver on in response to said first timing signals and for maintaining said radio section off at reception timings of synchronizing signals after said detection of said first synchronizing signal.

4. The power supply control apparatus as claimed in claim 3, wherein said received signal comprises said preamble and a plurality of batches, each batch consisting of said synchronizing signal and several groups which include first and second codeword blocks, further comprising:

second detecting means for detecting a selective calling number in one of said codeword blocks, said receiver being assigned a particular selective calling number;

error checking means for checking a block error in an error correction code received in said blocks; and

second control means for turning said radio section off in response to no detection of said particular selective calling number and a detection of a result of no block error.

5. The power supply control apparatus as claimed in claim 4, wherein said second control means comprises:

latching means for latching a result of said block error for one codeword block;

10

15

20

25

30

an AND gate for inputting said result of said block error and a signal indicating said detection of said particular selective calling number; and

5

10

15

20

30

35

supplying means for supplying a battery saving control signal to said radio section to turn off when said particular selective calling signal is not detected and no block error is detected.

- 6. The power supply control apparatus as claimed in claim 4, further comprising monitoring means for monitoring a bit rate of said received signal; and third control means for turning said radio section off when said bit rate of the received signal is different from a predetermined rate.

- 7. The power supply control apparatus as claimed in claim 3, further comprising first generating means for generating a regenerated clock based on a reference clock and said received signal and for supplying said regenerated clock to said first detecting means and said first control means as an operation clock.

- 8. The power supply control apparatus as claimed in claim 7, wherein said received signal comprises said preamble and a plurality of batches, each batch consisting of said synchronizing signal and several groups which include first and second codeword blocks, said first control means comprises:

second generating means for generating a second timing signal at a timing of each said group based on said regenerated clock and said detection of said first synchronizing signal; and

third generating means for generating said first timing signal in response to said second timing signal.

- 9. The power supply control apparatus as claimed in claim 3, wherein said first control means turns said radio section on before the reception timings of said assigned groups.

- 10. A method for controlling a power supply to a radio section in a receiver, the method comprising the steps of:

detecting a first synchronizing signal followed a preamble signal in a received signal;

generating a first timing signal at the timing of groups assigned to said receiver within said received signal;

turning a radio section in said receiver on in response to said first timing signal; and

keeping said radio section off at reception timings of synchronizing signals after said detection of said first synchronizing signal.

11. A method for controlling a power supply for a receiver turning a radio section on at reception timings of necessary parts in a received signal, the method comprising the steps of:

keeping said radio section off at timings of reception of synchronizing signals after a detection of a first synchronizing signal; and

turning said radio section on, based on said detection of the first synchronizing signal, at reception timings of assigned groups included in said received signal.

- 12. A decoder substantially as described herein with reference to Figs. 4, 5 and 6 of the accompanying drawings.

- 13. A receiver substantially as described herein with reference to Figs. 1 to 6 of the accompanying drawings.

DATED this Thirteenth Day of December 1996

NEC Corporation

Patent Attorneys for the Applicant

SPRUSON & FERGUSON

# Power Supply Control for a Receiver Abstract

A synchronization controller identifies the timing of the group assigned to the receiver based on a synchronization signal detected by a preamble and synchronization signal detector. At this timing the power supply of a radio section (4) is turned on. A selective calling number within the received group and preassigned selective calling number are compared in a selective calling number detector (6). The power supply of the radio section (4) is immediately turned off, if the result of the comparision is non-coincidence. In this way, the battery saving efficiency can be enhanced by arranging to turn on the radio section (4) only in the groups which are assigned to the receiver, and turning off immediately the power supply of the radio section when the receiver's assigned selective calling number is not found in the receiver's assigned 15 group.

(Fig. 1)

FIG. 6