(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5661990号

(P5661990)

(45) 発行日 平成27年1月28日(2015.1.28)

(24) 登録日 平成26年12月12日(2014.12.12)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 21/02 (2006.01)  | HO 1 L 27/12 B       |

| HO 1 L 27/12 (2006.01)  | HO 1 L 21/265 F      |

| HO 1 L 21/265 (2006.01) | HO 1 L 21/265 Q      |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 2 7 D |

| HO 1 L 29/786 (2006.01) | HO 5 B 33/02         |

請求項の数 7 (全 27 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-109391 (P2008-109391)  |

| (22) 出願日     | 平成20年4月18日 (2008.4.18)        |

| (65) 公開番号    | 特開2008-288579 (P2008-288579A) |

| (43) 公開日     | 平成20年11月27日 (2008.11.27)      |

| 審査請求日        | 平成23年4月4日 (2011.4.4)          |

| (31) 優先権主張番号 | 特願2007-112432 (P2007-112432)  |

| (32) 優先日     | 平成19年4月20日 (2007.4.20)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 大沼 英人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 飯窪 陽一<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 佐藤 崇佳<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

審査官 右田 勝則

最終頁に続く

(54) 【発明の名称】 SOI 基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

質量の異なる複数種の水素イオンを半導体基板の一表面から導入して、前記半導体基板の表面から前記質量の異なる複数種の水素イオンの平均進入深さに近い深さ領域に分離層を形成し、

前記半導体基板に接合層を形成し、

前記半導体基板と、ガラス基板とを、前記接合層を挟んで重ね合わせた状態で、前記分離層に亀裂を生じさせ、前記ガラス基板上に半導体層を残存させつつ、前記半導体基板を前記分離層で分離する第1の熱処理を行い、

前記半導体層が接合された前記ガラス基板に、前記第1の熱処理温度以上の温度で第2の熱処理を行い、

前記第1の熱処理の温度は、400以上600未満であり、

前記第2の熱処理の温度は、前記第1の熱処理の温度以上であって、かつ前記ガラス基板の歪み点以下の温度であり、

前記質量の異なる複数種の水素イオンは、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ イオンであり、

前記質量の異なる複数種の水素イオンのうち、 $H_3^+$ イオンの割合が他のイオン種の割合よりも大きいことを特徴とするSOI基板の製造方法。

## 【請求項 2】

半導体基板に酸化シリコン層を形成し、

質量の異なる複数種の水素イオンを前記酸化シリコン層の一表面から前記半導体基板に

10

20

導入して、前記半導体基板の表面から前記質量の異なる複数種の水素イオンの平均進入深さに近い深さ領域に分離層を形成し、

ガラス基板にバリア層を形成し、

前記バリア層上に接合層を形成し、

前記半導体基板の前記酸化シリコン層と、前記ガラス基板の前記接合層とを、密着させた状態で、前記分離層に亀裂を生じさせ、前記ガラス基板上に半導体層を残存させつつ、前記半導体基板を前記分離層で分離する第1の熱処理を行い、

前記半導体層が接合された前記ガラス基板に、前記第1の熱処理温度以上の温度で第2の熱処理を行い、

前記第1の熱処理の温度は、400以上600未満であり、

10

前記第2の熱処理の温度は、前記第1の熱処理の温度以上であって、かつ前記ガラス基板の歪み点以下の温度であり、

前記質量の異なる複数種の水素イオンは、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ イオンであり、

前記質量の異なる複数種の水素イオンのうち、 $H_3^+$ イオンの割合が他のイオン種の割合よりも大きいことを特徴とするSOI基板の製造方法。

#### 【請求項3】

請求項2において、

前記バリア層は、複数の層から構成されることを特徴とするSOI基板の製造方法。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

20

前記接合層は、酸化シリコン膜であることを特徴とするSOI基板の製造方法。

#### 【請求項5】

請求項4において、

前記酸化シリコン膜を、有機シランガスを用いて化学気相成長法により形成することを特徴とするSOI基板の製造方法。

#### 【請求項6】

請求項5において、

前記有機シランガスが、珪酸エチル(TEOS: Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、テトラメチルシラン(TMS: Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMC-TS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)から選ばれた一種を用いることを特徴とするSOI基板の製造方法。

30

#### 【請求項7】

請求項1乃至請求項6のいずれか一項において、

前記ガラス基板の歪み点は、580以上680未満であることを特徴とするSOI基板の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

40

結晶系半導体基板から半導体層を薄片化して異種基板に接合するSOI構造を有する基板に関する。特に貼り合わせSOI技術に関するものであって、ガラス等の絶縁表面を有する基板に単結晶若しくは多結晶の半導体層を接合させたSOI基板の製造方法に関する。また、このようなSOI構造を有する基板を用いる表示装置若しくは半導体装置に関する。

#### 【背景技術】

#### 【0002】

単結晶半導体のインゴットを薄く切断して作製されるシリコンウエハーに代わり、絶縁層の上に薄い単結晶半導体層を設けたシリコン・オン・インシュレータと呼ばれる半導体基板(SOI基板)が開発されており、マイクロプロセッサなどを製造する際の基板として

50

普及しつつある。これは、SOI基板を使った集積回路はトランジスタのドレインと基板間ににおける寄生容量を低減し、半導体集積回路の性能を向上させ、低消費電力化を図るものとして注目されているからである。

#### 【0003】

SOI基板を製造する方法としては、水素イオン注入剥離法が知られている（例えば、特許文献1参照）。水素イオン注入剥離法は、シリコンウエハーに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面とすることで、別のシリコンウエハーに薄いシリコン層（SOI層）を接合する。さらにSOI層を剥離する熱処理を行うことに加え、酸化性雰囲気下での熱処理によりSOI層に酸化膜を形成した後に該酸化膜を除去し、次に1000乃至1300の還元性雰囲気下で熱処理を行って接合強度を高める必要があるとされている。

10

#### 【0004】

一方、ガラスなどの絶縁基板にSOI層を形成しようとする試みもなされている。ガラス基板上にSOI層を形成したSOI基板の一例として、水素イオン注入剥離法を用いて、コーティング膜を有するガラス基板上に薄い単結晶シリコン層を形成したものが知られている（特許文献2参照）。この場合にも、単結晶シリコン片に水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、ガラス基板と単結晶シリコン片を張り合わせ後に、微小気泡層を劈開面としてシリコン片を剥離することで、ガラス基板上に薄いシリコン層（SOI層）を形成している。

20

【特許文献1】米国特許第6372609号

【特許文献2】米国特許第7119365号

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

水素イオン注入剥離法によって、単結晶シリコン層をシリコンウエハーから剥離するためには600以上の高温で熱処理をする必要があった。しかし、基板コストを下げるために液晶パネルなどで使われるガラス基板に単結晶シリコンを接合させてSOI基板を形成する場合、このような高温で熱処理をすると、ガラス基板が反ってしまうという問題が生じていた。ガラス基板が反ってしまうと、単結晶シリコン層との接合強度の低下が懸念される。また、単結晶シリコン層に歪み応力が加わり、トランジスタの特性に悪影響を与えるといった問題もある。すなわち、従来の技術では、ガラス基板上に単結晶シリコン層を設け、その単結晶シリコン層でトランジスタを作製しても、十分な特性を出すことが出来なかつた。

30

#### 【0006】

このような問題点に鑑み、ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる結晶半導体層を備えたSOI基板を提供することを目的のーとする。また、そのようなSOI基板を用いた半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

絶縁表面を有する支持基板へその歪み点以下の温度で単結晶半導体を接合することを要旨とする。この単結晶半導体層は複数回の熱処理工程を経て形成される。

40

#### 【0008】

単結晶又は多結晶半導体基板の表面からある深さの領域に分離層を形成し、該分離層上の半導体層を支持基板と接合させて剥離する際に第1の熱処理を行う。その後、半導体層が接合された支持基板に対して第2の熱処理を行う。第1の熱処理と第2の熱処理は異なる温度で行うことが好ましい。この場合、第1の熱処理の温度に対し第2の熱処理は、その温度よりも高い温度であって半導体層を接合する基板の歪み点温度を超えない温度で行うことが好ましい。或いは、同じ温度であっても第2の熱処理の処理時間を長くしても良い。

#### 【0009】

50

単結晶又は多結晶半導体基板の表面から所定の深さに設けられる分離層は、加速されたイオンを当該半導体基板の表面から導入することにより形成される。導入されるべきイオンは、一の原子から成るイオン又は同一の原子から成り質量の異なる複数種のイオンを含ませることが好ましい。例えば、所定のガスをプラズマ化することにより複数のイオン種を生成し、それらのイオン種を質量分離することなく電界で加速して単結晶又は多結晶半導体基板に導入する。代表的には水素イオンが選択され、同一の原子から成り質量の異なる複数種のイオンとして  $H^+$ 、 $H_2^+$ 、 $H_3^+$  イオンが適用される。この場合において、 $H_3^+$  イオンの割合が他のイオン種よりも高くすることが好ましい。

#### 【0010】

支持基板へ単結晶又は多結晶半導体基板から薄片分離された半導体層を固定するに際し、接合を形成する面の一方又は双方に平滑面を有し親水性表面を形成する層を接合面として設ける。このような層として、代表的には酸化シリコン層が適用される。この酸化シリコン膜は、熱酸化、化学反応又は化学気相成長法により形成されるものであることが好ましい。

10

#### 【発明の効果】

#### 【0011】

単結晶又は多結晶半導体基板から分離された結晶性半導体層を支持基板へ接合する際に、複数の熱処理を行うことにより結晶性に優れた SOI 構造を有する基板を得ることができる。支持基板と接合される結晶半導体層とが、歪み点や熱膨張係数など熱的特性が異なる場合においても、接合を形成する熱処理と、その後の熱処理を異なる温度及び / 又は異なる処理時間で行うことで、歪みが緩和され結晶性に優れた SOI 基板を得ることができる。

20

#### 【発明を実施するための最良の形態】

#### 【0012】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。

30

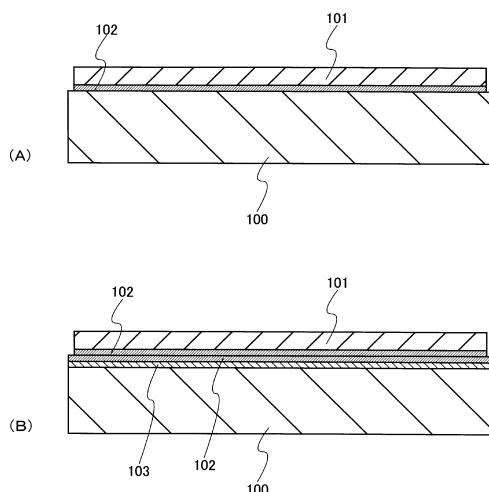

#### 【0013】

本形態に係る SOI 構造を有する基板を図 1 (A) (B) に示す。図 1 (A) において支持基板 100 は絶縁性を有するもの又は絶縁表面を有するものであり、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板（「無アルカリガラス基板」とも呼ばれる）が適用される。すなわち、熱膨張係数が  $25 \times 10^{-7} /$  から  $50 \times 10^{-7} /$  (好ましくは、 $30 \times 10^{-7} /$  から  $40 \times 10^{-7} /$ ) であって歪み点が 580 から 680 (好ましくは、600 から 680) のガラス基板を適用することができる。その他に石英基板、セラミック基板、表面が絶縁膜で被覆された金属基板などのも適用可能である。

#### 【0014】

単結晶半導体層 101 は、代表的には単結晶シリコンが適用される。その他に、水素イオン注入剥離法のようにして単結晶半導体基板若しくは多結晶半導体基板から剥離可能であるシリコン、ゲルマニウム、その他、ガリウムヒ素、インジウムリンなどの化合物半導体による単結晶半導体若しくは多結晶半導体に置き換えることもできる。

40

#### 【0015】

支持基板 100 と単結晶半導体層 101 の間には、平滑面を有し親水性表面を形成する接合層 102 を設ける。この接合層 102 は平滑面を有し親水性表面を有する層とする。このような表面を形成可能なものとして、化学的な反応により形成される絶縁層が好ましい。例えば、熱的又は化学的な反応により形成される酸化膜が適している。主として化学的な反応により形成される膜であれば表面の平滑性を確保できるからである。平滑面を有し親水性表面を形成する接合層 102 は 0.2 nm 乃至 500 nm の厚さで設けられる。こ

50

の厚さであれば、被成膜表面の表面荒れを平滑化すると共に、当該膜の表面の平滑性を確保することが可能である。

【0016】

単結晶半導体層101がシリコンによるものであれば、酸化性雰囲気下において熱処理により形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを接合層102とすることができます。接合層102としてケミカルオキサイドを用いる場合には0.2nmから1nmの厚さであれば良い。また、好適には化学気相成長法により堆積される酸化シリコンを接合層102とすることができます。この場合、有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。有機シランガスとしては、珪酸エチル(TEOS:Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、テトラメチルシラン(TMS:Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OC<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

【0017】

接合層102は単結晶半導体層101側に設けられ、支持基板100の表面と密接することで、室温であっても接合をすることが可能である。より強固に接合を形成するには、支持基板100と単結晶半導体層101を押圧すれば良い。異種材料である支持基板100と接合層102を接合するには表面を清浄化する。支持基板100と接合層102の互いに清浄化された表面を密接させると表面間引力により接合が形成される。さらに表面に多数の親水基を付着させるとより好ましい態様となる。例えば、支持基板100の表面を酸素プラズマ処理若しくはオゾン処理して親水性にすることが好ましい。このように表面を親水性にする処理を加えた場合には、表面の水酸基が作用して水素結合により接合が形成される。さらに清浄化された表面同士を密接させて接合を形成したものに対して、室温以上の温度で加熱すると接合強度高めることができる。

【0018】

異種材料である支持基板100と接合層102を接合するための処理として、接合を形成する表面にアルゴンなどの不活性ガスによるイオンビームを照射して清浄化しても良い。イオンビームの照射により、支持基板100若しくは接合層102の表面に未結合種が露呈して非常に活性な表面が形成される。このように活性化された表面同士を密接させると低温でも接合を形成することが可能である。表面を活性化して接合を形成する方法は、当該表面を高度に清浄化しておくことが要求されるので、真空中で行うことが好ましい。

【0019】

単結晶半導体層101は結晶半導体基板を薄片化して形成されるものである。例えば、単結晶半導体層101は、単結晶半導体基板の所定の深さに水素イオン又はフッ素イオンを導入し、その後熱処理を行って、表層の単結晶シリコン層を剥離することで形成される。また、ポーラスシリコン上に単結晶シリコンをエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。単結晶半導体層101の厚さは5nm乃至500nm、好ましくは10nm乃至200nmの厚さである。

【0020】

図1(B)は支持基板100にバリア層103と接合層102を設けた構成を示す。バリア層103を設けることで、支持基板100として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散して単結晶半導体層101が汚染されることを防ぐことができる。バリア層103上には接合層102を設けることが好ましい。支持基板100において、不純物の拡散を防止するバリア層103と接合強度を確保する接合層102とによる機能が異なる複数の層を設けることにより、支持基板の選択範囲を広げることができる。単結晶半導体層101側にも接合層102を設けておくことが好ましい。すなわち、支持基板100に単結晶半導体層101を接合するに際し

10

20

30

40

50

、接合を形成する面の一方若しくは双方に接合層 102 を設けることが好ましく、それにより接合強度を高めることができる。

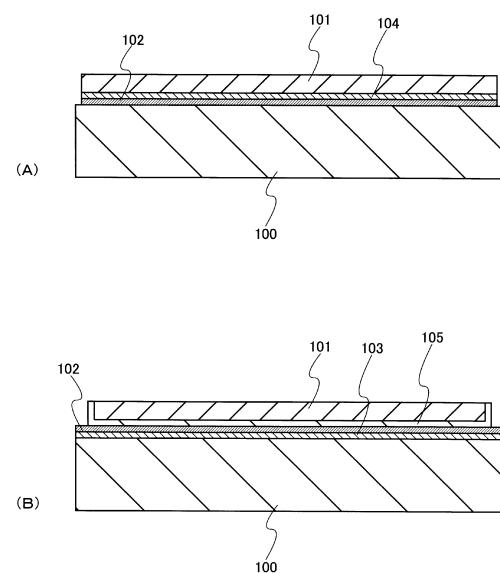

【0021】

図2(A)は単結晶半導体層 101 と接合層 102 の間に絶縁層 104 を設けた構成を示す。絶縁層 104 は窒素を含有する絶縁層であることが好ましい。例えば、窒化シリコン膜、窒化酸化シリコン膜若しくは酸化窒化シリコン膜から選ばれた一又は複数の膜を積層して形成することができる。例えば、単結晶半導体層 101 側から酸化窒化シリコン膜、窒化酸化シリコン膜を積層する絶縁層 104 とすることができる。接合層 102 が支持基板 100 と接合を形成する機能を有するのに対し、絶縁層 104 は不純物により単結晶半導体層 101 が汚染されることを防止する。

10

【0022】

なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (RBS: Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS: Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 15 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、Si が 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

20

【0023】

図2(B)は支持基板 100 に接合層 102 を設けた構成である。支持基板 100 と接合層 102 との間にはバリア層 103 が設けられていることが好ましい。支持基板 100 として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散して単結晶半導体層 101 が汚染されることを防ぐためである。単結晶半導体層 101 には直接酸化で形成された酸化シリコン層 105 が形成されている。この酸化シリコン層 105 が接合層 102 と接合を形成し、支持基板 100 上に単結晶半導体層 101 を固定する。酸化シリコン層 105 は熱酸化により形成されたものが好ましい。

30

【0024】

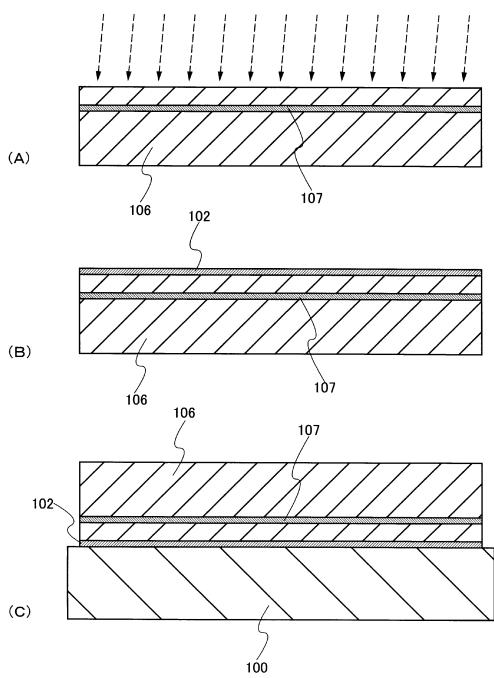

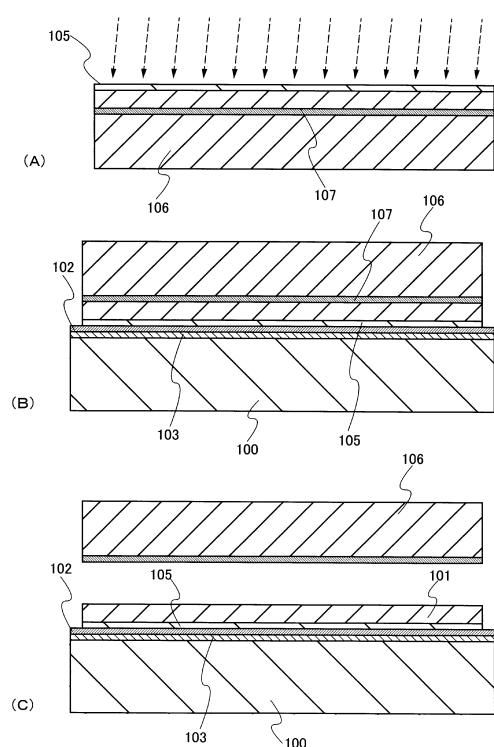

このような SOI 構造を有する基板の製造方法について図3と図4を参照して説明する。

【0025】

清浄化された半導体基板 106 の表面から電界で加速されたイオンを所定の深さに導入して分離層 107 を形成する(図3(A)参照)。半導体基板 106 に形成される分離層 107 の深さは、イオンの加速エネルギーとイオンの入射角によって制御する。半導体基板 106 の表面からイオンの平均進入深さに近い深さ領域に分離層 107 が形成される。例えば、単結晶半導体層の厚さは 5 nm 乃至 500 nm、好ましくは 10 nm 乃至 200 nm の厚さであり、イオンを導入する際の加速電圧はこのような厚さを考慮して行われる。イオンの導入はイオンドーピング装置を用いて行うことが好ましい。すなわち、ソースガスをプラズマ化して生成された複数のイオン種を質量分離しないで導入するドーピング方式を用いる。本形態の場合、一の原子から成るイオン又は同一の原子から成り質量の異なる複数種のイオンを導入することが好ましい。イオンドーピングは、加速電圧 10 kV から 100 kV、好ましくは 30 kV から 80 kV、ドーズ量は  $1 \times 10^{16}$  ions/cm<sup>2</sup> から  $4 \times 10^{16}$  ions/cm<sup>2</sup>、ビーム電流密度が 2  $\mu$ A/cm<sup>2</sup> 以上、好ましくは 5  $\mu$ A/cm<sup>2</sup> 以上、より好ましくは 10  $\mu$ A/cm<sup>2</sup> 以上とすれば良く、イオンの導入によって半導体層に生成される欠陥を低減することができる。

40

【0026】

水素イオンを導入する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup> イオンを含ませると共に、H<sub>3</sub><sup>+</sup> イオンの割合を高めておくことが好ましい。水素イオンを導入する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>

50

$H_3^+$ 、 $H_3^+$ イオンを含ませると共に、 $H_3^+$ イオンの割合を高めておくと単位時間当たりに半導体基板に導入できる水素原子の数が増加するので、イオンの導入に要する時間を短縮できる。それにより、半導体基板 106 に形成される分離層 107 の領域には  $1 \times 10^{20} \text{ atoms/cm}^3$  (好ましくは  $5 \times 10^{20} \text{ atoms/cm}^3$ ) 以上の水素を含ませることが可能である。半導体基板 106 中において、局所的に高濃度の水素が導入された領域を形成すると、結晶構造が乱されて微小な空孔が形成され、分離層 107 を多孔質構造とすることができる。この場合、比較的低温の熱処理によって分離層 107 に形成された微小な空洞の体積変化が起り、分離層に沿って劈開することにより薄い単結晶半導体層を形成することができる。

## 【0027】

10

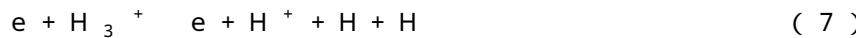

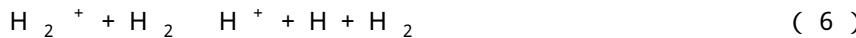

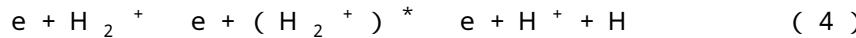

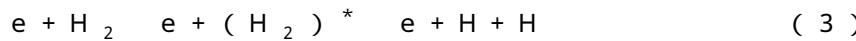

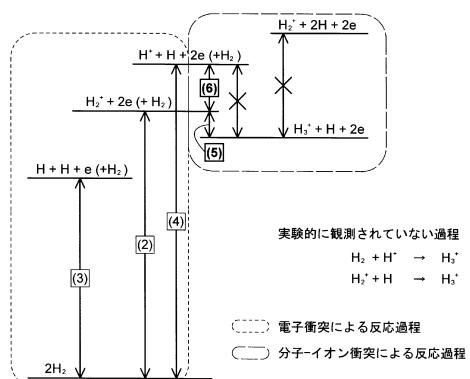

ここで、水素プラズマにより生成される  $H^+$ 、 $H_2^+$ 、 $H_3^+$ イオンについて概説する。各水素イオン種の反応過程 (生成過程、消滅過程) は、以下に示す反応式で説明される。

## 【0028】

## 【0029】

図 17 に、上記の反応の一部を模式的に表したエネルギーダイアグラムを示す。なお、図 17 に示すエネルギーダイアグラムは模式図に過ぎず、反応に係るエネルギーの関係を厳密に規定するものではない点に留意されたい。

## 【0030】

(  $H_3^+$  の生成過程 )

上記のように、 $H_3^+$ は、主として反応式 (5) により表される反応過程により生成される。一方で、反応式 (5) と競合する反応として、反応式 (6) により表される反応過程が存在する。 $H_3^+$ が増加するためには、少なくとも、反応式 (5) の反応が、反応式 (6) の反応より多く起こる必要がある (なお、 $H_3^+$ が減少する反応としては他にも (7)、(8)、(9) が存在するため、(5) の反応が (6) の反応より多いからといって、必ずしも  $H_3^+$ が増加するとは限らない。)。反対に、反応式 (5) の反応が、反応式 (6) の反応より少ない場合には、プラズマ中における  $H_3^+$ の割合は減少する。

30

## 【0031】

上記反応式における右辺 (最右辺) の生成物の増加量は、反応式の左辺 (最左辺) で示す原料の密度や、その反応に係る速度係数などに依存している。ここで、 $H_2^+$ の運動エネルギーが約 11 eV より小さい場合には (5) の反応が主要となり (すなわち、反応式 (5) に係る速度係数が、反応式 (6) に係る速度係数と比較して十分に大きくなり)、 $H_2^+$ の運動エネルギーが約 11 eV より大きい場合には (6) の反応が主要となることが実験的に確認されている。

40

## 【0032】

荷電粒子は電場から力を受けて運動エネルギーを得る。該運動エネルギーは、電場によるポテンシャルエネルギーの減少量に対応している。例えば、ある荷電粒子が他の粒子と衝突するまでの間に得る運動エネルギーは、その間に通過した電位差分のポテンシャルエネルギーに等しい。つまり、電場中において、他の粒子と衝突することなく長い距離を移動できる状況では、そうではない状況と比較して、荷電粒子の運動エネルギー (の平均) は大きくなる傾向にある。このような、荷電粒子に係る運動エネルギーの増大傾向は、粒子の平均自由行程が大きい状況、すなわち、圧力が低い状況で生じ得る。

50

## 【0033】

また、平均自由行程が小さくとも、その間に大きな運動エネルギーを得ることができる状況であれば、荷電粒子の運動エネルギーは大きくなる。すなわち、平均自由行程が小さくとも、電位差が大きい状況であれば、荷電粒子の持つ運動エネルギーは大きくなると言える。

## 【0034】

これを  $H_2^+$  に適用してみる。プラズマの生成に係るチャンバー内のように電場の存在を前提とすれば、該チャンバー内の圧力が低い状況では  $H_2^+$  の運動エネルギーは大きくなり、該チャンバー内の圧力が高い状況では  $H_2^+$  の運動エネルギーは小さくなる。つまり、チャンバー内の圧力が低い状況では(6)の反応が主要となるため、 $H_3^+$  は減少する傾向となり、チャンバー内の圧力が高い状況では(5)の反応が主要となるため、 $H_3^+$  は増加する傾向となる。また、プラズマ生成領域における電場(又は電界)が強い状況、すなわち、ある二点間の電位差が大きい状況では  $H_2^+$  の運動エネルギーは大きくなり、反対の状況では、 $H_2^+$  の運動エネルギーは小さくなる。つまり、電場が強い状況では(6)の反応が主要となるため  $H_3^+$  は減少する傾向となり、電場が弱い状況では(5)の反応が主要となるため、 $H_3^+$  は増加する傾向となる。

## 【0035】

## (イオン源による差異)

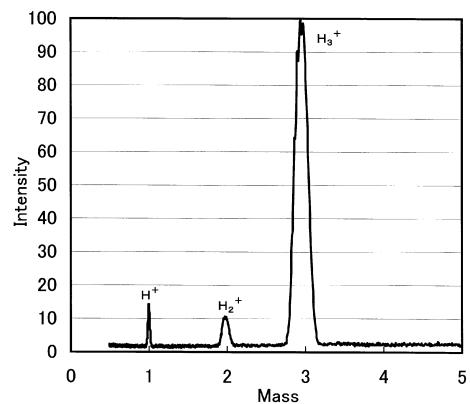

ここで、イオン種の割合(特に  $H_3^+$  の割合)が異なる例を示す。図18は、100%水素ガス(イオン源の圧力:  $4.7 \times 10^{-2}$  Pa)から生成されるイオンの質量分析結果を示すグラフである。なお、上記質量分析は、イオン源から引き出されたイオンを測定することにより行った。横軸はイオンの質量である。スペクトル中、質量1、2、3のピークは、それぞれ、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ に対応する。縦軸は、スペクトルの強度であり、イオンの数に対応する。図18では、質量が異なるイオンの数量を、質量3のイオンを100とした場合の相対比で表している。図18から、上記イオン源により生成されるイオンの割合は、 $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  程度となることが分かる。なお、このような割合のイオンは、プラズマを生成するプラズマソース部(イオン源)と、当該プラズマからイオンビームを引き出すための引出電極などから構成されるイオンドーピング装置によっても得ることが出来る。

## 【0036】

図19は、図18とは異なるイオン源を用いた場合であって、イオン源の圧力がおよそ  $3 \times 10^{-3}$  Pa の時に、PH<sub>3</sub>から生成したイオンの質量分析結果を示すグラフである。上記質量分析結果は、水素イオン種に着目したものである。また、質量分析は、イオン源から引き出されたイオンを測定することにより行った。図18と同様、横軸はイオンの質量を示し、質量1、2、3のピークは、それぞれ  $H^+$ 、 $H_2^+$ 、 $H_3^+$ に対応する。縦軸はイオンの数量に対するスペクトルの強度である。図19から、プラズマ中のイオンの割合は  $H^+ : H_2^+ : H_3^+ = 37 : 56 : 7$  程度であることが分かる。なお、図19はソースガスがPH<sub>3</sub>の場合のデータであるが、ソースガスとして100%水素ガスを用いたときも、水素イオン種の割合は同程度になる。

## 【0037】

図19のデータを得たイオン源の場合には、 $H^+$ 、 $H_2^+$  及び  $H_3^+$  のうち、 $H_3^+$  が7%程度しか生成されていない。他方、図18のデータを得たイオン源の場合には、 $H_3^+$  の割合を50%以上(上記の条件では80%程度)とすることが可能である。これは、上記考察において明らかになったチャンバー内の圧力及び電場に起因するものと考えられる。

## 【0038】

(  $H_3^+$  の照射メカニズム)

図18のような複数のイオン種を含むプラズマを生成し、生成されたイオン種を質量分離しないで単結晶半導体基板に照射する場合、単結晶半導体基板の表面には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$  の各イオンが照射される。イオンの照射からイオン導入領域形成にかけてのメカ

10

20

30

40

50

ニズムを再現するために、以下の5種類のモデルを考える。

1. 照射されるイオン種が  $H^+$  で、照射後も  $H^+$  ( $H$ ) である場合

2. 照射されるイオン種が  $H_2^+$  で、照射後も  $H_2^+$  ( $H_2$ ) のままである場合

3. 照射されるイオン種が  $H_2^+$  で、照射後に2個の  $H$  ( $H^+$ ) に分裂する場合

4. 照射されるイオン種が  $H_3^+$  で、照射後も  $H_3^+$  ( $H_3$ ) のままである場合

5. 照射されるイオン種が  $H_3^+$  で、照射後に3個の  $H$  ( $H^+$ ) に分裂する場合。

#### 【0039】

(シミュレーション結果と実測値との比較)

上記のモデルを基にして、水素イオン種を  $Si$  基板に照射する場合のシミュレーションを行った。シミュレーション用のソフトウェアとしては、SRIM (the Stopping and Range of Ions in Matter: モンテカルロ法によるイオン導入過程のシミュレーションソフトウェア、TRIM (the Transport of Ions in Matter) の改良版) を用いている。なお、計算の関係上、モデル2では  $H_2^+$  を質量2倍の  $H^+$  に置き換えて計算した。また、モデル4では  $H_3^+$  を質量3倍の  $H^+$  に置き換えて計算した。さらに、モデル3では  $H_2^+$  を運動エネルギー  $1/2$  の  $H^+$  に置き換え、モデル5では  $H_3^+$  を運動エネルギー  $1/3$  の  $H^+$  に置き換えて計算を行った。

10

#### 【0040】

なお、SRIMは非晶質構造を対象とするソフトウェアではあるが、高エネルギー、高ドーズの条件で水素イオン種を照射する場合には、SRIMを適用可能である。水素イオン種と  $Si$  原子の衝突により、 $Si$  基板の結晶構造が非単結晶構造に変化するためである。

20

#### 【0041】

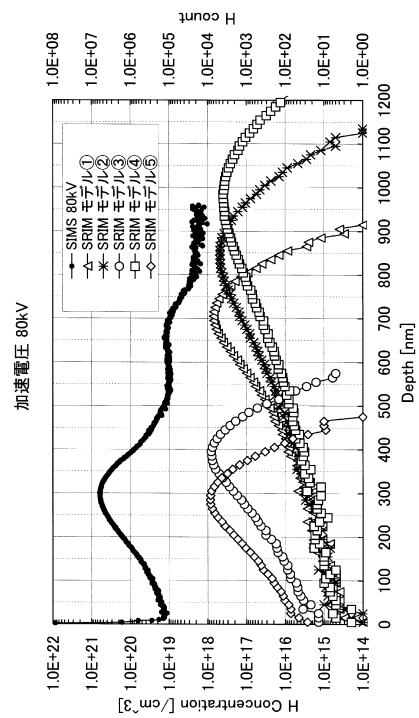

図20に、モデル1乃至モデル5を用いて水素イオン種を照射した場合 ( $H$  換算で10万個照射時) の計算結果を示す。また、図18の水素イオン種を照射した  $Si$  基板中の水素濃度 (SIMS (Secondary Ion Mass Spectroscopy) のデータ) をあわせて示す。モデル1乃至モデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータについては、縦軸を水素原子の密度で表している (左軸)。横軸は  $Si$  基板表面からの深さである。実測値であるSIMSデータと、計算結果とを比較した場合、モデル2及びモデル4は明らかにSIMSデータのピークから外れており、また、SIMSデータ中にはモデル3に対応するピークも見られない。このことから、モデル2乃至モデル4の寄与は、相対的に小さいことが分かる。イオンの運動エネルギーが数  $keV$  から数十  $keV$  のであるのに対して、 $H$ - $H$  の結合エネルギーは数  $eV$  程度に過ぎないことを考えれば、モデル2及びモデル4の寄与が小さいのは、 $Si$  元素との衝突により、大部分の  $H_2^+$  や  $H_3^+$  が、 $H^+$  や  $H$  に分離しているためと思われる。

30

#### 【0042】

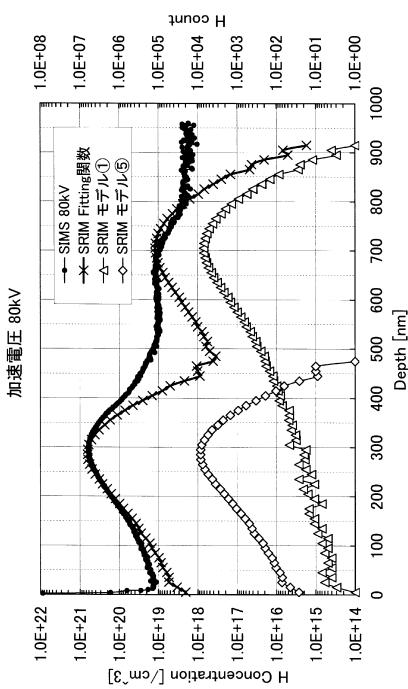

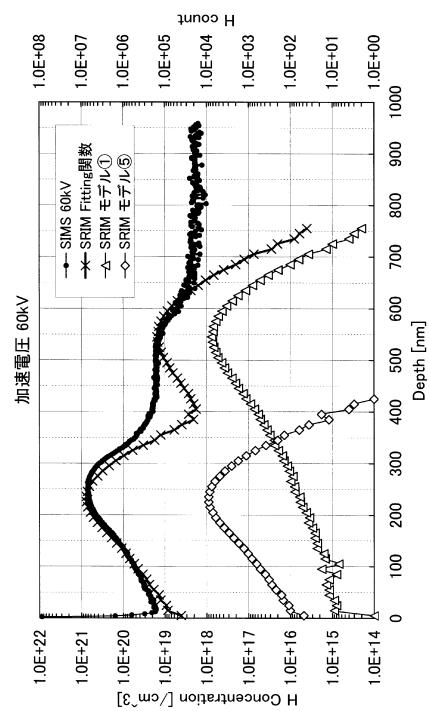

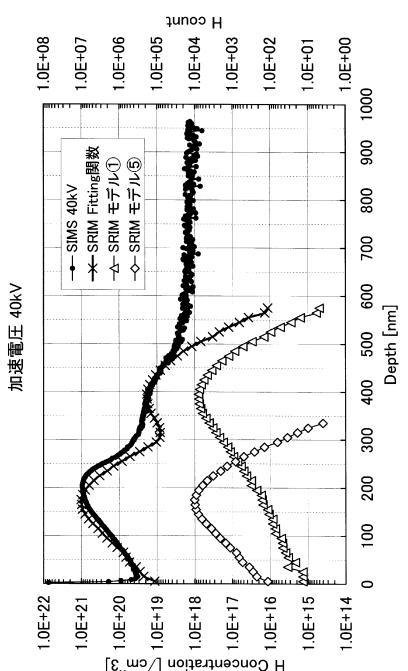

以上より、モデル2乃至モデル4については、以下では考慮しない。図21乃至図23に、モデル1及びモデル5を用いて水素イオン種を照射した場合 ( $H$  換算で10万個照射時) の計算結果を示す。また、図18の水素イオン種を照射した  $Si$  基板中の水素濃度 (SIMSデータ) 及び、上記シミュレーション結果をSIMSデータにフィッティングさせたもの (以下フィッティング関数と呼ぶ) を合わせて示す。ここで、図21は加速電圧を80  $kV$  とした場合を示し、図22は加速電圧を60  $kV$  とした場合を示し、図23は加速電圧を40  $kV$  とした場合を示している。なお、モデル1及びモデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータ及びフィッティング関数については、縦軸を水素原子の密度で表している (左軸)。横軸は  $Si$  基板表面からの深さである。

40

#### 【0043】

フィッティング関数はモデル1及びモデル5を考慮して以下の計算式により求めることとした。なお、計算式中、 $X$ 、 $Y$  はフィッティングに係るパラメータであり、 $V$  は体積である。

50

## [ フィッティング関数 ]

$$= X / V \times [ \text{モデル1のデータ} ] + Y / V \times [ \text{モデル5のデータ} ]$$

## 【 0 0 4 4 】

現実に照射されるイオン種の割合 ( $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  程度) を考えれば  $H_2^+$  の寄与 (すなわち、モデル3) についても考慮すべきであるが、以下に示す理由により、ここでは除外して考えた。

・モデル3に示される照射過程により導入される水素は、モデル5の照射過程と比較して僅かであるため、除外して考えても大きな影響はない (S I M S データにおいても、ピークが現れていない)。 10

・モデル5とピーク位置の近いモデル3は、モデル5において生じるチャネリング (結晶の格子構造に起因する元素の移動) により隠れてしまう可能性が高い。すなわち、モデル3のフィッティングパラメータを見積もるのは困難である。これは、本シミュレーションが非晶質Siを前提としており、結晶性に起因する影響を考慮していないことによるものである。

## 【 0 0 4 5 】

図24に、上記のフィッティングパラメータをまとめた。いずれの加速電圧においても、導入されるHの数の比は、[モデル1] : [モデル5] = 1 : 4.2 ~ 1 : 4.5 程度 (モデル1におけるHの数を1とした場合、モデル5におけるHの数は4.2以上4.5以下程度) であり、照射されるイオン種の数の比は、[ $H^+$  (モデル1)] : [ $H_3^+$  (モデル5)] = 1 : 1.4 ~ 1 : 1.5 程度 (モデル1における $H^+$ の数を1とした場合、モデル5における $H_3^+$ の数は1.4以上1.5以下程度) である。モデル3を考慮していないことや非晶質Siと仮定して計算していることなどを考えれば、実際の照射に係るイオン種の比 ( $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  程度) に近い値が得られていると言える。 20

## 【 0 0 4 6 】

(  $H_3^+$  を用いる効果 )

図18に示すような $H_3^+$ の割合を高めた水素イオン種を基板に照射することで、 $H_3^+$ に起因する複数のメリットを享受することができる。例えば、 $H_3^+$ は $H^+$ やHなどに分離して基板内に導入されるため、主に $H^+$ や $H_2^+$ を照射する場合と比較して、イオンの導入効率を向上させることができる。これにより、半導体基板の生産性向上を図ることができる。また、同様に、 $H_3^+$ が分離した後の $H^+$ やHの運動エネルギーは小さくなる傾向にあるから、薄い半導体層の製造に向いている。 30

## 【 0 0 4 7 】

なお、本明細書では、 $H_3^+$ を効率的に照射するために、図18に示すような水素イオン種を照射可能なイオンドーピング装置を用いる方法について説明している。イオンドーピング装置は廉価で、大面積処理に優れているため、このようなイオンドーピング装置を用いて $H_3^+$ を照射することで、半導体特性の向上、大面積化、低コスト化、生産性向上などの顕著な効果を得ることができる。一方で、 $H_3^+$ の照射を第一に考えるのであれば、イオンドーピング装置を用いることに限定して解釈する必要はない。

## 【 0 0 4 8 】

イオンを質量分離して半導体基板106に導入しても同様に分離層107を形成することができる。この場合にも、質量の大きいイオン (例えば $H_3^+$ イオン) を選択して半導体基板に導入することは上記と同様な効果を奏すこととなり好ましい。 40

## 【 0 0 4 9 】

イオン種を生成するガスとしては水素の他に重水素、ヘリウムのような不活性ガスを選択することも可能である。原料ガスにヘリウムを用い、質量分離機能を有さないイオンドーピング装置を用いることにより、 $He^+$ イオンの割合が高いイオンビームが得ることができる。このようなイオンを半導体基板106に導入することで、微小な空孔を形成することができ上記と同様な分離層107を半導体基板106中に設けることができる。

## 【 0 0 5 0 】

分離層の形成に当たってはイオンを高ドーズ条件で導入する必要があり、半導体基板10 50

6の表面が粗くなってしまう場合がある。そのためイオンが導入される表面に緻密な膜を設けておいても良い。例えば、窒化シリコン膜若しくは窒化酸化シリコン膜などによりイオンの導入に対する保護膜を50nm乃至200nmの厚さで設けておいても良い。

#### 【0051】

次に、支持基板と接合を形成する面に接合層102として酸化シリコン膜を形成する(図3(B)参照)。酸化シリコン膜の厚さは10nm乃至200nm、好ましくは10nm乃至100nm、より好ましくは20nm乃至50nmとすれば良い。酸化シリコン膜としては上述のように有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した分離層107から脱ガスが起こらない温度として、例えば350以下の成膜温度が適用される。また、単結晶若しくは多結晶半導体基板から結晶性半導体層を剥離する熱処理は、成膜温度よりも高い熱処理温度が適用される。

10

#### 【0052】

支持基板100と、半導体基板106の接合層102の面を対向させ、密接させることで接合を形成する(図3(C))。接合を形成する面は十分に清浄化しておく。支持基板100と接合層102の表面を対向させ、外部から一箇所を軽く押圧すると、両表面の間隔が縮まることによって、Van der Waals力が強まり、水素結合も寄与して接合する。更に、押圧部位の隣接した領域でも支持基板100と接合層102の対向する表面が近接することになるので、接合面が全面に広がっていく。

20

#### 【0053】

良好な接合を形成するために、一方若しくは両方の表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により200乃至400の温度であっても異種材料間の接合強度を高めることができる。

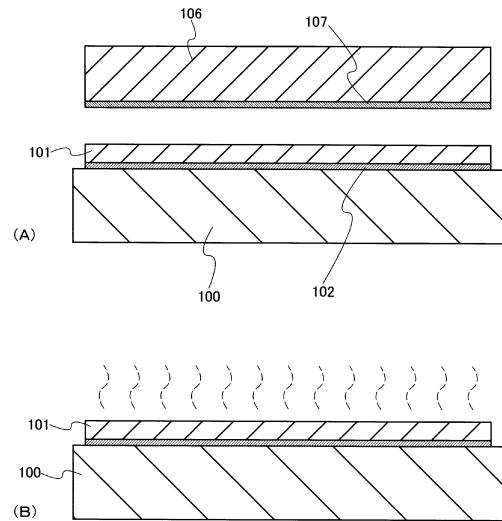

#### 【0054】

半導体基板106と支持基板100を重ね合わせた状態で第1の熱処理を行う。第1の熱処理により支持基板100上に薄い半導体層(単結晶半導体層101)を残して半導体基板106を分離を行う(図4(A))。第1の熱処理は接合層102の成膜温度以上で行うことが好ましく、400以上600未満の温度で行うことが好ましい。この温度範囲で熱処理を行うことで分離層107に形成された微小な空孔に体積変化が起こり、分離層107に沿って半導体基板106を劈開することができる。接合層102は支持基板100と接合しているので、支持基板100上には半導体基板106と同じ結晶性の単結晶半導体層101が固定された形態となる。この熱処理によって、水素結合から共有結合が生じ、接合強度が高まる。

30

#### 【0055】

次に支持基板100に単結晶半導体層101が接合された状態で第2の熱処理を行う(図4(B))。第2の熱処理は、第1の熱処理温度よりも高い温度であって支持基板100の歪み点を超えない温度で行うことが好ましい。或いは、第1の熱処理と第2の熱処理は同じ温度であっても、第2の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱又は輻射加熱などにより支持基板100及び/又は単結晶半導体層101が加熱されるようすれば良い。熱処理装置としては電熱炉、ランプアニール炉などを適用することができる。第2の熱処理は多段階に温度を変化させて行っても良い。また瞬間熱アニール(RTA)装置を用いても良い。RTA装置によって熱処理を行う場合には、基板の歪み点近傍又はそれよりも若干高い温度に加熱することもできる。

40

#### 【0056】

第2の熱処理を行うことで単結晶半導体層101に残留する応力を緩和することができる。すなわち、第2の熱処理は、支持基板100と単結晶半導体層101の膨張係数の違い

50

により生じる熱歪みを緩和する。また、第2の熱処理は、イオンを導入することによって結晶性が損なわれた単結晶半導体層101の結晶性を回復させるためにも有効である。さらに、第2の熱処理は、半導体基板106を支持基板100と接合させた後、第1の熱処理によって分割する際に生じる単結晶半導体層101のダメージを回復させることにも有効である。また、第1の熱処理と第2の熱処理を行うことで水素結合を、より強固な共有結合に変化させることができる。半導体基板106を取り除くことで試料の熱容量が小さくなるので、第2の熱処理に必要な熱量は低減する。また、第2の熱処理において、単結晶半導体層101上に半導体基板106が無くなることで、単結晶半導体層101表面に傷を付けてしまうことを防止できる。

## 【0057】

10

単結晶半導体層101の表面をより平坦化する目的で化学的機械研磨(CMP)処理を行っても良い。CMP処理は第1の熱処理後若しくは第2の熱処理後に行うことができる。尤も、第2の熱処理前に行えば、単結晶半導体層101の表面を平坦化すると共にCMP処理によって生じる表面の損傷層を第2の熱処理で修復することができる。

## 【0058】

いずれにしても、第1の熱処理と第2の熱処理を本形態のように組み合わせて行うことでのガラス基板のような熱的に脆弱な支持基板の上に、結晶性に優れた結晶半導体層を設けることが可能となる。

## 【0059】

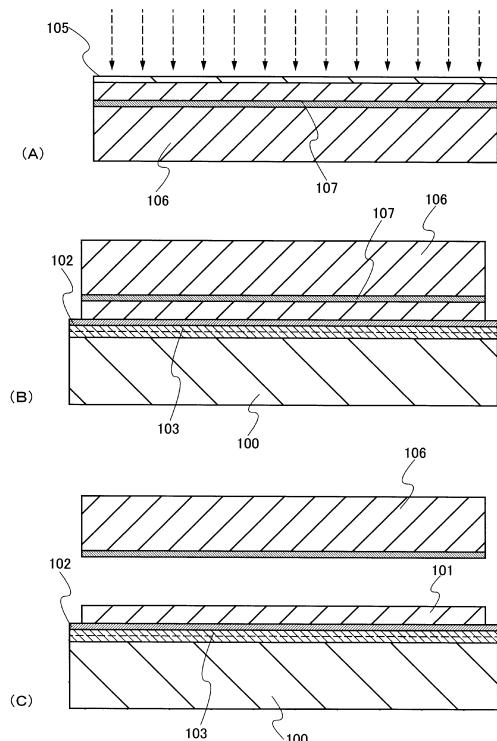

図5は支持基板側に接合層を設けて単結晶半導体層を有するSOI構造の基板を製造する工程を示す。

20

## 【0060】

まず、酸化シリコン層105が形成された半導体基板106に電界で加速されたイオンを所定の深さに導入し、分離層107を形成する(図5(A))。イオンの導入は図3(A)の場合と同様である。半導体基板106の表面に酸化シリコン層105を形成しておくことでイオンを導入することによって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。

## 【0061】

バリア層103及び接合層102が形成された支持基板100と半導体基板106の酸化シリコン層105の面を密着させて接合を形成する(図5(B))。この状態で第1の熱処理を行う。第1の熱処理は接合層102の成膜温度以上で行うことが好ましく、400以上600未満の温度で行うことが好ましい。それにより分離層107に形成された微小な空孔に体積変化が起こり、半導体基板106を劈開することができる。支持基板100上には半導体基板106と同じ結晶性を有する単結晶半導体層101が形成される(図5(C))。

30

## 【0062】

次に支持基板100に単結晶半導体層101が接合された状態で第2の熱処理を行う。第2の熱処理は、第1の熱処理温度よりも高い温度であって支持基板100の歪み点を超えない温度で行うことが好ましい。或いは、第1の熱処理と第2の熱処理は同じ温度であっても、第2の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱又は輻射加熱などにより支持基板100及び/又は単結晶半導体層101が加熱されるようにすれば良い。第2の熱処理を行うことで単結晶半導体層101に残留する応力を緩和することができ、第1の熱処理によって分割する際に生じる単結晶半導体層101のダメージを回復させることにも有効である。

40

## 【0063】

図16は支持基板側に接合層を設けて単結晶半導体層を接合する場合における他の形態を示す。最初に半導体基板106に分離層107を形成する(図16(A))。分離層107を形成するためのイオンの導入はイオンドーピング装置を用いて行う。この工程では質量の異なる複数種のイオンが高電界で加速されて半導体基板106に照射される。半導体基板106の表面はイオンの照射により平坦性が損なわれるおそれがあるので、保護膜と

50

して酸化シリコン層 105 を設けておくことが好ましい。酸化シリコン層 105 は熱酸化により形成しても良いし、ケミカルオキサイドを適用しても良い。ケミカルオキサイドは酸化性の薬液に半導体基板 106 を浸することで形成可能である。例えば、オゾン含有水溶液で半導体基板 106 を処理すれば表面にケミカルオキサイドが形成される。また、プラズマ CVD 法で形成した酸化窒化シリコン膜、窒化酸化シリコン膜、又は TEOS を用いて成膜した酸化シリコン膜であっても良い。

#### 【0064】

支持基板 100 にはバリア層 103 を設けることが好ましい。バリア層 103 を設けることで、支持基板 100 として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散して単結晶半導体層 101 が汚染されることを防ぐことができる。バリア層 103 は一層又は複数の層をもって構成する。例えば、ナトリウムなどのイオンをブロッキングする効果の高い窒化シリコン膜又は窒化酸化シリコン膜を第 1 層目として用い、その上層に第 2 層目として酸化シリコン膜又は酸化窒化シリコン膜を設ける。第 1 層目は不純部の拡散を防止する目的を持った絶縁膜であり緻密な膜であるのに対し、第 2 層目は第 1 層目の膜の内部応力が上層に作用しないように、応力を緩和することを一つの目的としている。このように支持基板 100 にバリア層 103 を設けることで、単結晶半導体層を接合する際の基板の選択範囲を広げることができる。

#### 【0065】

バリア層 103 の上層に接合層 102 を設けた支持基板 100 と半導体基板 106 を接合させる（図 16（B））。半導体基板 106 の表面は保護膜として設けた酸化シリコン層 105 をフッ酸で除去しておき、半導体表面が露出する状態となっている。半導体基板 106 の最表面はフッ酸溶液の処理により水素で終端されている状態であれば良い。接合形成に際して表面終端水素により水素結合が形成され、良好な接合を形成することができる。また、不活性ガスのイオンを照射して半導体基板 106 の最表面に未結合手が露出するようにして、真空中で接合を形成しても良い。

#### 【0066】

この状態で第 1 の熱処理を行う。第 1 の熱処理は接合層 102 の成膜温度以上で行うことが好ましく、400 以上 600 未満の温度で行うことが好ましい。それにより分離層 107 に形成された微小な空孔に体積変化が起り、半導体基板 106 を劈開することができる。支持基板 100 上には半導体基板 106 と同じ結晶性を有する単結晶半導体層 101 が形成される（図 16（C））。

#### 【0067】

次に支持基板 100 に単結晶半導体層 101 が接合された状態で第 2 の熱処理を行う。第 2 の熱処理は、第 1 の熱処理温度よりも高い温度であって支持基板 100 の歪み点を超えない温度で行うことが好ましい。或いは、第 1 の熱処理と第 2 の熱処理は同じ温度であっても、第 2 の熱処理の処理時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱又は輻射加熱などにより支持基板 100 及び / 又は単結晶半導体層 101 が加熱されるようにすれば良い。第 2 の熱処理を行うことで単結晶半導体層 101 に残留する応力を緩和することができ、第 1 の熱処理によって分割する際に生じる単結晶半導体層 101 のダメージを回復させることにも有効である。

#### 【0068】

本形態によれば、ガラス基板等の耐熱温度が 700 以下の支持基板 100 であっても接合部の接着力が強固な単結晶半導体層 101 を得ることができる。支持基板 100 として、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用することが可能となる。すなわち、一边が 1 メートルを超える基板上に単結晶半導体層を形成することができる。このような大面積基板を使って液晶ディスプレイのような表示装置のみならず、半導体集積回路を製造することができる。

#### 【0069】

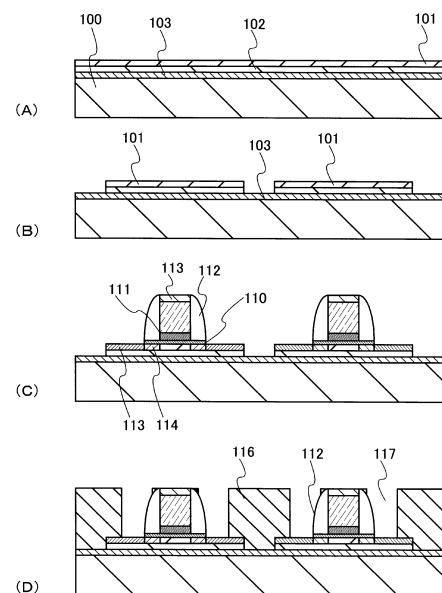

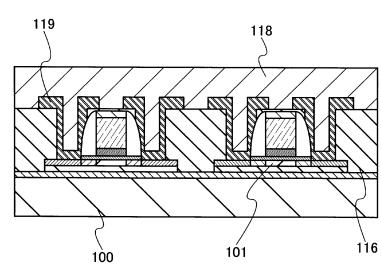

次いで、本形態による半導体装置について図 6 と図 7 を参照して説明する。まず、支持基

10

20

30

40

50

板 100 に接合層 102 を介して単結晶半導体層 101 が設けられている (図 6 (A))。単結晶半導体層 101 の膜厚は 5 nm から 500 nm、好ましくは 10 nm から 200 nm、より好ましくは 10 nm から 60 nm の厚さとすることが好ましい。単結晶半導体層 101 の厚さは、図 3 で説明した分離層 107 の深さを制御することにより適宜設定できる。単結晶半導体層 101 にはしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型不純物元素を添加する。例えば、p 型不純物元素として硼素を  $1 \times 10^{16} \text{ cm}^{-3}$  以上  $1 \times 10^{18} \text{ cm}^{-3}$  以下の濃度で添加されていても良い。支持基板 100 にはバリア層 103 として窒化シリコン層と酸化シリコン層が積層形成されている。支持基板 100 にバリア層を設けることで、単結晶半導体層 101 の汚染を防ぐことができる。なお、窒化シリコン層に換えて、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層を適用しても良い。 10

#### 【0070】

単結晶半導体層 101 をエッティングして、半導体素子の配置に合わせて島状に分離する (図 6 (B))。そして、単結晶半導体層 101 が露出した後ゲート絶縁層 110、ゲート電極 111、サイドウォール絶縁層 112 を形成し、第 1 不純物領域 113、第 2 不純物領域 114 を形成する (図 6 (C))。絶縁層 115 は窒化シリコンで形成し、ゲート電極 111 をエッティングするときのハードマスクとして用いる。

#### 【0071】

層間絶縁層 116 を形成する。層間絶縁層 116 は BPSG (Boron Phosphorus Silicon Glass) 膜を成膜するか、ポリイミドに代表される有機樹脂を塗布して形成する (図 6 (D))。層間絶縁層 116 にはコンタクトホール 117 を形成する。コンタクトホール 117 は、サイドウォール絶縁層 112 を利用してセルフアラインコンタクトの構成となっている。勿論、セルフアラインコンタクトを採用しなくても良い。 20

#### 【0072】

その後、コンタクトホール 117 に合わせて配線 119 を形成する。配線 119 はアルミニウム若しくはアルミニウム合金で形成し、上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属膜で形成する (図 7)。

#### 【0073】

このように、支持基板 100 に接合された単結晶半導体層 101 を用いて電界効果トランジスタを作製することができる。本形態に係る単結晶半導体層 101 は、結晶方位が一定の単結晶半導体であるため、均一で高性能な電界効果トランジスタを得ることができる。すなわち、閾値電圧や移動度などトランジスタ特性として重要な特性値の不均一性を抑制し、高移動化などの高性能化を達成することができる。 30

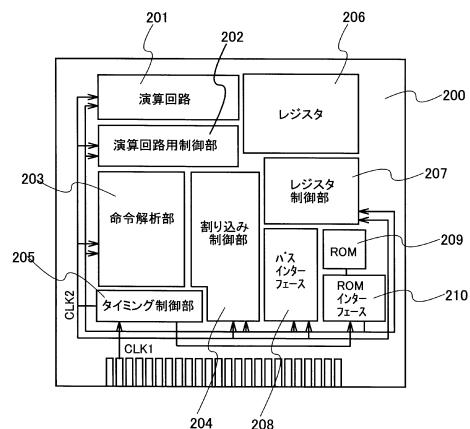

#### 【0074】

図 8 は半導体装置の一例として、マイクロプロセッサ 200 の一例を示す。このマイクロプロセッサ 200 は、上記したように本形態に係る半導体基板により製造されるものである。このマイクロプロセッサ 200 は、演算回路 201 (Arithmetic logic unit ; ALU ともいう。)、演算回路制御部 202 (ALU Control lever)、命令解析部 203 (Instruction Decoder)、割り込み制御部 204 (Interrupt Controller)、タイミング制御部 205 (Timing Controller)、レジスタ 206 (Register)、レジスタ制御部 207 (Register Controller)、バスインターフェース 208 (Bus I/F)、読み出し専用メモリ 209、及びメモリインターフェース 210 (ROM I/F) を有している。 40

#### 【0075】

バスインターフェース 208 を介してマイクロプロセッサ 200 に入力された命令は命令解析部 203 に入力され、デコードされた後に演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 に入力される。演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 は、デコ 50

ードされた命令に基づき各種制御を行う。具体的に演算回路制御部 202 は、演算回路 201 の動作を制御するための信号を生成する。また、割り込み制御部 204 は、マイクロプロセッサ 200 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部 207 は、レジスタ 206 のアドレスを生成し、マイクロプロセッサ 200 の状態に応じてレジスタ 206 の読み出しや書き込みを行う。タイミング制御部 205 は、演算回路 201、演算回路制御部 202、命令解析部 203、割り込み制御部 204、レジスタ制御部 207 の動作のタイミングを制御する信号を生成する。例えばタイミング制御部 205 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えており、クロック信号 CLK2 を上記各種回路に供給する。なお、図 8 に示すマイクロプロセッサ 200 は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

#### 【0076】

このようなマイクロプロセッサ 200 は、絶縁表面を有する支持基板に接合された結晶方位が一定の単結晶半導体層によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。

#### 【0077】

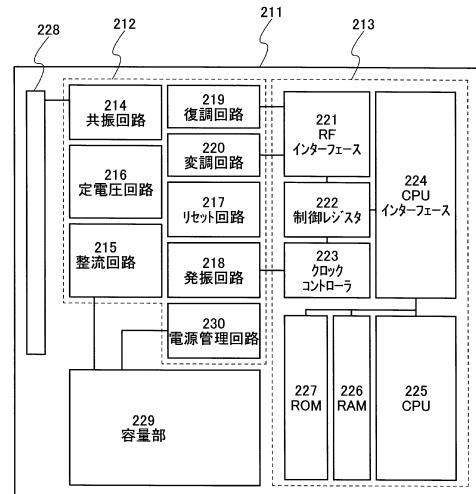

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図 9 を参照して説明する。図 9 は無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RF CPU」という）の一例を示す。RF CPU 211 は、アナログ回路部 212 とデジタル回路部 213 を有している。アナログ回路部 212 として、共振容量を有する共振回路 214、整流回路 215、定電圧回路 216、リセット回路 217、発振回路 218、復調回路 219 と、変調回路 220 を有している。デジタル回路部 213 は、RF インターフェース 221、制御レジスタ 222、クロックコントローラ 223、インターフェース 224、中央処理ユニット 225、ランダムアクセスメモリ 226、読み出し専用メモリ 227 を有している。

#### 【0078】

このような構成の RF CPU 211 の動作は概略以下の通りである。アンテナ 228 が受信した信号は共振回路 214 により誘導起電力を生じる。誘導起電力は整流回路 215 を経て容量部 229 に充電される。この容量部 229 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 229 は RF CPU 211 と一体形成されている必要はなく、別部品として RF CPU 211 を構成する絶縁表面を有する基板に取り付けられても良い。

#### 【0079】

リセット回路 217 は、デジタル回路部 213 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 218 は定電圧回路 216 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路 219 は、例えば振幅変調（ASK）方式の受信信号の振幅の変動を二値化する。変調回路 220 は、送信データを振幅変調（ASK）方式の送信信号の振幅を変動させて送信する。変調回路 220 は、共振回路 214 の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ 223 は、電源電圧又は中央処理ユニット 225 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 230 が行っている。

#### 【0080】

アンテナ 228 から RF CPU 211 に入力された信号は復調回路 219 で復調された後、RF インターフェース 221 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 222 に格納される。制御コマンドには、読み出し専用メモリ 227 に記憶されているデータの読み出し、ランダムアクセスメモリ 226 へのデータの書き込み、中央処理ユニット 225 への演算命令などが含まれている。中央処理ユニット 225 は、

10

20

30

40

50

インターフェース 224 を介して読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 にアクセスする。インターフェース 224 は、中央処理ユニット 225 が要求するアドレスより、読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 のいずれかに対するアクセス信号を生成する機能を有している。

【0081】

中央処理ユニット 225 の演算方式は、読み出し専用メモリ 227 に OS (オペレーティングシステム) を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算をプログラムを使って中央処理ユニット 225 が実行する方式を適用することができる。

10

【0082】

このような R F C P U 211 は、絶縁表面を有する基板若しくは絶縁基板上に接合された結晶方位が一定の単結晶半導体層によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部 229 を小型化しても長時間の動作を保証することができる。図 9 では R F C P U の形態について示しているが、通信機能、演算処理機能、メモリ機能を備えたものであれば、I C タグのようなものであっても良い。

20

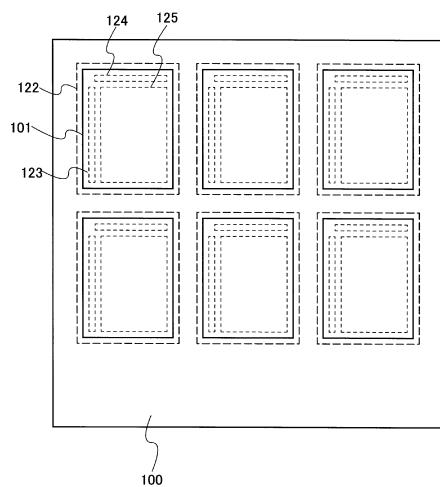

【0083】

図 1 及び図 2 で例示する単結晶半導体層 101 は、表示パネルを製造するマザーガラスと呼ばれる大型のガラス基板に接合することもできる。図 10 は支持基板 100 としてマザーガラスに単結晶半導体層 101 を接合する場合を示す。マザーガラスからは複数の表示パネルを切り出すが、単結晶半導体層 101 は、表示パネル 122 の形成領域に合わせて接合することが好ましい。半導体基板に比べて、マザーガラス基板は面積が大きいので、単結晶半導体層 101 は図 10 のように分割して配置することが好ましい。表示パネル 122 には、走査線駆動回路領域 123、信号線駆動回路領域 124、画素形成領域 125 があり、これらの領域が含まれるように単結晶半導体層 101 を支持基板 100 (マザーガラス) に接合する。

30

【0084】

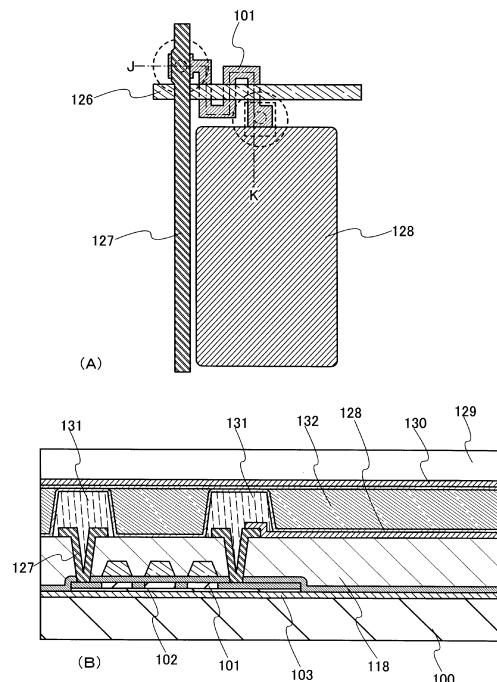

図 11 は単結晶半導体層 101 により画素トランジスタが形成される液晶表示パネルの画素の一例を示す。図 11 (A) は画素の平面図を示し、単結晶半導体層 101 に走査線 126 が交差し、信号線 127、画素電極 128 が接続する画素を示す。図 11 (A) に示す J - K 切断線に対応する断面図が図 11 (B) に示されている。

30

【0085】

図 11 (B) において、支持基板 100 にはバリア層 103 として窒化シリコン層と酸化シリコン層が積層されている。単結晶半導体層 101 は接合層 102 によってバリア層 103 と接合している。絶縁層 118 上に画素電極 128 が設けられている。単結晶半導体層 101 と信号線 127 を接続するコンタクトホールには絶縁層 118 をエッチングして凹段差が生じるのでそこを埋めるように柱状スペーサ 131 が設けられている。対向基板 129 には対向電極 130 が形成され、柱状スペーサ 131 によって形成される空隙に液晶層 132 が形成されている。

40

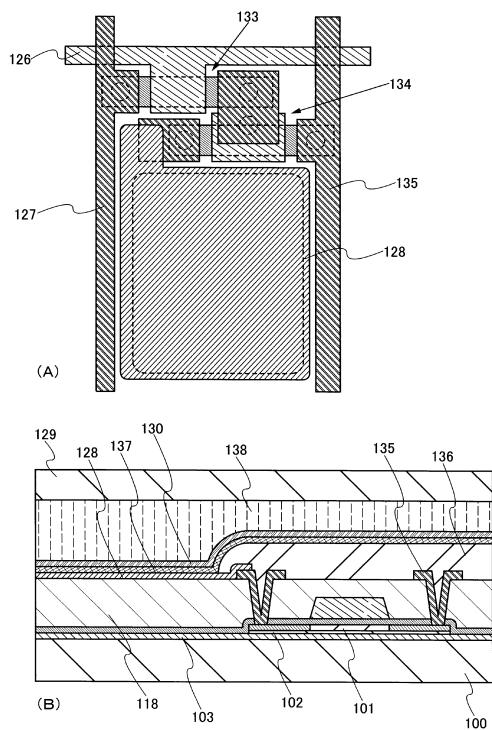

【0086】

図 12 (A) は単結晶半導体層 101 により画素部のトランジスタが形成されるエレクトロルミネセンス表示パネルの一例を示す。図 12 (A) は画素の平面図を示し、信号線 127 に接続する選択トランジスタ 133 と、電流供給線 135 に接続する表示制御トランジスタ 134 を有している。この表示パネルはエレクトロルミネセンス材料を含んで形成される層 (EL 層) を電極間に挟んだ発光素子が各画素に設けられる構成となっている。画素電極 128 は表示制御トランジスタ 134 に接続されている。図 12 (B) はこのような画素の要部を示す断面図である。

50

## 【0087】

図12(B)において、支持基板100、バリア層103、接合層102、単結晶半導体層101、絶縁層118などの構成は図11(B)と同様である。画素電極128は周辺部が絶縁性の隔壁層136で囲まれている。画素電極128上にはEL層137が形成されている。EL層137上には対向電極130が形成されている。画素部は封止樹脂138が充填され、補強板として対向基板129が設けられている。

## 【0088】

本形態のエレクトロルミネセンス表示パネルはこのような画素をマトリクス状に配列させて表示画面を構成する。この場合、画素のトランジスタのチャネル部が単結晶半導体層101で形成されるので、各トランジスタ間で特性バラツキがなく、画素毎の発光輝度に斑が出ないという利点がある。従って、発光素子の明るさを電流で制御して駆動することができる。トランジスタ特性のバラツキを補正する補正回路も不要となるので、駆動回路の負担を低減することができる。

10

## 【0089】

このように、表示パネルを製造するマザーガラスにも単結晶半導体層を形成しトランジスタを形成することが可能である。単結晶半導体層で形成されるトランジスタは、アモルファスシリコントランジスタよりも電流駆動能力など全ての動作特性が優れているので、トランジスタのサイズを小型化することができる。それにより、表示パネルにおける画素部の開口率を向上させることができる。また、図8及び図9で説明したようなマイクロプロセッサも形成することができるので、表示パネル内にコンピュータの機能搭載することもできる。

20

## 【実施例1】

## 【0090】

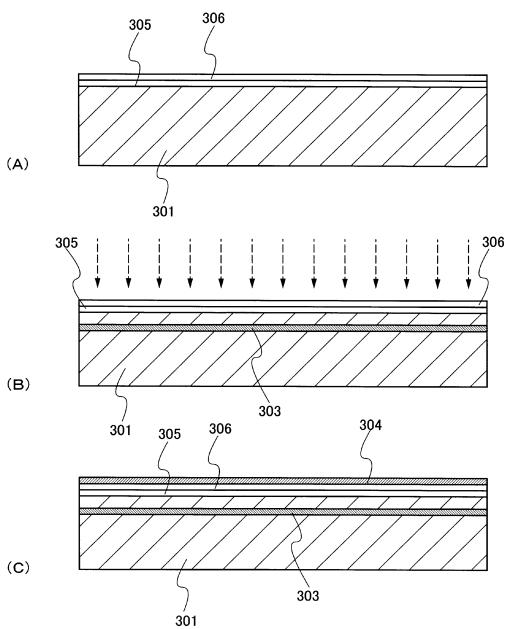

本例はSOI構造を有する基板の製造方法について図13と図14を参照して説明する。

## 【0091】

まず、自然酸化膜が除去された単結晶シリコン基板301にSiH<sub>4</sub>ガスとN<sub>2</sub>Oガスを用い、プラズマCVD法で100nmの厚さで酸化窒化シリコン膜305を形成する。さらにSiH<sub>4</sub>ガス、N<sub>2</sub>Oガス及びNH<sub>3</sub>ガスを用い、50nmの厚さで窒化酸化シリコン膜306を成膜する(図13(A))。

30

## 【0092】

そして、窒化酸化シリコン膜306の表面からイオンドーピング装置を用い水素イオンを導入する(図13(B))。本例では、水素をイオン化して単結晶シリコン基板301に分離層303を形成する。イオンドーピングは加速電圧80kVで、ドーズ量は2×10<sup>16</sup>ions/cm<sup>2</sup>として行う。

## 【0093】

イオンドーピング装置はイオン化したガスを質量分離せず、そのまま電界で加速して基板に導入させる方式である。イオンドーピング装置はイオン源に連接するドーピング室を有し、このドーピング室を真空ポンプで排気して減圧状態を保持すると共に、設置された基板にイオン流を照射する構成である。イオン源はプラズマ室と、プラズマ室で生成されたイオンを引き出す加速電極系を備えている。イオン源のプラズマ発生方式としては直流フライメント方式を用いることが好ましい。直流フライメント方式を用いると同一の原子からなる質量の異なる複数種のイオンを生成することができる。

40

## 【0094】

例えば、水素ガスを導入してイオンドーピングを行う場合、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>のイオン種を生成することができる。これらのイオン種はH<sup>+</sup>が12%、H<sub>2</sub><sup>+</sup>が8%、H<sub>3</sub><sup>+</sup>が80%の割合で存在し、これが単結晶シリコン基板301に導入されて分離層303を形成する。このように質量が小さく高次のイオンを分離層303に含ませることにより、熱処理工程において単結晶シリコン基板301の劈開を容易なものとすることができる。この場合において、単結晶シリコン基板301のイオンドーピング面に窒化酸化シリコン

50

膜 306 及び酸化窒化シリコン膜 305 を設けておくことで、イオンドーピングにより単結晶シリコン基板 301 の表面荒れを防ぐことができる。

【0095】

窒化酸化シリコン膜 306 上に接合層としての酸化シリコン膜 304 を形成する（図 13 (C)）。酸化シリコン膜 304 はプラズマ CVD 法で、珪酸エチル（TEOS：Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>）と酸素ガスを用いて 50 nm の厚さで成膜する。成膜温度は 350 以下として分離層 303 から水素が離脱しないようにする。

【0096】

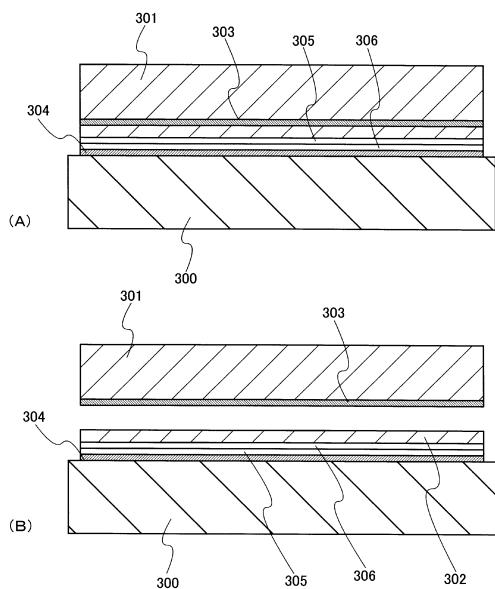

その後、超音波洗浄とオゾン含有水による洗浄がされたガラス基板 300 と、単結晶シリコン基板 301 を酸化シリコン膜 304 を挟んで重ね合わせ、押圧することで接合を形成する（図 14 (A)）。その後、第 1 の熱処理を行い単結晶シリコン基板 301 と支持基板であるガラス基板 300 を分離する（図 14 (B)）。そして、単結晶半導体層 302 がガラス基板 300 に接合されている状態で、さらに第 2 の熱処理を行う。

【0097】

本例では、第 1 の熱処理温度として 410 の場合と 500 の場合について行った。熱処理時間は共に 2 時間である。なお、この熱処理において、前記所定の温度で加熱する前に 410 で 10 分の予備加熱と、熱処理後に 410 で 2 時間の徐冷を行っている。また、第 2 の熱処理は 550 で 2 時間行った。第 2 の熱処理でも、加熱処理の前後には第 1 の熱処理と同様に、予備加熱と徐冷の期間を設けている。

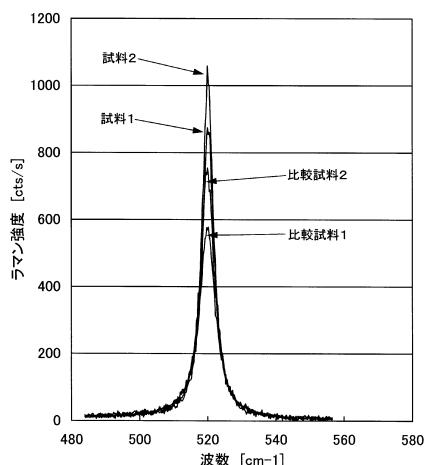

【0098】

表 1 は、第 1 の熱処理と第 2 の熱処理を行ったガラス基板上に設けられた単結晶半導体層のラマン分光特性を評価した結果を示す。また、図 15 はラマン分光スペクトルを示す。ラマン分光特性の評価はレーザラマン分光測定装置（HORIBA U1000）を用いて行った。

【表 1】

|                           | 試料1   | 試料2   | バルクSi |

|---------------------------|-------|-------|-------|

| 第1の熱処理温度                  | 410°C | 500°C | —     |

| 第2の熱処理温度                  | 550°C | 550°C | —     |

| ラマンシフト[cm <sup>-1</sup> ] | 520.2 | 520.1 | 520.7 |

| ラマン強度[cts/s]              | 905   | 1031  | 4384  |

| 半値全幅[cm <sup>-1</sup> ]   | 4.10  | 3.95  | 2.77  |

【0099】

また、比較例として第 1 の熱処理は同じ条件として、第 2 の熱処理を省略した試料を作製し、同様にラマン分光特性を評価した。その結果を表 2 に示す。

【表 2】

|                           | 比較試料A | 比較試料B |

|---------------------------|-------|-------|

| 第1の熱処理温度                  | 410°C | 500°C |

| 第2の熱処理温度                  | 無し    | 無し    |

| ラマンシフト[cm <sup>-1</sup> ] | 520.0 | 520.0 |

| ラマン強度[cts/s]              | 582   | 747   |

| 半値全幅[cm <sup>-1</sup> ]   | 5.59  | 4.77  |

【0100】

表 1 と表 2 及び図 15 を参照して本例と比較例を比較すると、ラマンスペクトルの半値幅が、第 2 の熱処理を行った本例に係る試料の半値幅が小さくなっている。このことより、第 2 の熱処理によって結晶欠陥及び格子の乱れが低減して結晶性が向上していることが判る。その他の項目として、第 2 の熱処理を行った本例に係る試料の方がラマン強度が強くなっている。ラマン強度は相対的な値であるが、結晶性が高いものほどその値が高くなる傾向があるので、第 2 の熱処理は、ガラス基板上に接合した単結晶半導体層の結晶性回復

10

20

30

40

50

に有用であることは明らかである。

【0101】

以上のように、本例によれば、ガラス基板300上に歪みが緩和され結晶性に優れた単結晶半導体層302を接合させることができる。本例で作製される単結晶半導体層302はガラス基板300と強固に接合しており、テープ剥離試験を行っても単結晶半導体層302が剥離することはない。すなわち、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板上に単結晶半導体層を設けることが可能となり、一辺が1メートルを超える基板を使って様々な集積回路、表示装置を製造することが可能となる。

【図面の簡単な説明】

10

【0102】

【図1】S0I構造を有する基板の構成を示す断面図。

【図2】S0I構造を有する基板の構成を示す断面図。

【図3】S0I構造を有する基板の製造方法を説明する断面図。

【図4】S0I構造を有する基板の製造方法を説明する断面図。

【図5】S0I構造を有する基板の製造方法を説明する断面図。

【図6】S0I構造を有する基板を用いた半導体装置の製造方法を説明する断面図。

【図7】S0I構造を有する基板を用いた半導体装置の製造方法を説明する断面図。

【図8】S0I構造を有する基板により得られるマイクロプロセッサの構成を示すプロック図。

20

【図9】S0I構造を有する基板により得られるRFCPUの構成を示すプロック図。

【図10】表示パネル製造用のマザーガラスに単結晶半導体層を接合する場合を例示する平面図。

【図11】単結晶半導体層により画素トランジスタが構成されている液晶表示パネルの一例を示す図。

【図12】単結晶半導体層により画素トランジスタが構成されているエレクトロルミネンス表示パネルの一例を示す図。

【図13】実施例1に係るS0I構造を有する基板の製造方法を説明する断面図。

【図14】実施例1に係るS0I構造を有する基板の製造方法を説明する断面図。

【図15】実施例1に係るS0I構造を有する基板における単結晶半導体層のラマン分光スペクトルを示すグラフ。

30

【図16】S0I構造を有する基板の製造方法を説明する断面図。

【図17】水素イオン種のエネルギーダイアグラムについて示す図である。

【図18】イオンの質量分析結果を示す図である。

【図19】イオンの質量分析結果を示す図である。

【図20】加速電圧を80kVとした場合の水素元素の深さ方向のプロファイル（実測値及び計算値）を示す図である。

【図21】加速電圧を80kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【図22】加速電圧を60kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

40

【図23】加速電圧を40kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【図24】フィッティングパラメータの比（水素元素比及び水素イオン種比）をまとめた図である。

【符号の説明】

【0103】

100 支持基板

101 単結晶半導体層

102 接合層

50

|       |              |    |

|-------|--------------|----|

| 1 0 3 | バリア層         |    |

| 1 0 4 | 絶縁層          |    |

| 1 0 5 | 酸化シリコン層      |    |

| 1 0 6 | 半導体基板        |    |

| 1 0 7 | 分離層          |    |

| 1 1 0 | ゲート絶縁層       |    |

| 1 1 1 | ゲート電極        |    |

| 1 1 2 | サイドウォール絶縁層   |    |

| 1 1 3 | 第1不純物領域      |    |

| 1 1 4 | 第2不純物領域      | 10 |

| 1 1 5 | 絶縁層          |    |

| 1 1 6 | 層間絶縁層        |    |

| 1 1 7 | コンタクトホール     |    |

| 1 1 8 | 絶縁層          |    |

| 1 1 9 | 配線           |    |

| 2 0 0 | マイクロプロセッサ    |    |

| 2 0 1 | 演算回路         |    |

| 2 0 2 | 演算回路制御部      |    |

| 2 0 3 | 命令解析部        |    |

| 2 0 4 | 割り込み制御部      | 20 |

| 2 0 5 | タイミング制御部     |    |

| 2 0 6 | レジスタ         |    |

| 2 0 7 | レジスタ制御部      |    |

| 2 0 8 | バスインターフェース   |    |

| 2 0 9 | 読み出し専用メモリ    |    |

| 2 1 0 | メモリインターフェース  |    |

| 2 1 1 | R F C P U    |    |

| 2 1 2 | アナログ回路部      |    |

| 2 1 3 | デジタル回路部      |    |

| 2 1 4 | 共振回路         | 30 |

| 2 1 5 | 整流回路         |    |

| 2 1 6 | 定電圧回路        |    |

| 2 1 7 | リセット回路       |    |

| 2 1 8 | 発振回路         |    |

| 2 1 9 | 復調回路         |    |

| 2 2 0 | 変調回路         |    |

| 2 2 1 | R F インターフェース |    |

| 2 2 2 | 制御レジスタ       |    |

| 2 2 3 | クロックコントローラ   |    |

| 2 2 4 | インターフェース     | 40 |

| 2 2 5 | 中央処理ユニット     |    |

| 2 2 6 | ランダムアクセスメモリ  |    |

| 2 2 7 | 読み出し専用メモリ    |    |

| 2 2 8 | アンテナ         |    |

| 2 2 9 | 容量部          |    |

| 2 3 0 | 電源管理回路       |    |

| 1 2 2 | 表示パネル        |    |

| 1 2 3 | 走査線駆動回路領域    |    |

| 1 2 4 | 信号線駆動回路領域    |    |

| 1 2 5 | 画素形成領域       | 50 |

|       |            |    |

|-------|------------|----|

| 1 2 6 | 走査線        |    |

| 1 2 7 | 信号線        |    |

| 1 2 8 | 画素電極       |    |

| 1 2 9 | 対向基板       |    |

| 1 3 0 | 対向電極       |    |

| 1 3 1 | 柱状スペーサ     |    |

| 1 3 2 | 液晶層        |    |

| 1 3 3 | 選択トランジスタ   |    |

| 1 3 4 | 表示制御トランジスタ |    |

| 1 3 5 | 電流供給線      | 10 |

| 1 3 6 | 隔壁層        |    |

| 1 3 7 | EL層        |    |

| 1 3 8 | 封止樹脂       |    |

| 3 0 0 | ガラス基板      |    |

| 3 0 1 | 単結晶シリコン基板  |    |

| 3 0 2 | 単結晶半導体層    |    |

| 3 0 3 | 分離層        |    |

| 3 0 4 | 酸化シリコン膜    |    |

| 3 0 5 | 酸化窒化シリコン膜  |    |

| 3 0 6 | 窒化酸化シリコン膜  | 20 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

| 加速電圧  | 水素元素(H)比(X:Y) | 水素イオン種比(X:Y/3) |

|-------|---------------|----------------|

| 80keV | 1:44.1        | 1:14.7         |

| 60keV | 1:42.5        | 1:14.2         |

| 40keV | 1:43.5        | 1:14.5         |

---

フロントページの続き

(51)Int.Cl. F I

H 05 B 33/02 (2006.01) H 05 B 33/14 A

H 01 L 51/50 (2006.01)

(56)参考文献 特開平11-163363 (JP, A)

特開2006-210899 (JP, A)

特開平07-099324 (JP, A)

特開2005-252244 (JP, A)

特開2003-142664 (JP, A)

特開2004-134675 (JP, A)

特開2000-077287 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/02

H 01 L 21/265

H 01 L 21/336

H 01 L 27/12

H 01 L 29/786

H 01 L 51/50

H 05 B 33/02