(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5348926号

(P5348926)

(45) 発行日 平成25年11月20日(2013.11.20)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

H01L 21/02 (2006.01)

H01L 27/12 (2006.01)

F 1

H01L 27/12

B

請求項の数 4 (全 56 頁)

(21) 出願番号 特願2008-102308 (P2008-102308)

(22) 出願日 平成20年4月10日 (2008.4.10)

(65) 公開番号 特開2008-311621 (P2008-311621A)

(43) 公開日 平成20年12月25日 (2008.12.25)

審査請求日 平成23年3月29日 (2011.3.29)

(31) 優先権主張番号 特願2007-127148 (P2007-127148)

(32) 優先日 平成19年5月11日 (2007.5.11)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 荒井 康行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】 S O I 基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ガラス基板上に第1の単結晶半導体層及び第2の単結晶半導体層を形成し、

前記ガラス基板を前記ガラス基板の歪み点以上の温度で熱処理を行うことにより、前記

ガラス基板を収縮させて、前記第1の単結晶半導体層と前記第2の単結晶半導体層とを接

しさせ、

前記第1の単結晶半導体層及び前記第2の単結晶半導体層にレーザ光を照射すること

で、前記第1の単結晶半導体層及び前記第2の単結晶半導体層を一体化することを特徴とす

るS O I 基板の製造方法。

## 【請求項 2】

表面から一定の深さにイオンを照射して形成された分離層をそれぞれ有する第1の単結

晶半導体基板及び第2の単結晶半導体基板を用意し、

前記第1の単結晶半導体基板と前記第2の単結晶半導体基板とが離間した状態で、ガラ

ス基板上に前記第1の単結晶半導体基板及び前記第2の単結晶半導体基板を接合させ、

前記第1の単結晶半導体基板及び前記第2の単結晶半導体基板に第1の熱処理を行うこと

により、各前記分離層において前記第1の単結晶半導体基板及び前記第2の単結晶半導

体基板を分離させ、前記ガラス基板上に第1の単結晶半導体層及び第2の単結晶半導体層

を形成し、

前記ガラス基板を前記ガラス基板の歪み点以上の温度で第2の熱処理を行うことにより

前記ガラス基板を収縮させて、前記第1の単結晶半導体層と前記第2の単結晶半導体層

10

20

とを接しさせ、

前記第1の単結晶半導体層及び前記第2の単結晶半導体層にレーザ光を照射することにより、前記第1の単結晶半導体層及び前記第2の単結晶半導体層を一体化することを特徴とするSOI基板の製造方法。

【請求項3】

請求項2において、前記ガラス基板と前記第1の単結晶半導体基板との間及び前記ガラス基板と前記第2の単結晶半導体基板との間に絶縁膜を設けた状態で、前記ガラス基板上に前記第1の単結晶半導体基板及び前記第2の単結晶半導体基板を接合させることを特徴とするSOI基板の製造方法。

【請求項4】

10

請求項2または請求項3において、前記第1の熱処理は、前記ガラス基板の歪み点より低い温度で行うことを特徴するSOI基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は絶縁表面に半導体層が設けられた所謂SOI(Silicon on Insulator)構造を有するSOI基板の製造方法及びSOI構造を有する半導体装置の作製方法に関する。

【背景技術】

【0002】

20

単結晶半導体のインゴットを薄くスライスして作製されるシリコンウエハーに代わり、絶縁表面に薄い単結晶半導体層を設けたシリコン・オン・インシュレータ(以下、「SOI」ともいう)と呼ばれる半導体基板を使った集積回路が開発されている。SOI基板を使った集積回路は、トランジスタのドレインと基板間における寄生容量を低減し、半導体集積回路の性能を向上させるものとして注目を集めている。

【0003】

SOI基板を製造する方法としては、水素イオン注入剥離法が知られている(例えば、特許文献1参照。)。水素イオン注入剥離法は、シリコンウエハーに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面として、別のシリコンウエハーに薄いシリコン層(SOI層)を接合する。さらにSOI層を剥離する熱処理を行うことに加え、酸化性雰囲気下での熱処理によりSOI層に酸化膜を形成した後に該酸化膜を除去し、次に1000から1300の還元性雰囲気下で熱処理を行って接合強度を高める必要があるとされている。

30

【0004】

一方、高耐熱性ガラスなどの絶縁基板に単結晶シリコン層を設けた半導体装置が開示されている(例えば、特許文献2参照。)。この半導体装置は、歪み点が750以上の結晶化ガラスの全面を絶縁性シリコン膜で保護し、水素イオン注入剥離法により得られる単結晶シリコン層を当該絶縁性シリコン膜上に固着する構成を有している。

【特許文献1】特開2000-124092号公報

【特許文献2】特開平11-163363号公報

40

【発明の開示】

【発明が解決しようとする課題】

【0005】

一方、大画面テレビジョン装置などに見られる半導体装置の大型化、またさらなる生産性の向上のために、大面積基板に大面積半導体層を形成する技術が求められている。しかし、従来の方法では基板上に形成できる単結晶シリコン層は、シリコンウエハーのサイズで決まってしまい、上記のような大面積単結晶シリコン層を基板上に形成することが困難である。

【0006】

このような問題点に鑑み、大面積の単結晶半導体層を備えたSOI基板の製造方法を提供

50

することを目的の一とする。また、基板としてガラス基板を用いて、低コスト化、高生産化を達成できるS O I基板の製造方法を提供することを目的の一とする。さらに、そのようなS O I基板を用いて高スループットで生産性よく半導体装置を作製することにより、大型な半導体装置や、低価格な半導体装置を提供することを目的の一とする。

【課題を解決するための手段】

【0007】

絶縁表面を有する支持基板として熱処理によって収縮する基板を用い、支持基板上に複数の単結晶半導体層を一定の間隔を有して隣接して設ける。支持基板は、熱処理によって収縮する基板であればよく好適にはガラス基板を用いることができる。

【0008】

上記複数の単結晶半導体層は、絶縁表面を有する支持基板の歪み点以下の温度で支持基板に接合する。この単結晶半導体層の基となる半導体基板を、支持基板の歪み点以上の高温熱処理によりその表面を絶縁膜で被覆し、他方、支持基板については不純物の拡散を防ぐブロッキング層を、支持基板の歪み点以下の温度で形成しておく。しかる後、分離層が形成された半導体基板と支持基板とを接合させ、半導体基板を分離する熱処理を行うことで支持基板上に単結晶半導体層を設ける。

【0009】

本発明において、分離層とは、単結晶半導体基板ヘイオンを照射し、イオンにより微小な空洞を有するように脆弱化された領域であり、この分離層を、後の熱処理によって分断することで、単結晶半導体基板より単結晶半導体層を分離することができる。

【0010】

支持基板上に複数の単結晶半導体層を一定の間隔を有して隣接して設けた後、支持基板を熱処理する。この熱処理により支持基板は収縮し、それに伴い隣接する単結晶半導体層同士が接する。複数の単結晶半導体層同士を接させた状態でエネルギーーム照射を行い、複数の単結晶半導体層を一体化し、連続的な単結晶半導体層を形成する。エネルギーームとしてはレーザ光が好ましい。

【0011】

支持基板への熱処理により、支持基板上の複数の単結晶半導体層同士の間隔を無くし、接するように、支持基板への熱処理の条件、及び単結晶半導体層の間隔を設定する。支持基板を収縮するように変形させるため、熱処理温度はガラス基板の歪み点以上の温度が好ましい。単結晶半導体層間の間隔は基となる半導体基板の大きさや、支持基板の大きさにもよるが、例えば、0.1 μm以上1 μm以下とすればよい。この熱処理は減圧下で行っても、大気圧下で行ってもよく、雰囲気も窒素雰囲気下、酸素雰囲気下などで行ってもよい。

【0012】

熱処理による支持基板の収縮を、予め設けた単結晶半導体層間の間隔を消失させることに利用するので、支持基板及び単結晶半導体層の反りや支持基板と単結晶半導体層の膜剥がれを防止することができる。さらに、複数の単結晶半導体層を一体化し連続膜とすることができるため、大面積の単結晶半導体層を有するS O I基板を製造することが可能となる。

【0013】

従って、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の半導体装置を作製することができる。

【0014】

半導体基板に対する熱処理は酸化性雰囲気で行うことが好ましい。特に好ましくはハロゲンを含む酸化性雰囲気で熱処理が行われることが好ましい。例えば、酸素に微量の塩酸を添加して熱処理を行い、半導体基板に酸化膜を形成する。それにより、半導体基板と酸化膜の界面の未結合手を水素で終端させることにより界面を不活性化して電気的特性の安定化を図ることができる。塩素は半導体基板に含まれる金属と反応し、それを除去（ゲッタリング）するように作用する。

10

20

30

40

50

## 【0015】

支持基板には、不純物元素の拡散を防止する窒化シリコン膜又は窒化酸化シリコン膜をブロッキング層として設ける。さらに応力を緩和する作用のある絶縁膜として酸化窒化シリコン膜を組み合わせても良い。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (R B S : R u t h e r f o r d B a c k s c a t t e r i n g S p e c t r o m e t r y ) 及び水素前方散乱法 (H F S : H y d r o g e n F o r w a r d S c a t t e r i n g ) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、Si が 2.5 ~ 3.5 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、R B S 及び H F S を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、Si が 2.5 ~ 3.5 原子%、水素が 1.0 ~ 3.0 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子% としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。10

## 【0016】

本発明の S O I 基板の製造方法の一形態は、ハロゲンを含む酸化雰囲気中で熱処理を行い第 1 の半導体基板及び第 2 の半導体基板の表面に、それぞれ酸化膜を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面側から、一又は複数の原子から成る質量の異なるイオンを照射して、第 1 の半導体基板及び第 2 の半導体基板の一表面から該イオンの平均進入深さに近い深さ領域に、それぞれ多孔質構造を有する分離層を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面に、それぞれ窒化シリコン膜又は窒化酸化シリコン膜となるブロッキング層を形成し、第 1 の半導体基板及び第 2 の半導体基板のブロッキング層上に、それぞれ酸化シリコン膜を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面とガラス基板とを、酸化シリコン膜を挟んで重ね合わせた状態で、分離層に亀裂を生じさせ、第 1 の半導体基板及び第 2 の半導体基板を分離層でそれぞれ分離する熱処理を行い、第 1 の半導体基板より第 1 の単結晶半導体層と第 2 の半導体基板より第 2 の単結晶半導体層とをガラス基板上に一定の間隔を有して形成し、ガラス基板をガラス基板の歪み点以上の温度で熱処理し、第 1 の単結晶半導体層、及び第 2 の単結晶半導体層にレーザ光を照射することで、第 1 の半導体層及び第 2 の半導体層を一体化する。結果として、連続的な第 3 の半導体層が形成される。20

## 【0017】

本発明の S O I 基板の製造方法の一形態は、ハロゲンを含む酸化雰囲気中で熱処理を行い第 1 の半導体基板及び第 2 の半導体基板の表面に、それぞれ酸化膜を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面側から、一又は複数の原子から成る質量の異なるイオンを照射して、第 1 の半導体基板及び第 2 の半導体基板の一表面から該イオンの平均進入深さに近い深さ領域に、それぞれ多孔質構造を有する分離層を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面に、それぞれ窒化シリコン膜又は窒化酸化シリコン膜となるブロッキング層を形成し、第 1 の半導体基板及び第 2 の半導体基板のブロッキング層上に、それぞれ酸化シリコン膜を形成し、第 1 の半導体基板及び第 2 の半導体基板の一表面とガラス基板とを、酸化シリコン膜を挟んで重ね合わせた状態で、分離層に亀裂を生じさせ、第 1 の半導体基板及び第 2 の半導体基板を分離層でそれぞれ分離する熱処理を行い、第 1 の半導体基板より第 1 の単結晶半導体層と第 2 の半導体基板より第 2 の単結晶半導体層とをガラス基板上に一定の間隔を有して形成し、ガラス基板をガラス基板の歪み点以上の温度で熱処理し、第 1 の単結晶半導体層と第 2 の単結晶半導体層が接するように収縮させ、第 1 の単結晶半導体層、及び第 2 の単結晶半導体層にレーザ光を照射し、第 1 の半導体層及び第 2 の半導体層を一体化する。40

## 【0018】

上記構成において、第 1 の半導体基板及び第 2 の半導体基板を分離層でそれぞれ分離する熱処理は、ガラス基板をガラス基板の歪み点以上の温度で行う熱処理より低い温度で行う50

と好ましい。

【0019】

上記S O I基板の製造方法により形成される単結晶半導体層を用いて、半導体装置を作製することができる。

【0020】

なお、本発明において、半導体装置とは、半導体特性を利用することで機能しうる装置を指す。本発明を用いて半導体素子（トランジスタ、メモリ素子やダイオードなど）を含む回路を有する装置や、プロセッサ回路を有するチップなどの半導体装置を作製することができる。

【0021】

本発明は表示機能を有する装置である半導体装置（表示装置ともいう）にも用いることができ、本発明を用いる半導体装置には、エレクトロルミネセンス（以下「E L」ともいう。）と呼ばれる発光を発現する有機物、無機物、若しくは有機物と無機物の混合物を含む層を、電極間に介在させた発光素子とT F Tとが接続された半導体装置（発光表示装置）や、液晶材料を有する液晶素子を表示素子として用いる半導体装置（液晶表示装置）などがある。本発明において、表示機能を有する半導体装置とは、表示素子（液晶素子や発光素子など）を有する装置のことを言う。なお、基板上に液晶素子やE L素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、I C、抵抗素子、容量素子、インダクタ、又はトランジスタなどを有するフレキシブルプリントサーキット（F P C）やプリント配線基盤（P W B）が取り付けられたものも含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライト（導光板やプリズムシートや拡散シートや反射シートや光源（L E Dや冷陰極管など）を含んでいても良い）を含んでいても良い。

10

【0022】

なお、表示素子や半導体装置は、様々な形態及び様々な素子を用いることができる。例えば、E L素子（有機E L素子、無機E L素子又は有機物及び無機物を含むE L素子）、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ（G L V）、プラズマディスプレイ（P D P）、デジタルマイクロミラーデバイス（D M D）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、E L素子を用いた半導体装置としてはE Lディスプレイ、電子放出素子を用いた半導体装置としてはフィールドエミッションディスプレイ（F E D）やS E D方式平面型ディスプレイ（S E D：S u r f a c e - c o n d u c t i o n E l e c t r o n - e m i t t e r D i s p l a y）など、液晶素子を用いた半導体装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた半導体装置としては電子ペーパーがある。

20

【発明の効果】

【0023】

熱処理によるガラス基板の収縮を、予め設けた単結晶半導体層間の間隔を消失させることに利用するので、ガラス基板及び単結晶半導体層の反りやガラス基板と単結晶半導体層の膜剥がれを防止することができる。さらに、複数の単結晶半導体層を一体化し連続膜とすることができるため、大面積の単結晶半導体層を有するS O I基板を製造することが可能となる。

30

【0024】

半導体基板に対しては、ガラス基板の歪み点以上の高温熱処理を行い、ガラス基板に対しては歪み点温度以下でプロッキング層を設け、その両者を接合させることにより、不純物により単結晶半導体層が汚染されることを防ぐことができる。また、単結晶半導体層とガラス基板との界面準位密度を下げることができる。それにより、実用に耐えうる半導体装置を提供することができる。

40

【0025】

50

従って、大型の半導体装置であっても高スループットで生産性よく、高性能及び高信頼性の半導体装置を作製することができる。また、安価なガラス基板を用いて低コストで作製することができるため、低価格な半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0026】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0027】

(実施の形態1)

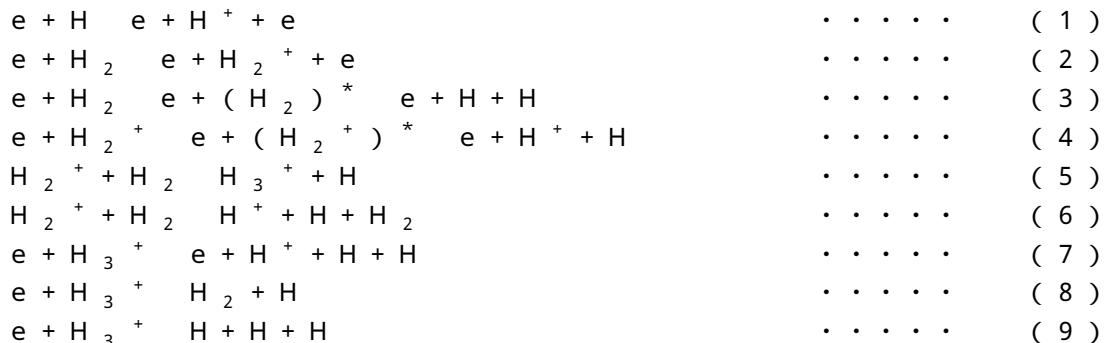

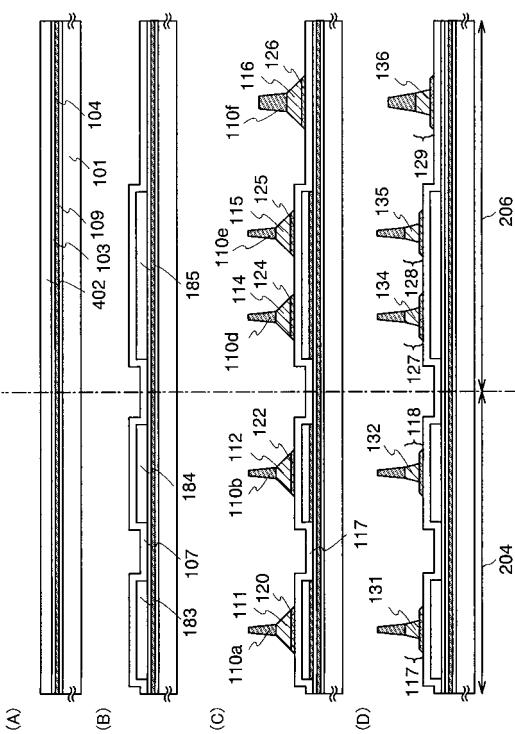

本発明の半導体基板の製造方法について図1(A)乃至(C)、図2(A)乃至(E)及び図3(A)乃至(D)を参照して説明する。

【0028】

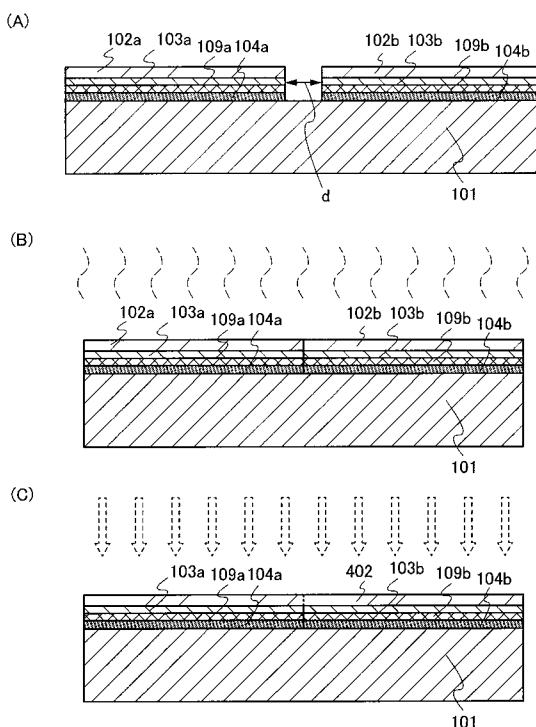

図2(A)において、半導体基板108として、代表的にはp型若しくはn型の単結晶シリコン基板(シリコンウエハー)が用いられる。また、他の結晶半導体基板としては、シリコン、ゲルマニウム、その他ガリウムヒ素、インジウムリンなどの化合物半導体の基板も適用することができる。本実施の形態は、結晶半導体基板の所定の深さに水素又はフッ素をイオン照射し、その後熱処理を行って表層の単結晶シリコン層を剥離するイオン照射剥離法で形成するが、ポーラスシリコン上に単結晶シリコン層をエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで分離する方法を適用しても良い。

20

【0029】

半導体基板108は脱脂洗浄をし、表面の酸化膜を除去して熱酸化を行う。熱酸化としては通常のドライ酸化でも良いが、酸化雰囲気中にハロゲンを添加した酸化を行うことが好みしい。例えば、酸素に対しHClを0.5~10体積%(好ましくは3体積%)の割合で含む雰囲気中で、700以上的温度で熱処理を行う。好適には950~1100の温度で熱酸化を行うと良い。処理時間は0.1~6時間、好ましくは0.5~1時間とすれば良い。形成される酸化膜103の膜厚としては、10nm~1000nm(好ましくは50nm~200nm)、例えば100nmの厚さとする。

30

【0030】

ハロゲンを含むものとしてはHClの他に、HF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF<sub>3</sub>、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub>、ジクロロエチレンなどから選ばれた一種又は複数種を適用することができる。

30

【0031】

このような温度範囲で熱処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去される。半導体基板108の表面を化学的機械研磨(CMP)処理をしたものに対しては有効である。また、水素は半導体基板108と酸化膜103の界面の欠陥を補償して界面の局在準位密度を低減する作用を奏し、半導体基板108と酸化膜103との界面が不活性化されて電気的特性が安定化する。

40

【0032】

この熱処理により形成される酸化膜103中にハロゲンを含ませることができる。ハロゲン元素は $1 \times 10^{17} / \text{cm}^3 \sim 5 \times 10^{20} / \text{cm}^3$ の濃度で含まれることにより金属などの不純物を捕獲して半導体基板108の汚染を防止する保護膜としての機能を発現させることができる。

【0033】

図2(B)では、半導体基板108にプロッキング層109を形成し、水素若しくはハロ

50

ゲンイオンを照射して分離層 110 を形成する。本発明では、複数の半導体基板よりそれぞれ分離させた複数の単結晶半導体層を一体化し、連続した大面積の単結晶半導体層を形成する。従って、分離される（半導体基板より切り出される）単結晶半導体層端部が酸化膜 103 やプロッキング層 109 に覆われず、露出している必要がある。

【0034】

本実施の形態では、半導体基板 108 に選択的にマスク層 123a、123b を設け、水素若しくはハロゲンイオンを照射して選択的に分離層 110 を形成する。図 2 で示すように分離層 110 は酸化膜 103 及びプロッキング層 109 とは接せず、半導体基板 108 内に選択的に形成することができる。

【0035】

プロッキング層 109 としては、窒化シリコン膜又は窒化酸化シリコン膜を気相成長法で 50 nm ~ 200 nm の厚さで形成する。例えば、窒化シリコン膜は SiH<sub>4</sub> と NH<sub>3</sub> をソースガスとしてプラズマ CVD 法で形成する。窒化酸化シリコン膜は SiH<sub>4</sub>、N<sub>2</sub>O 及び NH<sub>3</sub> を用いてプラズマ CVD 法で形成する。プロッキング層 109 は、この半導体基板 108 から形成される単結晶半導体層に対する不純物の拡散防止効果を発現する。また、分離層 110 を形成する際に、イオンの照射により半導体基板 108 の表面がダメージを受け、平坦性が損なわれるのを防ぐ効果がある。

【0036】

分離層 110 は、半導体基板 108 の表面から電界で加速されたイオンを所定の深さに照射することで形成される。半導体基板 108 に形成される分離層 110 の深さは、イオンの加速エネルギーとイオンの入射角によって制御する。半導体基板 108 の表面からイオンの平均進入深さに近い深さ領域に分離層 110 が形成される。例えば、単結晶半導体層の厚さは 5 nm 乃至 500 nm、好ましくは 10 nm 乃至 200 nm の厚さであり、イオンを照射する際の加速電圧はこのような厚さを考慮して行われる。イオンの照射はイオンドーピング装置を用いて行なうことが好ましい。すなわち、ソースガスをプラズマ化して生成された複数のイオン種を質量分離しないで照射するドーピング方式を用いる。本形態の場合、一又は複数の同一の原子から成る質量の異なるイオンを照射することが好ましい。イオンドーピングは、加速電圧 10 kV から 100 kV、好ましくは 30 kV から 80 kV、ドーズ量は  $1 \times 10^{16} / \text{cm}^2$  から  $4 \times 10^{16} / \text{cm}^2$ 、ビーム電流密度が 2  $\mu\text{A} / \text{cm}^2$  以上、好ましくは 5  $\mu\text{A} / \text{cm}^2$  以上、より好ましくは 10  $\mu\text{A} / \text{cm}^2$  以上とすれば良く、照射によって半導体層に生成される欠陥を低減することができる。

【0037】

水素イオンを照射する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup> イオンを含ませると共に、H<sub>3</sub><sup>+</sup> イオンの割合を高めておくことが好ましい。水素イオンを照射する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup> イオンを含ませると共に、H<sub>3</sub><sup>+</sup> イオンの割合を高めておくと照射効率を高めることができ、照射時間を短縮することができる。それにより、半導体基板 108 に形成される分離層 110 の領域には  $1 \times 10^{20} / \text{cm}^3$  (好ましくは  $5 \times 10^{20} / \text{cm}^3$  ) 以上の水素を含ませることが可能である。半導体基板 108 中において、局所的に高濃度の水素添加領域を形成すると、結晶構造が乱されて微小な空孔が形成され、分離層 110 を多孔質構造とすることができます。この場合、比較的低温の熱処理によって分離層 110 に形成された微小な空洞の体積変化が起こり、分離層に沿って分離することにより薄い単結晶半導体層を形成することができる。

【0038】

イオンを質量分離して半導体基板 108 に照射しても同様に分離層 110 を形成することができる。この場合にも、質量の大きいイオン ( 例えは H<sub>3</sub><sup>+</sup> イオン ) を選択的に照射することは上記と同様な効果を奏すこととなり好ましい。

【0039】

以下において、本発明の特徴の一であるイオンの照射方法について考察する。

【0040】

本発明では、水素 (H) に由来するイオン ( 以下「水素イオン種」と呼ぶ ) を単結晶半導

10

20

30

40

50

体基板に対して照射している。より具体的には、水素ガス又は水素を組成に含むガスを原材料として用い、水素プラズマを発生させ、該水素プラズマ中の水素イオン種を単結晶半導体基板に対して照射している。

【0041】

(水素プラズマ中のイオン)

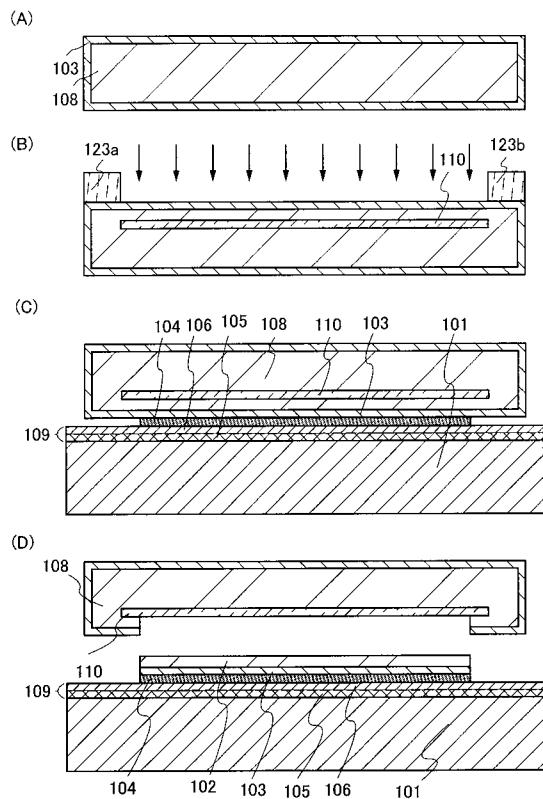

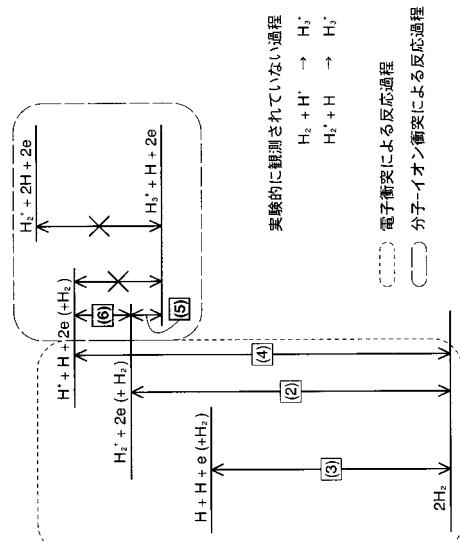

上記のような水素プラズマ中には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ といった水素イオン種が存在する。ここで、各水素イオン種の反応過程（生成過程、消滅過程）について、以下に反応式を列挙する。

10

【0042】

図24に、上記の反応の一部を模式的に表したエネルギーダイアグラムを示す。なお、図24に示すエネルギーダイアグラムは模式図に過ぎず、反応に係るエネルギーの関係を厳密に規定するものではない点に留意されたい。

20

【0043】

( $H_3^+$ の生成過程)

上記のように、 $H_3^+$ は、主として反応式(5)により表される反応過程により生成される。一方で、反応式(5)と競合する反応として、反応式(6)により表される反応過程が存在する。 $H_3^+$ が増加するためには、少なくとも、反応式(5)の反応が、反応式(6)の反応より多く起こる必要がある（なお、 $H_3^+$ が減少する反応としては他にも(7)、(8)、(9)が存在するため、(5)の反応が(6)の反応より多いからといって、必ずしも $H_3^+$ が増加するとは限らない。）。反対に、反応式(5)の反応が、反応式(6)の反応より少ない場合には、プラズマ中における $H_3^+$ の割合は減少する。

30

【0044】

上記反応式における右辺（最右辺）の生成物の増加量は、反応式の左辺（最左辺）で示す原料の密度や、その反応に係る速度係数などに依存している。ここで、 $H_2^+$ の運動エネルギーが約11eVより小さい場合には(5)の反応が主要となり（すなわち、反応式(5)に係る速度係数が、反応式(6)に係る速度係数と比較して十分に大きくなり）、 $H_2^+$ の運動エネルギーが約11eVより大きい場合には(6)の反応が主要となることが実験的に確認されている。

【0045】

荷電粒子は電場から力を受けて運動エネルギーを得る。該運動エネルギーは、電場によるポテンシャルエネルギーの減少量に対応している。例えば、ある荷電粒子が他の粒子と衝突するまでの間に得る運動エネルギーは、その間に通過した電位差分のポテンシャルエネルギーに等しい。つまり、電場中において、他の粒子と衝突することなく長い距離を移動できる状況では、そうではない状況と比較して、荷電粒子の運動エネルギー（の平均）は大きくなる傾向にある。このような、荷電粒子に係る運動エネルギーの増大傾向は、粒子の平均自由行程が大きい状況、すなわち、圧力が低い状況で生じ得る。

40

【0046】

また、平均自由行程が小さくとも、その間に大きな運動エネルギーを得ることができる状況であれば、荷電粒子の運動エネルギーは大きくなる。すなわち、平均自由行程が小さくとも、電位差が大きい状況であれば、荷電粒子の持つ運動エネルギーは大きくなると言える。

50

## 【0047】

これを  $H_2^+$  に適用してみる。プラズマの生成に係るチャンバー内のように電場の存在を前提とすれば、該チャンバー内の圧力が低い状況では  $H_2^+$  の運動エネルギーは大きくなり、該チャンバー内の圧力が高い状況では  $H_2^+$  の運動エネルギーは小さくなる。つまり、チャンバー内の圧力が低い状況では(6)の反応が主要となるため、 $H_3^+$  は減少する傾向となり、チャンバー内の圧力が高い状況では(5)の反応が主要となるため、 $H_3^+$  は増加する傾向となる。また、プラズマ生成領域における電場(又は電界)が強い状況、すなわち、ある二点間の電位差が大きい状況では  $H_2^+$  の運動エネルギーは大きくなり、反対の状況では、 $H_2^+$  の運動エネルギーは小さくなる。つまり、電場が強い状況では(6)の反応が主要となるため  $H_3^+$  は減少する傾向となり、電場が弱い状況では(5)の反応が主要となるため、 $H_3^+$  は増加する傾向となる。 10

## 【0048】

(イオン源による差異)

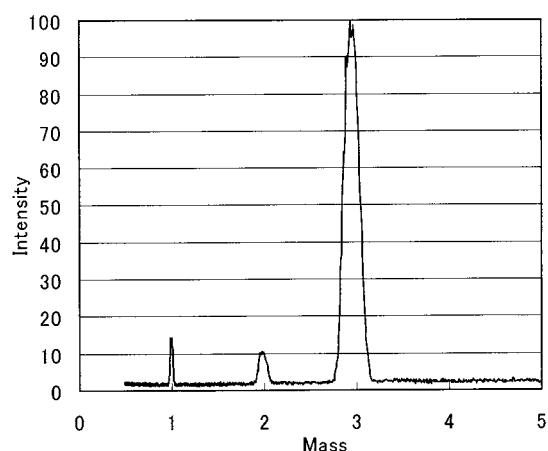

ここで、イオン種の割合(特に  $H_3^+$  の割合)が異なる例を示す。図25は、100%水素ガス(イオン源の圧力:  $4.7 \times 10^{-2}$  Pa)から生成されるイオンの質量分析結果を示すグラフである。なお、上記質量分析は、イオン源から引き出されたイオンを測定することにより行った。横軸はイオンの質量である。スペクトル中、質量1、2、3のピークは、それぞれ、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ に対応する。縦軸は、スペクトルの強度であり、イオンの数に対応する。図25では、質量が異なるイオンの数量を、質量3のイオンを100とした場合の相対比で表している。図25から、上記イオン源により生成されるイオンの割合は、 $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$ 程度となることが分かる。なお、このような割合のイオンは、プラズマを生成するプラズマソース部(イオン源)と、当該プラズマからイオンビームを引き出すための引出電極などから構成されるイオンドーピング装置によっても得ることが出来る。 20

## 【0049】

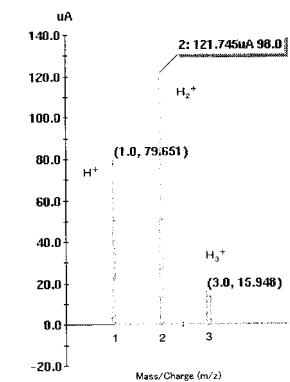

図26は、図25とは異なるイオン源を用いた場合であって、イオン源の圧力がおよそ  $3 \times 10^{-3}$  Paの時に、PH<sub>3</sub>から生成したイオンの質量分析結果を示すグラフである。上記質量分析結果は、水素イオン種に着目したものである。また、質量分析は、イオン源から引き出されたイオンを測定することにより行った。図25と同様、横軸はイオンの質量を示し、質量1、2、3のピークは、それぞれ  $H^+$ 、 $H_2^+$ 、 $H_3^+$ に対応する。縦軸はイオンの数量に対するスペクトルの強度である。図26から、プラズマ中のイオンの割合は  $H^+ : H_2^+ : H_3^+ = 37 : 56 : 7$ 程度であることが分かる。なお、図26はソースガスがPH<sub>3</sub>の場合のデータであるが、ソースガスとして100%水素ガスを用いたときも、水素イオン種の割合は同程度になる。 30

## 【0050】

図26のデータを得たイオン源の場合には、 $H^+$ 、 $H_2^+$ 及び $H_3^+$ のうち、 $H_3^+$ が7%程度しか生成されていない。他方、図25のデータを得たイオン源の場合には、 $H_3^+$ の割合を50%以上(上記の条件では80%程度)とすることが可能である。これは、上記考察において明らかになったチャンバー内の圧力及び電場に起因するものと考えられる。 40

## 【0051】

( $H_3^+$ の照射メカニズム)

図25のような複数のイオン種を含むプラズマを生成し、生成されたイオン種を質量分離しないで単結晶半導体基板に照射する場合、単結晶半導体基板の表面には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ の各イオンが照射される。イオンの照射からイオン導入領域形成にかけてのメカニズムを再現するために、以下の5種類のモデルを考える。

1. 照射されるイオン種が  $H^+$  で、照射後も  $H^+$  (H) である場合

2. 照射されるイオン種が  $H_2^+$  で、照射後も  $H_2^+$  ( $H_2$ ) のままである場合

3. 照射されるイオン種が  $H_2^+$  で、照射後に2個のH ( $H^+$ ) に分裂する場合

4. 照射されるイオン種が  $H_3^+$  で、照射後も  $H_3^+$  ( $H_3$ ) のままである場合

5. 照射されるイオン種が  $H_3^+$  で、照射後に 3 個の  $H$  ( $H^+$ ) に分裂する場合。

【0052】

(シミュレーション結果と実測値との比較)

上記のモデルを基にして、水素イオン種を  $Si$  基板に照射する場合のシミュレーションを行った。シミュレーション用のソフトウェアとしては、SRIM (the Stopping and Range of Ions in Matter: モンテカルロ法によるイオン導入過程のシミュレーションソフトウェア、TRIM (the Transport of Ions in Matter) の改良版) を用いている。なお、計算の関係上、モデル2では  $H_2^+$  を質量2倍の  $H^+$  に置き換えて計算した。また、モデル4では  $H_3^+$  を質量3倍の  $H^+$  に置き換えて計算した。さらに、モデル3では  $H_2^+$  を運動エネルギー  $1/2$  の  $H^+$  に置き換え、モデル5では  $H_3^+$  を運動エネルギー  $1/3$  の  $H^+$  に置き換えて計算を行った。

【0053】

なお、SRIMは非晶質構造を対象とするソフトウェアではあるが、高エネルギー、高ドーズの条件で水素イオン種を照射する場合には、SRIMを適用可能である。水素イオン種と  $Si$  原子の衝突により、 $Si$  基板の結晶構造が非単結晶構造に変化するためである。

【0054】

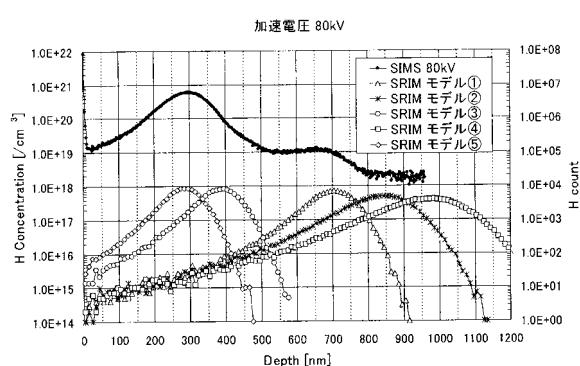

図27に、モデル1乃至モデル5を用いて水素イオン種を照射した場合 (H換算で10万個照射時) の計算結果を示す。また、図25の水素イオン種を照射した  $Si$  基板中の水素濃度 (SIMS (Secondary Ion Mass Spectroscopy) のデータ) をあわせて示す。モデル1乃至モデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータについては、縦軸を水素原子の密度で表している (左軸)。横軸は  $Si$  基板表面からの深さである。実測値であるSIMSデータと、計算結果とを比較した場合、モデル2及びモデル4は明らかにSIMSデータのピークから外れており、また、SIMSデータ中にはモデル3に対応するピークも見られない。このことから、モデル2乃至モデル4の寄与は、相対的に小さいことが分かる。イオンの運動エネルギーが  $keV$  のオーダーであるのに対して、 $H - H$  の結合エネルギーは数  $eV$  程度に過ぎないことを考えれば、モデル2及びモデル4の寄与が小さいのは、 $Si$  元素との衝突により、大部分の  $H_2^+$  や  $H_3^+$  が、 $H^+$  や  $H$  に分離しているためと思われる。

【0055】

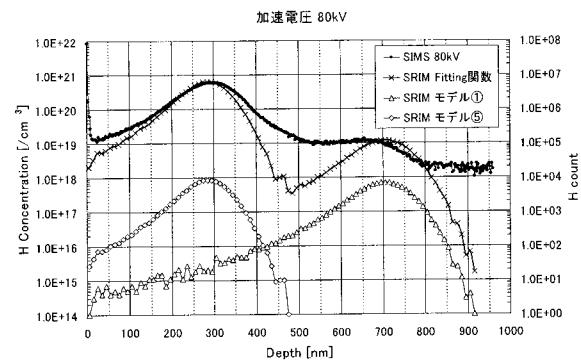

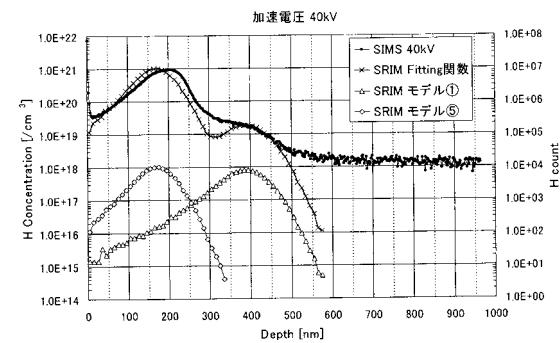

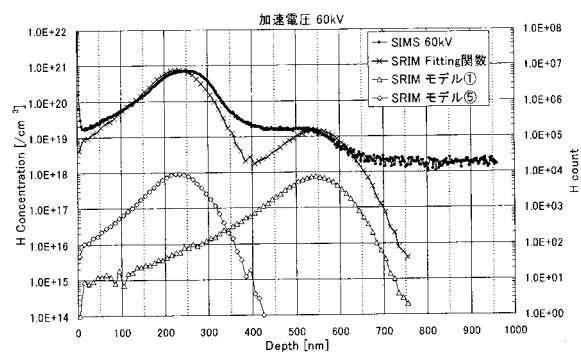

以上より、モデル2乃至モデル4については、以下では考慮しない。図28乃至図30に、モデル1及びモデル5を用いて水素イオン種を照射した場合 (H換算で10万個照射時) の計算結果を示す。また、図25の水素イオン種を照射した  $Si$  基板中の水素濃度 (SIMSデータ) 及び、上記シミュレーション結果をSIMSデータにフィッティングさせたもの (以下フィッティング関数と呼ぶ) を合わせて示す。ここで、図28は加速電圧を  $80kV$  とした場合を示し、図29は加速電圧を  $60kV$  とした場合を示し、図30は加速電圧を  $40kV$  とした場合を示している。なお、モデル1及びモデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータ及びフィッティング関数については、縦軸を水素原子の密度で表している (左軸)。横軸は  $Si$  基板表面からの深さである。

【0056】

フィッティング関数はモデル1及びモデル5を考慮して以下の計算式により求めることとした。なお、計算式中、X、Yはフィッティングに係るパラメータであり、Vは体積である。

[フィッティング関数]

$$= X / V \times [\text{モデル1のデータ}] + Y / V \times [\text{モデル5のデータ}]$$

【0057】

現実に照射されるイオン種の割合 ( $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  程度) を考えれば  $H_2^+$  の寄与 (すなわち、モデル3) についても考慮すべきであるが、以下に示す理由に

10

20

30

40

50

より、ここでは除外して考えた。

・モデル3に示される照射過程により導入される水素は、モデル5の照射過程と比較して僅かであるため、除外して考えても大きな影響はない(SIMSデータにおいても、ピークが現れていない)。

・モデル5とピーク位置の近いモデル3は、モデル5において生じるチャネリング(結晶の格子構造に起因する元素の移動)により隠れてしまう可能性が高い。すなわち、モデル3のフィッティングパラメータを見積もるのは困難である。これは、本シミュレーションが非晶質Siを前提としており、結晶性に起因する影響を考慮していないことによるものである。

#### 【0058】

図31に、上記のフィッティングパラメータをまとめた。いずれの加速電圧においても、導入されるHの数の比は、[モデル1] : [モデル5] = 1 : 42 ~ 1 : 45程度(モデル1におけるHの数を1とした場合、モデル5におけるHの数は42以上45以下程度)であり、照射されるイオン種の数の比は、[H<sup>+</sup>(モデル1)] : [H<sub>3</sub><sup>+</sup>(モデル5)] = 1 : 14 ~ 1 : 15程度(モデル1におけるH<sup>+</sup>の数を1とした場合、モデル5におけるH<sub>3</sub><sup>+</sup>の数は14以上15以下程度)である。モデル3を考慮していないことや非晶質Siと仮定して計算していることなどを考えれば、実際の照射に係るイオン種の比(H<sup>+</sup> : H<sub>2</sub><sup>+</sup> : H<sub>3</sub><sup>+</sup> = 1 : 1 : 8程度)に近い値が得られていると言える。

#### 【0059】

##### (H<sub>3</sub><sup>+</sup>を用いる効果)

図25に示すようなH<sub>3</sub><sup>+</sup>の割合を高めた水素イオン種を基板に照射することで、H<sub>3</sub><sup>+</sup>に起因する複数のメリットを享受することができる。例えば、H<sub>3</sub><sup>+</sup>はH<sup>+</sup>やHなどに分離して基板内に導入されるため、主にH<sup>+</sup>やH<sub>2</sub><sup>+</sup>を照射する場合と比較して、イオンの導入効率を向上させることができる。これにより、半導体基板の生産性向上を図ることができる。また、同様に、H<sub>3</sub><sup>+</sup>が分離した後のH<sup>+</sup>やHの運動エネルギーは小さくなる傾向にあるから、薄い半導体層の製造に向いている。

#### 【0060】

なお、本明細書では、H<sub>3</sub><sup>+</sup>を効率的に照射するために、図25に示すような水素イオン種を照射可能なイオンドーピング装置を用いる方法について説明している。イオンドーピング装置は廉価で、大面積処理に優れているため、このようなイオンドーピング装置を用いてH<sub>3</sub><sup>+</sup>を照射することで、半導体特性の向上、大面積化、低コスト化、生産性向上などの顕著な効果を得ることができる。一方で、H<sub>3</sub><sup>+</sup>の照射を第一に考えるのであれば、イオンドーピング装置を用いることに限定して解釈する必要はない。

#### 【0061】

イオンを生成するイオン種を生成するガスとしては水素の他に重水素、ヘリウムのような不活性ガスを選択することも可能である。原料ガスにヘリウムを用い、質量分離機能を有さないイオンドーピング装置を用いることにより、He<sup>+</sup>イオンの割合が高いイオンビームが得ることができる。このようなイオンを半導体基板108に照射することで、微小な空孔を形成することができ上記と同様な分離層110を半導体基板108中に設けることができる。

#### 【0062】

図2(C)は接合面を有する絶縁層(接合層)104を形成する段階を示す。本実施の形態では、絶縁層104を分離層110とほぼ同じ領域、好ましくは分離層110より内側の小さい領域に形成する。絶縁層104を選択的に成膜するために、新たなマスクを形成してもよいし、マスク層123a、123bを用いてもよい。

#### 【0063】

絶縁層104としては酸化シリコン膜を形成することが好ましい。酸化シリコン膜の厚さは10nm乃至200nm、好ましくは10nm乃至100nm、より好ましくは20nm乃至50nmとすれば良い。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。有機シランガスとしては、珪酸エチ

10

20

30

40

50

ル (TEOS: 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、テトラメチルシラン (TMS: 化学式  $\text{Si}(\text{CH}_3)_4$ )、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ )、トリスジメチルアミノシラン ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) 等のシリコン含有化合物を用いることができる。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、半導体基板に形成した分離層 110 から脱ガスが起こらない温度として、例えば 350 以下 の成膜温度が適用される。また、単結晶若しくは多結晶半導体基板から単結晶半導体層を剥離する熱処理は、成膜温度よりも高い熱処理温度が適用される。

10

#### 【0064】

また、図 2 (B) と (C) の工程において、分離層 110 を形成した後、プロッキング層 109 と絶縁層 104 を形成しても良い。この工程によれば、プロッキング層 109 と絶縁層 104 を大気に触れさせることなく連続的に形成することができ、異物の混入やカリウム、ナトリウムなどの汚染を防ぐことができる。プロッキング層 109 も絶縁層 104 と同様に分離層 110 に合わせて選択的に形成してもよい。

#### 【0065】

図 2 (D) は支持基板 101 と半導体基板 108 を接着させる段階を示す。支持基板 101 は絶縁性又は絶縁表面を有するものであり、アルミニシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板 (「無アルカリガラス基板」とも呼ばれる) が適用される。すなわち、熱膨張係数が  $25 \times 10^{-7} /$  から  $50 \times 10^{-7} /$  (好ましくは、 $30 \times 10^{-7} /$  から  $40 \times 10^{-7} /$ ) であって歪み点が 580 から 680 (好ましくは、600 から 680) のガラス基板を適用することができる。

20

#### 【0066】

支持基板 101 と半導体基板 108 の絶縁層 104 が形成された面を対向させ、密接させることで接合を形成する。接合を形成する面は十分に清浄化しておく。そして、支持基板 101 と絶縁層 104 を密接させることにより接合が形成される。接合は初期の段階においてファン・デル・ワールス力が作用するものと考えられ、支持基板 101 と半導体基板 108 とを圧接することで水素結合により強固な接合を形成することができる。

30

#### 【0067】

良好な接合を形成するために、絶縁層 104 と支持基板 101 の表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により 200 乃至 400 の温度であっても異種材料間の接合強度を高めることができる。

#### 【0068】

図 2 (E) は半導体基板 108 から単結晶半導体層 102 を剥離する段階を示す。半導体基板 108 と支持基板 101 を重ね合わせた状態で熱処理を行う。熱処理により支持基板 101 上に単結晶半導体層 102 を残して半導体基板 108 の分離を行う。熱処理は絶縁層 104 の成膜温度以上で行うことが好ましく、400 以上 600 未満の温度で行うことが好ましい。この温度範囲で熱処理を行うことで分離層 110 に形成された微小な空孔に体積変化が起り、分離層 110 に沿って半導体層を分離することができる。絶縁層 104 は支持基板 101 と接合しているので、支持基板 101 上には半導体基板 108 と同じ結晶性の単結晶半導体層 102 が接着される。

40

#### 【0069】

単結晶半導体層 102 は、半導体基板 108 における絶縁層 104 の形成領域が分離されて形成される。本実施の形態では、絶縁層 104 を分離層 110 より内側に選択的に形成しているため、支持基板 101 上に分離し接合される単結晶半導体層 102 端部は露出し

50

ており、酸化膜 103 やブロッキング層 109 で覆われていない。

【0070】

次に、以上の工程で支持基板 101 上に設けられた複数の単結晶半導体層 102 を一体化し連続膜とする工程を、図 1 を用いて説明する。

【0071】

図 1 (A) は支持基板 101 上に上記工程で単結晶半導体層 102a、102b が半導体基板 108 より設けられた例である。単結晶半導体層 102a、102b は同じ母体となる半導体基板 108 より分離されたものでもよいし、それぞれ異なる半導体基板より分離されたものでもよい。単結晶半導体層 102a、102b は図 2 (E) と同様な工程で接合されており、支持基板 101 上には絶縁層 104a、ブロッキング層 109a、酸化膜 103a、及び単結晶半導体層 102a の積層と、絶縁層 104b、ブロッキング層 109b、酸化膜 103b、及び単結晶半導体層 102b の積層とが一定の間隔 d を有して隣接して設けられている。

【0072】

本実施の形態では、支持基板 101 として絶縁表面を有するガラス基板を用いる。ガラス基板は加熱すると収縮し、形状が変形する。このガラス基板の収縮により単結晶半導体層の膜剥がれや反りなどの不良が生じる恐れがある。しかし本発明では、単結晶半導体層及び単結晶半導体層間を一定の間隔 d を有して設け、熱処理によりガラス基板である支持基板を収縮させることでその間隔 d を消失させ、単結晶半導体層同士を接触させる。

【0073】

図 1 (B) に示すように、支持基板 101 に対して熱処理を行う。熱処理によって支持基板 101 は収縮し、単結晶半導体層 102a 及び単結晶半導体層 102b 間の間隔 d も狭まつてしまい、単結晶半導体層 102a 及び単結晶半導体層 102b は接触する。

【0074】

支持基板への熱処理により、支持基板上の複数の単結晶半導体層同士の間隔を無くし、接するように、支持基板への熱処理の条件、及び単結晶半導体層の間隔を設定する。支持基板を収縮するように変形させるため、熱処理温度はガラス基板の歪み点以上の温度が好ましい。単結晶半導体層間の間隔は基となる半導体基板の大きさや、ガラス基板の大きさにもよるが、例えば、0.1 μm 以上 1 μm 以下とすればよい。この熱処理は減圧下で行つても、大気圧下で行つてもよく、雰囲気も窒素雰囲気下、酸素雰囲気下などで行つてもよい。

【0075】

また、この熱処理は分離層 110 の形成に添加された水素若しくはハロゲンを単結晶半導体層 102a、102b から脱離させることができる。支持基板 101 と単結晶半導体層 102a、102b の接合部における微小な空孔を除去することもできるために好ましい。熱処理の温度は、水素若しくはハロゲンが単結晶半導体層 102a、102b から放出される温度以上であって、支持基板 101 の歪み点近傍の温度までを可としいている。例えば、400 ~ 730 の温度範囲で行われる。熱処理装置としては電熱炉、ランプアーチ炉などを適用することができる。熱処理は多段階に温度を変化させて行つても良い。また瞬間熱アーチ (RTA) 装置を用いても良い。RTA 装置によって熱処理を行う場合には、基板の歪み点近傍又はそれよりも若干高い温度に加熱することもできる。

【0076】

単結晶半導体層 102a、102b に含まれる過剰な水素は複雑な挙動を示し、熱履歴によって半導体素子の特性を劣化させるように作用する場合がある。例えば、シリコンの格子間に含まれる水素は、価電子制御を目的としてドーピングされた不純物元素を不活性化させる作用がある。それにより、トランジスタのしきい値電圧の変動、ソース若しくはドレイン領域を高抵抗化させることとなる。また、シリコンの格子内に水素が含まれることとなると、シリコンの配位数が変化して格子欠陥を生成するように振る舞うことがある。勿論、水素若しくはハロゲンはシリコン中の未結合手を補償して、すなわち欠陥を補修する作用があるが、分離層 110 を形成するために添加された水素若しくはハロゲンは一旦

10

20

30

40

50

、単結晶半導体層 102a、102b から除去することが好ましい。

【0077】

このような熱処理を行うことで、支持基板 101 と単結晶半導体層 102a、102b の接合面においては水素結合を、より強固な共有結合に変化させることができる。

【0078】

次に、複数の単結晶半導体層同士を接させた状態でエネルギーービームの照射を行い、複数の単結晶半導体層を一体化し、連続的な単結晶半導体層を形成する。本実施の形態では、エネルギーービームとしてレーザ光を用いる。

【0079】

エネルギーービームは、単結晶半導体層 102a、102b に対し選択的に吸収されるものが好ましく、レーザ光（レーザビームともいう）を適用することが望まれる。これは支持基板 101 を過剰に加熱することなく、単結晶半導体層 102a、102b の欠陥を修復するためである。レーザ光は、エキシマレーザに代表される気体レーザ、YAG レーザに代表される固体レーザを光源として用いることができる。レーザビームの波長としては、紫外光から可視光域であることが好ましく、波長 190 nm から 700 nm が適用される。光源から放射されるレーザ光は光学系にて矩形状若しくは線状に集光されたものであることが好ましく、このレーザビームを単結晶半導体層 102a、102b 上を走査して処理を行えば良い。

【0080】

また、レーザ照射を用いる場合、連続発振型のレーザビーム（CW（CW : continuous-wave）レーザビーム）やパルス発振型のレーザビーム（パルスレーザビーム）を用いることができる。ここで用いることができるレーザビームは、Ar レーザ、Kr レーザ、エキシマレーザなどの気体レーザ、単結晶の YAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> に、ドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti : サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち 1 種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第 2 高調波から第 4 高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd : YVO<sub>4</sub> レーザ（基本波 1064 nm）の第 2 高調波（532 nm）や第 3 高調波（355 nm）を用いることができる。このレーザは、CW で射出することも、パルス発振で射出することも可能である。CW で射出する場合は、レーザのパワー密度としては 0.01 ~ 100 MW / cm<sup>2</sup> 程度（好ましくは 0.1 ~ 10 MW / cm<sup>2</sup>）が必要である。そして、走査速度を 10 ~ 2000 cm / sec 程度として照射する。

【0081】

なお、単結晶の YAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> に、ドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザ、Ar イオンレーザ、または Ti : サファイアレーザは、連続発振をさせることができあり、Qスイッチ動作やモード同期などを行うことによって 10 MHz 以上の発振周波数でパルス発振をさせることも可能である。パルス幅がピコ秒台、或いはフェムト秒（10<sup>-15</sup> 秒）台のパルスレーザを用いてもよい。

【0082】

その他、同様な目的においては、ハロゲンランプ若しくはキセノンランプなどを用いて行われるフラッシュランプアニールを適用しても良い。

【0083】

さらに、紫外線ランプ、ブラックライト、メタルハライドランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いてもよい。その

10

20

30

40

50

場合、ランプ光源は、必要な時間点灯させて照射してもよいし、複数回照射してもよい。

【0084】

図1(C)は単結晶半導体層102a、102bに、単結晶半導体層102a、102b同士を接触させた状態でレーザ光を照射して、単結晶半導体層102a及び単結晶半導体層102bを一体化し、連続的な単結晶半導体層402を形成する例である。単結晶半導体層102a、単結晶半導体層102bは端部接触面において、エネルギーービームにより結合が生じ、一体化する。このように、単結晶半導体層102a及び単結晶半導体層102bが一体化し、より大面積の単結晶半導体層402を形成することができる。

【0085】

また、エネルギーービームの照射により結晶欠陥を補修することができる。この工程は、単結晶半導体層102a、102bが支持基板101に接合される際に、熱的及び/又は機械的ダメージを受けて結晶性が劣化するので、その修復を図る上で行うことが好ましい。

【0086】

また本工程では、図1(C)において、単結晶半導体層102a、102bの脱水素化が成されているので、単結晶半導体層102a、102bにボイドを発生させることなく結晶欠陥の修復を行うことができる。また、単結晶半導体層102a、102bに対し、エネルギーービームを照射する処理を窒素雰囲気中で行えば、単結晶半導体層102a、102bの表面を平坦化することができる。

【0087】

次に、図1(A)のように支持基板上に単結晶半導体層を設ける他の製造方法について図3を参照して説明する。

【0088】

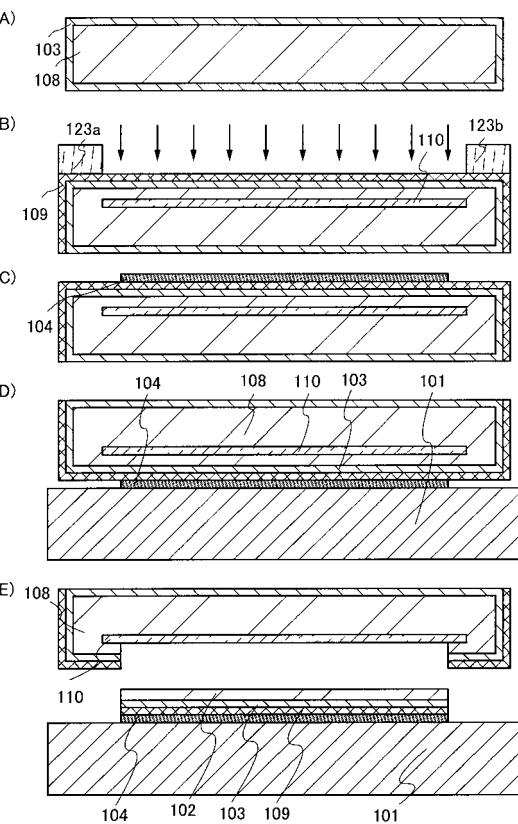

図3(A)に示すように半導体基板108に酸化膜103を形成する。酸化膜103は、酸素に対しHClを0.5~10体積% (好ましくは3体積%) の割合で含む雰囲気中で、700以上、好適には950~1100の温度で熱酸化を行い形成されたものであることが好ましい。そして、図3(B)で示すようにマスク層123a、123bを用いて半導体基板中に選択的に分離層110を形成する。

【0089】

図3(C)において、支持基板101にはブロッキング層109が設けられている。ブロッキング層109は、例えば、窒化酸化シリコン膜105と酸化窒化シリコン膜106により構成することができる。窒化酸化シリコン膜105は支持基板101に含まれる金属不純物が単結晶半導体層102側に拡散するのを防止する効果がある。酸化窒化シリコン膜106は、窒化酸化シリコン膜105の内部応力を緩和する作用がある。このような複合化したブロッキング層109を設けることにより単結晶半導体層102の不純物汚染を防止しつつ、応力歪みを緩和することができる。

【0090】

ブロッキング層109上には図2(C)と同様に選択的に絶縁層104が設けられている。この絶縁層104は平滑面を有し親水性表面を有する層とする。このような表面を形成可能なものとして、化学的な反応により形成される絶縁層が好ましい。平滑面を有し親水性表面を形成する絶縁層104は0.2nm乃至500nmの厚さで設けられる。この厚さであれば、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することができる。絶縁層104としては酸化シリコン膜を形成することが好ましい。酸化シリコン膜の厚さは10nm乃至200nm、好ましくは10nm乃至100nm、より好ましくは20nm乃至50nmとすれば良い。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。

【0091】

このようなブロッキング層109と絶縁層104とが形成された支持基板101と、酸化膜103が形成された半導体基板108を密接させて接着する。この場合、酸化膜103と絶縁層104とが接合することにより形成される。支持基板101上の絶縁層104と半導体基板108上の酸化膜103とを対向させて、一箇所を外部から押しつけると、局

10

20

30

40

50

所的に接合面同士の距離が縮まる事によるファン・デル・ワールス力の強まりや水素結合の寄与によって、お互いに引きつけ合う。更に、隣接した領域でも対向する支持基板101上の絶縁層104と半導体基板108上の酸化膜103間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、接合（ボンディングともいう）が進行し接合面全域に接合が広がる。

#### 【0092】

図3(D)は半導体基板108から単結晶半導体層102を剥離する段階を示す。半導体基板108と支持基板101を重ね合わせた状態で熱処理を行う。熱処理により支持基板101上に単結晶半導体層102を残して半導体基板108を分離を行う。熱処理は絶縁層104の成膜温度以上で行うことが好ましく、400以上600未満の温度で行うことが好ましい。しかし、支持基板101が収縮しない程度の温度で行う。支持基板101が収縮してしまうと、後工程での単結晶半導体層同士の一体化工程が困難になってしまうからである。この温度範囲で熱処理を行うことで分離層110に形成された微小な空孔に体積変化が起り、分離層110に沿って半導体層を分離することができる。絶縁層104は支持基板101と接合しているので、支持基板101上には半導体基板108と同じ結晶性の単結晶半導体層102が接着される。

#### 【0093】

図3(D)のように形成された支持基板上の単結晶半導体層102も図1で示したように、複数の単結晶半導体層を、熱処理によるガラス基板の収縮により接着させ、エネルギー・ビーム照射処理により一体化することができる。従って支持基板101上に大面積の単結晶半導体層を形成することができる。

#### 【0094】

本実施の形態によれば、ガラス基板等の耐熱温度が700以下の支持基板101であっても接合部の接着力が強固な単結晶半導体層102を得ることができる。支持基板101として、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用することが可能となる。すなわち、一辺が1メートルを超える基板上に単結晶半導体層を形成することができる。このような大面積基板を使って液晶ディスプレイのような表示装置のみならず、半導体集積回路を製造することができる。また、半導体基板に対しては、工程の最初の段階においてハロゲンを含む雰囲気中で熱酸化を行うことでゲッタリング作用が得られ、半導体基板を再利用する場合に有効である。

#### 【0095】

熱処理によるガラス基板の収縮を、予め設けた単結晶半導体層間の間隔を消失させることに利用するので、ガラス基板及び単結晶半導体層の反りやガラス基板と単結晶半導体層の膜剥がれを防止することができる。さらに、複数の単結晶半導体層を一体化し連続膜とすることができるため、大面積の単結晶半導体層を有するSOI基板を製造することができる。

#### 【0096】

半導体基板に対しては、ガラス基板の歪み点以上の高温熱処理を行い、ガラス基板に対しては歪み点温度以下でブロッキング層を設け、その両者を接合させることにより、不純物により単結晶半導体層が汚染されることを防ぐことができる。また、単結晶半導体層とガラス基板との界面準位密度を下げることができる。それにより、実用に耐えうる半導体装置を提供することができる。

#### 【0097】

従って、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の半導体装置を作製することができる。

#### 【0098】

##### (実施の形態2)

本実施の形態は、実施の形態1で作製される支持基板上に形成された複数の単結晶半導体層が一体化した単結晶半導体層を用いて半導体装置を作製する一例について示す。詳しく

10

20

30

40

50

は表示素子に液晶表示素子を用いる液晶表示装置について説明する。なお、実施の形態1と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

【0099】

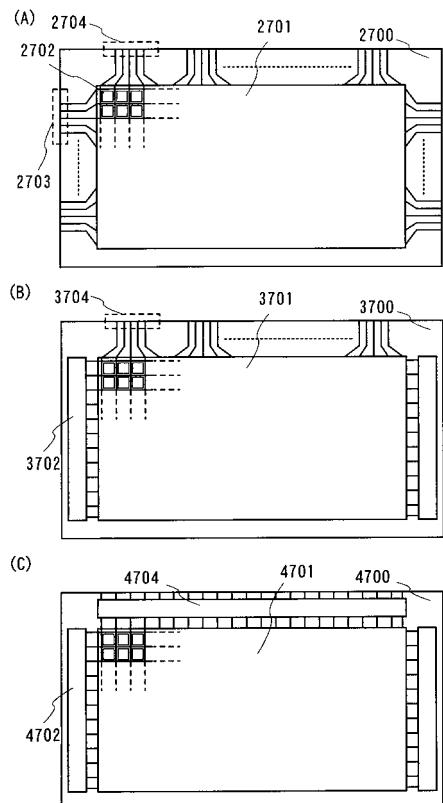

図16(A)は本発明に係る表示パネルの構成を示す上面図であり、絶縁表面を有する基板2700上に画素2702をマトリクス上に配列させた画素部2701、走査線側入力端子2703、信号線側入力端子2704が形成されている。画素数は種々の規格に従つて設ければ良く、XGAであれば $1024 \times 768 \times 3$ (RGB)、UXGAであれば $1600 \times 1200 \times 3$ (RGB)、フルスペックハイビジョンに対応させるのであれば $1920 \times 1080 \times 3$ (RGB)とすれば良い。

【0100】

画素2702は、走査線側入力端子2703から延在する走査線と、信号線側入力端子2704から延在する信号線とが交差することで、マトリクス状に配設される。画素2702のそれぞれには、スイッチング素子とそれに接続する画素電極層が備えられている。スイッチング素子の代表的な一例はTFTであり、TFTのゲート電極層側が走査線と、ソース若しくはドレイン側が信号線と接続されることにより、個々の画素を外部から入力する信号によって独立して制御可能としている。

【0101】

TFTは、その主要な構成要素として、半導体層、ゲート絶縁層及びゲート電極層が挙げられ、半導体層に形成されるソース領域及びドレイン領域に接続する配線層がそれに付随する。構造的には基板側から半導体層、ゲート絶縁層及びゲート電極層を配設したトップゲート型と、基板側からゲート電極層、ゲート絶縁層及びLPPS層を配設したボトムゲート型などが代表的に知られているが、本発明においてはそれらの構造のどのようなもの用いても良い。

【0102】

図16(A)は、走査線及び信号線へ入力する信号を、外付けの駆動回路により制御する表示パネルの構成を示しているが、COG(Chip on Glass)方式によりドライバICを基板上に実装しても良い。また他の実装形態としてTAB(Tape Automated Bonding)方式を用いてもよい。

【0103】

また、図16(B)に示すように走査線側駆動回路3702を基板3700上に形成することもできる。図16(B)において、画素部3701は、信号線側入力端子3704と接続した図16(A)と同様に外付けの駆動回路により制御する。また、図16(C)は、画素部4701、走査線駆動回路4702と、信号線駆動回路4704を基板4700上に一体形成することもできる。

【0104】

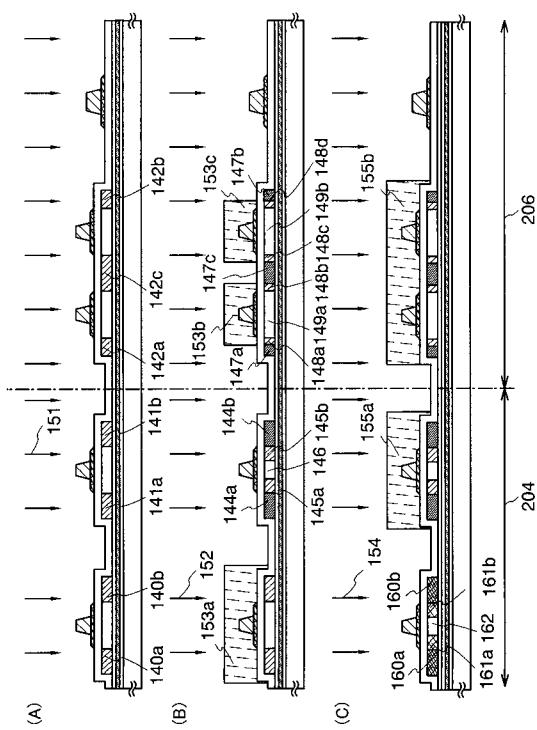

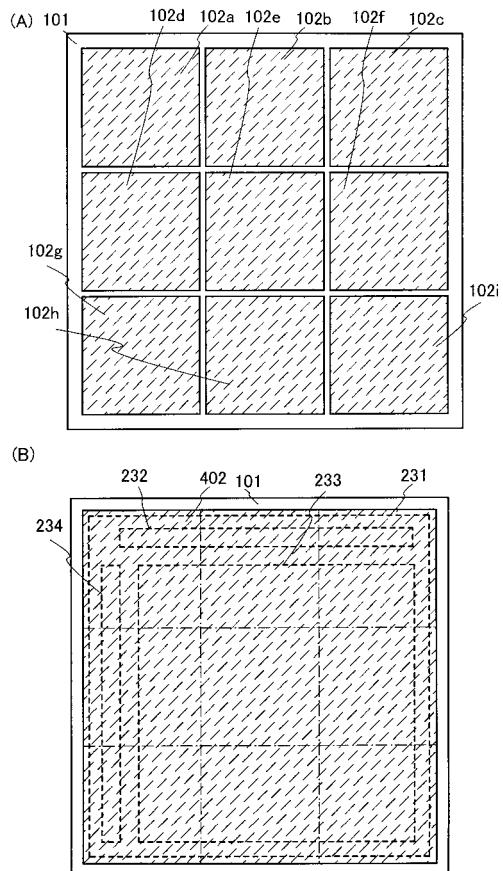

実施の形態1で示したように、ガラス基板である支持基板101の上にプロッキング層109、絶縁層104、酸化膜103が設けられ、単結晶半導体層402が形成されている(図4(A)参照。)。

【0105】

本発明を用いると、単結晶半導体層は、表示パネルを製造するマザーガラスと呼ばれる大型のガラス基板に連続膜として形成することができる。まず、実施の形態1と同様に、ガラス基板である支持基板101としてマザーガラスに複数の単結晶半導体層102(102a、102b、102c、102d、102e、102f、102g、102h、102i)を一定の間隔を有して接合する(図15(A)参照。)。次にガラス基板である支持基板101を加熱し、支持基板を収縮させることにより、単結晶半導体層102(102a、102b、102c、102d、102e、102f、102g、102h、102i)間の間隔を縮め、単結晶半導体層102(102a、102b、102c、102d、102e、102f、102g、102h、102i)同士を接させる。さらに接した状態の単結晶半導体層102(102a、102b、102c、102d、102e、102f、102g、102h、102i)にエネルギーービームを照射し、単結晶半導体

10

20

30

40

50

層 102 (102a、102b、102c、102d、102e、102f、102g、102h、102i) を一体化し、単結晶半導体層 402 を形成する (図 15 (B) 参照。)。図 15 (B) に示すように、大面積の単結晶半導体層 402 を用いて大型の半導体装置である表示パネル 231 を作製することができる。大型の表示パネル 231 には、走査線駆動回路領域 234、信号線駆動回路領域 233、画素形成領域 232 があり、これらの領域が含まれるように単結晶半導体層 402 を支持基板 101 (マザーガラス) に接合する。もちろん大面積の単結晶半導体層 402 より複数の表示パネルを切り出すことができる。

#### 【0106】

単結晶半導体層 402 にはしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型不純物を添加する。例えば、p 型不純物として硼素を  $5 \times 10^{17} \text{ cm}^{-3}$  以上  $1 \times 10^{18} \text{ cm}^{-3}$  以下の濃度で添加されていても良い。支持基板 101 にはプロッキング層 109 として窒化シリコン層と酸化シリコン層が積層形成されている。支持基板 101 にプロッキング層を設けることで、単結晶半導体層 402 の汚染を防ぐことができる。なお、窒化シリコン層に換えて、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層を適用しても良い。

#### 【0107】

単結晶半導体層 402 をエッティングして、半導体素子の配置に合わせて島状に分離した単結晶半導体層 183、184、185 を形成する。エッティングは、フォトリソグラフィなどを用いたマスクを用いて行えばよい。

#### 【0108】

エッティング加工は、プラズマエッティング (ドライエッティング) 又はウェットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、 $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、などのフッ素系又は塩素系のガスを用い、 $\text{He}$  や  $\text{Ar}$  などの不活性ガスを適宜加えても良い。また、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

#### 【0109】

本発明において、配線層若しくは電極層を形成する導電層や、所定のパターンを形成するためのマスク層などを、液滴吐出法のような選択的にパターンを形成できる方法により形成してもよい。液滴吐出 (噴出) 法 (その方式によっては、インクジェット法とも呼ばれる。) は、特定の目的に調合された組成物の液滴を選択的に吐出 (噴出) して所定のパターン (導電層や絶縁層など) を形成することができる。この際、被形成領域にぬれ性や密着性を制御する処理を行ってもよい。また、パターンが転写、または描写できる方法、例えば印刷法 (スクリーン印刷やオフセット印刷などパターンが形成される方法) なども用いることができる。

#### 【0110】

本実施の形態において、用いるマスクは、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フッ化アリーレンエーテル、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料等を用いることもできる。或いは、ポジ型レジスト、ネガ型レジストなどを用いてもよい。液滴吐出法を用いる場合、いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整する、界面活性剤等を加えるなどを行い適宜調整する。

#### 【0111】

単結晶半導体層 183、単結晶半導体層 184、単結晶半導体層 185 を覆うゲート絶縁層 107 を形成する。ゲート絶縁層 107 はプラズマ CVD 法またはスパッタ法などを用い、厚さを  $10 \sim 150 \text{ nm}$  として珪素を含む絶縁膜で形成する。ゲート絶縁層 107 としては、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の材料で形成すればよく、積層でも单層でもよい。また、絶縁層は窒

10

20

30

40

50

化珪素膜、酸化珪素膜、窒化珪素膜の3層の積層、酸化窒化珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を用いるとよい。さらに単結晶半導体層とゲート絶縁層の間に、膜厚1~100nm、好ましくは1~10nm、さらに好ましくは2~5nmである膜厚の薄い酸化珪素膜を形成してもよい。薄い酸化珪素膜の形成方法としては、G R T A法、L R T A法等を用いて半導体領域表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することができる。なお、低い成膜温度でゲートリーク電流に少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

#### 【0112】

次いで、ゲート絶縁層107上にゲート電極層として用いる膜厚20~100nmの第1の導電膜と、膜厚100~400nmの第2の導電膜とを積層して形成する。第1の導電膜及び第2の導電膜は、スパッタリング法、蒸着法、C V D法等の手法により形成することができる。第1の導電膜及び第2の導電膜はタンタル(T a)、タンゲステン(W)、チタン(T i)、モリブデン(M o)、アルミニウム(A l)、銅(C u)、クロム(C r)、ネオジム(N d)から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第1の導電膜及び第2の導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、A g P d C u合金を用いてもよい。また、2層構造に限定されず、例えば、第1の導電膜として膜厚50nmのタンゲステン膜、第2の導電膜として膜厚500nmのアルミニウムとシリコンの合金(A l - S i)膜、第3の導電膜として膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(A l - S i)膜に代えてアルミニウムとチタンの合金膜(A l - T i)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

#### 【0113】

次に、フォトリソグラフィ法を用いてレジストからなるマスク110a、マスク110b、マスク110c、マスク110d、マスク110e、及びマスク110fを形成し、第1の導電膜及び第2の導電膜を所望の形状に加工し、第1のゲート電極層120、第1のゲート電極層122、第1のゲート電極層124、第1のゲート電極層125、及び第1の導電層126、並びに導電層111、導電層112、導電層114、導電層115、及び導電層116を形成する(図4(C)参照。)。I C P (I n d u c t i v e l y C o u p l e d P l a s m a : 誘導結合型プラズマ)エッチング法を用い、エッチング条件(コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等)を適宜調節することにより、第1のゲート電極層120、第1のゲート電極層122、第1のゲート電極層124、第1のゲート電極層125、及び第1の導電層126、並びに導電層111、導電層112、導電層114、導電層115、及び導電層116を所望のテーパー形状を有するようにエッチングすることができる。また、テーパー形状は、マスク110a、マスク110b、マスク110d、マスク110e、及びマスク110fの形状によっても角度等を制御することができる。なお、エッチング用ガスとしては、C l<sub>2</sub>、B C l<sub>3</sub>、S i C l<sub>4</sub>もしくはC C l<sub>4</sub>などを代表とする塩素系ガス、C F<sub>4</sub>、S F<sub>6</sub>もしくはN F<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。本実施の形態では、C F<sub>4</sub>、C l<sub>2</sub>、O<sub>2</sub>からなるエッチング用ガスを用いて第2の導電膜のエッチングを行い、連続してC F<sub>4</sub>、C l<sub>2</sub>からなるエッチング用ガスを用いて第1の導電膜をエッチングする。

#### 【0114】

次に、マスク110a、マスク110b、マスク110d、マスク110e、及びマスク110fを用いて、導電層111、導電層112、導電層114、導電層115、及び導電層116を所望の形状に加工する。このとき、導電層を形成する第2の導電膜と、第1のゲート電極層を形成する第1の導電膜との選択比の高いエッチング条件で、導電層を工

10

20

30

40

50

ッチングする。このエッチングによって、導電層 111、導電層 112、導電層 114、導電層 115、及び導電層 116をエッチングし、第2のゲート電極層 131、第2のゲート電極層 132、第2のゲート電極層 134、第2のゲート電極層 135、及び第2の導電層 136を形成する。本実施の形態では、第2のゲート電極層及び第2の導電層もテーパー形状を有しているが、そのテーパー角度は、第1のゲート電極層 120、第1のゲート電極層 122、第1のゲート電極層 124、第1のゲート電極層 125、及び第1の導電層 126の有するテーパー角度より大きい。なおテーパー角度とは第1のゲート電極層、第2のゲート電極層、第1の導電層、第2の導電層表面に対する側面の角度である。よって、テーパー角度を大きくし、90度の場合導電層は垂直な側面を有すようになる。本実施の形態では、第2のゲート電極層及び第2の導電層を形成するためのエッチング用ガスとして  $\text{Cl}_2$ 、 $\text{SF}_6$ 、 $\text{O}_2$  を用いる。

10

#### 【0115】

本実施の形態では第1のゲート電極層、導電層、及び第2のゲート電極層をテーパー形状を有する様に形成するため、2層のゲート電極層両方がテーパー形状を有している。しかし、本発明はそれに限定されず、ゲート電極層の一層のみがテーパー形状を有し、他方は異方性エッチングによって垂直な側面を有していてもよい。本実施の形態のように、テーパー角度も積層するゲート電極層間で異なっていても良いし、同一でもよい。テーパー形状を有することによって、その上に積層する膜の被覆性が向上し、欠陥が軽減されるので信頼性が向上する。

20

#### 【0116】

以上の工程によって、周辺駆動回路領域 204 に第1のゲート電極層 120 及び第2のゲート電極層 131 からなるゲート電極層 117、第1のゲート電極層 122 及び第2のゲート電極層 132 からなるゲート電極層 118、画素領域 206 に第1のゲート電極層 124 及び第2のゲート電極層 134 からなるゲート電極層 127、第1のゲート電極層 125 及び第2のゲート電極層 135 からなるゲート電極層 128、第1の導電層 126 及び第2の導電層 136 からなる導電層 129 を形成することができる（図 4（D）参照。）。本実施の形態では、ゲート電極層の形成をドライエッチングで行うがウェットエッチングでもよい。

#### 【0117】

ゲート電極層を形成する際のエッチング工程によって、ゲート絶縁層 107 は多少エッチングされ、膜厚が減る（いわゆる膜減り）ことがある。

30

#### 【0118】

ゲート電極層を形成する際、ゲート電極層の幅を細くすることによって、高速動作が可能な薄膜トランジスタを形成することができる。ゲート電極層をチャネル方向の幅を細く形成する2つの方法を以下に示す。

#### 【0119】

第1の方法はゲート電極層のマスクを形成した後、マスクを幅方向にエッチング、アッティング等により細らせ、さらに幅の細いマスクを形成する。あらかじめ幅細い形状に形成されたマスクを用いることによって、ゲート電極層も幅細い形状に形成することができる。

40

#### 【0120】

次に、第2の方法は通常のマスクを形成し、そのマスクを用いてゲート電極層を形成する。次に得られたゲート電極層を幅方向にさらにサイドエッチングして細らせる。よって最終的に幅の細いゲート電極層を形成することができる。以上の工程を経ることによって、後にチャネル長の短い薄膜トランジスタを形成することが可能であり、高速度動作が可能な薄膜トランジスタを作製することが可能である。

#### 【0121】

次に、ゲート電極層 117、ゲート電極層 118、ゲート電極層 127、ゲート電極層 128 をマスクとして、n型を付与する不純物元素 151 を添加し、第1の n型不純物領域 140a、第1の n型不純物領域 140b、第1の n型不純物領域 141a、第1の n型不純物領域 141b、第1の n型不純物領域 142a、第1の n型不純物領域 142b、

50

第1のn型不純物領域142cを形成する(図5(A)参照。)。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン(PH<sub>3</sub>)(ドーピングガスはPH<sub>3</sub>を水素(H<sub>2</sub>)で希釈しており、ガス中のPH<sub>3</sub>の比率は5%)を用い、ガス流量80sccm、ビーム電流54μA/cm、加速電圧50kV、添加するドーザ量7.0×10<sup>13</sup>ions/cm<sup>2</sup>でドーピングを行う。ここでは、第1のn型不純物領域140a、第1のn型不純物領域140b、第1のn型不純物領域141a、第1のn型不純物領域141b、第1のn型不純物領域142a、第1のn型不純物領域142b、第1のn型不純物領域142cに、n型を付与する不純物元素が1×10<sup>17</sup>~5×10<sup>18</sup>/cm<sup>3</sup>程度の濃度で含まれるように添加する。本実施の形態では、n型を付与する不純物元素としてリン(P)を用いる。

10

#### 【0122】

本明細書では、不純物領域がゲート絶縁層を介してゲート電極層と重なる領域をLov領域と示し、不純物領域がゲート絶縁層を介してゲート電極層と重ならない領域をLoff領域と示す。図5では、不純物領域においてハッチングと白地で示されているが、これは、白地部分に不純物元素が添加されていないということを示すのではなく、この領域の不純物元素の濃度分布がマスクやドーピング条件を反映していることを直感的に理解できるようにしたためである。なお、このことは本明細書の他の図面においても同様である。

#### 【0123】

次に単結晶半導体層183、単結晶半導体層185の一部を覆うマスク153a、マスク153b、マスク153c、及びマスク153dを形成する。マスク153a、マスク153b、マスク153c、第2のゲート電極層132をマスクとしてn型を付与する不純物元素152を添加し、第2のn型不純物領域144a、第2のn型不純物領域144b、第3のn型不純物領域145a、第3のn型不純物領域145b、第2のn型不純物領域147a、第2のn型不純物領域147b、第2のn型不純物領域147c、第3のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dが形成される。本実施の形態では、不純物元素を含むドーピングガスとしてPH<sub>3</sub>(ドーピングガスはPH<sub>3</sub>を水素(H<sub>2</sub>)で希釈しており、ガス中のPH<sub>3</sub>の比率は5%)を用い、ガス流量80sccm、ビーム電流540μA/cm、加速電圧70kV、添加するドーザ量5.0×10<sup>15</sup>ions/cm<sup>2</sup>でドーピングを行う。ここでは、第2のn型不純物領域144a、第2のn型不純物領域144bにn型を付与する不純物元素が5×10<sup>19</sup>~5×10<sup>20</sup>/cm<sup>3</sup>程度の濃度で含まれるように添加する。第3のn型不純物領域145a、第3のn型不純物領域145bは、第3のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dと同程度、もしくは少し高めの濃度でn型を付与する不純物元素を含むように形成される。また、単結晶半導体層184にチャネル形成領域146、単結晶半導体層185にチャネル形成領域149a及びチャネル形成領域149bが形成される(図5(B)参照。)。

20

#### 【0124】

第2のn型不純物領域144a、第2のn型不純物領域144b、第2のn型不純物領域147a、第2のn型不純物領域147b、第2のn型不純物領域147cは高濃度n型不純物領域であり、ソース、ドレインとして機能する。一方、第3のn型不純物領域145a、第3のn型不純物領域145b、第3のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dは低濃度n型不純物領域であり、LDD(Lightly Doped Drain)領域となる。第3のn型不純物領域145a、第3のn型不純物領域145bは、ゲート絶縁層107を介して、第1のゲート電極層122に覆われているのでLov領域であり、ドレイン近傍の電界を緩和し、ホットキャリアによるオン電流の劣化を抑制することができる。この結果、高速動作が可能な薄膜トランジスタを形成することができる。一方、第3のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dはゲート電極層127、ゲート電極層128に覆われ

30

40

50

ていない L o f f 領域に形成されるため、オフ電流を低減する効果がある。この結果、信頼性の高く、低消費電力の半導体装置を作製することが可能である。

#### 【 0 1 2 5 】

次に、マスク 153a、マスク 153b、及びマスク 153c を除去し、単結晶半導体層 183、単結晶半導体層 185 を覆うマスク 155a、マスク 155b を形成する。マスク 155a、マスク 155b、ゲート電極層 117 をマスクとして p 型を付与する不純物元素 154 を添加し、第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b が形成される。本実施の形態では、不純物元素としてボロン (B) を用いるため、不純物元素を含むドーピングガスとしてジボラン (B<sub>2</sub>H<sub>6</sub>) (ドーピングガスは B<sub>2</sub>H<sub>6</sub> を水素 (H<sub>2</sub>) で希釈しており、ガス中の B<sub>2</sub>H<sub>6</sub> の比率は 15 %) を用い、ガス流量 70 sccm、ビーム電流 180 μA/cm、加速電圧 80 kV、添加するドーズ量 2.0 × 10<sup>15</sup> ions/cm<sup>2</sup> でドーピングを行う。ここでは、第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b に p 型を付与する不純物元素が 1 × 10<sup>-2</sup> ~ 5 × 10<sup>-2</sup> / cm<sup>3</sup> 程度の濃度で含まれるように添加する。本実施の形態では、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b は、ゲート電極層 117 の形状を反映し、自己整合的に第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b より低濃度となるように形成する。また、単結晶半導体層 183 にチャネル形成領域 162 が形成される (図 5 (C) 参照。)。

#### 【 0 1 2 6 】

第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b は高濃度 p 型不純物領域であり、ソース、ドレインとして機能する。一方、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b は低濃度不純物領域であり、L D D (Lightly Doped Drain) 領域となる。第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b は、ゲート絶縁層 107 を介して、第 1 のゲート電極層 120 に覆われているので L o v 領域であり、ドレイン近傍の電界を緩和し、ホットキャリアによるオン電流の劣化を抑制することが可能である。

#### 【 0 1 2 7 】

マスク 155a、マスク 155b を O<sub>2</sub> アッシングやレジスト剥離液により除去し、酸化膜も除去する。その後、ゲート電極層の側面を覆うように、絶縁膜、いわゆるサイドウォールを形成してもよい。サイドウォールは、プラズマ C V D 法や減圧 C V D (L P C V D) 法を用いて、珪素を有する絶縁膜により形成することができる。

#### 【 0 1 2 8 】

不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と単結晶半導体層との界面へのプラズマダメージを回復することができる。

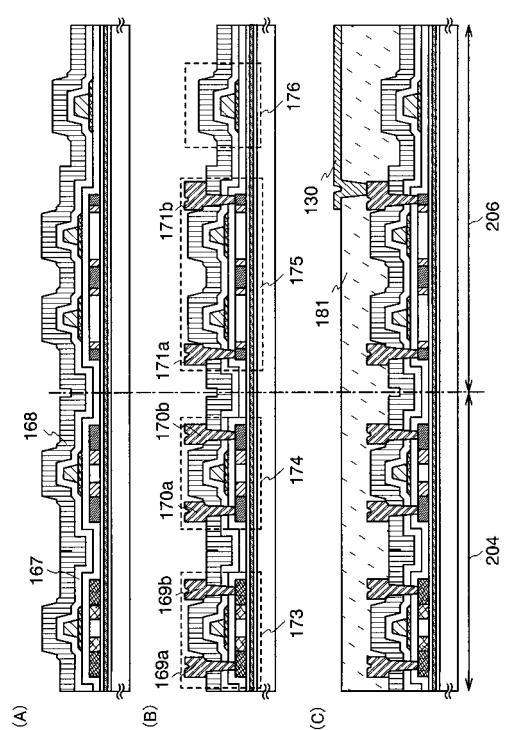

#### 【 0 1 2 9 】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、絶縁膜 167 と絶縁膜 168 との積層構造とする (図 6 (A) 参照。)。絶縁膜 167 として窒化酸化珪素膜を膜厚 100 nm 形成し、絶縁膜 168 として酸化窒化珪素膜を膜厚 900 nm 形成し、積層構造とする。また、ゲート電極層、ゲート絶縁層を覆って、酸化窒化珪素膜を膜厚 30 nm 形成し、窒化酸化珪素膜を膜厚 140 nm 形成し、酸化窒化珪素膜を膜厚 800 nm 形成し、3 層の積層構造としてもよい。本実施の形態では、絶縁膜 167 及び絶縁膜 168 を下地膜と同様にプラズマ C V D 法を用いて連続的に形成する。絶縁膜 167 と絶縁膜 168 は上記材料に限定されるものでなく、スパッタ法、またはプラズマ C V D を用いた窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または 3 層以上の積層構造として用いても良い。

#### 【 0 1 3 0 】

絶縁膜 167、絶縁膜 168 としては他に窒化アルミニウム (AlN)、酸化窒化アルミニウム (AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム (AlN)

10

20

30

40

50

O ) または酸化アルミニウム、ダイアモンドライクカーボン ( D L C ) 、窒素含有炭素膜 ( C N ) その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、 Si - O - Si 結合を含む樹脂に相当する。シロキサンは、シリコン ( Si ) と酸素 ( O ) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 ( 例えはアルキル基、アリール基 ) が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、ポリシラザンを用いることができる。平坦性のよい塗布法によって形成される塗布膜を用いてもよい。

10

### 【 0 1 3 1 】

次いで、レジストからなるマスクを用いて絶縁膜 1 6 7 、絶縁膜 1 6 8 、ゲート絶縁層 1 0 7 に単結晶半導体層及びゲート電極層に達するコンタクトホール ( 開口部 ) を形成する。エッチングは、用いる材料の選択比によって、一回で行っても複数回行っても良い。本実施の形態では、酸化窒化珪素膜である絶縁膜 1 6 8 と、窒化酸化珪素膜である絶縁膜 1 6 7 及びゲート絶縁層 1 0 7 と選択比が取れる条件で、第 1 のエッチングを行い、絶縁膜 1 6 8 を除去する。次に第 2 のエッチングによって、絶縁膜 1 6 7 及びゲート絶縁層 1 0 7 を除去し、ソース領域又はドレイン領域である第 1 の p 型不純物領域 1 6 0 a 、第 1 の p 型不純物領域 1 6 0 b 、第 2 の n 型不純物領域 1 4 4 a 、第 2 の n 型不純物領域 1 4 4 b 、第 2 の n 型不純物領域 1 4 7 a 、第 2 の n 型不純物領域 1 4 7 b に達する開口部を形成する。本実施の形態では、第 1 のエッチングをウェットエッチングによって行い、第 2 のエッチングをドライエッチングによって行う。ウェットエッチングのエッチャントは、フッ素水素アンモニウム及びフッ化アンモニウムを含む混合溶液のようなフッ酸系の溶液を用いるとよい。エッチング用ガスとしては、 C l <sub>2</sub> 、 B C l <sub>3</sub> 、 S i C l <sub>4</sub> もしくは C C l <sub>4</sub> などを代表とする塩素系ガス、 C F <sub>4</sub> 、 S F <sub>6</sub> もしくは N F <sub>3</sub> などを代表とするフッ素系ガス又は O <sub>2</sub> を適宜用いることができる。また用いるエッチング用ガスに不活性気体を添加してもよい。添加する不活性元素としては、 H e 、 N e 、 A r 、 K r 、 X e から選ばれた一種または複数種の元素を用いることができる。

20

### 【 0 1 3 2 】

開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又はドレイン領域の一部とそれ電気的に接続するソース電極層又はドレイン電極層 1 6 9 a 、ソース電極層又はドレイン電極層 1 6 9 b 、ソース電極層又はドレイン電極層 1 7 0 a 、ソース電極層又はドレイン電極層 1 7 0 b 、ソース電極層又はドレイン電極層 1 7 1 a 、ソース電極層又はドレイン電極層 1 7 1 b を形成する。ソース電極層又はドレイン電極層は、 P V D 法、 C V D 法、蒸着法等により導電膜を成膜した後、所望の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電解メッキ法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、 A g 、 A u 、 C u 、 N i 、 P t 、 P d 、 I r 、 R h 、 W 、 A l 、 T a 、 M o 、 C d 、 Z n 、 F e 、 T i 、 Z r 、 B a 等の金属、及び S i 、 G e 、又はその合金、若しくはその窒化物を用いて形成する。また、これらの積層構造としても良い。本実施の形態では、チタン ( T i ) を膜厚 6 0 n m 形成し、窒化チタン膜を膜厚 4 0 n m 形成し、アルミニウムを膜厚 7 0 0 n m 形成し、チタン ( T i ) を膜厚 2 0 0 n m 形成して積層構造とし、所望な形状に加工する。

30

### 【 0 1 3 3 】

以上の工程で周辺駆動回路領域 2 0 4 に L o v 領域に p 型不純物領域を有する p チャネル型薄膜トランジスタであるトランジスタ 1 7 3 、 L o v 領域に n 型不純物領域を有する n チャネル型薄膜トランジスタであるトランジスタ 1 7 4 を、画素領域 2 0 6 に L o f f 領域に n 型不純物領域を有するマルチチャネル型の n チャネル型薄膜トランジスタであるトランジスタ 1 7 5 、容量素子 1 7 6 を有するアクティブマトリクス基板を作製することができる ( 図 6 ( C ) 参照。 ) 。そして、アクティブマトリクス基板は、液晶表示素子を有

40

50

する表示装置に用いることができる。

【0134】

単結晶半導体層を用いることにより、画素領域と駆動回路領域を同一ガラス基板上に一体形成することができる。その場合、画素領域のトランジスタ175と、駆動回路領域のトランジスタ173、174とは同時に形成される。駆動回路領域に用いるトランジスタは、CMOS回路を構成する。

【0135】

本実施の形態に限定されず、画素領域の薄膜トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、周辺駆動回路領域の薄膜トランジスタも、シングルゲート構造、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

10

【0136】

なお、本実施の形態で示した薄膜トランジスタの作製方法に限らず、あるいはチャネル領域の上下にゲート絶縁膜を介して配置された2つのゲート電極層を有する、デュアルゲート型においても本発明は適用できる。

【0137】

次に第2の層間絶縁層として絶縁膜181を形成する(図6(C)参照。)。

【0138】

絶縁膜181としては酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素膜(CN)、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜、ポリシリザン、その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、感光性、非感光性どちらでも良く、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテンを用いることができる。

20

【0139】

本実施の形態では、平坦化のために設ける層間絶縁層としては、耐熱性および絶縁性が高く、且つ、平坦化率の高いものが要求されるので、絶縁膜181の形成方法としては、スピンドルコート法で代表される塗布法を用いると好ましい。

30

【0140】

絶縁膜181の形成方法としては、ディップ、スプレー塗布、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー、CVD法、蒸着法等を採用することができる。液滴吐出法により絶縁膜181を形成してもよい。液滴吐出法を用いた場合には材料液を節約することができる。また、液滴吐出法のようにパターンが転写、または描写できる方法、例えば印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)なども用いることができる。

【0141】

次に、画素領域206の絶縁膜181に微細な開口、つまりコンタクトホールを形成する。

40

【0142】

そして、並行平板RIE装置を用いて、絶縁膜181をエッチングする。なおエッチング時間は、配線層や絶縁膜168がオーバーエッチングされる程度とするとよい。このようにオーバーエッチングされる程度とすると、基板内の膜厚バラツキと、エッチングレートのバラツキを低減することができる。

【0143】

またエッチング装置にICP装置を用いてもよい。以上の工程で、画素領域206にソース電極層又はドレイン電極層171bに達する開口を形成する。

【0144】

50

次に、ソース電極層又はドレイン電極層と接するように、画素電極層 130 を形成する。画素電極層 130 は、インジウム錫酸化物 (ITO)、酸化インジウムに酸化亜鉛 (ZnO) を混合したIZO (indium zinc oxide)、酸化インジウムに酸化珪素 (SiO<sub>2</sub>) を混合した導電性材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、又はタンゲステン (W)、モリブデン (Mo)、ジルコニウム (Zr)、ハフニウム (Hf)、バナジウム (V)、ニオブ (Nb)、タンタル (Ta)、クロム (Cr)、コバルト (Co)、ニッケル (Ni)、チタン (Ti)、白金 (Pt)、アルミニウム (Al)、銅 (Cu)、銀 (Ag) 等の金属又はその合金、若しくはその金属窒化物を用いて形成することができる。 10

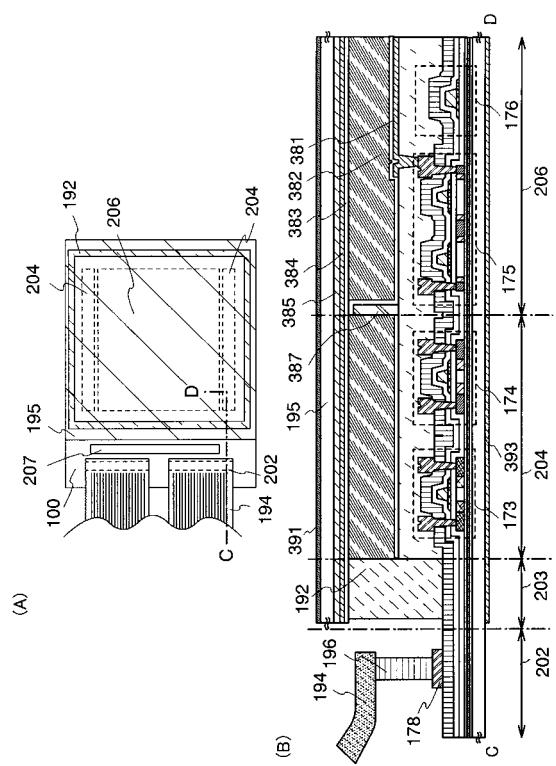

#### 【0145】

図7は、半導体装置の平面図及び断面図を示しており、図7(A)は半導体装置の平面図、図7(B)は図7(A)において線C-Dの断面図である。FPCの貼り付け部である外部端子接続領域202、封止領域203、周辺駆動回路領域204、画素領域206である。外部端子接続領域202には、外部端子と接続する端子電極層178が設けられている。

#### 【0146】

次に、画素電極層130及び絶縁膜181を覆うように、印刷法や液滴吐出法により、配向膜と呼ばれる絶縁層381を形成する。なお、絶縁層381は、スクリーン印刷法やオフセット印刷法を用いれば、選択的に形成することができる。その後、ラビング処理を行う。このラビング処理は液晶のモード、例えばVAモードのときには処理を行わないことがある。配向膜として機能する絶縁層383も絶縁層381と同様である。続いて、シール材192を液滴吐出法により画素を形成した周辺の領域に形成する。 20

#### 【0147】

その後、配向膜として機能する絶縁層383、対向電極として機能する導電層384、カラーフィルタとして機能する着色層385、偏光子391(偏光板ともいう)が設けられた対向基板195と、TFT基板である支持基板101とをスペーサ387を介して貼り合わせ、その空隙に液晶層382を設ける。本実施の形態の液晶表示装置は透過型であるため、支持基板101の素子を有する面と反対側にも偏光子(偏光板)143を設ける。偏光子は、接着層によって基板に設けることができる。シール材にはフィラーが混入されても良く、さらに対向基板195には、遮蔽膜(ブラックマトリクス)などが形成されても良い。なお、カラーフィルタ等は、液晶表示装置をフルカラー表示とする場合、赤色(R)、緑色(G)、青色(B)を呈する材料から形成すればよく、モノカラー表示とする場合、着色層を無くす、もしくは少なくとも一つの色を呈する材料から形成すればよい。 30

#### 【0148】

なお、バックライトにRGBの発光ダイオード(LED)等を配置し、時分割によりカラー表示する継時加法混色法(フィールドシーケンシャル法)を採用するときには、カラーフィルタを設けない場合がある。ブラックマトリクスは、トランジスタやCMOS回路の配線による外光の反射を低減するため、トランジスタやCMOS回路と重なるように設けるとよい。なお、ブラックマトリクスは、容量素子に重なるように形成してもよい。容量素子を構成する金属膜による反射を防止することができるからである。 40

#### 【0149】

液晶層を形成する方法として、ディスペンサ式(滴下式)や、素子を有する支持基板101と対向基板195とを貼り合わせてから毛細管現象を用いて液晶を注入する注入法を用いることができる。滴下法は、注入法を適用しづらい大型基板を扱うときに適用するとい。

#### 【0150】

スペーサは数μmの粒子を散布して設ける方法でも良く、基板全面に樹脂膜を形成した後これをエッチング加工して形成する方法でもよい。このようなスペーサの材料を、スピナ

10

20

30

40

50

ーで塗布した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンなどで150～200で加熱して硬化させる。このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせることができるが、好ましくは、スペーサの形状は柱状で頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示装置としての機械的な強度を確保することができる。形状は円錐状、角錐状などを用いることができ、特別な限定はない。

#### 【0151】

続いて、画素領域と電気的に接続されている端子電極層178に、異方性導電体層196を介して、接続用の配線基板であるFPC194を設ける。FPC194は、外部からの信号や電位を伝達する役目を担う。上記工程を経て、表示機能を有する液晶表示装置を作製することができる。

10

#### 【0152】

偏光板と、液晶層との間に位相差板を有した状態で積層してもよい。また、外光の視認側への反射を防ぐ反射防止膜を最視認側に設けても良い。

#### 【0153】

本実施の形態において用いる半導体層は、本発明を用いた単結晶半導体層を用いることができる。支持基板であるガラス基板上に複数の単結晶半導体層を一定の間隔を有して隣接して設けた後、支持基板を熱処理する。この熱処理により支持基板は収縮し、それに伴い隣接する単結晶半導体層同士が接する。複数の単結晶半導体層同士を接させた状態でエネルギーービーム照射を行い、複数の単結晶半導体層を一体化し、連続的な単結晶半導体層を形成する。エネルギーービームとしてはレーザ光が好ましい。

20

#### 【0154】

支持基板への熱処理により、支持基板上の複数の単結晶半導体層同士の間隔を無くし、接するように、支持基板への熱処理の条件、及び単結晶半導体層の間隔を設定する。支持基板を収縮するように変形させるため、熱処理温度は支持基板の歪み点以上の温度が好ましい。単結晶半導体層間の間隔は基となる半導体基板の大きさや、支持基板の大きさにもよるが、例えば、0.1μm以上1μm以下とすればよい。この熱処理は減圧下で行っても、大気圧下で行ってもよく、雰囲気も窒素雰囲気下、酸素雰囲気下などで行ってもよい。

#### 【0155】

熱処理による支持基板の収縮を、予め設けた単結晶半導体層間の間隔を消失させることに利用するので、支持基板及び単結晶半導体層の反りや支持基板と単結晶半導体層の膜剥がれを防止することができる。さらに、複数の単結晶半導体層を一体化し連続膜とすることができるため、大面積の単結晶半導体層を有するSOI基板を製造することが可能となる。

30

#### 【0156】

半導体基板に対しては、支持基板の歪み点以上の高温熱処理を行い、支持基板に対しては歪み点温度以下でブロッキング層を設け、その両者を接合させることにより、不純物により単結晶半導体層が汚染されることを防ぐことができる。また、単結晶半導体層と支持基板との界面準位密度を下げることができる。それにより、実用に耐えうる半導体装置を提供することができる。

40

#### 【0157】

従って、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の液晶表示素子を有する半導体装置を作製することができる。

#### 【0158】

##### (実施の形態3)

本発明を適用して発光素子を有する半導体装置を形成することができるが、該発光素子から発せられる光は、下面放射、上面放射、両面放射のいずれかを行う。本実施の形態では、下面放射型、両面放射型、上面放射型の高性能及び高信頼性を付与された半導体装置として表示機能を有する半導体装置（表示装置、発光装置ともいう）を歩留まり良く生産することを目的とした半導体装置の作製方法の例を、図8、図9、図10を用いて説明する

50

。

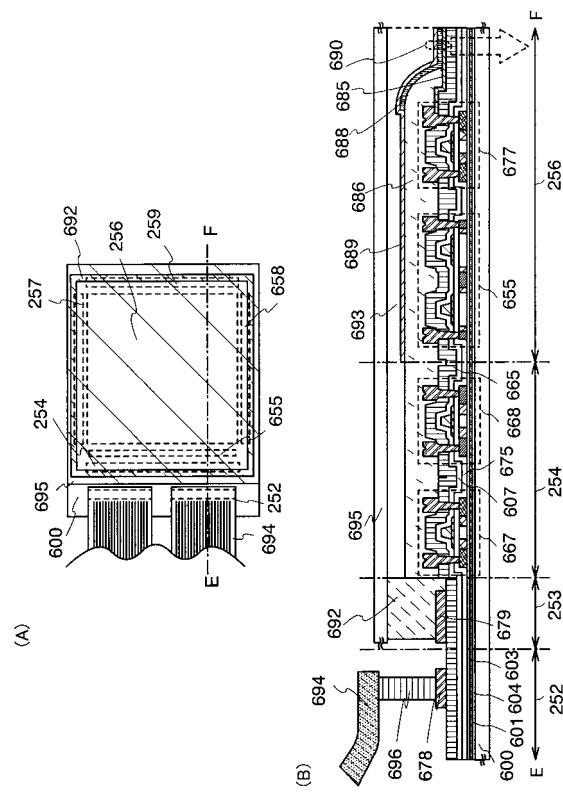

## 【0159】

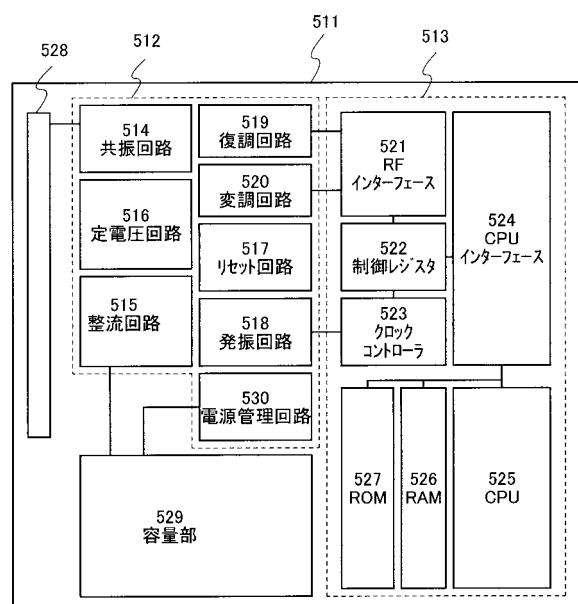

図8の半導体装置は、矢印の方向に下面射出する構造である。図8において、図8(A)は半導体装置の平面図であり、図8(B)は、図8(A)において線E-Fの断面図である。図8において半導体装置は、外部端子接続領域252、封止領域253、駆動回路領域254、画素領域256を有している。

## 【0160】

図8に示す半導体装置は、素子基板600、薄膜トランジスタ655、薄膜トランジスタ677、薄膜トランジスタ667、薄膜トランジスタ668、第1の電極層685と発光層688と第2の電極層689とを含む発光素子690、充填材693、シール材692、ブロッキング層601、絶縁層604、酸化膜603、ゲート絶縁層675、絶縁膜607、絶縁膜665、絶縁層686、封止基板695、配線層679、端子電極層678、異方性導電層696、FPC694によって構成されている。半導体装置は、外部端子接続領域252、封止領域253、駆動回路領域254、画素領域256を有している。充填材693は、液状の組成物の状態で、滴下法によって形成することができる。滴下法によって充填材が形成された素子基板600と封止基板695を張り合わせて半導体装置(発光表示装置)を封止する。

## 【0161】

図8の半導体装置において、第1の電極層685は、発光素子690より射出する光を透過できるように、透光性を有する導電性材料を用い、一方第2の電極層689は発光素子690より射出する光を反射する、反射性を有する導電性材料を用いて形成する。

## 【0162】

第2の電極層689としては、反射性を有すればよいので、チタン、タンゲステン、ニッケル、金、白金、銀、銅、タンタル、モリブデン、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いればよい。好ましくは、可視光の領域で反射性が高い物質を用いることがよく、本実施の形態では、アルミニウム膜を用いる。

## 【0163】

第1の電極層685に、具体的には透光性を有する導電性材料からなる透明導電膜を用いればよく、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いることができる。

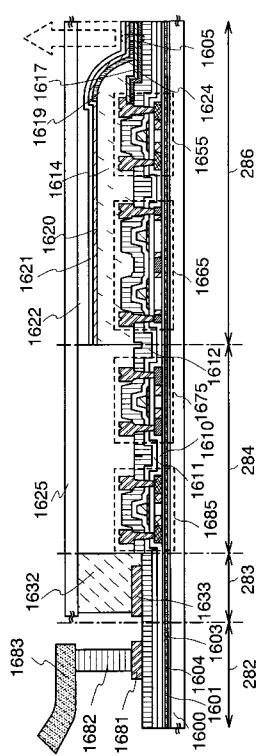

## 【0164】

図9の半導体装置は、矢印の方向に上面射出する構造である。図9に示す半導体装置は、素子基板1600、薄膜トランジスタ1655、薄膜トランジスタ1665、薄膜トランジスタ1675、薄膜トランジスタ1685、配線層1624、第1の電極層1617、発光層1619、第2の電極層1620、充填材1622、シール材1632、ブロッキング層1601、絶縁層1604、酸化膜1603、ゲート絶縁層1610、絶縁膜1611、絶縁膜1612、絶縁層1614、封止基板1625、配線層1633、端子電極層1681、異方性導電層1682、FPC1683によって構成されている。

## 【0165】

図9において半導体装置は、外部端子接続領域282、封止領域283、駆動回路領域284、画素領域286を有している。図9の半導体装置は、第1の電極層1617の下に、反射性を有する金属層である配線層1624を形成する。配線層1624の上に透明導電膜である第1の電極層1617を形成する。配線層1624としては、反射性を有すればよいので、チタン、タンゲステン、ニッケル、金、白金、銀、銅、タンタル、モリブデン、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いればよい。好ましくは、可視光の領域で反射性が高い物質を用いること

10

20

30

40

50

がよい。また、第1の電極層1617にも上記反射性を有する導電膜を用いてもよく、その場合、反射性を有する配線層1624は設けなくてもよい。

【0166】

第1の電極層1617及び第2の電極層1620に、具体的には透光性を有する導電性材料からなる透明導電膜を用いればよく、酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いることができる。

【0167】

また、透光性を有さない金属膜のような材料であっても膜厚を薄く(好ましくは、5nm～30nm程度の厚さ)して光を透過可能な状態としておくことで、第1の電極層685、第2の電極層1620から光を放射することが可能となる。また、第1の電極層685、第2の電極層1620に用いることのできる金属薄膜としては、チタン、タンゲスタン、ニッケル、金、白金、銀、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いることができる。

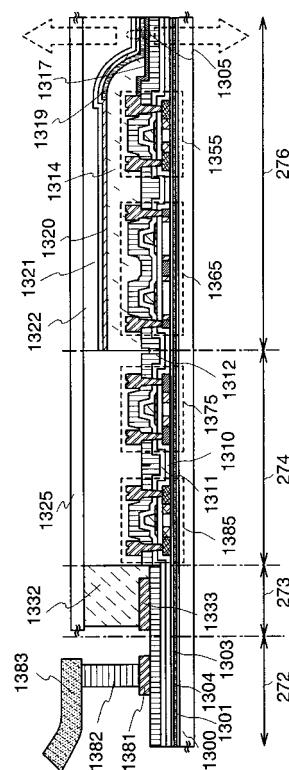

【0168】

図10に示す半導体装置は、素子基板1300、薄膜トランジスタ1355、薄膜トランジスタ1365、薄膜トランジスタ1375、薄膜トランジスタ1385、第1の電極層1317、発光層1319、第2の電極層1320、充填材1322、シール材1332、プロッキング層1301、絶縁層1304、酸化膜1303、ゲート絶縁層1310、絶縁膜1311、絶縁膜1312、絶縁層1314、封止基板1325、配線層1333、端子電極層1381、異方性導電層1382、FPC1383によって構成されている。半導体装置は、外部端子接続領域272、封止領域273、駆動回路領域274、画素領域276を有している。

【0169】

図10の半導体装置は、両面放射型であり、矢印の方向に素子基板1300側からも、封止基板1325側からも光を放射する構造である。よって、第1の電極層1317及び第2の電極層1320として透光性電極層を用いる。

【0170】

本実施の形態においては、透光性電極層である第1の電極層1317及び第2の電極層1320に、具体的には透光性を有する導電性材料からなる透明導電膜を用いればよく、酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いることができる。

【0171】

また、透光性を有さない金属膜のような材料であっても膜厚を薄く(好ましくは、5nm～30nm程度の厚さ)して光を透過可能な状態としておくことで、第1の電極層1317及び第2の電極層1320から光を放射することが可能となる。また、第1の電極層1317及び第2の電極層1320に用いることのできる金属薄膜としては、チタン、タンゲスタン、ニッケル、金、白金、銀、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いることができる。

【0172】

以上のように、図10の半導体装置は、発光素子1305より放射される光が、第1の電極層1317及び第2の電極層1320両方を通過して、両面から光を放射する構成となる。

【0173】

発光素子を用いて形成する半導体装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。また、デジタル駆動、アナログ駆動どちらで

10

20

30

40

50

も適用可能である。

【0174】

封止基板にカラーフィルタ(着色層)を形成してもよい。カラーフィルタ(着色層)は、蒸着法や液滴吐出法によって形成することができ、カラーフィルタ(着色層)を用いると、高精細な表示を行うこともできる。カラーフィルタ(着色層)により、各RGBの発光スペクトルにおいてプロードなピークが鋭いピークになるように補正できるからである。

【0175】

単色の発光を示す材料を形成し、カラーフィルタや色変換層を組み合わせることによりフルカラー表示を行うことができる。カラーフィルタ(着色層)や色変換層は、例えば封止基板に形成し、素子基板へ張り合わせればよい。

10

【0176】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの半導体装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

【0177】

単結晶半導体層を用いることにより、画素領域と駆動回路領域を同一基板上に一体形成することができる。その場合、画素領域のトランジスタと、駆動回路領域のトランジスタとは同時に形成される。

【0178】

図8乃至図10に示す本実施の形態の半導体装置に設けられるトランジスタは、実施の形態2で示したトランジスタと同様に作製することができる。

20

【0179】

図8乃至図10においても単結晶半導体層が接合される素子基板600、1300、1600としてガラス基板を用いる。

【0180】

本実施の形態の図8乃至図10において用いる半導体層は、本発明を用いた単結晶半導体層を用いることができる。素子基板600、1300、1600である支持基板上に複数の単結晶半導体層を一定の間隔を有して隣接して設けた後、支持基板を熱処理する。この熱処理により支持基板は収縮し、それに伴い隣接する単結晶半導体層同士が接する。複数の単結晶半導体層同士を接させた状態でエネルギーービーム照射を行い、複数の単結晶半導体層を一体化し、連続的な単結晶半導体層を形成する。エネルギーービームとしてはレーザ光が好ましい。

30

【0181】

支持基板への熱処理により、支持基板上の複数の単結晶半導体層同士の間隔を無くし、接するように、支持基板への熱処理の条件、及び単結晶半導体層の間隔を設定する。支持基板を収縮するように変形させるため、熱処理温度は支持基板の歪み点以上の温度が好ましい。単結晶半導体層間の間隔は基となる半導体基板の大きさや、支持基板の大きさにもよるが、例えば、0.1μm以上1μm以下とすればよい。この熱処理は減圧下で行っても、大気圧下で行ってもよく、雰囲気も窒素雰囲気下、酸素雰囲気下などで行ってもよい。

【0182】

熱処理による支持基板の収縮を、予め設けた単結晶半導体層間の間隔を消失させることに利用するので、支持基板及び単結晶半導体層の反りや支持基板と単結晶半導体層の膜剥がれを防止することができる。さらに、複数の単結晶半導体層を一体化し連続膜とすることができますため、大面積の単結晶半導体層を有するSOI基板を製造することが可能となる。

40

【0183】

半導体基板に対しては、支持基板の歪み点以上の高温熱処理を行い、支持基板に対しては歪み点温度以下でブロッキング層を設け、その両者を接合させることにより、不純物により単結晶半導体層が汚染されることを防ぐことができる。また、単結晶半導体層と支持基板との界面準位密度を下げることができる。それにより、実用に耐えうる半導体装置を提

50

供することができる。

【0184】

従って、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の半導体装置を作製することができる。

【0185】

本実施の形態は、上記の実施の形態1と適宜組み合わせることができる。

【0186】

(実施の形態4)

本実施の形態では、高性能及び高信頼性を付与された半導体装置として表示機能を有する半導体装置（表示装置、発光装置ともいう）の例について説明する。詳しくは表示素子に発光素子を用いる発光表示装置について説明する。

10

【0187】

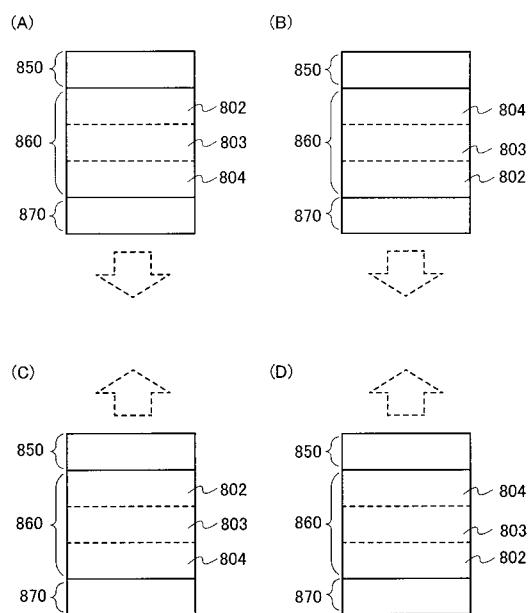

本実施の形態では、本発明の表示装置の表示素子として適用することのできる発光素子の構成を、図13を用いて説明する。

【0188】

図13は発光素子の素子構造であり、第1の電極層870と第2の電極層850との間に、EL層860が挟持されている発光素子である。EL層860は、図示した通り、第1の層804、第2の層803、第3の層802から構成されている。図13において第2の層803は発光層であり、第1の層804及び第3の層802は機能層である。

20

【0189】

第1の層804は、第2の層803に正孔（ホール）を輸送する機能を担う層である。図13では第1の層804に含まれる正孔注入層は、正孔注入性の高い物質を含む層である。モリブデン酸化物やバナジウム酸化物、ルテニウム酸化物、タンゲステン酸化物、マンガン酸化物等を用いることができる。この他、フタロシアニン（略称：H<sub>2</sub>PC）や銅フタロシアニン（CuPC）等のフタロシアニン系の化合物、4,4'-ビス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ビフェニル（略称：DPA B）、4,4'-ビス(N-[4-[N-(3-メチルフェニル)-N-フェニルアミノ]フェニル]-N-フェニルアミノ)ビフェニル（略称：DNTPD）等の芳香族アミン化合物、或いはポリ(エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)(PEDOT/PSS)等の高分子等によっても第1の層804を形成することができる。

30

【0190】

また、正孔注入層として、有機化合物と無機化合物とを複合してなる複合材料を用いることができる。特に、有機化合物と、有機化合物に対して電子受容性を示す無機化合物とを含む複合材料は、有機化合物と無機化合物との間で電子の授受が行われ、キャリア密度が増大するため、正孔注入性、正孔輸送性に優れている。

【0191】

また、正孔注入層として有機化合物と無機化合物とを複合してなる複合材料を用いた場合、電極層とオーム接触をすることが可能となるため、仕事関数に関わらず電極層を形成する材料を選ぶことができる。

40

【0192】

複合材料に用いる無機化合物としては、遷移金属の酸化物であることが好ましい。また元素周期表における第4族乃至第8族に属する金属の酸化物を挙げることができる。具体的には、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンゲステン、酸化マンガン、酸化レニウムは電子受容性が高いため好ましい。中でも特に、酸化モリブデンは大気中で安定であり、吸湿性が低く、扱いやすいため好ましい。

【0193】

複合材料に用いる有機化合物としては、芳香族アミン化合物、カルバゾール誘導体、芳香族炭化水素、高分子化合物（オリゴマー、デンドリマー、ポリマー等）など、種々の化合物を用いることができる。なお、複合材料に用いる有機化合物としては、正孔輸送性の高い有機化合物であることが好ましい。具体的には、10<sup>-6</sup> cm<sup>2</sup> / V s 以上の正孔移動

50

度を有する物質であることが好ましい。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。以下では、複合材料に用いることのできる有機化合物を具体的に列挙する。

【0194】

例えば、芳香族アミン化合物としては、N,N'-ジ(p-トリル)-N,N'-ジフェニル-p-フェニレンジアミン(略称: DTDPPA)、4,4'-ビス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ビフェニル(略称: DPAB)、4,4'-ビス(N-[4-[N-(3-メチルフェニル)-N-フェニルアミノ]フェニル]-N-フェニルアミノ)ビフェニル(略称: DNTPD)、1,3,5-トリス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ベンゼン(略称: DPAB3B)等を挙げができる。

10

【0195】

複合材料に用いることのできるカルバゾール誘導体としては、具体的には、3-[N-(9-フェニルカルバゾール-3-イル)-N-フェニルアミノ]-9-フェニルカルバゾール(略称: PCzPCA1)、3,6-ビス[N-(9-フェニルカルバゾール-3-イル)-N-フェニルアミノ]-9-フェニルカルバゾール(略称: PCzPCA2)、3-[N-(1-ナフチル)-N-(9-フェニルカルバゾール-3-イル)アミノ]-9-フェニルカルバゾール(略称: PCzPCN1)等を挙げができる。

【0196】

また、4,4'-ジ(N-カルバゾリル)ビフェニル(略称: CBP)、1,3,5-トリス[4-(N-カルバゾリル)フェニル]ベンゼン(略称: TCPB)、9-[4-(N-カルバゾリル)]フェニル-10-フェニルアントラセン(略称: CZPA)、1,4-ビス[4-(N-カルバゾリル)フェニル]-2,3,5,6-テトラフェニルベンゼン等を用いることができる。

20

【0197】

また、複合材料に用いることのできる芳香族炭化水素としては、例えば、2-tert-ブチル-9,10-ジ(2-ナフチル)アントラセン(略称: t-BuDNA)、2-tert-ブチル-9,10-ジ(1-ナフチル)アントラセン、9,10-ビス(3,5-ジフェニルフェニル)アントラセン(略称: DPPA)、2-tert-ブチル-9,10-ビス(4-フェニルフェニル)アントラセン(略称: t-BuDBA)、9,10-ジ(2-ナフチル)アントラセン(略称: DNA)、9,10-ジフェニルアントラセン(略称: DPAnth)、2-tert-ブチルアントラセン(略称: t-BuAnth)、9,10-ビス(4-メチル-1-ナフチル)アントラセン(略称: DMNA)、2-tert-ブチル-9,10-ビス[2-(1-ナフチル)フェニル]アントラセン、9,10-ビス[2-(1-ナフチル)フェニル]アントラセン、2,3,6,7-テトラメチル-9,10-ジ(1-ナフチル)アントラセン、2,3,6,7-テトラメチル-9,10-ジ(2-ナフチル)アントラセン、9,9'-ビアントリル、10,10'-ジフェニル-9,9'-ビアントリル、10,10'-ビス(2-フェニルフェニル)-9,9'-ビアントリル、10,10'-ビス[(2,3,4,5,6-ペンタフェニル)フェニル]-9,9'-ビアントリル、アントラセン、テトラセン、ルブレン、ペリレン、2,5,8,11-テトラ(tert-ブチル)ペリレン等が挙げられる。また、この他、ペンタセン、コロネン等も用いることができる。このように、 $1 \times 10^{-6} \text{ cm}^2 / \text{Vs}$ 以上の正孔移動度を有し、炭素数14~42である芳香族炭化水素を用いることがより好ましい。

30

【0198】

なお、複合材料に用いることのできる芳香族炭化水素は、ビニル骨格を有していてもよい。ビニル基を有している芳香族炭化水素としては、例えば、4,4'-ビス(2,2-ジフェニルビニル)ビフェニル(略称: DPVBi)、9,10-ビス[4-(2,2-ジフェニルビニル)フェニル]アントラセン(略称: DPVPA)等が挙げられる。

【0199】

また、ポリ( N - ビニルカルバゾール) (略称: PVK) やポリ( 4 - ビニルトリフェニルアミン) (略称: PVTPA) 等の高分子化合物を用いることもできる。

### 【 0 2 0 0 】

図 13 では第 1 の層 804 に含まれる正孔輸送層を形成する物質としては、正孔輸送性の高い物質、具体的には、芳香族アミン(すなわち、ベンゼン環 - 窒素の結合を有するもの)の化合物であることが好ましい。広く用いられている材料として、4, 4' - ビス[ N - (3 - メチルフェニル) - N - フェニルアミノ] ビフェニル、その誘導体である4, 4' - ビス[ N - (1 - ナフチル) - N - フェニルアミノ] ビフェニル(以下、NPB と記す)、4, 4', 4''' - トリス( N, N - ジフェニル - アミノ) トリフェニルアミン、4, 4', 4''' - トリス[ N - (3 - メチルフェニル) - N - フェニルアミノ] トリフェニルアミンなどのスターバースト型芳香族アミン化合物が挙げられる。ここに述べた物質は、主に  $10^{-6} \text{ cm}^2 / \text{Vs}$  以上の正孔移動度を有する物質である。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。なお、正孔輸送層は、単層のものだけでなく、上記物質の混合層、あるいは二層以上積層したものであってもよい。

### 【 0 2 0 1 】

第 3 の層 802 は、第 2 の層 803 に電子を輸送、注入する機能を担う層である。図 13 では第 3 の層 802 に含まれる電子輸送層について説明する。電子輸送層は、電子輸送性の高い物質を用いることができる。例えば、トリス(8 - キノリノラト)アルミニウム(略称: Alq)、トリス(4 - メチル - 8 - キノリノラト)アルミニウム(略称: Almq<sub>3</sub>)、ビス(10 - ヒドロキシベンゾ[ h ]キノリナト)ベリリウム(略称: BeBq<sub>2</sub>)、ビス(2 - メチル - 8 - キノリノラト)(4 - フェニルフェノラト)アルミニウム(略称: BALq)など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる層である。また、この他ビス[ 2 - (2 - ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: Zn(BOX)<sub>2</sub>)、ビス[ 2 - (2 - ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称: Zn(BTZ)<sub>2</sub>)などのオキサゾール系、チアゾール系配位子を有する金属錯体なども用いることができる。さらに、金属錯体以外にも、2 - (4 - ビフェニリル) - 5 - (4 - tert - ブチルフェニル) - 1, 3, 4 - オキサジアゾール(略称: PBD)や、1, 3 - ビス[ 5 - (p - tert - ブチルフェニル) - 1, 3, 4 - オキサジアゾール - 2 - イル]ベンゼン(略称: OXD - 7)、3 - (4 - ビフェニリル) - 4 - フェニル - 5 - (4 - tert - ブチルフェニル) - 1, 2, 4 - トリアゾール(略称: TAZ)、パソフェナントロリン(略称: BPhen)、パソキュプロイン(略称: BCp)なども用いることができる。ここに述べた物質は、主に  $10^{-6} \text{ cm}^2 / \text{Vs}$  以上の電子移動度を有する物質である。なお、正孔よりも電子の輸送性の高い物質であれば、上記以外の物質を電子輸送層として用いても構わない。また、電子輸送層は、単層のものだけでなく、上記物質からなる層が二層以上積層したものとしてもよい。

### 【 0 2 0 2 】

図 13 では第 3 の層 802 に含まれる電子注入層について説明する。電子注入層は、電子注入性の高い物質を用いることができる。電子注入層としては、フッ化リチウム( LiF)、フッ化セシウム( CsF)、フッ化カルシウム( CaF<sub>2</sub>) 等のようなアルカリ金属又はアルカリ土類金属又はそれらの化合物を用いることができる。例えば、電子輸送性を有する物質からなる層中にアルカリ金属又はアルカリ土類金属又はそれらの化合物を含有させたもの、例えば Alq 中にマグネシウム( Mg) を含有させたもの等を用いることができる。なお、電子注入層として、電子輸送性を有する物質からなる層中にアルカリ金属又はアルカリ土類金属を含有させたものを用いることにより、電極層からの電子注入が効率良く行われるためより好ましい。

### 【 0 2 0 3 】

次に、発光層である第 2 の層 803 について説明する。発光層は発光機能を担う層であり、発光性の有機化合物を含む。また、無機化合物を含む構成であってもよい。発光層は、種々の発光性の有機化合物、無機化合物を用いて形成することができる。ただし、発光層

10

20

30

40

50

は、膜厚は10nm～100nm程度が好ましい。

【0204】

発光層に用いられる有機化合物としては、発光性の有機化合物であれば特に限定されることはなく、例えば、9,10-ジ(2-ナフチル)アントラセン(略称:DNA)、9,10-ジ(2-ナフチル)-2-tert-ブチルアントラセン(略称:t-BuDNA)、4,4'-ビス(2,2-ジフェニルビニル)ビフェニル(略称:DPVBi)、クマリン30、クマリン6、クマリン545、クマリン545T、ペリレン、ルブレン、ペリフランテン、2,5,8,11-テトラ(tert-ブチル)ペリレン(略称:TBP)、9,10-ジフェニルアントラセン(略称:DPA)、5,12-ジフェニルテトラセン、4-(ジシアノメチレン)-2-メチル-[p-(ジメチルアミノ)スチリル]-4H-ピラン(略称:DCM1)、4-(ジシアノメチレン)-2-メチル-6-[2-(ジュロリジン-9-イル)エテニル]-4H-ピラン(略称:DCM2)、4-(ジシアノメチレン)-2,6-ビス[p-(ジメチルアミノ)スチリル]-4H-ピラン(略称:BiSDCM)等が挙げられる。また、ビス[2-(4',6'-ジフルオロフェニル)ピリジナト-N,C<sup>2'</sup>]イリジウム(ピコリナート)(略称:FIrpic)、ビス{2-[3',5'-ビス(トリフルオロメチル)フェニル]ピリジナト-N,C<sup>2'</sup>}イリジウム(ピコリナート)(略称:Ir(CF<sub>3</sub>ppy)<sub>2</sub>(pic))、トリス(2-フェニルピリジナト-N,C<sup>2'</sup>)イリジウム(略称:Ir(ppy)<sub>3</sub>)、ビス(2-フェニルピリジナト-N,C<sup>2'</sup>)イリジウム(アセチルアセトナート)(略称:Ir(ppy)<sub>2</sub>(acac))、ビス[2-(2'-チエニル)ピリジナト-N,C<sup>3'</sup>]イリジウム(アセチルアセトナート)(略称:Ir(thp)<sub>2</sub>(acac))、ビス(2-フェニルキノリナト-N,C<sup>2'</sup>)イリジウム(アセチルアセトナート)(略称:Ir(pq)<sub>2</sub>(acac))、ビス[2-(2'-ベンゾチエニル)ピリジナト-N,C<sup>3'</sup>]イリジウム(アセチルアセトナート)(略称:Ir(btp)<sub>2</sub>(acac))などの熒光を放出できる化合物を用いることもできる。

【0205】

発光層を一重項励起発光材料の他、金属錯体などを含む三重項励起発光材料を用いても良い。例えば、赤色の発光性の画素、緑色の発光性の画素及び青色の発光性の画素のうち、輝度半減時間が比較的短い赤色の発光性の画素を三重項励起発光材料で形成し、他を一重項励起発光材料で形成する。三重項励起発光材料は発光効率が良いので、同じ輝度を得るのに消費電力が少なくて済むという特徴がある。すなわち、赤色画素に適用した場合、発光素子に流す電流が少なくて済むので、信頼性を向上させることができる。低消費電力化として、赤色の発光性の画素と緑色の発光性の画素とを三重項励起発光材料で形成し、青色の発光性の画素を一重項励起発光材料で形成しても良い。人間の視感度が高い緑色の発光素子も三重項励起発光材料で形成することで、より低消費電力化を図ることができる。

【0206】

また、発光層においては、上述した発光を示す有機化合物だけでなく、さらに他の有機化合物が添加されていてもよい。添加できる有機化合物としては、先に述べたTDA、MTDATA、m-MTDAB、TPD、NPB、DNTPD、TCTA、Alq<sub>3</sub>、Almq<sub>3</sub>、BeBq<sub>2</sub>、BA1q、Zn(BOX)<sub>2</sub>、Zn(BTZ)<sub>2</sub>、BPheN、BCP、PBD、OXD-7、TPBI、TAZ、p-EtTAZ、DNA、t-BuDNA、DPVBiなどの他、4,4'-ビス(N-カルバゾリル)ビフェニル(略称:CBP)、1,3,5-トリス[4-(N-カルバゾリル)フェニル]ベンゼン(略称:TCPB)などを用いることができるが、これらに限定されることはない。なお、このように有機化合物以外に添加する有機化合物は、有機化合物を効率良く発光させるため、有機化合物の励起エネルギーよりも大きい励起エネルギーを有し、かつ有機化合物よりも多く添加されていることが好ましい(それにより、有機化合物の濃度消光を防ぐことができる)。あるいはまた、他の機能として、有機化合物と共に発光を示してもよい(それにより、白色発光なども可能となる)。

10

20

30

40

50

## 【0207】

発光層は、発光波長帯の異なる発光層を画素毎に形成して、カラー表示を行う構成としても良い。典型的には、R(赤)、G(緑)、B(青)の各色に対応した発光層を形成する。この場合にも、画素の光放射側にその発光波長帯の光を透過するフィルターを設けた構成とすることで、色純度の向上や、画素領域の鏡面化(映り込み)の防止を図ることができる。フィルターを設けることで、従来必要であるとされていた円偏光板などを省略することが可能となり、発光層から放射される光の損失を無くすことができる。さらに、斜方から画素領域(表示画面)を見た場合に起る色調の変化を低減することができる。

## 【0208】

発光層で用いることのできる材料は低分子系有機発光材料でも高分子系有機発光材料でもよい。高分子系有機発光材料は低分子系に比べて物理的強度が高く、素子の耐久性が高い。また塗布により成膜することが可能であるので、素子の作製が比較的容易である。

10

## 【0209】

発光色は、発光層を形成する材料で決まるため、これらを選択することで所望の発光を示す発光素子を形成することができる。発光層の形成に用いることができる高分子系の電界発光材料は、ポリパラフェニレンビニレン系、ポリパラフェニレン系、ポリチオフェン系、ポリフルオレン系が挙げられる。

## 【0210】

ポリパラフェニレンビニレン系には、ポリ(パラフェニレンビニレン) [PPV] の誘導体、ポリ(2,5-ジアルコキシ-1,4-フェニレンビニレン) [RO-PPV] 、ポリ(2-(2'-エチル-ヘキソキシ)-5-メトキシ-1,4-フェニレンビニレン) [MEH-PPV] 、ポリ(2-(ジアルコキシフェニル)-1,4-フェニレンビニレン) [ROPh-PPV] 等が挙げられる。ポリパラフェニレン系には、ポリパラフェニレン [PPP] の誘導体、ポリ(2,5-ジアルコキシ-1,4-フェニレン) [RO-PPP] 、ポリ(2,5-ジヘキソキシ-1,4-フェニレン) 等が挙げられる。ポリチオフェン系には、ポリチオフェン [PT] の誘導体、ポリ(3-アルキルチオフェン) [PAT] 、ポリ(3-ヘキシルチオフェン) [PHT] 、ポリ(3-シクロヘキシルチオフェン) [PCHT] 、ポリ(3-シクロヘキシル-4-メチルチオフェン) [PCHMT] 、ポリ(3,4-ジシクロヘキシルチオフェン) [PDCHT] 、ポリ[3-(4-オクチルフェニル)-チオフェン] [POPT] 、ポリ[3-(4-オクチルフェニル)-2,2ビチオフェン] [PTOPT] 等が挙げられる。ポリフルオレン系には、ポリフルオレン [PF] の誘導体、ポリ(9,9-ジアルキルフルオレン) [PDAF] 、ポリ(9,9-ジオクチルフルオレン) [PDOF] 等が挙げられる。

20

## 【0211】

発光層で用いられる無機化合物としては、有機化合物の発光を消光しにくい無機化合物であれば何であってもよく、種々の金属酸化物や金属窒化物を用いることができる。特に、周期表第13族または第14族の金属酸化物は、有機化合物の発光を消光しにくいため好ましく、具体的には酸化アルミニウム、酸化ガリウム、酸化ケイ素、酸化ゲルマニウムが好適である。ただし、これらに限定されることはない。

30

## 【0212】

なお、発光層は、上述した有機化合物と無機化合物の組み合わせを適用した層を、複数積層して形成していくてもよい。また、他の有機化合物あるいは他の無機化合物をさらに含んでいてもよい。発光層の層構造は変化しうるものであり、特定の電子注入領域や発光領域を備えていない代わりに、電子注入用の電極層を備えたり、発光性の材料を分散させて備えたりする変形は、本発明の趣旨を逸脱しない範囲において許容されうるものである。

40

## 【0213】

上記のような材料で形成した発光素子は、順方向にバイアスすることで発光する。発光素子を用いて形成する半導体装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。いずれにしても、個々の画素は、ある特定のタイミングで順方向バイアスを印加して発光させることとなるが、ある一定期間は非発光状態と

50

なっている。この非発光時間に逆方向のバイアスを印加することで発光素子の信頼性を向上させることができる。発光素子では、一定駆動条件下で発光強度が低下する劣化や、画素内で非発光領域が拡大して見かけ上輝度が低下する劣化モードがあるが、順方向及び逆方向にバイアスを印加する交流的な駆動を行うことで、劣化の進行を遅くすることができ、発光素子を有する半導体装置の信頼性を向上させることができる。また、デジタル駆動、アナログ駆動どちらでも適用可能である。

#### 【0214】

よって、封止基板にカラーフィルタ（着色層）を形成してもよい。カラーフィルタ（着色層）は、蒸着法や液滴吐出法によって形成することができ、カラーフィルタ（着色層）を用いると、高精細な表示を行うこともできる。カラーフィルタ（着色層）により、各RGBの発光スペクトルにおいてプロードなピークが鋭いピークになるように補正できるからである。

#### 【0215】

単色の発光を示す材料を形成し、カラーフィルタや色変換層を組み合わせることによりフルカラー表示を行うことができる。カラーフィルタ（着色層）や色変換層は、例えば封止基板に形成し、素子基板へ張り合わせればよい。

#### 【0216】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの半導体装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

#### 【0217】

第1の電極層870及び第2の電極層850は仕事関数を考慮して材料を選択する必要があり、そして第1の電極層870及び第2の電極層850は、画素構成によりいずれも陽極（電位が高い電極層）、又は陰極（電位が低い電極層）となりうる。駆動用薄膜トランジスタの極性がpチャネル型である場合、図13（A）のように第1の電極層870を陽極、第2の電極層850を陰極とするとよい。また、駆動用薄膜トランジスタの極性がnチャネル型である場合、図13（B）のように、第1の電極層870を陰極、第2の電極層850を陽極とすると好ましい。第1の電極層870および第2の電極層850に用いることのできる材料について述べる。第1の電極層870、第2の電極層850が陽極として機能する場合は仕事関数の大きい材料（具体的には4.5eV以上の材料）が好ましく、第1の電極層、第2の電極層850が陰極として機能する場合は仕事関数の小さい材料（具体的には3.5eV以下の材料）が好ましい。しかしながら、第1の層804の正孔注入、正孔輸送特性や、第3の層802の電子注入性、電子輸送特性が優れているため、第1の電極層870、第2の電極層850共に、ほとんど仕事関数の制限を受けることなく、種々の材料を用いることができる。

#### 【0218】

図13（A）、（B）における発光素子は、第1の電極層870より光を取り出す構造のため、第2の電極層850は、必ずしも光透光性を有する必要はない。第2の電極層850としては、Ti、Ni、W、Cr、Pt、Zn、Sn、In、Ta、Al、Cu、Au、Ag、Mg、Ca、LiまたはMoから選ばれた元素、または窒化チタン、Ti<sub>x</sub>Si<sub>x</sub>N<sub>y</sub>、WSi<sub>x</sub>、窒化タンゲステン、WSi<sub>x</sub>N<sub>y</sub>、NbNなどの前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそれらの積層膜を総膜厚100nm～800nmの範囲で用いればよい。

#### 【0219】

また、第2の電極層850に第1の電極層870で用いる材料のような透光性を有する導電性材料を用いると、第2の電極層850からも光を取り出す構造となり、発光素子から放射される光は、第1の電極層870と第2の電極層850との両方より放射される両面放射構造とすることができます。

#### 【0220】

なお、第1の電極層870や第2の電極層850の種類を変えることで、本発明の発光素

10

20

30

40

50

子は様々なバリエーションを有する。

【0221】

図13(B)は、EL層860が、第1の電極層870側から第3の層802、第2の層803、第1の層804の順で構成されているケースである。

【0222】

図13(C)は、図13(A)において、第1の電極層870に反射性を有する電極層を用い、第2の電極層850に透光性を有する電極層を用いており、発光素子より放射された光は第1の電極層870で反射され、第2の電極層850を透過して放射される。同様に図13(D)は、図13(B)において、第1の電極層870に反射性を有する電極層を用い、第2の電極層850に透光性を有する電極層を用いており、発光素子より放射された光は第1の電極層870で反射され、第2の電極層850を透過して放射される。

10

【0223】

なお、EL層860に有機化合物と無機化合物が混合させて設ける場合、その形成方法としては種々の手法を用いることができる。例えば、有機化合物と無機化合物の両方を抵抗加熱により蒸発させ、共蒸着する手法が挙げられる。その他、有機化合物を抵抗加熱により蒸発させる一方で、無機化合物をエレクトロンビーム(EB)により蒸発させ、共蒸着してもよい。また、有機化合物を抵抗加熱により蒸発させると同時に、無機化合物をスパッタリングし、両方を同時に堆積する手法も挙げられる。その他、湿式法により成膜してもよい。

20

【0224】

第1の電極層870および第2の電極層850の作製方法としては、抵抗加熱による蒸着法、EB蒸着法、スパッタリング法、CVD法、スピンドル法、印刷法、ディスペンサ法または液滴吐出法などを用いることができる。

【0225】

本実施の形態は、実施の形態1及び実施の形態3と適宜組み合わせることができる。

【0226】

本発明を用いると、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の発光素子を有する半導体装置を作製することができる。

【0227】

(実施の形態5)

30

本実施の形態では、高性能及び高信頼性を付与された半導体装置として表示機能を有する半導体装置の他の例を説明する。本実施の形態では、本発明の半導体装置における発光素子に適用することのできる他の構成を、図11及び図12を用いて説明する。

【0228】

エレクトロルミネセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0229】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。前者は、発光材料の粒子をバインダ中に分散させた電界発光層を有し、後者は、発光材料の薄膜からなる電界発光層を有している点に違いはあるが、高電界で加速された電子を必要とする点では共通である。なお、得られる発光のメカニズムとしては、ドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光と、金属イオンの内殻電子遷移を利用する局在型発光がある。一般的に、分散型無機ELではドナー-アクセプター再結合型発光、薄膜型無機EL素子では局在型発光である場合が多い。

40

【0230】

本発明で用いることのできる発光材料は、母体材料と発光中心となる不純物元素とで構成される。含有させる不純物元素を変化させることで、様々な色の発光を得ることができる。発光材料の作製方法としては、固相法や液相法(共沈法)などの様々な方法を用いることができる。また、噴霧熱分解法、複分解法、プレカーサーの熱分解反応による方法、逆

50

ミセル法やこれらの方と高温焼成を組み合わせた方法、凍結乾燥法などの液相法なども用いることができる。

【0231】

固相法は、母体材料と、不純物元素又は不純物元素を含む化合物を秤量し、乳鉢で混合、電気炉で加熱、焼成を行い反応させ、母体材料に不純物元素を含有させる方法である。焼成温度は、700～1500が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。比較的高温での焼成を必要とするが、簡単な方法であるため、生産性がよく大量生産に適している。

【0232】

液相法（共沈法）は、母体材料又は母体材料を含む化合物と、不純物元素又は不純物元素を含む化合物を溶液中で反応させ、乾燥させた後、焼成を行う方法である。発光材料の粒子が均一に分布し、粒径が小さく低い焼成温度でも反応が進むことができる。

【0233】

発光材料に用いる母体材料としては、硫化物、酸化物、窒化物を用いることができる。硫化物としては、例えば、硫化亜鉛（ZnS）、硫化カドミウム（CdS）、硫化カルシウム（CaS）、硫化イットリウム（Y<sub>2</sub>S<sub>3</sub>）、硫化ガリウム（Ga<sub>2</sub>S<sub>3</sub>）、硫化ストロンチウム（SrS）、硫化バリウム（BaS）等を用いることができる。また、酸化物としては、例えば、酸化亜鉛（ZnO）、酸化イットリウム（Y<sub>2</sub>O<sub>3</sub>）等を用いることができる。また、窒化物としては、例えば、窒化アルミニウム（AlN）、窒化ガリウム（GaN）、窒化インジウム（InN）等を用いることができる。さらに、セレン化亜鉛（ZnSe）、テルル化亜鉛（ZnTe）等も用いることができ、硫化カルシウム-ガリウム（CaGa<sub>2</sub>S<sub>4</sub>）、硫化ストロンチウム-ガリウム（SrGa<sub>2</sub>S<sub>4</sub>）、硫化バリウム-ガリウム（BaGa<sub>2</sub>S<sub>4</sub>）、等の3元系の混晶であってもよい。

【0234】

局在型発光の発光中心として、マンガン（Mn）、銅（Cu）、サマリウム（Sm）、テルビウム（Tb）、エルビウム（Er）、ツリウム（Tm）、ユーロピウム（Eu）、セリウム（Ce）、プラセオジウム（Pr）などを用いることができる。なお、フッ素（F）、塩素（Cl）などのハロゲン元素が添加されていてもよい。上記ハロゲン元素は電荷補償として機能することができる。

【0235】

一方、ドナー-アクセプター再結合型発光の発光中心として、ドナー準位を形成する第1の不純物元素及びアクセプター準位を形成する第2の不純物元素を含む発光材料を用いることができる。第1の不純物元素は、例えば、フッ素（F）、塩素（Cl）、アルミニウム（Al）等を用いることができる。第2の不純物元素としては、例えば、銅（Cu）、銀（Ag）等を用いることができる。

【0236】

ドナー-アクセプター再結合型発光の発光材料を固相法を用いて合成する場合、母体材料と、第1の不純物元素又は第1の不純物元素を含む化合物と、第2の不純物元素又は第2の不純物元素を含む化合物をそれぞれ秤量し、乳鉢で混合した後、電気炉で加熱、焼成を行う。母体材料としては、上述した母体材料を用いることができ、第1の不純物元素又は第1の不純物元素を含む化合物としては、例えば、フッ素（F）、塩素（Cl）、硫化アルミニウム（Al<sub>2</sub>S<sub>3</sub>）等を用いることができ、第2の不純物元素又は第2の不純物元素を含む化合物としては、例えば、銅（Cu）、銀（Ag）、硫化銅（Cu<sub>2</sub>S）、硫化銀（Ag<sub>2</sub>S）等を用いることができる。焼成温度は、700～1500が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。

【0237】

また、固相反応を利用する場合の不純物元素として、第1の不純物元素と第2の不純物元

10

20

30

40

50

素で構成される化合物を組み合わせて用いてもよい。この場合、不純物元素が拡散されやすく、固相反応が進みやすくなるため、均一な発光材料を得ることができる。さらに、余分な不純物元素が入らないため、純度の高い発光材料が得ることができる。第1の不純物元素と第2の不純物元素で構成される化合物としては、例えば、塩化銅(CuCl)、塩化銀(AgCl)等を用いることができる。

【0238】

なお、これらの不純物元素の濃度は、母体材料に対して0.01~10atom%であればよく、好ましくは0.05~5atom%の範囲である。

【0239】

薄膜型無機EL素子の場合、電界発光層は、上記発光材料を含む層であり、抵抗加熱蒸着法、電子ビーム蒸着(EB蒸着)法等の真空蒸着法、スパッタリング法等の物理気相成長法(PVD)、有機金属CVD法、ハイドライド輸送減圧CVD法等の化学気相成長法(CVD)、原子層エピタキシ法(ALE)等を用いて形成することができる。

10

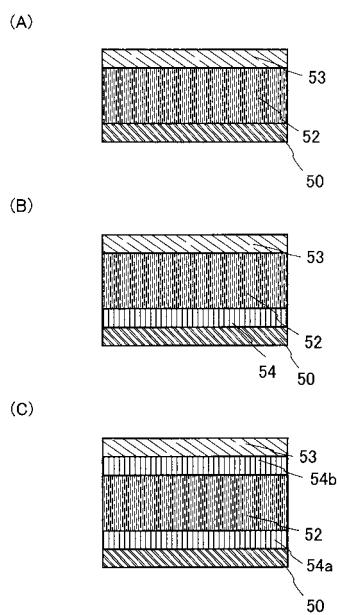

【0240】

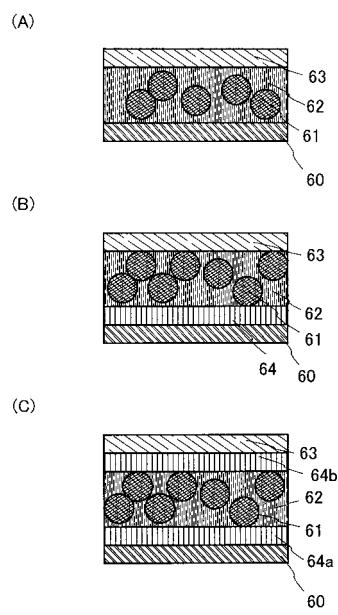

図11(A)乃至(C)に発光素子として用いることのできる薄膜型無機EL素子の一例を示す。図11(A)乃至(C)において、発光素子は、第1の電極層50、電界発光層52、第2の電極層53を含む。

【0241】

図11(B)及び図11(C)に示す発光素子は、図11(A)の発光素子において、電極層と電界発光層間に絶縁層を設ける構造である。図11(B)に示す発光素子は、第1の電極層50と電界発光層52との間に絶縁層54を有し、図11(C)に示す発光素子は、第1の電極層50と電界発光層52との間に絶縁層54a、第2の電極層53と電界発光層52との間に絶縁層54bとを有している。このように絶縁層は電界発光層を挟持する一対の電極層のうち一方の間にのみ設けてよいし、両方の間に設けてよい。また絶縁層は単層でもよいし複数層からなる積層でもよい。

20

【0242】

また、図11(B)では第1の電極層50に接するように絶縁層54が設けられているが、絶縁層と電界発光層の順番を逆にして、第2の電極層53に接するように絶縁層54を設けてよい。

【0243】

30

分散型無機EL素子の場合、粒子状の発光材料をバインダ中に分散させ膜状の電界発光層を形成する。粒子状に加工する。発光材料の作製方法によって、十分に所望の大きさの粒子が得られない場合は、乳鉢等で粉碎などによって粒子状に加工すればよい。バインダとは、粒状の発光材料を分散した状態で固定し、電界発光層としての形状に保持するための物質である。発光材料は、バインダによって電界発光層中に均一に分散し固定される。

【0244】

分散型無機EL素子の場合、電界発光層の形成方法は、選択的に電界発光層を形成できる液滴吐出法や、印刷法(スクリーン印刷やオフセット印刷など)、スピンドル法などの塗布法、ディッピング法、ディスペンサ法などを用いること也可以。膜厚は特に限定されることは無いが、好ましくは、10~1000nmの範囲である。また、発光材料及びバインダを含む電界発光層において、発光材料の割合は50wt%以上80wt%以下とするよい。

40

【0245】

図12(A)乃至(C)に発光素子として用いることのできる分散型無機EL素子の一例を示す。図12(A)における発光素子は、第1の電極層60、電界発光層62、第2の電極層63の積層構造を有し、電界発光層62中にバインダによって保持された発光材料61を含む。

【0246】

本実施の形態に用いることのできるバインダとしては、有機材料や無機材料を用いることができ、有機材料及び無機材料の混合材料を用いてよい。有機材料としては、シアノエ

50

チルセルロース系樹脂のように、比較的誘電率の高いポリマーや、ポリエチレン、ポリブロピレン、ポリスチレン系樹脂、シリコーン樹脂、エポキシ樹脂、フッ化ビニリデンなどの樹脂を用いることができる。また、芳香族ポリアミド、ポリベンゾイミダゾール (polybenzimidazole) などの耐熱性高分子、又はシロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 (例えばアルキル基、芳香族炭化水素) が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂、オキサゾール樹脂 (ポリベンゾオキサゾール) 等の樹脂材料を用いてもよい。これらの樹脂に、チタン酸バリウム (BaTiO<sub>3</sub>) やチタン酸ストロンチウム (SrTiO<sub>3</sub>) などの高誘電率の微粒子を適度に混合して誘電率を調整することもできる。

#### 【0247】

バインダに含まれる無機材料としては、酸化珪素 (SiO<sub>x</sub>)、窒化珪素 (SiN<sub>x</sub>)、酸素及び窒素を含む珪素、窒化アルミニウム (AlN)、酸素及び窒素を含むアルミニウムまたは酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化チタン (TiO<sub>2</sub>)、BaTiO<sub>3</sub>、SrTiO<sub>3</sub>、チタン酸鉛 (PbTiO<sub>3</sub>)、ニオブ酸カリウム (KNbO<sub>3</sub>)、ニオブ酸鉛 (PbNbO<sub>3</sub>)、酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>)、タンタル酸バリウム (BaTa<sub>2</sub>O<sub>6</sub>)、タンタル酸リチウム (LiTaO<sub>3</sub>)、酸化イットリウム (Y<sub>2</sub>O<sub>3</sub>)、酸化ジルコニウム (ZrO<sub>2</sub>)、ZnS その他の無機材料を含む物質から選ばれた材料で形成することができる。有機材料に、誘電率の高い無機材料を含ませる (添加等によって) ことによって、発光材料及びバインダよりなる電界発光層の誘電率をより制御することができ、より誘電率を大きくすることができる。

#### 【0248】

作製工程において、発光材料はバインダを含む溶液中に分散されるが本実施の形態に用いることのできるバインダを含む溶液の溶媒としては、バインダ材料が溶解し、電界発光層を形成する方法 (各種ウェットプロセス) 及び所望の膜厚に適した粘度の溶液を作製できるような溶媒を適宜選択すればよい。有機溶媒等を用いることができ、例えばバインダとしてシロキサン樹脂を用いる場合は、プロピレングリコールモノメチルエーテル、プロピレングリコールモノメチルエーテルアセテート (PGMEAともいう)、3-メトキ-3メチル-1-ブタノール (MMBともいう) などを用いることができる。

#### 【0249】

図12 (B) 及び図12 (C) に示す発光素子は、図12 (A) の発光素子において、電極層と電界発光層間に絶縁層を設ける構造である。図12 (B) に示す発光素子は、第1の電極層60と電界発光層62との間に絶縁層64を有し、図12 (C) に示す発光素子は、第1の電極層60と電界発光層62との間に絶縁層64a、第2の電極層63と電界発光層62との間に絶縁層64bとを有している。このように絶縁層は電界発光層を挟持する一対の電極層のうち一方の間にのみ設けてよいし、両方の間に設けてもよい。また絶縁層は単層でもよいし複数層からなる積層でもよい。

#### 【0250】

また、図12 (B) では第1の電極層60に接するように絶縁層64が設けられているが、絶縁層と電界発光層の順番を逆にして、第2の電極層63に接するように絶縁層64を設けてよい。

#### 【0251】

図11における絶縁層54、図12における絶縁層64のような絶縁層は、特に限定されることはないが、絶縁耐圧が高く、緻密な膜質であることが好ましく、さらには、誘電率が高いことが好ましい。例えば、酸化シリコン (SiO<sub>2</sub>)、酸化イットリウム (Y<sub>2</sub>O<sub>3</sub>)、酸化チタン (TiO<sub>2</sub>)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化ハフニウム (HfO<sub>2</sub>)、酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>)、チタン酸バリウム (BaTiO<sub>3</sub>)、チタン酸

10

20

30

40

50

ストロンチウム (SrTiO<sub>3</sub>)、チタン酸鉛 (PbTiO<sub>3</sub>)、窒化シリコン (Si<sub>3</sub>N<sub>4</sub>)、酸化ジルコニア (ZrO<sub>2</sub>) 等やこれらの混合膜又は 2 種以上の積層膜を用いることができる。これらの絶縁膜は、スパッタリング、蒸着、CVD 等により成膜することができる。また、絶縁層はこれら絶縁材料の粒子をバインダ中に分散して成膜してもよい。バインダ材料は、電界発光層に含まれるバインダと同様な材料、方法を用いて形成すればよい。膜厚は特に限定されることはないが、好ましくは 10 ~ 1000 nm の範囲である。

【0252】

本実施の形態で示す発光素子は、電界発光層を挟持する一対の電極層間に電圧を印加することで発光が得られるが、直流駆動又は交流駆動のいずれにおいても動作することができる。

10

【0253】

本実施の形態は、実施の形態 1 及び実施の形態 3 と適宜組み合わせることができる。

【0254】

本発明を用いると、大型の半導体装置であっても高スループットで生産性よく高性能及び高信頼性の発光素子を有する半導体装置を作製することができる。

【0255】

(実施の形態 6)

本実施の形態では、バックライトの構成について説明する。バックライトは光源を有するバックライトユニットとして実施の形態 2 のような液晶素子を有する半導体装置に設けられ、バックライトユニットは効率よく光を散乱させるため、光源は反射板により囲まれている。

20

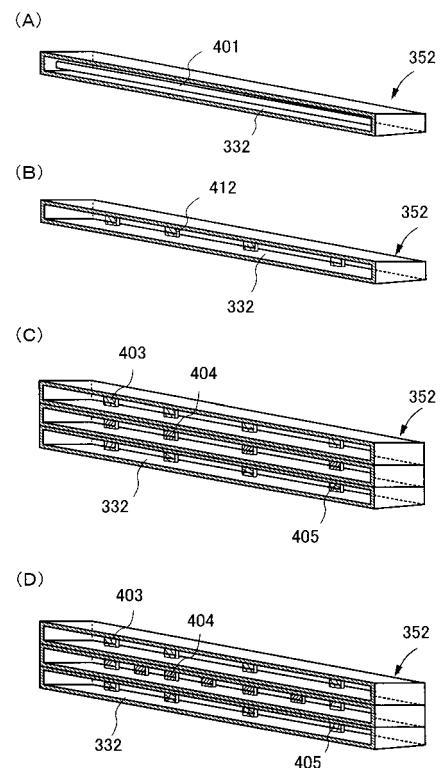

【0256】

図 14 (A) に示すように、バックライトユニット 352 は、光源として冷陰極管 401 を用いることができる。また、冷陰極管 401 からの光を効率よく反射させるため、ランプリフレクタ 332 を設けることができる。冷陰極管 401 は、大型の半導体装置に用いることが多い。これは冷陰極管からの輝度の強度のためである。そのため、冷陰極管を有するバックライトユニットは、パーソナルコンピュータのディスプレイに用いることができる。

【0257】

30

図 14 (B) に示すように、バックライトユニット 352 は、光源として発光ダイオード (LED) 412 を用いることができる。例えば、白色に発する発光ダイオード (W) 412 を所定の間隔に配置する。また、発光ダイオード (W) 412 からの光を効率よく反射させるため、ランプリフレクタ 332 を設けることができる。

【0258】

また図 14 (C) に示すように、バックライトユニット 352 は、光源として各色 RGB の発光ダイオード (LED) 403、404、405 を用いることができる。各色 RGB の発光ダイオード (LED) 403、404、405 を用いることにより、白色を発する発光ダイオード (W) 412 のみと比較して、色再現性を高くすることができる。また、発光ダイオードからの光を効率よく反射させるため、ランプリフレクタ 332 を設けることができる。

40

【0259】

またさらに図 14 (D) に示すように、光源として各色 RGB の発光ダイオード (LED) 403、404、405 を用いる場合、それらの数や配置を同じとする必要はない。例えば、発光強度の低い色 (例えば緑) の発光ダイオードを他の色の発光ダイオードより多く配置してもよい。

【0260】

さらに白色を発する発光ダイオード 412 と、各色 RGB の発光ダイオード (LED) 403、404、405 とを組み合わせて用いてもよい。

【0261】

50

なお R G B の発光ダイオードを有する場合、フィールドシーケンシャルモードを適用すると、時間に応じて R G B の発光ダイオードを順次点灯させることによりカラー表示を行うことができる。

【 0 2 6 2 】

発光ダイオードを用いると、輝度が高いため、大型の半導体装置に適する。また、R G B 各色の色純度が良いため冷陰極管と比べて色再現性に優れており、配置面積を小さくすることができるため、小型の半導体装置に適応すると、狭額縫化を図ることができる。

【 0 2 6 3 】

また、光源を必ずしも図 1 4 に示すバックライトユニットとして配置する必要はない。例えば、大型の半導体装置に発光ダイオードを有するバックライトを搭載する場合、発光ダイオードは該基板の背面に配置することができる。このとき発光ダイオードは、所定の間隔を維持し、各色の発光ダイオードを順に配置させることができる。発光ダイオードの配置により、色再現性を高めることができる。10

【 0 2 6 4 】

従って、本発明により高性能かつ高信頼性のバックライトを用いた半導体装置を生産性よく作製することができる。特に、発光ダイオードを有するバックライトは、大型の半導体装置に適しており、大型の半導体装置のコントラスト比を高めることにより、暗所でも質の高い映像を提供することができる。

【 0 2 6 5 】

本実施の形態は、上記の実施の形態 2 と適宜組み合わせることができる。20

【 0 2 6 6 】

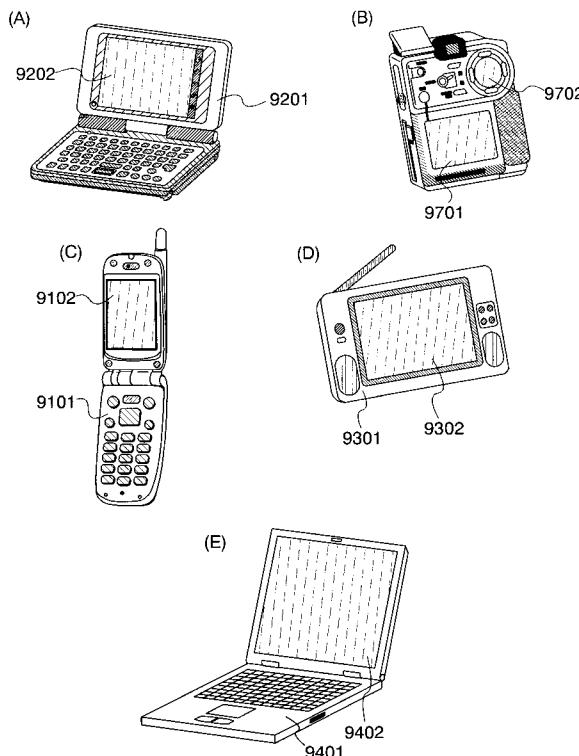

( 実施の形態 7 )

本発明によって形成される表示素子を有する半導体装置によって、テレビジョン装置を完成させることができる。高性能で、かつ高信頼性を付与することを目的としたテレビジョン装置の例を説明する。

【 0 2 6 7 】

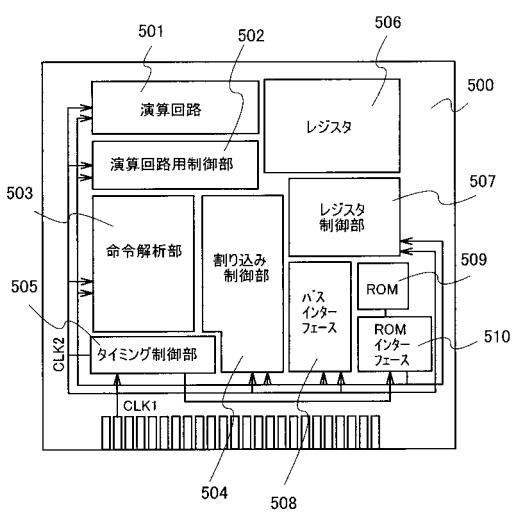

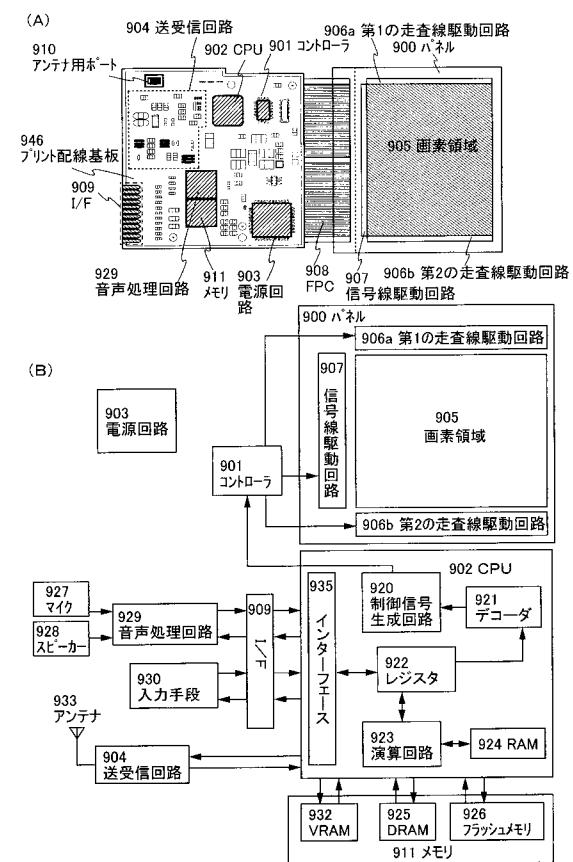

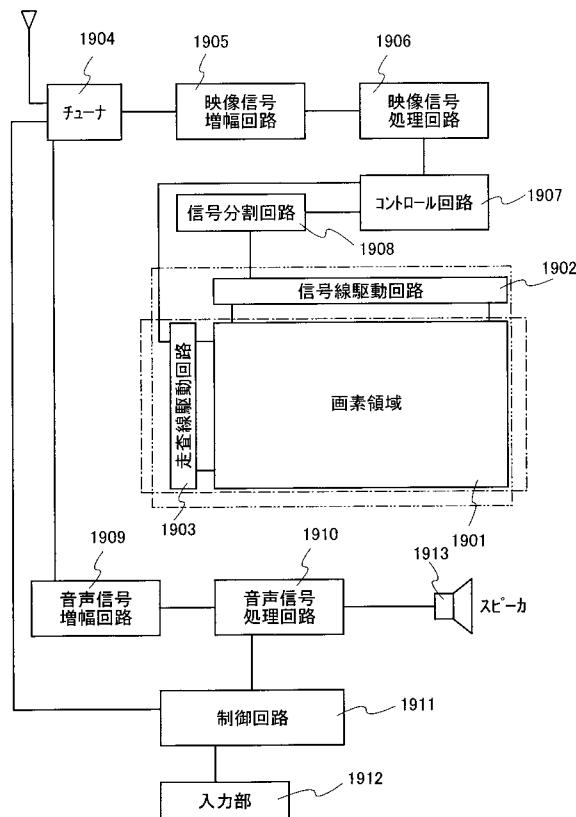

図 2 3 はテレビジョン装置（液晶テレビジョン装置、又は E L テレビジョン装置等）の主要な構成を示すブロック図を示している。表示パネルには、図 1 6 ( B ) に示すように T F T を形成し、画素領域 1 9 0 1 と走査線駆動回路 1 9 0 3 を基板上に一体形成し信号線駆動回路 1 9 0 2 を別途ドライバ I C として実装する場合、また図 1 6 ( C ) に示すように画素領域 1 9 0 1 と信号線駆動回路 1 9 0 2 と走査線駆動回路 1 9 0 3 を基板上に一体形成する場合などがあるが、どのような形態としても良い。30

【 0 2 6 8 】

その他の外部回路の構成として、映像信号の入力側では、チューナ 1 9 0 4 で受信した信号のうち、映像信号を增幅する映像信号增幅回路 1 9 0 5 と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路 1 9 0 6 と、その映像信号をドライバ I C の入力仕様に変換するためのコントロール回路 1 9 0 7 などからなっている。コントロール回路 1 9 0 7 は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路 1 9 0 8 を設け、入力デジタル信号を m 個に分割して供給する構成としても良い。40

【 0 2 6 9 】

チューナ 1 9 0 4 で受信した信号のうち、音声信号は、音声信号增幅回路 1 9 0 9 に送られ、その出力は音声信号処理回路 1 9 1 0 を経てスピーカ 1 9 1 3 に供給される。制御回路 1 9 1 1 は受信局（受信周波数）や音量の制御情報を入力部 1 9 1 2 から受け、チューナ 1 9 0 4 や音声信号処理回路 1 9 1 0 に信号を送出する。

【 0 2 7 0 】

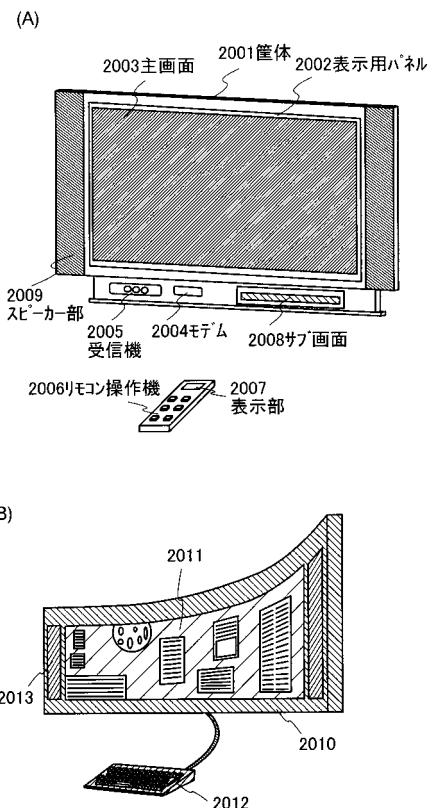

表示モジュールを、図 2 0 ( A ) 、 ( B ) に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。F P C まで取り付けられた図 8 のような表示パネルのことを一般的には E L 表示モジュールともいう。よって図 8 のような E L 表示モジュールを用いると、E L テレビジョン装置を完成することができ、図 7 のような液晶表示モジュ50

ールを用いると、液晶テレビジョン装置を完成することができる。表示モジュールにより主画面 2003 が形成され、その他付属設備としてスピーカー部 2009、操作スイッチなどが備えられている。このように、本発明によりテレビジョン装置を完成させることができる。

【0271】

また、位相差板や偏光板を用いて、外部から入射する光の反射光を遮断するようにしてもよい。また上面放射型の半導体装置ならば、隔壁となる絶縁層を着色しブラックマトリクスとして用いてもよい。この隔壁は液滴吐出法などによっても形成することができ、顔料系の黒色樹脂や、ポリイミドなどの樹脂材料に、カーボンブラック等を混合させてもよく、その積層でもよい。液滴吐出法によって、異なった材料を同領域に複数回吐出し、隔壁を形成してもよい。位相差板としては  $1/4$  板と  $1/2$  板とを用い、光を制御できるように設計すればよい。構成としては、TFT 素子基板側から順に、発光素子、封止基板（封止材）、位相差板（ $1/4$ 、 $1/2$ ）、偏光板という構成になり、発光素子から放射された光は、これらを通過し偏光板側より外部に放射される。この位相差板や偏光板は光が放射される側に設置すればよく、両面放射される両面放射型の半導体装置であれば両方に設置することもできる。また、偏光板の外側に反射防止膜を有していても良い。これにより、より高繊細で精密な画像を表示することができる。

【0272】

図 20 (A) に示すように、筐体 2001 に表示素子を利用した表示用パネル 2002 が組みこまれ、受信機 2005 により一般のテレビ放送の受信をはじめ、モデム 2004 を介して有線又は無線による通信ネットワークに接続することにより一方向（送信者から受信者）又は双方向（送信者と受信者間、又は受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機 2006 により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部 2007 が設けられていても良い。

【0273】

また、テレビジョン装置にも、主画面 2003 の他にサブ画面 2008 を第 2 の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面 2003 を視野角の優れた EL 表示用パネルで形成し、サブ画面を低消費電力で表示可能な液晶表示用パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面 2003 を液晶表示用パネルで形成し、サブ画面 2008 を EL 表示用パネルで形成し、サブ画面は点滅可能とする構成としても良い。本発明を用いると、このような大型基板を用いて、多くの TFT や電子部品を用いても、高性能で、かつ信頼性の高い半導体装置を生産性よく作製することができる。

【0274】

図 20 (B) は例えば 20 ~ 80 インチの大型の表示部を有するテレビジョン装置であり、筐体 2010、操作部であるキーボード部 2012、表示部 2011、スピーカー部 2013 等を含む。本発明は、表示部 2011 の作製に適用される。図 20 (B) の表示部は、わん曲可能な物質を用いているので、表示部がわん曲したテレビジョン装置となっている。このように表示部の形状を自由に設計することができるので、所望な形状のテレビジョン装置を作製することができる。

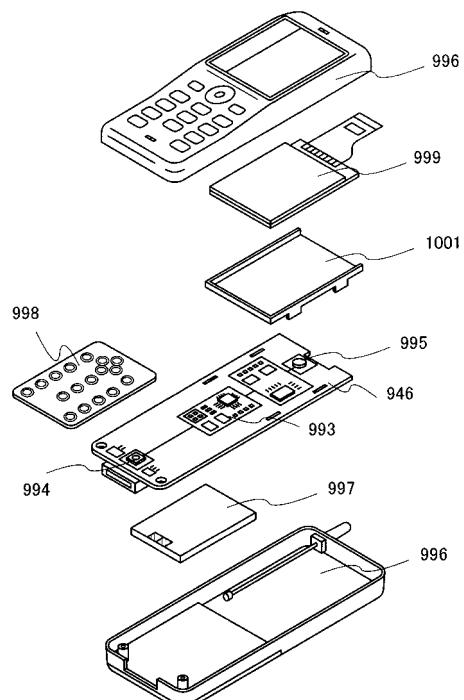

【0275】