(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6087630号

(P6087630)

(45) 発行日 平成29年3月1日(2017.3.1)

(24) 登録日 平成29年2月10日(2017.2.10)

(51) Int.Cl.

H05K 3/46 (2006.01)

F 1

H05K 3/46

3/46

N

H05K 3/46

B

H05K 3/46

Z

請求項の数 14 (全 23 頁)

(21) 出願番号 特願2012-557087 (P2012-557087)

(86) (22) 出願日 平成23年3月3日(2011.3.3)

(65) 公表番号 特表2013-522874 (P2013-522874A)

(43) 公表日 平成25年6月13日(2013.6.13)

(86) 國際出願番号 PCT/US2011/026960

(87) 國際公開番号 WO2011/112409

(87) 國際公開日 平成23年9月15日(2011.9.15)

審査請求日 平成26年2月28日(2014.2.28)

審判番号 不服2015-17131 (P2015-17131/J1)

審判請求日 平成27年9月17日(2015.9.17)

(31) 優先権主張番号 12/719,136

(32) 優先日 平成22年3月8日(2010.3.8)

(33) 優先権主張国 米国(US)

(73) 特許権者 505377474

フォームファクター、 インコーポレイテッド

アメリカ合衆国 カリフォルニア 94551, リバーモア, サウスフロント

ロード 7005

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(74) 代理人 100117189

弁理士 江口 昭彦

(74) 代理人 100134120

弁理士 内藤 和彦

最終頁に続く

(54) 【発明の名称】カスタマイズ層を有する配線基板

## (57) 【特許請求の範囲】

## 【請求項 1】

ベース基板と、

前記ベース基板の表面上に配置された第1導電性トレース層と、

前記第1導電性トレース層上に配置されかつ前記ベース基板の前記表面上に結合された第1電気絶縁材料剛性層と、

前記第1電気絶縁材料剛性層内に埋め込まれた導電性の第1ビアと、

前記ベース基板上および前記第1電気絶縁材料剛性層の外面上に形成された複数のジャンパと、

前記第1電気絶縁材料剛性層上に配置された第2導電性トレース層と、

を含み、

前記第1ビアの各々は、前記第1導電性トレース層のトレースのうちの1つに接合され、前記第1電気絶縁材料剛性層の前記外面上まで延在するワイヤスタッドのスタック又はワイヤを含み、

前記ジャンパは、前記第1導電性トレース層の前記トレースのうち、少なくとも二つのトレースを接続し、前記第2導電性トレース層のトレースのうち、少なくとも二つのトレースを接続する、

多層配線基板。

## 【請求項 2】

前記第1電気絶縁材料剛性層は、硬化工ポキシを含む、請求項1に記載の多層配線基板

10

20

。

## 【請求項 3】

前記第1ビアは、前記第1導電性トレース層の前記トレースのうちの1つに接合されたワイヤを含む、請求項1又は2に記載の多層配線基板。

## 【請求項 4】

前記ワイヤの各々の本体部は、前記第1導電性トレース層の前記トレースのうちの1つから、前記ベース基板の前記表面に対し実質的に垂直に延在する、請求項3に記載の多層配線基板。

## 【請求項 5】

前記ワイヤの各々の本体部は、前記第1導電性トレース層の前記トレースのうちの1つから、前記ベース基板の前記表面に対して15から75度の角度で延在する、請求項3に記載の多層配線基板。 10

## 【請求項 6】

前記第2導電性トレース層の前記トレースの各々は、前記第1ビアのうちの1つに電気的に接続される、請求項1～5のいずれかに記載の多層配線基板。

## 【請求項 7】

前記第2導電性トレース層及び前記第1電気絶縁材料剛性層の前記外面上に配置された第2電気絶縁材料層と、

前記第2電気絶縁材料層内に埋め込まれた導電性の第2ビアであって、前記第2ビアの各々は、前記第2導電性トレース層の前記トレースのうちの1つに接合されかつ前記第2電気絶縁材料層の外面まで延在するワイヤスタッッドのスタック又はワイヤを含む、請求項6に記載の多層配線基板。 20

## 【請求項 8】

前記第2電気絶縁材料層の外面上の第3導電性トレース層をさらに含み、前記第3導電性トレース層の前記トレースの各々は、前記第2ビアのうちの1つに電気的に接続される、請求項7に記載の多層配線基板。

## 【請求項 9】

前記第1ビアの各々は、ワイヤスタッッドの一つの前記スタッック又は一つの前記ワイヤのみから構成される、請求項1～8のいずれかに記載の多層配線基板。

## 【請求項 10】

前記第1ビアは、第1導電性トレース層の前記トレースのうちの1つに接合されたワイヤスタッッドのスタッックを、それぞれ含む、請求項1～9のいずれかに記載の多層配線基板。 30

## 【請求項 11】

ワイヤスタッッドの各々の前記スタッックは、他のワイヤスタッッドの上部に積み重ねられた少なくとも三つのワイヤスタッッドを含む、請求項1～10のいずれかに記載の多層配線基板。

## 【請求項 12】

前記第1電気絶縁材料剛性層は、前記第1ビアのワイヤスタッッドの前記スタッックの各々又は前記ワイヤの各々の周りに配置された、固められた材料である、請求項1～11のいずれかに記載の多層配線基板。 40

## 【請求項 13】

前記第1電気絶縁材料剛性層は、シリカ粒子を含む、請求項1～12のいずれかに記載の多層配線基板。

## 【請求項 14】

前記第1電気絶縁材料剛性層内の前記シリカ粒子の濃度は、50～90重量%である、請求項1～13のいずれかに記載の多層配線基板。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

(原文の対応する箇所に記載なし)

【背景技術】

【0002】

[0001] いくつかの既知の配線基板は、当該配線基板の外面において特定のパターンに配置された電気素子への電気的接続を与える。このような配線基板の一例としては、プローブヘッドであり、プローブヘッドは、プローブヘッドの外面上に特定のパターンに配置された導電性プローブと、プローブへの内部配線とを有しうる。本発明の実施形態は、標準ベース配線基板にカスタマイズ層を追加するプロセスを含む。カスタマイズ層は、カスタマイズ層の外面における、プローブのようなカスタム配置された電気素子へのカスタマイズされた電気的接続を与える。このようなプロセスは、所望のパターンに配置されていない接点を有するベース配線基板が、ベース配線基板上の接点のパターンとは異なる所望のパターンに配置されたプローブといった電気素子を有するようにカスタマイズされることを可能にしうる。10

【発明の概要】

【課題を解決するための手段】

【0003】

[0002] 本発明のいくつかの実施形態では、ベース基板を得ることによって多層配線基板内に電気ジャンパを作成しうる。ベース基板は、当該ベース基板の表面上にカスタマイズ層を含みうる。カスタマイズ層は、第1電気絶縁材料層の外面上に導電性トレース層を含みうる。トレース層は、第1トレース、第2トレース及び第3トレースを含みうる。第3トレースの一部は、第1トレース及び第2トレースの端間の空間内にありうる。プロセスは、第1トレース及び第2トレースの端間の空間内、及び、第3トレースの一部上に、電気絶縁物質をプリントすることも含み、また、プロセスは、第3トレースに電気的に接觸することなく第1トレース及び第2トレースに電気的に接続する電気ジャンパを形成することをさらに含みうる。電気ジャンパは、第1トレースの端、絶縁物質及び第2トレースの端上に導電性物質をプリントすることによって形成されうる。20

【0004】

[0003] 本発明のいくつかの実施形態では、多層配線基板は、ベース基板と、ベース基板の表面上のカスタマイズ層とを含みうる。カスタマイズ層は、第1電気絶縁材料層と、第1絶縁材料層の表面上の第1導電性トレース層とを含みうる。第1トレース層は、第1トレース、第2トレース及び第3トレースを含み、第3トレースの一部は、第1トレース及び第2トレースの端間の空間内にありうる。カスタマイズ層はさらに、第3トレースの一部上と、第1トレース及び第2トレースの端間の空間内に、乾燥プリント可能導電材料を含む電気絶縁物質を含みうる。カスタマイズ層はさらに、導電性ジャンパを含み、導電性ジャンパは、第1トレース及び第2トレースの端上の乾燥プリント可能導電材料と、絶縁物質とを含む導電性物質を含みうる。ジャンパは、第3トレースに電気的に接觸することなく第1トレース及び第2トレースを電気的に接続しうる。30

【0005】

[0004] 本発明のいくつかの実施形態では、多層配線基板は、ベース基板の表面上の第1導電性トレース層内の導電性トレースに結合されかつそこから延在する導電性の第1ビア構造を形成することを含むプロセスによって作成されうる。プロセスはさらに、ベース基板の表面に結合され、第1ビア構造がその中に埋め込まれる剛性の第1電気絶縁材料層を形成することを含みうる。剛性の第1電気絶縁材料層は、第1ビア構造の周りにかつ第1トレース層及びベース基板の表面上に第1電気絶縁材料層を流し込む(casting)ことによって形成されうる。第1ビア構造は、第1トレース層内のトレースから第1絶縁材料層の外面への電気的接続を与えうる。40

【0006】

[0005] 本発明のいくつかの実施形態では、多層配線基板は、ベース基板と、ベース基板の表面上の第1導電性トレース層とを含みうる。配線基板はさらに、第1トレース層上にかつベース基板の表面上に結合された剛性の第1電気絶縁材料層を含み、配線基板はま50

たさらに、第1絶縁材料層内に埋め込まれた導電性の複数の第1ビアを含みうる。第1ビアの各々は、第1トレース層のトレースのうちの1つに接合し、第1絶縁材料層の外面へと延在するワイヤスタッドのスタック又はワイヤを含みうる。

【0007】

[0006] 本発明のいくつかの実施形態では、多層配線基板における電気的接続は、複数のカスタマイズ層をその表面上に含むベース基板を得ることを含むプロセスによって作成されうる。カスタマイズ層は、第1導電性トレース層における第1トレースと、第1導電性トレース層を覆う第1電気絶縁材料層と、第1絶縁材料層の外面上の第2導電性トレース層における第2トレースとを含みうる。プロセスはさらに、第1電気絶縁材料層において、第1トレースのうちの1つの一部への第1開口を作成することを含みうる。第1開口は、第1トレースのうちの1つにおけるよりも第1絶縁材料の外面において大きくてよく、第1開口の側壁は第1絶縁材料の外面から第1トレースのうちの1つへと傾斜しうる。プロセスはさらに、第2トレースのうちの1つを第1トレースのうちの1つに電気的に接続する第1電気コネクタを形成することを含みうる。第1電気コネクタは、第2トレースのうちの1つの一部、第1開口の側壁の一部、及び第1トレースのうちの1つの一部上に導電性物質をプリントすることによって形成されうる。

【図面の簡単な説明】

【0008】

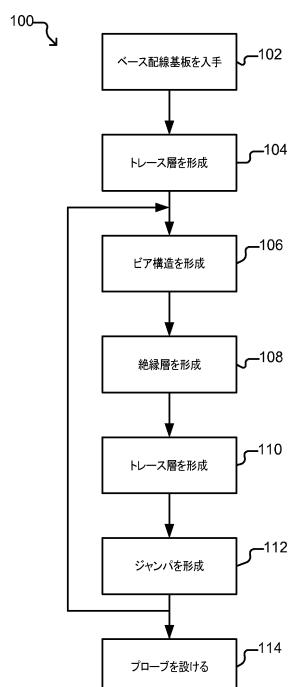

【図1】[0007] 図1は、本発明のいくつかの実施形態による、ベース配線基板にカスタマイズ層を追加してカスタマイズされた多層回路基板を作成するためのプロセスの一例を示す。

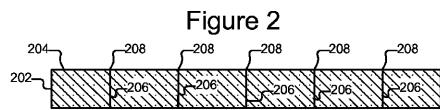

【図2】[0008] 図2は、本発明のいくつかの実施形態によるベース配線基板の一例を示す。

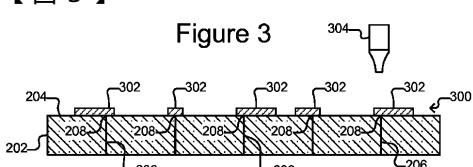

【図3】[0009] 図3は、本発明のいくつかの実施形態による、図2の配線基板上のトレース層を示す。

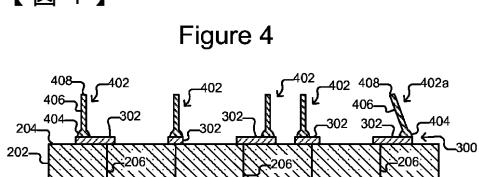

【図4】[0010] 図4は、本発明のいくつかの実施形態による、図3のトレースに結合されたビア構造を示す。

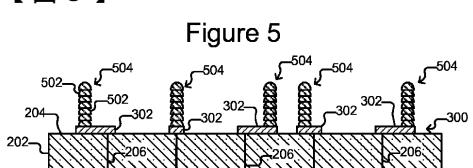

【図5】[0011] 図5は、本発明のいくつかの実施形態による、ワイヤスタッドのスタックを含むビア構造を示す。

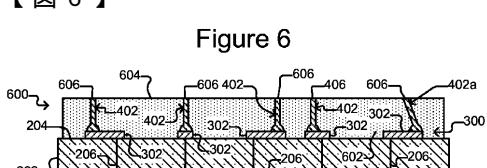

【図6】[0012] 図6は、本発明のいくつかの実施形態による、ビア構造を囲む絶縁材料層を示す。

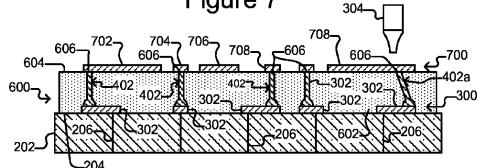

【図7】[0013] 図7は、本発明のいくつかの実施形態による、図6の絶縁層上のトレース層を示す。

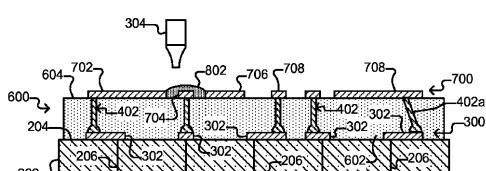

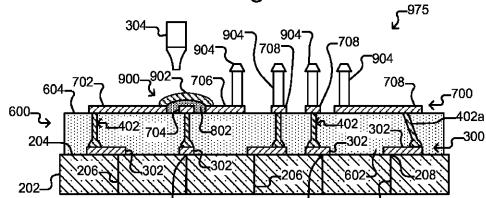

【図8】[0014] 図8は、本発明のいくつかの実施形態による、図7のトレース上の電気ジャンパの形成を示す。

【図9】[0014] 図9は、本発明のいくつかの実施形態による、図7のトレース上の電気ジャンパの形成を示す。

【図10】[0015] 図10は、本発明のいくつかの実施形態による、別の絶縁材料層及びトレース層を示す。

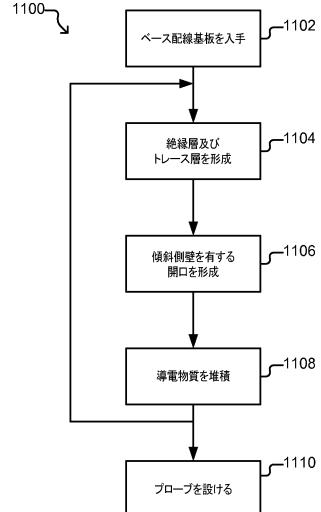

【図11】[0016] 図11は、本発明のいくつかの実施形態による、ベース配線基板にカスタマイズ層を追加してカスタマイズされた多層回路基板を作成するためのプロセスの別の例を示す。

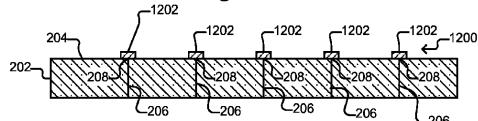

【図12】[0017] 図12は、本発明のいくつかの実施形態による、トレース層を有するベース配線基板の一例を示す。

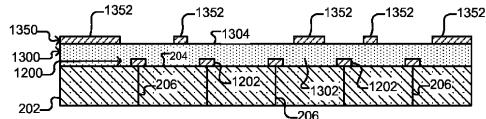

【図13】[0018] 図13は、本発明のいくつかの実施形態による、図12のトレース上の絶縁材料層上の別のトレース層を示す。

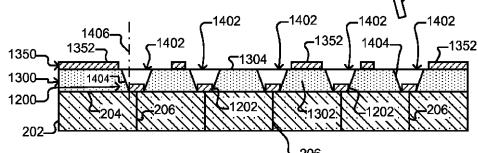

【図14】[0019] 図14は、本発明のいくつかの実施形態による、図13の絶縁層内の少なくとも1つの傾斜側壁を有する開口を示す。

【図15】[0020] 図15は、本発明のいくつかの実施形態による、トレース層を電気的に接続しうる図14の開口内に形成されたビア構造を示す。

10

20

30

40

50

【図16】[0021] 図16は、本発明のいくつかの実施形態による、別の絶縁材料層上のさらに別のトレース層を示す。

【図17】[0022] 図17は、本発明のいくつかの実施形態による、図16の他の絶縁材料層における開口内に形成されたビア構造を示す。

【図18】[0023] 図18は、本発明のいくつかの実施形態による、ベース配線基板と、カスタマイズ層の外面上のカスタム配置プローブへの電気的接続を与えるカスタマイズ層とを含むプローブヘッドを有するプローブカードアセンブリの一例を示す。

【図19】[0024] 図19は、本発明のいくつかの実施形態による、DUTを試験するよう图18のプローブカードアセンブリを使用しうる試験システムの一例を示す。

【発明を実施するための形態】

10

【0009】

[0025] 本明細書には、本発明の例示的な実施形態及び用途が記載される。しかし、本発明は、これらの例示的な実施形態及び用途、又は、これらの実施形態及び用途が本明細書中において動作する及び記載される態様に限定されない。さらに、図面は簡略図又は部分図であって、図面中の構成要素の寸法は明確にするために拡大されているか又はそうでなければ比例しているわけではない。また、本明細書中で用語「上に」、「～に取り付けられる」又は「～に結合される」を使用する際に、1つの対象物（例えば材料、層、基板等）が、かかる1つの対象物が別の対象物に直接的に上にある、取り付けられる若しくは結合されるか、又は、かかる1つの対象物と別の対象物との間に1以上の介在対象物があるかに関わらず、別の対象物の「上に」ある、「取り付けられる」又は「結合される」ことができる。また、与えられている場合には、方向（例えば、上方、下方、上部、底部、側部、上、下、～より下、～より上、上位の、下位の、水平、垂直、「x」、「y」、「z」等）は相対的であり、例としてまた例示及び説明の便宜上与えているに過ぎず、限定として与えているものではない。さらに、構成要素の列挙（例えば構成要素a、b、c）を参照する場合、このような参照は、列挙された構成要素のいずれか1つの構成要素それ自体、列挙された構成要素のすべてではないが幾つかの任意の組み合わせ、及び/又は、列挙された構成要素のすべての組み合わせを含むことを意図している。

20

【0010】

[0026] 本発明のいくつかの実施形態は、所定パターンの電気接点をその表面に含むベース配線基板をカスタマイズするプロセスであってよく、また、本発明のいくつかの実施形態は、カスタマイズされたベース配線基板であってよい。プロセスは、ベース配線基板の表面における接点から、カスタマイズ層の外面における電気接点（例えばプローブ）へのカスタマイズされた電気的接続を与える1以上のカスタマイズ層を配線基板の表面に追加することを含みうる。カスタマイズ層の外面における接点は、ベース配線基板の表面における接点とは異なるパターンにあってよい。カスタマイズ層は、電気絶縁材料、導電性ビア構造、導電性トレース、2つのトレースを、当該2つのトレース間に配置されたトレースに接触することなく電気的に接続する導電性ジャンパ、及び/又は、他のかかる素子を含みうる。いくつかの実施形態では、プロセスは、接続されるべき2つのトレース間に比較的小さい電気絶縁材料の堆積物を作成し、次に、その2つのトレースと絶縁材料の一部上に比較的小さい導電材料の堆積物を作成することによってかかるジャンパを形成することを含みうる。いくつかの実施形態では、プロセスはさらに、ビア構造をトレースに結合し、次にビア構造の周りに絶縁材料層を流し込むことによって、絶縁層を通り延在するビア構造を有する絶縁材料層を形成することを含みうる。他のいくつかの実施形態では、ビア構造は、導電性物質を、絶縁材料の下のトレースを露出する絶縁材料層内の傾斜側壁を有する開口上に堆積させることによって形成されうる。

30

【0011】

[0027] 図1は、本発明のいくつかの実施形態に従って、ベース配線基板に1以上のカスタマイズ層を追加し、それによりベース基板と、1以上のカスタマイズ層とを含む多層配線基板を作成するためのプロセス100を示す。説明及び議論の便宜上、プロセス100は、カスタマイズ層がベース配線基板202に追加される図2～図10に示される例に

40

50

ついて以下に述べられる。しかし、プロセス 100 は、図 2 ~ 図 10 に示される例に限定されない。

【 0 0 1 2 】

[0028] 図 1 を参照すると、ステップ 102 において、ベース配線基板（ベース基板の一例でありうる）が、プロセス 100 の 102 において得られうる。図 2 は、そのようなベース配線基板 202 の一例を示し、ベース配線基板は、基板の表面 204 において又は上に導電性接点 208 を有する任意の剛性又は半剛性基板構造でありうる。いくつかの実施形態では、ベース配線基板 202 は、プリント回路基板又はセラミック材料を含みうる。図 2 に示されるように、接点 208 は、配線基板 202 を通る導電性ビア 206 の端部でありうる。或いは、接点 208 は、配線基板 202 の表面 204 上の端子、パッド、トレース、又は他のかかる導電性構造（図示せず）でありうる。5 つのビア 206 及び接点 208 が示されるが、より多くても少なくてもよい。また、ビア 206 は、完全に垂直である必要はなく、水平の構成要素（図示せず）を含んでもよい。

【 0 0 1 3 】

[0029] 図 1 のプロセス 100 のステップ 102 においてベース配線基板を得た後、ステップ 104 において、配線基板の表面上に導電性トレース層が形成されうる。図 3 は、トレース 302 の層 300（層 300 は「トレース層」と呼びうる）が、配線基板 202 の表面 204 上に形成されうる一例を示す。トレース層 300 は、カスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等のトレース層）の一例でありうる。本明細書において用いられるように、用語「トレース」とは、細長構造、及び、細長である必要のない端子又はパッド又は同様のかかる構造を含む。したがって、トレース 302 は、様々なサイズ、形状等でありうる。トレース 302 の各々は、図 3 に示されるように、配線基板 202 の表面 204 上の接点 208 のうちの 1 つの上に形成され、したがってその 1 つに電気的に接続されうる。一部又は全部のトレース 302 は、以下において分かるように、トレース 302 を、トレース 302 の層 300 の上方に形成されるべきトレース（例えば図 7 における 702、704、706 及び / 又は 708）の層（例えば図 7 では 700）に接続するようにビア構造（例えば図 4 における 402）が作成されるべき場所へと延在しうる。

【 0 0 1 4 】

[0030] トレース 302 は、導電性トレースを形成するのに適した任意の方法で形成されうる。いくつかの実施形態では、トレース 302 は、配線基板 202 の表面 204 上に流体又はプリント可能導電材料を施すことによって形成されうる。例えば、このような材料は、表面 204 の周囲を移動し、したがって配線基板 202 の表面 204 上の所望の位置にそのようなトレース 302 を堆積させうるディスペンサ 304 を介して施されうる。いくつかの実施形態では、ディスペンサ 304 は、インクジェットプリントヘッド（例えばエアゾール噴射機構）といったプリントヘッドでありうる。他の実施形態では、ディスペンサ 304 は、他のタイプのディスペンサであってもよい。例えばディスペンサ 304 は、トレース材料が充填されうる比較的小型の管を備えるピペットであってよく、このトレース材料は、ピペットが配線基板 202 の表面 204 上に沿って引かれる際に表面 204 上に堆積されうる。ディスペンサ 304 のタイプの関わらず、トレース 302 は、流体状でディスペンサ 304 を通じて堆積され、その後導電性トレース 302 を形成すべく乾燥又は硬化されうる材料を含みうる。例えば、トレース 302 の材料は、導電性粒子（例えば銀、金、銅等の粒子又はナノ粒子）がその中に懸濁されるインク材料でありうる。このようなインク材料は、配線基板 202 の表面 204 上に液体状態、粘性状態、又はエアゾール状態でディスペンサ 304 によって堆積され、その後乾燥されうる。しかし、ディスペンサ 304 を用いなくてもよい。例えばいくつかの実施形態では、トレース 302 は、ディスペンサを使用しない技術によって配線基板 202 の表面 204 上に形成されうる。このような技術には、電気めっき、化学蒸着、スパッタリング等が含まれうる。このような場合、トレース 302 は、導電性金属（例えば銀、金、銅等）を含みうる。

【 0 0 1 5 】

10

20

30

40

50

[0031] 図3におけるトレース302の数、形状、サイズ、及び位置は例に過ぎず、したがって、図3に示すものとは異なってもよい。例えば5つのトレース302が示されるが、より多くても少なくてもよい。別の例として、接点208毎にトレース302がある必要はない。なお、ベース配線基板202は、或いは、配線基板202の表面204上にトレース層300及びトレース302が既にある状態で、図1のプロセス100のステップ102において得られうる。他のステップのうちでもステップ104は、少なくともこの理由から任意選択であってよい。

#### 【0016】

[0032] 図1のプロセス100のステップ106において、導電性ピア構造が、トレースのうちの1以上のトレース上に形成されうる。図4は、ピア構造402（第1、第2等のピア構造の例でありうる）がトレース302上に形成される一例を示す。以下において分かるように、ピア構造402は、トレース302のうちの1以上のトレースと、トレース302の上方に形成される別のトレース層700（図7参照）におけるトレース702との間に電気的接続を与える。各ピア構造402は、近位端部404において、トレース302のうちの1つに結合され、ピア構造402がトレース702（図7参照）のうちの1つに接触するほぼその位置にある遠位端部408にまで延在しうる。図4に示されるように、各ピア構造402は、配線基板402の表面204に対して（近位端部404から遠位端部408へと）大体又はほぼ垂直に方向付けられうる。或いは、ピア構造402のうちの1以上のピア構造の本体部406（近位端部404と遠位端部408との間）が、遠位端部408が配線基板202の表面204と平行な方向において近位端部404からオフセットされるように配線基板402の表面204に対して角度が付けられうる。配線基板202の表面204と本体部406との間の角度は、15～89度、25～89度、30～89度、45～89度、60～89度及び/又は75～89度、及び/又は、20、30、45、60、75、80、85度以上との限定を含む0度と90度の間の任意の角度であってよい。（上記角度数値は例に過ぎず、本発明はこれらの角度数値のいずれにも必ずしも限定されない。）図4におけるピア構造402aは、配線基板202の表面204と約90度以外の角度が付けられた本体部406を有するピア構造の一例である。1つのそのようなピア構造402aが図4に示されるが、より多くても少なくてもよい。さらに本体部406は配線基板202の表面204から任意の方向に延在しうる。

#### 【0017】

[0033] 図4に示される例では、ピア構造402は、それらの近位端部404においてトレース302に（例えば半導体産業において知られているようなワイヤボンディング技術を用いて）接合される導電性ワイヤであってよい。例えば標準ワイヤボンディング技術を用いて、ワイヤがトレース302に接合され、繰り出され、次に切断されて、ピア構造402が形成される。しかし、ピア構造402は、ワイヤである必要はない。図5は、ピア構造402のもう1つの例を示す。図5では、ピア構造402は、ワイヤスタッド502のスタック504を含みうる。例えばワイヤは、トレース302に接合されてすぐに切断され、それにより、実質的に、トレース302に結合されたワイヤスタッド502のみを残しうる。その後、ワイヤがそのワイヤスタッド502に接合されてすぐに切断され、それにより、トレース302に結合されたワイヤスタッド502に結合された第2のワイヤスタッド502を残しうる。上記はトレース302に結合されたワイヤスタッド502のスタック504を作成するよう好きなだけ繰り返されてよく、このワイヤスタッド502のスタック504が、図4におけるピア構造402であってよい（したがって図4におけるピア構造402に取って代わってもよい。）。

#### 【0018】

[0034] （図4に示されるようにワイヤとして実施されようとも図5に示されるようにワイヤスタッド502のスタック504として実施されようとも、或いはいくつかの他の方法で実施されようとも）図4におけるピア構造402の数、形状、サイズ及び位置は、例に過ぎず、図4に示されるものと異なってもよい。例えば、図4には5つのピア構造402が示されるが、より多くても少なくてもよい。別の例として、各トレース302に結

10

20

30

40

50

合されるピア構造 402 がなくてもよい。さらに別の例として、1つのトレース 302 に 2 以上のピア構造 402 が結合されてもよい。

#### 【0019】

[0035] 図 1 のプロセス 100 に再び戻り、ステップ 108 において、ピア構造の周りに電気絶縁層が形成されうる。図 6 は、絶縁層 600 が、配線基板 202 の表面 204 及びトレース 302 上とピア構造 402 の周りに形成されうる一例を示す。絶縁層 600 は、電気絶縁材料 602 を含んでよく、また、カスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等の絶縁層）の一例でありうる。

#### 【0020】

[0036] いくつかの実施形態では、絶縁層 600 の材料 602 は、ピア構造 402 の周りに流し込まれうる。例えばダム又はモールド構造（図示せず）が、配線基板 202 の表面 204 の周辺周りに配置されて、絶縁材料 602 は、図 6 に大まかに示されるように、ダム又はモールド構造（図示せず）内に及びピア構造 402 の周りに堆積されうる。例えば、絶縁材料 602 は、配線基板 402 の表面 204 及びトレース 302 上、並びにピア構造 402 の周りに粘性状態で堆積されうる。いくつかの実施形態では、絶縁材料 602 は、シリジン又は他のディスペンサ機構を介して施されうる。別の実施形態では、絶縁材料は、配線基板 202 の表面 204 及びトレース 302 上に注がれてもよい。ピア構造 402 を損傷しないように注意しうる。

#### 【0021】

[0037] 絶縁材料 602 が配線基板 202 の表面 204 及びトレース 302 上、並びにピア構造 402 の周りに堆積された後、絶縁材料 602 は硬化されるかそうでなければ固められうる。いくつかの実施形態では、絶縁材料 602 は、硬化熱、放射（例えば紫外線）、周囲空気等にさらされて絶縁材料 602 を固めうる。他の実施形態では、絶縁材料 602 は、高温では粘性があり、室温では硬化する材料であってよい。このような絶縁材料 602 が用いられる場合、この絶縁材料 602 は、配線基板 202 上及びピア構造 402 の周りに堆積される前に十分に加熱されて（或いは配線基板 202 が加熱されて）絶縁材料 602 を粘性状態にしうる。次に、絶縁材料 602 が配線基板 202 上及びピア構造 402 の周りに堆積された後、絶縁材料 602 は、冷却され、それにより固まる。

#### 【0022】

[0038] 上記に関係なく、絶縁材料 602 が固まった後、絶縁層 600 の外面 604 は平坦化されうる（これには、絶縁材料 600 及び / 又はピア構造 402 の遠位端部 408 の一部を除去することを含みうる）。このようにすると、絶縁層 600 の厚さ及び / 又はピア構造 402 の長さが制御されうる。示されるように、ピア構造 402 の新しい遠位端部 606 が、絶縁層 600 の表面 604 に置かれうる。

#### 【0023】

[0039] 絶縁材料 602 は、配線基板 202 上及びピア構造 402 の周りに流し込むのに適している任意の材料でありうる。幾つかの実施形態では、以下の特性のうち 1 以上を考慮して、適切な絶縁材料 602 を選択しうる。すなわち、固められた際の絶縁材料 602 の熱膨張係数、固められた絶縁材料 602 が再流動する温度、固められた絶縁材料 602 の強度、剛性及び / 又は硬度等。いくつかの実施形態では、絶縁材料 602 はエポキシを含みうる。例えば、絶縁材料 602 はシリカ（石英）粉末が混合された電気絶縁材料（例えばノボラックエポキシ）を含みうる。例えば、いくつかの実施形態では、絶縁材料 602 は、ノボラックエポキシといった電気絶縁材料内に 50 ~ 90 重量パーセントの濃度でシリカ粒子を含みうる。特定の数値範囲を含む上記例は例に過ぎない。絶縁材料 602 は、他の材料及び / 又は絶縁材料内に他の濃度のシリカ又は別のそのような材料を含みうる。

#### 【0024】

[0040] 図 1 のプロセス 100 を再び参照すると、ステップ 110 において、絶縁層の外面上に別の導電性トレース層が形成されうる。図 7 は、導電性トレース 702、704、706、及び / 又は 708 を含むトレース層 700 が絶縁層 600 の外面 604 上に形

10

20

30

40

50

成されうる一例を示す。トレース層 700 は、カスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等のトレース層）の一例であってよく、トレース 702、704、706、及び／又は 708 の各々は、第 1、第 2、第 3、第 4 等のトレースの一例でありうる。トレース 702、704、706、及び／又は 708 の各々は、図 7 に示されるようにビア構造 402 のうちの 1 以上のビア構造の遠位端部 606 上に形成され、したがって遠位端部 606 に電気的に接続されうる。一部又は全部のトレース 702、704、706、及び／又は 708 は、以下において分かるように、導電性プローブ（又は他の導電性接点構造）（例えば図 9 におけるプローブ 904）が設けられるべき、又は、ビア構造（例えば図 10 における 1012）がトレース 702、704、706、及び／又は 708 に結合されるべき場所にまで延在しうる。トレース 702、704、706、及び／又は 708 は、上述したようにトレース 302 とほぼ同じであり、また、それらと同じ方法でかつ同じ 1 以上の材料で作られうる。例えばトレース 702、704、706、及び／又は 708 は、トレース 302 について可能な材料として上で特定された材料のいずれかを含み、また、トレース 702、704、706、及び／又は 708 は、トレース 302 を作成するために上で特定した方法のいずれでも作成されうる。

#### 【0025】

[0041] 図 1 のプロセス 100 を再び参照すると、ステップ 112 において、2 つ以上のトレースを、その 2 つ以上のトレース間に配置されるトレースに電気的に接続することなく、電気的に接続する導電性ジャンパが形成されうる。図 8 及び図 9 は、導電性ジャンパ 900 が形成されうる一例を示す。図 8 及び図 9 に示される例では、トレース 702 及び 706 は、トレース 704 に電気的に接続することなくジャンパ 900 によって電気的に接続されうる。しかし、上記は一例に過ぎず、ジャンパ 900 といったジャンパは、トレース層 700 における他のトレースに接続するように形成されてもよい。図 8 及び図 9 には 1 つのジャンパ 900 が示されるが、より多くの又は少ないこのようないジャンパが形成されてもよい。

#### 【0026】

[0042] 図 8 に示されるように、絶縁物質 802 が、電気的に接続されているトレース 702 及び 706 間（例えばトレース 702 及び 706 の端部間）の絶縁層 600 の表面 604 上に堆積されうる。さらに示されるように、絶縁物質 802 はさらに、ジャンパ 900 が電気的に接続されず、したがって電気的に迂回されるトレース 704 の一部上に堆積されうる。絶縁物質 802 は、電気的に接続されるべきトレース 702 及び 706 間の空間の少なくとも一部をほぼ充填しうるが、絶縁物質 802 は充填しなくてもよい。むしろ、いくつかの実施形態では、絶縁物質 802 は、トレース 702 及び 706 と絶縁物質 802 の一部に、トレース 704 に接触することなく、導電材料（図 9 では 902）が堆積されうるのに十分なトレース 704 を覆うのでよい。

#### 【0027】

[0043] 絶縁物質 802 は、基板上に電気絶縁材料を堆積させるのに適した任意の方法で堆積されうる。いくつかの実施形態では、絶縁物質 802 は、流体さもなければプリント可能材料として堆積されうる。例えば絶縁物質 802 は（図 3 に関連して説明した）ディスペンサ 304 を介して施されうる。絶縁物質 802 は、液体状態、粘性状態、又はエアゾール状態でディスペンサ 304 を介して堆積され、その後、ほぼ固体状態に乾燥又は硬化されうる材料を含みうる。例えば絶縁物質 802 は、インク材料であってよい。絶縁物質 802 がインク材料であるかどうかに関係なく、絶縁物質 802 は、特定の材料に適した任意の方法で乾燥又は硬化されうる。例えば絶縁物質 802 は、周囲空気及び温度への露出によって、又は、熱又は硬化エネルギー源への露出によって乾燥又は硬化されうる。いくつかの実施形態では、絶縁物質 802 は、ディスペンサ 304 の使用以外の技術によって堆積されうる。このような技術は、絶縁物質 802 を、スピンドルコーティングによって、又は、ブラシ、スパチュラ（spatula）等といったアプリケータを用いて堆積することを含みうる。

#### 【0028】

10

20

30

40

50

[0044] 図 9 に示されるように、導電性物質 902 が、電気的に接続されるべきトレース 702 及び 706 の一部（例えば端部）上に堆積されうる。さらに示されるように、導電性物質 902 はさらに、導電性物質 902 がトレース 702 及び 706 を、トレース 702 及び 706 間に少なくとも部分的に配置されるトレース 704 に接触することなく、そうでなければ電気的に接続することなく、電気的に接続するように、絶縁物質 802 上に堆積されうる。導電性物質 902 の堆積物は、上述したようにトレース 302 とほぼ同じであり、また、それらと同じ方法でかつ同じ 1 以上の材料で作られうる。例えば導電性物質 902 は、トレース 302 について可能な材料として上で特定された材料のいずれかを含み、また、導電性物質 902 は、トレース 302 を作成するために上で特定した方法のいずれでも堆積されうる。例えば導電性物質 902 は、導電性粒子（例えば銀、金、銅等の粒子又はナノ粒子）がその中で懸濁されるインク又は他の材料を含んでよく、また、導電性物質 902 は、液体状態、粘性状態又はエアゾール状態でディスペンサ 304（例えばインクジェットプリントヘッドといったプリントヘッド又はエアゾール噴射機構）を介してトレース 702 及び 704 並びに絶縁物質 802 上に堆積されて、次に乾燥、そうでなければ硬化されうる。10

#### 【0029】

[0045] 上述したように、ジャンパ 900 は、トレース層 700 における少なくとも 2 つのトレース（例えばトレース 702 及び 706）を、これら少なくとも 2 つのトレース間に配置されたトレース（例えば 704）に電気的に接続することなく、電気的に接続する単純で、高速、及び／又は効率的な方法でありうる。上で述べたとおり、トレース層 700 内の他のトレースを電気的に接続する 2 つ以上のそのようなジャンパ 900 がありうる。このようなジャンパ 900 は、トレース層内のトレースを電気的に接続するために追加の（例えば 600 のような）絶縁材料層及び（例えば 402 のような）ピア構造を必要とすることなく、同じトレース層（例えば 700）においてトレース（例えば 702 及び 706）間の電気的接続を与える。20

#### 【0030】

[0046] 図 3～図 10 には示されていないが、ジャンパ 900 のような 1 以上のジャンパが配線基板 202 の表面 204 上に形成されて、トレース 302 のうちの 2 つ以上のトレースを、それら 2 つ以上のトレース 302 間のトレース 302 のうちの 1 つに電気的に接続することなく、電気的に接続しうる。したがって、ステップ 112 は、図 1 のプロセス 100 におけるステップ 104 の後にも行うことができる。30

#### 【0031】

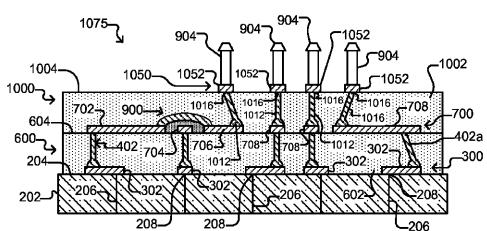

[0047] 図 1 のプロセス 100 を再び参照すると、示されるように、ステップ 106～ステップ 112 のうちの 1 以上が、ステップ 114 においてプローブを設ける前に繰り返されうる。図 10 は、ステップ 106～ステップ 112 のうちの 1 以上が繰り返されて、（第 1、第 2 等のピア構造の例であってよい）ピア構造 1012 が埋め込まれた（第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等の絶縁層の例であってよい）絶縁層 100 と、絶縁層 1000 の表面 1004 上の導電性トレース 1052 のトレース層 1050 とを含む追加のカスタマイズ層が形成される一例を示す。（トレース 1052 の層 1050 は、カスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等のトレース層）の一例であってよい。）40

#### 【0032】

[0048] 図 10 に示されるように、ピア構造 1012 は、ステップ 106 においてトレース 702、704、706、及び／又は 708 のうちの 1 以上に結合されうる。ピア構造 1012 は、ピア構造 402 と同様であってよく、またそれらと同じ方法で形成されうる。例えばピア構造 1012 は、上述したようにピア構造 402 が接合されたワイヤでありうるよう接合されたワイヤを含みうる。別の例として、ピア構造 1012 は、図 5 に關して示されかつ上述したワイヤスタッド 502 のスタック 504 のようなワイヤスタッドのスタックを含みうる。図 10 に示されるように、1 以上のピア構造 1012 は、ピア構造 402a が配線基板 202 の表面 204 に対して角度が付けられているのとほぼ同じ50

方法で、絶縁層 600 の表面 604 に対して角度が付けられる。

【0033】

[0049] 絶縁層 1000 は、絶縁材料 602 と同様でありうる電気絶縁材料 1002 を含みうる。例えば絶縁材料 1002 は、絶縁材料 602 に関して上述した材料のいずれかを含みうる。同様に、絶縁材料 1002 は、絶縁材料 602 が、配線基板 202 の表面 204 上に堆積されるかそうでなければ形成される上述した方法のいずれかにおいて表面 604、トレース層 700、及びジャンパ 900 上に堆積されるかさもなければ形成される。図 6 に関して上述したようにビア構造 402 の遠位端部 606 が絶縁材料層 600 の表面 606 に配置されるのとほぼ同じ方法で、ビア構造 1012 の遠位端部 1016 が、絶縁層 1000 の外面 1004 に配置されてよく、また、トレース層 1050 のトレース 1052 は、トレース層 700 のトレース 702、704、706、及び / 又は 708 がビア構造 402 の遠位端部 606 に電気的に接続されるのと同じ方法で遠位端部 1016 に電気的に接続される。 ( なお、絶縁層 1000 の外面 1004 は、上述したように絶縁層 600 の外面 604 が平坦化されるのと同じ方法で平坦化されうる。 ) トレース層 1050 のトレース 1052 は、上述したようにトレース 302 とほぼ同じであってよく、またそれらと同じ方法でかつ同じ 1 以上の材料で作られうる。例えばトレース 1052 は、トレース 302 について可能な材料として上で特定された材料のいずれかを含み、また、トレース 1052 は、トレース 302 を作成するために上で特定した方法のいずれでも作成されうる。図 10 には示されないが、ジャンパ 900 のような 1 以上のジャンパが、絶縁層 1000 の表面 1004 上に形成されて、トレース 1052 のうちの 2 つ以上を、ジャンパ ( 図示せず ) によって接続された当該 2 つ以上のトレース 1052 間のトレース 1052 のうちの 1 つに電気的に接続することなく、電気的に接続しうる。

【0034】

[0050] 図 1 のプロセス 100 を再び参照すると、ステップ 106 ~ ステップ 112 のうちの 1 以上が好きなだけ ( 0 回から必要に応じた回数又は好きな回数であってよい ) 繰り返された後に、ステップ 114 において、導電性接点構造 ( 例えばプローブ 904 ) がトレース層 700 内のトレース 702、704、706、及び / 又は 708 のうちの 1 以上に結合される、及び / 又はそれらの上に形成されうる。図 9 は、ステップ 106 ~ ステップ 112 が 1 回行われ、ステップ 114 が行われてプローブ 904 がトレース 702、704、706、及び / 又は 708 のうちの 1 以上に結合される一例を示す。図 10 は、ステップ 106 ~ ステップ 112 の一部又は全部が 2 回行われ、その後、ステップ 114 が行われてプローブ 904 がトレース 1052 のうちの 1 以上に結合される一例を示す。トレース 702、704、706、及び / 又は 708 に結合されているか、又はトレース 1052 に結合されているかに関わらず、プローブ 904 は、電子デバイス ( 図示せず ) の端子 ( 図示せず ) と圧力に基づいた電気的接続を行うためのものでありうる。このような場合、プローブ 904 は、トレース 702、704、706、及び / 又は 708、或いはトレース 1052 上に、接触されるべき端子 ( 図示せず ) に対応するパターンに配置されうる。プローブ 904 は、導電性のバネプローブ、ポスト、バンプ等であってよい。図 9 及び図 10 には 4 つのプローブ 904 が示されるが、より多くの又はより少ないプローブ 904 を用いてよい。さらに、図 9 及び図 10 におけるプローブ 904 のサイズ、形状、及びパターンは例に過ぎず、プローブ 904 は、図 9 又は図 10 に示されるものとは違うサイズ及び / 又は形状であっても、及び / 又は、違うパターンで配置されてもよい。

【0035】

[0051] いくつかの実施形態では、図 1 のプロセス 100 は、ベース配線基板上のカスタマイズ層がカスタム配置されたプローブへのカスタマイズされた電気的接続を与える、プローブヘッドといった多層配線基板を生成しうる。図 9 のプローブヘッド 975 は、そのようなプローブヘッドの一例でありうる。トレース層 300、絶縁層 600、トレース層 700、及び / 又はジャンパ 900 は、ベース配線基板 202 の接点 208 からカスタム配置されたプローブ 904 への電気的接続 ( 電気的に接続されたトレース 302、ビア構造 402、トレース 702、704、706、及び / 又は 708、及び / 又はジャンパ 900 ) によって接続される。

900の組み合わせ)を与えるカスタマイズ層の例でありうる。なお、プローブ904は、プローブ904が電気的に接続される接点208のパターンとは異なるパターンにあってよい。

### 【0036】

[0052] 図10のプローブヘッド1075は、そのようなプローブヘッドの別の例でありうる。トレース層300、絶縁層600、トレース層700、絶縁層1000、ジャンパ900、及び/又は、トレース層1050は、ベース配線基板202の接点208からカスタム配置されたプローブ904への電気的接続(電気的に接続されたトレース302、ピア構造402、トレース702、704、706、及び/又は708、ジャンパ900、ピア構造1012、及び/又は、トレース1052の組み合わせ)を与えるカスタマイズ層の例でありうる。再度言及するが、プローブ904は、プローブ904が電気的に接続される接点208のパターンとは違うパターンにあってよい。

### 【0037】

[0053] 以下において分かるように、プローブヘッド975及び1075は、(以下に説明する)図18及び図19におけるプローブカードアセンブリ1814と同様のプローブカードアセンブリの一部でありうるプローブヘッドの例でありうる。図9及び図10のプローブヘッド975及び1075は例に過ぎず、他のタイプの電子デバイスを、図1のプロセス100を用いて作成しうる。例えば図1のプロセス100の他のステップのうちでもステップ114は、任意選択的であってよく、行わなくてもよく、及び/又は、別のステップに取って代わられてもよい。例えばステップ114は行われなくてもよく、したがってプローブ904が任意のトレースに結合される必要もなく又はさらには存在しなくてもよい。別の例として、ステップ114においてプローブ904をトレースに結合するのではなく、1以上の別のタイプの電子構造をトレースに結合させうる。例えば抵抗、コンデンサ、トランジスタといった電子回路素子(図示せず)がトレース(例えばトレース702、704、706、及び/又は708、或いは1052)に結合されうる。いくつかの実施形態では、例えば抵抗(図示せず)がトレースを接地に電気的に接続するように抵抗(図示せず)がトレース702、704、706、及び/又は708、或いは1052に結合されうる。別の例として、抵抗がトレース702、704、706、及び/又は708、或いは1052に結合され、また、抵抗が、事実上、プローブ904へのトレースを通る電気経路において直列構成にあるようにプローブ904がトレースに結合される。上記に関係なく、このような電子回路素子(図示せず)は、トレース302を形成するために上述した技術化のいずれかを用いて形成されうる。例えば抵抗を形成する1以上の抵抗は、インク材料か、又は、所望の導電率(又は電気抵抗)を有する導電性粒子がその中に懸濁されている材料でありうる。このようなインク材料は、液体状態、粘性状態又はエアゾール状態においてディスペンサ304によって堆積され、堆積後に乾燥されうる。

### 【0038】

[0054] 別の例として、図1のプロセス100のうち特にステップ112は、任意選択であってよく、従って、ジャンパ900は作成されなくても又は含まれなくてもよい。

### 【0039】

[0055] 図11は、本発明のいくつかの実施形態に従って、ベース配線基板に1以上のカスタマイズ層を追加するための別のプロセス1100を示す。説明及び議論の便宜上、プロセス1100は、カスタマイズ層がベース配線基板202に追加される図12~図17に示される例について以下に述べられる。しかし、プロセス1100は、図12~図17に示される例に限定されない。

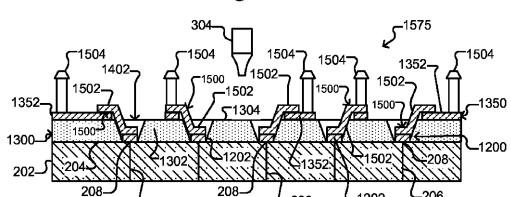

### 【0040】

[0056] 図11を参照すると、ステップ1102は、図2に関して上述したベース配線基板202であってよいベース配線基板を得ることを含みうる。図12に示されるように、配線基板202は、導電性トレース1202を含むトレース層1200を含みうる。配線基板202は、ステップ1102において、トレース1202がその上に既に形成されている状態で得られてもよいし、或いは、ステップ1102は、配線基板202の表面2

10

20

30

30

40

50

04上にトレース1202を形成することを含んでもよい。トレース1202は、上述したようにトレース302とほぼ同じであってよく、またそれらと同じ方法でかつ同じ1以上の材料で作成されうる。例えばトレース1202は、トレース302について可能な材料として上で特定された材料のいずれかを含み、またトレース302を作成するために上で特定した方法のいずれでも作成されうる。図12には5つのトレース1202が示されるが、より多くの又はより少ないトレース1202があつてよい。さらに、図12におけるトレース1202の形状、サイズ、及び配置は例に過ぎず、トレース1202は、異なる形状及び/又はサイズを有してよく、また、異なるパターンに配置されうる。トレース1202の層1200は、カスタマイズ層（例えば第1、第2、第3等のカスタマイズ層、又は、第1、第2、第3等のトレース層）の一例でありうる。

10

## 【0041】

[0057] 図11のプロセス1100を再び参照すると、ステップ1104において、絶縁層及びトレース層を含むカスタマイズ層が、配線基板上に形成されうる。図13は、電気絶縁材料1302の絶縁層1300と、複数の導電性トレース1352を含むトレース層1350とが、配線基板202上に形成されうる一例を示す。トレース1352の層1350はカスタマイズ層（例えば第1、第2、第3等のカスタマイズ層、又は、第1、第2、第3等のトレース層）の一例であつてよく、絶縁層1300はカスタマイズ層（例えば第1、第2、第3等のカスタマイズ層、又は、第1、第2、第3等の絶縁層）の一例であつてよい。

20

## 【0042】

[0058] 絶縁材料1302は、多少あるが限定された粘性を有する接着フィルム（例えばBステージエポキシフィルムといったエポキシフィルム）を含みうる。このような接着フィルムの形態の絶縁材料1302は、配線基板202の表面204上とトレース1202上に配置されうる。導電材料（例えば金、銀、銅等といった金属）のシートが、（接着フィルムの形態の）絶縁材料1302の外面1304上に配置されて、十分かつほぼ均一な圧力が導電材料シートに加えられて、それにより（接着フィルムの形態の）絶縁材料1302がトレース1202の周りに流れるようしうる。（接着フィルムの形態の）絶縁材料1302は、絶縁材料1302が配線基板202の表面204と、絶縁材料1302の外面1304上にある導電材料シートの両方に接着するように硬化されるかそうでなければ固められる。いくつかの実施形態では、絶縁材料1302は、配線基板202の表面204上に配置される前又は配置された直後に、軟化点にまで加熱されてよく、その後、絶縁材料1302は、絶縁材料1302を周囲温度にまで冷却させることによって硬化されうる。

30

## 【0043】

[0059] 上記に關係なく、絶縁材料1302が硬化された後、絶縁材料1302の表面1304上の導電材料シートは、トレース1352を形成するようにパターン付けされうる。例えば導電材料シートの一部が選択的に除去されて、トレース1352が残されうる。いくつかの実施形態では、導電材料シートの一部が絶縁材料1302から（例えばレーザを用いて）緩められて絶縁材料1302から（例えばエアブラスト、握りツール等を用いて緩められた部分に力を加えることによって）除去されうる。或いは、又は、さらには、絶縁材料1302の表面1304に接着された導電材料シートの一部が、ミリングマシン、化学エッティング等といった他の方法で除去されうる。形成方法に關係なく、トレース1352は、以下において分かるように、トレース1202及びプローブ1504へのピア構造1500（図15参照）、又は、トレース層1600への別のピア構造1750（図17参照）が形成される、絶縁層1300の表面1304上の位置に配置されうる。

40

## 【0044】

[0060] 或いは、絶縁層1300は、上述したように絶縁層600と同じ方法のいずれかで、かつ、それと同じ材料のいずれかで形成されうる。同様に、トレース1352は、上述したようにトレース302と同じ方法のいずれかで、かつ、それらと同じ材料のいずれかで形成されうる。例えばトレース1352は、トレース302について可能な材料と

50

して上で特定された材料のいずれかを含み、また、トレース 1352 は、トレース 302 を作成するために上で特定した方法のいずれでも作成されうる。

【0045】

[0061] 図 11 のプロセス 1100 を再び参照すると、ステップ 1106 及びステップ 1108 においてトレース（例えば 1202）のうちのいくつかを、トレース（例えば 1352）のうちのいくつかに電気的に接続する導電性ビア構造が形成されうる。図 14 及び図 15 は、図 11 のプロセス 1100 のステップ 1106 において絶縁層 1300 内に開口 1402 を作成し、次に図 11 のステップ 1108 において各開口 1402 の傾斜された側壁 1404 上に導電性物質 1502 を堆積させることによって、（第 1、第 2 等のビア構造の例であってよい）導電性ビア構造 1500 が形成される一例を示す。

10

【0046】

[0062] 図 14 に示されるように、各開口 1402 は、トレース 1352 のうちの 1 つに隣接して形成され、絶縁層 1300 内を延在し、トレース 1202 のうちの 1 つの一部を露出させる。各開口 1402 は、トレース 1352 に隣接する傾斜側壁 1404 を有しうる。傾斜側壁 1404 は、配線基板 202 の表面 204 に垂直な軸 1406 に対して角度を有するように傾斜されうる。いくつかの実施形態では、角度は少なくとも 15 度であります。他の実施形態では、角度は、少なくとも 10 度、少なくとも 20 度、少なくとも 30 度、又は少なくとも 45 度であります。上記角度数値は例に過ぎず、本発明はこれらの角度数値のいずれにも必ずしも限定されない。

【0047】

[0063] 開口 1402 は、絶縁材料 1302 に開口を形成するのに適した任意の方法で形成されうる。いくつかの実施形態では、レーザ 1408 が、絶縁材料 1302 内に開口 1402 を刻み込みうる。そのような場合、トレース 1202 は、レーザ 1408 が配線基板 202 内へと刻み込むことを防ぐ機能を有しうる。或いは、化学エッティング、機械的切断等を含む他の技術を用いて開口 1402 を形成しうる。

20

【0048】

[0064] 図 15 に示されるように、各ビア構造 1500 は、開口 1402 によって露出されているトレース 1202 の一部、開口 1402 の側壁 1404、及び開口 1402 に隣接するトレース 1352 の一部上に導電性基板 1502 を堆積させることによって形成されうる。導電性物質 1502 は、上述したトレース 302 と同じ 1 以上の材料であってよく、また、上述したようにトレース 302 と同じ方法で堆積されうる。例えば導電性物質 1502 は、トレース 302 について可能な材料として上で特定された材料のいずれかを含んでもよく、また、導電性物質 1502 は、トレース 302 を形成するために上で特定した方法のいずれでも堆積されかつ硬化されうる。例えば導電性物質 1502 は、導電性材料（例えば金、銀、銅等）の粒子又はナノ粒子がその中に懸濁されるインクを含んでもよく、インクはディスペンサ 304（例えばインクジェットプリントヘッドといったプリントヘッド又はエアゾール噴射機構）を介して堆積されてよく、次に、乾燥されるかそうでなければ硬化される又は固められうる。作成方法に關係なく、各ビア構造 1500 は、トレース層 1200 のトレース 1202 のうちの 1 つを、トレース層 1350 のトレース 1352 のうちの 1 つに電気的に接続しうる。いくつかの実施形態では、また、上述しきつ図面に示された例の代替として、トレース 1352 は、開口 1402 が形成された後に形成されてよく、また、トレース 1352 は、ビア構造 1500 と同時に、それと同じ材料で、また同じ方法で形成されてよく、さらには絶縁層 1300 の表面 1304 上のビア構造 1500 の延長部であってよい。

30

【0049】

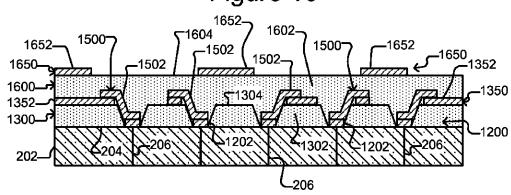

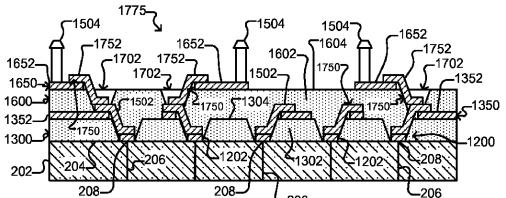

[0065] 図 11 のプロセス 1100 を再び参照すると、示されるように、ステップ 1110 においてプローブが設けられる前に、ステップ 1104～ステップ 1108 のうちの 1 回以上が繰り返されうる。図 16 及び図 17 は、絶縁層 1600、絶縁層 1600 の表面 1604 上のトレース 1652 の層 1650、及びビア構造 1750 を含む追加のカスタマイズ層を形成するようステップ 1104～ステップ 1108 が繰り返されうる例を示

40

50

す。絶縁層 1600 を通る開口 1702 内の（第 1、第 2 等のビア構造の例でありうる）導電性ビア構造 1750 は、トレース 1652 のうちのいくつかをトレース 1352 のうちのいくつかに電気的に接続しうる。

#### 【0050】

[0066] 図 16 は、図 11 のプロセス 1100 のステップ 1104 が繰り返されて、絶縁層 1300 及びトレース層 1350 上に絶縁層 1600 及びトレース層 1650 が形成される一例を示す。トレース層 1650 は、カスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等のトレース層）の一例であってよく、絶縁層 1600 はカスタマイズ層（例えば第 1、第 2、第 3 等のカスタマイズ層、又は、第 1、第 2、第 3 等の絶縁層）の一例であってよい。

10

#### 【0051】

[0067] 絶縁層 1600 の絶縁材料 1602 は、多少あるが限定された粘性を有する接着フィルム（上述したように絶縁材料 1302 と同じ材料を含みうる）を含みうる。（接着フィルムの形態の）絶縁材料 1602 は、絶縁層 1300 及びトレース層 1350 上に堆積されうる。導電材料（例えば金、銀、銅等といった金属）のシートを（接着フィルムの形態の）絶縁材料 1602 の外面 1604 上に配置させ、十分かつほぼ均一な圧力を導電材料シートに加え、それにより、図 16 に全体に示されるように、（接着フィルムの形態の）絶縁材料 1602 がトレース 1352 及びビア構造 1500 の周りに全体的に、かつ絶縁層 1300 における開口 1402 内に流れるようにしうる。図 16 には示されないが、表面 1604 は平面でなくともよい。例えば表面 1604 は、トレース 1352 に接続されたビア構造 1500 の一部の上方で隆起しうる。

20

#### 【0052】

[0068] （接着フィルムの形態の）絶縁材料 1602 は、（接着フィルムの形態の）絶縁材料 1602 がトレース 1352、ビア構造 1500 及び絶縁層 1300、並びに絶縁材料 1602 の外面 1604 上の導電材料シートに接着するように硬化されるかそうでなければ固められうる。いくつかの実施形態では、（接着フィルムの形態の）絶縁材料 1602 は、トレース 1352 及びビア構造 1500 上、並びに絶縁材料 1300 における開口 1402 内に配置される前又は配置された直後に軟化点にまで加熱されてよく、その後、（接着フィルムの形態の）絶縁材料 1602 は、絶縁材料 1602 を周囲温度にまで冷却させることによって硬化されうる。

30

#### 【0053】

[0069] 上記に関係なく、絶縁材料 1602 が硬化された後、絶縁材料 1602 の表面 1604 に接着された導電材料シートは、トレース 1652 を形成するようにパターン付けされうる。例えば導電材料シートの一部が選択的に除去されて、トレース 1652 が残されうる。これは、トレース 1352 を形成するために上述した方法のいずれでも実現可能であり、したがってトレース 1652 が形成されうる。形成方法に関係なく、トレース 1652 は、以下において分かるように、プローブ 1504（図 17 参照）又はトレース 1650 の上方に形成されるトレース層（図示せず）への別のビア構造（図示せず）が形成される、絶縁層 1600 の表面 1604 上の位置に配置されうる。

40

#### 【0054】

[0070] 或いは、絶縁層 1600 は、上述したように絶縁層 600 と同じ方法で、かつ、同じ材料で形成されうる。同様にトレース 1652 は、上述したようにトレース 302 と同じ方法のいずれでも、かつ、それと同じ材料のいずれでも形成されうる。例えばトレース 1652 は、トレース 302 について可能な材料として上で特定された材料のいずれかを含み、また、トレース 1652 は、トレース 302 を作るために上で特定した方法のいずれでも作成されうる。

#### 【0055】

[0071] 図 17 は、ステップ 1106 を繰り返して絶縁層 1600 内に開口 1702 が形成され、ステップ 1108 を繰り返してトレース 1652 のうちのいくつかをトレース 1352 及び / 又はビア構造 1500 のうちのいくつかに電気的に接続するビア構造 17

50

50が形成される一例を示す。開口1702は、図14に関して上述したような開口1402とほぼ同じであってよく、また、それらとほぼ同じ方法で形成されうる。ビア構造1750は、図15に関して上述したようなビア構造1500とほぼ同じであってよく、また、それらとほぼ同じ方法で形成されうる。さらに、ビア構造1750は、図15に関して上述したように導電物質1502と同じであってよく、また、それらと同じ方法で堆積されて硬化又は乾燥されうる導電物質1752を含みうる。トレース1352に関して上述したように、いくつかの実施形態では、また、上述しきつ図面に示された例の代替として、トレース1652は、開口1702が形成された後に形成されてよく、また、トレース1652は、ビア構造1750と同時に、それと同じ材料で、また同じ方法で形成されてよく、さらには絶縁層1600の表面1604上のビア構造1750の延長部であってよい。

10

#### 【0056】

[0072] 図11のプロセス1100を再び参照すると、ステップ1102～ステップ1108が好きなだけ(0回から必要に応じた回数又は好きな回数であってよい)繰り返された後に、ステップ1110において、導電性接点構造(例えばプローブ1504)が、カスタマイズ層の外面上の1以上のトレースに結合される及び/又はそれらの上に形成されうる。図15は、ステップ1102～ステップ1108が1回行われ、ステップ1110が行われてプローブ1504がトレース1352のうちの1以上に結合される一例を示す。図16は、ステップ1102～ステップ1108が2回行われて、次にステップ1110が行われて、プローブ1504がトレース1652のうちの1以上に結合される一例を示す。

20

#### 【0057】

[0073] トレース1352に結合されているか、又はトレース1652に結合されているかに関わらず、プローブ1504は、電子デバイス(図示せず)の端子(図示せず)との圧力に基づいた電気的接続を行うためのものであります。その場合、プローブ1504は、接触されるべき端子(図示せず)に対応するトレース1352又は1652上のパターンに配置されうる。プローブ1504は、プローブ904について上述したプローブのいずれかと同様であります。図15には5つのプローブ1504が示され、図16には3つのプローブ1504が示されるが、より多くの又は少ないプローブ904が用いられてもよい。さらには、図15及び図16におけるプローブ1504のサイズ、形状、及びパターンは例に過ぎず、プローブ1504は図15又は図16に示されるものとは違うサイズ及び/又は形状であっても、及び/又は、違うパターンで配置されてもよい。図12～図17には示されないが、図9のジャンパ900と同様の1以上のジャンパが、図11のプロセス1100の一部として形成されて、図12～図17のトレース層1200、1350、及び/又は1650のいずれかにおけるトレースを電気的に接続しうる。したがって、図1のステップ112は、図11のプロセス1100においても行われうる。

30

#### 【0058】

[0074] いくつかの実施形態では、図11のプロセス1100は、ベース配線基板上のカスタマイズ層がカスタム配置されたプローブへのカスタマイズされた電気的接続を与える、プローブヘッドといった多層配線基板を生成しうる。図15のプローブヘッド1575は、そのようなプローブヘッドの一例であります。トレース層1200、絶縁層1300、ビア構造1500、及び/又はトレース層1350は、ベース配線基板202の接点208からカスタム配置されたプローブ1504への電気的接続(電気的に接続されたトレース1202、ビア構造1500及びトレース1352の組み合わせ)を与えるカスタマイズ層の例であります。なお、プローブ1504は、プローブ904が電気的に接続される接点208のパターンとは異なるパターンにあってよい。

40

#### 【0059】

[0075] 図17のプローブヘッド1775は、別のそのようなプローブヘッドの一例であります。トレース層1200、絶縁層1300、ビア構造1500、トレース層1350、絶縁層1600、ビア構造1750、及び/又はトレース層1650は、ベース配線

50

基板 202 の接点 208 からカスタム配置されたプローブ 1504 への電気的接続（電気的に接続されたトレース 1202、ビア構造 1500、トレース 1352、ビア構造 1750 及びトレース 1652 の組み合わせ）を与えるカスタマイズ層の例でありうる。なお、プローブ 1504 は、プローブ 904 が電気的に接続される接点 208 のパターンとは異なるパターンにあってよい。

#### 【0060】

[0076] 以下において分かるように、プローブヘッド 1575 及び 1775 は（以下に説明する）図 18 及び図 19 におけるプローブカードアセンブリ 1814 と同様のプローブカードアセンブリの一部でありうるプローブヘッドの例でありうる。図 15 及び図 17 のプローブヘッド 1575 及び 1775 は例に過ぎず、他のタイプの電子デバイスを、図 11 のプロセス 1100 を用いて作成しうる。例えば図 11 のプロセス 1100 の他のステップのうちでもステップ 1110 は、任意選択的であってよく、行わなくてもよく、及び / 又は、別のステップに置き換えられてもよい。例えばステップ 1110 は行わなくてよく、したがってプローブ 1504 は任意のトレースに結合される必要もなく又は存在しなくてよい。別の例として、ステップ 1110 において、プローブ 1504 をトレースに結合するのではなく、1 以上の別のタイプの電子構造をトレースに結合してもよい。例えば抵抗、コンデンサ、トランジスタ等といった電子回路素子（図示せず）がトレース（例えばトレース 1352 又は 1652）に結合されうる。

10

#### 【0061】

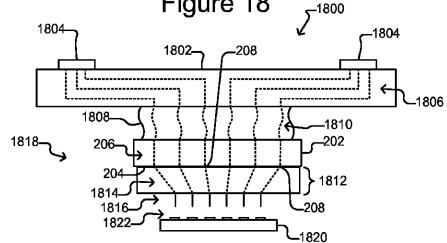

[0077] 上記の通り、図 1 及び図 11 のプロセス 100 及び 1100 は、ベース配線基板上に、ベース配線基板上又は内のビア又は他の電気的接点構造から、プローブといったカスタム配置された電気素子へのカスタマイズされた電気的接続を与えるカスタマイズ層を形成する例を示す。このようなカスタマイズされたベース配線基板には多くの実用的な用途がある。図 18 は、図 1 のプロセス 100 又は図 11 のプロセス 1100 によりカスタマイズされたベース配線基板が生成されて、プローブカードアセンブリ 1800 の構成要素として使用されうる、かかる用途の一例を示す。以下において分かるように、プローブカードアセンブリ 1800 は、図 1 のプロセス 100 又は図 11 のプロセス 1100 に従って配線基板 202 に 1 以上のカスタマイズ層 1812 が追加されたベース配線基板 202 を含みうるプローブヘッド 1818 を含みうる。

20

#### 【0062】

30

[0078] 図 18 は、1 以上の半導体ダイ（例えばダイがその上に作られたウェーハから単体化される又は単体化されていない、パッケージ化される又はパッケージ化されていない）又は入力及び / 又は出力端子 1822 を有する他の電子デバイスといった 1 以上の試験用電子デバイスでありうる DUT 1820 を試験するように用いられうるプローブカードアセンブリ 1800 の一例を示す。図 18 に示されるように、プローブカードアセンブリ 1800 は、配線基板 1802、電気コネクタ 1808、及びプローブヘッド 1818 を含んでよく、これらはすべて互いに（例えば、クランプ、ボルト、ネジ等（図示せず）によって）機械的に結合されうる。導電性プローブ 1816 は、DUT 1820 の端子 1822 の少なくともいくつかに対応するパターンで、プローブヘッド 1818 上に配置されうる。プローブ 1816 は、端子 1822 と電気的に接続するように DUT 1820 の端子 1822 に押し付けられると、主に弾性的挙動を示しうる。6 つのプローブ 1816 及び 6 つの端子 1822 が示されるが、より多くても少なくともよい。さらに、いくつかの実施形態では、端子 1822 より少ないプローブ 1816 があつてよく、したがって、その場合、すべての端子 1822 に接觸するようプローブ 1816 は複数の端子 1822 に接地しうる。プローブヘッド 1818 を通るカスタム電気的接続 1814 及びビア 206 と、電気コネクタ 1808 を通る電気的接続 1810 と、配線基板 1802 を通る電気的接続 1806 は、プローブ 1816 を、配線基板 1802 上の電気的インターフェース 1804 に電気的に接続しうる。

40

#### 【0063】

[0079] 電気的インターフェース 1804 は、図 19 における試験コントローラ 1902

50

と同様の試験コントローラ(図示せず)への及びそこからの個々の通信チャネルに接続される複数の電気コネクタを含みうる。例えば電気的インターフェース1804は、ゼロ插入力(ZIF)電気コネクタ、ポゴピンパッド又は他のそのような電気コネクタを含みうる。配線基板1802は、プリント回路基板等といった剛性又は半剛性配線基板でありうる。配線基板1802を通る電気接続1806は、配線基板1802上及び/又は内の導電性ビア及び/又はトレースでありうる。電気コネクタ1808は、電気的接続1806のうちのいくつかとプローブヘッド1818との間の複数の電気的接続1810を含みうる。電気的コネクタ1808は、電気的接続1806をプローブヘッド1818に接続するのに適した任意のデバイス又は電気コネクタの集まりでありうる。例えば電気コネクタ1808は、インターポーザ、ワイヤ、はんだ等を含みうる。

10

## 【0064】

[0080] プローブヘッド1818は、上述したベース配線基板202と、配線基板202の表面204上又は表面における接点208からカスタム配置されたプローブ1816へのカスタム電気的接続1814を与える1以上のカスタマイズ層1812とを含みうる。プローブ1816は、プローブ1816が端子1822のうちの少なくともいくつかと位置合わせされ、従って接触するようにDUT1820の端子1822の少なくともいくつかの端子のパターンに対応するパターンに配置されうる。

## 【0065】

[0081] いくつかの実施形態では、カスタマイズ層1812及びプローブ1816は、図1のプロセス100を用いてベース配線基板202に追加されうる。したがって、プローブヘッド975は、図18のプローブヘッド1818の一例であってよく、したがって、プローブヘッド975は、図18のプローブヘッド1818に取って代わりうる。その場合、図9におけるトレース層300及び700、絶縁層600、ビア構造402及びジャンパ900は、図18におけるカスタマイズ層1812の例であり、図9におけるプローブ904は、図18におけるプローブ1816の一例であり、また、図9における、接点208のうちの1つをプローブ904のうちの1つに電気的に接続する、電気的に接続されたトレース302、ビア構造402、ジャンパ900及び/又はトレース702は、図18におけるカスタム電気的接続1814の例でありうる。

20

## 【0066】

[0082] 同様に、プローブヘッド1075は、図18におけるプローブヘッド1818の別の例でありうる。したがって、プローブヘッド1075は、図18のプローブヘッド1818に取って代わりうる。その場合、図10におけるトレース層300、700及び1050、絶縁層600及び1000、ビア構造402及び1012及びジャンパ900は、図18におけるカスタマイズ層の一例でありうる。同様に、図10におけるプローブ904は、図18におけるプローブ1816の一例でありうる。図10における、接点208のうちの1つをプローブ904のうちの1つに電気的に接続する、電気的に接続されたトレース302、ビア構造402、トレース702、ジャンパ900、ビア構造1012及びトレース1052は、図18におけるカスタム電気的接続1814の例でありうる。

30

## 【0067】

[0083] 或いは、いくつかの実施形態では、カスタマイズ層1812及びプローブ1816は、図11のプロセス1100を用いてベース配線基板202に追加されうる。したがって、図15のプローブヘッド1575は、図18におけるプローブヘッド1818の一例であってよく、したがって、プローブヘッド1575は、図18におけるプローブヘッド1818に取って代わりうる。そのような場合、図15におけるトレース層1200及び1350、絶縁層1300及びビア構造1500は、図18におけるカスタマイズ層1812の例であってよく、図15におけるプローブ1504は、図18におけるプローブ1816の例でありうる。また、図15における、接点208のうちの1つをプローブ1504のうちの1つに電気的に接続する、電気的に接続されたトレース1202、ビア構造1500及びトレース1532は、図18におけるカスタム電気接続1814の例で

40

50

ありうる。

【0068】

[0084] 同様に、図17のプローブヘッド1775は、図18におけるプローブヘッド1818の別の例であってよく、したがって、プローブヘッド1775は、図18のプローブヘッド1818に取って代わりうる。そのような場合、図17における、トレース層1200、1350及び1650、絶縁層1300及び1600及びビア構造1500及び1750は、図18におけるカスタマイズ層1812の例でありうる。同様に、図17におけるプローブ1504は、図18におけるプローブ1816の例でありうる。図17における、接点208のうちの1つをプローブ1504のうちの1つに電気的に接続する、電気的に接続されたトレース1202、ビア構造1500、トレース1352、ビア構造1750及びトレース1652は、図18におけるカスタム電気的接続1814の例でありうる。

10

【0069】

[0085] 図18のプローブカードアセンブリは、次の通りに作成されうる。試験されるDUT1820の端子1822の位置に関する情報が受信されうる。端子1822の位置に必ずしも対応しない接点208のパターンを有するベース配線基板202が入手されうる。(接点208は、DUT1820の端子1822に対応する必要がないので、端子1822の位置についての情報を受信する前にベース配線基板202を入手してもよい。)図1のプロセス100、図11のプロセス1100、又は同様のプロセスに従って、配線基板202の接点208から、端子1822の位置に関する情報に従ってプローブ1816をDUT1820の端子1822に位置合わせするパターンに配置されうる、プローブ1816へのカスタム電気的接続1814を与えるカスタマイズ層1812が、ベース配線基板202に追加されうる。したがって、プローブ1816のパターンは、DUT1820の端子1822のパターンに対応するようにカスタマイズされうる。

20

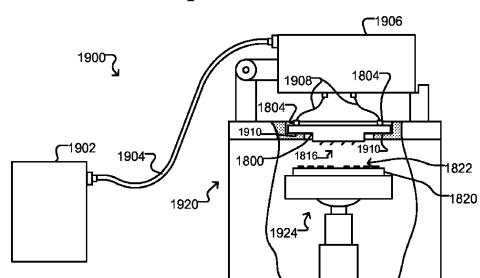

【0070】

[0086] 図19は、本発明のいくつかの実施形態に従って、DUT1820を試験するためにプローブカードアセンブリ1800を用いる試験システム1900の一例を示す。図19に示されるように、試験システム1900は、DUT1820に入力信号を提供でき、また、入力信号に呼応してDUT1820により生成される応答信号を受信しうる試験コントローラ1902を含みうる。「試験信号」との用語は、一般的に、試験コントローラ1902によって生成された入力信号及びDUT1820によって生成された応答信号の片方又は両方を指しうる。プローブカードアセンブリ1800は、試験システム1900のハウジング1920(例えばプローバー)のマウント機構1910に結合されうる。プローブカードアセンブリ1800のプローブ1816は、DUT1820の端子1822と圧力に基づいて電気的に接続して、試験信号が試験コントローラ1902とDUT1820との間で通信接続1904(例えば同軸ケーブル、ワイヤレスリンク、光ファイバーリンク等)、試験ヘッド1906内の電子機器(図示せず)、試験ヘッド1906と電気的インタフェース1804との間の電気的接続1908、及びプローブカードアセンブリ1800を介して送られうる。

30

【0071】

[0087] DUT1820は以下の通りに試験されうる。プローブカードアセンブリ1800は、ハウジング1920のマウント機構1910に結合され、DUT1820の端子1822は、プローブカードアセンブリ1800のプローブ1816に接触しうる。これは、その上にDUT1820が配置されるチャック1924を、DUT1820の端子1822がプローブカードアセンブリ1800のプローブ1816に押し付けられるように動かすことにより達成されうる。或いは、プローブカードアセンブリ1800、又は、チャック1924及びプローブカードアセンブリ1800の両方が動かされて、端子1822とプローブ1816とを接触させうる。

40

【0072】

[0088] プローブ1816及び端子1822が接触している間、DUT1820は、ブ

50

ロープカードアセンブリ 1800 を介して試験コントローラ 1902 と DUT 1820 との間で試験信号（上述したように、試験コントローラ 1902 によって生成された入力信号と、入力信号に呼応して DUT 1820 によって生成された応答信号を含みうる）を提供することによって試験されうる。試験コントローラ 1902 は、応答信号を分析して、DUT 1820 が試験を合格しているかどうかを判定する。例えば試験コントローラ 1902 は、応答信号を期待応答信号と比較しうる。応答信号が期待応答信号と一致する場合には、試験コントローラ 1902 は、DUT 1820 が試験を合格したと判定しうる。そうでなければ、試験コントローラ 1902 は、DUT 1820 が試験に不合格であったと判定しうる。別の例として、試験コントローラ 1902 は、応答信号が許容範囲内にあるかどうかを判定し、範囲内にある場合には、DUT 1820 が試験に合格したと判定しうる。

10

[ 0 0 7 3 ]

[0089] 図18のプローブカードアセンブリ1800及び図19の試験システム1900は例に過ぎない。例えば図9のプローブヘッド975、図10のプローブヘッド1075、図16のプローブヘッド1675及び図17のプローブヘッド1775は、異なるプローブカードアセンブリ又は試験コンタクタといった他の電子デバイスにおいて用いられる。別の例として、図18のプローブカードアセンブリ1800は、他の試験システムにおいて用いられる。

〔 0 0 7 4 〕

[0090] 本明細書において本発明の特定の実施形態及び用途を記載したが、これらの実施形態及び用途は例に過ぎず、多くのバリエーションが可能である。

20

( 1 )

### 【図2】

( 3 )

【図4】

( 5 )

【圖 6】

〔圖7〕

Figure 7

【 义 8 】

Figure 8

【圖 9】

Figure 9

【习题 1 2】

Figure 12

【 义 1 3 】

Figure 13

【図14】

Figure 14

【図10】

Figure 10

【 図 1 1 】

【 15 】

Figure 15

【 16 】

Figure 16

【図 17】

Figure 17

【図18】

Figure 18

【図19】

Figure 19

---

フロントページの続き

(72)発明者 エルドリッジ,ベンジャミン エヌ.

アメリカ合衆国 カリフォルニア州 94551, リバーモア, サウスフロント ロード 700

5

(72)発明者 マシュー, ガエタン エル.

アメリカ合衆国 カリフォルニア州 94551, リバーモア, サウスフロント ロード 700

5

合議体

審判長 阿部 利英

審判官 中川 隆司

審判官 小関 峰夫

(56)参考文献 特開平11-112145 (JP, A)

特開2003-152133 (JP, A)

特開2005-332887 (JP, A)

特開平11-317383 (JP, A)

特開昭63-301593 (JP, A)

実開昭60-187552 (JP, U)

特開平4-151899 (JP, A)

特開2006-132223 (JP, A)

特開2005-327986 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H05K3/46