(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년02월06일

(11) 등록번호 10-1826397

(24) 등록일자 2018년01월31일

(51) 국제특허분류(Int. Cl.)

G06F 13/42 (2006.01) G06F 13/38 (2006.01)

(52) CPC특허분류

G06F 13/4221 (2013.01)

G06F 13/385 (2013.01)

(21) 출원번호 10-2015-0157896

(22) 출원일자 2015년11월11일

심사청구일자 2015년11월11일

(65) 공개번호 10-2016-0072014

(43) 공개일자 2016년06월22일

(30) 우선권주장

14/569,041 2014년12월12일 미국(US)

(56) 선행기술조사문현

US20140129753 A1\*

(뒷면에 계속)

전체 청구항 수 : 총 20 항

(73) 특허권자

인텔 코포레이션

미합중국 캘리포니아 95054 산타클라라 미션 칼리지 블러바드 2200

(72) 발명자

타마킨 블라디미르

미국 펜실베니아주 19006 헨팅던 벨리 레이럴리 웨이 3573

제네티 웨인

미국 펜실베니아주 19464 사나토가 뉴 케플러 로드 1110

슈바이처 레이비드

미국 펜실베니아주 19426 콜리지빌 놀 로드 116

(74) 대리인

제일특허법인

심사관 : 김병균

(54) 발명의 명칭 다수의 PCIe 커넥터를 가진 PCIe 카드

**(57) 요 약**

일부 실시예는 회로 기판과, 회로 기판 상에 배치된 디바이스와, 회로 기판 상에 배치되고 디바이스에 연결된 제 1 PCIe(Peripheral Component Interconnect Express) 커넥터와, 회로 기판 상에 배치되고 디바이스에 연결된 제 2 PCIe 커넥터를 가진 장치 및 방법을 포함한다. 제 1 PCIe 커넥터는 추가 회로 기판의 제 1 커넥터에 연결하도록 구성된다. 제 2 PCIe 커넥터는 추가 회로 기판의 제 2 커넥터에 연결하도록 구성된다.

**대 표 도 - 도1**

(56) 선행기술조사문현

KR1020140110004 A\*

KR2019980029610 U

KR1020140142112 A

JP2013543609 A

\*는 심사관에 의하여 인용된 문현

---

## 명세서

### 청구범위

#### 청구항 1

회로 기판과,

상기 회로 기판 상에 배치된 디바이스와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 1 PCIe(Peripheral Component Interconnect Express) 커넥터 -상기 제 1 PCIe 커넥터는 추가 회로 기판의 제 1 커넥터에 연결하도록 구성됨- 와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 2 PCIe 커넥터 -상기 제 2 PCIe 커넥터는 상기 추가 회로 기판의 제 2 커넥터에 연결하도록 구성됨- 와,

상기 디바이스를 상기 회로 기판의 제 1 입출력(I/O) 커넥터에 연결하도록 배치된 제 1 도전성 콘택트 -상기 제 1 도전성 콘택트는 상기 제1 입출력(I/O) 커넥터를 통해 제1 컴퓨터 네트워크로부터 신호를 전도(conduct signals)하도록 배치됨- 와,

상기 디바이스를 상기 회로 기판의 제 2 입출력(I/O) 커넥터에 연결하도록 배치된 제 2 도전성 콘택트 -상기 제 2 도전성 콘택트는 상기 제2 입출력(I/O) 커넥터를 통해 제2 컴퓨터 네트워크로부터 신호를 전도하도록 배치됨- 를 포함하는

장치.

#### 청구항 2

제 1 항에 있어서,

상기 추가 회로 기판의 제 1 커넥터는 제 1 PCIe 슬롯을 포함하고, 상기 추가 회로 기판의 제 2 추가 커넥터는 제 2 PCIe 슬롯을 포함하는

장치.

#### 청구항 3

제 1 항에 있어서,

상기 회로 기판은 제 1 에지 및 제 2 에지를 포함하고, 상기 제 1 PCIe 커넥터는 상기 제 1 에지에 배치된 도전체를 포함하고, 상기 제 2 PCIe 커넥터는 상기 제 2 에지에 배치된 도전체를 포함하는

장치.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 에지는 상기 제 2 에지와 마주보는

장치.

#### 청구항 5

회로 기판과,

상기 회로 기판 상에 배치된 디바이스와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 1 PCIe(Peripheral Component Interconnect Express) 커넥터 -상기 제 1 PCIe 커넥터는 추가 회로 기판의 제 1 커넥터에 연결하도록 구성됨- 와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 2 PCIe 커넥터 -상기 제 2 PCIe 커넥터는 상기 추가 회로 기판의 제 2 커넥터에 연결하도록 구성됨- 를 포함하되,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각은 도전체를 포함하고,

상기 제 1 PCIe 커넥터의 도전체는 상기 회로 기판의 제 1 측면 상의 제 1 도전체 그룹 및 상기 회로 기판의 제 2 측면 상의 제 2 도전체 그룹을 포함하며,

상기 제 2 PCIe 커넥터의 도전체는 상기 회로 기판의 제 2 측면 상의 제 1 도전체 그룹 및 상기 회로 기판의 제 1 측면 상의 제 2 도전체 그룹을 포함하고,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 1 도전체 그룹은 인쇄 회로 기판(PCB)의 제 1 측면에 대한 PCIe 커넥터 핀아웃(pin-out) 사양에 기초하여 배치되며,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 2 도전체 그룹은 상기 PCB의 제 2 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 배치되는

장치.

## 청구항 6

회로 기판과,

상기 회로 기판 상에 배치된 디바이스와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 1 PCIe(Peripheral Component Interconnect Express) 커넥터 -상기 제 1 PCIe 커넥터는 추가 회로 기판의 제 1 커넥터에 연결하도록 구성됨- 와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 2 PCIe 커넥터 -상기 제 2 PCIe 커넥터는 상기 추가 회로 기판의 제 2 커넥터에 연결하도록 구성됨- 를 포함하되,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 1 추가 커넥터 -상기 제 1 추가 커넥터는 제 1 컴퓨터 네트워크 표준에 기초하여 신호를 전도하도록 배치됨- 와,

상기 회로 기판 상에 배치되고 상기 디바이스에 연결된 제 2 추가 커넥터 -상기 제 2 추가 커넥터는 제 2 컴퓨터 네트워크 표준에 기초하여 신호를 전도하도록 배치됨- 를 더 포함하는

장치.

## 청구항 7

제 6 항에 있어서,

상기 회로 기판은 제 1 에지, 제 2 에지 및 제 3 에지를 포함하고, 상기 제 1 PCIe 커넥터는 상기 제 1 에지에 배치된 도전체를 포함하고, 상기 제 2 PCIe 커넥터는 상기 제 2 에지에 배치된 도전체를 포함하며, 상기 제 1 추가 커넥터 및 상기 제 2 추가 커넥터는 상기 제 3 에지에 배치되는

장치.

## 청구항 8

제 5 항에 있어서,

상기 회로 기판과, 상기 디바이스와, 상기 제 1 PCIe 커넥터와, 상기 제 2 PCIe 커넥터는 확장 카드의 일부인 장치.

### 청구항 9

제 8 항에 있어서,

상기 확장 카드는 호스트 어댑터 디바이스, 네트워크 인터페이스 제어기(NIC) 디바이스 또는 수령 네트워크 어댑터 디바이스 중 하나를 포함하는 장치.

### 청구항 10

제 8 항에 있어서,

상기 확장 카드는 PCIe 폼 팩터(form factor)를 따르는 장치.

### 청구항 11

집적 회로(IC) 칩과,

PCIe 카드의 제 1 PCIe 커넥터에 연결하도록 배치된 상기 IC 칩의 제 1 도전성 콘택트와,

상기 PCIe 카드의 제 2 PCIe 커넥터에 연결하도록 배치된 상기 IC 칩의 제 2 도전성 콘택트와,

상기 PCIe 카드의 제 1 입출력(I/O) 커넥터에 연결하도록 배치된 제 3 도전성 콘택트와,

상기 PCIe 카드의 제 2 I/O 커넥터에 연결하도록 배치된 제 4 도전성 콘택트를 포함하되,

상기 제 3 도전성 콘택트는 상기 PCIe 카드의 상기 제 1 I/O 커넥터를 통해 제 1 컴퓨터 네트워크로부터 신호를 전도하도록 배치되고,

상기 제 4 도전성 콘택트는 상기 PCIe 카드의 상기 제 1 I/O 커넥터를 통해 제 2 컴퓨터 네트워크로부터 신호를 전도하도록 배치되는

장치.

### 청구항 12

제 11 항에 있어서,

상기 제 1 도전성 콘택트는, 상기 제 1 PCIe 커넥터를 통해 상기 IC 칩에 연결된 회로 기판 상의 구성요소들 중 하나와 상기 IC 칩 사이의 제 1 포인트 투 포인트 PCIe 접속부를 통해 신호를 전도하도록 배치되고, 상기 제 2 도전성 콘택트는, 상기 제 2 PCIe 커넥터를 통해 상기 IC 칩에 연결된 상기 회로 기판 상의 구성요소들 중 하나와 상기 IC 칩 사이의 제 2 포인트 투 포인트 PCIe 접속부를 통해 신호를 전도하도록 배치되는

장치.

### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

제 11 항에 있어서,

상기 제 1 도전성 콘택트, 상기 제 2 도전성 콘택트, 상기 제 3 도전성 콘택트, 및 상기 제 4 도전성 콘택트는

솔더 볼과 도전성 핀 중 하나를 포함하는

장치.

#### 청구항 16

제 1 PCIe 슬롯 및 제 2 PCIe 슬롯을 포함하는 회로 기판과,

디바이스, 상기 디바이스 및 상기 제 1 PCIe 슬롯에 연결된 제 1 PCIe 커넥터, 상기 디바이스 및 상기 제 2 PCIe 슬롯에 연결된 제 2 PCIe 커넥터, 상기 디바이스에 연결된 제 1 입출력(I/O) 커넥터, 및 상기 디바이스에

연결된 제 2 I/O 커넥터를 포함하는 PCIe 카드를 포함하되,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각은 도전체를 포함하고,

상기 제 1 PCIe 커넥터의 도전체는 상기 PCIe 카드의 제 1 측면 상의 제 1 도전체 그룹 및 상기 PCIe 카드의 제

2 측면 상의 제 2 도전체 그룹을 포함하며,

상기 제 2 PCIe 커넥터의 도전체는 상기 PCIe 카드의 상기 제 2 측면 상의 제 1 도전체 그룹 및 상기 PCIe 카드

의 상기 제 1 측면 상의 제 2 도전체 그룹을 포함하고,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 1 도전체 그룹은 인쇄 회로 기판(PCB)의 제

1 측면에 대한 PCIe 커넥터 핀아웃(pin-out) 사양에 기초하여 배치되며,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 2 도전체 그룹은 상기 PCB의 제 2 측면에

대한 PCIe 커넥터 핀아웃 사양에 기초하여 배치되는

전자 시스템.

#### 청구항 17

제 16 항에 있어서,

상기 제 1 PCIe 커넥터는 PCIe 라이저(riser)를 통해 상기 제 1 PCIe 슬롯에 연결되고, 상기 제 2 PCIe 커넥터

는 PCIe 확장기 케이블을 통해 상기 제 2 PCIe 슬롯에 연결되는

전자 시스템.

#### 청구항 18

제 16 항에 있어서,

상기 PCIe 카드는 상기 회로 기판과 별도로 배치되는

전자 시스템.

#### 청구항 19

제 16 항에 있어서,

상기 PCIe 카드는 상기 회로 기판에 수직으로 배치되는 전자 시스템.

### 청구항 20

회로 기판의 제 1 측면 상에 제 1 PCIe 커넥터의 제 1 도전체 그룹을 형성하는 단계와,

상기 회로 기판의 제 2 측면 상에 상기 제 1 PCIe 커넥터의 제 2 도전체 그룹을 형성하는 단계와,

상기 회로 기판의 상기 제 2 측면 상에 제 2 PCIe 커넥터의 제 1 도전체 그룹을 형성하는 단계와,

상기 회로 기판의 상기 제 1 측면 상에 상기 제 2 PCIe 커넥터의 제 2 도전체 그룹을 형성하는 단계를 포함하는

방법.

### 청구항 21

제 20 항에 있어서,

상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 1 도전체 그룹은 인쇄 회로 기판(PCB)의 제 1 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 형성되고, 상기 제 1 PCIe 커넥터 및 상기 제 2 PCIe 커넥터의 각각의 상기 제 2 도전체 그룹은 상기 PCB의 제 2 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 형성되는

방법.

### 청구항 22

제 20 항에 있어서,

상기 제 1 PCIe 커넥터의 제 1 도전체 그룹과 제 2 도전체 그룹은 상기 회로 기판의 제 1 에지에 형성되고, 상기 제 2 PCIe 커넥터의 제 1 도전체 그룹과 제 2 도전체 그룹은 상기 회로 기판의 제 2 에지에 형성되며, 상기 제 2 에지는 상기 제 1 에지와 마주보는

방법.

### 발명의 설명

#### 기술 분야

[0001] 본 명세서에 설명된 실시예는 PCIe(Peripheral Component Interconnect Express)에 관한 것이다. 일부 실시예는 PCIe 카드에 관한 것이다.

#### 배경 기술

[0002] 서버와 같은 컴퓨터의 다수의 회로 기판(예컨대, 마더보드)은 PCIe 슬롯을 포함한다. 각각의 PCIe 슬롯은 PCIe 카드의 PCIe 커넥터에 연결되어 PCIe 카드 상의 추가 기능이 컴퓨터에 추가되게 할 수 있다. 표준 PCIe 카드는 단일 PCIe 커넥터를 갖는다. 일부 경우에, 그러한 표준 PCIe 카드는 일부 컴퓨터에서 사용하기에 부적합할 수 있다.

#### 도면의 간단한 설명

[0003] 도 1은 본 명세서에 설명된 일부 실시예에 따라, 다수의 PCIe 커넥터를 가진 PCIe 카드 형태의 장치를 도시한다.

도 2는 본 명세서에 설명된 일부 실시예에 따라, PCIe 커넥터의 일부 도전체를 포함하는 도 1의 PCIe 카드의 일

부를 도시한다.

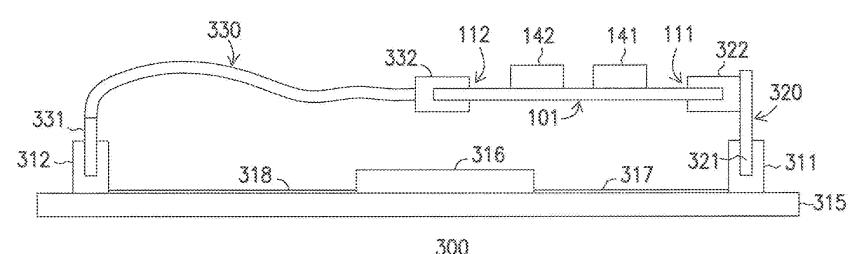

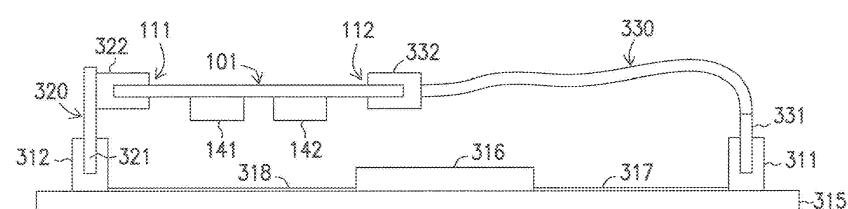

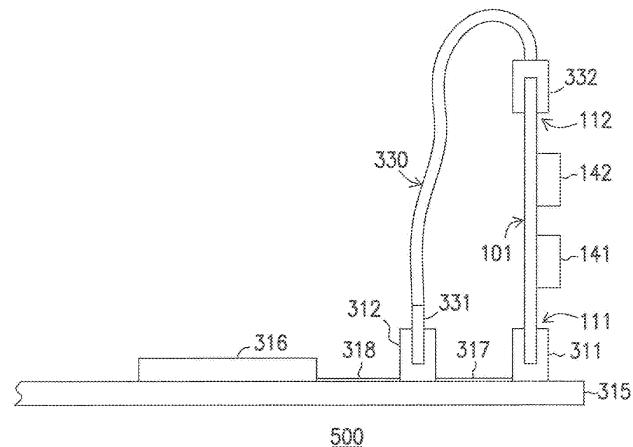

도 3, 도 4 및 도 5는 본 명세서에 설명된 일부 실시예에 따라, 상이한 전자 시스템에서 도 1의 PCIe 카드의 상이한 구성을 도시한다.

도 6은 본 명세서에 설명된 일부 실시예에 따라, PCIe 카드를 제조하는 방법을 도시하는 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

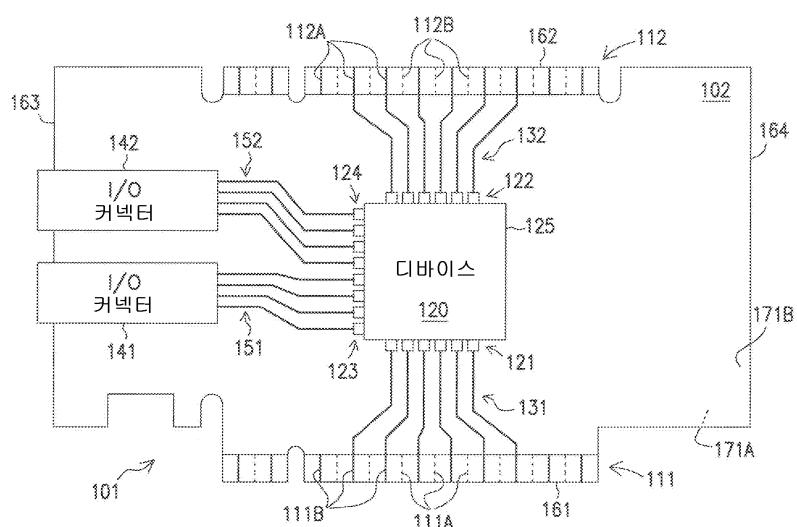

[0004] 도 1은 본 명세서에 설명된 일부 실시예에 따라, 다수의 PCIe 커넥터(예컨대, 포트)(111 및 112)를 가진 PCIe 카드(101) 형태의 장치를 도시한다. PCIe 커넥터(111 및 112)는 PCIe 사양을 준수한다. PCIe 커넥터(111 및 112)는 추가 회로 기판 상에 배치된 2 개의 다른 PCIe 커넥터(예컨대, 2 개의 PCIe 슬롯)를 통해 추가 회로 기판(예컨대, 컴퓨터의 마더보드) 상의 PCIe 버스에 연결될 수 있다. 이 설명에서, PCIe 사양은 미국 오리건주 포트랜드에 위치한 PCI-SIG(Peripheral Component Interconnect Special Interest Group) 기구에 의해 개발되고 유지되는 PCIe 사양을 지칭한다.

[0005] 도 1의 PCIe 카드(101)는 PCIe 폼 팩터(form factor)에 따르는 확장 카드일 수 있다. 그러한 확장 카드의 예는 호스트 어댑터 디바이스(예컨대, 호스트 버스 어댑터 디바이스), 네트워크 인터페이스 제어기(NIC) 디바이스, 수령 네트워크 어댑터 디바이스 및 다른 유형의 확장 카드를 포함한다.

[0006] 도 1에 도시된 바와 같이, PCIe 카드(101)는 회로 기판(예컨대, 인쇄 회로 기판(PCB))(102) 및 회로 기판(102) 상에 배치된 디바이스(120)를 포함할 수 있다. 디바이스(120)의 예는 ASIC(application specific integrated circuit)과 같은 제어기 디바이스를 포함한다. 디바이스(120)는 하나보다 많은 PCIe 포트(예컨대, PCIe 커넥터)를 지원할 수 있다. 예컨대, 디바이스(120)는 PCIe 커넥터(111)에 연결된 추가 회로 기판(예컨대, 마더보드) 상의 구성요소와 디바이스(120) 사이의 통신을 지원하도록 회로 기판(102) 상의 접속부(131)를 통해 PCIe 커넥터(111)에 연결될 수 있다. 접속부(131)는 추가 회로 기판 상의 그러한 구성요소와 디바이스(120) 사이의 독립적인 접속부의 일부일 수 있다. 그러한 독립적인 접속부는 PCIe 사양에 기초하여 디바이스(120)와 다른 구성요소 사이의 전기적 통신을 허용하는 포인트 투 포인트 PCIe 접속부와 같은 전용 접속부를 포함할 수 있다. 다른 예에서, 디바이스(120)는 PCIe 커넥터(112)에 연결된 추가 회로 기판 상의 구성요소와 디바이스(120) 사이의 통신을 지원하도록 회로 기판(102) 상의 접속부(132)를 통해 PCIe 커넥터(112)에 연결될 수 있다. 접속부(132)는 추가 회로 기판 상의 그러한 구성요소와 디바이스(120) 사이의 다른 독립적인 접속부(예컨대, 다른 포인트 투 포인트 PCIe 접속부와 같은 다른 전용 접속부)의 일부일 수 있다.

[0007] 도 1에 도시된 바와 같이, PCIe 카드(101)는 또한 회로 기판(102) 상에 배치되고 회로 기판(102) 상에서 각각 접속부(예컨대, 도전 경로)(151 및 152)를 통해 디바이스(102)에 연결된 입출력(I/O) 커넥터(141 및 142)를 포함할 수 있다. 커넥터(141 및 142)의 각각은 (예컨대, 네트워크를 통해) 다른 디바이스 또는 시스템에 연결하도록 배열될 수 있다. 예컨대, 커넥터(141)는 네트워크 접속부를 통해 디바이스(또는 시스템)에 연결될 수 있다. 커넥터(142)는 다른 네트워크를 통해 다른 디바이스(또는 시스템)에 연결될 수 있다. 커넥터(141 및 142)에 연결된 네트워크는 이더넷, 파이버 채널 및 인피니밴드와 같은 상이한 네트워크를 포함할 수 있다.

[0008] 도 1에 도시된 바와 같이, 회로 기판(102)은 서로 마주보는 에지(161 및 162), 에지(161 및 162) 중 하나와 바로 인접하는 에지(163), 및 에지(161 및 162) 중 하나와 바로 인접하는 에지(164)를 포함한다. PCIe 커넥터(111 및 112)는 각각 에지(161 및 162)에 배치될 수 있다. I/O 커넥터(141 및 142)는 에지(163)에 배치될 수 있다. 도 1은 예로써 PCIe 커넥터(111 및 112)가 회로 기판(102)의 마주보는 에지(161 및 162)에 배치되는 예를 도시한다. 다른 배열에서, PCIe 커넥터(111 및 112) 중 하나(예컨대, 111)는 에지(161)(또는 162)에 배치될 수 있고 다른 PCIe 커넥터(예컨대, 112)는 에지(163)에 배치될 수 있다. 그러나, PCIe 커넥터(111 및 112)를 마주보는 에지(도 1에 도시된 바와 같이 에지(161 및 162))에 배치하는 것은 다른 PCIe 커넥터(예컨대, 111)가 추가 회로 기판(예컨대, 마더보드) 상의 슬롯 내에 삽입된 후에 다른 PCIe 구성요소(예컨대, PCIe 확장기 케이블)를 위한 더 많은 공간이 PCIe 커넥터(111 및 112) 중 하나(예컨대, 112)에 연결되게 할 수 있다.

[0009] 도 1에 도시된 바와 같이, 회로 기판(102)은 측면(예컨대, 하부 측면)(171A) 및 측면(171A)에 대향하는 측면(예컨대, 상부 측면)(171B)을 포함한다. PCIe 커넥터(111 및 112)의 각각은 회로 기판(102)의 양 측면(171A 및 171B) 상의 도전체(예컨대, 금속 기반 트레이스와 같은 전기 트레이스)를 포함할 수 있다. 예컨대, PCIe 커넥터(111)는 측면(171A) 상에 배치된 도전체(도전체 그룹)(111A) 및 측면(171B) 상에 배치된 도전체(다른 도전체 그룹)(111B)를 포함할 수 있다. 도전체(111A 및 111B)는 접속부(131)를 통해 디바이스(120)에 연결될 수 있다. PCIe 커넥터(112)는 측면(171B) 상에 배치된 도전체(도전체 그룹)(112A) 및 측면(171A) 상에 배치된 도전체(다

른 도전체 그룹(112B)를 포함할 수 있다. 도전체(112A 및 112B)는 접속부(132)를 통해 디바이스(120)에 연결될 수 있다. PCIe 접속부(111 및 112)의 각각이 회로 기판(102)의 에지(예컨대, 에지(161 또는 162))에 배치된 도전체를 포함할 수 있으므로, PCIe 커넥터(111 및 112)의 각각은 에지-커넥터 유형을 포함할 수 있다.

[0010] (측면(171A) 상의) PCIe 커넥터(111)의 도전체(111A) 및 (측면(171B) 상의) PCIe 커넥터(112)의 도전체(112A)는 PCB의 측면(예컨대, 측면 A)에 대한 PCIe 커넥터 핀아웃(pin-out) 사양에 기초하여 배열될 수 있다. 예컨대, 도전체(111A 및 112A)는 PCIe 커넥터 핀아웃 사양에 기초하여 PCB의 솔더 측면(측면 A) 상의 도전체와 연관된 핀 이름을 가질 수 있다.

[0011] (측면(171B) 상의) PCIe 커넥터(111)의 도전체(111B) 및 (측면(171A) 상의) PCIe 커넥터(112)의 도전체(112B)는 PCB의 다른 측면(예컨대, 측면 B)에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 배열될 수 있다. 예컨대, 도전체(111B 및 112B)는 PCIe 커넥터 핀아웃 사양에 기초하여 PCB의 구성요소 측면(측면 B) 상의 도전체와 연관된 핀 이름을 가질 수 있다.

[0012] 도 1에서, 회로 기판(102)의 측면(171A 및 171B)은 각각 PCIe 사양에 따라 PCIe 카드의 PCB의 솔더 측면(측면 A) 및 구성요소 측면(측면 B)에 대응할 수 있다. PCIe 커넥터(111)의 도전체(111A 및 111B)가 PCIe 커넥터 핀아웃 사양의 측면(A 및 B)에 각각 기초한 핀 이름을 갖고, 도전체(111A 및 111B)가 PCB 기판(102)의 솔더 측면 및 구성요소 측면 상에 각각 배치되므로, 도전체(111A 및 111B)는 PCIe 커넥터 핀아웃 사양에 의해 명시된 동일한 배치를 따른다. PCIe 커넥터(112)에서, PCIe 커넥터(112)의 도전체(112A 및 112B)가 PCIe 커넥터 핀아웃 사양의 측면(A 및 B)에 각각 기초한 핀 이름을 갖고, 도전체(112A 및 112B)가 PCB 기판(102)의 구성요소 측면 및 솔더 측면 상에 각각 배치되므로, 도전체(112A 및 112B)는 PCIe 커넥터 핀아웃 사양에 의해 명시된 배치와 반대인 배치를 따른다.

[0013] PCIe 커넥터(112)의 도전체(112A 및 112B)를 (예컨대, PCIe 커넥터 핀아웃 사양에 의해 명시된 배치와 반대인) 측면(171B 및 171A) 상에 각각 배치하는 것은 PCIe 카드(101)가 표준 PCIe 구성요소(예컨대, PCIe 라이저 카드 및 PCIe 확장기 케이블)를 사용하여 마더보드의 다수의 PCIe 슬롯에 연결되게 할 수 있고, PCIe 카드(101)가 마더보드의 다수의 PCIe 슬롯에 연결되는 경우 PCIe 카드(101)의 플리핑(flippping)(예컨대, 180도 플리핑)을 방지할 수 있다.

[0014] PCIe 카드(101)의 디바이스(120)는 상이한 컴퓨터 네트워크 표준에 기초한 기능과 같은 다수의 상이한 기능을 수행하도록 배치(예컨대, 구성)될 수 있다. 도 1에 도시된 바와 같이, 디바이스(120)는 접적 회로(IC) 칩(예컨대, 반도체 칩)(125)을 포함할 수 있고, 디바이스(120)의 구성요소(예컨대, 회로 소자)는 IC 칩(125) 상에 배치(예컨대, IC 칩(125) 내에 또는 IC 칩(125) 상에 형성)될 수 있다. IC 칩(125)은 접속부(131, 132, 151 및 152)에 각각 연결된 도전성 콘택트(121, 122, 123 및 124)를 포함할 수 있다. 도 1은 IC 칩(125)이 20 개의 도전성 콘택트(도전성 콘택트(121 및 122)의 각각으로부터 6 개의 도전성 콘택트 및 도전성 콘택트(123 및 124)의 각각으로부터 4 개의 도전성 콘택트)를 포함하는 예를 도시한다. IC 칩(125)의 도전성 콘택트의 개수는 변할 수 있다.

[0015] 접속부(131, 132, 151 및 152)의 각각은 회로 기판(102)의 한 측면 또는 양 측면(171A 및 171B) 상의 도전체(예컨대, 금속 기반 트레이스와 같은 전기 트레이스)를 포함할 수 있다. 도전성 콘택트(121, 122, 123 및 124)는 솔더 볼, 솔더 범프, 핀 또는 다른 유형의 도전성 콘택트를 포함할 수 있다. 도 1은 접속부(131, 132, 151 및 152)의 20 개의 도전체(예컨대, 20 개의 전기 트레이스)의 예를 도시한다. 접속부(131, 132, 151 및 152)의 도전체의 개수는 변할 수 있다.

[0016] 도 1에 도시된 바와 같이, 도전성 콘택트(121)는 접속부(131)를 통해 PCIe 커넥터(111)에 연결될 수 있다. 도전성 콘택트(122)는 접속부(132)를 통해 PCIe 커넥터(112)에 연결될 수 있다. 도전성 콘택트(123)는 접속부(151)를 통해 커넥터(141)에 연결될 수 있다. 도전성 콘택트(124)는 접속부(152)를 통해 커넥터(142)에 연결될 수 있다.

[0017] 도전성 콘택트(121)는 IC 칩(125)(디바이스(120))과 회로 기판(102)에 연결된 추가 회로 기판(예컨대, 마더보드) 상의 구성요소 사이의 독립적인 접속부(예컨대, 포인트 투 포인트 PCIe 접속부와 같은 전용 접속부)를 통해 신호를 전도(예컨대, 신호 송신, 신호 수신 또는 신호 송신과 수신 양자 모두)하도록 배치될 수 있다. 추가 회로 기판 상의 구성요소는 추가 회로 기판 상의 PCIe 버스에 연결된 디바이스(예컨대, 버스 제어기 디바이스) 또는 칩셋(예컨대, 버스 제어기 칩셋)을 포함할 수 있다. 도전성 콘택트(122)는 IC 칩(125)(디바이스(120))과 추가 회로 기판 상의 구성요소 사이의 다른 독립적인 접속부(예컨대, 다른 포인트 투 포인트 PCIe 접

속부와 같은 다른 전용 접속부)를 통해 신호를 전도(예컨대, 신호 송신, 신호 수신 또는 신호 송신과 수신 양자 모두)하도록 배치될 수 있다.

[0018] 도전성 콘택트(123)는 IC 칩(125)(디바이스(120))과 I/O 커넥터(141)에 연결된 구성요소(예컨대, 디바이스 또는 시스템) 사이의 독립적인 접속부를 통해(예컨대, 네트워크를 통해) 신호를 전도(예컨대, 신호 송신, 신호 수신 또는 신호 송신과 수신 양자 모두)하도록 배치될 수 있다. 도전성 콘택트(124)는 IC 칩(125)(디바이스(120))과 I/O 커넥터(142)에 연결된 구성요소(예컨대, 디바이스 또는 시스템) 사이의 다른 독립적인 접속부를 통해(예컨대, 다른 네트워크를 통해) 신호를 전도(예컨대, 신호 송신, 신호 수신 또는 신호 송신과 수신 양자 모두)하도록 배치될 수 있다. 접속부(141 및 142)를 통해 전도된 신호는 상이한 컴퓨터 네트워크 표준(예컨대, 이더넷, 파이버 채널 및 인피니밴드 표준)에 기초할 수 있다.

[0019] 이상의 설명에서, PCIe 카드(101) 및 구성요소(예컨대, PCIe 구성요소(111 및 112))는 예로써 PCIe 사양에 기초하여 설명된다. 다른 배치에서, PCIe 카드(101)는 다른 표준 또는 사양을 준수할 수 있다. 그러므로, 그러한 다른 배치에서, 다른 표준 또는 사양(상이한 PCIe 사양)을 준수하는 다른 커넥터(예컨대, 다른 에지 커넥터)는 PCIe 커넥터(111 및 112)를 대체할 수 있다. 카드 상의 다른 커넥터 및 (다른 커넥터에 연결하도록 배치된) 마더보드 상의 슬롯은 동일한 표준 또는 사양을 준수할 수 있다.

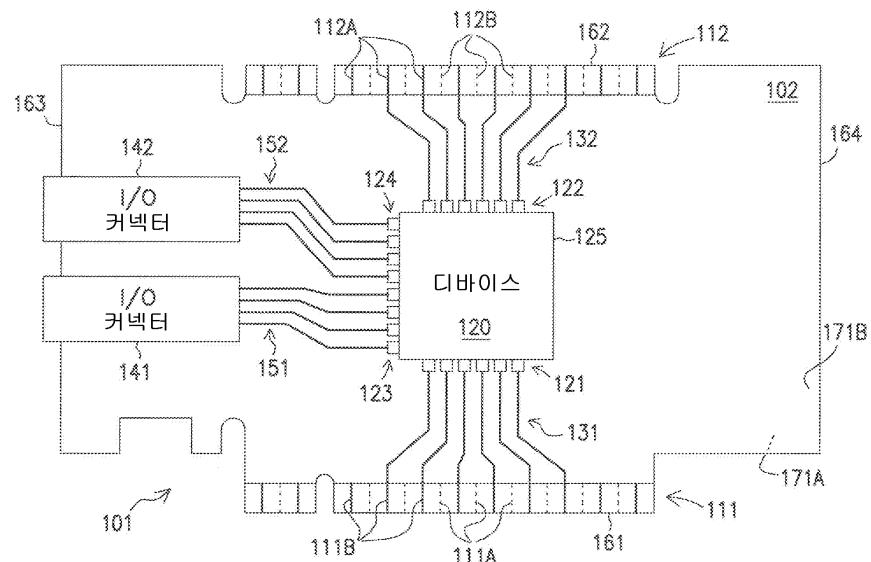

[0020] 도 2는 본 명세서에 설명된 일부 실시예에 따라, 도 1의 도전체(111A, 111B, 112A 및 112B) 중 일부의 배치를 포함하는 도 1의 PCIe 카드(101)의 일부(예컨대, 단면)를 도시한다. 간결함을 위해, 도전체(111A) 중 하나, 도전체(111B) 중 하나, 도전체(112A) 중 하나 및 도전체(112B) 중 하나만이 도 2에 도시된다.

[0021] 도 2에서 알 수 있듯이, PCIe 커넥터(111)의 (접속부(131)에 연결된) 도전체(111A) 중 하나 및 (접속부(131)에 연결된) 도전체(111B) 중 하나는 PCIe 카드(101)의 회로 기판(102)의 대향 측면(171A 및 171B) 상에 배치된다. PCIe 커넥터(112)의 (접속부(131)에 연결된) 도전체(112A) 중 하나 및 (접속부(132)에 연결된) 도전체(112B) 중 하나는 PCIe 카드(101)의 회로 기판(102)의 대향 측면(171A 및 171B) 상에 배치된다.

[0022] 도 1과 관련하여 전술한 바와 같이 그리고 도 2에서 알 수 있듯이, PCIe 커넥터(111)의 도전체(111A) 및 PCIe 커넥터(112)의 도전체(112A)는 PCIe 커넥터 핀아웃에 기초하여 PCB의 솔더 측면(측면 A) 상의 도전체와 연관된 핀 이름을 가질 수 있지만, 도전체(111A 및 112A)는 PCIe 카드(101)의 대향 측면(예컨대, 측면(171A 및 171B)) 상에 배치된다. 유사하게, PCIe 커넥터(111)의 도전체(111B) 및 PCIe 커넥터(112)의 도전체(112B)는 PCIe 커넥터 핀아웃에 기초하여 PCB의 구성요소 측면(측면 B) 상의 도전체와 연관된 핀 이름을 가질 수 있지만, 도전체(111B 및 112B)는 PCIe 카드(101)의 대향 측면(예컨대, 측면(171A 및 171B)) 상에 배치된다.

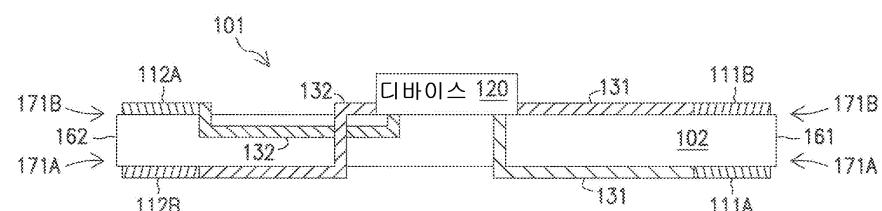

[0023] 도 3, 도 4 및 도 5는 본 명세서에 설명된 일부 실시예에 따라 상이한 시스템(예컨대, 전자 시스템)(300, 400 및 500)에서 도 1의 PCIe 카드(101)의 상이한 배치를 도시한다. 시스템(300, 400 및 500)의 각각은 컴퓨터(예컨대, 서버)를 포함하거나 이에 포함될 수 있다. 시스템(300, 400 및 500)은 유사하거나 동일한 구성요소를 포함할 수 있다. 그러므로, 도 3, 도 4 및 도 5에서, 유사하거나 동일한 구성요소의 설명은 반복되지 않는다.

[0024] 도 3에 도시된 바와 같이, 시스템(300)은 PCIe 슬롯(311)을 가지며 하나의 PCIe 카드 또는 다수의 PCIe 카드를 수용하도록 배치될 수 있는 마더보드(315)를 포함할 수 있다. 마더보드(315)는 구성요소(316) 및 구성요소(316)에 연결된 버스 부분(317 및 318)을 가진 버스(예컨대, PCIe 버스)를 포함할 수 있다. 구성요소(316)의 예는 디바이스(예컨대, 버스 제어기 디바이스), 칩셋(예컨대, 버스 제어기 칩셋) 및 다른 유형의 디바이스 또는 칩셋을 포함한다.

[0025] 도 3은 PCIe 카드(101)가 마더보드와 병렬로 배치(예컨대, 수평으로 배치)되는 예를 도시한다. 예컨대, PCIe 커넥터(111 및 112)는 각각 PCIe 라이저(예컨대, PCIe 라이저 카드)(320) 및 PCIe 확장기 케이블(330)을 통해 PCIe 슬롯(311 및 312)에 연결될 수 있다. PCIe 라이저(320)는 PCIe 슬롯(311)에 연결된(예컨대, 삽입된) 단부(예컨대, 메일 단부(male end))(321) 및 PCIe 카드(101)의 PCIe 커넥터(111)에 연결된 단부(예컨대, 피메일 단부(female end))(322)를 포함할 수 있다. PCIe 확장기 케이블(330)은 PCIe 슬롯(312)에 연결된(예컨대, 삽입된) 단부(예컨대, 메일 단부)(331) 및 PCIe 카드(101)의 PCIe 커넥터(112)에 연결된 단부(예컨대, 피메일 단부)(332)를 포함할 수 있다.

[0026] 도 3의 배치에서, 버스 부분(317), PCIe 커넥터(111)의 도전체(111A 및 111B)(도 1) 및 접속부(131)(도 1)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 독립적인 접속부(예컨대, 포인트 투 포인트 PCIe 접속부와 같은 전용 접속부)의 일부일 수 있다. 버스 부분(318), PCIe 커넥터(112)의 도전체(112A 및 112B)(도 1) 및 접속부(132)(도 1)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 다른

독립적인 접속부(예컨대, 다른 포인트 투 포인트 PCIe 접속부와 같은 다른 전용 접속부)의 일부일 수 있다.

[0027] PCIe 커넥터(111 및 112)는 PCIe 준수 구성요소이며 표준 PCIe 폼 팩터 커넥터와 호환가능하다. PCIe 슬롯(311 및 312), PCIe 라이저(320) 및 PCIe 확장기 케이블(330) 또한 PCIe 준수 구성요소이며 표준 PCIe 폼 팩터 커넥터와 호환가능하다. 그러므로, 본 명세서에 설명된 바와 같이 다수의(예컨대, 듀얼) PCIe 커넥터를 가진 PCIe 카드(101)는 상용가능한 PCIe 구성요소를 사용하여 PCIe 구성요소의 에코시스템에서 사용하기에 적합할 수 있다. 또한, 디바이스(120)가 하나보다 많은 PCIe 커넥터를 지원할 수 있으므로, 단일 PCIe 커넥터를 가진 종래의 PCIe 카드는 디바이스(120)의 기능을 제한할 수 있다. 반대로, 본 명세서에서 설명된 바와 같이 다수의 PCIe 커넥터를 가진 PCIe 카드(101)는 하나보다 많은 PCIe 커넥터를 지원하는 디바이스(예컨대, 디바이스(120))가 그러한 디바이스의 전체 기능을 이용하게 할 수 있다.

[0028] 도 4는 시스템(400) 내의 PCIe 카드(101)의 배치를 도시한다. 도 3 및 도 4에 도시된 바와 같이, PCIe 카드(101)는 마더보드(315)와 병렬로 배치될 수 있다. 그러나, 도 4에서, 마더보드(315)의 위치에 관하여 PCIe 카드(101)의 구성요소의 배치는 도 3의 PCIe 카드(101)의 구성요소의 배치(예컨대, 똑바로("right-side" up))에 비해 거꾸로("up-side" down) 배치되는 것처럼 보일 수 있다. 도 4에 도시된 바와 같이, PCIe 카드(101)의 PCIe 커넥터(111)는 PCIe 라이저(320)를 통해 PCIe 슬롯(312)에 연결될 수 있다. PCIe 카드(101)의 PCIe 커넥터(112)는 PCIe 확장기 케이블(330)를 통해 PCIe 슬롯(312)에 연결될 수 있다.

[0029] 도 4의 배치에서, 버스 부분(318), PCIe 커넥터(111)의 도전체(111A 및 111B)(도 1) 및 접속부(131)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 독립적인 접속부(예컨대, 포인트 투 포인트 접속부와 같은 전용 접속부)의 일부일 수 있다. 버스 부분(317), PCIe 커넥터(112)의 도전체(112A 및 112B)(도 1) 및 접속부(132)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 다른 독립적인 접속부(예컨대, 다른 포인트 투 포인트 접속부와 같은 다른 전용 접속부)의 일부일 수 있다.

[0030] 도 5는 시스템(500) 내의 PCIe 카드(101)의 배치를 도시한다. 도 3 및 도 5에 도시된 바와 같이, 시스템(500)의 PCIe 슬롯(311)과 PCIe 슬롯(312) 사이의 간격은 시스템(300)의 PCIe 슬롯(311)과 PCIe 슬롯(312) 사이의 간격 미만일 수 있다. 그러므로, 도 5에서, PCIe 카드(101)는 마더보드(315)에 직각으로(예컨대, 수직으로) 배치될 수 있다. 이 배치에서, PCIe 카드(101)의 PCIe 커넥터(111)는 PCIe 라이저를 통과하지 않고 PCIe 슬롯(311)에 연결(예컨대, 직접 연결)될 수 있다. PCIe 카드(101)의 PCIe 커넥터(112)는 PCIe 확장기 케이블(330)을 통해 PCIe 슬롯(312)에 연결될 수 있다.

[0031] 도 5의 배치에서, 버스 부분(317), PCIe 커넥터(111)의 도전체(111A 및 111B)(도 1) 및 접속부(131)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 독립적인 접속부(예컨대, 포인트 투 포인트 접속부와 같은 전용 접속부)의 일부일 수 있다. 버스 부분(318), PCIe 커넥터(112)의 도전체(112A 및 112B)(도 1) 및 접속부(132)는 마더보드(315) 상의 구성요소(316)와 디바이스(120)(도 1) 사이의 다른 독립적인 접속부(예컨대, 다른 포인트 투 포인트 접속부와 같은 다른 전용 접속부)의 일부일 수 있다.

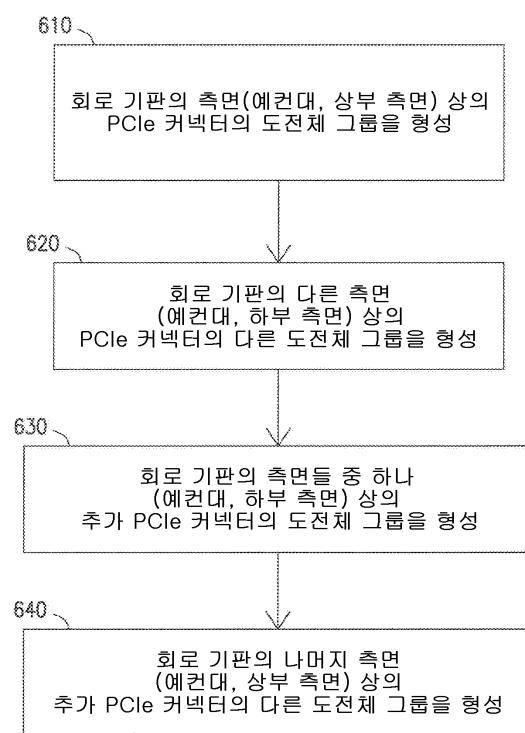

[0032] 도 6은 본 명세서에 설명된 일부 실시예에 따라, PCIe 카드를 제조하는 방법을 도시하는 흐름도이다. 방법(600)에 의해 제조된 PCIe 카드는 도 1 내지 도 5와 관련하여 전술된 PCIe 카드(101)를 포함할 수 있다.

[0033] 도 6에 도시된 바와 같이, 방법(600)의 동작(610)은 회로 기판의 측면(예컨대, 상부 측면) 상의 PCIe 커넥터의 도전체 그룹을 형성하는 것을 포함할 수 있다. 동작(620)은 회로 기판의 다른 측면(예컨대, 하부 측면) 상의 PCIe 커넥터의 다른 도전체 그룹을 형성하는 것을 포함할 수 있다. 동작(630)은 회로 기판의 측면들 중 하나(예컨대, 하부 측면) 상의 추가 PCIe 커넥터의 도전체 그룹을 형성하는 것을 포함할 수 있다. 동작(640)은 회로 기판의 나머지 측면(예컨대, 상부 측면) 상의 추가 PCIe 커넥터의 다른 도전체 그룹을 형성하는 것을 포함할 수 있다.

[0034] 동작(610, 620, 630 및 640)의 일부 또는 전부는 동시에(예컨대, 일제히) 수행될 수 있다. 예컨대, 동작(610 및 640)은 동시에 수행되어, 각각의 PCIe 커넥터의 하나의 도전체 그룹(예컨대, 도 1의 도전체(111B 및 112A))이 동시에 형성될 수 있다. 다른 예에서, 동작(620 및 630)은 동시에 수행되어, 각각의 PCIe 커넥터의 다른 도전체 그룹(예컨대, 도 1의 도전체(111A 및 112B))이 동시에 형성될 수 있다. 또 다른 예에서, 동작(610, 620, 630 및 640)은 동시에 수행되어, PCIe 커넥터의 모든 도전체가 동시에 형성될 수 있다.

[0035] 방법(600)에 의해 제조된 PCIe 카드가 도 1 내지 도 5와 관련하여 전술된 PCIe 카드(101)의 구성요소와 유사하거나 동일한 구성요소를 포함할 수 있도록, 방법(600)은 동작(610, 620, 630 및 640) 외의 다른 동작, 예컨대, 회로 기판 상에 디바이스(예컨대, 도 1의 디바이스(120))를 부착하는 것, I/O 커넥터(예컨대, 도 1의 I/O 커넥

터(141 및 142))를 형성하는 것, 접속부(예컨대, 접속부(131, 132, 133 및 134))를 형성하는 것 및 다른 동작을 포함할 수 있다.

[0036] 전술된 장치(예컨대, PCIe 카드(101) 및 시스템(300, 400 및 500)) 및 방법(예컨대, 방법(600))의 예시는 상이한 실시예의 구조에 대한 일반적인 이해를 제공하도록 의도되며, 본 명세서에 설명된 구조를 이용할 수 있는 장치의 모든 요소 및 특징부의 완전한 설명을 제공하도록 의도되지는 않는다.

[0037] 전술된 장치 및 방법은 고속 컴퓨터, 통신 및 신호 처리 회로, 단일 또는 다중 프로세서 모듈, 단일 또는 다중 내장형 프로세서, 멀티코어 프로세서, 메시지 정보 스위치, 및 다중, 다칩 모듈을 포함하는 애플리케이션 특정 모듈을 포함하거나 포함될 수 있다. 그러한 장치는 텔레비전, 셀룰러 전화, 개인용 컴퓨터(예컨대, 랩톱 컴퓨터, 데스크톱 컴퓨터, 휴대형 컴퓨터 등), 태블릿(예컨대, 태블릿 컴퓨터), 워크스테이션, 라디오, 비디오 플레이어, 오디오 플레이어(예컨대, MP3 플레이어), 차량, 의료 기기(예컨대, 심장 모니터, 혈압 모니터 등), 셋톱 박스 등과 같은 다양한 다른 장치(예컨대, 전자 시스템) 내의 서브 구성요소로서 또한 포함될 수 있다.

#### 추가 주석 및 예

[0039] 예 1은 회로 기판과, 회로 기판 상에 배치된 디바이스와, 회로 기판 상에 배치되고 디바이스에 연결된 제 1 PCIe(Peripheral Component Interconnect Express) 커넥터 -제 1 PCIe 커넥터는 추가 회로 기판의 제 1 커넥터에 연결하도록 배치됨- 와, 회로 기판 상에 배치되고 디바이스에 연결된 제 2 PCIe 커넥터 -제 2 PCIe 커넥터는 추가 회로 기판의 제 2 커넥터에 연결하도록 배치됨- 를 포함하는 청구 대상(예컨대, 디바이스, 회로 장치 또는 전자 시스템 장치, 또는 머신)을 포함한다.

[0040] 예 2에서, 예 1의 청구 대상은, 추가 회로 기판의 제 1 커넥터는 제 1 PCIe 슬롯을 포함하고, 추가 회로 기판의 제 2 추가 커넥터는 제 2 PCIe 슬롯을 포함하는 것을 선택적으로 포함할 수 있다.

[0041] 예 3에서, 예 1의 청구 대상은, 회로 기판은 제 1 에지 및 제 2 에지를 포함하고, 제 1 커넥터의 도전체는 상기 제 1 에지에 배치되고, 상기 제 2 커넥터의 도전체는 제 2 에지에 배치되는 것을 선택적으로 포함할 수 있다.

[0042] 예 4에서, 예 3의 청구 대상은, 제 1 에지는 상기 제 2 에지와 마주보는 것을 선택적으로 포함할 수 있다.

[0043] 예 5에서, 예 1의 청구 대상은, 제 1 PCIe 커넥터 및 제 2 PCIe 커넥터의 각각은 도전체를 포함하고, 제 1 PCIe 커넥터의 도전체는 회로 기판의 제 1 측면 상의 제 1 도전체 그룹 및 회로 기판의 제 2 측면 상의 제 2 도전체 그룹을 포함하며, 제 2 PCIe 커넥터의 도전체는 회로 기판의 제 2 측면 상의 제 1 도전체 그룹 및 회로 기판의 제 1 측면 상의 제 2 도전체 그룹을 포함하며, 제 1 PCIe 커넥터 및 제 2 PCIe 커넥터의 각각의 제 1 도전체 그룹은 인쇄 회로 기판(PCB)의 제 1 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 배치되고, 제 1 PCIe 커넥터 및 제 2 PCIe 커넥터의 각각의 제 2 도전체 그룹은 PCB의 제 2 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 배치되는 것을 선택적으로 포함할 수 있다.

[0044] 예 6에서, 예 1의 청구 대상은, 회로 기판 상에 배치되고 디바이스에 연결된 제 1 추가 커넥터 -제 1 추가 커넥터는 제 1 컴퓨터 네트워크 표준에 기초하여 신호를 전도하도록 배치됨- 와, 회로 기판 상에 배치되고 디바이스에 연결된 제 2 추가 커넥터 -제 2 추가 커넥터는 제 2 컴퓨터 네트워크 표준에 기초하여 신호를 전도하도록 배치됨- 를 선택적으로 포함할 수 있다.

[0045] 예 7에서, 예 6의 청구 대상은, 회로 기판은 제 1 에지, 제 2 에지 및 제 3 에지를 포함하고, 제 1 PCIe 커넥터는 제 1 에지에 배치된 도전체를 포함하고, 제 2 PCIe 커넥터는 제 2 에지에 배치된 도전체를 포함하며, 제 1 추가 커넥터 및 제 2 추가 커넥터는 제 3 에지에 배치되는 것을 선택적으로 포함할 수 있다.

[0046] 예 8에서, 예 1의 청구 대상은, 회로 기판과, 디바이스와, 제 1 PCIe 커넥터와, 제 2 PCIe 커넥터는 확장 카드의 일부인 것을 선택적으로 포함할 수 있다.

[0047] 예 9에서, 예 8의 청구 대상은, 확장 카드는 호스트 어댑터 디바이스, 네트워크 인터페이스 제어기(NIC) 디바이스 또는 수령 네트워크 어댑터 디바이스 중 하나를 포함하는 것을 선택적으로 포함할 수 있다.

[0048] 예 10에서, 예 8의 청구 대상은, 확장 카드는 PCIe 폼 팩터를 따르는 것을 선택적으로 포함할 수 있다.

[0049] 예 11은 집적 회로(IC) 칩과, PCIe 카드의 제 1 PCIe 커넥터에 연결하도록 배치된 IC 칩의 제 1 도전성 콘택트와, PCIe 카드의 제 2 PCIe 커넥터에 연결하도록 배치된 IC 칩의 제 2 도전성 콘택트를 포함하는 청구 대상(예컨대, 디바이스, 회로 장치 또는 전자 시스템 장치, 또는 머신)을 포함한다.

- [0050] 예 12에서, 예 11의 청구 대상은, 제 1 도전성 콘택트는, 제 1 PCIe 커넥터를 통해 IC 칩에 연결된 회로 기판 상의 구성요소들 중 하나와 IC 칩 사이의 제 1 포인트 투 포인트 PCIe 접속부를 통해 신호를 전도하도록 배치되고, 제 2 도전성 콘택트는, 제 2 PCIe 커넥터를 통해 IC 칩에 연결된 회로 기판 상의 구성요소들 중 하나와 IC 칩 사이의 제 2 포인트 투 포인트 PCIe 접속부를 통해 신호를 전도하도록 배치되는 것을 선택적으로 포함할 수 있다.

- [0051] 예 13에서, 예 11의 청구 대상은, PCIe 카드의 제 1 입출력(I/O) 커넥터에 연결하도록 배치된 제 3 도전성 콘택트와, PCIe 카드의 제 2 I/O 커넥터에 연결하도록 배치된 제 4 도전성 콘택트를 선택적으로 포함할 수 있다.

- [0052] 예 14에서, 예 13의 청구 대상은, 제 3 도전성 콘택트는 PCIe 카드의 제 1 I/O 커넥터를 통해 제 1 컴퓨터 네트워크로부터 신호를 전도하도록 배치되고, 제 4 도전성 콘택트는 PCIe 카드의 제 1 I/O 커넥터를 통해 제 2 컴퓨터 네트워크로부터 신호를 전도하도록 배치되는 것을 선택적으로 포함할 수 있다.

- [0053] 예 15에서, 예 13의 청구 대상은, 제 1 도전성 콘택트, 제 2 도전성 콘택트, 제 3 도전성 콘택트, 및 제 4 도전성 콘택트는 슬더 볼과 도전성 핀 중 하나를 포함하는 것을 선택적으로 포함할 수 있다.

- [0054] 예 16은 제 1 PCIe 슬롯 및 제 2 PCIe 슬롯을 포함하는 회로 기판과, 디바이스, 디바이스 및 제 1 PCIe 슬롯에 연결된 제 1 PCIe 커넥터, 디바이스 및 제 2 PCIe 슬롯에 연결된 제 2 PCIe 커넥터, 디바이스에 연결된 제 1 입출력(I/O) 커넥터, 및 디바이스에 연결된 제 2 I/O 커넥터를 포함하는 PCIe 카드를 포함하는 청구 대상(예컨대, 디바이스, 회로 장치 또는 전자 시스템 장치, 또는 머신)을 포함한다.

- [0055] 예 17에서, 예 16의 청구 대상은, 제 1 PCIe 커넥터는 PCIe 라이저(riser)를 통해 제 1 PCIe 슬롯에 연결되고, 제 2 PCIe 커넥터는 PCIe 확장기 케이블을 통해 제 2 PCIe 슬롯에 연결되는 것을 선택적으로 포함할 수 있다.

- [0056] 예 18에서, 예 16의 청구 대상은, PCIe 카드는 회로 기판과 병렬로 배치되는 것을 선택적으로 포함할 수 있다.

- [0057] 예 19에서, 예 16의 청구 대상은, PCIe 카드는 회로 기판에 수직으로 배치되는 것을 선택적으로 포함할 수 있다.

- [0058] 예 20은 회로 기판의 제 1 측면 상에 제 1 PCIe 커넥터의 제 1 도전체 그룹을 형성하는 단계와, 회로 기판의 제 2 측면 상에 제 1 PCIe 커넥터의 제 2 도전체 그룹을 형성하는 단계와, 회로 기판의 제 2 측면 상에 제 2 PCIe 커넥터의 제 1 도전체 그룹을 형성하는 단계와, 회로 기판의 제 1 측면 상에 제 2 PCIe 커넥터의 제 2 도전체 그룹을 형성하는 단계를 포함하는 PCIe 카드 제조 방법을 포함하는 청구 대상을 포함한다.

- [0059] 예 21에서, 예 20의 청구 대상은, 제 1 PCIe 커넥터 및 제 2 PCIe 커넥터의 각각의 제 1 도전체 그룹은 인쇄 회로 기판(PCB)의 제 1 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 형성되고, 제 1 PCIe 커넥터 및 제 2 PCIe 커넥터의 각각의 제 2 도전체 그룹은 PCB의 제 2 측면에 대한 PCIe 커넥터 핀아웃 사양에 기초하여 형성되는 것을 선택적으로 포함할 수 있다.

- [0060] 예 22에서, 예 20의 청구 대상은, 제 1 PCIe 커넥터의 제 1 도전체 그룹과 제 2 도전체 그룹은 회로 기판의 제 1 에지에 형성되고, 제 2 PCIe 커넥터의 제 1 도전체 그룹과 제 2 도전체 그룹은 회로 기판의 제 2 에지에 형성되며, 제 2 에지는 상기 제 1 에지와 마주보는 것을 선택적으로 포함할 수 있다.

- [0061] 예 1 내지 예 22의 청구 대상을 임의의 조합으로 조합될 수 있다.

- [0062] 이상의 설명 및 도면은 당업자로 하여금 본 발명의 실시예를 실시하게 하는 일부 실시예를 예시한다. 다른 실시예는 구조, 로직, 전기적, 프로세스 및 다른 변경을 통합할 수 있다. 예는 단지 가능한 변경을 유형화한 것일 뿐이다. 일부 실시예의 부분 및 특징부는 다른 실시예의 부분 및 특징부에 포함되거나 이를 대신할 수 있다. 다수의 다른 실시예는 이상의 설명을 판독하고 이해할 때 당업자에게 자명할 것이다. 그러므로, 다양한 실시예의 범위는 첨부된 청구범위가 권한을 부여받은 균등물의 전체 범위와 함께, 그 첨부된 청구범위에 의해 결정된다.

- [0063] 요약은 요약이 독자로 하여금 기술적 개시내용의 특성과 요점을 확인하게 할 것을 요구하는 37 C.F.R. 섹션 1.72(b)를 준수하도록 제공된다. 요약이 청구범위의 범주 또는 의미를 제한하거나 해석하는 데 사용되지 않을 것임을 이해해야 한다. 후속하는 청구범위는 상세한 설명에 통합되며, 각각의 청구항은 개별 실시예로서 독립적이다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

400

## 도면5

## 도면6