(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-142351

(P2015-142351A)

(43) 公開日 平成27年8月3日(2015.8.3)

(51) Int.Cl.

HO4N 5/378 (2011.01)

F 1

HO4N

5/335

780

テーマコード(参考)

5C024

審査請求 未請求 請求項の数 10 O L (全 19 頁)

(21) 出願番号

特願2014-16023 (P2014-16023)

(22) 出願日

平成26年1月30日 (2014.1.30)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 岩根 正晃

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72) 発明者 大下内 和樹

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム

(57) 【要約】 (修正有)

【課題】撮像装置の信号出力の高速化を実現する。

【解決手段】画素セル3のフォトダイオードD1が蓄積した電荷に基づく信号を出力する信号をバッファ部APが容量CP2に保持させるためスイッチ部SP2が導通状態としている期間が、フォトダイオードD1が蓄積した電荷とフォトダイオードD2が蓄積した電荷とを足した電荷に基づく信号をバッファ部APが容量CP2に保持させるためスイッチ部SP2が導通状態としている期間よりも短い。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

第1光電変換部と、第2光電変換部と、前記第1光電変換部と前記第2光電変換部に対して共通に設けられた出力部とを有する画素セルと、

前記出力部が出力する信号をバッファするバッファ部と、前記バッファ部が出力する信号を保持する容量素子と、前記バッファ部と前記容量素子との間の導通状態と非導通状態とを切り替えるスイッチ部とを有する読み出し回路とを有する撮像装置であって、

前記第1光電変換部が蓄積した電荷に基づく第1光信号を前記出力部が出力し、前記第1光信号をバッファした第1バッファ信号を前記バッファ部が出力し、

前記第1光電変換部が蓄積した電荷と前記第2光電変換部が蓄積した電荷とを足した電荷に基づく第2光信号を前記出力部が出力し、前記第2光信号をバッファした第2バッファ信号を前記バッファ部が出力し、

前記第1バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間が、

前記第2バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間よりも短いことを特徴とする撮像装置。

## 【請求項 2】

前記出力部が出力する信号を增幅した增幅信号を前記バッファ部に出力する增幅部をさらに有し、

前記第1バッファ信号は、前記增幅部が前記第1光信号を增幅した第1增幅信号を前記バッファ部がバッファした信号であり、

前記第2バッファ信号は、前記增幅部が前記第2光信号を增幅した第2增幅信号を前記バッファ部がバッファした信号であることを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

前記読み出し回路は、前記增幅信号を保持する第2容量素子と、前記增幅部と前記第2容量素子との間の電気的経路の導通状態と非導通状態とを切り替える第2スイッチ部とをさらに有し、

前記增幅部が前記第1增幅信号を出力している場合に、前記增幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間が、

前記增幅部が前記第2增幅信号を出力している場合に、前記增幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間よりも短いことを特徴とする請求項2に記載の撮像装置。

## 【請求項 4】

前記読み出し回路は、さらに前記增幅信号を保持する第3容量素子と、前記增幅部と前記第3容量素子との間の電気的経路の導通状態と非導通状態とを切り替える第3スイッチ部とを有し、

前記出力部は、さらにノイズ信号を出力し、

前記增幅部は、前記ノイズ信号を增幅した增幅ノイズ信号を出力し、

前記增幅ノイズ信号を前記第3容量素子に保持させるために、前記增幅部と前記第3容量素子との間の電気的経路を前記第3スイッチ部が導通状態としている期間が、

前記第1增幅信号を前記第2容量素子に保持させるために、前記增幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間よりも短いことを特徴とする請求項3に記載の撮像装置。

## 【請求項 5】

前記読み出し回路は、前記增幅信号を保持するとともに前記バッファ部に前記增幅信号を出力する第2容量素子と、前記增幅部と前記第2容量素子との間の電気的経路の導通状態と非導通状態とを切り替える第2スイッチ部とをさらに有し、

前記第2容量素子は、前記第1增幅信号を保持した後、前記第1增幅信号をリセットせずに前記第2增幅信号を保持する容量素子であって、

10

20

30

40

50

前記第1増幅信号を前記第2容量素子に保持させるために、前記増幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間の長さが、

前記第2増幅信号を前記第2容量素子に保持させるために、前記増幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間の長さ以下であることを特徴とする請求項2に記載の撮像装置。

【請求項6】

前記読み出し回路は、さらに前記増幅信号を保持する第3容量素子と、前記増幅部と前記第3容量素子との間の電気的経路の導通状態と非導通状態とを切り替える第3スイッチ部とを有し、

前記出力部は、さらにノイズ信号を出力し、

10

前記増幅部は、前記ノイズ信号を増幅した増幅ノイズ信号を出力し、

前記増幅ノイズ信号を前記第3容量素子に保持させるために、前記増幅部と前記第3容量素子との間の電気的経路を前記第3スイッチ部が導通状態としている期間が、

前記第1増幅信号を前記第2容量素子に保持させるために、前記増幅部と前記第2容量素子との間の電気的経路を前記第2スイッチ部が導通状態としている期間よりも短いことを特徴とする請求項5に記載の撮像装置。

【請求項7】

前記第1光電変換部と前記第2光電変換部とに光を導く共通のマイクロレンズをさらに有することを特徴とする請求項1～6のいずれかに記載の撮像装置。

【請求項8】

前記画素セルが前記第1光電変換部と前記第2光電変換部とを含むL個の光電変換部を含み、

20

前記第1光信号は、前記L個の光電変換部のうちの、前記L個よりも少ないM個の光電変換部の各々が蓄積した電荷同士を足した電荷に基づく信号であり、

前記第2光信号は、前記L個の光電変換部の各々が蓄積した電荷同士を足した電荷に基づく信号であり、

前記第1バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間の長さが、

前記第2バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間の長さのM/L以下であることを特徴とする請求項1～7のいずれかに記載の撮像装置。

30

【請求項9】

請求項1～8のいずれかに記載の撮像装置と、前記撮像装置が出力する信号を処理する出力信号処理部とを有することを特徴とする撮像システム。

【請求項10】

請求項7に記載の撮像装置と、

前記撮像装置に光を集光する光学系と、

前記撮像装置から信号が入力される出力信号処理部とを有する撮像システムであって、

前記出力信号処理部は、前記第1バッファ信号に基づく信号と前記第2バッファ信号に基づく信号との差の信号と、前記第1バッファ信号に基づく信号とによって焦点検出を行い、

40

前記出力信号処理部は、前記第2バッファ信号に基づく信号によって画像を生成することを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置、撮像システムに関する。

【背景技術】

【0002】

撮像装置を高速化する構成の一例として、特許文献1のように、画素が出力する信号を

50

保持する第1の蓄積部と、第1の蓄積部が保持した信号を伝達するバッファ部と、バッファ部から信号が伝達される第2の蓄積部とを有する構成が知られている。特許文献1の撮像装置では第1の画素の信号をまず第1の蓄積部が保持する。そして、バッファ部は、第2の蓄積部に、第1の蓄積部が保持した第1の画素の信号を伝達する。そして、第2の蓄積部から第1の画素の信号を読み出す期間に、第2の画素の信号を第1の蓄積部が保持する。これにより、第2の蓄積部から第1の画素の信号を読み出す期間と、第2の画素から第1の蓄積部に信号を出力させる期間とを重ねることができる。これにより、第2の蓄積部を有しない構成の撮像装置に比して撮像装置を高速化することができる。

#### 【0003】

また、特許文献2には、光電変換部が蓄積した電荷に基づく信号を垂直信号線に出力する増幅素子が、複数の光電変換部で共有された撮像装置が記載されている。そして、第1の光電変換部が生成した電荷に基づく第1の信号と、第1の光電変換部が生成した電荷と別の光電変換部が生成した電荷とを加えることで得られる電荷に基づく第2の信号とを増幅素子が出力する。

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開2009-089367号公報

【特許文献2】特開2004-134867号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、特許文献1および特許文献2は、動作のさらなる高速化についての検討がなされていない。

#### 【課題を解決するための手段】

#### 【0006】

本発明は、上記の課題を鑑みて為されたものであり、一の態様は、第1光電変換部と、第2光電変換部と、前記第1光電変換部と前記第2光電変換部に対して共通に設けられた出力部とを有する画素セルと、前記出力部が出力する信号をバッファするバッファ部と、前記バッファ部が出力する信号を保持する容量素子と、前記バッファ部と前記容量素子との間の導通状態と非導通状態とを切り替えるスイッチ部とを有する読み出し回路とを有する撮像装置であって、前記第1光電変換部が蓄積した電荷に基づく第1光信号を前記出力部が出力し、前記第1光信号をバッファした第1バッファ信号を前記バッファ部が出力し、前記第1光電変換部が蓄積した電荷と前記第2光電変換部が蓄積した電荷とを足した電荷に基づく第2光信号を前記出力部が出力し、前記第2光信号をバッファした第2バッファ信号を前記バッファ部が出力し、前記第1バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間が、前記第2バッファ信号を前記容量素子に保持させるために、前記バッファ部と前記容量素子との間の電気的経路を前記スイッチ部が導通状態としている期間よりも短いことを特徴とする撮像装置である。

#### 【発明の効果】

#### 【0007】

本発明により、撮像装置の信号出力の高速化を実現することができる。

#### 【図面の簡単な説明】

#### 【0008】

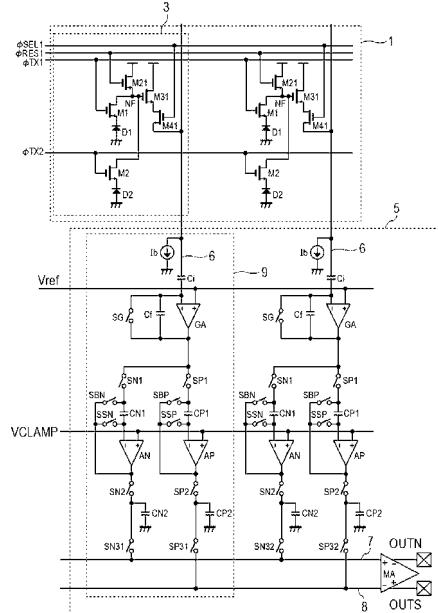

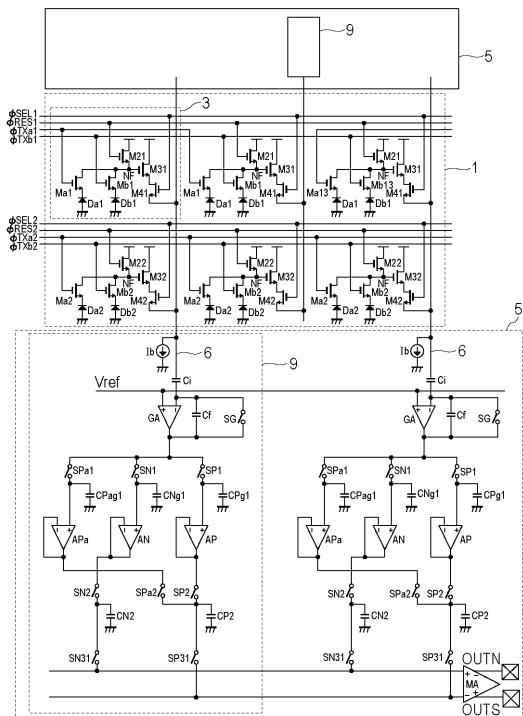

【図1】撮像装置の構成の一例を示した図

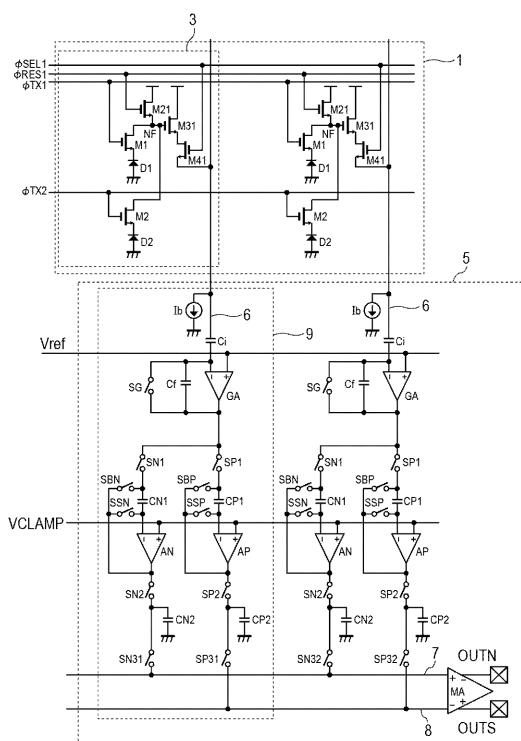

【図2】撮像装置の動作の一例を示した図

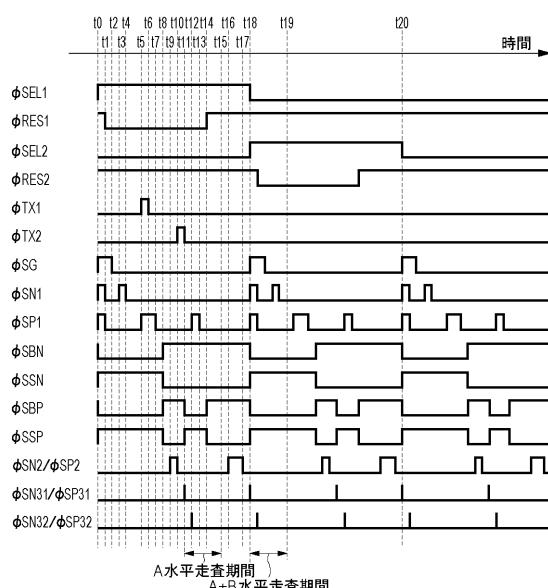

【図3】撮像装置の構成の一例を示した図

【図4】撮像装置の動作の一例を示した図

【図5】撮像装置の動作の一例を示した図

10

20

30

40

50

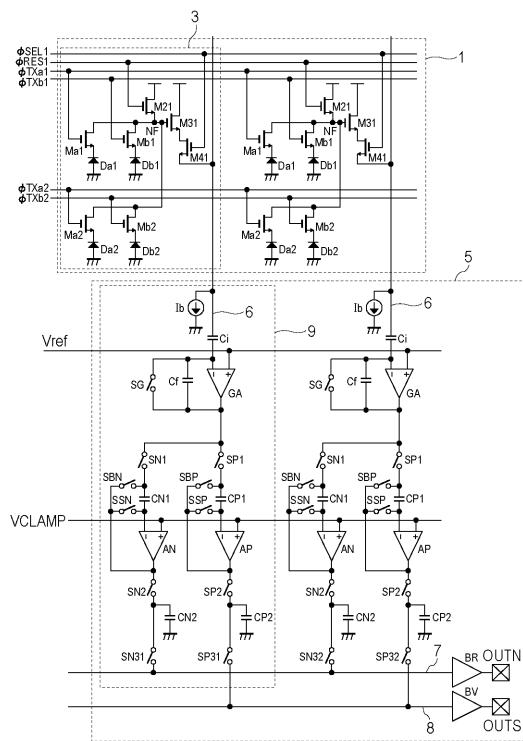

【図6】撮像装置の構成の一例を示した図

【図7】撮像装置の動作の一例を示した図

【図8】撮像システムの構成の一例を示した図

【発明を実施するための形態】

【0009】

以下、図面を参照しながら各実施例の撮像装置を説明する。

【0010】

(実施例1)

図1は、本実施例の撮像装置の構成を示した図である。

【0011】

10

撮像装置は、画素セル3が含まれる画素アレイ1と、バッファ部であるバッファAPが含まれる周辺回路部5とを有する。画素アレイ1は、複数の画素セル3を有する。画素セル3の各々は、フォトダイオードD1、フォトダイオードD2、トランジスタM1、トランジスタM2、トランジスタM21、トランジスタM31、トランジスタM41を有する。フォトダイオードD1は、画素セル3が有する第1光電変換部である。また、フォトダイオードD2は、画素セル3が有する第2光電変換部である。また、ノードNFは、トランジスタM31の入力ノードと、トランジスタM21の一方の主ノードと、トランジスタM1の一方の主ノードと、トランジスタM2の一方の主ノードとに対して電気的に接続されている。1つの画素セル3は、フォトダイオードD1を有する画素と、フォトダイオードD2を有する画素の2つの画素を有する。トランジスタM31は、フォトダイオードD1とフォトダイオードD2とが蓄積した各々の電荷に基づく信号、あるいはフォトダイオードD1とフォトダイオードD2の各々が蓄積した電荷を足した電荷に基づく信号を出力する出力部である。

20

【0012】

20

尚、撮像装置は、数千行および数千列に渡って配された2次元アレイの画素セル3を有している。図1では、2次元アレイの画素セル3の一部として、1行2列の画素セル3を示したものである。尚、特に断りのない場合は、X列目と表記する場合には、図面の左端から画素セル3を数えるものとする。また、Y行目と表記する場合には、図面の上端から画素セル3を数えるものとする。

【0013】

30

さらに撮像装置は、画素アレイ1の外部に周辺回路部5を有している。周辺回路部5は、読み出し回路9を有する。画素セル3のトランジスタM41は、垂直信号線6を介して、容量素子Ciに電気的に接続されている。また、電流源Ibは、垂直信号線6とトランジスタM41を介して、トランジスタM31に電流を供給する。よって、電流源IbとトランジスタM31とトランジスタM31に電圧を供給する電圧源とでソースフォロワ回路が構成される。

【0014】

40

読み出し回路9は、增幅アンプGA、バッファ回路AN、バッファ回路AP、容量素子Ci、容量素子Cf、容量素子CN1、容量素子CP1、容量素子CN2、容量素子CP2を有する。さらに、読み出し回路9は、スイッチSG、スイッチSN1、スイッチSP1、スイッチSBN、スイッチSBP、スイッチSSN、スイッチSSP、スイッチSN2、スイッチSP2、スイッチSN31、スイッチSP31を有する。增幅アンプGAは、画素セル3の出力部が出力する信号を增幅した增幅信号を出力する增幅部である。また、バッファ回路APは、增幅部が出力する增幅信号をバッファするバッファ部である。また、バッファ回路ANは、增幅部が出力する增幅信号をバッファする第2バッファ部である。また、スイッチSP2は、バッファ部であるバッファ回路APと容量素子CP2との間の電気的経路の導通状態と非導通状態とを切り替えるスイッチ部である。バッファ部は、増幅部とバッファ部との間の電気的経路のインピーダンスと、バッファ部とバッファ部の後段のスイッチ部との間の電気的経路のインピーダンスとを変換する回路である。また、バッファ部の増幅率は1としている。また、スイッチSP1は、増幅部である増幅アン

50

PGA と容量素子 CP1 との間の電気的経路の導通状態と非導通状態とを切り替える第2スイッチ部である。また、スイッチ SN1 は、増幅部である増幅アンプ GA と容量素子 CN1 との間の電気的経路の導通状態と非導通状態とを切り替える第3スイッチ部である。また、スイッチ SN2 は、第2バッファ部であるバッファ回路 AN と、容量素子 CN2 との間の電気的経路の導通状態と非導通状態とを切り替える第4スイッチ部である。容量素子 CP1 は、スイッチ SP1 が導通状態にある時に、増幅アンプ GA から増幅信号が出力される第2容量素子である。容量素子 CN1 は、スイッチ SN1 が導通状態にある時に、増幅アンプ GA から増幅信号が出力される第3容量素子である。容量素子 CN2 は、スイッチ SN2 が導通状態にある時に、バッファ回路 AN からバッファ信号が出力される第4容量素子である。

10

## 【0015】

読み出し回路9の容量素子 CP2、容量素子 CN2 のそれぞれは、出力アンプ MA に、出力線7、出力線8を介して、容量素子 CP2、容量素子 CN2 の各々が保持した信号を出力する。

## 【0016】

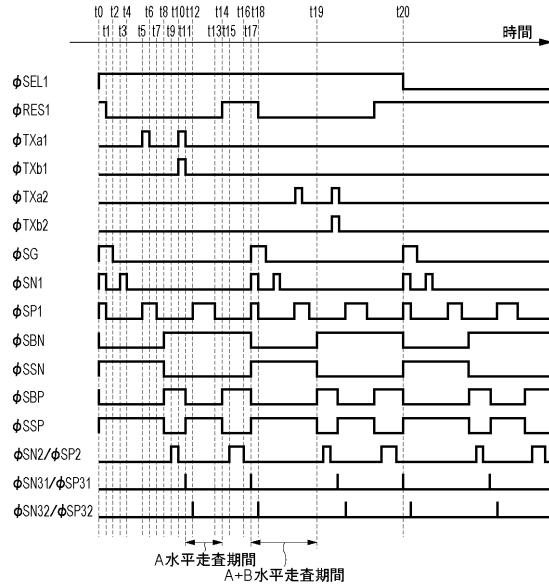

図2は、図1に示した撮像装置の動作を示したタイミング図である。

## 【0017】

図2に示した信号 SEL1、RES1、TX1、TX2 のそれぞれは、図1に示した同じ符号の信号と対応している。信号 SEL2、RES2 は、信号 SEL1 が入力される画素セル3に隣接する行に位置する画素セル3を制御する信号である。

20

## 【0018】

信号 SEL1、RES1、SEL2、RES2、TX1、TX2 のそれぞれは、不図示の垂直走査回路が出力する信号である。また、図2では、図1の読み出し回路9が有する各スイッチを制御する信号を、図1で付したスイッチの符号の先頭に を付して表している。信号 SG は、図1では不図示のタイミングジェネレータが、スイッチ SG を制御する信号である。信号 SG が High レベル（以下、H レベル）の場合には導通状態、Low レベル（以下、L レベル）の場合には、非導通状態である。他の信号 SN1、信号 SP1、信号 SBP、信号 SSP、信号 SN2、信号 SP2、信号 SN31、信号 SP31、信号 SN32、信号 SP32 も、H レベルの場合には、スイッチが導通状態であり、L レベルの場合には非導通状態である。尚、信号 SN2 と信号 SP2 は互いに同相の信号である。また、信号 SN31 と信号 SP31 は互いに同相の信号である。また、信号 SN32 と信号 SP32 は互いに同相の信号である。

30

## 【0019】

時刻 t1 に、垂直走査回路は RES1 を L レベルとする。これにより、トランジスタ M21 がオフとなり、ノード NF のリセットが解除される。この、ノード NF のリセットが解除されることによって、トランジスタ M31 がトランジスタ M41 を介して垂直信号線6に出力する信号をノイズ信号と表記する。また、タイミングジェネレータは、信号 SN1 と信号 SP1 とをそれぞれ L レベルとする。これにより、増幅アンプ GA と容量素子 CN1 との間の電気的経路と、増幅アンプ GA と容量素子 CP1 との間の電気的経路がそれぞれ非導通状態となる。尚、時刻 t1 において、垂直走査回路は、信号 SEL1、信号 RES2 を H レベルとしている。また、時刻 t1 において、垂直走査回路は、信号 SEL2、信号 TX1、信号 TX2 をそれぞれ L レベルとしている。また、時刻 t1 において、タイミングジェネレータは、信号 SG、信号 SSSN、信号 SSP をそれぞれ H レベルとしている。また、時刻 t1 において、タイミングジェネレータは、信号 SBN、信号 SBP、信号 SN2、信号 SP2、信号 SN31、信号 SP31、信号 SN32、信号 SP32 をそれぞれ L レベルとしている。

40

## 【0020】

時刻 t2 に、タイミングジェネレータが信号 SG を L レベルとする。これにより、スイッチ SG が非導通状態となる。増幅アンプ GA は、入力される信号に対して、容量素子

50

$C_f$  の容量値を  $C_f$  、容量素子  $C_i$  の容量値を  $C_i$  とすると、 $C_i / C_f$  の増幅率を掛けた信号を出力する。すなわち、増幅アンプ  $G_A$  は画素セル 3 から垂直信号線 6 に出力されているノイズ信号を増幅した信号（以下、増幅ノイズ信号と表記する。）を出力する。

【0021】

時刻  $t_3$  に、タイミングジェネレータは、信号  $S_N 1$  を H レベルとする。これにより、スイッチ  $S_N 1$  が導通状態となる。同時ににおいて、増幅アンプ  $G_A$  は、増幅ノイズ信号を出力している。スイッチ  $S_N 1$  が導通状態となる事によって、増幅アンプ  $G_A$  が容量素子  $C_N 1$  に増幅ノイズ信号を出力する期間が開始する。

【0022】

時刻  $t_4$  に、タイミングジェネレータは、信号  $S_N 1$  を L レベルとする。これにより、スイッチ  $S_N 1$  が非導通状態となる。よって、容量素子  $C_N 1$  は、この時刻の増幅ノイズ信号を保持する。

【0023】

時刻  $t_5$  に、垂直走査回路は、信号  $T_X$  を H レベルとする。これにより、トランジスタ  $M_1$  は、フォトダイオード  $D_1$  が蓄積した電荷のノード  $N_F$  への転送を開始する。また、タイミングジェネレータは、信号  $S_P 1$  を H レベルとする。これにより、増幅アンプ  $G_A$  が容量素子  $C_P 1$  に信号を出力する期間が開始する。

【0024】

時刻  $t_6$  に、垂直走査回路は、信号  $T_X$  を L レベルとする。これにより、トランジスタ  $M_1$  は、フォトダイオード  $D_1$  が蓄積した電荷のノード  $N_F$  への転送を終了する。この時に、トランジスタ  $M_3 1$  がトランジスタ  $M_4 1$  を介して垂直信号線 6 に出力する信号を、 $A$  信号と表記する。 $A$  信号は、第 1 光電変換部が蓄積した電荷に基づく第 1 光信号である。また、増幅アンプ  $G_A$  が、 $A$  信号を増幅して出力する信号を、増幅  $A$  信号と表記する。増幅  $A$  信号は、第 1 光信号を増幅アンプ  $G_A$  が増幅して出力する第 1 増幅信号である。

【0025】

時刻  $t_7$  に、タイミングジェネレータは信号  $S_P 1$  を L レベルとする。これにより、容量素子  $C_P 1$  は、この時刻の増幅  $A$  信号を保持する。

【0026】

時刻  $t_8$  に、タイミングジェネレータは、信号  $S_B N$  を H レベルとし、信号  $S_S N$  を L レベルとする。これにより、スイッチ  $S_B N$  が導通状態となり、スイッチ  $S_S N$  が非導通状態となる。よって、バッファ回路  $A_N$  は、容量素子  $C_N 1$  が保持した増幅ノイズ信号をスイッチ  $S_N 2$  に出力する。また、同時に、タイミングジェネレータは、信号  $S_B P$  を H レベルとし、信号  $S_S P$  を L レベルとする。これにより、スイッチ  $S_B P$  が導通状態となり、スイッチ  $S_S P$  が非導通状態となる。よって、バッファ回路  $A_P$  は、容量素子  $C_P 1$  が保持した増幅  $A$  信号をスイッチ  $S_P 2$  に出力する。バッファ回路  $A_P$  が出力する信号は、第 1 増幅信号である増幅  $A$  信号をバッファした第 1 バッファ信号である。

【0027】

時刻  $t_9$  に、タイミングジェネレータは、信号  $S_N 2$  と信号  $S_P 2$  を H レベルとする。これにより、バッファ回路  $A_N$  が容量素子  $C_N 2$  に増幅ノイズ信号を出力する期間が開始する。また、バッファ回路  $A_P$  が容量素子  $C_P 2$  に増幅  $A$  信号を出力する期間が開始する。

【0028】

時刻  $t_{10}$  に、信号  $S_N 2$  と信号  $S_P 2$  を L レベルとする。これにより、容量素子  $C_N 2$  は、増幅ノイズ信号を保持し、容量素子  $C_P 2$  は第 1 バッファ信号である増幅  $A$  信号を保持する。

【0029】

その後、不図示の水平走査回路は、信号  $S_N 3 1$  と信号  $S_P 3 1$  を H レベルとする。これにより、図 1 の 1 列目の画素セル 3 に関わる読み出し回路 9 に含まれる容量素子  $C_N 2$  から画素セル 3 のノイズ信号に基づく増幅ノイズ信号が出力アンプ  $M_A$  に出力される。また、1 列目の画素セル 3 に関わる読み出し回路 9 に含まれる容量素子  $C_P 2$  から、

10

20

30

40

50

フォトダイオード D 1 の蓄積した電荷に基づく増幅 A 信号が出力アンプ M A に出力される。出力アンプ M A は、増幅 A 信号と増幅ノイズ信号との差の信号を、端子 O U T N と端子 O U T S とに出力する。その後、水平走査回路は、信号 S N 3 2 と信号 S P 3 2 とを H レベルとする。このようにして、各列の読み出し回路 9 は、増幅 A 信号と増幅ノイズ信号とを出力アンプ M A に出力する。この各列の読み出し回路 9 が、増幅 A 信号と増幅ノイズ信号とを出力アンプ M A に出力する期間を、A 水平走査期間と表記する。A 水平走査期間は、図 2 では時刻 t 1 1 から時刻 t 1 5 までとしている。

#### 【0030】

一方、垂直走査回路は、時刻 t 1 0 に、信号 T X 2 を H レベルとする。1 行目の画素セル 3 のトランジスタ M 2 は、フォトダイオード D 2 が蓄積した電荷のノード N F への転送を開始する。ノード N F は、先の動作によって、フォトダイオード D 1 が蓄積した電荷を保持している。時刻 t 1 1 に垂直走査回路が信号 T X 2 を L レベルとすることによって、1 行目の画素セル 3 のノード N F は、フォトダイオード D 1 が蓄積した電荷と、フォトダイオード D 2 が蓄積した電荷とを足した電荷を保持する。この時に、トランジスタ M 3 1 がトランジスタ M 4 1 を介して垂直信号線 6 に出力する信号を A + B 信号と表記する。尚、A + B 信号と A 信号との差の信号は B 信号である。B 信号とは、フォトダイオード D 2 が蓄積した電荷のみに基づいて、トランジスタ M 3 1 がトランジスタ M 4 1 を介して垂直信号線 6 に出力した場合に得られると想定される信号である。また、増幅アンプ G A が、A + B 信号を増幅して出力する信号を増幅 A + B 信号と表記する。増幅 A + B 信号は、A + B 信号を増幅した第 2 増幅信号である。

10

20

#### 【0031】

また、時刻 t 1 1 に、タイミングジェネレータは、信号 S B P を L レベルとし、信号 S S P を H レベルとする。これにより、容量素子 C P 1 が増幅アンプ G A の出力する信号を再び保持する準備が整う。

#### 【0032】

時刻 t 1 2 に、タイミングジェネレータは、信号 S P 1 を H レベルとし、その後、時刻 t 1 3 に、タイミングジェネレータは、信号 S P 1 を L レベルとする。この動作により、容量素子 C P 1 は、増幅 A + B 信号を保持する。

#### 【0033】

時刻 t 1 4 に、タイミングジェネレータは、信号 S B P を H レベルとし、信号 S S P を L レベルとする。これにより、バッファ回路 A P は、増幅 A + B 信号を、スイッチ S P 2 に出力する。バッファ回路 A P が出力する信号は、第 2 増幅信号である増幅 A + B 信号をバッファした第 2 バッファ信号である。尚、バッファ回路 A N が出力する信号が、増幅ノイズ信号をバッファした第 3 バッファ信号である。

30

#### 【0034】

A 水平走査期間後の時刻 t 1 6 に、タイミングジェネレータは、信号 S N 2 と信号 S P 2 とを H レベルとする。これにより、容量素子 C N 2 は、容量素子 C N 1 が保持していた増幅ノイズ信号を保持する。また、容量素子 C P 2 は、増幅 A + B 信号を保持する。

#### 【0035】

その後、水平走査回路は信号 S N 3 1 と信号 S P 3 1 とを H レベルとする。これにより、容量素子 C N 1 から増幅ノイズ信号が出力アンプ M A に出力される。また、容量素子 C P 1 から、増幅 A + B 信号が出力アンプ M A に出力される。出力アンプ M A は、増幅 A + B 信号と増幅ノイズ信号との差の信号を端子 O U T S と端子 O U T N とに出力する。この各列の読み出し回路 9 が、増幅 A + B 信号と増幅ノイズ信号とを出力アンプ M A に出力する期間を、A + B 水平走査期間と表記する。A + B 水平走査期間は、図 2 では時刻 t 1 8 から時刻 t 1 9 までとしている。

40

#### 【0036】

時刻 t 1 8 以降、垂直走査回路とタイミングジェネレータは、時刻 t 0 から時刻 t 1 8 までの期間と同様に、2 行目の画素セル 3 に基づく、増幅ノイズ信号、増幅 A 信号、増幅 A + B 信号を得る動作を行う。

50

## 【0037】

本実施例では、信号 S P 2 を H レベルとしている期間は、増幅 A + B 信号の場合は時刻  $t_{16}$  から時刻  $t_{17}$  の期間である。一方、信号 S P 2 を H レベルとしている期間は、増幅 A 信号の場合は、時刻  $t_{16}$  から時刻  $t_{17}$  までの期間よりも短い、時刻  $t_9$  から時刻  $t_{10}$  までの期間である。これは、増幅 A 信号は、増幅 A + B 信号に対して、取り得る振幅範囲が小さいことによるものである。バッファ回路 A P が容量素子 C P 2 に出力する増幅 A 信号と増幅 A + B 信号とのそれぞれの信号の出力を開始してから収束するまでのセトリング期間は、増幅 A 信号の方が増幅 A + B 信号よりも短い。よって、容量素子 C P 2 に増幅 A 信号を保持させるためにスイッチ S P 2 を導通状態としている期間を、容量素子 C P 2 に増幅 A + B 信号を保持させるためにスイッチ S P 2 を導通状態としている期間よりも短くしても、スイッチ S P 2 を非導通状態に切り替えるまでにバッファ回路 A P の出力は静定するので、容量素子 C P 2 に保持される増幅 A 信号の信号精度の低下が生じにくい。さらに、容量素子 C P 2 に増幅 A 信号を保持させるためにスイッチ S P 2 を導通状態としている期間を、容量素子 C P 2 に増幅 A + B 信号を保持させるためにスイッチ S P 2 を導通状態としている期間よりも短くする分、A 水平走査期間を早く開始することができる。これにより、撮像装置が出力する信号精度の低下を抑制しながら、撮像装置の高速化を実現することができる。

10

## 【0038】

本実施例の撮像装置は、容量素子 C P 2 に増幅 A 信号を保持させるためにスイッチ S P 2 を導通状態としている期間の長さを、容量素子 C P 2 に増幅 A + B 信号を保持させるためにスイッチ S P 2 を導通状態としている期間の長さの  $1/2$  以下とすることが好ましい。これは、増幅 A 信号の取り得る信号振幅が、増幅 A + B 信号の信号振幅のおよそ  $1/2$  であるためである。また、本実施例では、画素セル 3 が 2 つのフォトダイオードを有している例を説明した。他の例として、画素セル 3 がさらに多くのフォトダイオードを有していても良い。画素セル 3 が有するフォトダイオードの数を  $L$  個とする。  $L$  個のフォトダイオードのうち、上述した A 信号に相当する信号として、画素セル 3 は  $L$  個のフォトダイオードのうちの、 $L$  個よりも少ない  $M$  個のフォトダイオードの各々が蓄積した電荷同士を足した電荷に基づく信号（以下、M 信号とする）を出力する。また、画素セル 3 は、上述した A + B 信号に相当する信号として、 $L$  個のフォトダイオードの各々が蓄積した電荷同士を足した電荷に基づく信号（以下、L 信号とする）を出力する。このような場合には、本実施例の撮像装置は、M 信号に基づく信号を容量素子 C P 2 に保持させるためにスイッチ S P 2 を導通状態としている期間の長さを、L 信号に基づく信号を容量素子 C P 2 に保持させるためにスイッチ S P 2 を導通状態としている期間の長さの  $M/L$  以下とすることが好ましい。

20

30

## 【0039】

さらに本実施例の撮像装置は、容量素子 C P 1 に増幅 A 信号を保持させるためにスイッチ S P 1 を導通状態としている期間を、容量素子 C P 1 に増幅 A + B 信号を保持させるためにスイッチ S P 1 を導通状態としている期間よりも短くしても良い。これにより本実施例の撮像装置は、撮像装置の高速化をさらに進展させることができる。

40

## 【0040】

また、本実施例の撮像装置は、フォトダイオード D 1 とフォトダイオード D 2 に共通のマイクロレンズを設けることができる。この場合には、本実施例の撮像装置は、位相差検出による焦点検出用の焦点検出信号と、画像生成用の画像信号とを出力することができる。すなわち、本実施例の場合には、焦点検出用の信号は、増幅 A 信号であり、画像信号は増幅 A + B 信号である。撮像装置の外部に設けられた出力信号処理部は、撮像装置から入力される増幅 A 信号と増幅 A + B 信号との差の信号である、増幅 B 信号に相当する信号を生成する。そして出力信号処理部は、この増幅 B 信号に相当する信号と、増幅 A 信号とを用いて位相差を検出する。出力信号処理部は、検出した位相差に基づいて、合焦か否かを検出することができる。また、出力信号処理部は増幅 A + B 信号を用いて画像を生成する。

50

## 【0041】

焦点検出信号は、焦点検出を行えるだけの信号精度を有していれば良いため、画像信号に比して信号精度の低下を許容しやすい。従って、本実施例のように、容量素子C P 2に増幅A信号を保持させるための、スイッチS P 2を導通状態としている期間を短くすることで増幅A信号の信号精度の低下が仮に生じたとしても、焦点検出の精度には影響しにくい。従って、焦点検出の精度の低下を抑制しながら、撮像装置を高速化することができる。

## 【0042】

尚、本実施例の撮像装置は、画素セル3が出力する信号を増幅する増幅アンプG Aを有していた。本実施例の撮像装置は、必ずしも増幅アンプG Aを有していなくともよく、読み出し回路3が、画素セル3が出力する信号をバッファするバッファ回路A Pと、スイッチS P 2と、容量素子C P 2とを有していれば良い。

10

## 【0043】

(実施例2)

本実施例の撮像装置について、図面を参照しながら、実施例1と異なる点を中心に説明する。

## 【0044】

図3は、本実施例の撮像装置の構成を示した図である。図3では、図1に示した素子と同じ機能を有する素子については、図1で付した符号と同じ符号を付して表している。1つの画素セル3は、フォトダイオードD a 1、フォトダイオードD b 1、フォトダイオードD a 2、フォトダイオードD b 2の4つのフォトダイオードを有する。フォトダイオードD a 1は、トランジスタM a 1を介してノードN Fに電気的に接続されている。同様に、フォトダイオードD b 1、フォトダイオードD a 2、フォトダイオードD b 2はそれぞれ、トランジスタM b 1、トランジスタM a 2、トランジスタM b 2を介してノードN Fに電気的に接続されている。

20

## 【0045】

また、本実施例の撮像装置は、各列の容量素子C N 2が出力線7に出力した増幅ノイズ信号は、第1出力アンプB Rに入力される。第1出力アンプB Rは、入力された増幅ノイズ信号を端子OUT Nに出力する。また、各列の容量素子C P 2が出力線8に出力した信号は、第2出力アンプB Vに入力される。第2出力アンプB Vは、入力された信号を端子OUT Sに出力する。

30

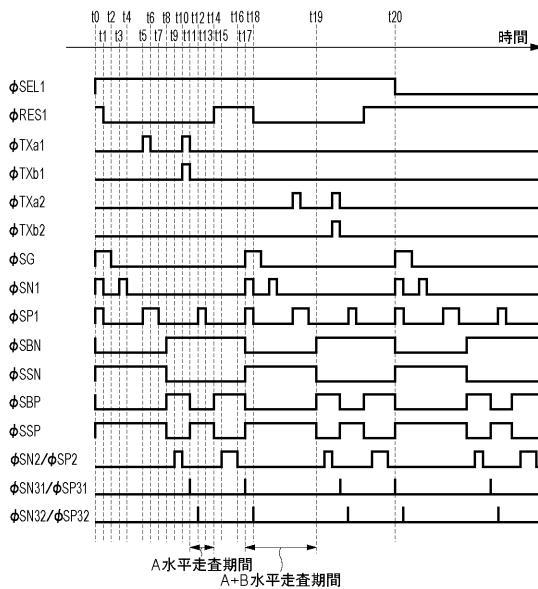

## 【0046】

図4は、図3に示した撮像装置の動作を示したタイミング図である。図4では、図2と同じ素子を駆動する信号については、図2で付した符号と同じ符号を付して表している。

## 【0047】

図4に示した信号T X a 1、信号T X b 1、信号T X a 2、信号T X b 2は、それぞれ図3で付したそれぞれの信号に対応している。

## 【0048】

時刻t 5に、垂直走査回路は、信号T X a 1をHレベルとする。これにより、トランジスタM a 1は、フォトダイオードD a 1が蓄積した電荷のノードN Fへの転送を開始する。また、同時刻に、タイミングジェネレータは、信号S P 1をHレベルとする。これにより、容量素子C P 1は、増幅アンプG Aが出力する信号の保持を開始する。

40

## 【0049】

時刻t 6に、垂直走査回路は、信号T X a 1をLレベルとする。これにより、トランジスタM a 1は、フォトダイオードD a 1が蓄積した電荷のノードN Fへの転送を終了する。この時に、トランジスタM 3 1が垂直信号線6に出力する信号は、A信号である。増幅アンプG Aは、A信号を増幅した増幅A信号を容量素子C P 1に出力する。

## 【0050】

時刻t 7にタイミングジェネレータは、信号S P 1をLレベルとする。これにより、容量素子C P 1が、増幅A信号を保持する。

50

## 【0051】

時刻  $t_9$  にタイミングジェネレータは信号  $S_N 2$  と信号  $S_P 2$  とを H レベルとする。これにより、バッファ回路  $A_N$  が容量素子  $C_N 2$  に増幅ノイズ信号を出力する期間が開始する。また、バッファ回路  $A_P$  が容量素子  $C_P 2$  に増幅  $A$  信号を出力する期間が開始する。

## 【0052】

時刻  $t_{10}$  にタイミングジェネレータは、信号  $S_N 2$  と信号  $S_P 2$  とを L レベルとする。これにより、容量素子  $C_N 2$  は増幅ノイズ信号を保持する。また、容量素子  $C_P 2$  は増幅  $A$  信号を保持する。

## 【0053】

時刻  $t_{10}$  に、垂直走査回路は、信号  $TX_a 1$  と信号  $TX_b 1$  とを H レベルとする。これにより、トランジスタ  $M_b 1$  はフォトダイオード  $D_b 1$  が蓄積した電荷のノード  $N_F$  への転送を開始する。また、トランジスタ  $M_a 1$  は、フォトダイオード  $D_a 1$  が時刻  $t_6$  以降に蓄積した電荷のノード  $N_F$  への転送を開始する。

10

## 【0054】

時刻  $t_{11}$  に、垂直走査回路は、信号  $TX_a 1$  と信号  $TX_b 1$  とを L レベルとする。これにより、ノード  $N_F$  は、フォトダイオード  $D_a 1$  が蓄積した電荷と、フォトダイオード  $D_b 1$  が蓄積した電荷とを足した電荷を保持する。この時、トランジスタ  $M_3 1$  がトランジスタ  $M_4 1$  を介して垂直信号線  $6$  に出力する信号が  $A + B$  信号である。増幅アンプ  $G_A$  は、 $A + B$  信号を増幅した増幅  $A + B$  信号をスイッチ  $S_P 1$  に出力する。

20

## 【0055】

時刻  $t_{12}$  に、タイミングジェネレータは、信号  $S_P 1$  を H レベルとする。これにより、増幅アンプ  $G_N$  が容量素子  $C_P 1$  に増幅  $A + B$  信号を出力する期間が開始する。

## 【0056】

時刻  $t_{13}$  に、タイミングジェネレータは、信号  $S_P 1$  を L レベルとする。これにより、容量素子  $S_P 1$  は増幅  $A + B$  信号を保持する。

## 【0057】

時刻  $t_{15}$  にタイミングジェネレータは信号  $S_N 2$  と信号  $S_P 2$  とを H レベルとする。これにより、バッファ回路  $A_N$  が容量素子  $C_N 2$  に増幅ノイズ信号を出力する期間が開始する。また、バッファ回路  $A_P$  が容量素子  $C_P 2$  に増幅  $A + B$  信号を出力する期間が開始する。

30

## 【0058】

時刻  $t_{16}$  に、タイミングジェネレータは信号  $S_N 2$  と信号  $S_P 2$  とを L レベルとする。これにより、容量素子  $C_N 2$  は増幅ノイズ信号を保持する。また、容量素子  $C_P 2$  は増幅  $A + B$  信号を保持する。

## 【0059】

時刻  $t_{18}$  以降、垂直走査回路とタイミングジェネレータは、フォトダイオード  $D_a 2$  が蓄積した電荷に基づく増幅  $A$  信号を撮像装置の外部に出力する動作を行う。また、垂直走査回路とタイミングジェネレータは、フォトダイオード  $D_a 2$  が蓄積した電荷とフォトダイオード  $D_b 2$  が蓄積した電荷とを足した電荷に基づく増幅  $A + B$  信号を撮像装置の外部に出力する動作を行う。また、垂直走査回路とタイミングジェネレータは、画素セル  $3$  のノイズ信号に基づく増幅ノイズ信号を撮像装置の外部に出力する動作を行う。

40

## 【0060】

本実施例の撮像装置においても、実施例 1 と同様に、容量素子  $C_P 2$  に増幅  $A$  信号を保持させるためにスイッチ  $S_P 2$  を導通状態としている期間を、容量素子  $C_P 2$  に増幅  $A + B$  信号を保持させるためにスイッチ  $S_P 2$  を導通状態としている期間よりも短くしている。これにより、撮像装置が出力する信号精度の低下を抑制しながら、撮像装置の高速化を実現することができる。

## 【0061】

また、本実施例の撮像装置は、フォトダイオード  $D_a 1$  とフォトダイオード  $D_b 1$  とで

50

共通のマイクロレンズを設けることができる。また、本実施例の撮像装置は、フォトダイオード D a 2 とフォトダイオード D b 2 とで共通のマイクロレンズを設けることができる。これにより、フォトダイオード D a 1 が蓄積した電荷に基づく増幅 A 信号と、フォトダイオード D a 1 とフォトダイオード D b 1 とが蓄積した電荷の和に基づく増幅 A + B 信号とを用いて、位相差検出による焦点検出と画像の生成を行うことができる。

#### 【0062】

また、本実施例の撮像装置は、フォトダイオード D a 1 と、フォトダイオード D b 1 と、フォトダイオード D a 2 と、フォトダイオード D b 2 とで共通のマイクロレンズを設けることができる。この場合には、撮像装置は、フォトダイオード D a 1 とフォトダイオード D b 1 のそれぞれが蓄積した電荷同士を足した電荷に基づく第 1 の増幅 A + B 信号を撮像装置の外部の出力信号処理部に出力する。そして撮像装置は、フォトダイオード D a 2 とフォトダイオード D b 2 のそれぞれが蓄積した電荷同士を足した電荷に基づく第 2 の増幅 A + B 信号を出力信号処理部に出力する。出力信号処理部は、第 1 の増幅 A + B 信号と第 2 の増幅 A + B 信号とを足した信号に基づいて画像を生成する。一方で、位相差検出による焦点検出は、例えば以下の(1)から(6)までの組み合わせで行うことができる。尚、以下に示す増幅 B 信号は、出力信号処理部が増幅 A + B 信号から増幅 A 信号を差し引いて得られる信号である。

#### 【0063】

(1) フォトダイオード D a 1 の電荷に基づく増幅 A 信号と、フォトダイオード D b 1 の電荷に基づく増幅 B 信号

(2) フォトダイオード D a 1 の電荷に基づく増幅 A 信号と、フォトダイオード D b 2 の電荷に基づく増幅 B 信号

(3) フォトダイオード D a 1 の電荷に基づく増幅 A 信号と、フォトダイオード D a 2 の電荷に基づく増幅 A 信号

(4) フォトダイオード D a 2 の電荷に基づく増幅 A 信号と、フォトダイオード D b 1 の電荷に基づく増幅 B 信号

(5) フォトダイオード D a 1 の電荷に基づく増幅 A 信号とフォトダイオード D a 2 の電荷に基づく増幅 A 信号とを足した信号と、フォトダイオード D b 1 の電荷に基づく増幅 B 信号とフォトダイオード D b 2 の電荷に基づく増幅 B 信号とを足した信号

(6) フォトダイオード D a 1 の電荷に基づく増幅 A 信号とフォトダイオード D b 1 の電荷に基づく増幅 B 信号とを足した信号と、フォトダイオード D a 2 の電荷に基づく増幅 A 信号とフォトダイオード D b 2 の電荷に基づく増幅 B 信号とを足した信号

(7) フォトダイオード D b 1 の電荷に基づく増幅 B 信号と、フォトダイオード D b 2 の電荷に基づく増幅 B 信号

(8) フォトダイオード D a 2 の電荷に基づく増幅 A 信号と、フォトダイオード D b 2 の電荷に基づく増幅 B 信号

#### (9) 第 1 の増幅 A + B 信号と第 2 の増幅 A + B 信号

#### 【0064】

さらに本実施例の撮像装置は、容量素子 C P 1 に増幅 A 信号を保持させるためにスイッチ S P 1 を導通状態としている期間を、容量素子 C P 1 に増幅 A + B 信号を保持させるためにスイッチ S P 1 を導通状態としている期間よりも短くしても良い。これにより本実施例の撮像装置は、撮像装置が output する信号精度の低下を抑制しつつ、撮像装置の高速化をさらに進展させることができる。

#### 【0065】

また、撮影シーンによっては、画素アレイ 1 の一部の列の画素の焦点検出信号を用いて焦点検出がある。この場合には、画素アレイ 1 の一部の列の読み出し回路 9 が増幅 A 信号を出力する。さらに、この一部の列の読み出し回路 9 を含む読み出し回路 9 が増幅 A + B 信号を出力する。この場合には、A 水平走査期間を、A + B 水平走査期間よりも短くすることができる。これにより本実施例の撮像装置は、さらに撮像装置を高速化させることができる。

10

20

30

40

50

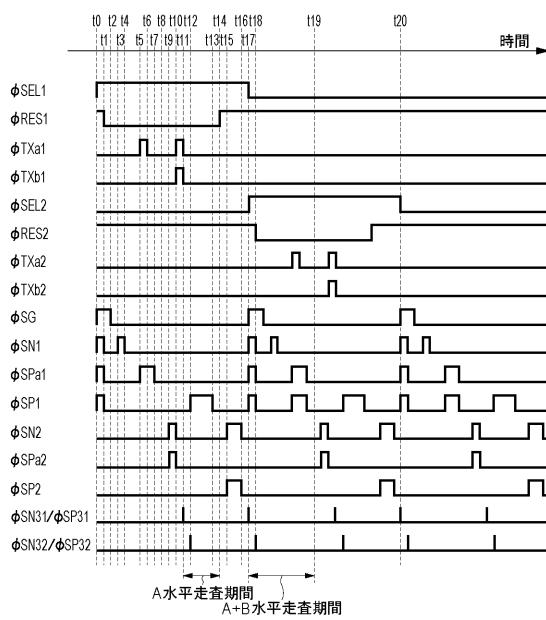

## 【0066】

## (実施例3)

本実施例の撮像装置について、実施例2と異なる点を中心に説明する。本実施例の撮像装置の構成は、実施例2の図3で示したものと同一である。本実施例の撮像装置は、容量素子C P 1に増幅A+B信号を保持させるためにスイッチS P 1を導通状態としている期間を、増幅A信号を保持させるためにスイッチS P 1を導通状態としている期間と同じ、あるいは短くする点が、実施例2と異なる。

## 【0067】

図5は、本実施例の撮像装置の動作を示したタイミング図である。

## 【0068】

タイミングジェネレータは、時刻t5から時刻t7までの期間、信号S P 1をHレベルとしている。タイミングジェネレータが時刻t7に、信号S P 1をLレベルとすることにより、容量素子S P 1は増幅A信号を保持する。

10

## 【0069】

その後、タイミングジェネレータは、信号S B Pを時刻t8から時刻t11までの間にHレベルとし、時刻t11から時刻t14までの期間に、信号S B PをLレベルとする。また、タイミングジェネレータは、信号S S Pを時刻t8から時刻t11までの期間にLレベルとし、時刻t11から時刻t14までの期間にHレベルとする。

## 【0070】

また、タイミングジェネレータは、信号S B PをLレベルとし、かつ信号S S PをHレベルとしている期間内の、時刻t12から時刻t13までの期間に、信号S P 1をHレベルとする。時刻t12から時刻t13までの期間は、時刻t5から時刻t7までの期間よりも短い。

20

## 【0071】

増幅A+B信号の振幅範囲は増幅A信号の振幅範囲よりも大きい。しかし、容量素子S P 1は、既に時刻t7に増幅A信号を保持している。本実施例の撮像装置は、容量素子S P 1が保持した増幅A信号をリセットせずに、増幅A+B信号を保持させている。よって、増幅A+B信号を保持させるためにスイッチS P 1を導通状態としている期間は、容量素子S P 1は、増幅A+B信号と増幅A信号との差の信号を保持するのに十分な期間とすれば良い。よって、時刻t12から時刻t13までの期間の長さを、時刻t5から時刻t7までの期間の長さ以下とすることができます。

30

## 【0072】

これにより、本実施例の撮像装置は、増幅A+B信号を容量素子C P 1に保持させる期間を、実施例2の撮像装置に対して短くすることができる。これにより、さらに撮像装置を高速化することができる。

## 【0073】

## (実施例4)

本実施例の撮像装置について、実施例1と異なる点を中心に説明する。本実施例の撮像装置は、実施例1とは読み出し回路9の構成と動作が異なる。

40

## 【0074】

図6は、本実施例の撮像装置の構成を示した図である。図6では、図1に示した素子と同じ機能を有する素子については、図1で付した符号と同じ符号を付して表している。また、本実施例の撮像装置は、画素アレイ1を挟むように周辺回路部5が設けられている。

## 【0075】

本実施例の読み出し回路9は、バッファ回路A P, バッファ回路A Nに加えて、さらにバッファ回路A P aを有する。さらに、本実施例の読み出し回路9は、容量素子C P g 1の代わりに、容量素子C P g 1を有する。また、本実施例の読み出し回路9は、容量素子C N 1の代わりに、容量素子C N g 1を有する。また、本実施例の読み出し回路9は、さらに、容量素子C P a g 1とスイッチS P a 2とを有する。

## 【0076】

50

図7は、図6に示した撮像装置の動作を示したタイミング図である。図7に示した信号S P a 1は、スイッチS P a 1を制御する信号であり、信号S P a 2は、スイッチS P a 2を制御する信号である。

【0077】

時刻t5に、タイミングジェネレータは信号S P a 1をHレベルとする。これにより、増幅アンプG Aが容量素子C P a g 1に増幅A信号を出力する期間が開始する。その後、時刻t6に、タイミングジェネレータは信号S P a 1をLレベルとする。これにより、容量素子C P a g 1は、増幅A信号を保持する。

【0078】

時刻t9に、タイミングジェネレータは、信号S N 2と信号S P a 2とをHレベルとする。これにより、バッファ回路A Nが容量素子C N 2に増幅ノイズ信号を出力する期間が開始する。また、バッファ回路A Pが容量素子C P 2に増幅A信号を出力する期間が開始する。

【0079】

時刻t10に、タイミングジェネレータは、信号S N 2と信号S P a 2とをLレベルとする。これにより、容量素子C N 2が増幅ノイズ信号を保持する。また、容量素子C P 2が増幅A信号を保持する。

【0080】

時刻t12に、タイミングジェネレータは信号S P 1をHレベルとする。これにより、増幅アンプG Aが容量素子C p g 1に増幅A+B信号を出力する期間が開始する。

【0081】

時刻t13に、タイミングジェネレータは、信号S P 1をLレベルとする。これにより、容量素子C P g 1が、増幅A+B信号を保持する。

【0082】

時刻t15に、タイミングジェネレータは信号S N 2と信号S P 2とをHレベルとする。これにより、バッファ回路A Nが容量素子C N 2に増幅ノイズ信号を出力する期間が開始する。また、バッファ回路A Pが容量素子C P 2に増幅A+B信号を出力する期間が開始する。

【0083】

時刻t16に、タイミングジェネレータは信号S N 2と信号S P 2とをLレベルとする。これにより、容量素子C N 2が増幅ノイズ信号を保持する。また、容量素子C P 2が増幅A+B信号を保持する。

【0084】

容量素子C P 2に増幅A信号を保持させるためにスイッチS P 2を導通状態としている期間は時刻t9から時刻t10までの期間である。また、容量素子C P 2に増幅A+B信号を保持させるためにスイッチS P 2を導通状態としている期間は時刻t15から時刻t16までの期間である。本実施例の撮像装置は、容量素子C P 2に増幅A信号を保持させるためにスイッチS P 2を導通状態としている期間を、容量素子C P 2に増幅A+B信号を保持させるためにスイッチS P 2を導通状態としている期間よりも短くしている。これにより本実施例の撮像装置も、実施例1と同様の効果を得ることができる。

【0085】

(実施例5)

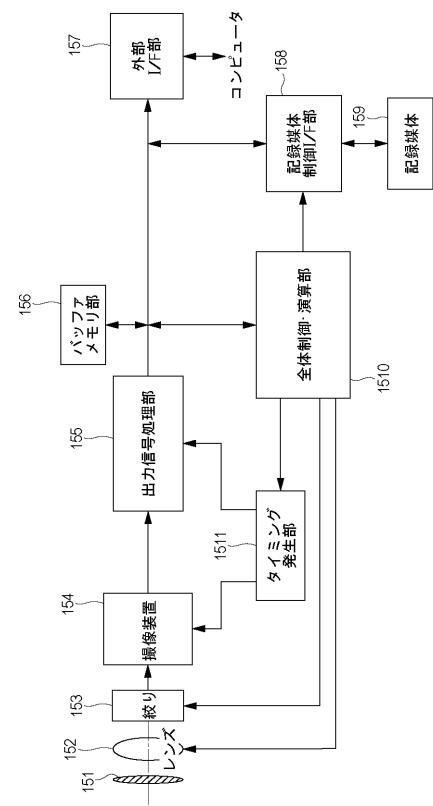

実施例1～4で述べた撮像装置を撮像システムに適用した場合の実施例について述べる。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図8に、撮像システムの例としてデジタルスチルカメラに撮像装置を適用した場合の模式図を示す。

【0086】

図8に例示した撮像システムは、レンズの保護のためのバリア151、被写体の光学像を撮像装置154に結像させるレンズ152、レンズ152を通過する光量を可変にするための絞り153を有する。レンズ152、絞り153は撮像装置154に光を集光する

10

20

30

40

50

光学系である。また、図8に例示した撮像システムは撮像装置154より出力される出力信号の処理を行う出力信号処理部155を有する。

【0087】

出力信号処理部155は、撮像装置154が出力する信号をデジタル信号に変換するA/D変換を行う。実施例1、実施例3、実施例4の撮像装置154は、増幅A信号と増幅ノイズ信号との差の信号(以下、増幅A-N信号と表記する。)と、増幅A+B信号と増幅ノイズ信号との差の信号(以下、増幅A+B-N信号と表記する。)とを出力する。この場合には、増幅A-N信号と、増幅A+B-N信号のそれぞれをデジタル信号に変換する。以下では、デジタル化された増幅A-N信号を、デジタルA信号と表記し、デジタル化された増幅A+B-N信号をデジタルA+B信号と表記する。

10

【0088】

また、実施例2の撮像装置154は、増幅A信号と、増幅A+B信号と、増幅ノイズ信号とをそれぞれ出力する。出力信号処理部155は、増幅A信号と、増幅A+B信号と、増幅ノイズ信号をそれぞれデジタル信号に変換する。そして出力信号処理部155は、デジタル化された増幅A信号と、デジタル化された増幅ノイズ信号との差の信号を得る。この差の信号は、先に述べたデジタルA信号に相当する。また、出力信号処理部155は、デジタル化された増幅A+B信号と、デジタル化された増幅ノイズ信号との差の信号とを生成する。この差の信号は、先に述べたデジタルA+B信号に相当する。デジタルA信号は、増幅A信号に含まれるノイズ成分を低減した信号である。また、デジタルA+B信号は、増幅A+B信号に含まれるノイズ成分を低減した信号である。

20

【0089】

また、出力信号処理部155はその他、必要に応じて各種の補正、圧縮を行って信号を出力する動作を行う。

【0090】

図8に例示した撮像システムはさらに、画像データを一時的に記憶する為のバッファメモリ部156、外部コンピュータ等と通信する為の外部インターフェース部157を有する。さらに撮像システムは、撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体159、記録媒体159に記録または読み出しを行うための記録媒体制御インターフェース部158を有する。さらに固体撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510、撮像装置154と出力信号処理部155に各種タイミング信号を出力するタイミング発生部1511を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置154と、撮像装置154から出力された出力信号を処理する出力信号処理部155とを有すればよい。

30

【0091】

出力信号処理部155は、デジタルA+B信号からデジタルA信号を差し引いた信号を生成する。この生成する信号は、増幅A+B信号から増幅A信号を差し引いた信号をデジタル信号に変換した信号に相当する。この生成する信号を、以下デジタルB信号と表記する。このデジタルA+B信号からデジタルA信号を差し引く処理は、共通のマイクロレンズが設けられたフォトダイオードに基づく信号同士で行う。そして、出力信号処理部155は、デジタルA信号とデジタルB信号とを用いて、位相差検出方式の焦点検出が行う。また、出力信号処理部155はデジタルA+B信号を用いて画像の形成を行う。

40

【0092】

以上のように、本実施例の撮像システムは、撮像装置154を適用して焦点検出動作、撮像動作を行うことが可能である。

【0093】

本実施例の出力信号処理部155は、B信号に基づくデジタル信号を、デジタルA+B信号からデジタルA信号を差し引く、デジタル減算処理によって生成した。他の例として、出力信号処理部155が、増幅A+B信号から増幅A信号を差し引いて増幅B信号を生成する。そして、出力信号処理部155が増幅B信号をデジタル信号に変換することでデ

50

ジタルB信号を得るようにも良い。

【0094】

なお、上記実施例は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。また、これまで述べた各実施例を種々組み合わせて実施することができる。

【符号の説明】

【0095】

1 画素アレイ、3 画素セル、6 垂直信号線、9 読み出し回路、A P バッファ回路(バッファ部)、A N バッファ回路(第2バッファ部)、S P 2 スイッチ(スイッチ部)、S P 1 スイッチ(第2スイッチ部)、S N 1 スイッチ(第3スイッチ部)、S N 2 スイッチ(第4スイッチ部)、C P 2 容量素子、C P 1 容量素子(第2容量素子)、C N 1 容量素子(第3容量素子)、C N 2 容量素子(第4容量素子)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 沖田 彰

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

Fターム(参考) 5C024 CX04 EX43 GX14 GX16 GZ24 HX35 HX50 HX58 JX45