(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-105068

(P2009-105068A)

(43) 公開日 平成21年5月14日(2009.5.14)

(51) Int.Cl.

|             |              |                  |

|-------------|--------------|------------------|

| <b>H05B</b> | <b>33/26</b> | <b>(2006.01)</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> |

| <b>H05B</b> | <b>33/22</b> | <b>(2006.01)</b> |

| <b>H05B</b> | <b>33/10</b> | <b>(2006.01)</b> |

F 1

|      |       |

|------|-------|

| H05B | 33/26 |

| H05B | 33/14 |

| H05B | 33/22 |

| H05B | 33/10 |

|   |

|---|

| Z |

| A |

| Z |

|   |

テーマコード(参考)

3K107

審査請求 有 請求項の数 14 O L (全 29 頁)

(21) 出願番号

特願2009-27076 (P2009-27076)

(22) 出願日

平成21年2月9日 (2009.2.9)

(62) 分割の表示

特願2003-198128 (P2003-198128)

の分割

原出願日

平成15年7月16日 (2003.7.16)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 茅野 苞治

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 DD03 DD37

DD44Z DD45Z DD90 EE03 FF04

GG05

(54) 【発明の名称】電気光学装置、電気光学装置の製造方法及び電子機器

## (57) 【要約】

【課題】表示ムラの発生を抑制することで表示品位を向上するようにした電気光学装置、電気光学装置の製造方法及び電子機器を提供する。

【解決手段】各画素20に形成される透明導電層47を、全てコンタクトホールHを介して導電層MLに電気的に接続されたようにした。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備え、前記陽極は前記発光性材料が設けられる画素毎に形成された電気光学装置において、

前記基板と前記陽極との間に形成された導電層と、

前記陰極と前記導電層とを電気的に接続するための接続部とを備えていることを特徴とする電気光学装置。

**【請求項 2】**

請求項 1 に記載の電気光学装置において、

前記接続部は前記画素毎に備えられていることを特徴とする電気光学装置。

**【請求項 3】**

請求項 1 または 2 に記載の電気光学装置において、

前記接続部はコンタクトホールで構成されていることを特徴とする電気光学装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一つに記載の電気光学装置において、

前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層を備え、

前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層が形成されていることを特徴とする電気光学装置。

**【請求項 5】**

請求項 4 に記載の電気光学装置において、

前記絶縁層は、その誘電率を  $2 / 3 . 5 \mu m$  以上であることを特徴とする電気光学装置。

**【請求項 6】**

請求項 1 乃至 5 のいずれか一つに記載の電気光学装置において、

前記導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、バナジウム (V)、ジルコニウム (Zr)、及びこれらの合金またはシリサイドのうちの一つで構成されることを特徴とする電気光学装置。

**【請求項 7】**

請求項 1 乃至 5 のいずれか一つに記載の電気光学装置において、

前記導電層は少なくとも一層の金属層を含む複数の導電層から構成されていることを特徴とする電気光学装置。

**【請求項 8】**

請求項 7 に記載の電気光学装置において、

前記基板上に該基板を保護する下地保護層を備え、その下地保護層は二酸化珪素で構成され、

前記複数の導電層は前記下地保護層上から順に第 1 導電層、第 2 導電層から構成される導電層であって、

前記第 1 導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第 2 導電層はアルミニウム (Al)、ニッケル (Ni) 及び白金 (Pt)、及びこれらの合金またはシリサイドのいずれか一つで構成されていることを特徴とする電気光学装置。

**【請求項 9】**

請求項 7 に記載の電気光学装置において、

前記基板上に該基板を保護する下地保護層を備え、その保護層は二酸化珪素で構成され、

前記複数の導電層は前記下地保護層上から順に第 1 導電層、第 2 導電層、第 3 導電層から構成され、

10

20

30

40

50

前記第1導電層はチタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第2導電層は銅(Cu)、アルミニウム(Al)、ニッケル(Ni)及び白金(Pl)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第3導電層は窒化チタン(TiN)、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成されていることを特徴とする電気光学装置。

#### 【請求項10】

請求項1乃至9のいずれか一つに記載の電気光学装置において、

前記導電層は前記基板から突出して形成された突出部を備えていることを特徴とする電気光学装置。 10

#### 【請求項11】

基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備えるとともに、前記発光性材料を画素毎に区分けするためのバンク層と、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部と、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層とを備えた電気光学装置の製造方法において、

前記基板の上方に前記導電層を形成する工程と、

前記導電層の上方に前記絶縁層、前記素子形成層、前記陽極及びバンク層を形成する工程と、

前記絶縁層に開口パターンを形成するのと同時に前記陰極と前記導電層とを電気的に接続するための接続部開口パターンを形成する工程と、

前記発光性材料を形成する工程と、

前記接続部を含む前記発光性材料を形成した領域の全面に透明性導電膜を形成する工程とを備えたことを特徴とする電気光学装置の製造方法。 20

#### 【請求項12】

請求項11に記載の電気光学装置の製造方法において、

前記導電層は第1導電層、第2導電層及び第3導電層から構成される導電層を備え 30

前記素子形成層は前記能動素子に信号を供給するための第1の信号線と第2の信号線とを備え、

前記第1導電層は前記第1の信号線を形成すると同時に形成され、

前記第2導電層は前記第2の信号線を形成すると同時に形成されるようにしたことを特徴とする電気光学装置の製造方法。 40

#### 【請求項13】

請求項11または12に記載の電気光学装置の製造方法において、

前記導電層はスパッタ法で形成するようにしたことを備えたことを特徴とする電気光学装置の製造方法。

#### 【請求項14】

請求項1乃至10のいずれか一つに記載の電気光学装置を備えていることを特徴とする電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、電気光学装置及び電気光学装置の製造方法に関するものである。

#### 【背景技術】

#### 【0002】

液晶素子、有機EL素子、電気泳動素子、電子放出素子等といった電気光学素子を複数備えた表示ディスプレイの駆動方式の一つにアクティブマトリクス駆動方式がある。アク 50

ティップマトリクス駆動方式の表示ディスプレイには、例えば、各電気光学素子の陰極が透明電極で形成され、その陰極側から有機EL素子にて発せられた光が出射されるトップエミッションタイプの表示ディスプレイがある。

#### 【0003】

この種の表示ディスプレイにおいては、透明電極はスズドープ酸化インジウム(ITO)で構成された透明導電性薄膜であって表示パネル部の全面に渡って形成されている。一般に、透明導電性薄膜は金属と比較してその抵抗率が高いことが知られている。従って、表示パネル上に形成される位置によって電気光学素子の陰極の電位に差が生じる。その結果、例えば、全ての画素に同じ電圧レベルのデータ信号を供給したとき、画素が形成される位置によって輝度に差が生じてしまう。この結果、表示パネル部に、所謂、表示ムラが生じる。特に表示パネル部が大型化されるのに伴ってこの表示ムラが顕著に現れてしまう。

10

#### 【0004】

例えば、表示パネル部の中央部に形成される画素の有機EL素子OLEDの陰極の電位が外周部に形成される画素の有機EL素子OLEDの陰極の電位に比べて高くなってしまう場合がある。この結果、表示パネル部の中央部と外周部とで表示ムラが生じる。

#### 【0005】

そこで、表示パネル部の陽極側である基板上に導電性の突起部を設け、その突起部を有機EL素子の陰極に接続された透明導電性薄膜に接続するようにした構造を備えた表示ディスプレイが知られている(例えば、特許文献1参照)。このようにすることで、有機EL素子OLEDの陰極の電位が、各画素を形成される位置によって差が生じるのを抑制することができる。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

#### 【特許文献1】特開2000-36391号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、前記したような導電性の突起部を形成することは技術的に困難である。本発明は上記問題点を解消するためになされたものであって、表示ムラの発生を抑制することで表示品位を向上するようにした電気光学装置、電気光学装置の製造方法及び電子機器を提供することにある。

30

#### 【課題を解決するための手段】

#### 【0008】

本発明の電気光学装置は、基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備え、前記陽極は前記発光性材料が設けられる画素毎に形成された電気光学装置において、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部とを備えている。

40

#### 【0009】

これによれば、接続部を介して前記陰極と前記導電層と電気的に接続した。従って、前記陰極が、例えば、スズドープ酸化インジウム(ITO)といった比較的抵抗率が高い透明導電性薄膜であっても前記陰極の電位が画素毎で異なることはない。この結果、画素が形成される位置によって表示ムラが発生するのを抑制することができる。このことから、表示品位が優れた電気光学装置を提供することができる。

#### 【0010】

この電気光学装置において、前記接続部は前記画素毎に備えられていてよい。

これによれば、形成される位置によって表示ムラが発生するのを画素毎に確実に抑制することができる。

50

【 0 0 1 1 】

この電気光学装置において、前記接続部はコンタクトホールで構成されていてもよい。これによれば、前記接続部を容易に形成することができる。

【 0 0 1 2 】

この電気光学装置において、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層を備え、前記素子形成層と前記導電層との間に前記素子形成層と前記導電層とを電気的に切断するための絶縁層が形成されていてよい。

【 0 0 1 3 】

これによれば、前記導電層の上方に前記能動素子を形成した電気光学装置において、画素が形成される位置によって表示ムラが発生するのを抑制することができる。

【 0 0 1 4 】

この電気光学装置において、前記絶縁層は、その誘電率を としたとき、膜厚が 2 / 3.5  $\mu$ m 以上であってもよい。

これによれば、絶縁層を、その膜厚が  $2 / 3.5 \mu\text{m}$  以上になるように形成した。従って、絶縁層上に形成される前記能動素子に前記導電層を構成する材料が拡散するのを確実に防止することができる。また、前記導電層と前記能動素子の間に形成される寄生容量を低減し、駆動回路を安定動作させることができ、それによって電気光学装置の表示品質を向上させることができる。

【 0 0 1 5 】

この電気光学装置において、前記導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、バナジウム (V)、ジルコニウム (Zr)、及びこれらの合金またはシリサイドのうちの一つで構成されていてもよい。

これによれば、導電層を容易に形成することができる。

【 0 0 1 6 】

この電気光学装置において、前記導電層は少なくとも一層の金属層を含む複数の導電層から構成されていてもよい。

【 0 0 1 7 】

これによれば、例えば、導電層のうち他の層に接して形成される導電層を、該導電層が構成される材料が拡散されにくいもので構成することで前記他の層の物性を変化させないようにすることができる。

[ 0 0 1 8 ]

この電気光学装置において、前記基板上に該基板を保護する下地保護層を備え、その下地保護層は二酸化珪素で構成され、前記複数の導電層は前記下地保護層上から順に第1導電層、第2導電層から構成される導電層であって、前記第1導電層はチタン(Ti)、タンタル(Ta)、タンクスチル(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成され、前記第2導電層はアルミニウム(Al)、ニッケル(Ni)及び白金(Pt)、及びこれらの合金またはシリサイドのいずれか一つで構成されていてもよい。

これによれば、前記保護層との密着性に優れ且つ導電率の低い導電層を備えた電気光学装置を提供することができる。

【 0 0 1 9 】

か一つで構成されていてもよい。

【0020】

これによれば、チタン(Ti)で第1導電層を構成した。従って、第1導電層を下地保護層に密着して形成することができる。また、銅(Cu)で第2導電層を構成した。従って、導電層の導電率を高くすることができます。さらに、窒化チタン(TiN)で第3導電層を構成した。従って、第2導電層を構成する銅(Cu)と第3導電層上に形成される層を構成する材料とが反応して、その結果、第2導電層の導電率が低下するのを防止することができる。

【0021】

この電気光学装置において、前記導電層は前記基板から突出して形成された突出部を備えていてもよい。

これによれば、突出された導電層を各種外部装置と直接接続することで特別なインターフェースといった接続手段を設けることなく前記各陰極の電位を直接制御することができる。

【0022】

本発明の電気光学装置の製造方法は、基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備えるとともに、前記発光性材料を画素毎に区分けするためのバンク層と、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部と、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層とを備えた電気光学装置の製造方法において、前記基板の上方に前記導電層を形成する工程と、前記導電層の上方に前記絶縁層、前記素子形成層、前記陽極及びバンク層を形成する工程と、前記絶縁層に開口パターンを形成するのと同時に前記陰極と前記導電層とを電気的に接続するための接続部開口パターンを形成する工程と、前記発光性材料を形成する工程と、前記接続部を含む前記発光性材料を形成した領域の全面に透明性導電膜を形成する工程とを備えた。

【0023】

これによれば、前記陰極が、例えば、スズドープ酸化インジウム(ITO)といった比較的の抵抗率が高い透明導電性薄膜であっても画素が形成される位置によって表示ムラが発生するのを抑制することができる電気光学装置を製造することができる。また、4層から6層ある絶縁層に開口部(コンタクトホール、画素発光領域など)を形成するのと同時に、前記陰極と前記導電層とを電気的に接続する接続部(コンタクトホール)を形成できるので、工程を変更せずに高品質な電気光学装置を製造することができる。

【0024】

この電気光学装置の製造方法において、前記導電層は第1導電層、第2導電層及び第3導電層から構成される導電層を備え、前記素子形成層は前記能動素子に信号を供給するための第1の信号線と第2の信号線とを備え、前記第1導電層は前記第1の信号線を形成すると同時に形成され、前記第2導電層は前記第2の信号線を形成すると同時に形成されていてもよい。

これによれば、前記接続部を容易に形成することができる。

【0025】

この電気光学装置の製造方法において、前記導電層はスパッタ法で形成するようにしてよい。

【0026】

これによれば、蒸着法といった他の方法で形成する場合と比較して前記導電層の成膜温度を低くすることができる。この結果、基板等に欠陥等が生じるのを防止することができる。

【0027】

本発明の電子機器は、上記電気光学装置を備えている。

10

20

30

40

50

これによれば、陰極が、例えば、スズドープ酸化インジウム(ITO)といった比較的抵抗率が高い透明導電性薄膜であっても表示品位が優れた電子機器を提供することができる。

【図面の簡単な説明】

【0028】

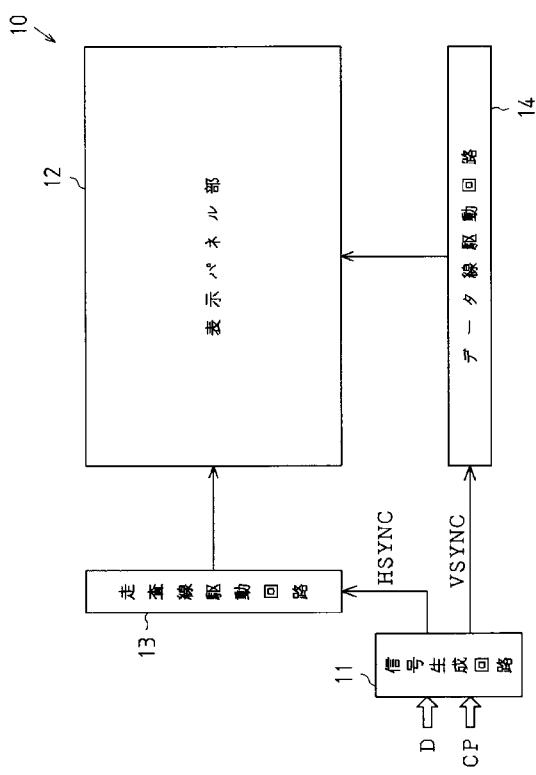

【図1】有機ELディスプレイの電気的構成を説明するためのブロック図である。

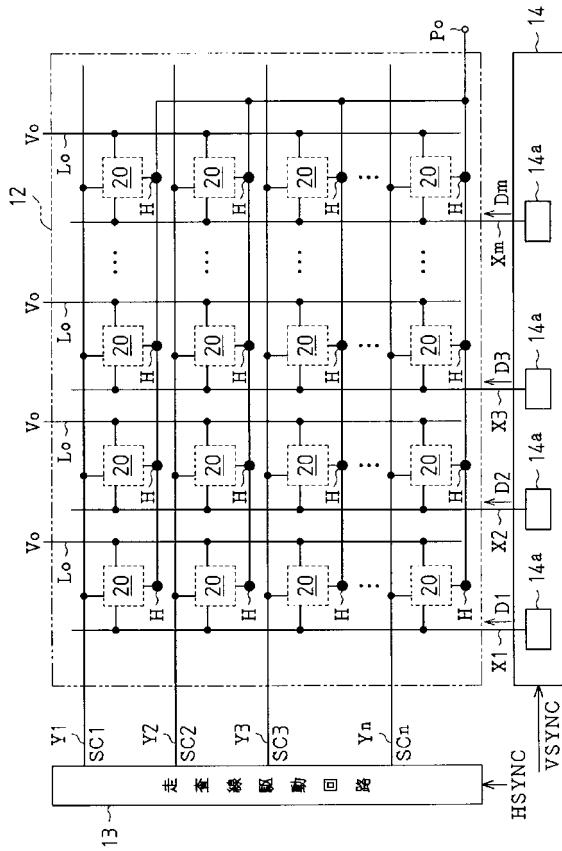

【図2】表示パネル部及びデータ線駆動回路の電気的構成を示す回路図である。

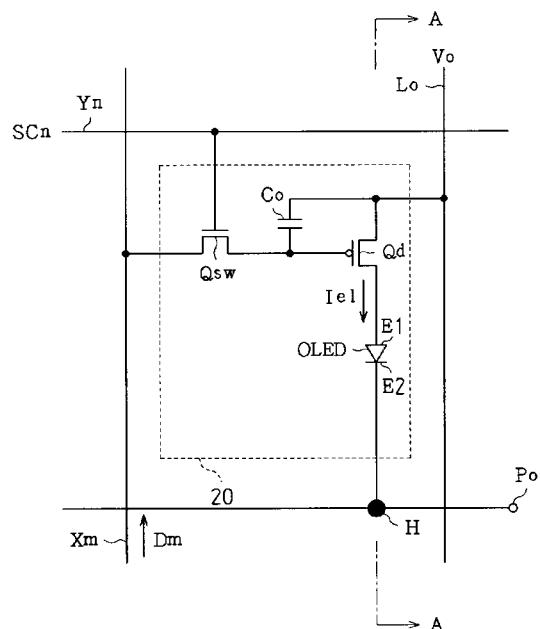

【図3】画素の回路図である。

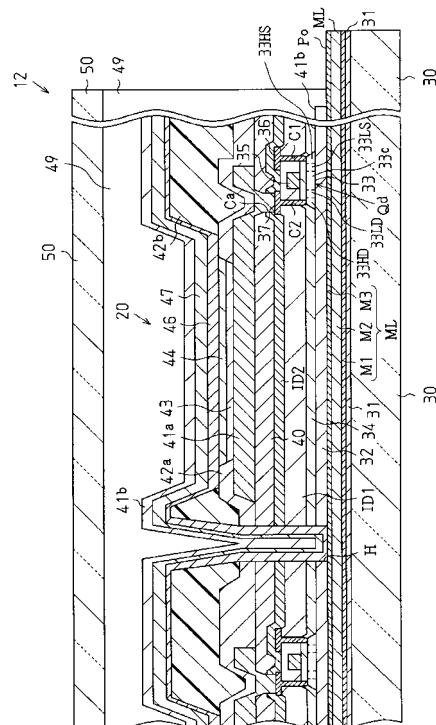

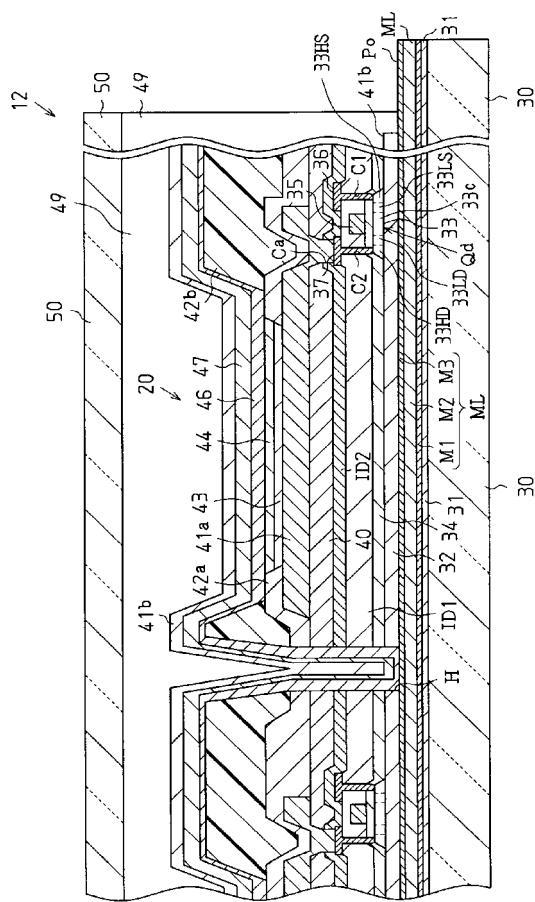

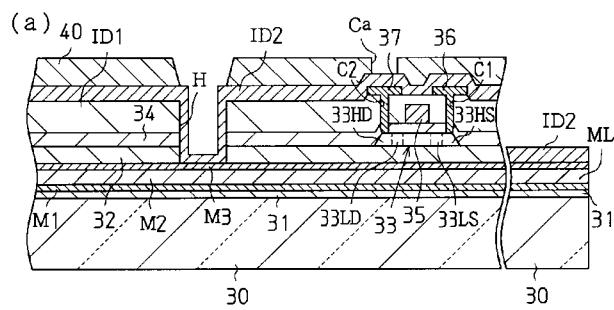

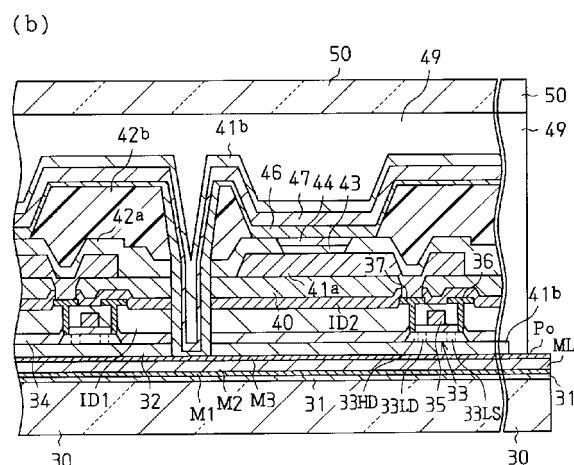

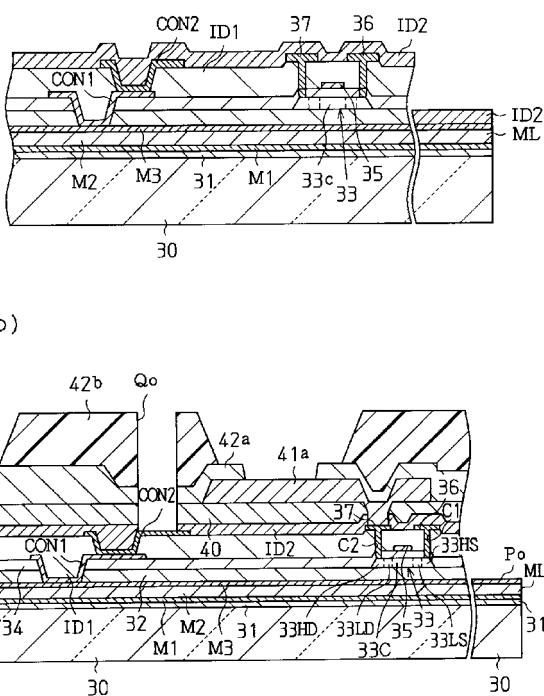

【図4】第1実施形態における表示パネル部の一部断面図である。

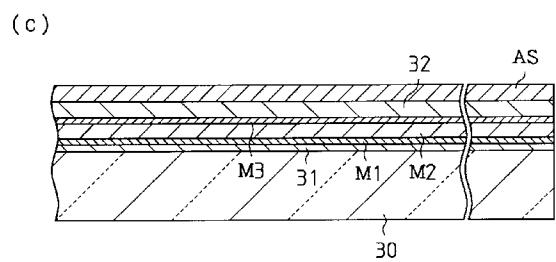

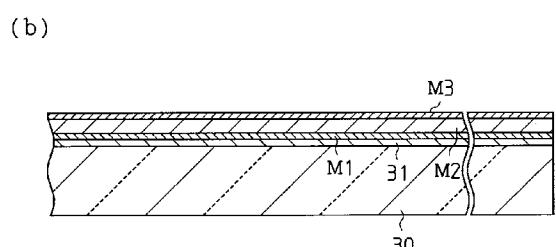

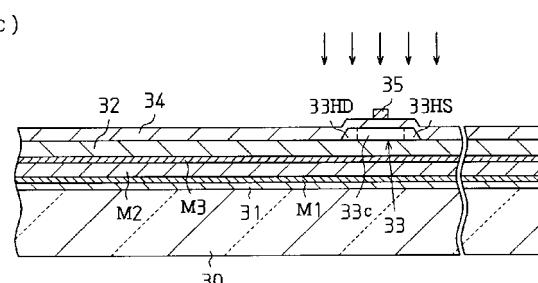

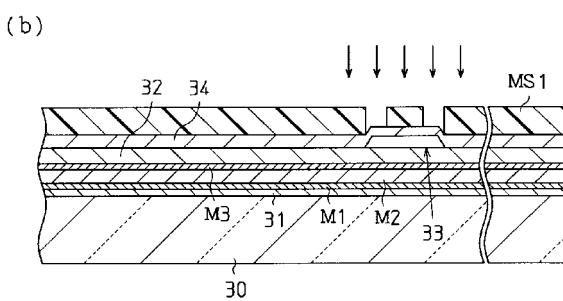

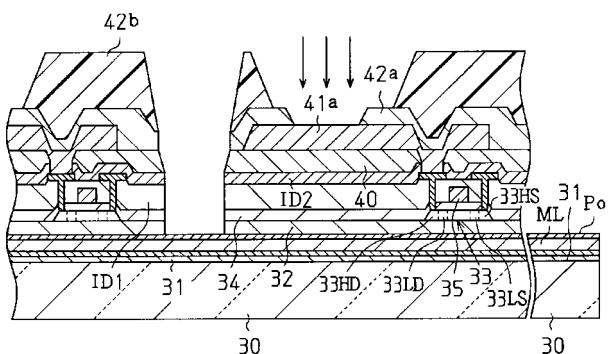

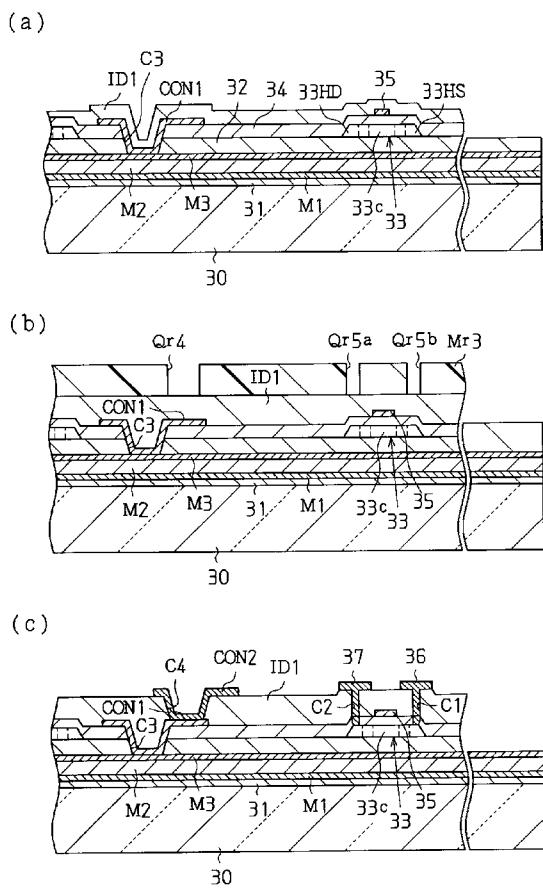

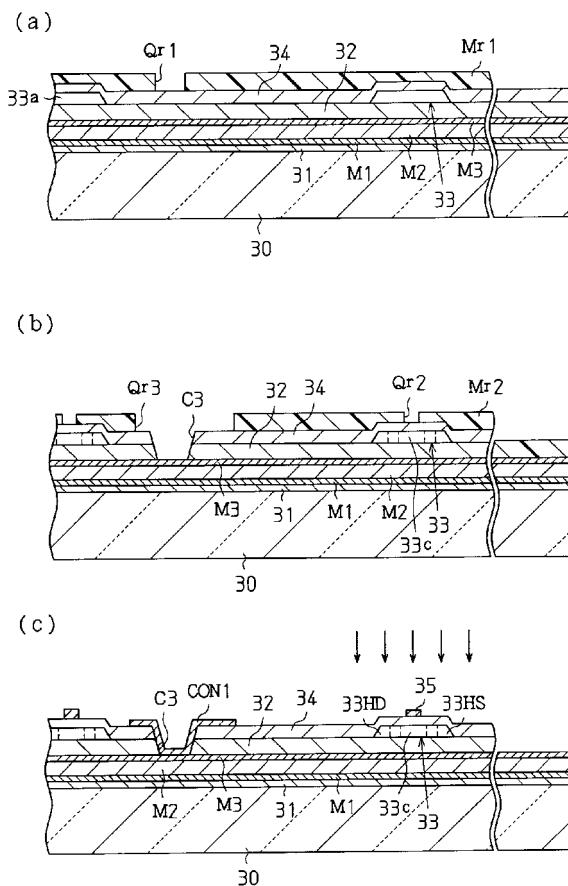

【図5】(a), (b), (c)は、第1実施形態の表示パネル部の製造方法を説明するための図である。 10

【図6】(a), (b), (c)は、第1実施形態の表示パネル部の製造方法を説明するための図である。

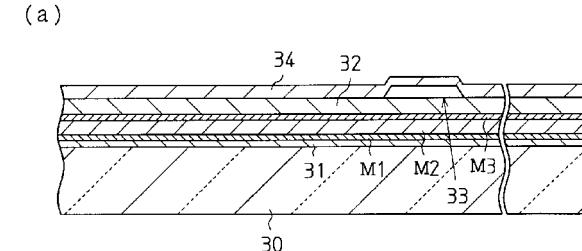

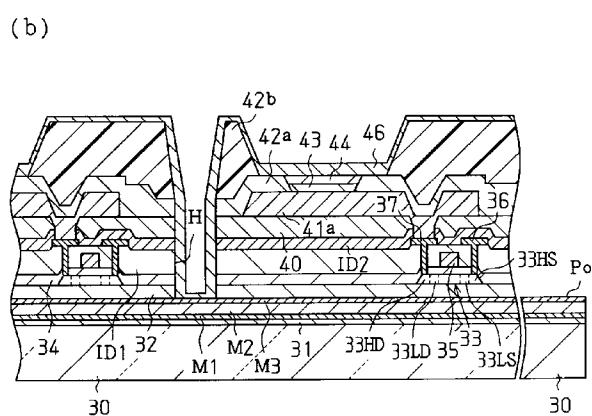

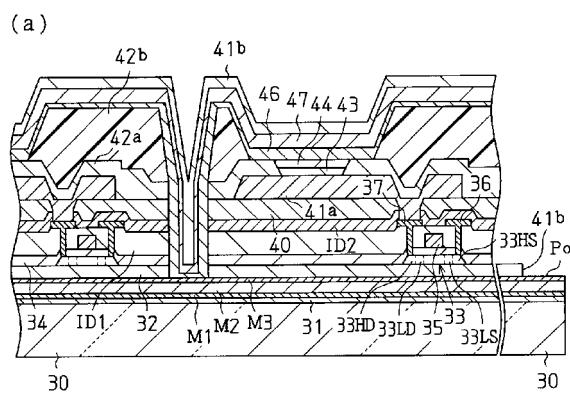

【図7】(a), (b)は、第1実施形態の表示パネル部の製造方法を説明するための図である。

【図8】第1実施形態の表示パネル部の製造方法を説明するための図である。

【図9】(a), (b)は、第1実施形態の表示パネル部の製造方法を説明するための図である。

【図10】(a), (b)は、第1実施形態の表示パネル部の製造方法を説明するための図である。 20

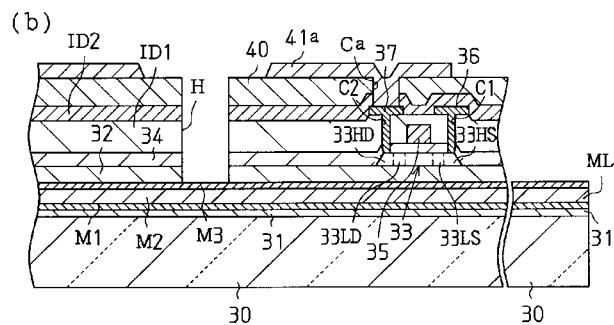

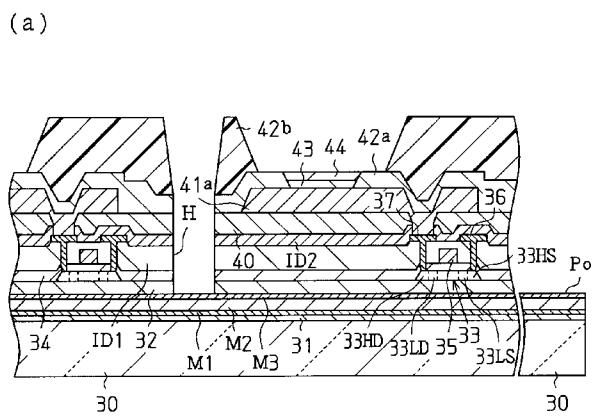

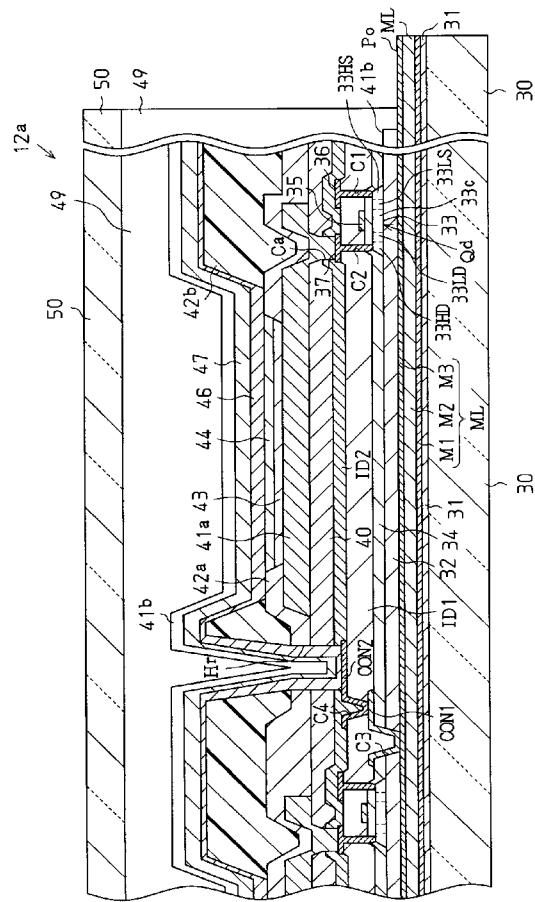

【図11】第2実施形態における表示パネル部の一部断面図である。

【図12】(a), (b), (c)は、第2実施形態の表示パネル部の製造方法を説明するための図である。

【図13】(a), (b), (c)は、第2実施形態の表示パネル部の製造方法を説明するための図である。

【図14】(a), (b)は、第2実施形態の表示パネル部の製造方法を説明するための図である。

【図15】第3の実施形態を説明するためのモバイル型パーソナルコンピュータの構成を示す斜視図である。

【発明を実施するための形態】

【0029】

以下、本発明を液晶表示装置に適用した各実施形態を図面に基づいて説明する。また、各実施形態は、本発明の一態様を示すものであり、この発明を限定するものではなく、本発明の技術思想の範囲内で任意に変更可能である。さらに、以下に示す各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材ごとに縮尺を異らせてある。

(第1実施形態)

本発明を具体化した第1実施形態を図1～図10に従って説明する。図1は、有機ELディスプレイの電気的構成を説明するためのブロック図である。図2は、表示パネル部及びデータ線駆動回路の電気的構成を示す回路図である。図3は、本実施形態における画素の回路図である。また、図4は本実施形態における表示パネル部の一部断面図である。 40

【0030】

図1に示すように、有機ELディスプレイ10は、信号生成回路11、表示パネル部12、走査線駆動回路13及びデータ線駆動回路14を備えている。有機ELディスプレイ10の信号生成回路11、走査線駆動回路13及びデータ線駆動回路14は、それぞれが独立した電子部品によって構成されていてもよい。例えば、信号生成回路11、走査線駆動回路13及びデータ線駆動回路14が、各々1チップの半導体集積回路装置によって構成されていてもよい。また、信号生成回路11、走査線駆動回路13及びデータ線駆動回路14の全部若しくは一部がプログラマブルなICチップで構成され、その機能がICチップに書き込まれたプログラムによりソフトウェア的に実現されてもよい。 50

## 【0031】

信号生成回路11は、図示しない外部装置から供給されるクロックパルスCP及び画像デジタルデータDを入力する。信号生成回路11は、クロックパルスCPに基づいて水平同期信号HSYNC及び垂直同期信号VSYNCを作成する。

また、信号生成回路11は、その作成した水平同期信号HSYNCを走査線駆動回路13に出力するとともに、前記垂直同期信号VSYNCをデータ線駆動回路14に出力する。さらに、信号生成回路11は、画像デジタルデータDをデータ線駆動回路14に出力する。

## 【0032】

表示パネル部12は、図2に示すように、行方向に沿って延設されるn本の走査線Y1, Y2, …, Ynを備えている。また、表示パネル部12は、列方向に沿って延設されるm本のデータ線X1, X2, …, Xmを備えている。走査線Y1, Y2, …, Ynは同表示パネル部12の図中上部側から下部側に向かって第1の走査線Y1、第2の走査線Y2、…、第nの走査線Ynの順に備えられている。そして、前記各走査線Y1, Y2, …, Ynと前記各データ線X1, X2, …, Xmとの交差部に対応した各位置には画素20が形成されている。

10

## 【0033】

さらに、表示パネル部12は、前記各データ線X1, X2, …, Xmに並行して延設されるm本の電源線Loを備えている。全ての電源線Loには電源電圧Voが供給されている。

20

## 【0034】

各画素20は、対応する走査線Y1, Y2, …, Ynを介して走査線駆動回路13に接続されている。また、各画素20は、対応するデータ線X1, X2, …, Xmを介してデータ線駆動回路14に接続されている。さらに、各画素20は、電源線Loに接続されている。

## 【0035】

画素20は、その各々が図3に示すように、駆動トランジスタQd、スイッチングトランジスタQsw、保持キャパシタCo及び有機EL素子OLEDを備えている。尚、図3は、n番目の走査線Ynとm番目のデータ線Xmとの交差部に対応する位置に形成された画素20の等価回路図である。各画素20の電気的構成は全て同じであるので、説明の便宜上、以下、n番目の走査線Ynとm番目のデータ線Xmとの交差部に対応する位置に形成された画素20についてのみについて説明し、他の画素20についてはその説明を省略する。

30

## 【0036】

駆動トランジスタQdは、通常はTFT(薄膜トランジスタ)で構成されている。また、駆動トランジスタQdは本実施形態ではその導電型がP型である。スイッチングトランジスタQswは本実施形態ではその導電型がN型である。

## 【0037】

スイッチングトランジスタQswは、そのソースがデータ線Xmに接続されている。スイッチングトランジスタQswのゲートは走査線Ynに接続されている。スイッチングトランジスタQswのドレインは、駆動トランジスタQdのゲートに接続されている。駆動トランジスタQdのゲート/ソース間に保持キャパシタCoが接続されている。また、駆動トランジスタQdのソースは電源線Loに接続されている。駆動トランジスタQdのドレインは有機EL素子OLEDの陽極E1に接続されている。

40

## 【0038】

上記のように構成された画素20は、その有機EL素子OLEDの陰極E2がコンタクトホールHを介して他の有機EL素子と共に陰極に電気的に接続されている。また、前記陰極E2は図示しない外部装置に接続するための接続ポートPoに接続されている。

## 【0039】

走査線駆動回路13は、走査信号SC1, SC2, …, SCnを作成する。各走査信号

50

S C 1 , S C 2 , … , S C n は L レベル及び H レベルを有する電圧信号である。また、走査線駆動回路 1 3 は前記水平同期信号 H S Y N C に従って、H レベルの走査信号を各走査線 Y 1 , Y 2 , … , Y n に出力することで順次走査線 Y 1 , Y 2 , … , Y n を選択駆動する。

【 0 0 4 0 】

データ線駆動回路 1 4 は、図 2 に示すように複数の単一ラインドライバ 1 4 a を備えている。複数の単一ラインドライバ 1 4 a の各々は対応するデータ線 X 1 , X 2 , … , X m に接続されている。また、各単一ラインドライバ 1 4 a は、前記信号生成回路 1 1 から出力された画像デジタルデータ D を入力する。そして、各単一ラインドライバ 1 4 a は、入力された画像デジタルデータ D の大きさに対応したレベルのアナログ電圧信号であるデータ信号 D 1 , D 2 , … , D m を作成する。そして、単一ラインドライバ 1 4 a は、前記信号生成回路 1 1 から出力された垂直同期信号 V S Y N C に従って前記データ信号 D 1 , D 2 , … , D m を対応するデータ線 X 1 , X 2 , … , X m を介して各画素 2 0 に一斉に出力する。

【 0 0 4 1 】

そして、前記走査線駆動回路 1 3 が水平同期信号 H S Y N C に従って走査線 Y 1 , Y 2 , … , Y n のうちの一本の走査線に H レベルの走査信号を出力すると、その走査線に接続された一行分の全ての画素 2 0 の各スイッチングトランジスタ Q s w がオンになる。このとき、前記データ線駆動回路 1 4 の各単一ラインドライバ 1 4 a から対応するデータ線 X 1 , X 2 , … , X m を介してデータ信号 D 1 , D 2 , … , D m が一斉に出力される。すると、前記スイッチングトランジスタ Q s w がオンになった前記一行分の全ての画素 2 0 の各保持キャパシタ C o にデータ信号が供給される。この結果、前記各画素 2 0 は、このデータ信号に応じて同画素 2 0 の内部状態（保持キャパシタ C o の電荷量）が設定され、これに応じて駆動トランジスタ Q d の導電率が制御される。この結果、その導電率に応じたレベルの駆動電流 I e 1 が有機 E L 素子 O L E D に供給され、有機 E L 素子 O L E D が同駆動電流 I e 1 の電流レベルに応じた輝度で発光する。

【 0 0 4 2 】

以降、各走査線 Y 1 , Y 2 , … , Y n が順次選択されることで各画素 2 0 にデータ信号 D 1 , D 2 , … , D m が供給され、各有機 E L 素子 O L E D が駆動電流 I e 1 の電流レベルに応じた輝度で発光する。このようにすることで表示パネル部 1 2 上にデータ信号 D 1 , D 2 , … , D m に応じた画像が表示される。

【 0 0 4 3 】

次に、表示パネル部 1 2 の構造について図 4 に従って説明する。図 4 は駆動トランジスタ Q d と有機 E L 素子 O L E D とを含む表示パネル部 1 2 の一部断面図である。図 4 に示す断面図は、図 3 中の A - A 線に沿う断面に対応している。

【 0 0 4 4 】

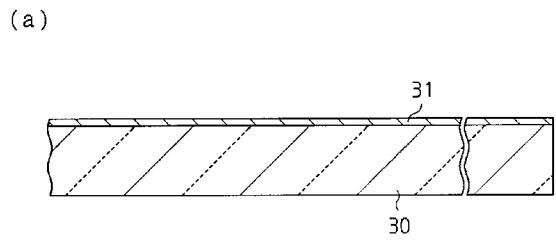

図 4 に示すように、ガラス基板 3 0 上には二酸化珪素 ( S i O<sub>2</sub> ) で構成された下地保護層 3 1 が形成されている。下地保護層 3 1 上には第 1 導電層 M 1 が前記ガラス基板 3 0 のほぼ全面に形成されている。第 1 導電層 M 1 は導電率が高く且つ下地保護層 3 1 との密着性に優れた材料で構成されている。本実施形態の第 1 導電層 M 1 は、二酸化珪素 ( S i O<sub>2</sub> ) との密着性に優れた金属であるチタン ( T i ) で構成されている。また、第 1 導電層 M 1 上には第 2 導電層 M 2 が形成されている。

【 0 0 4 5 】

第 2 導電層 M 2 は、導電率が高い材料で構成されている。本実施形態の第 2 導電層 M 2 は銅 ( C u ) で構成されている。また、第 2 導電層 M 2 上には第 3 導電層 M 3 が形成されている。

【 0 0 4 6 】

第 3 導電層 M 3 は、導電率が高く且つ前記第 2 導電層 M 2 を構成する材料が第 3 導電層 M 3 上に形成される下地絶縁膜 3 2 に拡散するのを抑制する材料で構成されている。第 3 導電層 M 3 を第 2 導電層 M 2 と下地絶縁膜 3 2 との間に形成することで、第 2 導電層 M 2

を構成する材料と下地絶縁膜32を構成する材料とが反応して、その結果、第2導電層M2の物性が変化してその導電率が低下する若しくは下地絶縁膜32の絶縁性が低下するのを防止することができる。本実施形態の第3導電層M3は、二酸化珪素(SiO<sub>2</sub>)に拡散しにくい金属である窒化チタン(TiN)で構成されている。そして、本実施形態では前記第1～第3導電層M1, M2, M3で導電層MLが構成されている。

#### 【0047】

また、この導電層MLは、その一端(図中右側)が外方に突出されている。この突出した部分の導電層MLが前記接続ポートPoに対応している。

前記第3導電層M3上にはコンタクトホールHが形成される位置を除いて第3導電層M3と該第3導電層M3上に形成される駆動トランジスタQdを構成する後記するシリコン層33、データ線X1, X2, …, Xm及び走査線Y1, Y2, …, Yn等とを電気的に絶縁するための下地絶縁膜32が形成されている。この下地絶縁膜32は、その膜厚が2

10 /3.5 μm以上になるように形成されている。ここで、32は下地絶縁膜32を構成する材料の誘電率である。このように膜厚を2 /3.5 μm以上にすることで、下地絶縁膜32上に形成されるシリコン層33、データ線X1, X2, …, Xm及び走査線Y1, Y2, …, Yn等に導電層MLを構成する材料が拡散するのを確実に防止することができる。また、導電層MLと、シリコン層33、データ線X1、X2、…、Xm及び走査線Y1, Y2, …, Ynの間に生じる寄生容量を低減し、駆動回路を安定して動作させ、表示品質を向上させることができる。尚、本実施形態においては下地絶縁膜32は二酸化珪素(SiO<sub>2</sub>)で構成されているが、窒化珪素や酸化窒化珪素やその他の材料でも良い。

#### 【0048】

下地絶縁膜32上にはその所定の位置に多結晶シリコンで構成された島状のシリコン層33が形成されている。シリコン層33及び下地絶縁膜32上には、二酸化珪素(SiO<sub>2</sub>)または窒化珪素(SiN)で構成されたゲート絶縁膜34が形成されている。また、シリコン層33上には、前記ゲート絶縁膜34を介してゲート電極35が形成されている。

#### 【0049】

ゲート絶縁膜34を介してゲート電極35と対向するシリコン層33の領域がチャネル領域33Cである。シリコン層33のうち、チャネル領域33Cの図中左側には低濃度ドレイン領域33LD及び高濃度ドレイン領域33HDが形成されている。一方、シリコン層33のうち、チャネル領域33Cの図中右側には低濃度ソース領域33LS及び高濃度ソース領域33HSが形成されている。

#### 【0050】

また、前記ゲート電極35及びゲート絶縁膜34上には二酸化珪素(SiO<sub>2</sub>)で構成された第1層間絶縁膜ID1が形成されている。この第1層間絶縁膜ID1上には前記シリコン層33の高濃度ソース領域33HS及び高濃度ドレイン領域33HDに対向する位置にそれぞれソース電極36及びドレイン電極37が形成されている。ゲート絶縁膜34及び第1層間絶縁膜ID1には、双方を貫通して開孔された第1及び第2電極用コンタクトホールC1, C2が形成されている。そして、この第1及び第2電極用コンタクトホールC1, C2に銅(Cu)やアルミニウム(Al)といった導電性材料が埋め込まれている。従って、ソース電極36は第1電極用コンタクトホールC1を介して前記シリコン層33の高濃度ソース領域33HSに電気的に接続されている。また、ドレイン電極37は第2電極用コンタクトホールC2を介して前記シリコン層33の高濃度ドレイン領域33HDに電気的に接続されている。

#### 【0051】

そして、シリコン層33、ゲート電極35、ソース電極36及びドレイン電極37で駆動トランジスタQdが構成されている。

前記第1層間絶縁膜ID1上には、二酸化珪素(SiO<sub>2</sub>)で形成された第2層間絶縁膜ID2が形成されている。第2層間絶縁膜ID2上には平坦化絶縁膜40が形成されている。

10

20

30

40

50

## 【0052】

平坦化絶縁膜40は、有機材料で構成された絶縁性材料で構成されている。平坦化絶縁膜40は、本実施形態では感光性ポリイミドで形成されている。また、この平坦化絶縁膜40は、本実施形態ではその膜厚が2000nmになるように形成されている。この平坦化絶縁膜40を形成することで、同平坦化絶縁膜40上に形成される発光層44を平坦化することができる。また、平坦化絶縁膜40上には導電性材料で構成された第1の電極層41aと無機材料で構成された第1バンク層42aとが形成されている。

## 【0053】

第1の電極層41aは前記有機EL素子OLEDの陽極E1に対応する電極層である。尚、本実施形態では第1の電極層41aはクロム(Cr)で構成されている。また、この第1の電極層41aは前記ドレイン電極37に対向する位置に前記平坦化絶縁膜40及び第2層間絶縁膜ID2をそれぞれ開孔して形成された陽極用コンタクトホールCaを介して、前記ドレイン電極37と電気的に接続されている。この陽極用コンタクトホールCaには前記第1の電極層41aを構成する導電性材料と同じ材料が埋め込まれている。従って、ドレイン電極37は陽極用コンタクトホールCaを介して前記第1の電極層41aに電気的に接続される。また、第1の電極層41a上には正孔注入層43と光を放射する有機材料で構成された発光層44とが積層して形成されている。

10

## 【0054】

第1バンク層42aは正孔注入層43及び発光層44と該正孔注入層43及び発光層44に隣接して形成される正孔注入層及び発光層の間とを区画する。第1バンク層42aは親水性であって且つ絶縁性の材料で構成されている。第1バンク層42aはSiO<sub>2</sub>、TiO<sub>2</sub>、SiN等の無機材料で構成される。また、この第1バンク層42aは、第1の電極層41aの周縁部上に乗上げて形成されている。第1バンク層42a上には、第2バンク層42bが形成されている。

20

## 【0055】

第2バンク層42bは、前記第1バンク層42aと同様に、正孔注入層43及び発光層44と該正孔注入層43及び発光層44に隣接して形成される正孔注入層及び発光層の間とを区画する。そして、この第1及び第2バンク層42a, 42bで区画された領域が1つの画素20に対応する。また、第2バンク層42bにはコンタクトホールHが設けられている。このコンタクトホールHは、第1及び第2バンク層42a, 42b、平坦化絶縁膜40、第1及び第2層間絶縁膜ID1, ID2、ゲート絶縁膜34及び下地絶縁膜32をそれぞれ貫通して形成されている。従って、本実施形態のコンタクトホールHは前記導電層MLを構成する第3導電層M3に至るまで連続して開孔されている。

30

## 【0056】

発光層44、第1バンク層42a及び第2バンク層42b、及び、コンタクトホールHの全面に渡って電子注入層46が形成されている。この電子注入層46は透明な材料で形成されている。電子注入層46上には透明な材料で構成された透明導電層47が形成されている。透明導電層47は前記した有機EL素子OLEDの陰極E2に対応する電極層である。従って、前記透明導電層47(有機EL素子OLEDの陰極E2)は、電子注入層46を介して前記導電層MLを構成する第3導電層M3に電気的に接続されている。

40

## 【0057】

尚、この透明導電層47は、本実施形態においては、スズドープ酸化インジウム(ITO)で構成されている。そして、第1の電極層41aと、透明導電層47と、該第1の電極層41aと透明導電層47とに挟まれた位置に形成された前記正孔注入層43、発光層44、及び電子注入層46とで前記有機EL素子OLEDを構成している。

## 【0058】

透明導電層47上には透明な材料で構成された薄膜封止層41bが形成されている。この薄膜封止層41bは酸化珪素、窒化珪素、酸化窒化珪素などの透明な無機材料から形成されていて、空気中の水分や酸素の影響を遮断し、有機EL素子OLEDの特性が劣化するのを防止する。また、前記薄膜封止層41b上には、透明な接着剤49を介して透明な

50

ガラスで構成された封止基板 50 が形成されている。

【0059】

そして、表示パネル部 12 は前記ガラス基板 30 に対向した封止基板 50 から前記発光層 44 にて発せられた光が出射される、所謂、トップエミッションタイプの有機 EL ディスプレイである。

【0060】

このように構成された表示パネル部 12 は、各画素 20 に形成される有機 EL 素子 OLE D の陰極 E2 が全てコンタクトホール H を介して導電層 M L に電気的に接続されている。この導電層 M L は、前記したように導電率が高い第 1 、第 2 及び第 3 導電層 M1 , M2 , M3 が積層されることで構成されている。従って、各画素 20 に形成される有機 EL 素子 OLE D の陰極 E2 の電位は全て前記導電層 M L の電位と等しい値になる。この結果、表示パネル部 12 上に形成される位置によって有機 EL 素子 OLE D の陰極 E2 の電位に差が生じることはない。つまり、例えば、全ての画素 20 に同じ電圧レベルのデータ信号 D1 , D2 , … , Dm を供給したとき、画素 20 が形成される位置によって有機 EL 素子 OLE D の輝度に差が生じることはないので、その分、表示ムラを低減させることができる。

10

【0061】

従って、たとえば、陰極 E2 をスズドープ酸化インジウム (ITO) といった比較的導電率が低い（抵抗率が比較的高い）透明材料で構成されたトップエミッションタイプの有機 EL ディスプレイであっても、データ信号 D1 , D2 , … , Dm に応じた画像を精度良く表示させることができる。

20

【0062】

また、従来は表示領域の外辺部・外周部に形成していた陰極 E2 との接続エリアを省略することができ、表示装置の狭額縫化を実現できる。

また、前記導電層 M L はその一端が表示パネル部 12 から直接外方に突出されている。そして、その突出された導電層 M L を接続ポート Po として使用するようにした。従って、前記接続ポート Po に各種外部装置を接続することで特別なインターフェースといった接続手段を設けることなく有機 EL 素子 OLE D の各陰極 E2 の電位を直接制御することができる。

30

【0063】

次に、本実施形態の有機 EL ディスプレイ 10 の製造方法を図 5 ~ 図 10 に従って説明する。図 5 ~ 図 10 は、図 3 に示した画素 20 を含む表示パネル部 12 の断面図である。

【0064】

図 5 (a) に示すように、まず、ガラス基板 30 上に、プラズマ CVD 法を用いて二酸化珪素 (SiO<sub>2</sub>) で構成された下地保護層 31 を形成する。その後、スパッタ法を用いて前記ガラス基板 30 の図中左端部を除いたほぼ全面に渡ってチタン (Ti) / 銅 (Cu) / 窒化チタン (TiN) の薄膜を順次形成する（図 5 (b) 参照）。本実施形態では、チタン (Ti) で構成された薄膜の膜厚が 100 nm 、銅 (Cu) で構成された薄膜の膜厚が 500 nm 、窒化チタン (TiN) で構成された薄膜の膜厚が 100 nm である。そして、チタン (Ti) で構成された前記薄膜が前記第 1 導電層 M1 に対応し、銅 (Cu) で構成された前記薄膜が前記第 2 導電層 M2 に対応し、窒化チタン (TiN) で構成された前記薄膜が前記第 3 導電層 M3 に対応する。そして、このように第 1 ~ 第 3 導電層 M1 , M2 , M3 をそれぞれスパッタ法を用いて形成することで蒸着法といった他の方法で形成する場合と比較してその成膜温度を低くすることができる。この結果、ガラス基板 30 や下地保護層 31 に加熱による欠陥等が生じるのを防止することができる。

40

【0065】

続いて、図 5 (c) に示すように、前記第 3 導電層 M3 上に CVD 法等を用いて二酸化珪素 (SiO<sub>2</sub>) を積層することで下地絶縁膜 32 を形成する。このとき、下地絶縁膜 32 の膜厚が 2 / 3 . 5 μm 以上になるように形成する。その後、プラズマ CVD 法等を用いて前記アモルファスシリコン層 AS を形成した後、レーザアニール法又は急速加熱法

50

により結晶粒を成長させて多結晶シリコンを形成する。そして、図6(a)に示すように、その多結晶シリコンをフォトリソグラフィ法によりパターニングして島状のシリコン層33を形成する。続いて、シリコン層33及び下地絶縁膜32上に二酸化珪素(SiO<sub>2</sub>)で構成された膜厚約30nm~200nmのゲート絶縁膜34を形成する。このゲート絶縁膜34の形成は、プラズマCVD法、熱酸化法等により行う。

#### 【0066】

次に、図6(b)に示すように、ゲート絶縁膜34上にイオン注入選択マスクMS1を形成し、この状態でリンイオン(P)を約 $1 \times 10^{15} \text{ cm}^{-2}$ のドーズ量でイオン注入する。その結果、シリコン層33中に高濃度ソース領域33HS及び高濃度ドレイン領域33HDがそれぞれ形成される。

10

#### 【0067】

次に、前記イオン注入選択マスクMS1をアッシングして除去した後に、ゲート絶縁膜34上に膜厚約500nm程度のアルミニウム(A1)膜を形成する。

その後、前記アルミニウム(A1)膜をパターニングすることにより、図6(c)に示すゲート電極35を形成する。このゲート電極35は、前記駆動トランジスタQdのゲートに対応する。

#### 【0068】

続いて、前記ゲート電極35をマスクとし、前記シリコン層33に対してリンイオン(P)を約 $4 \times 10^{13} \text{ cm}^{-2}$ のドーズ量でイオン注入する。その結果、図7(a)に示すように、シリコン層33中に低濃度ソース領域33LS及び低濃度ドレイン領域33LDが形成される。

20

#### 【0069】

次に、ゲート絶縁膜34及びゲート電極35上の全面に渡って二酸化珪素(SiO<sub>2</sub>)で構成された第1層間絶縁膜ID1を形成する。続いて、フォトリソグラフィ法及びエッチングによって、図7(a)に示すように、駆動トランジスタQdのソース電極36に対応する位置に第1電極用コンタクトホールC1を、ドレイン電極37に対応する位置に第2電極用コンタクトホールC2を、それぞれ形成する。そして、前記第1層間絶縁膜ID1上に、銅(Cu)やアルミニウム(A1)といった導電性材料からなる導電層およびパターン形成することにより、先に形成した第1及び第2電極用コンタクトホールC1, C2に導電性材料を埋め込むとともに、高濃度ソース領域33HSに対応した位置にソース電極36を、高濃度ドレイン領域33HDに対応した位置にドレイン電極37を、それぞれ形成する。ソース電極36及びドレイン電極37はそれぞれその膜厚が約200nmないし800nm程度となるように形成する。また、ドライエッチング処理を施すことで、第1層間絶縁膜ID1、ゲート絶縁膜34、下地絶縁膜32を貫通して開孔したコンタクトホールHを形成する。つまり、このコンタクトホールHは、前記導電層MLを構成する第3導電層M3に至るように形成されている。

30

#### 【0070】

さらに、第1層間絶縁膜ID1、ソース電極36、ドレイン電極37、導電層M(図中右端側)上、及び、コンタクトホールH内にそれぞれ二酸化珪素(SiO<sub>2</sub>)で構成された第2層間絶縁膜ID2を形成する。この第2層間絶縁膜ID2は、その膜厚が約100nm~2μm程度となるように形成されることが望ましい。その後、第2層間絶縁膜ID2上に感光性ポリイミドを塗布、乾燥、露光、現像、焼成する平坦化絶縁膜40を形成する。

40

#### 【0071】

その後、平坦化絶縁膜40をマスクとしてドライエッチングすることで、ドレイン電極37に対応する位置に前記平坦化絶縁膜40及び第1及び第2層間絶縁膜ID1, ID2をそれぞれ開孔した陽極用コンタクトホールCaを形成する。

また、スパッタ法等を用いて前記陽極用コンタクトホールCaにクロム(Cr)を埋め込む。

#### 【0072】

50

その後、図7(b)に示すように、第1層間絶縁膜ID1及び前記陽極用コンタクトホールCaに埋め込まれたクロム(Cr)上の所定の位置にパターニングしてクロム(Cr)で構成された第1の電極層41aを形成する。この結果、第1の電極層41aは前記ドレイン電極37と陽極用コンタクトホールCaを介して電気的に接続される。また、ドライエッティング等を施すことで前記コンタクトホールH内及び前記導電層M(図中右端側)上に形成された第2層間絶縁膜ID2を削除する。

【0073】

次に、図8に示すように、平坦化絶縁膜40及び第1の電極層41a上に、CVD法、スパッタ法、蒸着法等を用いてSiO<sub>2</sub>、TiO<sub>2</sub>、SiN等の無機質膜を形成する。そして、第1の電極層41aの一部が露出する態様にて形成されるように、同無機質膜に開口部をパターニングして第1バンク層42aを形成する。第1バンク層42aは、その膜厚が約50nmとなるように形成されている。

10

【0074】

続いて、その端部を除いた前記第1バンク層42a上に第2バンク層42bが形成される。第2バンク層42bは、アクリル樹脂、ポリイミド樹脂等の通常の感光性樹脂をスピニコーターやスリットコーターなどで基板全面に塗布し、ホットプレートやオーブンなどで乾燥させた後、所定パターンのフォトマスクを通して露光し、現像液で不要部分の樹脂を除去し、200~400で焼成する方法で形成される。ここでは、画素が形成される領域と、導電層MLに達するコンタクトホールHが形成される領域に開口部を形成している。第2バンク層42bはその膜厚が0.1~3.5μmの範囲が好ましく、特に2μm程度がよい。第2バンク層42bはその厚さが0.1μm未満では、正孔注入層43及び発光層44の合計膜厚より第2バンク層42bが薄くなり、発光層44が上部開口部から溢れるおそれがあるので好ましくない。また、膜厚が3.5μmを越えると、上部開口部による段差が大きくなり、第2バンク層42b上に形成される透明導電層47が断線する恐れがある。

20

【0075】

また、図8に示すように、前記導電層MLが外方に突出された領域が形成される。この外方に突出された部分の導電層MLが接続ポートPoになる。このようにして接続ポートPoが形成される。

30

【0076】

その後、第1及び第2バンク層42a, 42bの表面に、親液性を示す領域と、撥液性を示す領域を形成する。本実施例においてはプラズマ処理工程により、各領域を形成するものとしている。具体的には、前記プラズマ処理工程は、第1の電極層41a及び第1バンク層42aを親液性にする親液化工程と、第2バンク層42bを撥液性にする撥液化工程とを少なくとも具備している。

40

【0077】

詳しくは、第1及び第2バンク層42a, 42bを形成したガラス基板30を所定温度(例えば70~80程度)に加熱し、次いで親液化工程として大気圧下で酸素を反応ガスとするプラズマ処理(O<sub>2</sub>プラズマ処理)を行う。続いて、撥液化工程として大気圧下で4フッ化メタンを反応ガスとするプラズマ処理(CF<sub>4</sub>プラズマ処理)を行い、プラズマ処理のために加熱されたガラス基板30を室温まで冷却することで、第1バンク層42aの表面を親液性に、第2バンク層42bの表面を撥液性にする。

40

【0078】

その後、第1の電極層41a上に正孔注入層43及び発光層44をインクジェット法により形成する(図9(a)参照)。詳しくは、発光層44は、正孔注入層43を形成する所定の材料を含む組成物インクを吐出・乾燥した後に、発光層44を形成する所定の材料を含む組成物インクを吐出・乾燥することにより形成される。前記組成物インクは、前記撥液性及び撥液性化によって前記第1及び第2バンク層42a, 42bによって構成される画素20に確実に塗布される。尚、この発光層44の形成工程以降は、正孔注入層43及び発光層44の酸化・吸湿を防止するため、窒素雰囲気又はアルゴン雰囲気といった不

50

活性ガス雰囲気で行なうことが好ましい。

【0079】

続いて、図9(b)に示すように接続ポートPoを除いた発光層44、第1バンク層42a及び第2バンク層42b、及び、コンタクトホールHの全面に渡って電子注入層46を形成する。この電子注入層46は透明な材料であり、加熱蒸着法によって形成する。その後、図10(a)に示すように、電子注入層46上には透明な材料で構成された透明導電層47を、スパッタ法、真空蒸着法、CVD法などの方法によって形成する。この透明導電層47は前記した有機EL素子OLEDの陰極E2を構成する電極層である。従って、透明導電層47(有機EL素子OLEDの陰極E2)は、電子注入層48を介して前記導電層MLを構成する第3導電層M3に電気的に接続されている。

10

【0080】

尚、この透明導電層47は、本実施形態においては、スズドープ酸化インジウム(ITO)で構成されている。

透明導電層47上には、透明な材料で構成された薄膜封止層41bを形成する。本実施形態においては、薄膜封止層41bは酸化窒化珪素( $SiO_xN_y$ )からなり、スパッタ法、CVD法などの既知の適切な方法で形成される。ただし、前記接続ポートPoに薄膜封止層が形成されると導通できなくなるので、薄膜封止層41b形成時には、前記接続ポートPoをメタルマスクでカバーするなどの手段をとると良い。また、この薄膜封止層41bは、接続ポートPoを構成する図中右端側の導電層ML上にも形成されている。

20

【0081】

最後に、図10(b)に示すように、基板外周や実装端子接続部(図示せず)、前記接続ポートPoを除いたガラス基板30のほぼ全面にエポキシ樹脂などからなる透明な接着剤を塗布し、封止基板50を接合する。このようにして、表示パネル部12が製造される。

【0082】

尚、特許請求の範囲に記載の基板、電気光学装置、接続部及び能動素子は、それぞれ、本実施形態におけるガラス基板30、有機ELディスプレイ10、コンタクトホールH及び駆動トランジスタQdに対応している。また、特許請求の範囲に記載の素子形成層は、本実施形態における第1層間絶縁膜ID1またはゲート絶縁膜34に対応している。また、特許請求の範囲に記載の絶縁層は、本実施形態における下地絶縁膜32に対応している。さらに、特許請求の範囲に記載の突出部及び透明性導電膜は、それぞれ、本実施形態における接続ポートPo及び透明導電層47に対応している。さらに、特許請求の範囲に記載のバンク層は、本実施形態における第1バンク層42aまたは第2バンク層42bに対応している。また、特許請求の範囲に記載の金属層は本実施形態における第2導電層M2に対応している。

30

【0083】

前記実施形態によれば、以下のような特徴を得ることができる。

(1) 前記実施形態では、各画素20に形成される有機EL素子OLEDの陰極E2を全てコンタクトホールHを介して導電層MLに電気的に接続されるようにした。この結果、表示パネル部12上に形成される位置によって有機EL素子OLEDの陰極E2の電位に差が生じることはない。つまり、例えば、全ての画素20に同じ電圧レベルのデータ信号D1, D2, ..., Dmを供給したとき、画素20が形成される位置によって有機EL素子OLEDの輝度に差が生じることはないので、その分、表示ムラを低減させることができる。

40

【0084】

従って、たとえば、陰極E2をスズドープ酸化インジウム(ITO)といった比較的導電率が低い(抵抗率が比較的高い)透明材料で構成されたトップエミッショントラップ有機ELディスプレイであっても、データ信号D1, D2, ..., Dmに応じた画像を精度良く表示させることができる。

【0085】

50

(2) 前記実施形態では、前記導電層M Lはその一端が表示パネル部1 2から直接外方に突出されている。そして、その突出された導電層M Lを接続ポートP oとして使用するようにした。従って、前記接続ポートP oに各種外部装置を接続することで特別なインターフェースといった接続手段を設けることなく有機EL素子O L E Dの各陰極E 2の電位を直接制御することができる。

【0086】

(3) 前記実施形態では、チタン(T i)で第1導電層M 1を構成した。従って、第1導電層M 1を下地保護層3 1に密着良く形成することができる。また、銅(C u)で第2導電層M 2を構成した。従って、導電層M Lの導電率を高くすることができるので、その分、陰極E 2が表示パネル部1 2上に形成される位置によって、電位差が生じることを抑制することができる。

10

【0087】

さらに、窒化チタン(T i N)で第3導電層M 3を構成した。第2導電層M 2を構成する銅(C u)と下地絶縁膜3 2を構成する(S i O<sub>2</sub>)とが反応して、その結果、第2導電層M 2の導電率が低下する若しくは下地絶縁膜3 2の絶縁性が低下するのを防止することができる。

【0088】

(4) 前記実施形態では、ガラス基板3 0上に下地保護層3 1、導電層M L、下地絶縁膜3 2、ゲート絶縁膜3 4、第1及び第2層間絶縁膜I D 1, I D 2、平坦化絶縁膜4 0を形成した。そして、平坦化絶縁膜4 0を形成した後、第1及び第2バンク層4 2 a, 4 2 bを形成し、ドライエッティング処理を施すことで、先に形成された下地絶縁膜3 2、ゲート絶縁膜3 4、第1及び第2層間絶縁膜I D 1, I D 2、第1バンク層4 2 aの各々を除去してコンタクトホールHを形成した。その後、このコンタクトホールH上に順次、電子注入層4 6、透明導電層4 7を形成した。

20

【0089】

このようにすることで、透明導電層4 7と導電層M Lとを電気的に接続することができる。この結果、表示ムラを低減させた有機ELディスプレイ1 0を製造することができる。

【0090】

(5) 前記実施形態では、第1～第3導電層M 1, M 2, M 3をそれぞれスパッタ法を用いて形成した。従って、蒸着法といった他の方法で形成する場合と比較してその成膜温度を低くすることができる。この結果、ガラス基板3 0や下地保護層3 1に欠陥等が生じるのを防止することができる。

30

【0091】

(6) 前記実施形態では、下地絶縁膜3 2を、その膜厚が2 / 3 . 5 μm以上になるように形成した。従って、下地絶縁膜3 2上に形成されるシリコン層3 3、データ線X 1, X 2, …, X m及び走査線Y 1, Y 2, …, Y n等に導電層M Lを構成する材料が拡散するのを確実に防止することができる。また、導電層M Lと、シリコン層3 3、データ線X 1, X 2, …, X m及び走査線Y 1, Y 2, …, Y nの間に生じる寄生容量を低減し、駆動回路を安定して動作させ、表示品質を向上させることができる。

40

(第2実施形態)

次に、本発明を具体化した第2実施形態を図1 1～図1 3に従って説明する。

まず、本発明の第2実施形態に係る表示パネル部の構造について図1 1に従って説明する。尚、図1 1は、第1の実施形態の図3中のA - A線に沿う断面に対応している。

【0092】

本実施形態に係る表示パネル部1 2 aは、そのコンタクトホールH rと第3導電層M 3との電気的接続するための構造及びその製造方法が異なっていること以外は前記第1実施形態と同じである。従って、コンタクトホールH rと第3導電層M 3とを電気的に接続するための構造及びその製造方法以外は、その詳細な説明は省略する。

【0093】

50

図11に示すように、表示パネル部12aは、その下地絶縁膜32及びゲート絶縁膜34を連通して開孔した第3のコンタクトホールC3が形成されている。

また、この第3のコンタクトホールC3には、駆動トランジスタQdを構成するゲート電極35を構成する導電性材料と同じ材料が埋め込まれている。また、この第3のコンタクトホールC3に埋め込まれた導電性材料はゲート絶縁膜34上の一部に乗り上げて形成されている。そして、このゲート絶縁膜34上の一部に乗り上げて形成された導電性材料は第1コンタクト部CON1になる。そして、第1コンタクト部CON1に対応する位置に、前記ゲート絶縁膜34上に形成された第1層間絶縁膜ID1を開孔する第4のコンタクトホールC4が形成されている。

【0094】

10

前記第4のコンタクトホールC4には、駆動トランジスタQdを構成するソース電極36またはドレイン電極37を構成する導電性材料と同じ材料が埋め込まれている。また、この第4のコンタクトホールC4に埋め込まれた導電性材料は第1層間絶縁膜ID1上の一部に乗り上げて形成されている。そして、この第1層間絶縁膜ID1上の一部に乗り上げて形成された導電性材料は第2コンタクト部CON2になる。そして、第2コンタクト部CON2に対応する位置に、第1及び第2バンク層42a, 42b、平坦化絶縁膜40及び第2層間絶縁膜ID2をそれぞれ貫通して形成されるコンタクトホールHrが設かれている。そして、このコンタクトホールHrには、上記第1実施形態に記載されたように、電子注入層46、透明導電層47及び薄膜封止層41bが順次形成されている。従って、透明導電層47は前記第2コンタクト部CON2及び第1コンタクト部CON1を介して前記導電層MLと電気的に接続された状態になる。この結果、前記第1実施形態と同様な効果を得ることができる。

20

【0095】

次に、本実施形態の有機ELディスプレイ10の製造方法を図12～図14に従って説明する。尚、コンタクトホールHと導電層MLとの電気的接続をする部分の製造方法についてのみ説明し、他の前記第1実施形態と同じ構造については符号を付しその製造方法の詳細は省略する。

【0096】

30

まず、ガラス基板30上に下地保護層31、第1、第2及び第3導電層M1, M2, M3、下地絶縁膜32、シリコン層33及びゲート絶縁膜34を順次形成した後、図12(a)に示すように、前記シリコン層33と隣接して形成されるシリコン層33a(図中左側に形成されたシリコン層)との間に開孔部Qr1を備えたマスクMr1を設ける。続いて、ドライエッチング処理を施すことによって図12(b)に示すように、開孔部Qr1に対応する前記ゲート絶縁膜34及び下地絶縁膜32を除去して第3のコンタクトホールC3を形成する。同時に、後述する接続ポートPoに対応する位置(図中右側端)の前記ゲート絶縁膜34及び下地絶縁膜32も除去しておく。

【0097】

40

その後、シリコン層33のチャネル領域33C及び第3のコンタクトホールC3に対応した領域に開孔部Qr2, Qr3を備えたマスクMr2を設ける。続いて、スパッタ法等を用いてアルミニウム(A1)膜を形成する。その後、前記マスクMr2を除去することで、アルミニウム(A1)で構成された膜厚約500nm程度のゲート電極35及び第1コンタクト部CON1がそれぞれ形成される(図12(c)参照)。従って、第1コンタクト部CON1はゲート電極35と同時に形成される。続いて、前記ゲート電極35をマスクとし、前記シリコン層33に対してリンイオン(P)を約 $4 \times 10^{13} \text{ cm}^{-2}$ のドーズ量でイオン注入してシリコン層33中に低濃度ソース領域33LS及び低濃度ドレン領域33LDを形成する。

【0098】

50

次に、ゲート絶縁膜34、ゲート電極35及び第1コンタクト部CON1上に第1層間絶縁膜ID1を形成し(図13(a)参照)、その形成した第1層間絶縁膜ID1をCMP(化学的機械的研磨)等を用いて平坦化処理する。その後、図13(b)に示すように

、前記第1層間絶縁膜ID1上に第1コンタクト部CON1に対応する位置に開孔部Qr4が、また、シリコン層33に形成された高濃度ソース領域33HS及び高濃度ドレイン領域33HDに対応する位置に開孔部Qr5a, Qr5bがそれぞれ形成されたマスクMr3を設ける。そして、エッチング処理を施すことによって、図13(c)に示すように、第1コンタクト部CON1に対応する位置に第4のコンタクトホールC4が形成される。また、駆動トランジスタQdのソース電極36に対応する位置に第1電極用コンタクトホールC1が、ドレイン電極37に対応する位置に第2電極用コンタクトホールC2が、それぞれ形成される。また同時に、後述する接続ポートPoに対応する位置の第1層間絶縁膜ID1も除去しておく。

【0099】

10

そして、前記第1層間絶縁膜ID1上に、銅(Cu)やアルミニウム(Al)といった導電性材料からなる導電層を形成することにより、先に形成した第4のコンタクトホールC4、第1及び第2電極用コンタクトホールC1, C2に導電性材料を埋め込む。その結果、第1コンタクト部CON1と電気的に接続し第1層間絶縁膜ID1上の一部に乗り上げた位置に形成される第2コンタクト部CON2が形成される。また、高濃度ソース領域33HSに対応した位置にソース電極36が、高濃度ドレイン領域33HDに対応した位置にドレイン電極37が、それぞれ形成される。従って、第2コンタクト部CON2はソース電極36及びドレイン電極37と同時に形成される。

【0100】

20

続いて、図14(a)に示すように、第1層間絶縁膜ID1、第2コンタクト部CON2、ソース電極36及びドレイン電極37上に二酸化珪素(SiO<sub>2</sub>)からなる第2層間絶縁膜ID2を形成する。その後、第2層間絶縁膜ID2上に二酸化珪素(SiO<sub>2</sub>)で構成された平坦化絶縁膜40を形成する。形成された平坦化絶縁膜40をCMP(化学的機械的研磨)等を用いて平坦化処理する。その後、第2層間絶縁膜ID2および平坦化絶縁膜40のドレイン電極37に対応する位置にコンタクトホールを形成する。同時に第2コンタクト部CON2に対応する位置にもコンタクトホールを形成する。また同時に、後述する接続ポートPoに対応する位置の第2層間絶縁膜ID2および平坦化絶縁膜40も除去しておく。

【0101】

30

その後、図14(b)に示すように、平坦化絶縁膜40上に第1の電極層41a、第1バンク層42a及び第2バンク層42bを順次形成する。第1バンク層42a成膜後に発光領域に開口部を形成するが、それと同時にドレイン電極37に対応する位置にもコンタクトホールを形成する。第2バンク層42bは、感光性のアクリル樹脂やポリイミド樹脂を塗布・乾燥後、露光・現像・焼成することで画素の開口部を形成するが、それと同時に、ドレイン電極37に対応する位置にも開口部を形成する。また、それぞれの開口部を形成するのと同時に、後述する接続ポートPoに対応する位置の第1バンク層42a及び第2バンク層42bも除去しておく。

【0102】

40

この状態で、図14(b)に示すような開口部Qoに対応した位置が開孔したコンタクトホールHrが形成される。

また、ガラス基板30の端部(図中右端側)に示すような前記導電層MLが外方に突出された領域が形成される。この外方に突出された部分の導電層MLが接続ポートPoになる。このようにして接続ポートPoが形成される。

【0103】

そして、プラズマ処理によって第1及び第2バンク層42a、42b表面に親液性と撥液性の領域を形成し、第1の電極層41a上に正孔注入層43及び発光層44をインクジェット法により形成する。

【0104】

その後、発光層44、第1バンク層42a及び第2バンク層42b、及び、コンタクトホールHの全面に渡って電子注入層46が形成されている。この電子注入層46は透明な

50

材料で形成されている。電子注入層46上には透明な材料で構成された透明導電層47が形成されている。透明導電層47は前記した有機EL素子OLEDの陰極E2を構成する電極層である。従って、透明導電層47(有機EL素子OLEDの陰極E2)は、電子注入層46を介して前記導電層MLを構成する第3導電層M3に電気的に接続されている。

【0105】

透明導電層47上には、透明な材料で構成された薄膜封止層41bを形成する。本実施形態においては、薄膜封止層41bは酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)からなり、スパッタ法、CVD法などの既知の適切な方法で形成される。ただし、前記接続ポートPoに薄膜封止層が形成されると導通できなくなるので、薄膜封止層41b形成時には、前記接続ポートPoをメタルマスクでカバーするなどの手段をとると良い。

10

【0106】

最後に、基板外周や実装端子接続部(図示せず)、前記接続ポートPoを除いたガラス基板30のほぼ全面にエポキシ樹脂などからなる透明な接着剤を塗布し、封止基板50を接合することで図11に示す表示パネル部12が製造される。

【0107】

このように有機ELディスプレイ10を製造することで、コンタクトホールHは前記導電層MLに至るまで形成される必要はなく、前記したように、第1層間絶縁膜ID1上に渡って先に形成された前記第2コンタクト部CON2に至るまで形成すればよい。この結果、第1実施形態の有機ELディスプレイに比べてコンタクトホールHを容易に形成することができる。この結果、第1実施形態の有機ELディスプレイに比べてその歩留まりを向上させることができる。

20

【0108】

前記実施形態によれば、以下のような特徴を得ることができる。

(1) 前記実施形態では、ゲート絶縁膜34上に導電層MLに電気的に接続された第1コンタクト部CON1を形成した。そして、第1コンタクト部CON1はゲート電極35と同時に形成した。第1層間絶縁膜ID1上に第1コンタクト部CON1に電気的に接続された第2コンタクト部CON2を形成した。そして、第2コンタクト部CON2はソース電極36及びドレイン電極37と同時に形成した。そして、第1層間絶縁膜ID1上に第2層間絶縁膜ID2、平坦化絶縁膜40、第1及び第2バンク層42a, 42bの各層を形成して開口部(コンタクトホールなど)を形成するのと同時に、コンタクトホールHrに対応する部分にも開口部を形成することによって、前記第2コンタクト部CON2に至るコンタクトホールHrを形成した。その後、このコンタクトホールHr上に順次、電子注入層46、透明導電層47及び薄膜封止層41bを形成した。

30

【0109】

従って、導電層MLまでドライエッチング処理を施すことなく透明導電層47と導電層MLとを電気的に接続することができる。この結果、コンタクトホールHを容易に形成することができるので、その歩留まりを向上させることができる。

(第3実施形態)

次に、第1又は第2実施形態で説明した電気光学装置としての有機ELディスプレイ10の電子機器の適用について図15に従って説明する。有機ELディスプレイ10は、モバイル型のパーソナルコンピュータ、携帯電話、デジタルカメラ等種々の電子機器に適用できる。

40

【0110】

図15は、モバイル型パーソナルコンピュータの構成を示す斜視図を示す。図15において、パーソナルコンピュータ70は、キーボード71を備えた本体部72と、前記有機ELディスプレイ10を用いた表示ユニット73とを備えている。この場合においても、有機ELディスプレイ10を用いた表示ユニット73は前記第1及び第2実施形態と同様な効果を発揮する。

【0111】

尚、発明の実施形態は、上記実施形態に限定されるものではなく、以下のように実施し

50

てもよい。

上記各実施形態では、第1導電層M1と第2導電層M2と第3導電層M3とで1つの導電層MLを構成した。これを、導電層MLを一つの材料で構成された単一の層で構成するようにしてもよい。この場合、導電層MLは、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、バナジウム(V)、ジルコニウム(Zr)、及びこれらの合金またはシリサイドで構成されることが好ましい。

【0112】

上記各実施形態では、第1導電層M1と第2導電層M2と第3導電層M3とで1つの導電層MLを構成した。これを、導電層MLを第1導電層M1と第2導電層M2のみから成る2層で構成するようにしてもよい。この場合、第1導電層M1は、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドで構成されることが好ましい。また、第2導電層M2は、アルミニウム(A1)、ニッケル(Ni)及び白金(Pl)で構成されることが好ましい。

【0113】

上記各実施形態では、第1導電層M1をチタン(Ti)で構成した。また、第2導電層M2を銅(Cu)で構成した。さらに、第3導電層M3を窒化チタン(TiN)で構成した。

【0114】

これを、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドで第1導電層M1を構成してもよい。また、アルミニウム(A1)、ニッケル(Ni)、白金(Pl)、金(Au)、銀(Ag)、及びこれらの合金またはシリサイドで第2導電層M2を構成してもよい。さらに、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、及びこれらの合金またはシリサイドで第3導電層M3を構成してもよい。

このようにすることで上記実施形態と同じ効果を奏することができる。

【0115】

上記各実施形態では、電気光学装置として、その発光層が有機EL素子で構成された有機ELディスプレイ10に具体化したが、これに限定されるものではなく、トップエミッションタイプの電気光学装置ならどのような電気光学装置に適応してもよい。

【0116】

上記各実施形態では、各画素20に形成される有機EL素子OLEDの陰極E2を全てコンタクトホールH<sub>c</sub>、H<sub>r</sub>を介して導電層MLに電気的に接続されたようにした。これをコンタクトホールH<sub>c</sub>、H<sub>r</sub>ではなく、他の形状を成したもので有機EL素子OLEDの陰極E2と導電層MLとを電気的に接続するようにしてもよい。

【0117】

上記各実施形態では、有機EL素子OLEDの陰極E2をスズドープ酸化インジウム(ITO)で構成された陰極を使用したが、これに限定されるものではなく、例えば、陰極E2が酸化亜鉛(ZnO)といった透明導電性薄膜で構成された有機ELディスプレイに適応してもよい。つまり、有機EL素子OLEDの陰極E2を構成する材料には限定されるものではない。

【0118】

上記各実施形態では、各層の成膜方法は上記実施形態に記載された方法に限定されるものではなく、他の方法を用いて形成されるようにしてもよい。

上記各実施形態では、ポリシリコンで構成されたシリコン層33をチャネル領域33Cとした駆動トランジスタQdで画素20を構成した有機ELディスプレイ10に対して適応した。これを、単結晶で構成されたシリコン層をチャネル領域とした駆動トランジスタで画素20を構成した有機ELディスプレイに対して適応してもよい。

【符号の説明】

【0119】

30...基板としてのガラス基板、E1...陽極、E2...陰極、発光性材料としての発光層

10

20

30

40

50

、20…画素、10…電気光学装置としての有機ELディスプレイ、ML…導電層、H、Hr…接続部としてのコンタクトホール、Qd…能動素子としての駆動トランジスタ、ID1、34…素子形成層としての第1層間絶縁膜及びゲート絶縁膜、31…下地保護層、32…絶縁層としての下地絶縁膜、ML…導電層、M1…第1導電層、M2…金属層としての第2導電層、M3…第3導電層、Po…突出部としての接続ポート、42a、42b…バンク層として第1及び第2バンク層、41b…透明性導電膜としての薄膜封止層、70…電子機器としてのモバイル型のパーソナルコンピュータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

### 【 図 1 1 】

【 図 1 3 】

【 図 1 2 】

【 図 1 4 】

## 【図 15】

## 【手続補正書】

【提出日】平成21年3月4日(2009.3.4)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

基板上に形成された導電層と、前記導電層の上方に形成された素子形成層と、前記素子形成層の上方に形成された陽極と、前記陽極の上方に形成された発光性材料と、前記発光性材料の上方に形成された陰極と、を有し、前記素子形成層は、前記陽極と前記陰極の間に設けられた前記発光性材料に供給される電流を制御するための能動素子が形成されており、

前記陰極と前記導電層とを電気的に接続するための接続部を備えていることを特徴とする電気光学装置。

## 【請求項2】

請求項1に記載の電気光学装置において、

前記陽極および前記接続部は前記発光性材料が設けられる画素毎に備えられていることを特徴とする電気光学装置。

## 【請求項3】

請求項1または2に記載の電気光学装置において、

前記接続部はコンタクトホールで構成されていることを特徴とする電気光学装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一つに記載の電気光学装置において、

前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切斷するための絶縁層が形成されていることを特徴とする電気光学装置。

**【請求項 5】**

請求項 1 乃至 4 のいずれか一つに記載の電気光学装置において、

前記導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、バナジウム (V)、ジルコニウム (Zr)、及びこれらの合金またはシリサイドのうちの一つで構成されることを特徴とする電気光学装置。

**【請求項 6】**

請求項 1 乃至 4 のいずれか一つに記載の電気光学装置において、

前記導電層は少なくとも一層の金属層を含む複数の導電層から構成されていることを特徴とする電気光学装置。

**【請求項 7】**

請求項 6 に記載の電気光学装置において、

前記基板上に該基板を保護する下地保護層を備え、その下地保護層は二酸化珪素で構成され、

前記複数の導電層は前記下地保護層上から順に第 1 導電層、第 2 導電層から構成される導電層であって、

前記第 1 導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第 2 導電層はアルミニウム (Al)、ニッケル (Ni) 及び白金 (Pt)、及びこれらの合金またはシリサイドのいずれか一つで構成されていることを特徴とする電気光学装置。

**【請求項 8】**

請求項 6 に記載の電気光学装置において、

前記基板上に該基板を保護する下地保護層を備え、その保護層は二酸化珪素で構成され、

前記複数の導電層は前記下地保護層上から順に第 1 導電層、第 2 導電層、第 3 導電層から構成され、

前記第 1 導電層はチタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第 2 導電層は銅 (Cu)、アルミニウム (Al)、ニッケル (Ni) 及び白金 (Pt)、及びこれらの合金またはシリサイドのいずれか一つで構成され、

前記第 3 導電層は窒化チタン (TiN)、チタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、及びこれらの合金またはシリサイドのいずれか一つで構成されていることを特徴とする電気光学装置。

**【請求項 9】**

請求項 1 乃至 8 のいずれか一つに記載の電気光学装置において、

前記導電部は、前記基板 に対向して配置された対向基板 から 平面的に突出して形成された突出部 を備えていることを特徴とする電気光学装置。

**【請求項 10】**

請求項 9 に記載の電気光学装置において、

前記対向基板は封止基板であり、

前記封止基板は、前記基板上の少なくとも前記陽極と前記発光性材料と前記陰極と前記素子形成層とを平面的に覆うように形成されていることを特徴とする電気光学装置。

**【請求項 11】**

基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備えるとともに、前記発光性材料を画素毎に区分けするためのバンク層と、前記基板と前記陽極と

の間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部と、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層とを備えた電気光学装置の製造方法において、

前記基板の上方に前記導電層を形成する工程と、

前記導電層の上方に前記絶縁層、前記素子形成層、前記陽極及びバンク層を形成する工程と、

前記陰極と前記導電層とを電気的に接続するための接続部開口パターンを形成するのと同時に前記絶縁層に少なくとも前記接続部を除いた開口パターンを形成する工程と、

前記発光性材料を形成する工程と、

前記接続部を含む前記発光性材料を形成した領域の全面に前記陰極を形成する工程とを備えたことを特徴とする電気光学装置の製造方法。

#### 【請求項 1 2】

請求項 1 1 に記載の電気光学装置の製造方法において、

前記導電層は第 1 導電層、第 2 導電層及び第 3 導電層から構成される導電層を備え

前記素子形成層は前記能動素子に信号を供給するための第 1 の信号線と第 2 の信号線とを備え、

前記第 1 導電層は前記第 1 の信号線を形成すると同時に形成され、

前記第 2 導電層は前記第 2 の信号線を形成すると同時に形成されるようにしたことを特徴とする電気光学装置の製造方法。

#### 【請求項 1 3】

請求項 1 1 または 1 2 に記載の電気光学装置の製造方法において、

前記導電層はスパッタ法で形成するようにしたことを備えたことを特徴とする電気光学装置の製造方法。

#### 【請求項 1 4】

請求項 1 乃至 1 0 のいずれか一つに記載の電気光学装置を備えていることを特徴とする電子機器。

#### 【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 8

【補正方法】変更

【補正の内容】

【0 0 0 8】

本発明の電気光学装置は、基板上に形成された導電層と、前記導電層の上方に形成された素子形成層と、前記素子形成層の上方に形成された陽極と、前記陽極の上方に形成された発光性材料と、前記発光性材料の上方に形成された陰極と、を有し、前記素子形成層は、前記陽極と前記陰極の間に設けられた前記発光性材料に供給される電流を制御するための能動素子が形成されており、前記陰極と前記導電層とを電気的に接続するための接続部を備えている。

本発明の電気光学装置は、基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備え、前記陽極は前記発光性材料が設けられる画素毎に形成された電気光学装置において、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部とを備えている。

#### 【手続補正 3】

【補正対象書類名】明細書

【補正対象項目名】0 0 1 0

【補正方法】変更

【補正の内容】

【0 0 1 0】

この電気光学装置において、前記陽極および前記接続部は前記発光性材料が設けられる画素毎に備えられていてもよい。

この電気光学装置において、前記接続部は前記画素毎に備えられていてもよい。

これによれば、形成される位置によって表示ムラが発生するのを画素毎に確実に抑制することができる。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0021

【補正方法】変更

【補正の内容】

【0021】

この電気光学装置において、前記導電層は前記基板と対向して配置された対向基板から平面的に突出して形成された突出部を備えていることを特徴とする。前記対向基板は封止基板であり、前記封止基板は、前記基板上の少なくとも前記陽極と、前記発光性材料と、前記陰極と、前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、を平面的に覆うように形成されていることを特徴とする。

この電気光学装置において、前記導電層は前記基板から突出して形成された突出部を備えっていてもよい。

これによれば、突出された導電層を各種外部装置と直接接続することで特別なインターフェースといった接続手段を設けることなく前記各陰極の電位を直接制御することができる。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0022

【補正方法】変更

【補正の内容】

【0022】

本発明の電気光学装置の製造方法は、基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備えるとともに、前記発光性材料を画素毎に区分けするためのバンク層と、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部と、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層とを備えた電気光学装置の製造方法において、前記基板の上方に前記導電層を形成する工程と、前記導電層の上方に前記絶縁層、前記素子形成層、前記陽極及びバンク層を形成する工程と、前記陰極と前記導電層とを電気的に接続するための接続部開口パターンを形成するのと同時に前記絶縁層に少なくとも前記接続部を除いた開口パターンを形成する工程と、前記発光性材料を形成する工程と、前記接続部を含む前記発光性材料を形成した領域の全面に前記陰極を形成する工程とを備えた。

本発明の電気光学装置の製造方法は、基板上に、陽極と、該陽極に対向する位置に形成された陰極と、前記陽極と前記陰極との間に設けられた発光性材料とを備えるとともに、前記発光性材料を画素毎に区分けするためのバンク層と、前記基板と前記陽極との間に形成された導電層と、前記陰極と前記導電層とを電気的に接続するための接続部と、前記基板上には前記発光性材料に供給される電流を制御するための能動素子が形成される素子形成層と、前記素子形成層と前記導電層との間には前記素子形成層と前記導電層とを電気的に切断するための絶縁層とを備えた電気光学装置の製造方法において、前記基板の上方に前記導電層を形成する工程と、前記導電層の上方に前記絶縁層、前記素子形成層、前記陽極及びバンク層を形成する工程と、前記絶縁層に開口パターンを形成するのと同時に前記陰極と前記導電層とを電気的に接続するための接続部開口パターンを形成する工程と、前記発光性材料を形成する工程と、前記接続部を含む前記発光性材料を形成した領域の全面

に透明性導電膜を形成する工程とを備えた。