(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4617782号

(P4617782)

(45) 発行日 平成23年1月26日(2011.1.26)

(24) 登録日 平成22年11月5日(2010.11.5)

|               |                                 |

|---------------|---------------------------------|

| (51) Int.Cl.  | F 1                             |

| G 0 6 F 13/36 | (2006.01) G 0 6 F 13/36 5 3 O B |

| G 0 6 F 13/38 | (2006.01) G 0 6 F 13/38 3 4 O A |

| H 0 4 B 1/38  | (2006.01) H 0 4 B 1/38          |

| H 0 4 B 7/26  | (2006.01) H 0 4 B 7/26          |

| H 0 4 M 1/00  | (2006.01) H 0 4 M 1/00 J        |

請求項の数 10 (全 16 頁) 最終頁に続く

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2004-253730 (P2004-253730) |

| (22) 出願日  | 平成16年9月1日 (2004.9.1)         |

| (65) 公開番号 | 特開2006-72592 (P2006-72592A)  |

| (43) 公開日  | 平成18年3月16日 (2006.3.16)       |

| 審査請求日     | 平成19年3月2日 (2007.3.2)         |

|           |                                                 |

|-----------|-------------------------------------------------|

| (73) 特許権者 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号     |

| (74) 代理人  | 100100310<br>弁理士 井上 学                           |

| (72) 発明者  | 恒原 克彦<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

| (72) 発明者  | 石井 裕丈<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

| (72) 発明者  | 川辺 学<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内  |

最終頁に続く

(54) 【発明の名称】データ専用バスを有する無線機

## (57) 【特許請求の範囲】

## 【請求項 1】

無線通信装置において、

該無線通信装置の制御を行うメインプロセッサと、

前記メインプロセッサに使用されるメモリと、

該無線通信装置が送受信する信号を入出力するための外部インタフェースと、

前記無線通信の信号処理を行う複数のプロセッサユニットと、

前記メインプロセッサと前記メモリと前記外部インタフェースと複数の前記プロセッサユニットそれぞれとに接続され、当該接続された構成要素の間での信号転送を行う制御バスと、

前記外部インタフェースと複数の前記プロセッサユニットとに接続され、当該接続された構成要素の間での信号転送を行うデータバスと、を備え、

前記プロセッサユニットは、プロセッサユニットごとに構成されるユニット間信号線を介して、他のプロセッサユニットに接続され、前記制御バス及び前記データバスとは異なるユニットインターフェースを有する、ことを特徴とすることを特徴とする無線通信装置。

## 【請求項 2】

請求項1に記載の無線通信装置において、前記データバスは、前記1つ以上のプロセッサユニットのそれぞれから前記外部インタフェースへ信号を転送するための第一の信号線と、前記外部インタフェースから前記1つ以上のプロセッサユニットのそれぞれへ信号を転送するための第二の信号線を備え、前記プロセッサユニット毎に前記第一の信号線と前

10

20

記第二の信号線を個別に備えることを特徴とする無線通信装置。

【請求項 3】

請求項1に記載の無線通信装置において、複数のプロセッサユニットを有し、前記データバスは、前記複数のプロセッサユニットから前記外部インターフェースへ信号を転送するための第一の信号線と、前記外部インターフェースから前記複数のプロセッサユニットへ信号を転送するための第二の信号線を備え、前記複数のプロセッサユニットが前記第一の信号線を共有し、前記複数のプロセッサユニットが前記第二の信号線を共有することを特徴とする無線通信装置。

【請求項 4】

請求項1に記載の無線通信装置において、前記データバスは、前記1つ以上のプロセッサユニットのそれぞれから前記外部インターフェースへの信号の転送と、前記外部インターフェースから前記1つ以上のプロセッサユニットのそれぞれへの信号の転送の両方を行う信号線を備え、前記プロセッサユニット毎に前記信号線を個別に備えることを特徴とする無線通信装置。 10

【請求項 5】

請求項1に記載の無線通信装置において、前記データバスは、前記複数のプロセッサユニットから前記外部インターフェースへの信号の転送と、前記外部インターフェースから前記複数のプロセッサユニットへの信号の転送の両方を行う信号線を備え、前記複数のプロセッサユニットが前記信号線を共有することを特徴とする無線通信装置。

【請求項 6】

請求項3記載の無線通信装置において、前記第一の信号線と前記第二の信号線は、該信号線の利用を時間で区切るためのタイムスロットに分割され、前記プロセッサユニット毎にそれぞれタイムスロットが割り当てられ、前記各プロセッサユニットは前記それぞれに割り当てられたタムスロットの中で該信号線を利用して信号の転送を行なうことを特徴とする無線通信装置。 20

【請求項 7】

請求項5記載の無線通信装置において、前記信号線は、該信号線の利用を時間で区切るためのタイムスロットに分割され、前記プロセッサユニット毎にそれぞれタイムスロットが割り当てられ、前記各プロセッサユニットは前記それぞれに割り当てられたタイムスロットの中で該信号線を利用して信号の転送を行なうことを特徴とする無線通信装置。 30

【請求項 8】

請求項3記載の無線通信装置において、前記第一の信号線と前記第二の信号線は複数の信号線を含み、前記プロセッサユニット毎にそれぞれ前記複数の信号線のうちの少なくとも一つの信号線が割当てられ、前記各プロセッサユニットはそれぞれに割り当てられた信号線を用いて信号の転送を行なうことを特徴とする無線通信装置。

【請求項 9】

請求項5記載の無線通信装置において、前記信号線は複数の信号線を備え、前記プロセッサユニット毎にそれぞれ前記複数の信号線のうちの少なくとも一つの信号線が割当てられ、前記各プロセッサユニットはそれぞれに割り当てられた信号線を用いて信号の転送を行なうことを特徴とする無線通信装置。 40

【請求項 10】

請求項1に記載の無線通信装置において、

前記プロセッサユニットは、少なくとも該プロセッサユニットの制御を行う少なくとも一つのサブプロセッサと、該サブプロセッサが利用するメモリと、

信号処理を行なう信号処理回路と、該プロセッサユニットが前記制御バス及び前記データバスを介して信号を転送するための制御を行なうバスインターフェースと、

前記ユニット間信号線を介して他のプロセッサユニットとの間で信号を転送するための前記ユニットインターフェースと、

少なくとも前記サブプロセッサと前記メモリと前記信号処理回路と前記バスインターフェースが接続される内部バスとを備えることを特徴とする無線通信装置。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は無線通信装置に関する。さらに詳しくは、並列に設置され、それぞれが送受信信号の信号処理を行うプロセッサユニットを1つまたは複数有する無線通信装置に関する。

**【背景技術】****【0002】**

移動通信や無線アクセス技術の普及に伴い、セルラ通信、無線LANやDSRC(Dedicated Short Range Communication)等の様々な無線通信方式が存在している。これら既存の無線通信方式の通信速度の高速化等の高度化を実現するため、各無線通信方式の機能追加や変更が今後実施される予定である。また、これら既存の無線通信方式に加え、例えばIEEE802.20委員会で策定中のMBWA(Mobile Broadband Wireless Access)のように、新規の無線通信方式を策定するための検討が進められている。

10

**【0003】**

このように無線通信方式が多様化する状況に対応する無線通信装置として、ソフトウェア無線機が考えられる。ソフトウェア無線機とは、ソフトウェアの書換えにより各種無線通信方式に対応することが可能な無線通信装置のことである。

一般に、無線通信の信号処理の処理量は極めて大きい。従って、ソフトウェア無線機には高い信号処理能力が要求される。このため、ソフトウェア無線機を複数のプロセッサを備えたハードウェアで構成する方法が検討されている。

20

**【0004】**

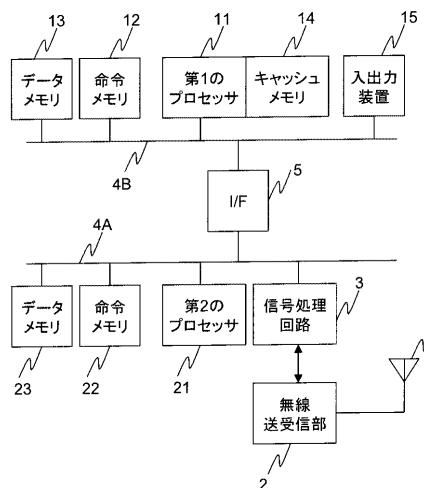

複数のプロセッサを備えたハードウェアを用いて、ソフトウェア無線機を構成する方法の一例が特開2003-283651号公報（特許文献1）で開示されている。特開2003-283651で開示されているソフトウェア無線機の構成を図14に示す。例えば受信の場合、アンテナ1で受信された無線信号は、無線送受信部2、信号処理回路3、第2のプロセッサ21及び第1のプロセッサ11で復調のための信号処理を施された後、バス4Bを介して入出力装置15から出力される。逆に送信の場合、入出力装置15から入力された送信信号は、バス4Bを介して第1のプロセッサ11に入力され、更に第2のプロセッサ21、信号処理回路3及び無線送受信部2で信号処理を施された後、アンテナ1から送信される。

30

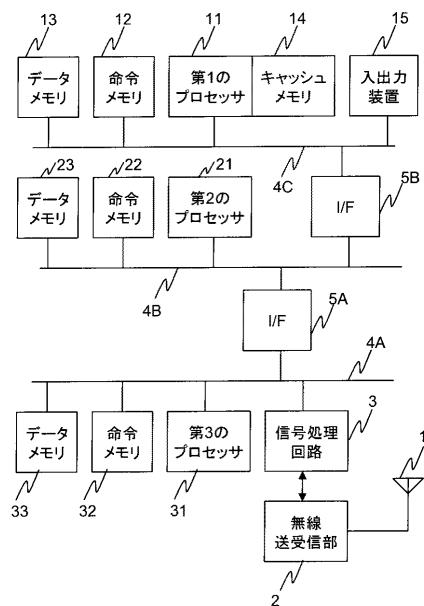

**【0005】**

また特開2003-283651では、図15に示すような第3のプロセッサを追加した構成も開示されている。この場合、送受信される信号はアンテナ1、無線送受信部2、信号処理回路3、第2のプロセッサ21、第1のプロセッサ11に加え、第3のプロセッサ31でも信号処理を施され、バス4Cを介して入出力装置15で外部デバイスとの間で入出力される。また、この場合、第2のプロセッサ21は少なくとも信号処理回路3の制御を行うと記載されている。

**【0006】****【特許文献1】特開2003-283651号公報****【0007】****【特許文献2】特開2003-337805号公報**

40

**【発明の開示】****【発明が解決しようとする課題】****【0008】**

第一の課題を以下で説明する。無線通信の高速化が進むと、送受信信号の伝送速度は現在の伝送速度より大きくなる。また、複数の無線通信方式を同時に利用するマルチタスクに対応する場合、送受信信号の伝送速度は各無線通信方式毎の伝送速度の合計となる。従って無線機全体で見た場合の送受信信号の伝送速度は、単一の無線通信方式のみを使用する場合と比較して大きくなる。ここでマルチタスクとしては、例えばセルラ電話で音声通信をしながら無線LANでデータのダウンロードを行うような利用形態が考えられる。

**【0009】**

50

例えば、図14に示した従来の構成の無線機では、全ての送受信信号はバス4Bに接続された入出力装置15を介して、外部との間で転送される。従って、全ての送受信信号はバス4Bを通る。従って、上記のように無線通信の高速化やマルチタスクに対応することにより送受信信号の伝送速度が増大した場合、バス4Bの転送能力が不足し、当該無線機が正常に動作できなくなることが考えられる。

#### 【0010】

例えば送受信信号の伝送速度がバス4Bの転送能力を上回った場合、送受信信号の正常な転送が行えなくなる。また、例えば送受信信号の伝送速度がバス4Bの転送能力の大部分を占有する場合、バス4Bを介して行われる制御情報の転送、例えば第1のプロセッサ11によるデータメモリ13へのアクセスや第2のプロセッサ21への制御信号の転送等、の転送遅延が増大し、制御遅延が発生する。この結果、当該無線機が予期した通りに制御されず、正常に動作できなくなる可能性が考えられる。第一の課題は、送受信信号の伝送速度が増大した場合でも、転送遅延、制御遅延を生じることなく動作することができる無線通信装置を実現することである。

10

#### 【0011】

第二の課題を以下で説明する。無線通信の高度化に伴い、ソフトウェア無線機に要求される処理能力は高くなる。従って、ソフトウェア無線機は例えばプロセッサの追加により、その処理能力を向上させることが可能な構成であることが望ましい。しかし、特開2003-283651では、図14のような構成で第2のプロセッサ21を複数化するための技術が必要である。

20

#### 【0012】

図14の第2のプロセッサ21の複数化に適用可能な技術として、特開2003-337805号公報（特許文献2）で開示された方法が考えられる。特開2003-337805では、複数のプロセッサをクロスバースイッチにより接続する構成が開示されている。しかし、一般にクロスバースイッチを用いた構成は、プロセッサの数の増加に伴い指數関数的に配線量が増大し、ハードウェアの規模が極端に大きくなるという問題がある。ハード規模の増大は無線機の大型化や高価格化を招き、ソフトウェア無線機の利便性を低下させる。第二の課題は、複数のプロセッサ間の通信を効率よく小規模なハードウェア構成で行う無線通信装置を実現することである。

#### 【0013】

30

第三の課題を以下で説明する。特開2003-283651では、図15の構成において、第2のプロセッサ21が信号処理回路3を制御する。この場合、第2のプロセッサ21から出力された制御信号は、少なくともバス4B、インタフェース5A及びバス4Aを介して信号処理回路3に入力される。一般にバスを用いた信号転送では遅延が発生し、遅延量はバスのトラフィック量に依存する。従って、図15で第2のプロセッサ21が信号処理回路3を制御する際、制御遅延が大きくなる可能性がある。従って図15の構成の無線機は、制御遅延の時間制約が厳しい処理を含む無線通信方式に対応することができない可能性がある。ここで、制御遅延の時間制約が厳しい無線通信方式としては、例えば受信信号に対するAck信号を10マイクロ秒後に送信する必要のある無線LAN(IEEE802.11)等がある。第三の課題は、無線通信の高速化、および異なるプロトコルによる通信に伴って必要となる複数のプロセッサ間を効率良く連動させることができる構成を実現することである。

40

#### 【課題を解決するための手段】

#### 【0014】

上記第一の課題を解決するために本発明では、送受信信号の転送を行うデータバスと、制御信号の転送を行う制御バスを個別に設ける。また、上記第二の課題を解決するために本発明では、プロセッサ間インタフェースを介して複数のプロセッサをシリアルに接続する。更に上記第三の課題を解決するために、プロセッサ及びその周辺回路をユニット化し、当該ユニット同士を接続するための専用インタフェースを設ける。

#### 【発明の効果】

#### 【0015】

50

本発明のハードウェア構成により、無線通信の高速化やマルチタスク対応により送受信信号の転送速度が増大した場合においても、バスの転送能力の不足や転送遅延による異常動作を回避できるソフトウェア無線機を構成することが出来る。

#### 【0016】

また、無線通信の高度化に伴って複数のプロセッサで信号処理を行なう必要が生じた際に、本発明の複数プロセッサ接続方法を用いることにより、ハードウェア規模の増加を抑えつつ、高度化された無線通信の信号処理に複数のプロセッサで対応することが可能となる。この結果、無線機の小型化及び低価格化を実現することがで、ソフトウェア無線機の利便性を向上させることが出来る。

更に、プロセッサユニット同士を本発明のユニット間インターフェースで直接接続することにより、ユニット間での信号転送の遅延を小さくすることが可能となり、時間制約の厳しい無線通信方式に対応可能なソフトウェア無線機を構成することができる。 10

#### 【発明を実施するための最良の形態】

#### 【0017】

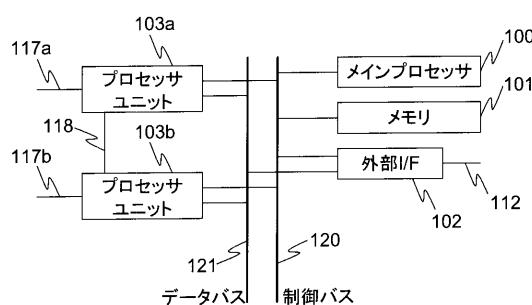

本発明による無線通信装置の例を図1に示す。本発明のソフトウェア無線機は、メインプロセッサ100、メモリ101、外部I/F 102及びプロセッサユニット103aと103bから構成され、これら構成要素は制御バス120とデータバス121の両方あるいは一方を介して接続されている。なお、以下の説明では、図1で示すように、プロセッサユニットが二つの場合を例とするが、プロセッサユニットは一つであっても良いし、三つ以上であっても良い。

#### 【0018】

メインプロセッサ100は本ソフトウェア無線機全体の制御、及びプロセッサユニット103aと103bの制御を行う。また、メインプロセッサ100は、主にプロセッサユニット103a及び103bと連携して、例えば無線通信のプロトコル制御のように、処理量が少なく時間的制約の緩やかな信号処理を行なう。ここでメインプロセッサ100としては、例えば一般的なCPUを用いればよい。 20

#### 【0019】

メモリ101はメインプロセッサ100が処理を行なうためのワークメモリとして使用される。また、メモリ101はメインプロセッサ100及びプロセッサユニット103aと103bの動作を規定するプログラムを格納するためのプログラムメモリとして使用されても良い。ここで、メモリ101としては、例えば汎用的なSRAMやDRAM、フラッシュメモリ等を用いればよい。 30

#### 【0020】

外部I/F 102は信号線112を介して外部デバイスと接続され、本ソフトウェア無線機と外部デバイスとの間で信号をやり取りするためのインターフェースを担う。ここで外部デバイスとしては、たとえばディスプレイ装置やパソコン、スピーカー、マイクなどがある。インターフェース仕様としては、例えばUSB等を用いればよい。

#### 【0021】

プロセッサユニット103aと103bは無線通信を実現するために必要な信号処理を行なう。具体的にはプロセッサユニット103aと103bは、例えば送受信信号の変復調処理、誤り制御処理や波形整形等のように、処理量が大きく時間的制約の厳しい信号処理を実施する。プロセッサユニット103aと103bが、例えば103aは無線LAN信号処理、103bはセルラ通信信号処理のように、異なる無線通信の信号処理を担当することで、当該ソフトウェア無線機が二つの無線通信方式の同時利用、いわゆるマルチタスク、に対応できるようにすればよい。あるいはプロセッサユニット103aと103bは、例えば送信処理と受信処理のように、ある一つの無線通信を実現するための信号処理を分担して処理してもよい。 40

#### 【0022】

プロセッサユニット103aと103bは、それぞれ信号線107aと107bを介して、アナログとデジタルのインターフェースを担うアナログフロントエンド、アナログ信号の変復調処理を行なう無線信号処理部、及び無線周波数の信号を送受信するアンテナ部と接続される。なお図1では、簡単のため上記のアナログフロントエンド、無線信号処理部及びアンテナは図示していない。プロセッサユニット103aと103bはサブプロセッサや信号処理回路から構

10

20

30

40

50

成される。プロセッサユニット103aと103bの構成は後述する。

#### 【0023】

一般に無線通信装置内では、各構成要素間では様々な信号が転送される。無線通信を行なう場合、転送される信号としては主に、各構成要素を制御するための制御信号と、無線通信により送受信するためのデータ信号が存在する。

#### 【0024】

制御信号は以下の特徴を持つ。制御信号の転送は一般に間欠的であり、その転送量も少ない。また制御信号は、例えばメインプロセッサ100とその他の構成要素間や、前記その他の構成要素同士の間など、様々な接続で転送が行われる。また制御信号は、各種フラグなどの制御情報や、各構成要素の動作を規定するパラメータ等、様々な種類の信号から構成される。このため制御信号には、1ビットの論理情報から多ビットの数値情報まで、様々な形態の信号が含まれる。また制御信号の転送には、例えば割り込みやDMA転送等、高い機能が利用できることが望ましい。また、上記の特徴を持つ制御信号の転送は、主にメインプロセッサ100を中心に実施される。

10

#### 【0025】

一方、データ信号は以下の特徴を持つ。送受信データから構成されるデータ信号の転送は連続的であり、その転送量は大きく、無線通信の高速化に伴い転送量は今後更に大きくなる。また、複数の無線通信方式を同時に使用するマルチタスク時には、同時使用する無線通信方式の数に応じて、データ信号の転送量は更に大きくなる。また、データ信号はプロセッサユニット103a及び103bと外部I/F 102の間で転送される。また、データ信号は本質的には1ビット幅の論理情報で構成される。また、マルチタスク時にプロセッサユニット103aと103bが異なる無線通信方式を実現する場合、各無線通信方式での信号伝送は基本的に独立であるため、プロセッサユニット103aと103bによるデータ信号転送はそれぞれ独立に発生する。また、マルチタスクにおいて、例えばプロセッサユニット103aを用いて音声通信を行い、プロセッサユニット103bを用いてデータ通信を行う場合、外部I/F 102を介して接続される外部デバイスがプロセッサユニット毎に異なる可能性がある。従って、各プロセッサユニットによるデータ転送はお互いに影響を及ぼさない独立性を持つことが望ましい。

20

#### 【0026】

以上のように、本発明の無線通信装置内では、性質の異なる二つの信号である制御信号とデータ信号の転送が行なわれる。従って、これらの転送を単一のバスで行なう場合、一方の転送に効率の良いバス構成は、他方の転送には効率の悪いものとなる。また、これらの転送を単一のバスで行なう場合、転送量の大きなデータ信号の転送が制御信号の転送を圧迫し、制御信号の転送遅延を発生させる可能性もある。

30

#### 【0027】

上記に示したような、無線通信特有の制御信号転送とデータ信号転送の特徴を踏まえ、本発明のソフトウェア無線機では図1に示すように、制御信号の転送に適した構成を持ち専ら制御信号の転送に使用される制御バスと、データ信号の転送に適した構成を持ち専らデータ信号の転送に使用されるデータバスを別々に備える。以下、制御バスとデータバスの構成について説明する。

40

#### 【0028】

メインプロセッサ100、メモリ101、外部I/F 102及びプロセッサユニット103aと103bは制御バス120と接続されている。制御バス120は上記各構成要素間での制御信号やパラメータ、変数データ等の転送に使用される。具体的には制御バス120は、メインプロセッサ100から外部I/F 102及びプロセッサユニット103aと103bへのパラメータ設定や制御コマンド送信、或いは外部I/F 102及びプロセッサユニット103aと103bからメインプロセッサ100への内部状態報告や割込み等に使用される。また制御バス120は、メインプロセッサ100によって実施される処理に必要な変数データ等を、メインプロセッサ100がメモリ101との間でリード或いはライトする際にも使用される。ここで制御バス120としては、例えば汎用バスであるPCIバスやVMEバス等を用いればよい。これらのバスでは、バスに接続された各構

50

成要素は、データを送出する際には宛先装置のアドレスを指定して送出し、バス上で送信されているデータのうち自装置宛のアドレスが添付されたものを受信する。

【0029】

外部I/F 102及びプロセッサユニット103aと103bはデータバス121に接続される。データバス121は、本ソフトウェア無線機が受信して復調したデータを外部デバイスに出力する際に必要となる、プロセッサユニット103aと103bから外部I/F 102への受信データ転送に使用される。またデータバス121は、外部デバイスから入力されたデータを本ソフトウェア無線機が変調して送信する際に必要となる、外部I/F 102からプロセッサユニット103aと103bへの送信データ転送に使用される。このように、送受信データの転送に用いるデータバスを制御バスとは別に設けることにより、制御バスで転送される制御データは送受信データの多少に依存しない遅延量で転送することができる。また、データバスは、優先度の高い制御信号を扱う必要がないため、効率よく送受信データの転送を行うことが可能となる。

【0030】

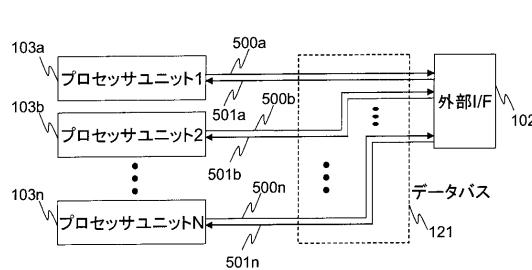

データバス121の構成の第一例を図2に示す。図2で、プロセッサユニット103a、103bと103nから出力される信号は、それぞれ独立の信号線500a、500bと500nを介して、外部I/F 102へ転送される。また、プロセッサユニット103a、103bと103nへ入力される信号は、それぞれ独立の信号線501a、501bと501nを介して、外部I/F 102から転送される。データバス121は、独立の信号線500a - n、501a - nの集合により構成される。

【0031】

上記のように図2の構成では、各プロセッサユニットと外部I/F 102の間で転送される送受信データは全て独立の信号線を介して転送される。従って、各プロセッサユニットと外部I/F 102の間の送受信データの転送速度や転送タイミングは高い自由度を持つことができる。また、各プロセッサユニットは信号線を占有できるため、送受信データ転送に関する制御が単純であり、ハードウェア構成を単純化することができる。この結果、図2の構成のデータバスを備えることにより、単純なハードウェア構成で高い自由度を持つソフトウェア無線機を実現することができる。なお図2では簡単のため、信号線500a、500b、500n、501a、501b、501nは一本しか描いていないが、各信号線はそれぞれ複数の信号線で構成されていてもよい。本実施例では、各プロセッサユニットは、専用の信号線により外部I/F102と接続されるため、アドレス情報を添付しなくてもデータ転送を行うことも可能である。この場合、オーバーヘッドを低減させるという効果も得られる。

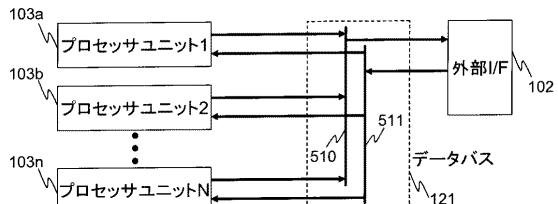

【0032】

データバス121の構成の第二例を図3に示す。図3で、プロセッサユニット103a、103bと103nから出力される信号は共通の信号線510を介して、外部I/F 102へ転送される。また、プロセッサユニット103a、103bと103nへ入力される信号は共通の信号線511を介して、外部I/F 102から転送される。

【0033】

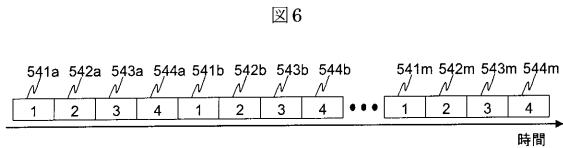

信号線510の共有方法の第一例を図6に示す。なお、信号線511の共有方法についても同様である。この例では図6に示すように、時間軸上にタイムスロット541a、542b等を設定し、当該タイムスロットを各プロセッサユニットに割り当てるにより、信号線510を複数のプロセッサユニットで共有する。具体的には例えば図6に示したように、四つのタイムスロット(541a、542a、543a、544a)が繰り返される(プロセッサの添え字a、b . . . nに対応)ようにタイムスロットを設定する。ここで例えば、図3のプロセッサユニット103aに一番のタイムスロット群を割り当てるにより、プロセッサユニット103aはタイムスロット541a、541b . . . 541mでデータ転送を行なうことが出来る。

【0034】

同様に例えば図3のプロセッサユニット103bに二番のタイムスロット群を割り当てることで、プロセッサユニット103bはタイムスロット542a、542b . . . 542mでデータ転送を、図3のプロセッサユニット103nに三番のタイムスロット群を割り当てることで、プロセッサユニット103nはタイムスロット543a、543b . . . 543mでデータ転送を、それぞれ実

10

20

30

40

50

施することが出来る。また、例えば図3のプロセッサユニット103nが他のプロセッサユニット103aや103bより多くのデータ転送を必要とする場合、プロセッサユニット103nに複数のタイムスロット、例えば三番と四番のタイムスロット、を割り当てることにより、プロセッサユニット103nはタイムスロット543a、544a、543b、544b . . . 543m、544mを使用してデータ転送を行なうことができる。この結果プロセッサユニット103nはプロセッサユニット103a及び103bと比較して、二倍のデータ転送を行なうことができる。タイムスロットの割当てはメインプロセッサで決定し、制御バスを用いてメインプロセッサから各プロセッサユニット103および外部I/F102に予め通知しておく構成にするとよい。

#### 【0035】

なお、上記ではタイムスロットを四つ設定した例を示したが、設定するタイムスロットの数はいくつでも良い。また信号線510を構成する信号線の本数は一本であっても複数本であっても良い。本実施例では、各プロセッサユニットがそれぞれ割当てられたタイムスロットで転送データの送受信を行うため、アドレス情報を添付しなくてもデータ転送を行うことも可能である。この場合、オーバーヘッドを低減させるという効果も得られる。

10

#### 【0036】

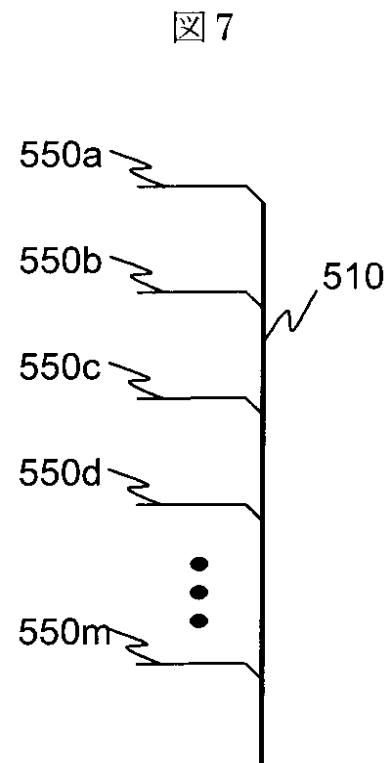

信号線510の共有方法の第二例を図7に示す。なお、信号線511の共有方法についても同様である。この例では図7に示すように、信号線510は複数の信号線550a、550b . . . 550mから構成され、各信号線を各プロセッサユニットに割り当てることにより、信号線510を複数のプロセッサユニットで共有する。具体的には例えば図3のプロセッサユニット103aに信号線550aを割り当てることにより、プロセッサユニット103aは信号線550aを用いてデータ転送を行なうことができる。同様に例えば図3のプロセッサユニット103bに信号線550bを割り当てることで、プロセッサユニット103bは信号線550bを用いてデータ転送を、図3のプロセッサユニット103nに信号線550cを割り当てることで、プロセッサユニット103nは信号線550cを用いてデータ転送を、それぞれ実施することが出来る。

20

#### 【0037】

また、無線通信方式の高速化などにより、例えば図3のプロセッサユニット103aが要求するデータ転送量が増加した場合は、従来の信号線550aに加え、信号線550dもプロセッサユニット103aに割り当てることで、プロセッサユニット103aのデータ転送量増加の要求に対応することが出来る。信号線の割当てはメインプロセッサで決定し、制御バスを用いてメインプロセッサから各プロセッサユニット103および外部I/F102に予め通知しておく構成にするとよい。本実施例では、各プロセッサユニットがそれぞれ割当てられた信号で転送データの送受信を行うため、アドレス情報を添付しなくてもデータ転送を行うことも可能となる。この場合、オーバーヘッドを低減させるという効果も実現できる。

30

#### 【0038】

上記のように図3の構成では、各プロセッサユニットと外部I/F 102の間で転送される送受信データは共通の信号線510と511を共有して転送される。従って信号線の数を減らすことができ、図2の例よりハードウェア規模を小さくすることができる。（図7の構成でも、プロセッサの数nよりも信号船の数mを少なくすれば、同様に図2の例よりもハードウェア規模を小さくすることができる。）また、上記の例のように割り当てるタイムスロットの数や信号線の数を変更することにより、各プロセッサユニットが必要とするデータ転送量に適したデータバスを構成することが可能である。この結果、図3の構成のデータバスを備えることにより、図2の例より少ないハードウェア規模で自由度の高いソフトウェア無線機を実現することができる。

40

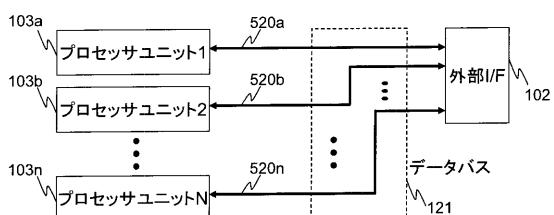

#### 【0039】

データバス121の構成の第三例を図4に示す。図4でプロセッサユニット103aから出力される信号、及びプロセッサユニット103aに入力される信号は信号線520aを共有して外部I/F 102との間で転送される。同様にプロセッサユニット103b及び103nに入出力される信号は、それぞれ信号線520b及び520nを使用して外部I/F 102との間で転送される。ここで、信号線520a、520b及び520nの共有方法は、図6及び図7で示した前記の方法を用いればよい。すなわち、たとえば信号線520aをタイムスロットに分割、あるいは複数本の信号線で構

50

成し、プロセッサユニット103aの入力と出力にそれぞれタイムスロット及び信号線を割り当てればよい。データバス121は、独立の信号線520a - nの集合により構成される。

#### 【 0 0 4 0 】

上記のように図4の構成では、各プロセッサユニットと外部I/F 102の間で転送される送受信データは一つの信号線を共有して転送される。従って信号線の数を減らすことができ図2の例よりハードウェア規模を小さくすることが出来る。また、前記の例のように割り当てるタイムスロットの数や信号線の数を変更することにより、プロセッサユニットの入力及び出力が必要とするデータ転送量に適したデータバスを構成することが可能である。この結果、図4の構成のデータバスを備えることにより、図2の例より少ないハードウェア規模で自由度の高いソフトウェア無線機を実現することができる。本実施例では、各プロセッサユニットは、専用の信号線により外部I/F102と接続されるため、アドレス情報を添付しなくてもデータ転送を行うことも可能である。この場合、オーバーヘッドを低減させるという効果も得られる。

#### 【 0 0 4 1 】

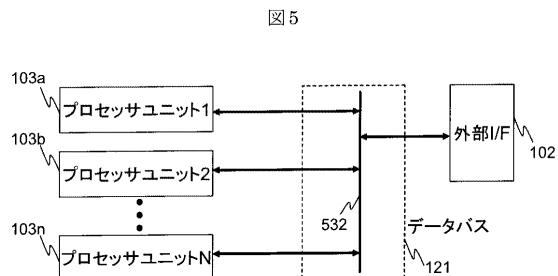

データバス121の構成の第四例を図5に示す。図5でプロセッサユニット103a、103b、103nから出力される信号、及びプロセッサユニット103a、103b、103nに入力される信号は全て、信号線532を共有して外部I/F 102との間で転送される。ここで、信号線532の共有方法は、図6及び図7で示した前記の方法を用いればよい。すなわち、たとえば信号線532をタイムスロットに分割、あるいは複数本の信号線で構成し、各プロセッサユニット及びその入力と出力にそれぞれタイムスロット及び信号線を割り当てればよい。

#### 【 0 0 4 2 】

上記のように図4の構成では、全てのプロセッサユニットと外部I/F 102の間で転送される送受信データは一つの信号線を共有して転送される。従って信号線の数を減らすことができ、図3及び図4の例よりハードウェア規模を小さくすることが出来る。また、前記の例のように割り当てるタイムスロットの数や信号線の数を変更することにより、各プロセッサユニットの入力及び出力が必要とするデータ転送量に適したデータバスを構成することが可能である。この結果、図4の構成のデータバスを備えることにより、図3及び図4の例より少ないハードウェア規模で自由度の高いソフトウェア無線機を実現することができる。本実施例では、各プロセッサユニットがそれぞれ割当てられたタイムスロットまたは信号線で転送データの送受信を行うため、アドレス情報を添付しなくてもデータ転送を行うことも可能である。この場合、オーバーヘッドを低減させるという効果も得られる。

#### 【 0 0 4 3 】

なお、以上ではデータバス121を制御バス120とは異なる方法で動作する実施例を説明したが、制御バス120と同様に、汎用バスとしてもよい。制御信号と送受信データを別のバスで転送するようにするだけでも、制御信号を遅延なく転送することができるというメリットがある。ただし、データバス121の転送能力は、送受信データの通信速度に対応できる程度のものとする必要があるため、制御バス120よりも高い転送能力が必要となる。

#### 【 0 0 4 4 】

図1でプロセッサユニット103aと103bはユニット間インターフェース118で接続される。ユニット間インターフェース118は、プロセッサユニット103aと103bの間での制御信号やデータ信号の転送に使用される。ユニット間インターフェース118を用いて転送される信号としては、例えばクロック信号や、プロセッサユニット103aと103bが同期動作をするために必要な同期信号等がある。また、例えばプロセッサユニット103aが復調処理を行ない、プロセッサユニット103bが誤り制定処理を行う場合のように、一方のプロセッサユニットが実施した信号処理の結果を他方のプロセッサユニットに転送する際にも、ユニット間インターフェース118を用いた信号転送を行なっても良い。

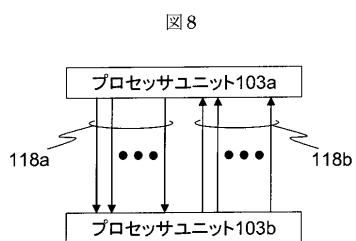

#### 【 0 0 4 5 】

ユニット間インターフェース118の構成の例を図8に示す。図8の例では、ユニット間インターフェースとしてプロセッサユニット103aから出力される信号線118aと、プロセッサユニット103bに入力される信号線118bが予め備えられている。ここで信号線118a及び118bを構

10

20

30

40

50

成する信号線の数は一本でも複数本でも良い。各信号線にどのような信号を割り当てるかは、プロセッサユニット103a及び103bに割り当てられた機能に応じて、例えばメインプロセッサ100が決定し、制御バスで各プロセッサユニットに通知するようにして制御すればよい。

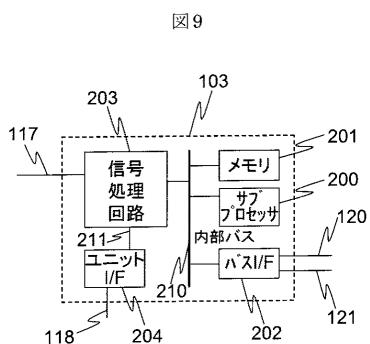

#### 【0046】

図1のプロセッサユニット103(図1では103aと103bの符号を付してある)の構成の例を図9に示す。プロセッサユニット103はサブプロセッサ200、メモリ201、バスI/F 202、信号処理回路203及び、ユニットI/F 204から構成され、構成要素は内部バス210を介して接続されている。図9の例ではユニットI/F 204は信号線211を介して信号処理回路203のみと接続されているが、内部バス210とも接続しても良い。バスI/F202は制御バス120及びデータバス121に接続される。信号処理回路203は、信号線117を介してアナログとデジタルのインターフェースを担うアナログフロントエンド、アナログ信号の変復調処理を行なう無線信号処理部、及び無線周波数の信号を送受信するアンテナ部と接続され、送受信信号のベースバンド処理を行う。

10

#### 【0047】

なお図9では、簡単のため上記のアナログフロントエンド、無線信号処理部及びアンテナは図示していない。ユニットI/F204は、信号線118を介して他のプロセッサユニットのユニットI/Fと接続される。プロセッサユニット103は、固定の通信プロトコル対応のものでもよく、また、メモリ201或いは図1のメモリ101に格納されるソフトウェアの書換えにより様々な通信プロトコルに対応して動作することが可能な、いわゆるソフトウェア無線機用のプロセッサユニットでも良い。

20

#### 【0048】

サブプロセッサ200はプロセッサユニット103全体の制御を行なう。また、サブプロセッサ200は、主に信号処理回路203と連携して、例えば無線通信のフレーム処理のように比較的時間制約の厳しい信号処理や、例えばアダプティブアレイアンテナ制御のように比較的高速で且つ複雑な演算が必要な信号処理を行なう。ここでサブプロセッサ200としては、例えば一般的なDSPを用いればよい。

#### 【0049】

メモリ201はサブプロセッサ200が信号処理を行なうためのワークメモリとして使用される。また、メモリ201はサブプロセッサ200と信号処理回路203が信号をやりとりするためのバッファ領域として利用されてもよい。また、メモリ201はサブプロセッサ200や信号処理回路203の動作を規定するプログラムやコンフィグレーションデータを格納してもよい。ここで、メモリ201としては、例えば汎用的なSRAMやDRAM等を用いればよい。

30

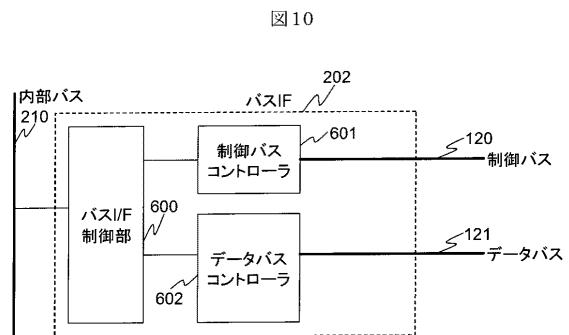

バスI/F 202はプロセッサユニット103が制御バス120及びデータバス121を介して、本発明のソフトウェア無線機の他の構成要素との間で信号を転送するためのインターフェースを担う。

#### 【0050】

バスIF 202の構成例を図10に示す。バスI/F制御部600は、内部バス210を介して行なわれるバスIF 202へのアクセスのアクセス制御を行なう。具体的には、例えばプロセッサユニット103がバスI/F 202を介して制御バス120あるいはデータバス121にデータを出力する場合、バスI/F制御部600は以下の動作を行なう。バスI/F制御部600は内部バス210から指定されるアドレスをデコードし、当該アドレスが制御バス120に割当てられたアドレス空間に含まれる場合は制御バスコントローラ601へデータを出力し、当該アドレスがデータバス121に割当てられたアドレス空間に含まれる場合はデータバスコントローラ602へデータを出力する。ここで、内部バス210から指定されるアドレスとしては、図1に記載の構成要素、例えばメモリ101や外部I/F 102、に含まれるメモリやレジスタ等を特定するアドレスを用いれば良い。また、内部バス210から指定されるアドレスとして、バスI/F 202に含まれるメモリやレジスタ等を特定するアドレスを用ても良い。またこの際バスI/F制御部600は、必要であれば制御バスやデータバスで使用されるアドレスや制御信号等も制御バスコントローラ601及びデータバスコントローラ602へ出力しても良い。

40

50

## 【0051】

プロセッサユニット103がバスI/F 202を介して制御バス120あるいはデータバス121からデータを入力する場合には、バスI/F制御部600は以下の動作を行なう。バスI/F制御部600は内部バス210から指定されるアドレスをデコードし、当該アドレスが制御バス120に割当てられたアドレス空間に含まれる場合は制御バスコントローラ601からデータを読み出し、当該アドレスがデータバス121に割当てられたアドレス空間に含まれる場合はデータバスコントローラ602からデータを読み出す。ここで、内部バス210から指定されるアドレスとしては、図1に記載の構成要素、例えばメモリ101や外部I/F 102、に含まれるメモリやレジスタ等を特定するアドレスを用いれば良い。また、内部バス210から指定されるアドレスとして、バスI/F 202に含まれるメモリやレジスタ等を特定するアドレスを用ても良い。またこの際バスI/F制御部600は、必要であれば制御バスやデータバスで使用されるアドレスや制御信号等を制御バスコントローラ601及びデータバスコントローラ602へ出力しても良い。10

## 【0052】

なお、外部I/F102も各プロセッサユニットのバスI/Fと同様の構成・動作のバスI/Fを具備する。

制御バスコントローラ601は、制御バス120のプロトコルに従って、制御バス120を介してデータを転送するための制御を行なう。具体的には、例えば制御バス120として、前記のようにPCIバスが用いられた場合、制御バスコントローラ601はPCIバスで規定されたデータ転送処理を行なうためのアドレス、データ及び制御信号の転送を行う。また、制御バスコントローラ601は、必要であればメモリを含んでもよい。20

## 【0053】

データバスコントローラ602は、データバス121のプロトコルに従って、データバス121を介してデータを転送するための処理を行なう。具体的には、例えばデータバス121として図2～図7で示した例が用いられた場合、データバスコントローラ602は、図6に示したタイムスロットや図7で示した信号線割り当ての管理を行い、当該プロセッサユニットに割り当てられたタイムスロットや信号線を用いてデータの転送を行なう。また、データバスコントローラ602は、必要であればメモリを含んでもよい。図2から7について説明したように、データバス上での転送ではアドレス情報を省略することも可能なので、データバスコントローラ602は、当該プロセッサユニットに割り当てられたタイムスロットや信号線を用いてアドレス情報なしにデータの送受信を行うことができる。30

## 【0054】

図9の信号処理回路203は、例えば波形整形や拡散処理のように、非常に高速で且つ時間制約の厳しい信号処理を行なう。ここで信号処理回路203は、例えば専用LSIやFPGA等を単独或いは組み合わせて構成すれば良い。

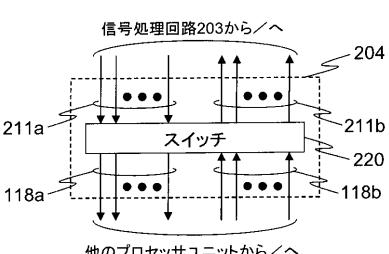

図9のユニットI/F 204は、ユニット間インターフェース108を介してプロセッサユニット同士で信号転送を行なうためのインターフェースを担う。ユニットI/F 204の構成の一例を図11に示す。スイッチ220は、信号処理回路203から入力されてくる信号線211aの各信号線を、他のプロセッサユニットへ出力される信号線118aの所望の信号線と接続する。また、スイッチ220は、他のプロセッサユニットから入力されてくる信号線118bの各信号線を、信号処理回路203へ出力される信号線211bの所望の信号線と接続する。スイッチ220での信号線の接続に関する制御は、信号処理回路203やサブプロセッサ200、あるいはメインプロセッサ100から行なえばよい。40

## 【0055】

内部バス210は、制御バス120と同様に、例えば汎用バスであるPCIバスやVMEバス等を用いればよい。

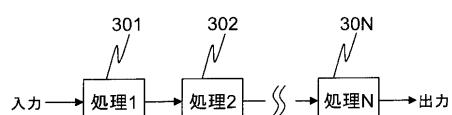

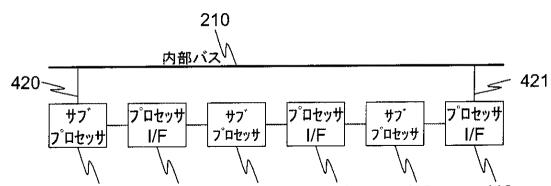

図9に示したプロセッサユニット103は、一つのサブプロセッサ200を含んだ例であるが、プロセッサユニット103は複数のサブプロセッサを含んでもよい。一般に、無線通信の信号処理は図12のように、複数の信号処理301、302...30Nが直列に行なわれる特徴を持つ。従ってこの特徴を利用することにより、複数のサブプロセッサで無線通信の信号処理50

を行なう場合の、サブプロセッサの接続方法を簡単化することができる。プロセッサユニット103が複数のサブプロセッサを含む場合の、サブプロセッサの接続方法の例を図13に示す。図13の例では、三つのサブプロセッサ(400a、400b、400c)が三つのプロセッサI/F(410、411、412)を介してシリアルに接続され、先頭のサブプロセッサ400aと最後のプロセッサI/F 412が、それぞれ信号線420と421を介して内部バス210に接続されている。ここでプロセッサI/F(410、411、412)としては、例えばデュアルポートメモリを用いればよい。また図13には図示していないが、プロセッサI/F 410及び411も内部バス210に接続しても良い。

#### 【0056】

図13のように複数のサブプロセッサを接続した場合の動作を以下で説明する。第一のサブプロセッサ400aは、内部バス210から信号線420を介して入力された信号に対して第一の信号処理を行い、結果をプロセッサI/F 410に書き込む。第二のサブプロセッサ400bは、前記サブプロセッサ400aが書き込んだ結果をプロセッサI/F 410から読み込み、当該結果に対して第二の信号処理を行い、結果をプロセッサI/F 411に書き込む。第三のサブプロセッサ400cは、前記サブプロセッサ400bが書き込んだ結果をプロセッサI/F 411から読み込み、当該結果に対して第三の信号処理を行い、結果をプロセッサI/F 412に書き込む。プロセッサI/F 412に書き込まれた信号処理結果は、信号線421及びデータバス210を介して、図9のプロセッサユニット103の構成要素、例えば信号処理回路203やバスI/F 202など、へ転送される。

#### 【0057】

上記のように複数のサブプロセッサを直列に接続し動作させることにより、図12に示した直列処理を特徴とする無線通信の信号処理を実現することができる。なお、図13の例では三つのサブプロセッサを接続する場合を例として示したが、接続するサブプロセッサの数は三以外の数であっても良い。

#### 【図面の簡単な説明】

#### 【0058】

【図1】本発明の無線通信装置のハードウェア構成図。

【図2】データバスの構成の第一例。

【図3】データバスの構成の第二例。

【図4】データバスの構成の第三例。

【図5】データバスの構成の第四例。

【図6】データバスの信号線の共有方法の第一例。

【図7】データバスの信号線の共有方法の第二例。

【図8】ユニット間インターフェースの構成例。

【図9】プロセッサユニットの構成例。

【図10】プロセッサユニット内バスI/Fの構成例。

【図11】プロセッサユニット内ユニットI/Fの構成例。

【図12】無線通信の信号処理の特徴。

【図13】複数のサブプロセッサの接続方法の例。

【図14】従来のソフトウェア無線機の構成の第一例。

【図15】従来のソフトウェア無線機の構成の第二例。

#### 【符号の説明】

#### 【0059】

1...アンテナ、2...無線送受信部、3...信号処理回路、4A、4B、4C...バス、5、5a、5b...バス間インターフェース、11...第一のプロセッサ、12、22、32...命令メモリ、13、23、33...データメモリ、14...キャッシュメモリ、15...入出力装置、21...第二のプロセッサ、31...第三のプロセッサ、

100...メインプロセッサ、101、201...メモリ、102...外部I/F、103、103a、103b、103n...プロセッサユニット、112、117、117a、117b、118、118a、118b、211a、211b...信号線、120...制御バス、121...データバス、

10

20

30

40

50

500a、500b、500n、501a、501b、501n、510、511、520a、520b、520n、532、550a、550b、550c、550d、550n、...データバス信号線、

541a、542a、543a、544a、541b、542b、543b、544b、541m、542m、543m、544m...データバスタイムスロット、

200、400a、400b、400c...サブプロセッサ、202...バスI/F、203...信号処理回路、204...ユニットI/F、210...内部バス、220...スイッチ、

301、302、30N...信号処理ステップ、420、421...内部バス信号線、410、411、412...プロセッサI/F、

600...バスI/F制御部、601...制御バスコントローラ、602...データバスコントローラ。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

---

フロントページの続き

(51)Int.Cl. F I

H 04M 11/00 (2006.01) H 04M 1/00 V

H 04M 11/00 302

(72)発明者 石川 崇

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

審査官 鈴村 理絵子

(56)参考文献 特開2003-037655 (JP, A)

特開平11-265342 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 36

G 06 F 13 / 38

H 04 B 1 / 38

H 04 B 7 / 26

H 04 M 1 / 00

H 04 M 11 / 00