(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5150518号

(P5150518)

(45) 発行日 平成25年2月20日(2013.2.20)

(24) 登録日 平成24年12月7日(2012.12.7)

(51) Int.Cl.

F 1

|                   |                  |                   |             |

|-------------------|------------------|-------------------|-------------|

| <b>H01L 23/12</b> | <b>(2006.01)</b> | <b>H01L 23/12</b> | <b>501B</b> |

| <b>H01L 21/60</b> | <b>(2006.01)</b> | <b>H01L 23/12</b> | <b>501Z</b> |

| <b>H05K 3/46</b>  | <b>(2006.01)</b> | <b>H01L 21/60</b> | <b>311S</b> |

| <b>H05K 3/34</b>  | <b>(2006.01)</b> | <b>H05K 3/46</b>  | <b>Q</b>    |

|                   |                  | <b>H05K 3/34</b>  | <b>502E</b> |

請求項の数 18 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2009-1253 (P2009-1253)

(22) 出願日

平成21年1月7日(2009.1.7)

(65) 公開番号

特開2009-260255 (P2009-260255A)

(43) 公開日

平成21年11月5日(2009.11.5)

審査請求日

平成22年2月12日(2010.2.12)

(31) 優先権主張番号

特願2008-77557 (P2008-77557)

(32) 優先日

平成20年3月25日(2008.3.25)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100107641

弁理士 鎌田 耕一

(74) 代理人 100148769

弁理士 麻生 紀明

(72) 発明者 萩原 清己

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 今井 淳一

最終頁に続く

(54) 【発明の名称】半導体装置および多層配線基板ならびにそれらの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

裏面に電極パッドが設けられた半導体チップと、表面に前記電極パッドと対向する接続パッドが設けられた多層配線基板と、を備え、

前記電極パッドは、前記半導体チップの裏面の各角に近接して配置された電極パッドを含む第1電極パッドと、前記第1電極パッド以外の第2電極パッドとからなり、

前記接続パッドは、前記第1電極パッドとバンプを介して接続された第1接続パッドと、前記第2電極パッドとバンプを介して接続された第2接続パッドとからなり、

前記多層配線基板は、前記第1接続パッドを支持する第1絶縁領域と、前記第2接続パッドを支持する第2絶縁領域とを有し、

前記第1絶縁領域は、熱可塑性樹脂で構成されており、前記第2絶縁領域は、熱硬化性樹脂で構成されている、半導体装置。

## 【請求項 2】

前記多層配線基板は、第1絶縁領域を構成する第1絶縁層と、第2絶縁領域を構成する第2絶縁層とを有し、前記第1絶縁層は、前記第2絶縁層上に積層されている、請求項1に記載の半導体装置。

## 【請求項 3】

裏面に電極パッドが設けられた半導体チップと、表面に前記電極パッドと対向する接続パッドが設けられた多層配線基板と、を備え、

前記電極パッドは、前記半導体チップの裏面の各角に近接して配置された電極パッドを

10

20

含む第1電極パッドと、前記第1電極パッド以外の第2電極パッドとからなり、

前記接続パッドは、前記第1電極パッドとバンプを介して接続された第1接続パッドと、前記第2電極パッドとバンプを介して接続された第2接続パッドとからなり、

前記多層配線基板は、前記第1接続パッドを支持する第1絶縁領域を構成する第1絶縁層と、前記第2接続パッドを支持する第2絶縁領域を構成する第2絶縁層とを有し、

前記第1絶縁層は、前記第2絶縁層上に積層されている、半導体装置。

**【請求項4】**

前記第1絶縁層は、熱可塑性樹脂で構成されており、前記第2絶縁層は、熱硬化性樹脂で構成されている、請求項3に記載の半導体装置。

**【請求項5】**

前記第1絶縁層の厚さは、前記多層配線基板中の第1絶縁層の下にある回路パターンの厚さの1.5倍以上であり、かつ、前記第2電極パッドと前記第2接続パッドの間に形成されるバンプの高さの2分の1以下である、請求項2～4のいずれか一項に記載の半導体装置。

**【請求項6】**

前記多層配線基板は、前記第1絶縁層および前記第2絶縁層を覆い、前記第1接続パッドおよび前記第2接続パッドに対応する位置に開口が設けられたソルダーレジストをさらに有し、

前記第1接続パッドに対応する位置の開口の大きさは、前記第2接続パッドに対応する位置の開口の大きさよりも大きく設定されている、請求項2～5のいずれか一項に記載の半導体装置。

**【請求項7】**

前記バンプは、いずれも略同じ体積のはんだバンプである、請求項1～6のいずれか一項に記載の半導体装置。

**【請求項8】**

前記熱可塑性樹脂は、融点が280℃以上のものである、請求項1、2または4に記載の半導体装置。

**【請求項9】**

前記熱硬化性樹脂は、無機フィラーが配合されたものである、請求項1、2、4または8に記載の半導体装置。

**【請求項10】**

前記多層配線基板と前記半導体チップとの間には、アンダーフィルが充填されている、請求項1～9のいずれか一項に記載の半導体装置。

**【請求項11】**

前記多層配線基板は、裏面に外部接続用パッドが設けられたインターポーラである、請求項1～10のいずれか一項に記載の半導体装置。

**【請求項12】**

前記多層配線基板は、ガラスクロスを含むコア基板を有している、請求項1～11のいずれか一項に記載の半導体装置。

**【請求項13】**

表面上に半導体チップが実装される多層配線基板であって、

前記表面上の矩形領域内に配置された複数のパッドと、前記複数のパッドのうち少なくとも四隅に位置するパッドを支持する第1絶縁領域を構成する第1絶縁層と、前記複数のパッドのうち前記第1絶縁層で支持されるパッド以外のパッドを支持する第1絶縁領域を構成する第2絶縁層と、を備え、

前記第1絶縁層は、熱可塑性樹脂で構成されており、前記第2絶縁層は、熱硬化性樹脂で構成されているとともに、前記第1絶縁層は、前記第2絶縁層上に積層されている、多層配線基板。

**【請求項14】**

前記第1絶縁層の厚さは、5～50μmである、請求項13に記載の多層配線基板。

10

20

30

40

50

**【請求項 15】**

前記多層配線基板は、前記第1絶縁層および前記第2絶縁層を覆い、前記複数のパッドに対応する位置に開口が設けられたソルダーレジストをさらに有し、

前記第1絶縁層で支持されるパッドに対応する位置の開口の大きさは、前記第2絶縁層で支持されるパッドに対応する位置の開口の大きさよりも大きく設定されている、請求項13または14に記載の多層配線基板。

**【請求項 16】**

前記熱可塑性樹脂は、融点が280以上ものである、請求項13～15のいずれか一項に記載の多層配線基板。

**【請求項 17】**

前記熱硬化性樹脂は、無機フィラーが配合されたものである、請求項13～16のいずれか一項に記載の多層配線基板。

10

**【請求項 18】**

ガラスクロスを含むコア基板をさらに有する、請求項13～17のいずれか一項に記載の多層配線基板。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、多層配線基板およびこれに半導体チップが実装された半導体装置ならびにそれらの製造方法に関する。

20

**【背景技術】****【0002】**

近年、電子機器では、高機能化および軽薄短小化の要求に伴い、電子部品の高密度集積化、さらには高密度実装化が進んできている。このような電子機器に使用される半導体装置（半導体パッケージ）では、従来にもまして小型化かつ多ピン化が進んできている。

**【0003】**

従来のようなリードフレームを使用した形態のパッケージでは、小型化に限界がきいている。そこで、半導体装置の高密度集積化と高密度実装化を可能とするために、ワイヤボンディング実装、TAB (Tape Automated Bonding) 実装、またはフリップチップ実装によって半導体装置を構成することが行われている。これらの実装技術の中でもフリップチップ実装技術が、半導体装置の大きさを抑えて半導体装置の最も高密度な実装を可能とする技術として、コンピュータ機器または高機能モバイル機器などに使用される半導体装置に多く用いられている。

30

**【0004】**

フリップチップ実装では、多層配線基板上に半導体チップが実装される。具体的には、半導体チップの裏面に、電極端子、実際には電極パッドを予め形成しておき、多層配線基板上に、電極パッドと対応する接続パッドを設ける。そして、電極パッドと接続パッドとを、導電性バンプを利用して接続する（例えば、特許文献1参照）。導電性バンプは、金やはんだなどの導電性金属によって形成されるが、実装の容易さおよび接合部での応力緩和といった観点からはなんだが使用されることが多い。このはんだバンプは、ボール搭載法、ペースト印刷法、またはめっき法などの工法により形成されうる。

40

**【0005】**

フリップチップ実装では、面実装のために小さい面積で多数の電気的接続を行うことができるものの、半導体装置の小型化かつ多ピン化に伴って接続パッドの狭ピッチ化を招くことになる。接続パッドのピッチが狭くなるにつれて、はんだバンプの高さも低くなる傾向がある。今後は、このように狭いピッチ（特に接続パッドピッチが200μm以下）での接続形態をもつ半導体装置が主流になると考えられる。

**【0006】**

はんだバンプを形成する一般的な工法としては、生産性およびコストの観点から、ペースト印刷法が広く採用されていた。しかしながら、この工法では、はんだバンプのピッチ

50

が狭くなると、はんだ印刷時に隣り合うバンプ同士の短絡が発生し、歩留まりを極端に低下せることがある。そこで、狭ピッチのはんだバンプの形成には、電解めっきによってはんだバンプを形成するめっき法、またははんだボールをパッド上に搭載してリフローすることによりはんだバンプを形成するボール搭載法が望ましい工法となっている。

#### 【0007】

また、フリップチップ実装に使用される多層配線基板としては、配線の高密度化、軽量化、薄型化、さらには低コストといった観点から、ビルドアップ工法により製造されたビルドアップ基板が多く用いられている。このビルドアップ基板は、ガラスクロスにエポキシ樹脂を含浸させたガラスエポキシ基板（コア基板）上に回路パターンと絶縁層を交互に形成していく、半導体チップとの電気的な接続を行うための接続パッドを表面に形成したものである。絶縁層の形成には、熱硬化性の絶縁樹脂が用いられる。10

#### 【0008】

しかしながら、半導体チップと多層配線基板とでは、それぞれの熱膨張率が大きく異なる。するために、半導体チップおよび多層配線基板がフリップチップ実装時または実装後において大きな温度変化を受けると、半導体チップと多層配線基板との接続を担うはんだバンプに応力が集中し、はんだバンプまたはその近傍にクラックが発生して接続不良が起きるおそれがあった。

#### 【0009】

そこで、接続信頼性確保のために、フリップチップ実装後に半導体チップと多層配線基板との間のギャップ部分にアンダーフィルと呼ばれる絶縁性の樹脂を注入充填して硬化させることで、はんだバンプを封じ込める技術も実施されている。ところが、前述したように、半導体装置の小型化かつ多ピン化によりはんだバンプがますます微細化することによって、はんだバンプへの応力負荷は多大なものとなり、樹脂によるはんだバンプの封じ込めによる保護だけではクラックの発生は防げなくなることが懸念される。20

#### 【0010】

このような問題に対する対策として、例えば特許文献2に記載されているように、はんだバンプのうち特に応力が集中する四隅に位置するはんだバンプの体積を大きくすることによりその位置のはんだバンプの断面積を大きくすることが考えられる。

【特許文献1】特開2001-135749号公報

【特許文献2】特開2007-242782号公報30

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、一部のはんだバンプのみの体積を大きくするには、同一サイズのはんだボールをパッド上に搭載するボール搭載法は不向きである。特許文献2には、それを実現するにはペースト印刷法またはペーストイスピエンス法が好ましいことが記載されているが、これらの工法は、前述したように狭ピッチのはんだバンプの形成に不向きである。そこで、はんだバンプの体積をどれも同程度に保ったままでクラックの発生を抑えられるようになることが望まれる。

#### 【0012】

本発明は、上述の事情に鑑みてなされたものであり、接続パッドピッチが $200\mu m$ 以下であってもバンプの体積をどれも同程度に保ったままでクラックの発生を抑えることのできる半導体装置およびこれに用いる多層配線基板ならびにそれらの製造方法を提供することを目的とする。40

#### 【課題を解決するための手段】

#### 【0013】

前記目的を達成するために、本発明は、裏面に電極パッドが設けられた半導体チップと、表面に前記電極パッドと対向する接続パッドが設けられた多層配線基板と、を備え、前記電極パッドは、前記半導体チップの裏面の各角に近接して配置された電極パッドを含む第1電極パッドと、前記第1電極パッド以外の第2電極パッドとからなり、前記接続パッ50

ドは、前記第1電極パッドとバンプを介して接続された第1接続パッドと、前記第2電極パッドとバンプを介して接続された第2接続パッドとからなり、前記多層配線基板は、前記第1接続パッドを支持する第1絶縁領域と、前記第2接続パッドを支持する第2絶縁領域とを有し、前記第1絶縁領域は、熱可塑性樹脂で構成されており、前記第2絶縁領域は、熱硬化性樹脂で構成されている、半導体装置を提供する。

#### 【0014】

ここで、第1電極パッドとは、電極パッドのうち半導体チップの裏面の中心から比較的に遠くに位置する電極パッドのことであり、第2電極パッドとは、半導体チップの裏面の中心側に一塊の電極パッド群を構成する電極パッドのことである。

#### 【0015】

本発明は、他の側面から、裏面に電極パッドが設けられた半導体チップと、表面に前記電極パッドと対向する接続パッドが設けられた多層配線基板と、を備え、前記電極パッドは、前記半導体チップの裏面の各角に近接して配置された電極パッドを含む第1電極パッドと、前記第1電極パッド以外の第2電極パッドとからなり、前記接続パッドは、前記第1電極パッドとバンプを介して接続された第1接続パッドと、前記電極パッドのうち前記第2電極パッドとバンプを介して接続された第2接続パッドとからなり、前記多層配線基板は、前記第1接続パッドを支持する第1絶縁領域を構成する第1絶縁層と、前記第2接続パッドを支持する第2絶縁領域を構成する第2絶縁層とを有し、前記第1絶縁層は、前記第2絶縁層上に積層されている、半導体装置を提供する。

#### 【0016】

また、本発明は、表面上に半導体チップが実装される多層配線基板であって、前記表面上の矩形領域内に配置された複数のパッドと、前記複数のパッドのうち少なくとも四隅に位置するパッドを支持する第1絶縁領域を構成する第1絶縁層と、前記複数のパッドのうち前記第1絶縁層で支持されるパッド以外のパッドを支持する第2絶縁領域を構成する第2絶縁層と、を備え、前記第1絶縁層は、熱可塑性樹脂で構成されており、前記第2絶縁層は、熱硬化性樹脂で構成されるとともに、前記第1絶縁層は、前記第2絶縁層上に積層されている、多層配線基板を提供する。

#### 【0017】

さらに、本発明は、ガラスクロスを含むコア基板上に、回路パターンを形成する工程と、前記回路パターンが形成されたコア基板上に、熱硬化性樹脂で下側絶縁層を形成する工程と、前記下側絶縁層上に、前記コア基板上の前記回路パターンと電気的に接続された複数のパッドおよび回路パターンを形成する工程と、前記回路パターンが形成された前記下側絶縁層上に、前記複数のパッドを取り囲むように熱可塑性樹脂で上側絶縁層を形成する工程と、前記上側絶縁層上に、前記下側絶縁層上の前記回路パターンと電気的に接続された複数のパッドを形成する工程と、を含む、多層配線基板の製造方法を提供する。

#### 【0018】

また、本発明は、前記の多層配線基板の製造方法により製造された多層配線基板、および裏面に電極パッドが設けられた半導体チップを用意し、前記電極パッド上にはんだボールを搭載してリフローすることによりはんだバンプを形成し、前記多層配線基板の表面上に前記半導体チップを前記接続パッドと前記電極パッドとが前記はんだバンプを挟んで対向するように搭載し、その状態でリフローすることにより前記多層配線基板の表面上に前記半導体チップを実装する、半導体装置の製造方法を提供する。

#### 【発明の効果】

#### 【0019】

前記の第1の構成によれば、温度変化による応力が特に集中する位置のバンプと接続された第1接続パッドが、熱可塑性樹脂で構成された第1絶縁領域で支持されている。このため、周囲環境温度が高温になった場合には第1絶縁領域が軟化するようになる。このような第1絶縁領域の軟化によって、第1接続パッドと接続されたバンプにかかる応力を緩和することができる。従って、いずれも略同じ体積のバンプを用いても、クラックの発生を効果的に抑えることができる。しかも、残りのバンプと接続された第2接続パッドが、

10

20

30

40

50

熱硬化性樹脂で構成された第2絶縁領域で支持されている。このため、周囲環境温度が高温になった場合でも第2接続パッドは定位置に保たれる。それ故に、多層配線基板と半導体チップとの接合強度を高く保ちつつ前記の効果を得ることができる。

#### 【0020】

前記の第2の構成によれば、温度変化による応力が特に集中する位置のバンプと接続された第1接続パッドを支持する第1絶縁層が、他の位置のバンプと接続された第2接続パッドを支持する第2絶縁層上に積層されている。すなわち、第1接続パッドと第2接続パッドとの間には高低差が形成されていて、第1接続パッドが第2接続パッドよりも半導体チップに近づいている。このため、バンプがいずれも略同じ体積となっていても、第1接続パッドに接続されたバンプを第2接続パッドに接続されたバンプよりも押し広げられた形状とすることができます。これにより、第1接続パッドと接続されたバンプにかかる応力を、当該バンプの大きく拡張された断面積によって小さくすることができる。従って、いずれも略同じ体積のバンプを用いても、クラックの発生を効果的に抑えることができる。10

#### 【0021】

このように、本発明によれば、温度変化によるクラックの発生を抑えることができ、半導体チップと多層配線基板との高い接続信頼性を得ることができます。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下、図面を参照して、本発明の実施形態について説明する。なお、以下に示す実施形態は本発明の最良の実施形態の一例であって、本発明はこの実施形態に限定されるものではない。20

#### 【0023】

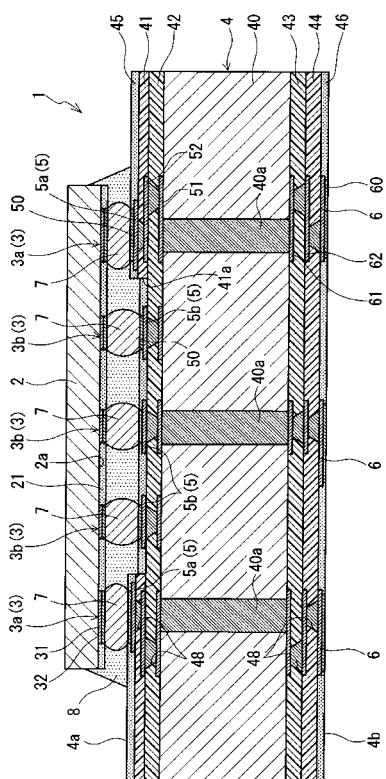

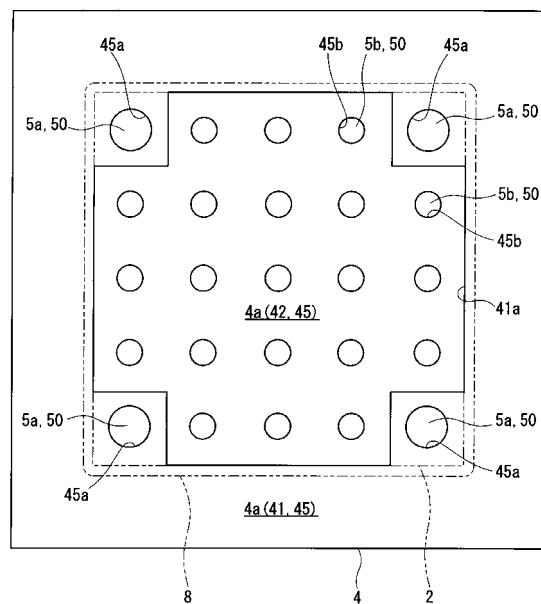

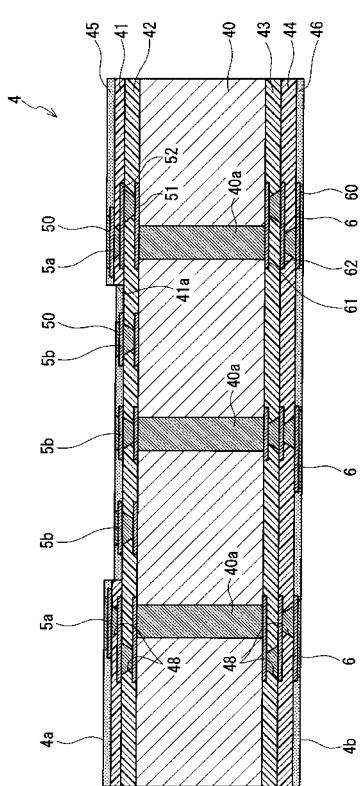

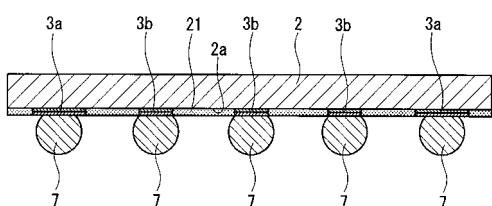

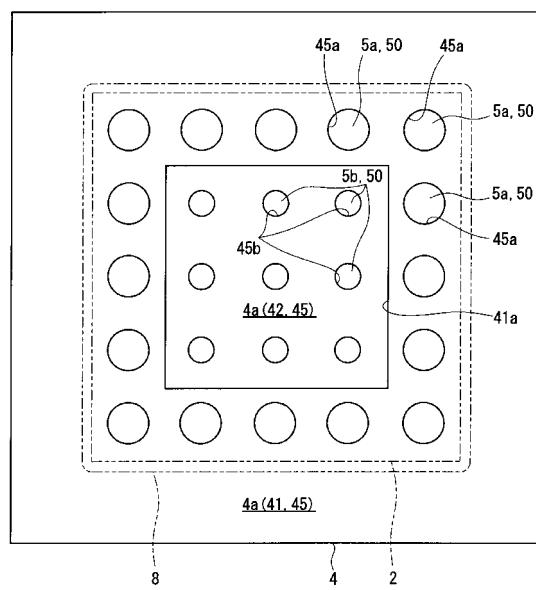

図1および図2に示すように、本発明の一実施形態に係る半導体チップ1は、多層配線基板4と、この多層配線基板4の表面4a上に実装された半導体チップ2とを備えている。なお、図2では、半導体チップ2および後述するアンダーフィル8を二点鎖線で示している。

#### 【0024】

半導体チップ2は、フラットな矩形板状の形状を有している。半導体チップ2の裏面2aには、複数（例えば1000～2000個、図面は簡略化のため25個で作図）の電極パッド3が設けられている。これらの電極パッド3は、行列状に配置されていてもよいし、千鳥状に配置されていてもよい。30

#### 【0025】

各電極パッド3は、例えば円形状をなしており、アルミパッド31上にUBM(Under Bump Metal)32が積層されて構成されている。UBM32を構成するには、例えば、アルミパッド31上に、厚さ10μmの無電解ニッケルめっき層を形成し、さらにその上に厚さ0.1μmの金めっき層を形成すればよい。また、半導体チップ2の裏面2aの電極パッド3以外の領域は、例えばポリイミド樹脂からなる絶縁保護膜21で覆われている。

#### 【0026】

より詳しくは、電極パッド3は、半導体チップ2の裏面2aの各角（4つの頂点）に近接して配置された第1電極パッド3aと、それ以外の第2電極パッド3bとで構成されている。第1電極パッド3aの大きさは、第2電極パッド3bの大きさよりも大きく設定されていることが好ましい。例えば、第1電極パッド3aの直径を140μm、第2電極パッド3bの直径を100μmとしてもよい。40

#### 【0027】

多層配線基板4は、コア基板40の表裏両面上に回路パターンと絶縁層とが交互に積層されて構成されたインターポーザである。多層配線基板4の表面4aには、電極パッド3とそれぞれ対向する複数の接続パッド5が設けられており、裏面4bには、接続パッド5とそれぞれ電気的に接続された複数の外部接続用パッド6が設けられている。

#### 【0028】

具体的に、コア基板40の表面上には、回路パターン51、第2絶縁層（下側絶縁層）50

42、回路パターン52、第1絶縁層(上側絶縁層)41がこの順に積層されており、コア基板40の裏面上には、回路パターン61、第3絶縁層43、回路パターン62、第4絶縁層44がこの順に積層されている。第1絶縁層41は、第2絶縁層42を露出させて半導体チップ2の裏面2aに対向させる開口41aを有している。そして、第1絶縁層41および第2絶縁層42によって接続パッド5が支持されており、第4絶縁層44によって外部接続用パッド6が支持されている。なお、第1絶縁層41は、後述する第1接続パッド5aを支持する第1絶縁領域を構成しており、第2絶縁層42は、後述する第2接続パッド5bを支持する第2絶縁領域を構成している。

#### 【0029】

本実施形態では、開口41aは、十字状に形成されている。すなわち、第1絶縁層41は、開口41aによって半導体チップ2の裏面2aの四隅にのみ対向する形状に形成されており、第2絶縁層42は、開口41aを通じて半導体チップ2の裏面2aの四隅を除く部分に対向している。

#### 【0030】

各絶縁層41～44には、当該絶縁層41～44の中を通ってパッド5(または6)と回路パターン51, 52(または62)とをまたは回路パターン51, 52(または61, 62)同士を導通させるためのバイアホール48が形成されている。また、コア基板40には、当該コア基板40の中を通って回路パターン51, 61同士を電気的に接続する貫通電極40aが設けられている。

#### 【0031】

さらに、多層配線基板4は、第1絶縁層41および第2絶縁層42を覆う表側ソルダーレジスト45と、第4絶縁層44を覆う裏側ソルダーレジスト46とを有している。そして、表側ソルダーレジスト45の外側面によって多層配線基板4の表面4aが構成され、裏側ソルダーレジスト46の外側面によって多層配線基板4の裏面4bが構成されている。

#### 【0032】

コア基板40としては、セラミック基板あるいは有機材料基板を用いることができるが、コスト及び熱ストレス負荷時の接合部分に負荷されるストレスの効果的な緩和が可能であるとの観点から、ガラスクロスに熱硬化性樹脂を含浸させたガラスエポキシ基板を用いることが好ましい。コア基板40の厚さは例えば0.4mmである。コア基板40を構成する熱硬化性樹脂としては、エポキシ樹脂が好適であるが、これ以外の樹脂を使用することもできる。例えば、ビスマレイミドトリアジン樹脂または熱硬化性ポリフェニレンエーテルなどの耐熱性の高い熱硬化性樹脂を1つ用いてもよいし、これらの2種類以上の混合物を用いてもよい。

#### 【0033】

接続パッド5は、それぞれはんだバンプ7を介して半導体チップ2の電極パッド3と接続されている。はんだバンプ7は、いずれも略同じ体積(例えば、 $5.0 \times 10^{-4} \text{ mm}^3$ )のものである。

#### 【0034】

より詳しくは、接続パッド5は、第1電極パッド3aと接続された第1接続パッド5aと、第2電極パッド3bと接続された第2接続パッド5bとで構成されている。そして、第1接続パッド5aが第1絶縁層41で支持されており、第2接続パッド5bが第2絶縁層42で支持されている。換言すれば、多層配線基板4の表面4a上の矩形領域内に配置された複数の接続パッド5のうち四隅に位置する第1接続パッド5aが第1絶縁層41に支持され、残りの第2接続パッド5bが第2絶縁層42に支持されている。これにより、第1接続パッド5aと第2接続パッド5bとの間には、第1絶縁層41の厚さと等しい高低差が形成されており、その高低差分だけ第1接続パッド5aが第2接続パッド5bよりも半導体チップ2に近い位置にある。

#### 【0035】

第1接続パッド5aおよび第2接続パッド5bの形状は、特に限定されないが、例えば

10

20

30

40

50

円形状であってもよいし矩形状であってもよい。ただし、第1接続パッド5aの大きさは、第2接続パッド5bの大きさよりも大きいことが好ましい。例えば、第1接続パッド5aを直径140μmの円形状とし、第2接続パッド5bを直径100μmの円形状としてもよい。

#### 【0036】

第1絶縁層41は、熱可塑性樹脂で構成されていることが好ましい。第1絶縁層41を構成する熱可塑性樹脂としては、特にその種類は問わないが、多層配線基板の製造工法、密着性、加工性といった観点から、例えば、ポリフェニレンエーテル(PP-E)、液晶ポリマー(LCP)、ポリエーテルエーテルケトン(PEEK)、ポリエーテルイミド(PEI)、ポリエーテルサルホン(PES)、熱可塑性ポリイミド(PI)などの、一般にスーパーエンジニアリングプラスチックと呼ばれる耐熱性の高い樹脂を好適に用いることができる。10

#### 【0037】

より好ましくは、第1絶縁層41を構成する熱可塑性樹脂は、融点が280以上の中である。フリップチップ実装におけるリフロー処理時には、はんだバンプ7の融点(例えば、錫97.5重量%、銀2.5重量%の組成のはんだバンプでは、217)よりも高い温度(例えば260)環境となるので、その場合でも第1絶縁層41が溶融しないようにするためである。

#### 【0038】

また、第1絶縁層41の厚さは、多層配線基板中の第1絶縁層41のすぐ下にある回路パターン52の厚さの1.5倍以上であることが好ましい。回路パターン52は、第1絶縁層41に埋め込まれる形で形成されるため、第1絶縁層41が回路パターン52より薄い厚さだと第1絶縁層41の上下に回路パターンが形成できない。さらに、第1絶縁層41の厚さが回路パターン52の厚さの1.5倍未満であると、回路パターン形成時のエッティングなどの処理あるいは絶縁層形成時の表面粗化処理などにより、第1絶縁層41を上下に貫通する空孔が形成され、この空孔を介して、電気的に接続してはいけない第1絶縁層41の上下の回路が短絡する可能性があるためである。さらに、第1絶縁層41の厚さは、第2電極パッド3bと第2接続パッド5bの間に形成されるはんだバンプ7の高さの2分の1以下であることが好ましい。第1絶縁層41の厚さが第2電極パッド3bと第2接続パッド5bの間に形成されるはんだバンプ7の高さの2分の1を超えると、第1接続パッド5aと第2接続パッド5bとの間の高低差が大きくなり過ぎて、第1接続パッド5aと接続されるはんだバンプ7が極端に大きく潰れてしまい、接続信頼性が低下するおそれがあるからである。例えば、第1絶縁層41の厚さを5~50μmとしてもよい。2030

#### 【0039】

第2~第4絶縁層42~44は、無機フィラーが配合された熱硬化性樹脂で構成されていることが好ましい。無機フィラーは、絶縁層の絶縁性を保ちながら熱膨張率の低下および弾性率の向上を図るために添加されるものであり、その配合量は、例えば10~60体積%である。無機フィラーとしては、例えば平均粒径が5μmの球状のシリカが挙げられる。シリカの他にも、アルミナ、水酸化アルミニウム、チタン酸バリウムなどからなる球状のものまたは破碎フィラーを使用してもよい。40

#### 【0040】

熱硬化性樹脂としては、エポキシ樹脂が好適であるが、これ以外の樹脂を使用することもできる。例えば、ビスマレイミドトリアジン樹脂または熱硬化性ポリフェニレンエーテルなどの耐熱性の高い熱硬化性樹脂を1つ用いてもよいし、これらの2種類以上の混合物を用いてもよい。

#### 【0041】

表側ソルダーレジスト45には、第1接続パッド5aおよび第2接続パッド5bに対応する位置に、第1接続パッド5aおよび第2接続パッド5bを露出させる開口45a, 45b(図2参照)が設けられている。第1接続パッド5aに対応する位置の開口45aの大きさは、第2接続パッド5bに対応する位置の開口45bの大きさよりも大きく設定さ50

れていることが好ましい。本実施形態では、前述した第1接続パッド5aと第2接続パッド5bとの間の高低差により、多層配線基板4上への半導体チップ2の実装時に第1接続パッド5aに接続されるはんだバンプ7が大きく潰れるので、大きく潰れて押し広げられたはんだバンプ7と第1接続パッド5aとの接触面積を大きく確保するためである。これにより、それらの接合部分での耐久性が向上する。例えば、開口45aの大きさを直径130μmとし、開口45bの大きさを直径90μmとしてもよい。なお、第1接続パッド5aに対応する位置の開口45aの大きさは、第1絶縁層41の厚さおよびはんだバンプ7の体積に応じて決定すればよい。表側ソルダーレジスト層45の厚さは、例えば20μmである。

## 【0042】

10

また、開口45a, 45bを通じて露出する第1接続パッド5aおよび第2接続パッド5b上には、バリアメタル層50が積層されている。バリアメタル層50を構成するには、例えば、第1接続パッド5aおよび第2接続パッド5b上に、厚さ10μmの無電解ニッケルめっき層を形成し、さらにその上に厚さ0.1μmの金めっき層を形成すればよい。そして、第1接続パッド5aおよび第2接続パッド5bは、バリアメタル層50を介してはんだバンプ7と接続されている。

## 【0043】

裏側ソルダーレジスト46にも、外部接続用バンプ6に対応する位置に開口が形成されており、この開口内にバリアメタル層60が形成されている。

## 【0044】

20

さらに、本実施形態の半導体装置1では、多層配線基板4と半導体チップ2との間に、アンダーフィル8が充填されている。アンダーフィル8としては、例えば、耐熱性の観点から多官能エポキシ樹脂が用いられることが多い、特にビスフェノールAノボラック型エポキシ樹脂、ビスフェノールFノボラック型エポキシ樹脂、クレゾールノボラック型エポキシ樹脂などの絶縁性の樹脂を用いることができる。

## 【0045】

以上説明した半導体装置1では、半導体チップ2と多層配線基板4がはんだバンプ7を介して接続される際に最も応力がかかる四隅に位置するはんだバンプ7が、熱可塑性樹脂からなる第1絶縁層41上に形成された第1接続パッド5aに接続されている。熱ストレスが負荷された際に熱可塑性樹脂からなる第1絶縁層41が軟化することで、四隅に位置するはんだバンプ7に特に集中的にかかる応力を緩和することができる。また、残りのはんだバンプ7の全てが、熱負荷時にも弾性率の高い第2絶縁層42上に形成された接続パッド4bに接続されているので、半導体チップ2と多層配線基板4との接続を全体として剛性の高い強固なものにすることができる。さらに、第1接続パッド5aと第2接続パッド5bとの間の高低差によって四隅に位置するはんだバンプ7の断面積を大きく拡張することができるため、当該はんだバンプ7にかかる応力をより小さくすることができる。それ故に、本実施形態のようにいずれも略同じ体積のはんだバンプ7を用いても、クラックの発生を効果的に抑えることができるとともに、半導体チップ2と多層配線基板4との接合強度が高い半導体装置を得ることができる。

## 【0046】

30

そして、本実施形態のようにいずれも略同じ体積のはんだチップ7を用いれば、ボール搭載法によりはんだバンプ7を形成することができるため、接続パッドピッチが200μm以下と狭い場合であってもはんだバンプ7を良好に形成することができる。

## 【0047】

次に、半導体装置1を製造する方法を説明する。

## 【0048】

## 1) 多層配線基板の製造

多層配線基板4の製造方法としては、第2～第4絶縁層42～44の製造までは一般的にシーケンシャルビルドアップ製造工法と呼ばれるビルドアップ基板作製方法を用い、ガラスクロスを含むコア基板40上に絶縁層と回路パターンとを順次形成する。以下に、多

50

層配線基板 4 の具体的な製造方法を図 3 ~ 図 5 を参照しながら説明する。

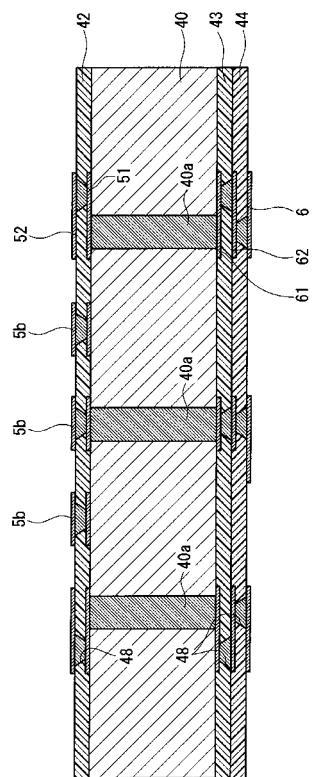

#### 【 0 0 4 9 】

図 3 は、第 1 絶縁層 4 1 を形成する前段階の状態を示す断面図である。まず、コア基板 4 0 の表裏両面に例えれば厚さ 15 μm の金属箔を熱圧着により貼り合わせる。金属箔としては、電解めっきにより作製した銅箔を使用することができる。ついで、表面および裏面上の金属箔同士を電気的に接続するために、炭酸ガスレーザを使用してコア基板 4 0 を金属箔と共に貫通する貫通孔を加工した後、貫通孔内を無電解銅めっきと電解銅めっきにて充填して貫通電極 4 0 a を形成する。その後、金属箔をエッチングすることでコア基板 4 0 上に回路パターン 5 1 , 6 1 を形成する。

#### 【 0 0 5 0 】

次に、前述したような無機フィラーが配合された熱硬化性樹脂によって予め成形されたフィルムを、回路パターン 5 1 が形成されたコア基板 4 0 の表面上に熱圧着により貼り合わせるとともに硬化させて、第 2 絶縁層 4 2 を形成する。第 2 絶縁層 4 2 の形成方法は、これに限らず、例えは無機フィラーが配合された未硬化液状の熱硬化性樹脂をスクリーン印刷法またはスピンドルコート法によって塗布した後に加熱して硬化させて行ってもよい。

#### 【 0 0 5 1 】

次に、炭酸ガスレーザを用いて第 2 絶縁層 4 2 に、これを厚さ方向に貫通してその下にある回路パターン 5 1 に到達する有底バイアホール 4 8 を形成する。レーザによる有底バイアホール 4 8 の形成は、炭酸ガスレーザの他にも第三高調波 Nd - YAG レーザまたは 300 nm より波長の短い深紫外エキシマレーザなどのレーザ加工装置を用いて行ってもよい。

#### 【 0 0 5 2 】

次に、第 2 絶縁層 4 2 上に、無電解銅めっきを施した後にさらに電解銅めっきを施すことで、有底バイアホール 4 8 を満たした例えは厚さ 15 μm の銅めっき膜を形成する。ついで、形成した銅めっき膜の表面に感光性のドライフィルムレジストを熱圧着プレスによって貼り合わせるとともに、その上から所望の導体パターンのネガイメージが描画されたガラスマスクを位置合わせる。その後、露光と現像を行うことで必要な導体パターン以外の部位の銅めっき膜を露出させたエッチングレジストを形成する。そして、銅めっき膜のうちエッチングレジストに覆われていない部分をエッチングにより溶解させて除去した後、エッチングレジストを剥離することで、第 2 絶縁層 4 2 上に回路パターン 5 1 に電気的に接続された第 2 接続パッド 5 b および回路パターン 5 2 を形成する。

#### 【 0 0 5 3 】

その後、コア基板 4 0 の裏面側にも前記と同様の方法により、第 3 絶縁層 4 3 、回路パターン 6 1 に電気的に接続された回路パターン 6 2 、第 4 絶縁層 4 4 、および回路パターン 6 2 に電気的に接続された外部接続用パッド 6 を形成する。

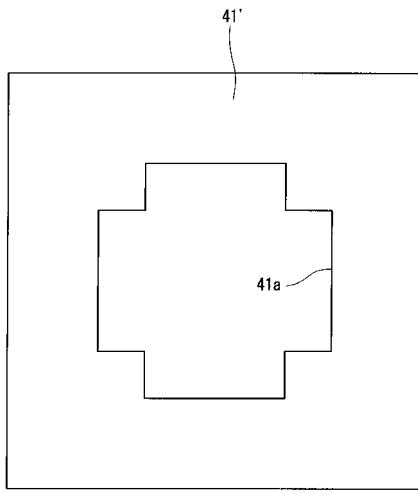

#### 【 0 0 5 4 】

次に、図 4 に示すように、前述したような熱可塑性樹脂からなる、開口 4 1 a が形成されて第 2 絶縁層 4 2 上の第 2 接続パッド 5 b が配置された領域以外の部分を全て覆うことが可能な形状のフィルム 4 1 ' を用意する。開口 4 1 a の形成は、例えは炭酸ガスレーザによってフィルムを切り抜くことにより行えばよい。このフィルム 4 1 ' を第 2 絶縁層 4 2 上に位置合わせした後に熱圧着することにより、第 2 接続パッド 5 b を取り囲むように第 1 絶縁層 4 1 を形成する。第 1 絶縁層 4 1 の形成は、液状の熱可塑性樹脂を第 2 絶縁層 4 2 上に塗布することによって行うことも可能であるが、多層配線基板製造工法の容易性およびコストを考慮するとフィルム 4 1 ' を用いることが好ましい。次に、第 2 絶縁層 4 2 上に第 2 接続パッド 5 b を形成した方法と同じ方法で、第 1 絶縁層 4 1 上に第 1 接続パッド 5 a を形成する。

#### 【 0 0 5 5 】

次に、フリップチップ実装時の隣り合うはんだバンプ 7 間のショートを避けるために、第 1 絶縁層 4 1 および第 2 絶縁層 4 2 上に感光性エポキシ樹脂からなるソルダーレジスト樹脂を使用して露光処理によって、第 1 接続パッド 5 a および第 2 接続パッド 5 b を露出

10

20

30

40

50

させる開口 4 5 a , 4 5 b を有する表側ソルダーレジスト 4 5 を形成する。表側ソルダーレジスト 4 5 を形成する下地となる第 1 絶縁層 4 1 と第 2 絶縁層 4 2 との間に段差が存在するため、表側ソルダーレジスト 4 5 形成の際には、まず第 2 絶縁層 4 2 上の部分を先に形成し、その後に第 1 絶縁層 4 1 上の部分を形成する。第 4 絶縁層 4 4 上にも同様に、外部接続用パッド 6 を露出させる開口を有する裏側ソルダーレジスト 4 6 を形成する。裏面側は下地に段差がないため、裏側ソルダーレジスト 4 6 は表側ソルダーレジスト 4 5 を形成した後に 1 回の処理で形成することができる。これらのソルダーレジスト 4 5 , 4 6 の形成は、一般的に感光性タイプのソルダーレジスト材料を使用し、露光処理によってパターン加工することにより行われるが、所望の形状に加工できればどのような工法を用いてもよい。例えば、炭酸ガスレーザ、第三高調波 N d - Y A G レーザ、3 0 0 n m より波長の短い深紫外エキシマレーザなどのレーザ加工装置を用いて加工してもよい。10

#### 【 0 0 5 6 】

次に、第 1 接続パッド部 5 a および第 2 接続パッド 5 b ならびに外部接続用パッド 6 のソルダーレジスト 4 5 , 4 6 の開口から露出する部分に、バリアメタル層 5 0 , 6 0 を形成する。

#### 【 0 0 5 7 】

以上の工程により、図 5 に示すような多層配線基板 4 を製造することができる。

#### 【 0 0 5 8 】

##### 2 ) はんだバンプの形成

図 6 に示すように、半導体チップ 2 の第 1 電極パッド 3 a および第 2 電極パッド 3 b 上の所定位置に直径 1 0 0 μ m のはんだボールを搭載し、窒素ガス雰囲気下でリフロー処理を行うことではんだバンプ 7 を形成する。20

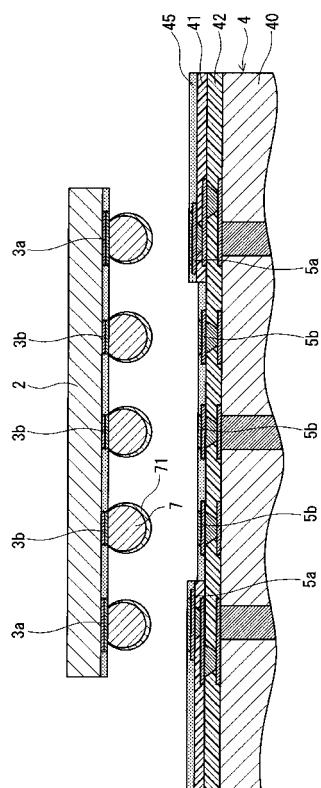

#### 【 0 0 5 9 】

次に、図 7 に示すように、はんだバンプ 7 にフラックス 7 1 を付着させる。はんだバンプ 7 にフラックス 7 1 を付着させる方法は、はんだバンプ 7 の表面全体にフラックス 7 1 がぬれ広がり、かつ半導体チップ 2 の裏面 2 a に形成されている絶縁保護膜 2 1 にフラックス 7 1 が付着しなければ特に問わない。例えば、はんだバンプ 7 の高さよりも薄い膜厚（例えば 5 0 μ m ）で平坦面に均一に塗布されたフラックス 7 1 中に、半導体チップ 2 に形成されたはんだバンプ 7 を浸漬することによって、はんだバンプ 7 にフラックス 7 1 を付着させることができる。こうすることで、フラックス 7 1 のはんだに対する濡れ性の作用により、はんだバンプ 7 のフラックス 7 1 中に浸漬されていない部分にまでフラックス 7 1 がぬれ広がり、はんだバンプ 7 の表面を均一にフラックス 7 1 で覆うことができる。30

#### 【 0 0 6 0 】

##### 3 ) 多層配線基板上への半導体チップの実装

図 7 に示すように、多層配線基板 4 と半導体チップ 2 を所定の位置関係となるように位置合わせし、多層配線基板 4 の表面 4 a 上に半導体チップ 2 を接続パッド 5 と電極パッド 3 とがはんだバンプ 7 を挟んで対向するように搭載する。この搭載段階では、多層配線基板 4 の第 1 接続パッド 5 a および第 2 接続パッド 5 b にフラックス 7 1 を介して（正確にはバリアメタル層 5 0 をも介して）はんだバンプ 7 が接触しているのみであり、はんだ接続は行われていない。40

#### 【 0 0 6 1 】

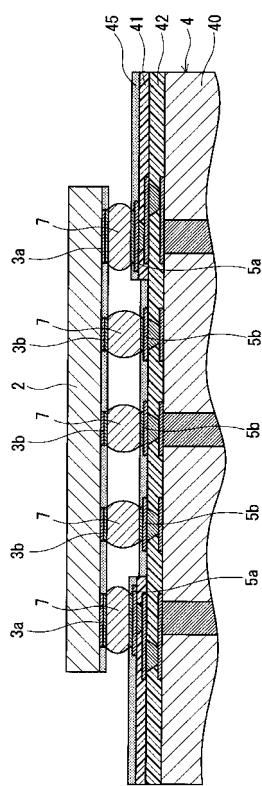

次に、はんだリフロー装置を用い、半導体チップ 2 が搭載された多層配線基板 4 を窒素雰囲気下ではんだバンプ 7 が溶融する温度よりも 3 0 ℃ 以上高い温度で 2 0 秒以上加熱する（リフロー処理を行う）ことで、図 8 に示すように、はんだバンプ 7 によって半導体チップ 2 を多層配線基板 4 の表面 4 a 上に実装する。

#### 【 0 0 6 2 】

次に、はんだバンプ 7 周辺に残渣するフラックス 7 1 を除去するため、フラックス 7 1 を洗浄する。このフラックス洗浄では、図 8 に示すような多層配線基板 4 に半導体チップ 2 が実装された実装体を洗浄液に完全に浸漬し、周波数 1 0 0 k H z 、出力 1 0 0 W の超音波による洗浄を 5 分間行った後、洗浄液から取り出した実装体に対し、速やかに純水を50

使用して5分間のリーンス処理を行う。このように、洗浄液中で超音波処理を行うことで、実装体のはんだバンプ7が存在するギャップ部分へ、洗浄液を効果的に進入させ、中に残渣しているフラックスを比較的効率よく除去することができる。実際に、実装後にダミーサンプルの半導体チップを剥がしてはんだバンプ7周辺の観察を行ったところ、はんだバンプ7周辺に残渣するフラックスは存在しなかった。

#### 【0063】

洗浄の効果を高めるためには洗浄中の超音波出力を高くすることが好ましいが、超音波出力を1000Wより高くすると、はんだバンプ7内または電極パッド3にクラックが発生し、50Wより低くすると残渣するフラックスが全く除去されない。そこで、超音波出力は50W以上1000W以下であることが好ましい。また、超音波の周波数を600kHzより高くした場合および50kHzより低くした場合には、残渣するフラックスが除去されなくなるため、超音波の周波数は50kHz以上600kHz以下が好ましい。洗浄時間およびリーンス処理時間は、1分を越えていれば残渣するフラックスの除去性に差は見られないが、長時間の超音波処理は多層配線基板4が吸湿してしまい、以降の熱処理工程で多層配線基板4内の膨れまたはデラミネーションを引き起こすおそれがあるため、10分以下であることが好ましい。10

#### 【0064】

次に、フラックス洗浄が終了した図8に示すような実装体に対し、窒素雰囲気下で115～125にて例えれば1時間のベーク処理を行う。ベーク時間が1時間よりも短い場合、またはベーク温度が115を下回る場合には、多層配線基板4の表面4aに付着した表面吸着水の除去が十分に行われず、次のアンダーフィル充填工程でソルダーレジスト45, 46の表面に対するアンダーフィル8の濡れ性が低下し、アンダーフィル8の充填が十分に行われなくおそれがある。また、ベーク時間が3時間を超える場合、またはベーク温度が125を超える場合は、ソルダーレジスト45, 46の表面が変色する。そこで、ベーク時間は1時間以上3時間以下であることが好ましく、ベーク温度は115以上125以下であることが好ましい。20

#### 【0065】

次に、多層配線基板4と半導体チップ2との間のギャップ部分へ、アンダーフィル塗布装置によって未硬化のアンダーフィル8の塗布を行う。アンダーフィル8は、半導体チップ2の外形を成す4つの辺の内、最も長い辺に沿って所定量塗布する。このアンダーフィル8の塗布は、塗布されたアンダーフィル8の粘度を下げてギャップ部分（隙間）への浸透性を高めるために、図8に示すような半導体チップ2が実装された多層配線基板4を例えれば65に過熱した状態で行うことが好ましい。塗布後も例えれば10分間程度同一温度に保つことで、アンダーフィル8の浸透性を利用してアンダーフィル8をギャップ部分に完全に充填させることができる。30

#### 【0066】

次に、多層配線基板4と半導体チップ2との間にアンダーフィル8が充填された実装体をオープンへ入れて、窒素雰囲気下で例えれば145～155の温度で例えれば1時間加熱する。この熱処理工程により、未硬化のアンダーフィル8が硬化することで、はんだバンプ7を封止し、水分の浸入および外的なストレス、さらに熱変形や内部残留応力によって発生する圧縮やせん断応力から接合部を保護する役割となる。40

#### 【0067】

ここで、加熱温度が130より低い場合、または加熱時間が1時間より短い場合は、アンダーフィル8の硬化が十分に行われず、水分の浸入による電気絶縁性の低下、あるいは封止効果が不十分となり、震度または熱変形による局所的応力負荷が発生した場合に接合部の破壊が発生する。また、加熱温度が170を超えた場合、または加熱時間が3時間を越えた場合には、アンダーフィル8の過剰な硬化反応により、多層配線基板4が変形したり、接合部または多層配線基板4内の破壊あるいは剥離が発生したりする。

#### 【0068】

以上の工程により、図1に示すような半導体装置1を製造することができる。

## 【0069】

なお、前記実施形態で示した製造方法では、半導体チップ2の電極パッド3にはんだバンプ7を形成しているが、半導体チップ2の電極パッド3と多層配線基板4の接続パッド5の両方にはんだバンプを形成し、それらのはんだバンプ同士を接合してはんだバンプ7を形成してもよい。

## 【0070】

また、前記実施形態では、第1絶縁層41が熱可塑性樹脂で構成されていたが、第1絶縁層41は、第2絶縁層42と同一の熱硬化性樹脂で構成されていてもよい。この場合でも、第1接続パッド5aと第2接続パッド5bとの間の高低差により、第1接続パッド5aに接続されたはんだバンプ7を第2接続パッド5bに接続されたはんだバンプ7よりも押し広げられた形状とすることができる、熱応力によるクラックの発生を抑えることができる。10

## 【0071】

あるいは、第1絶縁層41は第2絶縁層42上に積層されている必要はなく、例えば図9に示すように、第2絶縁層42が第1絶縁層41の開口41a内に嵌り込んでいて、前述したような無機フィラーが配合された熱硬化性樹脂で構成された別の絶縁層47上に第1絶縁層41および第2絶縁層42が積層されていてもよい。すなわち、第1接続パッド5aを支持する第1絶縁領域と第2接続パッド5bを支持する第2絶縁領域とは同一平面上にあってもよい。この場合でも、第1絶縁層41の軟化によって、熱応力によるクラックの発生を抑えることができる。20

## 【0072】

ただし、前記実施形態のように、第1絶縁層41が熱可塑性樹脂で構成されており、かつ、第1絶縁層41が第2絶縁層42上に積層されていれば、その相乗効果により、クラックの発生をさらに効果的に抑えることができる。

## 【0073】

さらに、前記実施形態では、電極パッド3のうち半導体チップ2の裏面2aの各角に近接して配置された電極パッドが第1電極パッド3aとなり、残りの電極パッドが第2電極パッド3bとなっているが、第1電極パッド3aは、少なくとも半導体チップ2の裏面2aの各角に近接して配置された電極パッド3aを含むものであればよい。換言すれば、接続パッド5のうち少なくとも四隅に位置する接続パッドが第1絶縁層41に支持されなければならない。例えば、電極パッド3のうち最外周の全ての電極パッドが第1電極パッド3aとなり、この第1電極パッド3aで囲まれる電極パッドが第2電極パッド3bとなっているてもよい。すなわち、図10に示すように、接続パッド5のうち最外周の全ての接続パッドが第1接続パッド5aとなっていて第1絶縁層41に支持されていてもよい。このように、第1絶縁層41に形成される開口41aの形状および大きさは、第1電極パッド3aとはんだバンプ7を介して接続される第1接続パッド5aの配置に合わせて適宜変更可能である。30

## 【0074】

また、本発明は、ウエハレベルCSPを実装基板に実装する場合にも適用可能である。すなわち、多層配線基板4は、インターポーザである必要はなく、例えばコア基板40の表面にのみ第1絶縁層41および第2絶縁層42が形成された2層または3層の基板であってもよい。40

## 【0075】

さらに、本発明は、バンプとしてはんだバンプ以外の例えば金バンプ等を用いた場合でも同様の効果が得られることは言うまでもない。

## 【実施例】

## 【0076】

本発明の効果を確認するために、以下に示す実施例1～3ならびに比較例の半導体装置に対して、温度サイクル試験を行った。

## 【0077】

50

具体的には、半導体装置に対し、JEDEC STANDARD TEST METHOD A 113-A LEVEL 3で規定される条件下で吸湿保存の前処理を行い、その直後に260℃の温度ではんだリフロー試験を3回行う前処理を行った。このように前処理された半導体装置を-55℃の環境下に30分設置した後に125℃の環境下に30分設置するサイクルを1000サイクルおよび1500サイクル行い、半導体装置におけるはんだバンプを含む全ての配線部分の接続抵抗値の変化を確認した。

#### 【0078】

##### (実施例1)

実施例1では、8.0×8.0mmの大きさの半導体チップ2を用い、電極パッド3、接続パッド5、およびはんだバンプ7の数量を1600個とした(パッドピッチ:180μm)。コア基板40としてガラスエポキシ基板を用いた。第1絶縁層41を構成する熱可塑性樹脂としてはポリフェニレンエーテルを用い、第2絶縁層42を構成する熱硬化性樹脂としては平均粒径5μmの球状のシリカ(無機フィラー)が50体積%配合されたエポキシ樹脂を用いた。最表面に存在する第1絶縁層41の厚さを30μmとし、第2絶縁層42の厚さを45μmとした。その他(はんだバンプ7の体積、電極パッド3および接続パッド5の形状および大きさ、開口45a, 45bの大きさなど)は前記実施形態で具体的に例示したものを探用した。以上の条件で、半導体装置を製造した。

#### 【0079】

実施例1の半導体装置は、温度サイクル試験の結果、信頼性評価の判断基準である1000サイクル後における接続抵抗値の変化率が初期抵抗値に対して+10%以下であり、また1500サイクル後における接続抵抗値の変化率も初期抵抗値に対して+10%以下であり、繰り返しの温度変化に対して良好な耐性を持つことが分かった。

#### 【0080】

##### (実施例2)

実施例1に対し、表側ソルダーレジスト45における第1接続パッド5aに対応する位置の開口45aの大きさを130μmから他の開口45bと同じ90μmに変更した以外は、実施例1と同様の条件で半導体装置を製造した。

#### 【0081】

実施例2の半導体装置では、温度サイクル試験の結果、1000サイクル後における接続抵抗値の変化率が初期抵抗値に対して+10%以下であった。しかし、1500サイクル後では一部断線不良が発生した。断線不良の発生原因を確認するため、温度サイクル試験後の半導体装置に対して不良モード解析を行った結果、発生した断線箇所に係るはんだバンプ7の周辺には、はんだバンプ7内に表側ソルダーレジスト45aの開口45a上部に対応する位置を起点としたクラックが観察された。

#### 【0082】

##### (実施例3)

実施例1に対し、第1絶縁層41の厚さが第2電極パッド3bと第2接続パッド5bの間に形成されるはんだバンプ7の高さの2分の1となるように45μmと変更した以外は、実施例1と同様の条件で半導体装置を製造した。

#### 【0083】

実施例3の半導体装置では、温度サイクル試験の結果、1000サイクル後における接続抵抗値の変化率が初期抵抗値に対して+10%以下であった。しかし、1200サイクル後では一部断線不良が発生した。断線不良の発生原因を確認するため、温度サイクル試験後の半導体装置に対して不良モード解析を行った結果、発生した断線箇所に係るはんだバンプ7が実施例1と比較して大きく潰れて変形しており、変形部に沿ってはんだ内にクラックが観察された。

#### 【0084】

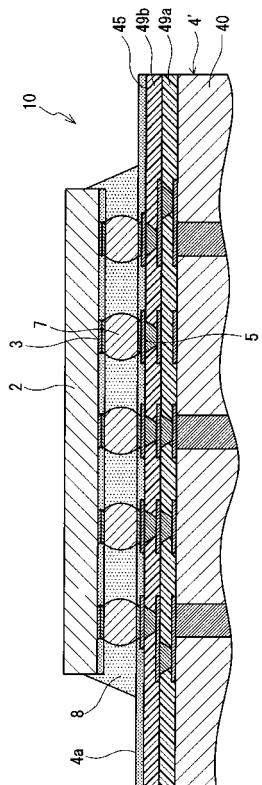

##### (比較例)

比較例では、図11に示すような半導体装置10を製造した。比較例に係る多層配線基板4'は、半導体チップ2の電極パッド3とはんだバンプ7を介して接続する接続パッド

10

20

30

40

50

5が、全て同一の絶縁層上に形成された構造を有している。この比較例に係る多層配線基板4'の製造は、第2絶縁層に相当する絶縁層49aを形成するまでは前記実施形態と同様に行い、絶縁層49aの全面上に絶縁層49bを絶縁層49aと同じ材料（無機フィラーが配合された熱硬化性樹脂）で形成した。すなわち、全ての絶縁層を同一材料とし、その厚さを全て45μmとした。そして、絶縁層49b上に接続パッド5を形成した。また、ソルダーレジストの厚さを20μmとし、接続パッド5を露出させる開口の直径を全て90μmとした。その他の部分は実施例1と同様にした。

#### 【0085】

比較例の半導体装置10では、温度サイクル試験の結果、200サイクル後に接続抵抗値の変化率が初期抵抗値に対して+10%を越え、500サイクル後に断線不良が発生し、温度変化に対する耐性が劣ることを確認した。

10

#### 【0086】

断線不良の発生原因を確認するため、温度サイクル験後の半導体装置に対して不良モード解析を行った結果、発生した断線箇所に係るはんだバンプ7の周辺には、半導体チップ側のアルミパッド内部にクラックが観察された。

#### 【産業上の利用可能性】

#### 【0087】

本発明は、半導体チップのサイズが比較的に大きな場合、および個々のはんだバンプの体積が小さな場合に、特に有用である。

#### 【図面の簡単な説明】

#### 【0088】

【図1】本発明の一実施形態に係る半導体装置の断面図である。

【図2】図1に示す半導体装置の平面図である。

【図3】多層配線基板の製造方法を説明する説明図である。

【図4】第1絶縁層用フィルムの平面図である。

【図5】多層配線基板の断面図である。

【図6】電極パッドにバンプを形成した半導体チップの断面図である。

【図7】半導体装置の製造方法を説明する説明図である。

【図8】半導体装置の製造方法を説明する説明図である。

【図9】変形例の半導体装置の断面図である。

【図10】他の変形例の半導体装置の平面図である。

【図11】比較例の半導体装置の断面図である。

#### 【符号の説明】

#### 【0089】

1 半導体装置

2 半導体チップ

2a 裏面

3 電極パッド

3a 第1電極パッド

3b 第2電極パッド

4 多層配線基板（インターポーザ）

4a 表面

4b 裏面

41 第1絶縁層（上側絶縁層）

42 第2絶縁層（下側絶縁層）

45 表側ソルダーレジスト

46 裏側ソルダーレジスト

45a, 45b 開口

5 接続パッド

5a 第1接続パッド

20

30

40

50

- 5 b 第2接続パッド

6 外部接続用パッド

7 はんだバンプ

8 アンダーフィル

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 5 K 3/46

T

(56)参考文献 特開平09-064095(JP,A)

国際公開第2005/034231(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 3 / 1 2

H 0 1 L 2 1 / 6 0

H 0 5 K 3 / 3 4

H 0 5 K 3 / 4 6