(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년07월10일

(11) 등록번호 10-1418347

(24) 등록일자 2014년07월04일

(51) 국제특허분류(Int. Cl.)

H04N 5/363 (2011.01) H01L 27/146 (2006.01)

(21) 출원번호 10-2011-0058434

(22) 출원일자 2011년06월16일

심사청구일자 2012년06월15일

(65) 공개번호 10-2011-0140082

(43) 공개일자 2011년12월30일

(30) 우선권주장

JP-P-2010-144221 2010년06월24일 일본(JP)

(56) 선행기술조사문현

KR1020060024796 A\*

JP2005192191 A\*

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

캐논 가부시끼가이사

일본 도쿄도 오오따꾸 시모마루코 3조메 30방 2고

(72) 발명자

미노와 마사아끼

일본 도쿄도 오오따꾸 시모마루코 3조메 30방 2고

캐논 가부시끼가이사 내

오끼따 아끼라

일본 도쿄도 오오따꾸 시모마루코 3조메 30방 2고

캐논 가부시끼가이사 내

(74) 대리인

장수길, 박충범

전체 청구항 수 : 총 19 항

심사관 : 김용권

(54) 발명의 명칭 고체 콜상 장치 및 고체 콜상 장치의 구동 방법

**(57) 요약**

본 발명의 증폭형 고체 콜상 장치는, 수직 출력선의 신호가 판독될 때 리셋 트랜지스터의 게이트에 VRESL1의 전압을 공급하고, 포토다이오드에 축적된 신호 전하가 리셋 트랜지스터의 게이트와 FD 사이에 형성된 커패시터를 거쳐서 FD에 전송될 때 VRESL1보다 큰 VRESL2의 전압을 공급하며, 신호가 판독될 때 FD의 전압을 저하시킴으로써 양호한 선형성을 확보하고, 전하 전송시에 FD의 전압을 상승시킴으로써 전송 가능한 최대 전하량이 증가된다.

**대 표 도** - 도1

## 특허청구의 범위

### 청구항 1

고체 활상 장치이며,

제1 광전 변환부와,

플로팅 디퓨전(floating diffusion) 노드와,

상기 제1 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

전압 제어 노드와,

상기 전압 제어 노드의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋(reset)된 제1 상태에서 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 전압 제어 노드는, 상기 제1 전송 트랜지스터의 도통 상태를 설정하도록 구성된 전압이 공급되는 노드와는 다른 노드이고,

상기 전압 제어 노드는 결합 커패시턴스(coupling capacitance)를 거쳐서 상기 플로팅 디퓨전 노드에 결합되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 전압 제어 노드의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 전압 제어 노드의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때 상기 전압 제어 노드의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 전압 제어 노드의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 높은, 고체 활상 장치.

### 청구항 2

고체 활상 장치이며,

제1 광전 변환부와,

플로팅 디퓨전 노드와,

상기 제1 광전 변환부에서 발생된 홀(hole)을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

전압 제어 노드와,

상기 전압 제어 노드의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 홀이 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 전압 제어 노드는, 상기 제1 전송 트랜지스터의 도통 상태를 설정하도록 구성된 전압이 공급되는 노드와는

다른 노드이고,

상기 전압 제어 노드는 결합 커패시턴스를 거쳐서 상기 플로팅 디퓨전 노드에 결합되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 전압 제어 노드의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 전압 제어 노드의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때 상기 전압 제어 노드의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 전압 제어 노드의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 낮은, 고체 활상 장치.

### 청구항 3

제1항 또는 제2항에 있어서,

상기 플로팅 디퓨전 노드의 전압을 리셋하도록 구성된 리셋 트랜지스터를 더 포함하고,

상기 리셋 트랜지스터의 소스 및 드레인 중 하나가 상기 플로팅 디퓨전 노드에 접속되고,

상기 리셋 트랜지스터의 게이트가 상기 전압 제어 노드에 접속되며,

상기 결합 커패시턴스는 상기 리셋 트랜지스터의 게이트와 상기 플로팅 디퓨전 노드 사이의 커패시턴스 성분을 포함하고,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 리셋 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

### 청구항 4

제1항 또는 제2항에 있어서,

제2 광전 변환부와,

상기 제2 광전 변환부에서 발생된 신호 전하를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제2 전송 트랜지스터를 더 포함하고,

상기 제2 전송 트랜지스터의 게이트가 상기 전압 제어 노드에 접속되며,

상기 결합 커패시턴스는 상기 제2 전송 트랜지스터의 게이트와 상기 플로팅 디퓨전 노드 사이의 커패시턴스 성분을 포함하고,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 제2 전송 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

### 청구항 5

제1항 또는 제2항에 있어서,

상기 제1 광전 변환부 및 상기 플로팅 디퓨전 노드를 각각 구비하는 복수의 화소와,

상기 복수의 화소 중 2개의 화소의 각각의 상기 플로팅 디퓨전 노드 사이의 전기적 접속을 제어하도록 구성된 접속 트랜지스터를 더 포함하고,

상기 접속 트랜지스터의 소스 및 드레인 중 하나가 상기 2개의 화소 중 하나 또는 다른 하나에 포함된 상기 플로팅 디퓨전 노드에 접속되고,

상기 접속 트랜지스터의 게이트가 상기 전압 제어 노드에 접속되며,

상기 결합 커패시턴스는 상기 접속 트랜지스터의 게이트와 상기 플로팅 디퓨전 노드 사이의 커패시턴스 성분을 포함하는, 고체 활상 장치.

### 청구항 6

제5항에 있어서,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 접속 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

### 청구항 7

제5항에 있어서,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 접속 트랜지스터를 도통 상태로 설정하도록 구성된, 고체 활상 장치.

### 청구항 8

제5항에 있어서,

상기 복수의 화소 각각은, 제2 광전 변환부, 및 상기 제2 광전 변환부에서 발생된 신호 전하를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제2 전송 트랜지스터를 더 포함하는, 고체 활상 장치.

### 청구항 9

제8항에 있어서,

상기 증폭 트랜지스터는 매립 채널형(buried-channel type) 트랜지스터인, 고체 활상 장치.

### 청구항 10

제1항 또는 제2항에 있어서,

상기 증폭 트랜지스터는 매립 채널형 트랜지스터인, 고체 활상 장치.

### 청구항 11

제1항 또는 제2항에 있어서,

상기 제1 전압과 상기 제3 전압은 동일한, 고체 활상 장치.

### 청구항 12

고체 활상 장치이며,

제1 광전 변환부와,

플로팅 디퓨전 노드와,

상기 제1 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 플로팅 디퓨전 노드의 전압을 리셋하도록 구성된 리셋 트랜지스터와,

상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 전압 제어부는, 상기 리셋 트랜지스터의 상기 게이트의 전압이 제1 전압 또는 상기 제1 전압보다 높은 제2 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 전압 제어부는, 또한, 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 리셋 트랜지스터의 게이트의 전압이 상기 제2 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하

도록 구성되며,

상기 전압 제어부는, 또한, 상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때 상기 리셋 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제1 전압 및 상기 제2 전압 각각은 상기 리셋 트랜지스터를 비도통 상태로 설정하도록 구성되고,

상기 제2 전압은 상기 제3 전압보다 높은, 고체 활상 장치.

### 청구항 13

제12항에 있어서,

상기 전압 제어부는, 또한, 상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 리셋 트랜지스터의 게이트의 전압이 상기 제1 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제3 전압은 상기 리셋 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

### 청구항 14

제12항 또는 제13항에 있어서,

상기 전압 제어부는 제1 도전형 채널을 갖는 제1 MOS 트랜지스터와, 제2 도전형 채널을 갖는 제2 MOS 트랜지스터를 포함하는 회로이고,

상기 제1 MOS 트랜지스터의 게이트는 상기 제2 MOS 트랜지스터의 게이트에 접속되며,

상기 제1 MOS 트랜지스터의 소스 및 드레인 중 하나는 기준 전압을 공급하는 배선에 접속되고,

상기 제1 MOS 트랜지스터의 소스 및 드레인 중 다른 하나는 상기 리셋 트랜지스터의 게이트에 전기적으로 접속되며,

상기 제2 MOS 트랜지스터의 소스 및 드레인 중 하나는 상기 리셋 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제2 MOS 트랜지스터의 소스 및 드레인 중 다른 하나는 상기 제1 전압을 공급하는 배선, 및 상기 제2 전압을 공급하는 배선에 선택적으로 접속 가능한, 고체 활상 장치.

### 청구항 15

고체 활상 장치이며,

제1 광전 변환부와,

제2 광전 변환부와,

플로팅 디퓨전 노드와,

상기 제1 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 제2 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제2 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 제1 광전 변환부에서 발생된 상기 전자가 전송된 제2 상태에서 제2 신호를 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 제2 전송 트랜지스터의 게이트의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 제2 전송 트랜지스터의

게이트의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 출력할 때, 상기 제2 전송 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 높으며,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 제2 전송 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

## 청구항 16

고체 활상 장치이며,

제1 광전 변환부와; 플로팅 디퓨전 노드와; 상기 제1 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와; 상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터를 각각 구비하는 복수의 화소와,

상기 복수의 화소 중 제1 화소의 상기 플로팅 디퓨전 노드와, 상기 복수의 화소 중 제2 화소의 상기 플로팅 디퓨전 노드 사이의 전기적 접속을 제어하도록 구성된 접속 트랜지스터와,

상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 제2 신호를 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 접속 트랜지스터의 게이트의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 접속 트랜지스터의 게이트의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 출력할 때, 상기 접속 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 높은, 고체 활상 장치.

## 청구항 17

청구항 17은(는) 설정등록료 납부시 포기되었습니다.

고체 활상 장치이며,

제1 광전 변환부와,

플로팅 디퓨전 노드와,

상기 제1 광전 변환부에서 발생된 홀을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 플로팅 디퓨전 노드의 전압을 리셋하도록 구성된 리셋 트랜지스터와,

상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 홀이 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 전압 제어부는, 상기 리셋 트랜지스터의 상기 게이트의 전압이 제1 전압 또는 상기 제1 전압보다 낮은 제2 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 전압 제어부는, 또한, 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기

리셋 트랜지스터의 게이트의 전압이 상기 제2 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되며,

상기 전압 제어부는, 또한, 상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때 상기 리셋 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제1 전압 및 상기 제2 전압 각각은 상기 리셋 트랜지스터를 비도통 상태로 설정하도록 구성되고,

상기 제2 전압은 상기 제3 전압보다 낮은, 고체 콤상 장치.

### 청구항 18

청구항 18은(는) 설정등록료 납부시 포기되었습니다.

제17항에 있어서,

상기 전압 제어부는, 또한, 상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 리셋 트랜지스터의 게이트의 전압이 상기 제1 전압이 되도록, 상기 리셋 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제3 전압은 상기 리셋 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 콤상 장치.

### 청구항 19

청구항 19은(는) 설정등록료 납부시 포기되었습니다.

제17항 또는 제18항에 있어서,

상기 전압 제어부는 제1 도전형 채널을 갖는 제1 MOS 트랜지스터와, 제2 도전형 채널을 갖는 제2 MOS 트랜지스터를 포함하는 회로이고,

상기 제1 MOS 트랜지스터의 게이트는 상기 제2 MOS 트랜지스터의 게이트에 접속되며,

상기 제1 MOS 트랜지스터의 소스 및 드레인 중 하나는 기준 전압을 공급하는 배선에 접속되고,

상기 제1 MOS 트랜지스터의 소스 및 드레인 중 다른 하나는 상기 리셋 트랜지스터의 게이트에 전기적으로 접속되며,

상기 제2 MOS 트랜지스터의 소스 및 드레인 중 하나는 상기 리셋 트랜지스터의 게이트에 전기적으로 접속되고,

상기 제2 MOS 트랜지스터의 소스 및 드레인 중 다른 하나는 상기 제1 전압을 공급하는 배선, 및 상기 제2 전압을 공급하는 배선에 선택적으로 접속 가능한, 고체 콤상 장치.

### 청구항 20

청구항 20은(는) 설정등록료 납부시 포기되었습니다.

고체 콤상 장치이며,

제1 광전 변환부와,

제2 광전 변환부와,

플로팅 디퓨전 노드와,

상기 제1 광전 변환부에서 발생된 홀을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와,

상기 제2 광전 변환부에서 발생된 홀을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제2 전송 트랜지스터와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 제1 광전 변환부에서 발생된 상기 홀이 전송된

제2 상태에서 제2 신호를 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 제2 전송 트랜지스터의 게이트의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 제2 전송 트랜지스터의 게이트의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 출력할 때, 상기 제2 전송 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 낮으며,

상기 제1 전압, 상기 제2 전압 및 상기 제3 전압 각각은 상기 제2 전송 트랜지스터를 비도통 상태로 설정하도록 구성된, 고체 활상 장치.

## 청구항 21

청구항 21은(는) 설정등록료 납부시 포기되었습니다.

고체 활상 장치이며,

제1 광전 변환부와; 플로팅 디퓨전 노드와; 상기 제1 광전 변환부에서 발생된 홀을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 제1 전송 트랜지스터와; 상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터를 각각 구비하는 복수의 화소와,

상기 복수의 화소 중 제1 화소의 상기 플로팅 디퓨전 노드와, 상기 복수의 화소 중 제2 화소의 상기 플로팅 디퓨전 노드 사이의 전기적 접속을 제어하도록 구성된 접속 트랜지스터와,

상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성된 전압 제어부를 포함하고,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 홀이 전송된 제2 상태에서 제2 신호를 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 접속 트랜지스터의 게이트의 전압이 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 접속 트랜지스터의 게이트의 전압이 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 출력할 때, 상기 접속 트랜지스터의 게이트의 전압이 제3 전압이 되도록, 상기 전압 제어부가 상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성되고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 낮은, 고체 활상 장치.

## 청구항 22

고체 활상 장치의 구동 방법이며,

상기 고체 활상 장치는,

광전 변환부와,

플로팅 디퓨전 노드와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전 노드에 전송하도록 구성된 전송 트랜지스터와,

상기 전송 트랜지스터를 도통 상태로 설정하도록 구성된 전압이 공급되는 노드와는 다르며, 결합 커패시턴스를 거쳐서 상기 플로팅 디퓨전 노드에 결합되는 노드를 포함하고,

상기 방법은,

상기 증폭 트랜지스터를 통해, 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 신호선에 출력하는 단계와,

상기 증폭 트랜지스터를 통해, 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하는 단계와,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 노드의 전압을 제1 전압으로 제어하는 단계와,

상기 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 노드의 전압을 제2 전압으로 제어하는 단계와,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때, 상기 노드의 전압을 제3 전압으로 제어하는 단계를 포함하고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 높은, 고체 활상 장치의 구동 방법.

### 청구항 23

청구항 23은(는) 설정등록료 납부시 포기되었습니다.

고체 활상 장치의 구동 방법이며,

상기 고체 활상 장치는,

광전 변환부와,

플로팅 디퓨전 노드와,

상기 플로팅 디퓨전 노드의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와,

상기 광전 변환부에서 발생된 홀을 상기 플로팅 디퓨전 노드에 전송하도록 구성된 전송 트랜지스터와,

상기 전송 트랜지스터를 도통 상태로 설정하도록 구성된 전압이 공급되는 노드와는 다르며, 결합 커패시턴스를 거쳐서 상기 플로팅 디퓨전 노드에 결합되는 노드를 포함하고,

상기 방법은,

상기 증폭 트랜지스터를 통해, 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 제1 신호를 신호선에 출력하는 단계와,

상기 증폭 트랜지스터를 통해, 상기 플로팅 디퓨전 노드에 상기 홀이 전송된 제2 상태에서 제2 신호를 상기 신호선에 출력하는 단계와,

상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때, 상기 노드의 전압을 제1 전압으로 제어하는 단계와,

상기 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에, 상기 노드의 전압을 제2 전압으로 제어하는 단계와,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때, 상기 노드의 전압을 제3 전압으로 제어하는 단계를 포함하고,

상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 낮은, 고체 활상 장치의 구동 방법.

### 청구항 24

제15항에 있어서,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 상기 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 상기 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호 저장부가 상기 신호선의 신호를 샘플링할 때 상기 제2 전송 트랜지스터의 게이트의 전압이 상기 제3 전압이 되도록, 상기 전압 제어부가 상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성된, 고체 활상 장치.

### 청구항 25

제16항에 있어서,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 상기 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 전자가 전송된 제2 상태에서 상기 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호저장부가 상기 신호선의 신호를 샘플링할 때 상기 접속 트랜지스터의 게이트의 전압이 상기 제3 전압이 되도록, 상기 전압 제어부가 상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성된, 고체 활상 장치.

## 청구항 26

청구항 26은(는) 설정등록료 납부시 포기되었습니다.

제20항에 있어서,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 상기 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 흘러 전송된 제2 상태에서 상기 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호저장부가 상기 신호선의 신호를 샘플링할 때 상기 제2 전송 트랜지스터의 게이트의 전압이 상기 제3 전압이 되도록, 상기 전압 제어부가 상기 제2 전송 트랜지스터의 게이트의 전압을 제어하도록 구성된, 고체 활상 장치.

## 청구항 27

청구항 27은(는) 설정등록료 납부시 포기되었습니다.

제21항에 있어서,

상기 증폭 트랜지스터는 상기 플로팅 디퓨전 노드의 전압이 리셋된 제1 상태에서 상기 제1 신호를 신호선에 출력하도록 구성되고,

상기 증폭 트랜지스터는 또한 상기 플로팅 디퓨전 노드에 상기 흘러 전송된 제2 상태에서 상기 제2 신호를 상기 신호선에 출력하도록 구성되며,

상기 증폭 트랜지스터가 상기 제2 신호를 상기 신호선에 출력하는 기간 중 상기 신호선의 후측에 배치된 신호저장부가 상기 신호선의 신호를 샘플링할 때 상기 접속 트랜지스터의 게이트의 전압이 상기 제3 전압이 되도록, 상기 전압 제어부가 상기 접속 트랜지스터의 게이트의 전압을 제어하도록 구성된, 고체 활상 장치.

## 명세서

### 기술 분야

[0001]

본 발명은 고체 활상 장치에 관한 것이다.

### 배경기술

[0002]

고체 활상 장치 중 하나의 타입인 증폭형 고체 활상 장치에서는, 각 화소의 광전 변환부에서 발생된 전하를, 전송부를 거쳐서 증폭 트랜지스터의 입력 노드에 전송한다.

[0003]

전하가 전송될 때, 광전 변환부의 전하가 완전 전송되면 노이즈가 감소될 수 있다. 일본 공개 특허 공보 제2005-192191호는, 광전 변환부로부터 전송될 수 있는 최대 전하량을 증가시키는데 유용한 방법을 개시하고 있다.

### 발명의 내용

## 해결하려는 과제

[0004]

일본 공개 특허 공보 제2005-192191호에 개시된 고체 활상 장치에 따르면, 포토다이오드로부터 플로팅 디퓨전 (floating diffusion; FD)으로의 전하의 전송을 개시하기 전에, FD의 전압을 FD가 리셋(reset)될 때의 FD의 전압보다 높은 값으로 설정하고 있다. 그러나, 전하가 전송된 후, 증폭 트랜지스터로부터 신호를 출력할 때에, FD의 전압을 제어하는 것에 대해서는 개시하고 있지 않다.

[0005]

증폭형 고체 활상 장치에 따르면, 출력 신호의 선형성(linearity)이 양호한 동작 범위 내에서 증폭 회로를 동작 시키는 것이 바람직하다. 일본 공개 특허 공보 제2005-192191호에 개시된 고체 활상 장치에 따르면, FD의 전압이 높은 경우, 몇몇의 경우에서, 증폭 트랜지스터가 선형 영역에서 동작하거나, 또는 포화 영역과 선형 영역의 경계 영역에서 동작하는 경우가 있다. 출력 신호의 선형성을 유지하기 위해서는, 증폭 트랜지스터가 포화 영역에서 동작하는 것이 바람직하다. 따라서, 일본 공개 특허 공보 제2005-192191호에 개시되는 고체 활상 장치는, 증폭 트랜지스터로부터의 출력 신호의 선형성의 관점에 있어서 개선의 여지가 있다.

## 과제의 해결 수단

[0006]

본 발명은 광전 변환부로부터 플로팅 디퓨전으로의 전하 전송 효율을 향상시키면서 출력 신호의 양호한 선형성을 실현하는 고체 활상 장치에 관한 것이다.

[0007]

본 발명에 일 양태에 따르면, 고체 활상 장치는, 제1 광전 변환부와, 플로팅 디퓨전과, 상기 제1 광전 변환부에서 발생된 전자를 상기 플로팅 디퓨전에 전송하도록 구성된 제1 전송 트랜지스터와, 상기 플로팅 디퓨전의 전하량에 기초하는 신호를 출력하도록 구성된 증폭 트랜지스터와, 전압 제어 노드와, 상기 전압 제어 노드의 전압을 제어하도록 구성된 전압 제어부를 포함한다. 증폭 트랜지스터는 상기 플로팅 디퓨전의 전압이 리셋된 제1 상태에서 제1 신호를 출력하고, 또한 증폭 트랜지스터는 상기 플로팅 디퓨전에 상기 전자가 전송된 제2 상태에서 제2 신호를 출력하며, 전압 제어 노드는, 상기 제1 전송 트랜지스터의 도통 상태를 제어하는데 사용되는 전압이 공급되는 노드와는 다른 노드이고, 결합 커패시턴스(coupling capacitance)를 거쳐서 상기 플로팅 디퓨전에 결합된다. 상기 전압 제어 노드의 전압이, 상기 증폭 트랜지스터가 상기 제1 신호를 출력할 때 제1 전압이 되고; 상기 제1 전송 트랜지스터가 도통 상태에 있는 기간 중 적어도 일부 동안에 제2 전압이 되며; 상기 증폭 트랜지스터가 상기 제2 신호를 출력할 때 제3 전압이 되도록, 상기 전압 제어부가 상기 전압 제어 노드의 전압을 제어하고, 상기 제2 전압은 상기 제1 전압 및 상기 제3 전압 각각보다 높은 전압이다.

[0008]

본 발명의 예시적인 실시예에 따르면, 선형성이 향상될 수 있으며, 따라서 향상된 활상 품질을 실현하는 고체 활상 장치가 제공될 수 있다.

[0009]

본 발명의 추가적인 특징들 및 양태들은 첨부된 도면을 참조하여 하기의 예시적인 실시예들의 상세한 설명으로부터 명백해질 것이다.

[0010]

명세서의 일부에 포함되어 명세서의 일부를 구성하는 첨부된 도면은 상세한 설명과 함께 본 발명의 예시적인 실시예, 특징 및 양태를 도시하며, 본 발명의 원리를 설명한다.

## 도면의 간단한 설명

[0011]

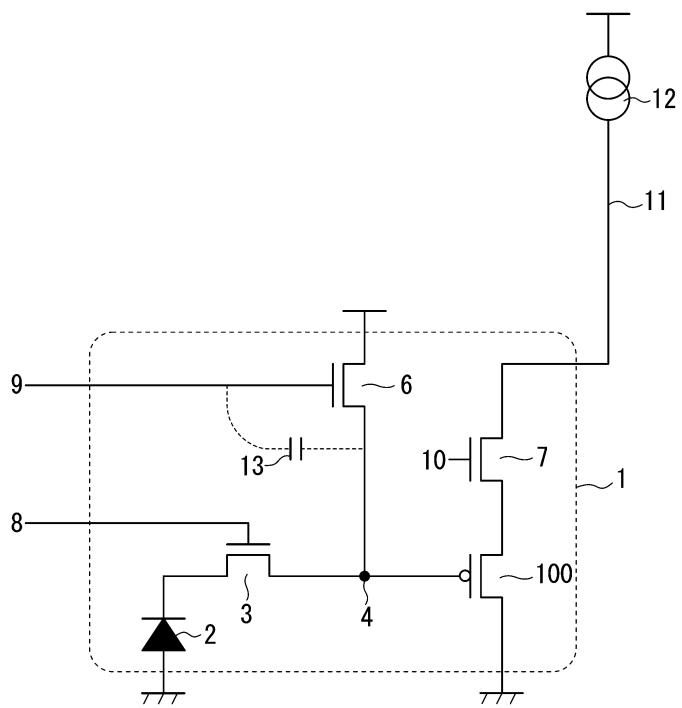

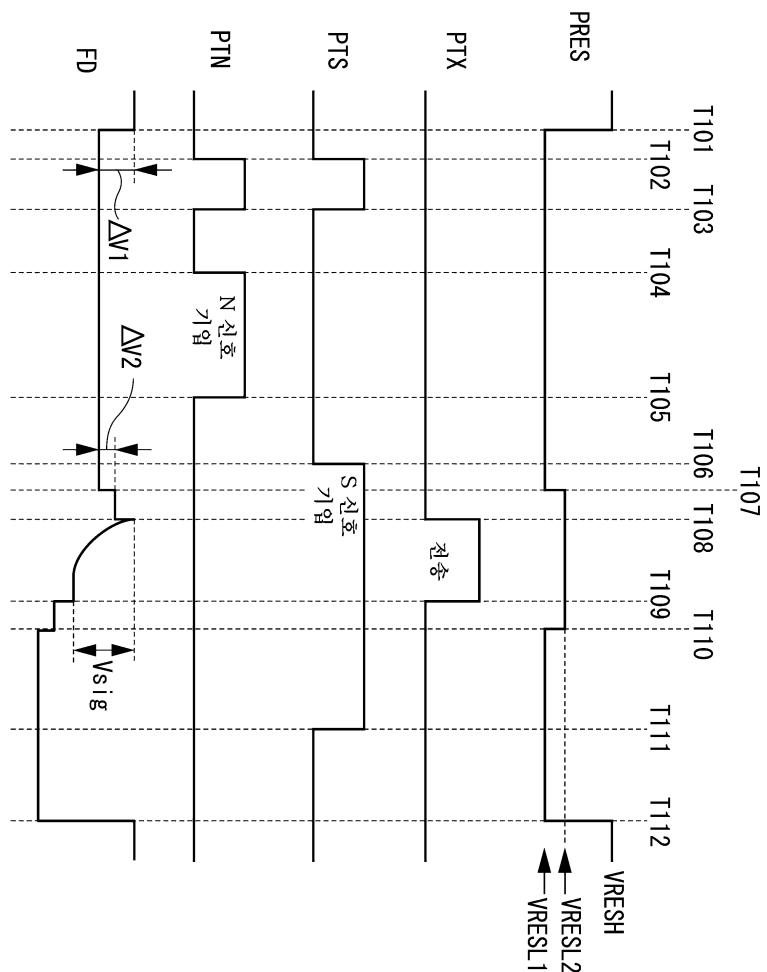

도 1은 본 발명의 예시적인 제1 실시예에 따른 화소의 등가 회로도.

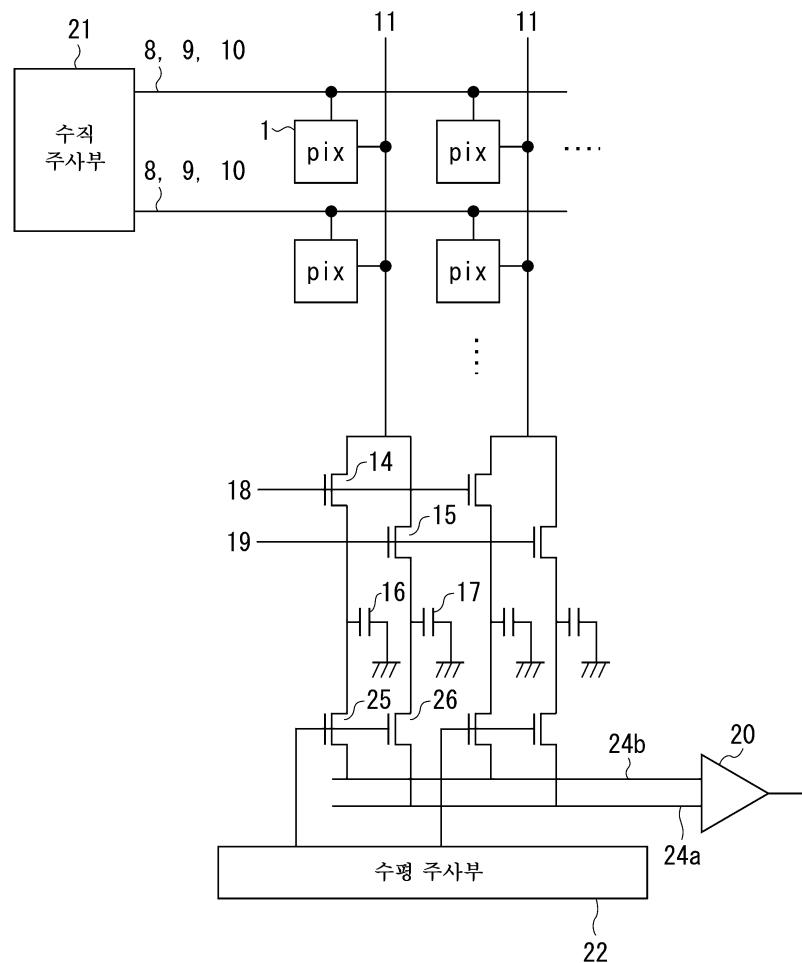

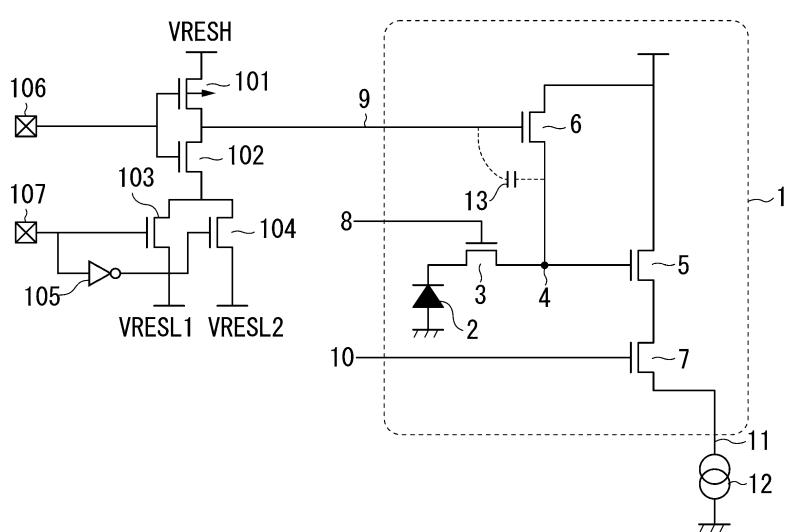

도 2는 예시적인 제1 실시예에 따른 화소 영역과 신호 저장부의 회로도.

도 3은 예시적인 제1 실시예에 따른 고체 활상 장치를 구동시키기 위한 구동 펄스를 도시하는 도면.

도 4는 예시적인 제1 실시예에 따른, 화소의 등가 회로와 도 3에 도시된 구동 펄스를 실현하는 회로를 도시하는 도면.

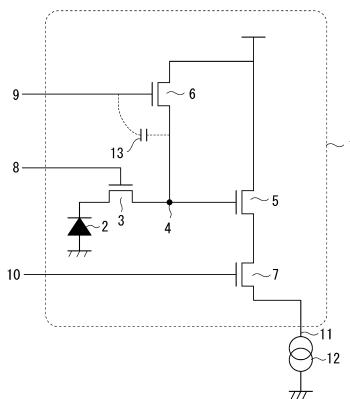

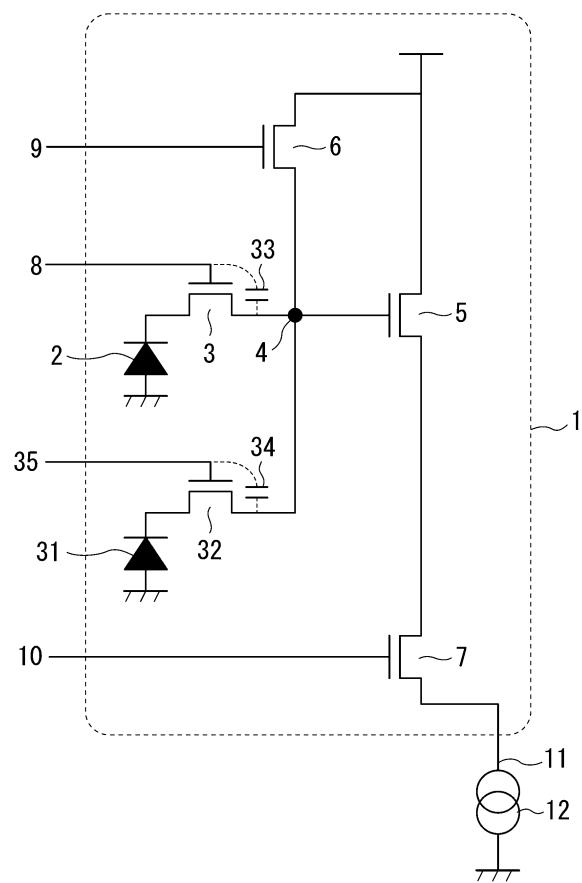

도 5는 본 발명의 예시적인 제2 실시예에 따른 화소의 등가 회로도.

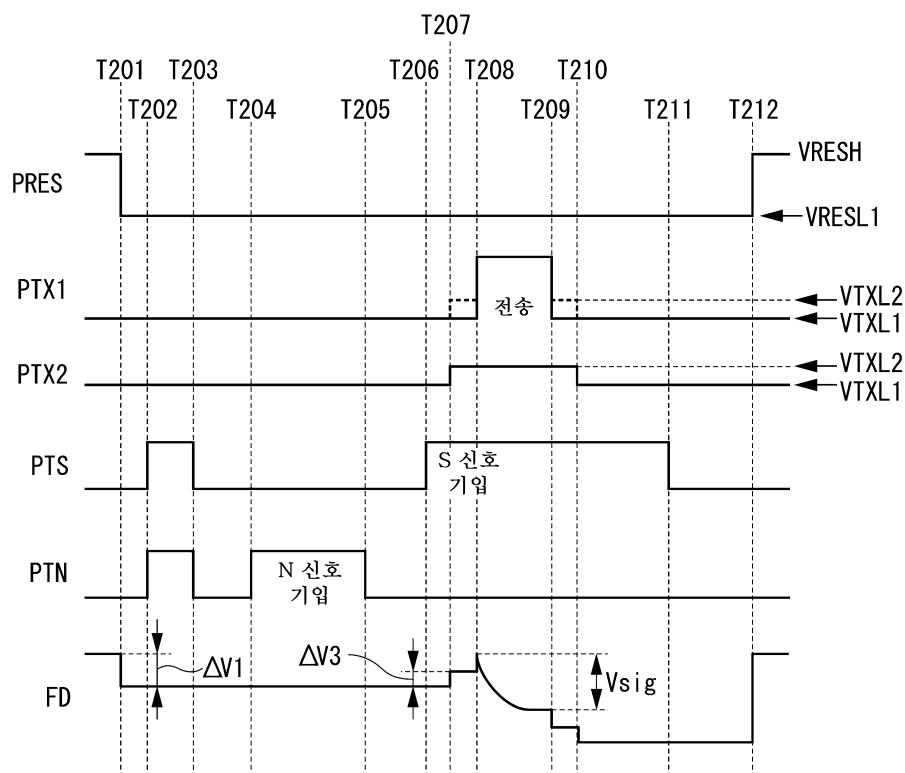

도 6은 예시적인 제2 실시예에 따른 고체 활상 장치를 구동시키기 위한 구동 펄스를 도시하는 도면.

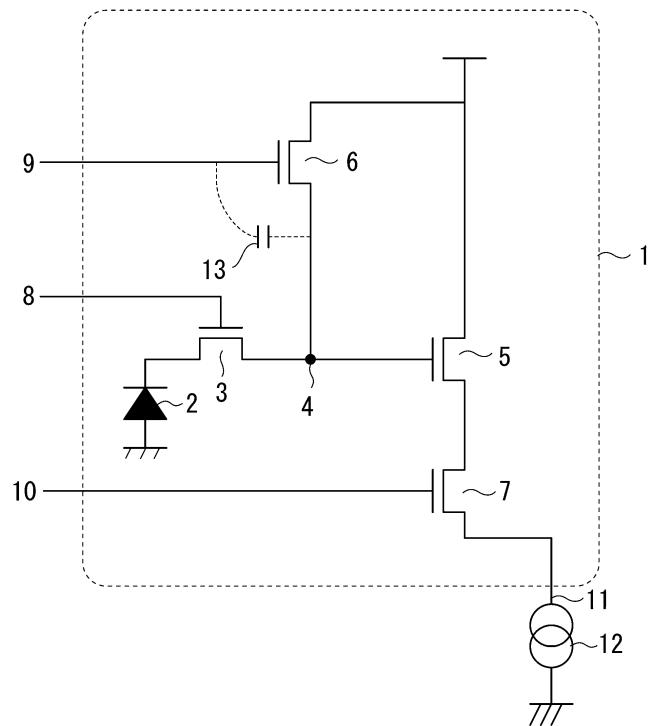

도 7은 본 발명의 예시적인 제3 실시예에 따른 화소의 등가 회로도.

도 8은 예시적인 제3 실시예에 따른 고체 활상 장치를 구동시키는데 사용되는 구동 펄스를 도시하는 도면.

도 9는 예시적인 제3 실시예에 따른 고체 활상 장치를 구동시키는데 사용되는 구동 펄스를 도시하는 도면.

도 10은 예시적인 제1 실시예에 따른 변형예에 따른 화소의 등가 회로를 도시하는 도면.

### 발명을 실시하기 위한 구체적인 내용

- [0012] 본 발명의 다양한 예시적인 실시예, 특징 및 양태가 도면을 참조하여 하기에 상세하게 기술될 것이다.

- [0013] 도 1은 본 발명의 예시적인 제1 실시예에 따른 화소의 등가 회로를 도시한다. 예시적인 제1 실시예에 따르면, 신호 전하로서 전자를 다룬다.

- [0014] 도 1에 있어서, 화소(1)는, 광전 변환부인 포토다이오드(PD)(2), 전송 트랜지스터(3), FD(4), 증폭 트랜지스터(5), 리셋 트랜지스터(6), 선택 트랜지스터(7)를 포함한다. 입사광은 PD(2)에 의해 광전 변환된다. 본 실시예에 따르면, PD(2)에서의 전자-홀 쌍(electron-hole pair)의 발생과 관련하여, 전자를 신호 전하로서 다룬다. 전송 트랜지스터(3)는 신호 전하를 PD(2)로부터 FD(4)에 전송한다. FD(4)는 증폭 트랜지스터(5)의 게이트에 접속된다.

- [0015] 증폭 트랜지스터(5)는 FD(4)의 전하량에 기초하는 신호를 출력한다. 본 실시예에 따르면, 증폭 트랜지스터(5)는 매립 채널형(buried-channel type)의 n형 채널 금속 산화물 반도체(metal oxide semiconductor; MOS) 트랜지스터이다. 리셋 트랜지스터(6)는 리셋 전원에 기초하는 전압을 FD(4)에 공급하고, FD(4)의 전압을 리셋시킨다. 선택 트랜지스터(7)에 의해, 판독될 화소 행(row)이 복수의 화소 행으로부터 선택된다.

- [0016] 전송 트랜지스터(3), 리셋 트랜지스터(6), 선택 트랜지스터(7)의 게이트에, 각각 제어선(8, 9, 10)이 접속된다. 트랜지스터의 게이트는 서로 전기적으로 단락되지 않고 있다. 각각의 게이트 사이에 결합 커패시턴스가 형성될 수 있지만, 각각의 트랜지스터의 도통 상태는 독립적으로 제어될 필요가 있다. 증폭 트랜지스터(5)로부터의 증폭 신호는 수직 출력선(11)에 출력된다. 수직 출력선(11)에는, 정전류원(constant current source)(12)이 접속된다. 증폭 트랜지스터(5)와 정전류원(12)에 의해 소스 팔로워(source follower) 회로가 구성된다.

- [0017] 커패시터(13)는, 리셋 트랜지스터(6)의 게이트와 FD(4) 사이에 형성되며, 리셋 트랜지스터(6)의 게이트 및 소스 사이의 결합 커패시턴스이다. 커패시터(13)가 형성됨으로써, 리셋 트랜지스터(6)의 게이트에 공급되는 전압에 따라, FD(4)의 전압을 변화시키는 것이 가능하다.

- [0018] 상세한 것은 후술하지만, 본 실시예에 따르면, 리셋 트랜지스터(6)의 게이트에 접속되는 제어선(9)의 전압을 제어하는 것에 의해, FD(4)의 전압이 제어될 수 있다. 구체적으로는, PD(2)로부터 FD(4)에 전자를 전송할 때의 제어선(9)의 전압을, 증폭 트랜지스터(5)가 신호를 출력할 때의 제어선(9)의 전압보다 높도록 제어한다.

- [0019] 도 2는 본 실시예에 따른 화소 영역과 신호 저장부의 회로도이다. 도 1에 도시된 행렬 형상(matrix)의 복수의 화소(1)에 의해 화소 영역이 구성된다. 제어선(8, 9, 10)은, 1개의 화소 행에 포함되는 복수의 화소에 공통적으로 접속된다. 수직 주사부(21)는 각각의 제어선(8, 9, 10)에 소정의 전압을 공급한다. 수직 주사부(21)는 대응하는 트랜지스터의 도통 상태를 제어한다. 화소의 트랜지스터의 게이트들은 서로 단락되어 있지 않으므로, 각각의 트랜지스터의 도통 상태는 독립적으로 제어될 수 있다. 수직 주사부(21)는 후술하는 전압 제어부의 일부를 구성한다.

- [0020] 수직 출력선(11)은 1개의 화소 열(column)에 포함되는 복수의 화소의 출력 노드에 공통적으로 접속된다. 도 1에 도시된 바와 같이, 화소의 출력 노드는, 예컨대 선택 트랜지스터(7)의 소스이다. 다른 경우에 있어서, 출력 노드는 증폭 트랜지스터의 소스이다. 복수의 수직 출력선(11)으로부터 출력된 각각의 신호는 대략 동일한 타이밍에 신호 저장부에 공급되어, 신호 저장부에 저장된다.

- [0021] 본 실시예에 따르면, 신호 저장부는 각 화소 열에 형성된다. 본 실시예에 따른 신호 저장부는, 2개의 샘플-앤파드-홀드(sample-and-hold) 커패시터(16, 17) 뿐만 아니라, 2개의 스위치(14, 15)를 포함한다. 스위치(14, 15)는 수직 출력선(11)과 샘플-앤파드-홀드 커패시터(16, 17) 사이의 전기적 접속을 제어한다. 스위치(14, 15)의 각각의 게이트에는 제어선(18, 19)이 접속된다. 또한, 제어선(18, 19)에는, 대응하는 스위치의 도통 상태를 제어하는데 사용되는 구동 펄스가 공급된다.

- [0022] 샘플-앤파드-홀드 커패시터(17)는, FD(4)의 전압이 리셋될 때, 증폭 트랜지스터(5)로부터 출력되는 신호(이하, N 신호로서 지칭됨)를 보유한다. 본 실시예에 따르면, FD(4)는, 리셋 트랜지스터(6)가 리셋 전원에 기초하는 전압을 FD(4)에 공급할 때로부터 신호 전하가 FD(4)에 전송될 때까지, 전압 리셋 상태에 있다. 이 기간 동안의 적어도 일부의 타이밍에 있어서, N 신호의 샘플링(sampling)이 샘플-앤파드-홀드 커패시터(17)에서 수행될 수 있다. N 신호에는, 리셋 트랜지스터(6)가 턴 오프(turn off)될 때에 발생되는 리셋 노이즈가 포함될 수 있다.

- [0023] 샘플-앤드-홀드 커패시터(16)는, FD(4)에 신호 전하가 전송될 때 증폭 트랜지스터(5)로부터 출력되는 신호(이하, S 신호로서 지칭됨)를 보유한다. 본 실시예에 따르면, FD(4)는, FD(4)에 신호 전하가 전송될 때로부터 리셋 전원에 기초하는 전압이 FD(4)에 공급될 때까지, 전하 전송 상태에 있다. 이 기간 동안의 적어도 일부의 타이밍에 있어서, S 신호의 샘플링이 수행될 수 있다.

- [0024] 스위치(25, 26)는 샘플-앤드-홀드 커패시터(16, 17)와 수평 출력선(24a, 24b)의 접속을 제어한다. 스위치(25, 26)의 도통 상태를 제어하는데 사용되는 구동 펄스가 수평 주사부(22)로부터 대응하는 스위치에 공급된다. 수평 주사부(22)에 의해, 샘플-앤드-홀드 커패시터(16)에 의해 보유되는 S 신호와, 샘플-앤드-홀드 커패시터(17)에 의해 보유되는 N 신호가 차동 증폭기(20) 내의 각각의 열에 순차적으로 입력된다.

- [0025] 차동 증폭기(20)는 S 신호와 N 신호 사이의 차분을 증폭해서, 얻어진 결과를 출력한다. S 신호와 N 신호 사이의 차분 연산 처리에 의해, 증폭 트랜지스터(5)의 역치 격차로 인한 고정 패턴 노이즈가 제거된다. S 신호와 N 신호가 서로 상관된 리셋 노이즈를 포함하는 경우에는, FD(4)가 리셋될 때 발생되는 리셋 노이즈가 제거될 수 있다.

- [0026] 도 3은 본 실시예에 따른 고체 활상 장치를 구동시키는데 사용되는 구동 펄스를 도시한다. 또한, 도 3은 본 실시예의 고체 활상 장치의 동작에 따르는 FD(4)의 전압의 변화를 개략적으로 도시하고 있다.

- [0027] 도 3에서, PRES는 제어선(9)을 거쳐 리셋 트랜지스터(6)의 게이트에 공급되는 구동 펄스를 지칭한다. PTX는 제어선(8)을 거쳐 전송 트랜지스터(3)의 게이트에 공급되는 구동 펄스를 지칭한다. PTS는 제어선(18)을 거쳐 스위치(14)에 공급되는 구동 펄스를 지칭한다. PTN은 제어선(19)을 거쳐 스위치(15)에 공급되는 구동 펄스를 지칭한다. 구동 펄스의 전압이 하이 레벨(high level)에 있는 경우, 대응하는 트랜지스터와 스위치는 턴 온(turn on)된다. 구동 펄스의 전압이 로우(low) 레벨에 있는 경우, 대응하는 트랜지스터는 턴 오프된다.

- [0028] 또한, 본 실시예에 따르면, 제어선(9)으로부터 공급되는 PRES의 로우 레벨의 전압으로서, 2개의 다른 전압 VRESL1 및 VRESL2가 설정될 수 있다. VRESL1 및 VRESL2는 모두 리셋 트랜지스터(6)가 턴 오프되는 전압이지만, VRESL2는 VRESL1보다 높다. 즉, 리셋 트랜지스터(6)는, PRES에 공급되는 전압이 하이 레벨의 전압 VRESH일 때에 턴 온되고, PRES에 공급되는 전압이 로우 레벨의 전압 VRESL1 또는 VRESL2(VRESL2>VRESL1)일 때에 턴 오프된다.

- [0029] 다음에, 도 3을 참조하여, 본 실시예에 따른 고체 활상 장치의 구동 방법을 설명한다. 도 3에서, 이미 노광이 개시되어 있고, PD(2)는 신호 전하를 갖고 있다. 또한, 판독될 화소 행의 선택 트랜지스터(7)는 턴 온되어 있다.

- [0030] 처음에는, PTX, PTS 및 PTN이 로우 레벨이며, 전송 트랜지스터(3) 및 스위치(14, 15)는 턴 오프되어 있다. PRES가 하이 레벨이며, 리셋 트랜지스터(6)가 턴 온되어 있으므로, FD(4)의 전압은 리셋되어 있다. 이 상태에서, FD(4)의 리셋 전압 Vrs는, 리셋 트랜지스터(6)의 게이트에 공급된 전압 VRESH와, 리셋 트랜지스터(6)의 역치 전압 Vth\_res를 사용하여, 하기 식 (1)에 의해 얻어진다. 리셋 전원의 전압은 VRESH-Vth\_res보다 높다.

- [0031] [식 (1)]

- [0032]

$$V_{rs} = V_{RESH} - V_{th\_res}$$

- [0033] 시간 T101에서, PRES가 VRESH로부터 VRESL1로 변화된다. 이러한 리셋 트랜지스터(6)의 게이트의 전압의 변화에 따라, FD(4)의 전압이 커패시터(13)를 거쳐  $\Delta V1$ 만큼 저하된다. 시간 T101에서 리셋 트랜지스터(6)가 턴 오프된 후에, FD(4)의 전압이 리셋되었을 때 출력되는 신호인 N 신호가 수직 출력선(11)에 출력된다. N 신호에는, 리셋 트랜지스터(6)가 턴 오프되었을 때 발생되는 kTC 노이즈 등의 리셋 노이즈가 포함된다.

- [0034] 다음에, 시간 T102에서, PTS와 PTN이 하이 레벨로 변화되고, 스위치(14, 15)가 턴 온되고, 수직 출력선(11)과 샘플-앤드-홀드 커패시터(16, 17)가 도통된다. 따라서, 샘플-앤드-홀드 커패시터(16, 17)가 수직 출력선(11)에 출력된 N 신호에 의해 리셋된다. 시간 T103에서, PTS와 PTN이 로우 레벨로 변화되고, 수직 출력선(11)과 샘플-앤드-홀드 커패시터(16, 17)가 비도통이 된다.

- [0035] 시간 T104에서, PTN이 하이 레벨로 변화된다. 그 후에, 스위치(15)가 턴 온되고, 샘플-앤드-홀드 커패시터(17)에 N 신호의 기입이 개시된다. 시간 T105에서, PTN이 로우 레벨로 변화되고, 스위치(15)가 턴 오프되며, 샘플-앤드-홀드 커패시터(17)에의 N 신호의 기입이 종료한다. 도 3에 도시되는 바와 같이, 리셋 트랜지스터(6)의 게이트의 전압이 VRESL1로 제어되고, PTN이 하이 레벨인 기간(T104 내지 T105)이 FD의 전압 변화가 안정되는데

충분히 긴 것이 바람직하다.

[0036] 다음에, 시간 T106에서, PTS가 하이 레벨로 변화되고, 스위치(14)가 턴 온되며, 샘플-앤드-홀드 커페시터(16)에의 S 신호의 기입이 개시된다.

[0037] 시간 T107에서, PRES의 전압이 VRESL1로부터 VRESL2로 변화된다. 이러한 전압의 변화에 따라, 커페시터(13)를 거쳐서 FD(4)의 전압이  $\Delta V2$ 만큼 상승된다. PRES의 전압이 VRESL2로 상승되어도, 리셋 트랜지스터(6)는 턴 온되지 않는다.

[0038] 시간 T108에서, PTX가 하이 레벨로 변화되고, 전송 트랜지스터(3)가 턴 온된다. 이 시점에서, PD(2)의 신호 전하의 FD(4)로의 전송이 개시된다. 시간 T109에서, PTX가 로우 레벨로 변화되고, 전송 트랜지스터(3)가 턴 오프되며, 신호 전하의 전송이 종료한다. T108과 T109 사이의 시간은, PD(2)에 축적된 모든 신호 전하가 전송될 수 있을 만큼 충분히 긴 것이 바람직하다.

[0039] 모든 신호 전하가 전송될 경우, 즉 신호 전하가 완전 전송될 경우에는, 시간 T109 이전에 신호 전하의 전송이 완료될 수 있다. 또한, FD(4)에 전송된 신호 전하량에 따라, FD(4)의 전압은 전압  $Vsig$ 만큼 저하된다. 신호 전하가 FD(4)에 전송된 후에는, FD(4)에 신호 전하가 전송된 상태에서 출력된 신호인 S 신호가 수직 출력선(11)에 출력된다.

[0040] 시간 T110에서, PRES의 전압이 VRESL2로부터 VRESL1로 변화되면, FD(4)의 전압이  $\Delta V2$ 만큼 저하된다.

[0041] 다음에, 시간 T111에서, PTS가 로우 레벨로 변화된다. 그 후에, 스위치(14)가 턴 오프되고, 샘플-앤드-홀드 커페시터(16)에의 S 신호의 기입이 종료한다. 리셋 트랜지스터(6)의 게이트의 전압이 VRESL1로 제어되고, PTS가 하이 레벨인 기간(T110 내지 T111)이 FD의 전압 변화가 안정되는데 충분한 긴 것이 바람직하다. 시간 T112에서, PRES가 VRESH로 변화되고, FD(4)의 전압이 리셋된다.

[0042] 본 실시예에 관련된 2개의 중요한 요점이 있다. 제1 요점은, 시간 T105 및 시간 T111에서 리셋 트랜지스터(6)의 게이트에 공급되는 전압이 VRESL1로 제어된다는 점이다. 제2 요점은, 시간 T107 내지 T110에서 리셋 트랜지스터(6)의 게이트에 공급되는 전압이 VRESL1보다 높은 전압인 VRESL2로 제어된다는 점이다.

[0043] 제2 요점에 따르면, VRESL1이 공급되는 경우에 비해, 전압  $\Delta V2$ 로 FD(4)에 신호 전하가 전송될 수 있다. PD(2)의 전압은, 광전 변환 이전에 리셋되었을 때의 전압으로부터 광전 변환에 의해 발생된 신호 전하량을 따라 저하된다. 이러한 상태에서, FD(4)의 전압이  $\Delta V2$ 만큼 상승되므로, PD(2)와 FD(4) 사이의 전압 차가 증가될 수 있다. 이에 따라, PD(2)로부터 FD(4)에 전송할 수 있는 최대 전하량을 증가시킬 수 있으며, 신호 전하의 완전 전송이 보다 용이하게 된다.

[0044] 또한, 제1 요점에 따르면, FD(4)의 전압이 저하되므로, 증폭 트랜지스터(5)가 포화 영역에서 보다 용이하게 동작할 수 있다. 따라서, 증폭 트랜지스터로부터의 출력 신호의 선형성이 향상될 수 있다.

[0045] 도 3에 도시된 동작에 따르면, 전송 트랜지스터(3)가 턴 온되는 동안, 리셋 트랜지스터(6)의 게이트의 전압이 증폭 트랜지스터에 의해 출력되는 전압보다 높은 전압으로 계속 유지된다. 그러나, 리셋 트랜지스터(6)의 게이트에 공급되는 전압이 VRESL2로 제어되고 있는 기간이, 전송 트랜지스터(3)가 턴 온되어 있는 기간의 일부와 겹치고 있는 동안 동작이 수행될 수 있다.

[0046] 도 4는 VRESH, VRESL1, VRESL2 3개의 값을 제어선(9)에 공급하는데 사용되는 회로의 예를 도시한다. p형 채널 MOS(PMOS) 트랜지스터(101)는, 게이트에 로우 레벨의 전압이 공급되었을 때에 턴 온되고, 하이 레벨의 전압이 공급되었을 때에 턴 오프된다. n형 채널 MOS(NMOS) 트랜지스터(102, 103, 104)는, 각각의 게이트에 하이 레벨의 전압이 공급되었을 때에 턴 온되고, 각각의 게이트에 로우 레벨의 전압이 공급되었을 때에 턴 오프된다. 또한, 회로는 인버터(105)를 포함한다.

[0047] 제1 노드(106)의 전압을 로우 레벨의 전압으로 설정하면, 제2 노드(107)의 전압에 관계없이, 제어선(9)에 VRESH가 출력된다. 제1 노드(106), 제2 노드(107)의 전압을 모두 하이 레벨의 전압으로 설정하면, 제어선(9)에 VRESL1이 출력된다. 제1 노드(106)의 전압을 하이 레벨의 전압으로 설정하고, 제2 노드(107)의 전압을 로우 레벨의 전압으로 설정하면, 제어선(9)에 VRESL2가 출력된다.

[0048] 트랜지스터(101 내지 104) 및 인버터(105)는 도 2에 도시된 수직 주사부(21)의 후단에 배치되거나, 또는 수직 주사부(21)와 일체로 구성된다. 제1 노드(106)와 제2 노드(107) 중 적어도 한 쪽에 수직 주사부(21)로부터의 펄스가 공급된다. 즉, 제1 노드(106)와 제2 노드(107) 양자에 수직 주사부(21)로부터의 펄스가 공급될 수 있지

만, 하나의 노드에 공급될 수도 있다. 펄스가 단 하나의 노드에만 공급되는 경우, 펄스는 칩의 외부로부터 직접적으로 또는 칩의 외부로부터 간단한 로직 회로를 통해 다른 노드에 공급될 수 있다.

[0049] 따라서, 적어도 수직 주사부(21), 트랜지스터(101 내지 104) 및 인버터(105)에 의해, 제어선(9)에 3개以上の 전압을 공급할 수 있으므로, 이를 성분이 결합 커패시턴스를 거쳐서 FD에 접속된 노드의 전압 제어부로서 기능한다. 또한, 전압 제어부에 타이밍 발생기가 포함될 수 있다.

[0050] 다음에, 본 실시예에 의해 얻어지는 효과를 상세하게 설명한다. 우선, 광전 변환부의 신호 전하의 완전 전송을 수행하는데 필요한 조건과, 센서 출력의 선형성을 양호하게 유지시키는데 필요한 조건에 관하여 설명한다.

[0051] 하기의 설명에 있어서, PD(2)에 축적될 수 있는 최대 전하량을 포화 전하량이라고 한다. PD(2)에 포화 전하량의 신호 전하가 축적되었을 경우에, 신호 전하의 완전 전송을 수행하는데 필요한 조건은, 하기 식 (2)로 표현된다.

[0052] [식 (2)]

$$V_{rs} - V_{sat} > V_{dep}$$

[0054]  $V_{sat}$ 는 PD(2)의 포화 전하량의 신호 전하가 FD(4)에 전송되었을 때의 FD(4)의 전압 변화량이고,  $V_{dep}$ 는 PD(2)의 완전 공핍(full depletion)을 수행하는데 필요한 FD(4)의 전압이다.

[0055] 완전 공핍되는 영역은, PD(2)를 구성하는 반도체 영역 중, 적어도 n형의 반도체 영역이다.  $V_{dep}$ 는 PD(2)를 구성하는 n형 반도체 영역을 완전히 공핍시킬 수 있는 전압이다. 식 (2)로부터 알 수 있는 바와 같이, 신호 전하의 완전 전송에 대해, FD(4)의 리셋 전압  $V_{rs}$ 가 높은 쪽이 바람직하다.

[0056] 입사광량과 증폭 트랜지스터의 출력 신호 사이의 양호한 관계에 기초하는 선형성을 얻기 위해서, 증폭 트랜지스터(5)가 소스 팔로워 동작하기 위한 조건(포화 영역에서 동작하기 위한 조건)인 식 (3)을 만족시킬 필요가 있다.

[0057] [식 (3)]

$$V_g - V_d < V_{th\_sf}$$

[0059]  $V_g$ ,  $V_d$  및  $V_{th\_sf}$ 는 각각 증폭 트랜지스터(5)의 게이트 전압, 드레인 전압, 역치 전압이다.

[0060] 도 1에 도시된 바와 같이, 증폭 트랜지스터(5)의 게이트가 FD(4)에 접속되어 있으므로,  $V_g$ 는 FD(4)의 전압이다. 유사하게, 증폭 트랜지스터(5)의 드레인이 전원에 접속되어 있으므로,  $V_d$ 는 전원 전압이다. FD(4)에 신호 전하가 전송되면 FD(4)의 전압은 저하되므로,  $V_g$ 가 FD(4)의 리셋 전압인  $V_{rs}$ 일 때에 식 (3)이 만족되면, 광범위한 휘도 영역에 걸쳐 양호한 선형성이 유지될 수 있다. 따라서, 광범위한 휘도 영역에서의 양호한 선형성을 위한 조건은 식 (4)에 의해 표현될 수 있다.

[0061] [식 (4)]

$$V_{rs} - V_d < V_{th\_sf}$$

[0063] 식 (4)가 나타내는 바와 같이, 선형성을 향상시키기 위해, FD(4)의 보다 낮은 전압이 바람직하다. 즉, FD(4)의 보다 낮은 리셋 전압이 바람직하다. 그러나, 식 (4)을 만족시키기 위해 리셋 전압  $V_{rs}$ 를 저하시키면, 완전 전송을 위한 조건인 식 (2)를 만족시키는 것이 곤란해진다.

[0064] 일본 공개 특허 공보 제2005-192191호에 신호 전하의 완전 전송을 위한 FD(4)의 전압을 상승시키는 방법이 개시되어 있다. 그러나, FD(4)의 전압이 높은 상태에서 증폭 트랜지스터(5)로부터 신호가 출력되면, 식 (3)을 만족시키기 어려우므로, 선형성을 얻는 것이 곤란해진다.

[0065] 상술된 바와 같이, 신호 전하의 완전 전송 또는 고효율의 전하 전송과, 증폭 트랜지스터로부터의 출력 신호의 선형성 사이에는, 트레이드-오프의 관계가 존재한다. 따라서, 신호 전하의 완전 전송을 실현하기 위한 조건인 식 (2)와, 양호한 선형성을 실현하기 위한 조건인 식 (4)가 만족될 필요가 있는 시간이 주목되었다.

[0066] 식 (2)는 전하 전송시(도 3의 시간 T108 내지 T109)에만 만족될 필요가 있으며, 전하 전송이 수행되지 않을 때에는 반드시 만족될 필요는 없다. 한편, 식 (4)는, S 신호 및 N 신호가 대응하는 샘플-앤파-홀드 커패시터(16, 17)에 기입되는 시간 T111 및 T105에서만 만족될 필요가 있으며, 그 이외의 기간에서는 반드시 만족될 필요는 없다. 따라서, 2개의 조건을 만족시키기 위해서는, 시간 T111 및 T105에서 FD(4)의 전압은 로우 레벨로 제어되어

고, T108과 T109 사이의 적어도 일부의 시간에서 FD(4)의 전압은 하이 레벨로 제어된다.

[0067] 본 실시예에 따르면, 시간 T105 및 T111에서는 리셋 트랜지스터(6)의 게이트에 VRESL1이 공급되고, 시간 T107과 시간 T110 사이에서는 리셋 트랜지스터(6)의 게이트에 VRESL2가 공급된다. T107에서의 FD(4)의 전압은,  $V_{rs} - \Delta V_1 + \Delta V_2$ 로 표현된다. 시간 T105에서의 FD(4)의 전압은,  $V_{rs} - \Delta V_1$ 로 표현된다. 따라서, 신호 전하의 완전 전송을 위한 조건과, 양호한 선형성을 얻기 위한 조건은, 식 (1)을 사용하여, 식 (5) 및 식 (6)에 의해 표현될 수 있다.

[0068] [식 (5)]

$$V_{RESH} - V_{th\_res} - \Delta V_1 + \Delta V_2 - V_{sat} > V_{dep}$$

[0070] [식 (6)]

$$V_{RESH} - V_{th\_res} - \Delta V_1 - V_d < V_{th\_sf}$$

[0072] 시간 T111에서의 FD(4)의 전압은,  $V_{rs} - \Delta V_1 - V_{sig}$ 로 표현된다.  $V_{sig}$ 는 신호 전하의 전송으로 의한 FD(4)의 전압 변화량이다. 신호 전하가 전자인 경우에는, 신호 전하의 전송에 따라 FD(4)의 전압이 저하되므로, 식 (6)이 만족되면 양호한 선형성이 얻어질 수 있다.

[0073] 예를 들면, VRESH를 고정시키고, 식 (6)을 만족시키는  $\Delta V_1$ 을 제공하는 VRESL1을 설정한 후, 식 (5)을 만족시키는  $\Delta V_2$ 를 제공하는 VRESL2를 설정함으로써, 식 (5) 및 식 (6) 양자를 만족시킬 수 있다. 따라서, 본 실시예에 의하면, 전송할 수 있는 최대 전하량을 증가시키도록, 신호 전하의 전송시에 FD(4)의 전압을 상승시키는 경우에도, 센서 출력의 양호한 선형성을 얻을 수 있다. 식 (5) 및 식 (6)을 완전하게 만족시키는 것이 바람직하지만, 시간 T111 및 T105에서 FD(4)의 전압을 로우 레벨로 제어하고, T108과 T109 사이의 적어도 일부의 시간에서 FD(4)의 전압을 하이 레벨로 제어함으로써, 식 (5) 및 식 (6)이 완전하게 만족되지 않는 경우에도, 소정의 효과가 얻어질 수 있다.

[0074] 또한, 증폭 트랜지스터(5)로서 매립 채널형 트랜지스터를 사용함으로써, 랜덤 텔레그래프 신호(random telegraph signal; RTS) 노이즈 등의 노이즈를 저감시킬 수 있다. 채널을 게이트 절연막과 채널부의 계면으로부터 채널부에 깊게 매립할수록, 얻어지는 노이즈 저감의 효과는 커진다. 그러나, 증폭 트랜지스터(5)로서 매립 채널형 트랜지스터를 사용하면,  $V_{th\_sf}$ 가 저하된다. 채널부에 채널을 깊게 매립할수록  $V_{th\_sf}$ 는 저하되므로, 식 (4)를 만족시키기 어려워진다. 따라서, 증폭 트랜지스터로서 사용되는 매립 채널형 트랜지스터에 본 실시예의 구성을 적용하면, 선형성과 관련된 향상 효과가 보다 현저해질 수 있다.

[0075] 식 (2) 및 식 (4)는 각각 하기의 식 (7) 및 식 (8)로 변형될 수 있다. 증폭 트랜지스터(5)의 역치 전압이 낮을 경우, 특히 네거티브(negative)가 되는 경우에는,  $V_{sat} + V_{dep}$ 이  $V_d + V_{th\_sf}$ 보다 커질 수 있다. 식 (7) 및 식 (8) 양자를 동시에 만족시키는 리셋 전압  $V_{rs}$ 는 존재하지 않는다. 이러한 경우에 본 발명을 실시하면, 저회도 영역에서의 선형성과 관련된 향상의 효과가 보다 현저해질 수 있다.

[0076] [식 (7)]

$$V_{sat} + V_{dep} < V_{rs}$$

[0078] [식 (8)]

$$V_{rs} < V_d + V_{th\_sf}$$

[0080] 또한, 완전 전송의 과제를 해결하기 위한 방법으로서, 일본 공개 특허 공보 제2005-192191호에는, 전하 전송시에 FD의 전압을 상승시키는 방법이 개시되어 있다. 이러한 방법은, 증폭 트랜지스터로부터 출력되는 증폭 신호의 신호 출력선과 FD 사이에 형성되는 결합 커패시턴스를 사용한다. 이러한 결합 커패시턴스는, 의도적으로 일체화된 커패시터일 수 있지만, 기생 커패시턴스일 수도 있다.

[0081] 결합 커패시턴스가 기생 커패시턴스인 경우에는, 제조 프로세스에 기인하는 편차가 상당하기 때문에, 전압 제어의 정밀도에 편차가 있다. FD의 커패시턴스는, p-n 접합 커패시턴스, FD로부터 증폭 트랜지스터의 게이트까지의 배선(와이어링)과 다른 배선 또는 실리콘 기판 사이에 제공되는 커패시턴스, 증폭 트랜지스터의 게이트 커패시턴스 등의 다수의 성분으로 구성된다.

[0082] 이들 커패시턴스 중에서, FD로부터 증폭 트랜지스터의 게이트까지의 배선과, 상층의 배선 사이에 제공되는 커패시턴스는, 충간 절연막의 두께의 편차에 따라 변동하기 쉽다. 특히 평탄화 프로세스에서 화학적 기계적 평탄화

(chemical mechanical planarization; CMP) 프로세스를 사용하는 일반적인 다층 배선 기술이 사용될 때, 그 편차가 현저하다.

[0083] 본 실시예에 따르면, 리셋 트랜지스터(6)의 소스가 FD(4)에 접속되고, 리셋 트랜지스터(6)의 게이트와 소스 사이에 형성된 결합 커패시턴스에 의해, FD(4)의 전압이 제어된다. 리셋 트랜지스터(6)의 게이트와 소스 사이의 결합 커패시턴스가 커패시터(13)의 주요 성분이다.

[0084] MOS 트랜지스터의 게이트 전극 형성 프로세스에 기인하는 제조 편차는, CMP 프로세스에 기인하는 제조 편차보다 작기 때문에, 상술된 구성에 따라, 고정밀도로 FD(4)의 전압을 제어할 수 있다. 소스 또는 드레인에 FD에 접속된 MOS 트랜지스터의 게이트 전압을 제어하는 구성에 따르면, 제조 프로세스에 기인하는 편차의 영향이 적은 방법을 사용함으로써, 센서 출력의 선형성이 향상될 수 있다.

[0085] 또한, 본 실시예는, FD(4)에 대하여 의도적으로 커패시턴스를 형성함으로써 실현될 수 있다. 그러나, 이 경우, 화소부의 레이아웃 면적에 악영향을 미친다. 본 실시예에 따르면, 리셋 트랜지스터(6)의 게이트와 소스 사이에 형성된 결합 커패시턴스를 사용함으로써 FD(4)의 전압이 제어되기 때문에, 화소부의 레이아웃에 악영향을 미치는 일이 없다.

[0086] 제조 프로세스에 기인하는 편차가 작다고 하는 이점은, 결합 커패시턴스가 MOS 트랜지스터의 게이트와 FD에 접속될 경우에 얻어진다. 화소부의 레이아웃에 악영향을 미칠 일이 없다고 하는 이점은, 화소에 포함되는 MOS 트랜지스터의 게이트와 FD에 결합 커패시턴스가 접속되는 경우에 얻어진다. MOS 트랜지스터는, 예를 들면 리셋 트랜지스터, 전송 트랜지스터 또는 선택 트랜지스터이다.

[0087] 본 실시예에 따르면, 시간 T105 및 T111에서, 전압 VRESL1이 공급되도록 리셋 트랜지스터(6)의 게이트에 공급되는 전압이 제어된다. 그러나, 리셋 트랜지스터(6)의 게이트에 공급되는 전압이 VRESL2보다 낮으면, 시간 T105 및 T111에서 리셋 트랜지스터(6)의 게이트에 다른 전압이 공급될 수 있다. 이는 S 신호 및 N 신호가 출력될 때, 리셋 트랜지스터(6)의 게이트의 전압이 전하 전송이 수행될 때 사용되는 전압보다 낮은 전압으로 제어되는 동안, 선형성의 향상이 얻어질 수 있기 때문이다.

[0088] 본 실시예에서와 같이, 시간 T105 및 T111에서, 리셋 트랜지스터(6)의 게이트에 동일한 값의 전압이 공급되면, S 신호 및 N 신호의 기준 전압에 차이가 생기지 않는다. 따라서, S 신호와 N 신호의 차분 처리를 행했을 때에, 오프셋이 적은 센서 출력을 얻을 수 있다.

[0089] 신호 전하가 전자에 의해 이동되는 경우에, p형 채널의 증폭 트랜지스터가 사용될 수 있다. 도 10은 예시적인 제1 실시예의 변형예에 따른 화소의 등가 회로도이다. 도 10에서, 도 1에 도시된 것과 유사한 구성요소는 동일한 도면부호로 나타내고, 상세한 설명은 반복하지 않는다.

[0090] 예시적인 제1 실시예의 변형예에 따르면, p형 채널의 증폭 트랜지스터(100)가 MOS 트랜지스터이다. p형 채널 증폭 트랜지스터(100)의 드레인이 그라운드(GND) 전압을 공급하는 노드에 접속된다. p형 채널 증폭 트랜지스터(100)의 소스가, 선택 트랜지스터(7)를 거쳐서 수직 출력선(11)에 접속된다. 수직 출력선(11)에는 정전류원(12)이 접속된다. p형 채널 증폭 트랜지스터(100)와 정전류원(12)에 의해 소스 팔로워 회로가 구성된다.

[0091] 이러한 구성에 따르면, FD(4)의 전압이 상승되면 수직 출력선(11)의 전압이 상승되므로, 정전류원(12)의 양단의 전압이 저하된다. 따라서, 정전류원(12)에 포함된 트랜지스터가 선형 영역에서 보다 용이하게 동작할 수 있다. 정전류원(12)의 트랜지스터가 선형 영역에서 동작하면, 수직 출력선(11)을 흐르는 전류값이 변화되므로, 출력 신호의 선형성이 악화한다.

[0092] 또한, 신호 전하가 홀(hall)에 의해 이동되는 경우에, 증폭 트랜지스터로서 p형 채널의 트랜지스터가 사용되면, 예시적인 제1 실시예와 동일한 효과가 얻어진다.

[0093] 도 5는 본 발명의 예시적인 제2 실시예에 따른 화소의 등가 회로를 도시한다. 예시적인 제1 실시예의 구성요소와 유사한 구성요소는 동일한 도면부호로 나타내고, 상세한 설명은 반복하지 않는다.

[0094] 본 실시예에 따르면, PD(2) 및 PD(31)가 전송 트랜지스터(3) 및 전송 트랜지스터(32)를 거쳐서 1개의 FD(4)에 접속된다. 2개의 화소가 1개의 FD(4) 및 1개의 증폭 트랜지스터(5)를 공유하고 있다. 상술된 구성에 따르면, 2개의 화소의 신호 전하를 가산해서 판독할 수 있다. 또한, 각각의 PD에 축적된 신호 전하를 독립적으로 판독할 수 있다. 또한, 1개의 FD(4)가 도 5에 도시되어 있지만, 1개의 반도체 영역이 각각의 화소에 대해 형성되고, 반도체 영역들이 전기적으로 접속되어서 FD(4)의 하나의 노드를 형성하고 있는 경우도 FD(4)의 공유

로서 고려된다.

[0095] 커패시터(33)는 전송 트랜지스터(3)의 게이트와 FD(4) 사이에 형성된 결합 커패시턴스이다. 커패시터(34)는 전송 트랜지스터(32)의 게이트와 FD(4) 사이에 형성된 결합 커패시턴스이다. 도 5에 도시되지는 않았지만, 본 실시예에 따라 제어선(9)과 FD(4) 사이에 결합 커패시턴스가 형성될 수도 있다.

[0096] 본 실시예에 따르면, 전하를 전송하고 있지 않는 전송 트랜지스터의 게이트에 접속되는 제어선에 공급되는 전압이 제어될 수 있다. 보다 구체적으로는, 하나의 전송 트랜지스터가 턴 온될 때, 다른 전송 트랜지스터의 게이트에 공급되는 전압을, 증폭 트랜지스터(5)가 신호를 출력할 때 다른 전송 트랜지스터의 게이트에 공급되는 전압보다 높은 전압으로 제어한다.

[0097] 도 6은 본 실시예에 따른 고체 콜상 장치를 구동시키는데 사용되는 구동 펄스를 도시한다. 도 6을 참조하여, PD(2)의 신호 전하를 전송 트랜지스터(3)에 의해 FD(4)에 전송하는 구동을 설명한다. 도 6에서, PRES, PTS, PTN, FD는 도 3에 도시된 것과 유사한 구동 펄스 및 FD를 지칭한다. PTX1은 제어선(8)을 거쳐서 전송 트랜지스터(3)의 게이트에 공급되는 구동 펄스를 지칭하며, PTX2는 제어선(35)을 거쳐서 전송 트랜지스터(32)의 게이트에 공급되는 구동 펄스를 지칭한다. 구동 펄스의 전압이 하이 레벨이 되면, 대응하는 트랜지스터는 턴 온된다. 구동 펄스의 전압이 로우 레벨이 되면, 대응하는 트랜지스터는 턴 오프된다.

[0098] 본 실시예에 따르면, PTX1 및 PTX2의 로우 레벨의 전압으로서, 2개의 다른 전압 VTXL1 및 VTXL2가 설정될 수 있다. VTXL2는 VTXL1보다 높다. 전송 트랜지스터(3, 32)는 VTXL1 및 VTXL2 양자에 의해 턴 오프된다. 즉, 전송 트랜지스터(3)는, PTX1이 VTXH(하이 레벨의 전압)일 때 턴 온되고, PTX1이 VTXL1 또는 VTXL2(로우 레벨의 전압)일 때 턴 오프된다. 전송 트랜지스터(32)는, PTX2가 하이 레벨의 전압인 VTXH일 때 턴 온되고, PTX2가 VTXL1 또는 VTXL2(로우 레벨의 전압)일 때 턴 오프된다.

[0099] 도 6에 있어서, 시간 T201과 시간 T206 사이 및 시간 T211과 시간 T212 사이의 구동은, 예시적인 제1 실시예에 따른 도 3에 도시된 T101과 T106 사이, T111과 T112 사이의 시간에서의 구동과 유사하다.

[0100] 시간 T207에서, PTX2의 전압은 VTXL1로부터 VTXL2로 변화된다. 전송 트랜지스터(32)의 게이트의 전압의 변화에 따라, 커패시터(34)를 거쳐서 FD(4)의 전압이  $\Delta V3$ 만큼 상승된다. PTX2의 전압이 VTXL1로부터 VTXL2로 상승되더라도, 전송 트랜지스터(32)는 턴 온되지 않는다.

[0101] 시간 T208에서, PTX1은 하이 레벨로 변화되고, 전송 트랜지스터(3)는 턴 온된다. 이 시점에서, PD(2)의 신호 전하의 FD(4)로의 전송이 개시된다. 시간 T209에서, PTX1은 로우 레벨로 변화된다. 그 후에, 전송 트랜지스터(3)는 턴 오프되고, 신호 전하의 전송이 종료된다. 신호 전하가 FD(4)에 전송된 후에는, FD(4)에 신호 전하가 전송되었을 때 출력되는 신호인 S 신호가 수직 출력선(11)에 출력된다.

[0102] 시간 T210에서, PTX2의 전압이 VTXL2로부터 VTXL1로 변화되면, FD(4)의 전압은  $\Delta V3$ 만큼 저하된다. 또한, PTX1은, T207과 T208 사이 및 T209와 T210 사이의 시간 동안에 VTXL1 또는 VTXL2일 수 있다.

[0103] 본 실시예에 따르면, 시간 T205 및 T211에는 전송 트랜지스터(32)의 게이트에 VTXL1이 공급되고, 시간 T207과 시간 T210 사이에는 전송 트랜지스터(32)의 게이트에 VTXL2가 공급된다. 시간 T207에서의 FD(4)의 전압은,  $V_{RS} - \Delta V1 + \Delta V3$ 으로 표현된다. 시간 T205 및 T211에서의 FD(4)의 전압은,  $V_{RESH} - V_{th\_res} - \Delta V1$ 로 표현된다.

[0104] 식 (5)에 있어서  $\Delta V2$ 를  $\Delta V3$ 로 치환함으로써 본 실시예에 따른 신호 전하의 완전 전송을 위한 조건을 표현할 수 있다. 본 실시예에 따르면,  $\Delta V1$ 과  $\Delta V3$ 를 적절하게 설정함으로써, 식 (5) 및 식 (6) 양자가 만족될 수 있다. 따라서, 본 실시예에 따르면, 전송할 수 있는 최대 전하량을 증가시키도록 신호 전하의 전송시에 FD(4)의 전압을 상승시킨 경우에도, 센서 출력의 양호한 선형성이 얻어질 수 있다.

[0105] 또한, 전송 트랜지스터의 채널부에 있어서의 암전류(dark current)가 감소될 수 있도록 VTXL1을 네거티브 값으로 설정할 수 있다. 전송 트랜지스터(32)의 게이트의 전압을 일시적으로 VTXL2로 상승시킴으로써, 암전류에 의한 노이즈가 발생할 수 있다. 따라서, 전송 트랜지스터(32)의 게이트의 전압이 VTXL2로 제어되는 동안의 기간을 짧게 유지하는 것이 바람직하다. 또한, 암전류를 감소시키는 관점으로부터,  $VTXL2 > VTXL1$ 의 관계가 만족된다면, VTXL2에 대해 네거티브 값이 설정될 수 있다.

[0106] 또한, 본 실시예에 따르면, 3개 이상의 화소에 의해 FD(4)가 공유될 수 있다. 예를 들면, 4개의 화소로 1개의 FD 및 1개의 증폭 트랜지스터가 공유되는 경우에, 전하 전송 때문에 턴 온되는 전송 트랜지스터 이외의 3개의 전송 트랜지스터의 게이트의 전압을 제어할 수 있다. 단 1개의 전송 트랜지스터가 사용되는 경우에 비해, FD(4)의 전압의 변화량 ( $\Delta V3$ )이 대략 3배로 증가된다. 따라서, 본 실시예의 구성에 따르면, 예시적인 제1 실

시예로부터 얻어지는 효과에 더해서, 전송할 수 있는 전하의 최대량을 더욱 증가시킬 수 있다.

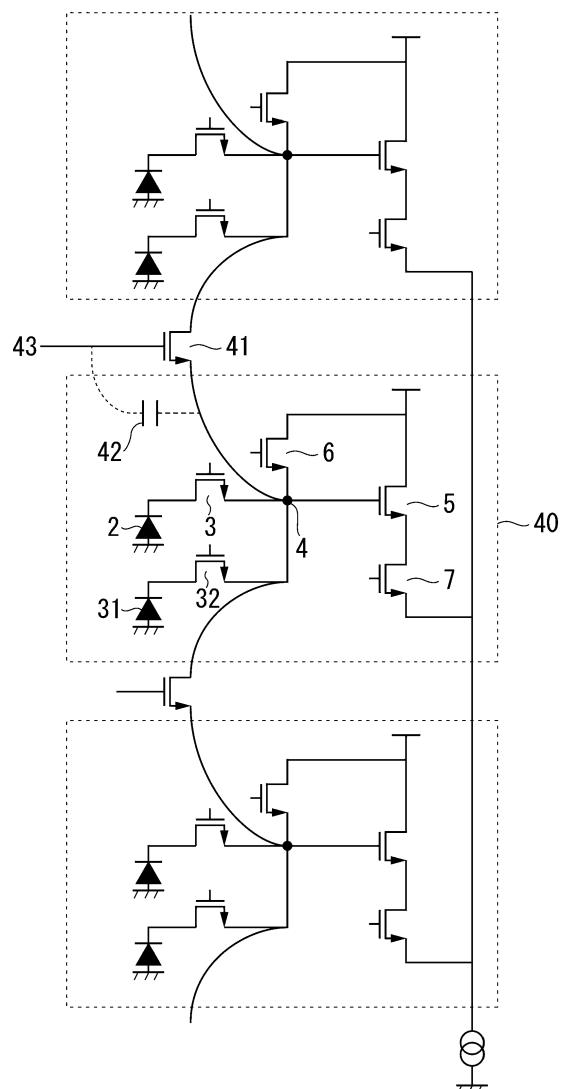

[0107] 도 7은 본 발명의 예시적인 제3 실시예에 따른 화소의 등가 회로를 도시한다. 예시적인 제1 실시예 또는 제2 실시예의 구성요소와 유사한 구성요소는 동일한 도면부호로 나타내고, 상세한 설명은 반복하지 않는다.

[0108] 도 7은 1개의 FD(4)와 1개의 증폭 트랜지스터(5)를 공유한 2개의 화소의 블록(40) 3개를 열방향으로 배치한 구성을 도시한다. 본 실시예에 따르면, 블록의 1개의 FD(4)가 접속 트랜지스터(41)를 거쳐서 인접하는 블록의 다른 FD(4)에 접속된다. 접속 트랜지스터(41)는 인접하는 블록의 FD간의 전기적 접속을 제어한다. 이러한 접속 트랜지스터(41)에 의해, 인접하는 블록의 신호를 가산하는 것이 가능해 진다. 커패시터(42)는 접속 트랜지스터(41)의 게이트와 FD(4) 사이에 형성된 결합 커패시턴스이다. 제어선(43)이 접속 트랜지스터(41)의 게이트에 접속된다. 도면에 도시되지는 않았지만, FD(4)와 각 트랜지스터의 제어선 사이에 결합 커패시턴스가 추가적으로 형성될 수 있다.

[0109] 도 7은 1개의 화소 열에 포함되는 복수의 화소를 도시한다. 실제로는, 도 7에 도시된 1열의 화소의 열이 행방향으로 배치되므로, 화소가 행렬 모양으로 배치된 화소 영역이 형성된다.

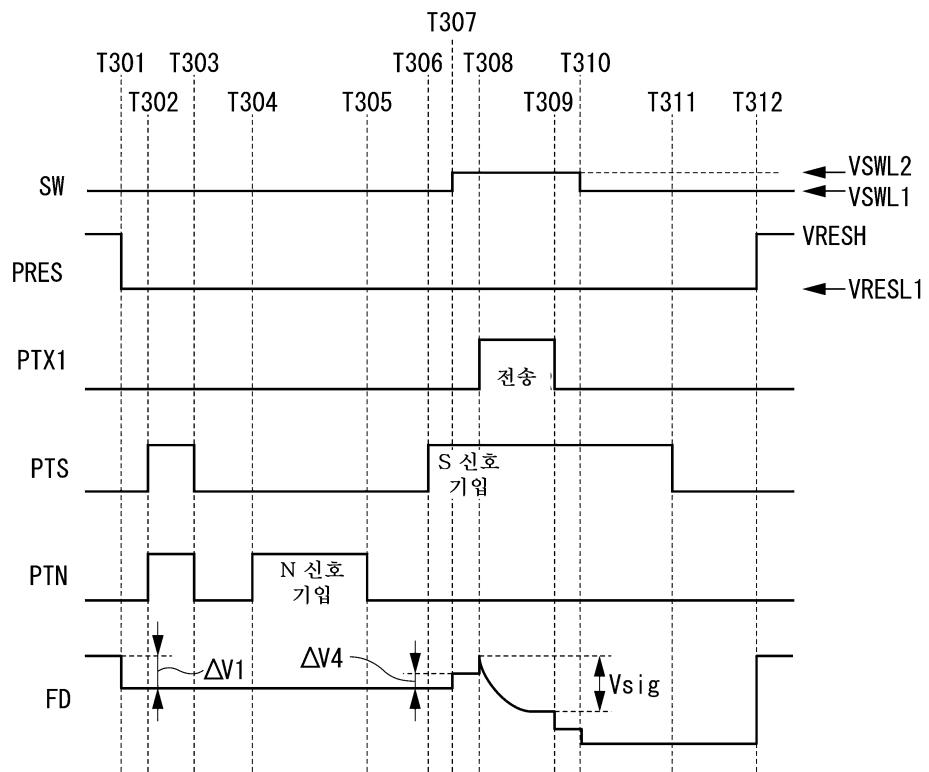

[0110] 도 8은 본 실시예에 따른 고체 측상 장치를 구동시키는데 사용되는 구동 펄스를 도시한다. 도 8을 참조하여 본 실시예의 구동을 설명한다. 하기의 설명에 있어서, 신호의 가산을 행하지 않고 각각의 블록에 신호를 개별적으로 출력할 때의 구동을 설명한다. 즉, 도 8에 도시된 기간 동안, 접속 트랜지스터(41)는 계속 턴 오프되어 있다.

[0111] 도 8에서, PRES, PTX1, PTS, PTN 및 FD는 도 6에 도시된 것과 유사한 구동 펄스 및 FD를 지칭한다. 전송 트랜지스터(32)의 게이트에 공급되는 구동 펄스 PTX2는 도 8에 도시되어 있지 않지만, 도 6에 도시된 구동 펄스 PTX2와 유사한 펄스가 전송 트랜지스터(32)의 게이트에 공급된다. 전송 트랜지스터(32)의 게이트에는, 도 8에서 도시된 기간 동안, 항상 정전압이 공급될 수 있다. SW는 제어선(43)을 거쳐서 접속 트랜지스터(41)의 게이트에 공급되는 구동 펄스를 지칭한다. 구동 펄스의 전압은 하이 레벨이 되고, 대응하는 트랜지스터는 턴 온된다. 구동 펄스의 전압은 로우 레벨이 되며, 대응하는 트랜지스터는 턴 오프된다.

[0112] 본 실시예에 따르면, SW의 로우 레벨의 전압으로서, 2개의 다른 전압 VSWL1 및 VSWL2가 설정될 수 있다. VSWL2는 VSWL1보다 높은 전압을 나타낸다. VSWL1 및 VSWL2 양자는 접속 트랜지스터(41)를 턴 오프시킬 수 있는 전압이다. 즉, 접속 트랜지스터(41)는, SW의 전압이 VSWH(하이 레벨의 전압)일 때 턴 온되고, SW의 전압이 VSWL1 또는 VSWL2(로우 레벨의 전압)일 때에 턴 오프된다.

[0113] 도 8에서, 시간 T301과 시간 T306 사이 및 시간 T311과 시간 T312 사이의 구동은, 예시적인 제1 실시예에 따른 도 3에 도시된 T101과 T106 사이와, T111과 T112 사이의 시간에서의 구동과 유사하다.

[0114] 시간 T307에 있어서, SW의 전압은 VSWL1로부터 VSWL2로 변화된다. 접속 트랜지스터(41)의 게이트의 전압의 변화에 따라, 커패시턴스(42)를 거쳐서 FD(4)의 전압이  $\Delta V4$ 만큼 상승된다. SW의 전압이 VSWL1로부터 VSWL2로 상승되더라도, 접속 트랜지스터(41)는 턴 온되지 않는다.

[0115] 시간 T308에서, PTX1은 하이 레벨로 변화되고, 전송 트랜지스터(3)는 턴 온된다. 이 시점에서, PD(2)의 신호 전하의 FD(4)로의 전송이 개시된다. 시간 T309에서, PTX1은 로우 레벨로 변화된다. 그 후에, 전송 트랜지스터(3)는 턴 오프되고, 신호 전하의 전송이 종료된다.

[0116] 시간 T310에서, SW의 로우 레벨의 전압이 VSWL2로부터 VSWL1로 저하되면, FD 전압은  $\Delta V4$ 만큼 저하된다.

[0117] 본 실시예에 따르면, 시간 T305 및 T311에서는 전송 트랜지스터(32)의 게이트에 VSWL1이 공급되고, 시간 T307과 시간 T310 사이에는 접속 트랜지스터(41)의 게이트에 VSWL2가 공급된다. 시간 T307에서의 FD(4)의 전압은  $V_{rs} - \Delta V1 + \Delta V4$ 로 표현된다. 시간 T305 및 T311에 있어서의 FD(4)의 전압은  $V_{RESH} - V_{th\_res} - \Delta V1$ 로 표현된다.

[0118] 식 (5)에 있어서  $\Delta V2$ 를  $\Delta V4$ 에 치환함으로써 본 실시예에 따른 신호 전하의 완전 전송을 위한 조건이 표현된다. 본 실시예에 따르면,  $\Delta V1$ 과  $\Delta V4$ 를 적절하게 설정함으로써, 식 (5)와 식 (6) 양자가 만족될 수 있다. 따라서, 본 실시예에 따르면, 상술된 실시예와 같이, 전송할 수 있는 최대 전하량을 증가시키도록 신호 전하의 전송시에 FD(4)의 전압을 상승시킨 경우에도, 센서 출력의 양호한 선형성이 얻어질 수 있다.

[0119] 도 8에 도시된 기간 동안 접속 트랜지스터(41)는 계속 턴 오프되어 있고, 블록 간에 신호의 가산이 수행되지 않는 것을 상술하였다. 블록 간에 신호를 가산하기 위해서 접속 트랜지스터(41)가 턴 온된 상태에서, 접속 트랜지스터(41)의 게이트의 전압이 제어될 수 있다.

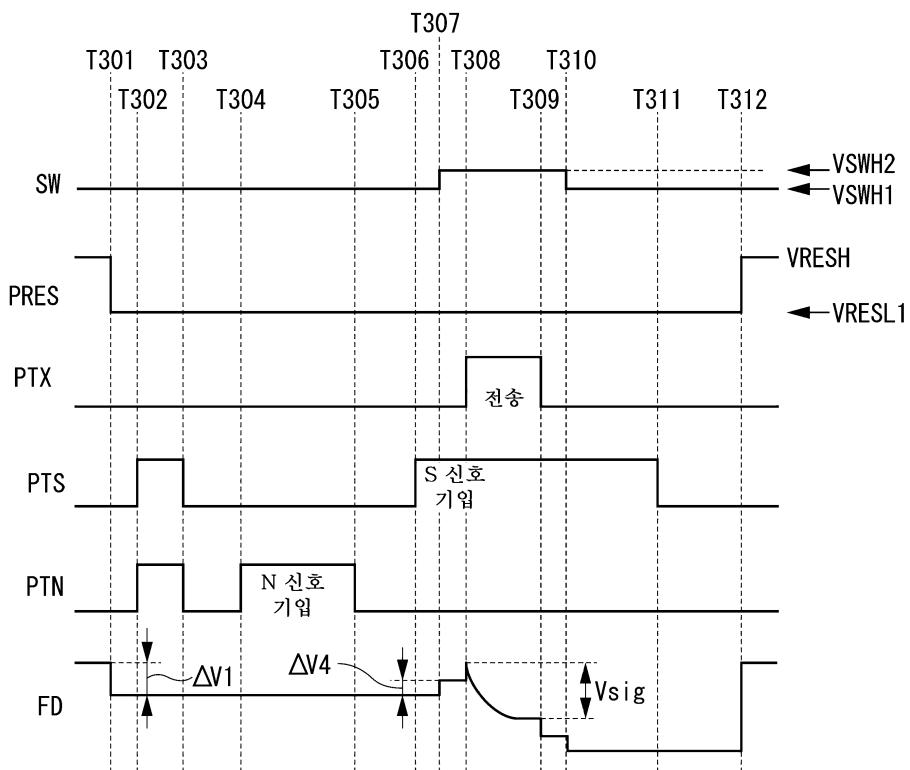

- [0120] 도 9는 본 실시예의 고체 콜상 장치를 구동시키는데 사용되는 다른 구동 펄스를 도시한다. 도 9에 도시된 기간 동안 접속 트랜지스터(41)는 계속 턴 온되어 있다. 도 9에서, PRES, PTS, PTN 및 FD는 도 8에 도시된 것과 유사한 구동 펄스 및 FD를 지칭한다. PTX는 전송 트랜지스터(3, 32) 및 접속 트랜지스터(41)에 접속된 인접 블록의 전송 트랜지스터의 게이트에 공급되는 구동 펄스를 지칭한다. SW는 제어선(43)을 거쳐서 접속 트랜지스터(41)의 게이트에 공급되는 구동 펄스를 지칭한다. 구동 펄스의 전압이 하이 레벨이 되면, 대응하는 트랜지스터는 턴 온된다. 구동 펄스의 전압이 로우 레벨이 되면, 대응하는 트랜지스터는 턴 오프된다.

- [0121] SW의 하이 레벨의 전압으로서, 2개의 다른 전압 VSWH1 및 VSWH2가 설정된다. VSWH2는 VSWH1보다 높다. VSWH1 및 VSWH2 양자는 접속 트랜지스터(41)를 턴 온시키는 전압이다.

- [0122] 접속 트랜지스터(41)가 턴 온인 것을 제외하고, 도 9에 도시된 구동 펄스에 의한 구동은, 도 8에 도시된 구동 펄스에 의한 구동과 유사하다. 전하 전송시(T308 내지 T309)에는, 접속 트랜지스터(41)의 게이트에 VSWH2가 공급된다. S 신호 및 N 신호가 출력될 때에는, 접속 트랜지스터(41)의 게이트에 VSWH1이 공급된다. 따라서, 도 8에 도시된 경우와 유사한 효과가 얻어진다.

- [0123] 본 발명의 예시적인 실시예가 상술되었지만, 실시예의 구성은 발명의 범위 내에 있는 한 변경 및 조합될 수 있다. 예를 들면, 전압을 제어하는 노드는, 증폭 트랜지스터의 드레인에 접속된 노드일 수 있다. 증폭 트랜지스터의 드레인과 게이트는, 게이트 커패시터를 거쳐서 결합되어 있으므로, 드레인의 전압을 제어함으로써, FD의 전압을 변화시킬 수 있다.

- [0124] 예시적인 제1 실시예 내지 제3 실시예에 따르면, 화소에 포함되는 트랜지스터가 n형 채널 MOS 트랜지스터이지만, 임의의 트랜지스터가 p형 채널 MOS일 수 있다. 예를 들면, 다른 트랜지스터가 n형 채널 트랜지스터인 경우에, 리셋 트랜지스터(6)는 p형 채널 MOS일 수 있다.

- [0125] 또한, 예시적인 제1 실시예 내지 제3 실시예에 따르면, 신호 전하가 전자이며, n형 채널 트랜지스터가 증폭 트랜지스터로서 사용된다. 그러나, 신호 전하가 홀일 수 있으며, p형 채널 트랜지스터가 증폭 트랜지스터로서 사용될 수 있다. 이 경우에는, 인가되는 전압의 극성이 역전된다.

- [0126] 또한, 예시적인 제1 실시예 및 제2 실시예에 따르면, VRESL2 및 VTXL2는 각각의 트랜지스터를 턴 오프시키는 전압이다. 그러나, VRESL2 및 VTXL2는, 인가되는 기간이 충분히 짧으면, 각각의 트랜지스터를 턴 온시키는 전압일 수 있다. 유사하게, VRESL2 및 VTXL2는 서브 역치 영역의 전압일 수 있다. 또한, VRESL2, VTXL2, VSWL2 및 VSWH2는 전송 트랜지스터가 턴 온되는 기간 동안 간헐적으로 공급될 수 있다.

- [0127] 본 발명이 예시적인 실시예를 참조하여 기술되었지만, 본 발명은 개시된 예시적인 실시예에 한정되지 않는다는 것이 이해되어야 한다. 하기의 특허청구범위의 범위는 모든 변형, 동등한 구성 및 기능을 포함하도록 가장 넓게 해석되어야 한다.

도면

도면1

도면2

도면3

도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10