(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6107933号

(P6107933)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

(51) Int.Cl.

G06F 3/00 (2006.01)

G06F 13/42 (2006.01)

F 1

G06F 3/00 A

G06F 3/00 X

G06F 13/42 350C

請求項の数 10 (全 25 頁)

(21) 出願番号 特願2015-507905 (P2015-507905)

(86) (22) 出願日 平成25年3月29日 (2013.3.29)

(86) 国際出願番号 PCT/JP2013/059700

(87) 国際公開番号 WO2014/155721

(87) 国際公開日 平成26年10月2日 (2014.10.2)

審査請求日 平成27年9月2日 (2015.9.2)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100092978

弁理士 真田 有

(74) 代理人 100112678

弁理士 山本 雅久

(72) 発明者 植栗 博幹

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 田上 隆一

最終頁に続く

(54) 【発明の名称】接続制御装置、情報処理装置、及び接続制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

バスに対するデバイスの接続制御を行なう接続制御装置であつて、

前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルの組み合わせに基づき前記バスのバスサイクルの開始タイミングを検出した場合、前記複数の信号線の各々から入力される信号の電圧レベルがそれぞれ所定の閾値未満であることを検出する検出部と、

前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記検出部により前記信号の電圧レベルが前記所定の閾値未満であることが検出された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、

をそなえたことを特徴とする、接続制御装置。

## 【請求項 2】

前記検出部は、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であることの検出を行なうことを特徴とする、請求項1記載の接続制御装置。

## 【請求項 3】

所定期間の計時を行なうタイマー部をさらにそなえ、

前記検出部は、前記複数の信号線の各々から入力される信号の電圧レベルが、前記タイ

マ一部による前記所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、請求項2記載の接続制御装置。

**【請求項4】**

前記バスは、2線式シリアルバスであり、

前記検出部は、前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であることの検出を行なうことを特徴とする、請求項2又は請求項3記載の接続制御装置。

10

**【請求項5】**

バスに含まれる複数の信号線の各々から入力される信号の電圧レベルの組み合わせに基づき前記バスのバスサイクルの開始タイミングを検出した場合、前記複数の信号線の各々から入力される信号の電圧レベルがそれぞれ所定の閾値未満であることを検出する検出部と、

前記バスと前記バスに接続するデバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部と、

前記切替部に対して、前記信号の電圧レベルが前記所定の閾値未満であることが検出された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、をそなえることを特徴とする、情報処理装置。

20

**【請求項6】**

前記バスは、2線式シリアルバスであり、

前記検出部は、

前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であることの検出を行ない、

前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であることの検出を行なうことを特徴とする、請求項5記載の情報処理装置。

30

**【請求項7】**

バスに対するデバイスの接続制御を行なう接続制御装置における接続制御方法であつて、

前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルの組み合わせに基づき前記バスのバスサイクルの開始タイミングを検出した場合、前記複数の信号線の各々から入力される信号の電圧レベルがそれぞれ所定の閾値未満であることを検出し、

前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記信号の電圧レベルが前記所定の閾値未満であることが検出された信号線を前記デバイスに接続せるように切替制御を行なう、ことを特徴とする、接続制御方法。

40

**【請求項8】**

前記バスは、2線式シリアルバスであり、

前記検出する処理において、

前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であることの検出を行ない、

前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であることの検出を行なうことを特徴とする、請求項7記載の接続制御方法。

50

**【請求項 9】**

バスに対するデバイスの接続制御を行なう接続制御装置であって、

前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルが所定の閾値未満であるか否かを判定する判定部と、

前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記判定部により前記信号の電圧レベルが前記所定の閾値未満であると判定された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、

をそなえ、

前記判定部は、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であるか否かの判定を行ない、 10

所定期間の計時を行なうタイマー部をさらにそなえ、

前記判定部は、前記複数の信号線の各々から入力される信号の電圧レベルが、前記タイマー部による前記所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、接続制御装置。

**【請求項 10】**

バスに含まれる複数の信号線の各々から入力される信号の電圧レベルが所定の閾値未満であるか否かを判定する判定部と、 20

前記バスと前記バスに接続するデバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部と、

前記切替部に対して、前記信号の電圧レベルが前記所定の閾値未満であると判定された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、

をそなえ、

前記判定部は、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であるか否かの判定を行ない、

所定期間の計時を行なうタイマー部をさらにそなえ、

前記判定部は、前記複数の信号線の各々から入力される信号の電圧レベルが、前記タイマー部による前記所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、情報処理装置。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、接続制御装置、情報処理装置、及び接続制御方法に関する。

**【背景技術】****【0002】**

サーバやパーソナルコンピュータ等の情報処理装置では、I2C（登録商標）バスに類する2線式シリアルバスが用いられることがある。2線式シリアルバスは、例えば比較的低速な周辺機器等のデバイスを接続するために用いられる。

2線式シリアルバスへデバイスを有するユニットを活線挿入する場合、ユニット内部の信号線のコンデンサ成分（浮遊容量）により、ごく短い時間（例えば数nS）ではあるが、バス線からユニットの端子側に電流が流れるという現象が発生することがある。

**【0003】**

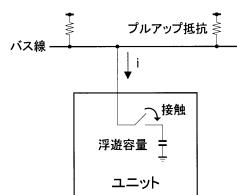

図14は、バス線へユニットを活線挿入したときのユニット内部の浮遊容量によるバス線への影響を説明する図である。図14に示すように、ユニットは、内部回路に依存した浮遊容量を有する。バス線は、プルアップ抵抗により所定の電圧レベルに維持されるが、バス線にユニットが活線挿入されると、バス線からユニットの浮遊容量に対するチャージ 40

10

20

30

40

50

電流  $i$  が流れる。このとき、バス線からユニットへの電流  $i$  の流出により瞬間にバス線の電圧レベルが低下するため、2線式シリアルバスに接続された他のデバイスが誤動作する可能性がある。

#### 【0004】

2線式シリアルバスへのユニットの追加による他のデバイスの誤動作を防ぐため、例えば以下の手法が知られている。

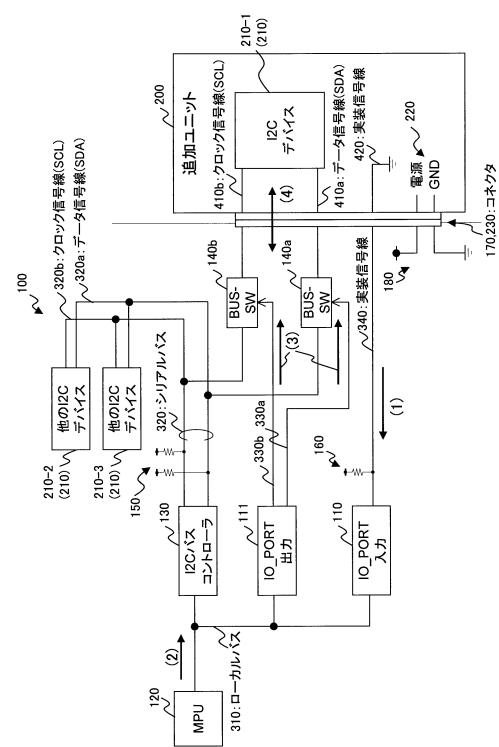

図15及び図16は、I<sub>2</sub>Cバスを有する情報処理装置100及び100の構成例を示す図である。

はじめに、図15に示す例を説明する。図15に示すように、情報処理装置100は、MPU (Micro Processing Unit) 120、I<sub>2</sub>Cバスコントローラ130、IO\_PORT入力110、IO\_PORT出力111、並びに、バススイッチ140a及び140bを備える。また、情報処理装置100は、プルアップ抵抗150及び160、コネクタ170、電源供給部180、並びに、I<sub>2</sub>Cデバイス210-2及び210-3を備える。さらに、追加ユニット200は、I<sub>2</sub>Cデバイス210-1、電源部220、及び、コネクタ230を備える。

10

#### 【0005】

MPU120は、I<sub>2</sub>Cデバイス210-1～210-3（以下、I<sub>2</sub>Cデバイス210-1～210-3を区別しない場合には、単にI<sub>2</sub>Cデバイス210という）の監視及び制御を行なうプロセッサである。MPU120は、ローカルバス310を介してIO\_PORT入力110、IO\_PORT出力111、及び、I<sub>2</sub>Cバスコントローラ130に接続される。

20

#### 【0006】

IO\_PORT入力110は、情報処理装置100に追加ユニット200が実装されたことを検出する。ここで、IO\_PORT入力110は、プルアップ抵抗160により所定の電圧レベルに維持された実装信号線340を介して、コネクタ170に接続される。また、追加ユニット200のコネクタ230には、GND接続（接地）された実装信号線420が接続される。コネクタ170がコネクタ230に接続されると、実装信号線340が実装信号線420を介してGND接続する。このため、IO\_PORT入力110は、実装信号線340の電圧が低下した場合に、情報処理装置100に追加ユニット200が実装されたことを検出する。

30

#### 【0007】

I<sub>2</sub>Cバスコントローラ130は、プルアップ抵抗150により所定の電圧レベルに維持されたシリアルバス（I<sub>2</sub>Cバス）320を介してI<sub>2</sub>Cデバイス210と接続され、I<sub>2</sub>Cデバイス210との間でデータ信号及びクロック信号の通信制御を行なう。

BUS-SW（バススイッチ）140a及び140bは、それぞれ、シリアルバス320に含まれるデータ信号線（SDA）320a及びクロック信号線（SCL）320bとコネクタ170との間に介装されるスイッチである。バススイッチ140a及び140bは、対応する信号線とコネクタ170及び230を介して接続された追加ユニット200のI<sub>2</sub>Cデバイス210-1との間の接続を切り替える。なお、バススイッチ140a及び140bは、コネクタ170に追加ユニット200が接続されるときにはいずれもディセーブル状態になり、シリアルバス320とI<sub>2</sub>Cデバイス210-1との間の接続を開放、つまり切り離された状態にする。

40

#### 【0008】

IO\_PORT出力111は、MPU120からの制御に応じて、制御線330a及び330bを介してバススイッチ140a及び140bにおける接続の切り替えを行なう。

なお、電源供給部180は、コネクタ170に追加ユニット200のコネクタ230が接続されると、電源部220に対して電力を供給する。

上述の如く構成された情報処理装置100では、追加ユニット200が実装されると、IO\_PORT110は、実装信号線340の実装信号がHighからLowに変化したことを通じて追加ユニット200の接続を検知する（図15の矢印（1）参照）。

50

**【0009】**

MPU120は、I/O\_PORT入力110を参照して追加ユニット200が接続されたことを認識すると、I2Cバスコントローラ130に対して、シリアルバス320のバスアクセスの動作を一旦停止させる（図15の矢印（2）参照）。

また、MPU120は、シリアルバス320が停止している間に、I/O\_PORT出力111を制御してバススイッチ140a及び140bをイネーブルに切り替える（図15の矢印（3）参照）。これにより、バススイッチ140a及び140bが閉じて、SDA320aと追加ユニット200のSDA410aとが導通するとともに、SCL320bと追加ユニット200のSCL410bとが導通する。

**【0010】**

バススイッチ140a及び140bがイネーブルに切り替えられると、I2Cバスコントローラ130は、バスアクセスの動作を再開し、追加ユニット200のI2Cデバイス210-1へのバスアクセスを実施する（図15の矢印（4）参照）。

以上の動作により、MPU120は、シリアルバス320のバスアクセスを一旦停止させて、シリアルバス320へ追加ユニット200を接続させる。これにより、追加ユニット200の信号線のコンデンサ成分（浮遊容量）による、バス線への追加ユニット200の接触時のノイズ（電圧低下）の影響を抑えることができる。つまり、追加ユニット200をコネクタ170に接続した際に発生する電圧低下のノイズは、ディセーブル状態のバススイッチ140a及び140bにより分離されるため、シリアルバス320には影響を及ぼさない。

**【0011】**

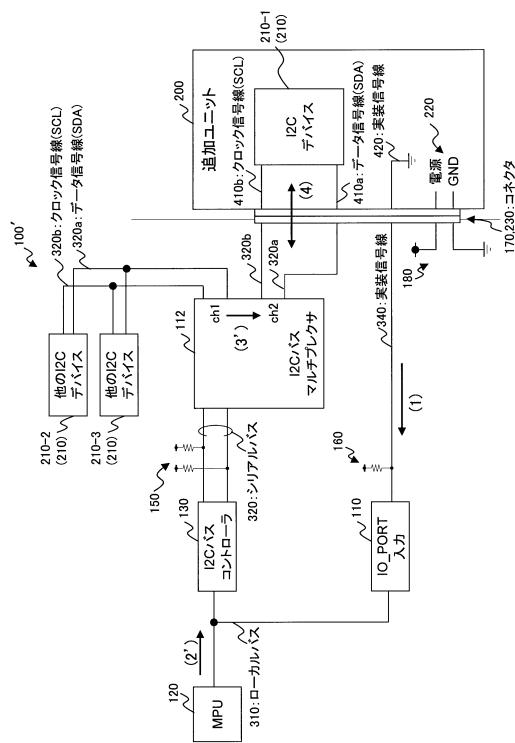

次に、図16に示す例を説明する。図16に示すように、情報処理装置100は、図15に示す情報処理装置100と同様の構成を備えるが、I/O\_PORT出力111、並びに、バススイッチ140a及び140bの代わりに、I2Cバスマルチプレクサ112を備える点が異なる。

I2Cバスマルチプレクサ112は、シリアルバス320とI2Cデバイス210及びコネクタ170との間に介装されるI2Cデバイスである。なお、I2Cバスマルチプレクサ112としては、NXP製PCA9542等が挙げられる。

**【0012】**

I2Cバスマルチプレクサ112は、情報処理装置100内部のI2Cデバイス210-2及び210-3用のチャネル1と、追加ユニット200のI2Cデバイス210-1用のチャネル2との間で、シリアルバス320のチャネル切替を行なう。具体的には、I2Cバスマルチプレクサ112は、バスがビジー状態でないタイミングでチャネル切替を行なう。なお、I2Cバスマルチプレクサ112は、内部にレジスタを備え、I2Cコントローラ130を介してMPU120によりチャネル切替を示す値がレジスタに書き込まれると、バスがビジー状態でないタイミングの検出を開始する。

**【0013】**

上述の如く構成された情報処理装置100では、追加ユニット200が実装されると、I/O\_PORT110は、情報処理装置100と同様に追加ユニット200の接続を検知する（図16の矢印（1）参照）。

MPU120は、追加ユニット200の接続の検出後、追加ユニット200へのアクセスに先立ち、シリアルバス320を介して、I2Cバスマルチプレクサ112の内部レジスタに対してチャネル切替制御を行なう（図16の矢印（2）参照）。

**【0014】**

I2Cバスマルチプレクサ112は、内部レジスタの値に基づき、バスがビジー状態でないタイミングでチャネル1からチャネル2への切り替えを行なう（図16の矢印（3）参照）。

I2Cバスマルチプレクサ112によりチャネルが切り替えられると、I2Cバスコントローラ130は、追加ユニット200のI2Cデバイス210-1へのバスアクセスを実施する（図16の矢印（4）参照）。

10

20

30

40

50

**【0015】**

以上の動作により、I<sub>2</sub>Cバスマルチプレクサ112は、バスがビジー状態でないときに、チャネルを切り替えてシリアルバス320へ追加ユニット200を接続させる。これにより、図15に示す例と同様に、追加ユニット200の信号線のコンデンサ成分（浮遊容量）による、バス線への追加ユニット200の接触時のノイズ（電圧低下）の影響を抑えることができる。つまり、追加ユニット200をコネクタ170に接続した際に発生する電圧低下のノイズは、I<sub>2</sub>Cバスマルチプレクサ112により分離されるため、シリアルバス320には影響を及ぼさない。

**【0016】**

なお、関連する技術として、システムのオンライン稼働中のモジュールの交換手法が知られている（例えば、特許文献1参照）。この技術では、モジュールの挿入／抜去のときに発生するノイズをバスに接続された他のモジュールが受信しても誤動作しないタイミングで、バススイッチがモジュールの接続／切り離しを行なう。10

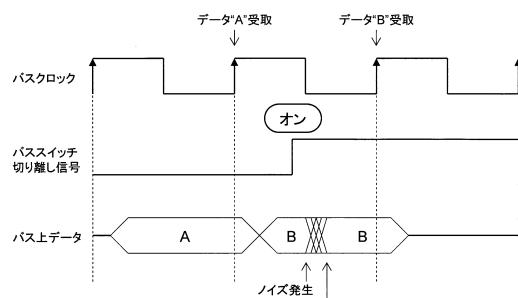

ここで、ノイズを他のモジュールが受信しても誤動作しないタイミングとしては、図17に示す例が挙げられる。図17は、バスへのモジュールの接続又は切り離しのタイミングを説明する図である。例えばパラレルバスでは、他のモジュールは、バスロックの立ち上がりのタイミングでデータを受け取る。換言すれば、他のモジュールは、追加モジュールをバスへ接続した際にノイズが発生したとしても、バスロックに同期してデータを受け取るときにこのノイズが消滅していれば、ノイズの影響を受けずにデータ（図17のデータ“B”）を受け取ることができる。20

**【0017】**

また、関連する他の技術として、バスとユニットとの間に介装されたスイッチにより、バス又はユニットの状態に応じて、バス及びユニットの接続状態を切り替える技術が知られている（例えば、特許文献2及び3参照）。

さらに、コンピュータ本体のバスの電位レベルを制御し、拡張ユニット側のバスと等しい電位レベルにすることで、バスサイクルが実行状態のときに、拡張ユニットとのバス接続を可能とする技術が知られている（例えば、特許文献4参照）。

**【先行技術文献】****【特許文献】****【0018】**

**【特許文献1】**特開平9-44280号公報30

**【特許文献2】**特開2008-197752号公報

**【特許文献3】**特表2004-528627号公報

**【特許文献4】**特開平9-237140号公報

**【発明の概要】****【発明が解決しようとする課題】****【0019】**

図15に示す情報処理装置100では、MPU120は、I<sub>2</sub>Cバスコントローラ130に対するソフトウェアによる制御により、I<sub>2</sub>Cバス320の動作を停止させる。本来、I<sub>2</sub>Cバス320のような共有バスは、常にデバイスへアクセスできる状態であることが望ましいが、情報処理装置100においては、共有バスへの追加ユニット200の接続の際に、他のデバイス210に対して継続アクセスができなくなる。40

**【0020】**

また、図16に示す情報処理装置100では、I<sub>2</sub>Cバスマルチプレクサ112が備えられることでI<sub>2</sub>Cバス320が分岐しバス構成が複雑になる。MPU120は、複雑なバス構成へ追加ユニット200を追加するために、I<sub>2</sub>Cバスマルチプレクサ112に対してソフトウェアによるチャネル切替制御を行なう。従って、情報処理装置100では、図15に示す情報処理装置100と同様の問題に加え、MPU120によるチャネル切替制御において処理の遅延が発生するという問題もある。

**【0021】**

10

20

30

40

50

さらに、図17を参照して説明した技術は、パラレルバスに適用されるものである。仮に、当該技術をI2C(シリアル)バスに適用したとしても、追加するモジュールの接続に伴いクロック信号にノイズが発生した場合には、他のモジュールは誤ってデータを取りこんでしまう可能性がある。

なお、上述した、バス又はユニットの状態に応じてスイッチによりバス及びユニットの接続状態を切り替える技術では、ユニットを接続する際に発生するノイズの影響を抑えることについては考慮されていない。

#### 【0022】

また、コンピュータ本体のバスの電位レベルを制御し、拡張ユニット側のバスと等しい電位レベルにする技術では、ソフトウェアによる複雑な制御が行なわれるため、拡張ユニットの接続処理の遅延が発生するという問題がある。10

以上のように、上述した技術では、デバイスの接続の際にバスは種々の影響を受ける。

1つの側面では、本発明は、デバイスの接続の際にバスが受ける影響を低減させることを目的とする。

#### 【0023】

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の1つとして位置付けることができる。

#### 【課題を解決するための手段】

#### 【0024】

本件の接続制御装置は、バスに対するデバイスの接続制御を行なう接続制御装置であって、前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルの組み合わせに基づき前記バスのバスサイクルの開始タイミングを検出した場合、前記複数の信号線の各々から入力される信号の電圧レベルがそれぞれ所定の閾値未満であることを検出する検出部と、前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記検出部により前記信号の電圧レベルが前記所定の閾値未満であることが検出された信号線を前記デバイスに接続せるように切替制御を行なう切替制御部と、をそなえる。

#### 【発明の効果】

#### 【0025】

第1又は第2実施形態によれば、デバイスの接続の際にバスが受ける影響を低減させることができる。30

#### 【図面の簡単な説明】

#### 【0026】

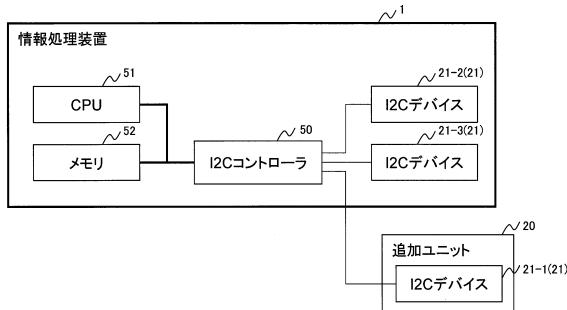

【図1】第1実施形態に係る情報処理装置の構成例を示す図である。

【図2】図1に示すI2Cコントローラの構成例を示す図である。

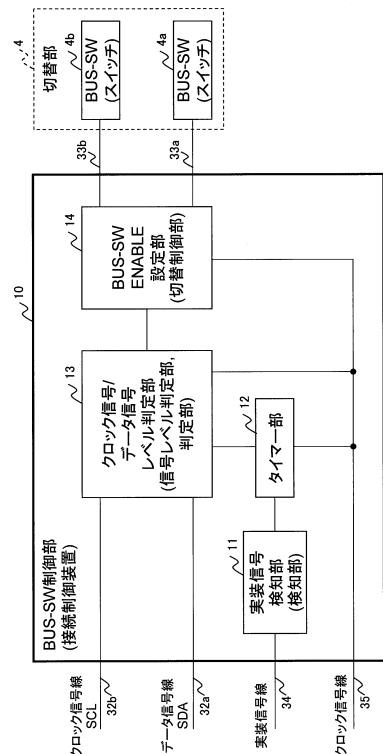

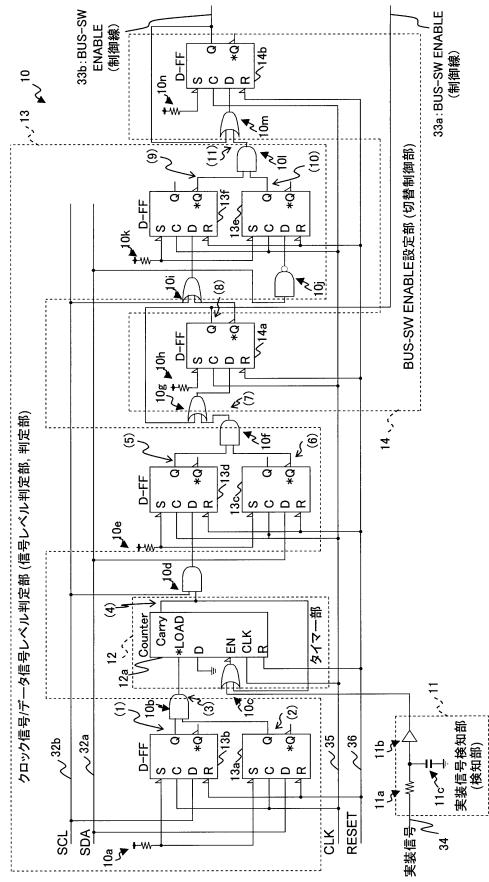

【図3】図2に示すBUS-SW制御部の構成例を示す図である。

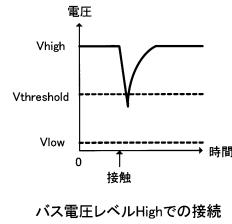

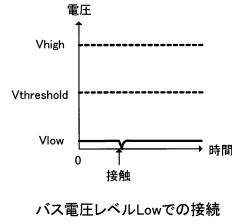

【図4】図2に示すシリアルバスへ追加ユニットを活線挿入したときのシリアルバスの電圧レベルを説明する図である。

【図5】図2に示すシリアルバスへ追加ユニットを活線挿入したときのシリアルバスの電圧レベルを説明する図である。40

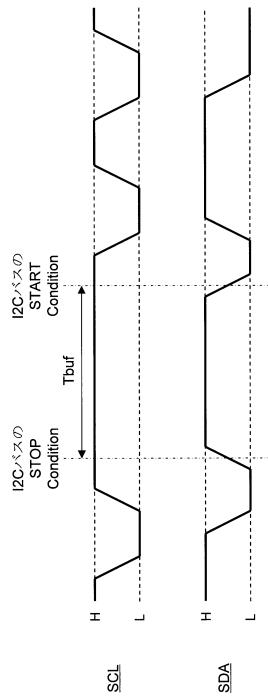

【図6】図2に示すシリアルバスの通信状態の遷移を説明する図である。

【図7】図2に示すBUS-SW制御部の詳細な構成例を示す図である。

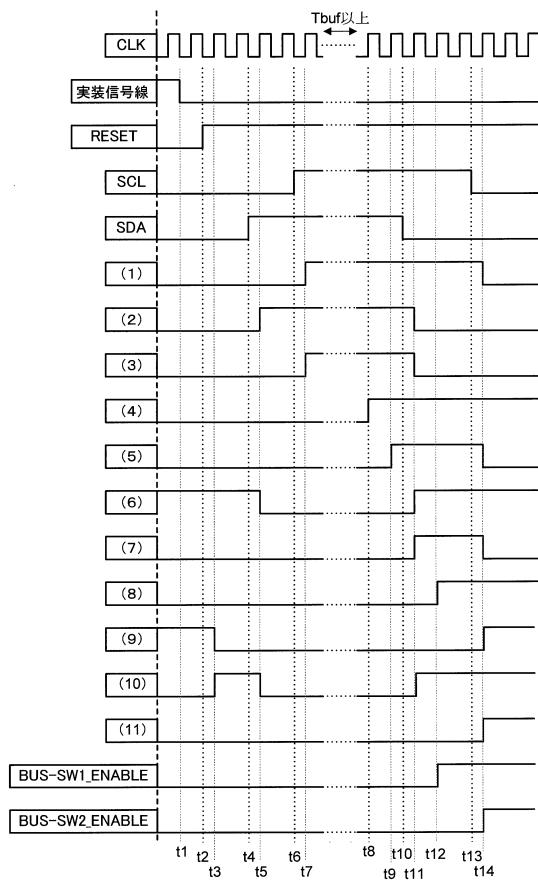

【図8】図7に示すBUS-SW制御部における各部の状態の一例を示すタイムチャートである。

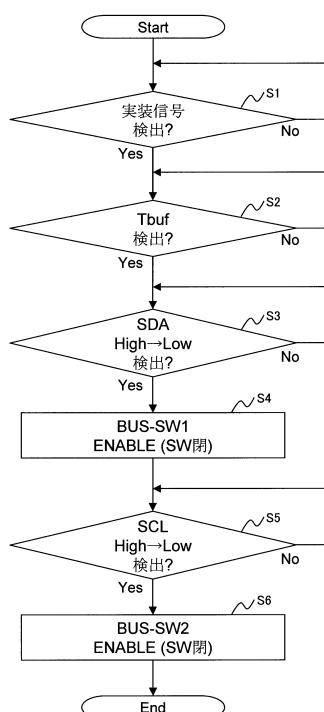

【図9】図1に示すI2Cコントローラの動作例を説明するフローチャートである。

【図10】図1に示すI2Cコントローラの動作例を説明する図である。

【図11】図2に示すシリアルバス、実装信号線、及びBUS-SW ENABLEの状態の一例を示すタイムチャートである。

【図12】第2実施形態に係る情報処理装置の構成例を示す図である。50

【図13】図12に示すI2Cコントローラの構成例を示す図である。

【図14】バス線へユニットを接続したときのユニット内部の浮遊容量によるバス線への影響を説明する図である。

【図15】I2Cバスを有する情報処理装置の構成例を示す図である。

【図16】I2Cバスを有する情報処理装置の構成例を示す図である。

【図17】バスへのモジュールの接続又は切り離しのタイミングを説明する図である。

【発明を実施するための形態】

【0027】

以下、図面を参照して実施の形態を説明する。

〔1〕第1実施形態

10

〔1-1〕情報処理装置の説明

図1は、第1実施形態に係る情報処理装置1の構成例を示す図である。図1に示すように、情報処理装置1は、I2Cコントローラ50、Central Processing Unit(CPU)51、メモリ52、並びに、I2Cデバイス21-2及び21-3を備える。

【0028】

CPU(プロセッサ)51は、種々の制御や演算を行なう処理装置である。CPU51は、メモリ52又は図示しないRead Only Memory(ROM)等に格納されたプログラムを実行することにより、種々の機能を実現する。なお、CPU51は、メモリ52及びI2Cコントローラ50とそれぞれシステムバスを介して接続される。

メモリ52は、種々のデータやプログラムを一時的に格納する記憶装置であって、CPU51がプログラムを実行する際に、データやプログラムを一時的に格納・展開して用いる。なお、メモリ52としては、例えばRandom Access Memory(RAM)等の揮発性メモリが挙げられる。

【0029】

I2Cコントローラ50は、2線式のシリアルバスの一例であるI2Cバスを介して、I2Cデバイス21-2及び21-3に対する各種制御を行なう装置である。また、第1実施形態に係るI2Cコントローラ50は、I2Cデバイス21-1を備える追加ユニット(I2Cユニット)20をI2Cバスに接続させるために、後述する各種制御を行なう。例えば、I2Cコントローラ50は、I2Cデバイス21を含む情報処理装置1の監視を行なう監視装置であってもよい。

30

【0030】

I2Cデバイス21-1～21-3(I2Cデバイス21-1～21-3を区別しない場合には、単にI2Cデバイス21という)は、情報処理装置1に対して接続が可能なデバイスである。例えば、I2Cデバイス21としては、Hard Disk Drive(HDD)又はSolid State Drive(SSD)等の記憶装置のほか、ファン、センサ、電源等の制御装置、又は、監視装置等、I2Cに準拠した種々のデバイスが挙げられる。

40

【0031】

〔1-2〕I2Cコントローラの説明

次に、図2を参照してI2Cコントローラ50の構成を説明する。

図2は、図1に示すI2Cコントローラ50の構成例を示す図である。

40

図2に示すように、I2Cコントローラ50は、BUS-SW(バススイッチ)制御部10、MPU2、I2Cバスコントローラ3、バススイッチ4a及び4b、プルアップ抵抗5及び6、コネクタ7、電源供給部8、並びに、クロック発振器9を備える。

【0032】

また、追加ユニット20は、図15又は図16に示す追加ユニット200と同様の構成であり、I2Cデバイス21-1、電源部22、及び、コネクタ23を備える。

MPU2は、図示しないROM等に格納されたファームウェアを実行することにより種々の制御を実行するプロセッサである。例えば、MPU2は、ローカルバス31を介してI2Cバスコントローラ3に接続され、I2Cデバイス21-1～21-3の監視及び制御を行なう。

50

**【0033】**

I<sub>2</sub>Cバスコントローラ3は、プルアップ抵抗5により所定の電圧レベルに維持されたシリアルバス(バス)32を介してI<sub>2</sub>Cデバイス21と接続され、MPU2からの制御を受けてI<sub>2</sub>Cデバイス21との間でデータ信号及びクロック信号の通信制御を行なう。

つまり、図2に示すように、シリアルバス32に含まれるデータ信号線(SDA)32a及びクロック信号線(SCL)32bは、それぞれプルアップ抵抗5に接続され、プルアップ抵抗5により各信号線の電圧が調整される。例えば、SDA32a及びSCl32bの各々は、I<sub>2</sub>Cバスコントローラ3により印加された電圧レベルがV<sub>high</sub>(High)又はV<sub>low</sub>(Low)で示す所定のレベルを維持するように、プルアップ抵抗5によって調整される(図4及び図5参照)。

10

**【0034】**

なお、図2において図示を省略しているが、MPU2及びI<sub>2</sub>Cバスコントローラ3の少なくとも一方は、システムバスを介して図1に示すCPU51に接続され、CPU51からの要求に応じて、上記制御を行なうのである。

BUS-SW(バススイッチ、スイッチ)4a及び4bは、それぞれ、SDA32a及びSCl32bとコネクタ7との間に介装されるスイッチである。バススイッチ14a及び14bは、対応する信号線について個別に、コネクタ7及び23を介して接続された追加ユニット20(I<sub>2</sub>Cデバイス21-1)との間の接続及び切り離しの切り替えを行う。なお、バススイッチ4a及び4bは、コネクタ7に追加ユニット20が接続されるときにはいずれもディセーブル状態になり、シリアルバス32とI<sub>2</sub>Cデバイス21-1との間の接続を開放、つまり切り離された状態にする。

20

**【0035】**

従って、バススイッチ4a及び4bは、シリアルバス32とI<sub>2</sub>Cデバイス21-1との間に介装され複数の信号線(SDA32a及びSCl32b)の各々とI<sub>2</sub>Cデバイス21との間の接続の切り替えを行なう切替部4の一例である。なお、ここでは、切替部4がバススイッチ4a及び4bである例を説明したが、これに限定されるものではなく、複数の信号線とI<sub>2</sub>Cデバイス21との間の接続の切り替えを個別に行なうことができれば、切替部4が一のスイッチ素子により実現されてもよい。

**【0036】**

コネクタ7は、追加ユニット20のコネクタ23と嵌合等によって接触することにより、I<sub>2</sub>Cコントローラ50と追加ユニット20とを接続する。具体的には、コネクタ7は、I<sub>2</sub>Cコントローラ50側のSDA32a、SCl32b、実装信号線34、電源供給部8と、追加ユニット20側のSDA41a、SCl41b、実装信号線42、電源部22と、をそれぞれ接触(導通)させる。

30

**【0037】**

実装信号線34は、バススイッチ制御部10とコネクタ7とを接続する信号線であり、プルアップ抵抗6により所定の電圧レベルに維持される。一方、追加ユニット20のコネクタ23には、GND接続(接地)された実装信号線42が接続されている。

電源供給部8は、コネクタ7に追加ユニット20のコネクタ23が接続されると、電源部22に対して電力を供給する。

40

**【0038】**

クロック発振器9は、バススイッチ制御部10においてサンプリングを行なうために用いられるクロック信号を生成するものである。なお、クロック発振器9が生成するクロック信号は、SDA32aにおけるクロック信号よりも十分に早い(例えば十倍程度の)周波数である。なお、クロック発振器9としては、LC回路を用いた発振器や水晶発振器等が挙げられる。

**【0039】**

バススイッチ制御部(接続制御装置)10は、シリアルバス32に対するI<sub>2</sub>Cデバイス21の接続制御を行なう装置である。バススイッチ制御部10は、図2に示すように、シリアルバス32から分岐したSDA32a及びSCl32b、実装信号線34、並びに

50

、クロック発振器 9 からのクロック信号線 35 が接続され、各信号線からの信号を入力信号とする。また、バススイッチ制御部 10 は、図 2 に示すように、バススイッチ 4a 及び 4b の各々と BUS-SW ENABLE (バススイッチイネーブル；以下、制御線という) 33a 及び 33b を介して接続され、バススイッチ 4a 及び 4b を制御する。

#### 【0040】

以下、図 3 ~ 図 6 を参照してバススイッチ制御部 10 の構成を説明する。図 3 は、図 2 に示すバススイッチ制御部 10 の構成例を示す図であり、図 4 及び図 5 は、それぞれ、図 2 に示すシリアルバス 32 へ追加ユニット 20 を活線挿入したときのシリアルバス 32 の電圧レベルを説明する図である。図 6 は、図 2 に示すシリアルバス 32 の通信状態の遷移を説明する図である。

10

#### 【0041】

図 3 に示すように、バススイッチ制御部 10 は、実装信号検知部 11、タイマー部 12、クロック信号 / データ信号レベル判定部 13、BUS-SW ENABLE (バススイッチイネーブル) 設定部 14 を備える。

実装信号検知部 (検知部) 11 は、実装信号線 34 からの実装信号を入力され、I2C ユニット 20 (I2C デバイス 21) がコネクタ 7 (バススイッチ 4a 及び 4b) に接続されたことを検知する。例えば、コネクタ 7 がコネクタ 23 に接続されると、実装信号線 34 は、実装信号線 42 を介して GND 接続する。実装信号検知部 11 は、実装信号線 42 の電圧が低下したことを検知すると、I2C デバイス 21 がバススイッチ 4a 及び 4b に接続されたことを検知する。

20

#### 【0042】

タイマー部 12 は、所定期間の計時を行なうものである。タイマー部 12 としては、例えばカウンター回路のほか、計時が可能な種々の回路を用いることができる。

バススイッチイネーブル設定部 (切替制御部) 14 は、切替部 4 に対して、後述する信号レベル判定部 13 により信号の強度 (電圧レベル) が所定の閾値未満であると判定された信号線を I2C デバイス 21 に接続させるように切替制御を行なう。具体的には、バススイッチイネーブル設定部 14 は、信号レベル判定部 13 により検出された SDA32a 又は SCL32b に対応するバススイッチ 4a 又は 4b に対して、切り離し状態から接続状態に切り替えさせる制御を行なう。

#### 【0043】

30

例えば、バススイッチイネーブル設定部 14 は、追加ユニット 20 が I2C コントローラ 50 に接続されたときは、制御線 33a 及び 33b の電圧レベルを Low (ディセーブル) にすることで、バススイッチ 4a 及び 4b を開放し、切り離し状態にする。一方、バススイッチイネーブル設定部 14 は、信号レベル判定部 13 からの指示に応じて、制御線 33a 又は 33b の電圧レベルを High (イネーブル) にすることで、バススイッチ 4a 又は 4b を閉じ、接続状態にする。

#### 【0044】

クロック信号 / データ信号レベル判定部 (信号レベル判定部、判定部) 13 は、追加ユニット 20 をシリアルバス 32 へ接触させる際に発生する、追加ユニット 20 内の信号線のコンデンサ成分によるノイズの大きさが最小限となるタイミングを検出する。

40

具体的には、信号レベル判定部 13 は、実装信号検知部 11 により I2C デバイス 21 がバススイッチ 4a 及び 4b に接続されたことが検知されると、SDA32a 及び SCL32b の各々から入力される信号の電圧レベルを監視する。そして、信号レベル判定部 13 は、SDA32a 及び SCL32b の各々から入力される信号の電圧レベルが所定の閾値 (Vthreshold) 未満であるか否かを判定する。より具体的に、信号レベル判定部 13 は、クロック発振器 9 から入力されるクロック信号を用いて、SDA32a 及び SCL32b から入力される信号をそれぞれサンプリングする。そして、信号レベル判定部 13 は、サンプリング結果から、各信号の電圧レベルが High 及び Low のいずれの状態であるかを判別する。

#### 【0045】

50

以下、図4及び図5を参照して、シリアルバス32へ追加ユニット20を接続するタイミングと、シリアルバス32の電圧レベルとの関係を説明する。

図4に示すように、シリアルバス32のうちのSDA32a又はSCL32bの信号の電圧レベルがHighである場合、図4中“接触”のタイミングでシリアルバス32に追加ユニット20が接続されると、浮遊容量による電圧低下の振れが大きい。図4に示す例では、SDA32a又はSCL32bの電圧レベルは、閾値(Vthreshold)の近傍にまで下降しているため、システムバス32に接続された他のI2Cデバイス21が誤動作する可能性がある。

#### 【0046】

これに対し、図5に示すように、SDA32a又はSCL32bの信号の電圧レベルがLowである場合、もともと電圧レベルがLowの状態であるため、浮遊容量に起因する電圧低下が発生しても他のI2Cデバイス21で誤動作は生じない。つまり、バス線の電圧レベルがLowの状態のときに、システムバス32に追加ユニット20を接続することで、追加ユニット20のコンデンサ成分によるノイズの影響を抑えることができる。10

#### 【0047】

そこで、信号レベル判定部13は、上述のようにバス線の電圧レベルがLowになったタイミングを判定し、Lowになったバス線(SDA32a又はSCL32b)について、バススイッチイネーブル設定部14に切替制御を指示する。

ここで、シリアルバス32の一例としてのI2Cバスは、図6に示すように、通信の過程で、バスアクセスとバスアクセスとの合間であるバスフリータイム(Bus free time between STOP and START conditions; 以下、Tbufという)の状態に遷移する。Tbufは、STOPコンディションとSTARTコンディションとの間の時間であり、この間、シリアルバス32に接続されたI2Cデバイス21-2及び21-3は、シリアルバス32を使用しない。20

#### 【0048】

I2CバスのSTARTコンディションは、図6に示すように、SCL32bがHighの状態のときに、SDA32aがHighの状態からLowに落ちるときの状態であり、I2Cバスにおけるバスアクセスの開始を表す。一方、I2CバスのSTOPコンディションは、図6に示すように、SCL32bがHighの状態のときに、SDA32aがLowの状態からHighに上がるときの状態であり、I2Cバスにおけるバスアクセスの終了を表す。30

#### 【0049】

図6に示すように、SDA32a及びSCL32bは、STARTコンディションにおいて、順にHighの状態からLowに落ちる。

そこで、信号レベル判定部13は、Tbufを検出し、その後のSTARTコンディションを検出することで、SDA32a及びSCL32bの電圧レベルについて、HighからLowへの切り替わりを、順に検出することができる。そして、信号レベル判定部13は、Lowへの切り替わりを検出したSDA32a及びSCL32bについて、個別にバススイッチ4a及び4b(バススイッチイネーブル設定部14)に対して切替制御を行なうことができる。40

#### 【0050】

すなわち、信号レベル判定部13は、SDA32a及びSCL32bの各々から入力される信号の電圧レベルが、タイマーパート12による所定期間の計時時間、いずれも所定の閾値(Vthreshold)以上である場合に、Tbufの期間であると判定する。ここで、Tbufは、I2Cバス固有の期間であり、SCL32bのクロック信号におけるHighの期間よりも長い。従って、タイマーパート12には、計時する期間として、予めTbufと同一或いは略同一、又はTbuf以上の期間が設定されることが好ましい。

#### 【0051】

##### 〔1-3〕バススイッチ制御部の詳細な構成例

次に、図7及び図8を参照して、バススイッチ制御部10の詳細な構成例を説明する。

50

図7は、図2に示すバススイッチ制御部10の詳細な構成例を示す図であり、図8は、図7に示すバススイッチ制御部10における各部の状態の一例を示すタイムチャートである。図7に示すように、バススイッチ制御部10は、例えば複数の回路素子を用いて、ハードウェアにより実現される。

#### 【0052】

実装信号検知部11は、実装信号線34に接続される抵抗11a、増幅器11b、及びコンデンサ11cを備える。

タイマー部12は、カウンター回路12a及びOR回路10cを備える。

信号レベル判定部13は、プルアップ抵抗10a、10e、及び10k、AND回路10b、10f、及び10l、OR回路10i、NAND回路10j、並びにDelay-Flip-Flop(ディレイフリップフロップ；D-FF)13a～13fを備える。

10

#### 【0053】

バススイッチイネーブル設定部14は、プルアップ抵抗10h及び10n、OR回路10g及び10m、並びにD-FF14a及び14bを備える。

なお、図7において、“RESET”は、例えばMPU2から送信されるリセット信号線36であり、実装信号線34がLowに落ちると、Highに維持される。

以下、クロック発振器9からのクロック信号線35、実装信号検知部11からの実装信号線34、リセット信号線36、SCL32b、SDA32a、図7に示す(1)～(11)の各部、並びに制御線33a及び33bの状態の一例を、図8を参照して説明する。

なお、図8においては、制御線33aを“BUS-SW1\_ENABLE”と表記し、制御線33bを“BUS-SW2\_ENABLE”と表記する。

20

#### 【0054】

なお、クロック発振器9からのクロック信号線35は、サンプリング用のクロック信号を出力し、バススイッチ制御部10内の各回路素子は、クロック信号に同期して動作を行なう。

タイミングt1において、実装信号線34がLow、つまり追加ユニット20がシステムバス32に接続されると、リセット信号線36がHighに維持される(タイミングt2)。また、タイミングt3において、D-FF13eの出力(9)がHighからLowに遷移するとともに、D-FF13fの出力(10)がLowからHighに遷移する。

30

#### 【0055】

タイミングt4において、SDA32aの電圧レベルがLowからHighに遷移すると、D-FF13aの出力(2)がHighになるとともに、D-FF13c及び13eの出力(6)及び(10)がそれぞれLowになる(タイミングt5)。なお、D-FF13a、13c、及び13eは、それぞれSDA32aの電圧レベルを監視するD-FFである。

#### 【0056】

次いで、タイミングt6において、SCL32bの電圧レベルがLowからHighに遷移すると、D-FF13bの出力(1)がHighになる(タイミングt7)。また、タイミングt7において、D-FF13a及び13bの出力のANDをとるAND回路10bの出力(3)がHighになる(タイミングt7)。なお、D-FF13b、13d、及び13fは、それぞれSCL32bの電圧レベルを監視するD-FFである。

40

#### 【0057】

なお、タイミングt6において、SDA32aの電圧レベルがHighの状態で、SCL32bの電圧レベルがHighに遷移したため(STOPコンディション)、システムバス32はバスフリータイムの状態になっている。

カウンター回路12aでは、AND回路10bの出力(3)がHighになったことで、“\*LOAD”端子にHighが入力される。そして、カウンター回路12aは、タイミングt7において、Tbufの期間のカウントを開始する。

#### 【0058】

カウンター回路 12 a による所定期間の計時が終了し、AND 回路 10 b の出力(3)が High である時間が Tbuf 以上であった場合には、カウンター回路 12 a の出力(4)が High に遷移する(タイミング t8)。また、出力(4)が High になったことにより、カウンター回路 12 a の後段の D-FF 13 d の出力(5)が High に遷移する(タイミング t9)。

#### 【0059】

ここで、タイミング t10において、SDA 32 a の電圧レベルが High から Low に遷移すると、つまり START コンディションになると、D-FF 13 a 及び AND 回路 10 b の出力(2)及び(3)が Low になる(タイミング t11)。また、タイミング t11において、D-FF 13 c 及び 13 e の出力(6)及び(10)が High になるとともに、D-FF 13 c 及び 13 d の AND をとる AND 回路 10 f の出力(7)が High になる。10

#### 【0060】

また、AND 回路 10 f の出力(7)が High になったことで、D-FF 14 a の出力(8)が High になり、制御線 33 a の電圧レベルが High になる(タイミング t12)。すなわち、バススイッチイネーブル設定部 14 によりバススイッチ 4 a が接続状態に切替制御され、I2C デバイス 21-1 の SDA 42 a がシリアルバス 32 の SDA 32 a に接続される。

#### 【0061】

次いで、タイミング t13において、SCL 32 b の電圧レベルが High から Low に遷移すると、D-FF 13 b 及び 13 d の出力(1)及び(5)が Low に遷移する(タイミング t14)。また、タイミング t14において、D-FF 13 c 及び 13 d の AND をとる AND 回路 10 f の出力(7)が Low になる。さらに、タイミング t14において、D-FF 13 f の出力(9)が High に遷移するとともに、D-FF 13 e 及び 13 f の AND をとる AND 回路 10 l の出力(11)が High になる。20

#### 【0062】

また、AND 回路 10 l の出力(11)が High になったことで、D-FF 14 b の出力が High になり、制御線 33 b の電圧レベルが High になる(タイミング t14)。すなわち、バススイッチイネーブル設定部 14 によりバススイッチ 4 b が接続状態に切替制御され、I2C デバイス 21-1 の SCL 41 b がシリアルバス 32 の SCL 32 b に接続される。30

#### 【0063】

以上のように、第 1 実施形態に係るバススイッチ制御部 10 によれば、信号レベル判定部 13 及びバススイッチイネーブル設定部 14 が論理回路により実現される。従って、I2C バスの動作の中で、追加ユニット 20 をシリアルバス 32 に接続する機会をハードウェアによって高速に検出し接続を行なうため、図 15 を参照して説明したソフトウェアによる制御と比べ、I2C バスコントローラ 3 の動作を停止しなくてよい。さらに、図 16 を参照して説明した I2C バスマルチプレクサ 112 のように、バス分岐がなくなるため、バス構成が複雑になることを抑止できる。また、ハードウェアによる制御は、MPU 2 の性能や負荷に依存するソフトウェアによる制御と比べて、安定した動作を実現することができる。40

#### 【0064】

なお、図 17 を参照して説明したパラレルバスに関する技術を I2C バスに適用した場合、I2C バスにはバス制御信号がないため、I2C デバイス 21 は、発生したノイズが原因で START コンディション又は STOP コンディションと誤認識する可能性がある。これに対し、第 1 実施形態に係るバススイッチ制御部 10 によれば、バス線の電圧レベルが Low の状態のときに、システムバス 32 に追加ユニット 20 を接続するため、I2C デバイス 21 は、発生するノイズが原因でシリアルバス 32 の状態を誤認識することができない。

#### 【0065】

10

20

30

40

50

なお、図7では、信号レベル判定部13及びバススイッチイネーブル設定部14の双方が論理回路により実現される例を示したが、これに限定されるものではない。例えば、信号レベル判定部13及びバススイッチイネーブル設定部14のうちの少なくとも一方が論理回路をそなえる構成としてもよい。この場合でも、信号レベル判定部13及びバススイッチイネーブル設定部14の双方がソフトウェアによる制御により実現される場合と比べて、安定した動作を実現することができる。

#### 【0066】

##### [1-4] 第1実施形態の動作例

次に、上述の如く構成された第1実施形態に係るI2Cコントローラ50における、シリアルバス32への追加ユニット20(I2Cデバイス21-1)の接続制御の動作例を10、図9～図11を参照して説明する。図9は、図1に示すI2Cコントローラ50の動作例を説明するフローチャートであり、図10は、図1に示すI2Cコントローラ50の動作例を説明する図である。図11は、図2に示すシリアルバス32、実装信号線34、及び制御線33の状態の一例を示すタイムチャートである。なお、図9においては、制御線33aを“BUS-SW1\_ENABLE”と表記し、制御線33bを“BUS-SW2\_ENABLE”と表記する。

#### 【0067】

はじめに、図9に示すように、バススイッチ制御部10により、追加ユニット20がコネクタ7に接続されたことに起因する実装信号が検出されたか否かが判定される(ステップS1)。実装信号が検出されなかったと判定された場合(ステップS1のNoルート)20、実装信号が検出されるまでステップS1の判定が行なわれる。

一方、実装信号が検出されたと判定された場合(ステップS1のYesルート；図10の矢印(1)及び図11のタイミングT1参照)、バススイッチ制御部10により、バスフリータイム(Tbuf)が検出されたか否かが判定される(ステップS2)。つまり、バススイッチ制御部10は、シリアルバス32のSDA32a及びSCL32bの電圧レベルを監視し、両方とも一定時間(Tbuf)High状態であるバスフリータイム(バスアクセスとバスアクセスとの合間)の検出が行なわれる。バススイッチ制御部10により、Tbufが検出されなかったと判定された場合(ステップS2のNoルート)、Tbufが検出されるまでステップS2の判定が行なわれる。

#### 【0068】

一方、Tbufが検出されたと判定された場合(ステップS2のYesルート；図10の(2)及び図11のタイミングT1～T2参照)、バススイッチ制御部10により、SDA32aの電圧レベルがHighからLowに遷移したことが検出されたか否かが判定される(ステップS3)。つまり、バススイッチ制御部10は、バスフリータイムを検出すると、I2CバスのSTARTコンディションの発生を検出する。バススイッチ制御部10により、SDA32aの電圧レベルがHighからLowに遷移したことが検出されなかつたと判定された場合(ステップS3のNoルート)、遷移したことが検出されるまでステップS3の判定が行なわれる。

#### 【0069】

これに対し、ステップS3において、SDA32aの電圧レベルがHighからLowに遷移したことが検出されたと判定された場合(ステップS3のYesルート；図10の矢印(3)及び図11のタイミングT2参照)、ステップS4に移行する。

ステップS4では、バススイッチ制御部10により、制御線33aがイネーブルにされ、バススイッチ4aが閉じられることで、SDA32aとSDA41aとが接続される(図10の矢印(4)及び(5)並びに図11のタイミングT3参照)。つまり、バススイッチ制御部10は、SDA32aがLowに維持されている状態でI2Cデバイス21-1のSDA41aをシリアルバス32に接続する。I2Cデバイス21-1は、SDA32aがLowに落ちた状態でシリアルバス32に接続されるため、追加ユニット20の端子のコンデンサ成分(浮遊容量)によるノイズの影響を抑えて接続することができる。また、これにより、I2Cバスのバスサイクルの途中ではなく、バスサイクルの先頭からI50

I<sub>2</sub>Cデバイス21-1をシリアルバス32に接続することができる。

#### 【0070】

次いで、バススイッチ制御部10により、SCL32bの電圧レベルがHighからLowに遷移したことが検出されたか否かが判定される(ステップS5)。遷移したことが検出されなかったと判定された場合(ステップS5のNoルート)、遷移したことが検出されるまでステップS5の判定が行なわれる。

これに対し、ステップS5において、SCL32bの電圧レベルがHighからLowに遷移したことが検出されたと判定された場合(ステップS5のYesルート;図10の矢印(6)及び図11のタイミングT4参照)、ステップS6に移行する。

#### 【0071】

ステップS6では、バススイッチ制御部10により、制御線33bがイネーブルにされ、バススイッチ4bが閉じられることで、SCL32bとSCL41bとが接続される(図10の矢印(7)及び(8)並びに図11のタイミングT5参照)。つまり、バススイッチ制御部10は、STARTコンディションが発生した後、SCL32bがLowに維持されている状態でI<sub>2</sub>Cデバイス21-1のSCL41bをシリアルバス32に接続する。

#### 【0072】

以上の処理により、I<sub>2</sub>Cコントローラ50における、シリアルバス32への追加ユニット20(I<sub>2</sub>Cデバイス21-1)の接続制御が完了する。

#### [1-5]まとめ

このように、第1実施形態に係るI<sub>2</sub>Cコントローラ50によれば、バススイッチイネーブル設定部14により、切替部4に対して、信号レベル判定部13により信号の強度(電圧レベル)が所定の閾値未満であると判定された信号線をI<sub>2</sub>Cデバイス21-1に接続させるように切替制御が行なわれる。従って、バススイッチ制御部10は、例えばLowに落ちた信号線ごとに個別に、I<sub>2</sub>Cデバイス21-1の対応するSDA41a及びSCL41bと接続することができる。これにより、I<sub>2</sub>Cコントローラ50は、システムバス32を停止させることなく、追加ユニット20の端子のコンデンサ成分によるノイズの影響を抑えることができる。つまり、I<sub>2</sub>Cデバイス21-1の各信号線を、ノイズの大きさが最小限となるタイミングでシリアルバス32に接続することができ、I<sub>2</sub>Cデバイス21の接続の際にシリアルバス32が受ける影響を低減させることができる。

#### 【0073】

また、上記判定は、各信号の強度(電圧レベル)に基づいて、シリアルバス32に接続された他のI<sub>2</sub>Cデバイス21によりシリアルバス32が使用されていない状態が検出された場合に行なわれる。従って、バススイッチ制御部10は、I<sub>2</sub>CバスがSTARTコンディションになったときに、SDA32a及びSCL32bの電圧レベルがそれぞれLowに落ちたことを検出することができる。これにより、I<sub>2</sub>Cコントローラ50は、I<sub>2</sub>Cバスのバスサイクルの途中ではなく先頭から、I<sub>2</sub>Cデバイス21をシステムバス32に接続することができ、バスサイクルの途中から接続されるよりもI<sub>2</sub>Cデバイス21-1の誤作動の発生確率を低減させることができる。

#### 【0074】

さらに、バススイッチ制御部10により、SDA32a及びSCL32bの各々から入力される信号の強度(電圧レベル)が、タイマー部12による所定期間の計時の間、いずれも所定の閾値以上である場合に、他のI<sub>2</sub>Cデバイス21によりシリアルバス32が使用されていない状態であると判定される。従って、バススイッチ制御部10は、バスフリータイムを確実に検出することができる。

#### 【0075】

また、STARTコンディションのあと、SDA32a、SCL32bの順序で電圧レベルがLowに落ちるため、バススイッチ制御部10は、毎回決まった手順で安定してI<sub>2</sub>Cデバイス21をI<sub>2</sub>Cバスへ接続することができる。

さらに、実装信号検知部11により、I<sub>2</sub>Cデバイス21-1が切替部4に接続された

10

20

30

40

50

ことが検知された場合に、バススイッチ制御部 10 によって他の I2C デバイス 21 によりシリアルバス 32 が使用されていない状態の検出が開始される。従って、I2C コントローラ 50 は、コネクタ 7 への追加ユニット 20 の接続に応じて、自律でシリアルバス 32 への I2C デバイス 21-1 の接続を行なうことができ、利便性が高い。

#### 【0076】

また、切替部 4 は、SDA 32a 及び SCL 32b について個別に SDA 41a 及び SCL 41bとの切替制御を行なうバススイッチ 4a 及び 4b を備える。従って、電圧レベルが Low に落ちた信号線から順に、I2C デバイス 21-1 をシリアルバス 32 へ効率的に接続することができる。

#### 〔2〕第2実施形態

10

第1実施形態においては、情報処理装置 1 が二つの I2C デバイス 21-2 及び 21-3 をそなえ、情報処理装置 1 に一つの追加ユニット 20 が接続されるものとして説明したが、これに限定されるものではない。例えば、図 12 に示すように、情報処理装置 1 に複数（例えば三つ）の追加ユニット 20-1 ~ 20-3 が接続されるものとしてもよい。

#### 【0077】

以下、図 12 及び図 13 を参照して、情報処理装置 1 の構成例を説明する。

図 12 は、第2実施形態に係る情報処理装置 1 の構成例を示す図であり、図 13 は、図 12 に示す I2C コントローラ 50 の構成例を示す図である。なお、図 12 及び図 13 において、図 1 及び図 2 に示す符号と同一の符号は、図 1 及び図 2 に示す構成と同一又は略同一のため、重複した説明は省略する。

20

#### 【0078】

図 12 に示すように、第2実施形態に係る情報処理装置 1 は、図 1 に示す I2C コントローラ 50 に代えて、I2C コントローラ 50 を備える。なお、情報処理装置 1 は、I2C デバイス 21 を備えてもよい。

I2C コントローラ 50 は、I2C デバイス 21-1 ~ 21-3 を備える追加ユニット（I2C ユニット）20-1 ~ 20-3 を I2C バスに接続させるために、I2C コントローラ 50 と同様の各種制御を行なう。

#### 【0079】

図 13 に示すように、第2実施形態に係る I2C コントローラ 50 は、追加ユニット 20-1 ~ 20-3 を接続するコネクタ 7 の数と同数のバススイッチ制御部 10、プルアップ抵抗 6、切替部 4、及び電源供給部 8 を備える。一方、I2C コントローラ 50 は、複数のコネクタ 7 に対して共通の MPU 2、I2C バスコントローラ 3、及びクロック発振器 9 を備える。

30

#### 【0080】

第2実施形態に係る I2C コントローラ 50 は、接続される複数の追加ユニット 20-1 ~ 20-3 の各々について、個別に、第1実施形態において説明した各種制御を行なうのである。

これにより、第2実施形態に係る情報処理装置 1（I2C コントローラ 50）によつても、第1実施形態と同様の効果を奏することができる。

#### 【0081】

40

#### 〔3〕その他

以上、本発明の好ましい実施形態について詳述したが、本発明は、係る特定の実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内において、種々の変形、変更して実施することができる。

例えば、上述した第1及び第2実施形態では、実装信号検知部 11 は、実装信号線 34 が GND 接続したことを検出すると、追加ユニット 20 が実装されたことを検知するものとして説明したが、これに限定されるものではない。実装信号検知部 11 による追加ユニット 20 が実装されたことの検知は、既知の種々の手法により行なうことが可能であり、その詳細な説明は省略する。

#### 【0082】

50

また、上述した第1及び第2実施形態では、シリアルバス32は、I2Cバスであるものとして説明したが、これに限定されるものではない。シリアルバス32として、他の2線式シリアルバスが用いられてもよく、また、2線式以外の複数の信号線を含むシリアルバスが用いられてもよい。シリアルバス32がいずれの場合であっても、バススイッチ制御部10は、信号の強度（電圧レベル）が所定の閾値以下になった信号線について、個別に切替部4に対して切替制御を行なわせればよい。なお、バススイッチ制御部10は、バスフリータイムの検出の手法については、他の2線式シリアルバス、又は複数の信号線を含むシリアルバスの規格に従って、適宜修正を加えればよい。

#### 【0083】

さらに、上述した第1及び第2実施形態では、信号レベル判定部13は、Tbufを検出した後に各信号の電圧レベルがLowに切り替わることを検出するものとして説明したが、これに限定されるものではない。例えば、信号レベル判定部13は、バスサイクルの途中でも、電圧レベルがLowになったことを検出した場合には、LowになったSDA32a又はSCL32bについて、バススイッチ4a又は4bの接続制御を行なってもよい。これにより、I2Cコントローラ50は、Tbufの検出を待つよりも、早いタイミングで追加ユニット20（I2Cデバイス21）をシリアルバス32に接続することができる。

#### 【0084】

また、上述した第1及び第2実施形態では、一つ又は三つの追加ユニット20が情報処理装置1又は1'に接続されるものとして説明したが、追加ユニット20の数はこれらに限定されるものではなく、種々増減することができる。

なお、図9に示すステップS1～S6の処理は、シリアルバス32に接続された他のI2Cデバイス21が存在する場合に行なわれればよく、他のI2Cデバイス21が存在しない場合には、少なくともステップS4及びS6の処理（順不同）が行なわれればよい。

#### 〔4〕付記

以上の第1及び第2実施形態に関し、更に以下の付記を開示する。

##### （付記1）

バスに対するデバイスの接続制御を行なう接続制御装置であって、

前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルが所定の閾値未満であるか否かを判定する判定部と、

前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記判定部により前記信号の電圧レベルが前記所定の閾値未満であると判定された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、

をそなえたことを特徴とする、接続制御装置。

##### （付記2）

前記判定部は、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であるか否かの判定を行なうことを行うことを特徴とする、付記1記載の接続制御装置。

##### （付記3）

所定期間の計時を行なうタイマー部をさらにそなえ、

前記判定部は、前記複数の信号線の各々から入力される信号の電圧レベルが、前記タイマー部による前記所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、付記2記載の接続制御装置。

##### （付記4）

前記バスは、2線式シリアルバスであり、

前記判定部は、前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線

10

20

30

40

50

のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であるか否かの判定を行なうことを特徴とする、付記2又は付記3記載の接続制御装置。

(付記5)

前記デバイスが前記切替部に接続されたことを検知する検知部をさらにそなえ、

前記判定部は、前記検知部により前記デバイスが前記切替部に接続されたことが検知された場合に、前記他のデバイスにより前記バスが使用されていない状態の検出を開始することを特徴とする、付記2~4のいずれか1項記載の接続制御装置。

(付記6)

前記切替部は、前記複数の信号線について個別に前記デバイスとの間の接続の切り替えを行なう複数のスイッチをそなえ、

前記切替制御部は、前記判定部により検出された信号線に対応するスイッチに対して、前記切替制御を行なうことを特徴とする、付記1~5のいずれか1項記載の接続制御装置。

(付記7)

前記判定部及び前記切替制御部のうちの少なくとも一方は、一以上の論理回路をそなえることを特徴とする、付記1~6のいずれか1項記載の接続制御装置。

(付記8)

バスに含まれる複数の信号線の各々から入力される信号の電圧レベルが所定の閾値未満であるか否かを判定する判定部と、

前記バスと前記バスに接続するデバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部と、

前記切替部に対して、前記信号の電圧レベルが前記所定の閾値未満であると判定された信号線を前記デバイスに接続させるように切替制御を行なう切替制御部と、

をそなえることを特徴とする、情報処理装置。

(付記9)

前記判定部は、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であるか否かの判定を行なうことを特徴とする、付記8記載の情報処理装置。

(付記10)

所定期間の計時を行なうタイマー部をさらにそなえ、

前記判定部は、前記複数の信号線の各々から入力される信号の電圧レベルが、前記タイマー部による前記所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、付記9記載の情報処理装置。

(付記11)

前記バスは、2線式シリアルバスであり、

前記判定部は、前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であるか否かの判定を行なうことを特徴とする、付記9又は付記10記載の情報処理装置。

(付記12)

前記デバイスが前記切替部に接続されたことを検知する検知部をさらにそなえ、

前記判定部は、前記検知部により前記デバイスが前記切替部に接続されたことが検知された場合に、前記他のデバイスにより前記バスが使用されていない状態の検出を開始することを特徴とする、付記9~11のいずれか1項記載の情報処理装置。

(付記13)

前記切替部は、前記複数の信号線について個別に前記デバイスとの間の接続の切り替え

10

20

30

40

50

を行なう複数のスイッチをそなえ、

前記切替制御部は、前記判定部により検出された信号線に対応するスイッチに対して、前記切替制御を行なうことを行うことを特徴とする、付記 8 ~ 12 のいずれか 1 項記載の情報処理装置。

(付記 14)

前記判定部及び前記切替制御部のうちの少なくとも一方は、一以上の論理回路をそなえることを特徴とする、付記 8 ~ 13 のいずれか 1 項記載の情報処理装置。

(付記 15)

バスに対するデバイスの接続制御を行なう接続制御装置における接続制御方法であって、

10

前記バスに含まれる複数の信号線の各々から入力される信号の電圧レベルが所定の閾値未満であるか否かを判定し、

前記バスと前記デバイスとの間に介装され前記複数の信号線の各々と前記デバイスとの間の接続の切り替えを行なう切替部に対して、前記信号の電圧レベルが前記所定の閾値未満であると判定された信号線を前記デバイスに接続させるように切替制御を行なう、ことを特徴とする、接続制御方法。

(付記 16)

前記判定する処理において、前記各信号の電圧レベルに基づいて、前記バスに接続された他のデバイスにより前記バスが使用されていない状態を検出した場合に、前記信号線ごとに前記信号の電圧レベルが所定の閾値未満であるか否かの判定を行なうことを特徴とする、付記 15 記載の接続制御方法。

20

(付記 17)

前記判定する処理において、前記複数の信号線の各々から入力される信号の電圧レベルが、所定期間の計時の間、いずれも前記所定の閾値以上である場合に、前記他のデバイスにより前記バスが使用されていない状態であると判定することを特徴とする、付記 16 記載の接続制御方法。

(付記 18)

前記バスは、2 線式シリアルバスであり、

前記判定する処理において、前記他のデバイスにより前記バスが使用されていない状態を検出した後、前記他のデバイスによる前記バスの使用開始のタイミングに応じて、前記複数の信号線のうちのデータ信号線及びクロック信号線の順で、各信号線から入力される信号の電圧レベルが前記所定の閾値未満であるか否かの判定を行なうことを特徴とする、付記 16 又は付記 17 記載の接続制御方法。

30

(付記 19)

前記デバイスが前記切替部に接続されたことを検知し、

前記判定する処理において、前記デバイスが前記切替部に接続されたことが検知された場合に、前記他のデバイスにより前記バスが使用されていない状態の検出を開始することを特徴とする、付記 16 ~ 18 のいずれか 1 項記載の接続制御方法。

(付記 20)

前記切替部は、前記複数の信号線について個別に前記デバイスとの間の接続の切り替えを行なう複数のスイッチをそなえ、

40

前記切替制御を行なう処理において、前記判定する処理により検出された信号線に対応するスイッチに対して、前記切替制御を行なうことを特徴とする、付記 15 ~ 19 のいずれか 1 項記載の接続制御方法。

#### 【符号の説明】

##### 【0085】

1 , 1 , 100 , 100 情報処理装置

2 MPU

3 I2C バスコントローラ (バス制御部)

4 切替部

50

4 a , 4 c , 4 e      B U S - S W 1 (バススイッチ, スイッチ)

4 b , 4 d , 4 f      B U S - S W 2 (バススイッチ, スイッチ)

5 , 6 , 1 5 0 , 1 6 0      プルアップ抵抗

7 , 2 3 , 1 7 0 , 2 3 0      コネクタ

8 , 1 8 0      電源供給部

9      クロック発振器

1 0      B U S - S W 制御部 (接続制御回路)

1 0 a , 1 0 e , 1 0 h , 1 0 k , 1 0 n      プルアップ抵抗

1 0 b , 1 0 d , 1 0 f , 1 0 j , 1 0 l      A N D 回路

1 0 c , 1 0 g , 1 0 i , 1 0 m      O R 回路      10

1 0 j      N A N D 回路

1 1      実装信号検知部 (検知部)

1 1 a      抵抗

1 1 b      増幅器

1 1 c      コンデンサ

1 2      タイマー部

1 2 a      カウンター回路

1 3      クロック信号 / データ信号レベル判定部 (信号レベル判定部, 判定部)

1 3 a ~ 1 3 f , 1 4 a , 1 4 b      D - F F

1 4      B U S - S W E N A B L E 設定部 (バススイッチイネーブル設定部, 切替制御部)      20

2 0 , 2 0 - 1 ~ 2 0 - 3 , 2 0 0      追加ユニット

2 1 , 2 1 - 1 ~ 2 1 - 3      I 2 C デバイス (デバイス)

2 2 , 2 2 0      電源部

3 1 , 3 1 0      ローカルバス

3 2 , 3 2 0      シリアルバス

3 2 a , 4 1 a , 4 1 c , 4 1 e , 3 2 0 a , 4 1 0 a      データ信号線 (S D A)

3 2 b , 4 1 b , 4 1 d , 4 1 f , 3 2 0 b , 4 1 0 b      クロック信号線 (S C L)

3 3 a , 3 3 c , 3 3 e , 3 3 0 a      B U S - S W 1 E N A B L E (制御線)

3 3 b , 3 3 d , 3 3 f , 3 3 0 b      B U S - S W 2 E N A B L E (制御線)      30

3 4 , 4 2 , 3 4 0 , 4 2 0      実装信号線

3 5      クロック信号線

3 6      リセット信号線

5 0 , 5 0      I 2 C コントローラ

5 1      C P U

5 2      メモリ

1 1 0      I O \_ P O R T 入力

1 1 1      I O \_ P O R T 出力

1 1 2      I 2 C バスマルチプレクサ

1 2 0      M P U      40

1 3 0      I 2 C バスコントローラ

1 4 0 a      B U S - S W 1 (バススイッチ)

1 4 0 b      B U S - S W 2 (バススイッチ)

2 1 0 , 2 1 0 - 1 ~ 2 1 0 - 3      I 2 C デバイス

3 2 , 3 2 0      シリアルバス

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 4】

【 図 15 】

【図 1 6】

【 図 17 】

---

フロントページの続き

(56)参考文献 特開2007-052543(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 00

G 06 F 13 / 42