(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년08월08일

(11) 등록번호 10-1054676

(24) 등록일자 2011년08월01일

(51) Int. Cl.

H01L 21/302 (2006.01)

(21) 출원번호 10-2006-7007734

(22) 출원일자(국제출원일자) 2004년07월30일

심사청구일자 2009년07월30일

(85) 번역문제출일자 2006년04월21일

(65) 공개번호 10-2006-0101758

(43) 공개일자 2006년09월26일

(86) 국제출원번호 PCT/US2004/024904

(87) 국제공개번호 WO 2005/045914

국제공개일자 2005년05월19일

(30) 우선권주장

10/690,060 2003년10월21일 미국(US)

(56) 선행기술조사문현

US05607773 A

전체 청구항 수 : 총 29 항

심사관 : 배근희

(54) 반도체 제조 공정에서 낮은 k 유전체를 형성하는 방법

### (57) 요 약

낮은 k 유전체 합성층(26, 28)은 낮은 k 장벽층(26) 및 낮은 k 장벽층(26) 상의 낮은 K 유전체 층(28)으로 이루어진다. 소수성 상부 표면을 갖는 결과로 침착된 장벽층(26)은, 상기 표면을 소수성에서 친수성으로 변환하기 위해 산소 플라즈마로 처리된다. 후속의 수계 세정제는, 장벽층(26) 표면의 변환으로 인해 장벽층(26)에 대한 수율 감소 결함들을 제거하는데 매우 효과적이다. 수계 세정제 후에, 낮은 K를 갖는 합성층(26, 28)을 달성하기 위해, 낮은 K 유전체 층(28)이 장벽층(26)의 표면 상에 형성된다.

### 대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

반도체 기판 상에 층을 형성하는 방법에 있어서:

반도체 기판을 제공하는 단계;

상기 기판 위에 놓이는 제 1 유전체 층을 형성하는 단계로서, 상기 제 1 유전체 층은 소수성 표면(hydrophobic surface)을 포함하는, 상기 제 1 유전체 층 형성 단계;

상기 소수성 표면을 친수성 표면(hydrophilic surface)으로 변환하는 단계;

상기 친수성 표면을 스크러빙(scrubbing)하는 단계; 및

상기 제 1 유전체 층 위에 놓이는 제 2 유전체 층을 형성하는 단계를 포함하는, 층 형성 방법.

### 청구항 2

제 1 항에 있어서,

상기 제 1 유전체 층은 규소, 탄소 및 질소를 포함하는, 층 형성 방법.

### 청구항 3

제 1 항에 있어서,

상기 소수성 표면을 상기 친수성 표면으로 변환하는 단계는 산소 플라즈마에 의해 이루어지는, 층 형성 방법.

### 청구항 4

제 1 항에 있어서,

상기 제 2 유전체 층은 규소, 탄소, 산소 및 수소를 포함하는, 층 형성 방법.

### 청구항 5

제 2 항에 있어서,

상기 소수성 표면을 상기 친수성 표면으로 변환하는 단계는 산소 플라즈마에 의해 이루어지는, 층 형성 방법.

### 청구항 6

제 5 항에 있어서,

상기 제 2 유전체 층은 규소, 탄소, 산소 및 수소를 포함하는, 층 형성 방법.

### 청구항 7

제 6 항에 있어서,

상기 친수성 표면을 수계 세정제(a water-based clean)로 스크러빙하는, 층 형성 방법.

### 청구항 8

제 7 항에 있어서,

상기 수계 세정제는 암모늄 하이드로옥사이드(ammonium hydroxide)를 포함하는, 층 형성 방법.

### 청구항 9

제 5 항에 있어서,

상기 제 1 유전체는 규소, 질소 및 탄소를 포함하는, 층 형성 방법.

### 청구항 10

제 9 항에 있어서,

상기 친수성 표면을 수계 세정제로 스크러빙하는, 층 형성 방법.

### 청구항 11

제 10 항에 있어서,

상기 수계 세정제는 암모늄 하이드로옥사이드를 포함하는, 층 형성 방법.

### 청구항 12

제 5 항에 있어서,

상기 제 1 유전체 층을 형성하는 단계 및 상기 소수성 표면을 친수성 표면으로 변환하는 단계는 인시츄(in-situ)로 수행되는, 층 형성 방법.

### 청구항 13

제 1 항에 있어서,

상기 제 1 유전체 층을 형성하는 단계 및 상기 소수성 표면을 친수성 표면으로 변환하는 단계는 인시츄로 수행되는, 층 형성 방법.

### 청구항 14

제 1 항에 있어서,

상기 제 1 유전체를 형성하는 단계는 플라즈마 침착되고, 변환하는 단계는 플라즈마에 의해 이루어지는, 층 형성 방법.

### 청구항 15

반도체 기판 상에 층을 형성하는 방법에 있어서:

반도체 기판을 제공하는 단계;

상기 기판 위에 놓이는 제 1 유전체 층을 형성하는 단계;

상기 제 1 유전체 층을 산소 플라즈마로 처리하는 단계;

상기 제 1 유전체 층을 수계 용액으로 세정하는 단계; 및

상기 세정된 제 1 유전체 층 위에 놓이는 제 2 유전체 층을 형성하는 단계를 포함하는, 층 형성 방법.

### 청구항 16

제 15 항에 있어서,

상기 제 1 유전체 층의 소수성 표면이 친수성 표면으로 변환되도록 상기 제 1 유전체 층을 상기 산소 플라즈마로 처리하는, 층 형성 방법.

### 청구항 17

제 16 항에 있어서,

상기 제 1 유전체 층을 세정하는 단계는 상기 제 1 유전체 층을 상기 수계 용액으로 스크러빙하는 단계를 포함하는, 층 형성 방법.

### 청구항 18

제 17 항에 있어서,

상기 수계 용액은 암모늄 하이드로옥사이드를 포함하는, 층 형성 방법.

### 청구항 19

제 18 항에 있어서,

상기 제 1 유전체 층은 규소, 탄소 및 질소를 포함하는, 층 형성 방법.

### 청구항 20

제 15 항에 있어서,

상기 제 1 유전체 층은 규소, 탄소 및 질소를 포함하는, 층 형성 방법.

### 청구항 21

제 20 항에 있어서,

상기 제 1 유전체 층을 형성하는 단계는 제 1 챔버에서 발생하는, 층 형성 방법.

### 청구항 22

제 21 항에 있어서,

상기 제 1 유전체 층을 상기 산소 플라즈마로 처리하는 단계는 상기 제 1 챔버에서 발생하는, 층 형성 방법.

### 청구항 23

반도체 구조를 형성하는 방법에 있어서:

반도체 기판을 제공하는 단계;

상기 기판 위에 놓이고, 규소, 탄소 및 질소를 포함하는 제 1 유전체 층을 형성하는 단계;

상기 제 1 유전체 층을 산소 플라즈마로 처리하는 단계;

상기 제 1 유전체 층을 스크러빙하는 단계; 및

상기 제 1 유전체 층 위에 놓이는 제 2 유전체 층을 형성하는 단계를 포함하는, 반도체 구조 형성 방법.

### 청구항 24

제 23 항에 있어서,

상기 제 1 유전체 층은 소수성 표면을 갖는, 반도체 구조 형성 방법.

### 청구항 25

제 24 항에 있어서,

상기 제 1 유전체 층을 처리하는 단계는 상기 소수성 표면을 친수성 표면으로 변환하는, 반도체 구조 형성 방법.

### 청구항 26

제 23 항에 있어서,

상기 스크러빙 단계는 수계 세정 용액으로 스크러빙하는 단계를 포함하는, 반도체 구조 형성 방법.

### 청구항 27

제 26 항에 있어서,

상기 수계 세정 용액은 암모늄 하이드로옥사이드를 포함하는, 반도체 구조 형성 방법.

### 청구항 28

제 27 항에 있어서,

상기 스크러빙 단계는 기계적 세정 및 화학적 세정을 포함하는, 반도체 구조 형성 방법.

## 청구항 29

제 23 항에 있어서,

상기 제 1 유전체 층을 형성하는 단계는, 규소, 탄소 및 질소의 상기 제 1 유전체 층을 형성하는 단계를 포함하고,

상기 제 1 유전체 형성 단계 및 상기 제 1 유전체 층 처리 단계는 인시츄로 수행되는, 반도체 구조 형성 방법.

## 명세서

### 기술 분야

[0001]

본 발명은 집적 회로 제조에 관한 것이며, 보다 상세하게는, 집적 회로 제조 시에 낮은  $k$  유전체 막들을 형성하는 것에 관한 것이다.

### 배경 기술

[0002]

반도체들의 제조 시에, 반도체 기판 위의 도전층들 사이의 층인 층간 유전체(Interlayer Dielectric; ILD)에 대해 낮은  $k$  유전체들을 사용하는 것이 개발되었다. 이러한 낮은  $k$  유전체는, 상호 접촉으로서 사용되는 도전체들 사이의 용량성 결합(capacitive coupling)을 감소시킨다. 이러한 용량성 결합을 감소시키는 것은, 속도가 우선 순위인 경우들에서 특히 중요하며, 이러한 경우는 종종 있다. 낮은  $k$  재료들은 통상적으로 최상의 절연체들이 아니며 높은 수율로 제조하기도 쉽지 않다. 성공적인 동작을 위해 필요한 모든 특성들을 성취하기 위해 종종 장벽층들(barrier layers) 및 덮개층들(capping layers)이 요구된다. 이러한 부가적인 층들은, 공정을 복잡하게 하고 잠재적으로 수율 문제들을 일으키는 단계들을 추가한다.

### 발명의 상세한 설명

[0003]

따라서, 수율에 대한 악영향을 적게 하면서 반도체 제조에서 낮은  $k$  유전체에 대한 필요성이 있다.

[0004]

본 발명은 예의 방법으로 예시되며, 첨부한 도면들에 의해 제한되지 않고, 도면들에서 동일한 참조 번호들은 동일한 요소들을 나타낸다.

### 실시 예

[0007]

도면들의 요소들은 간단하고 명료하게 예시되며 일정한 비율로 도시될 필요가 없음을 당업자는 인지한다. 예를 들면, 도면들의 일부 요소들의 크기들은 본 발명의 실시예들의 이해를 돋기 위해 다른 요소들에 비하여 확대될 수 있다.

[0008]

하나의 형태에서, 소수성 표면(hydrophobic surface)으로 침착된 낮은  $k$  장벽층은 소수성이 되도록 표면을 변환하기 위해 산소 플라즈마로 처리된다. 그후 스크러브(scrub)로 소수성 표면이 세정된다. 스크러브는 소수성 표면으로 인해 상당히 증가된 효과를 갖는다. 이것은 도면들 및 다음의 설명을 참조하여 보다 쉽게 이해된다.

[0009]

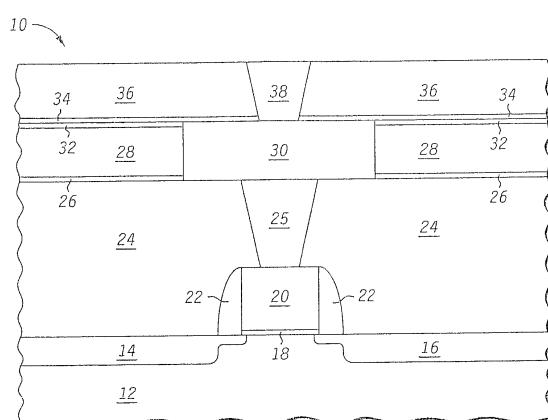

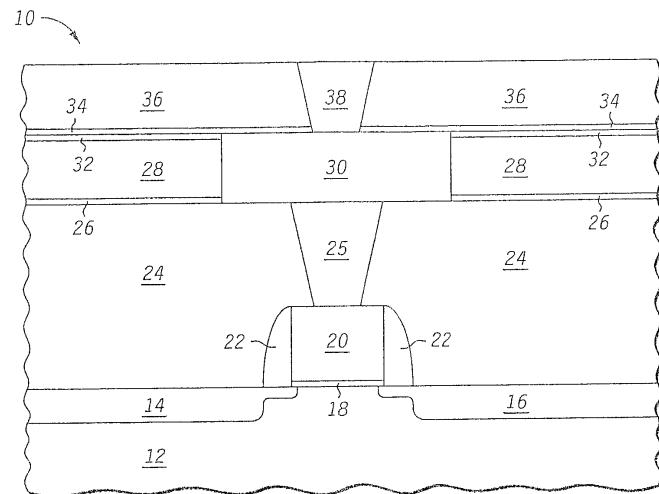

도 1은 반도체 기판(12), 기판(12)에 형성된 드레인 영역(14), 기판(12)에 형성된 소스 영역(16), 기판(12) 상에 있고 실질적으로 드레인(14)과 소스(16) 사이의 게이트 유전체(18), 게이트 유전체(18) 위의 게이트(20), 게이트(20) 주위의 측벽 스페이서(22), 게이트(20) 위와 주위의 유전체 층(24), 게이트(20) 상의 접촉(25), 유전체 층(24) 상의 낮은  $k$  장벽 유전체 층(26), 낮은  $k$  장벽 유전체 층(26) 상의 낮은  $k$  유전체 층(28), 낮은  $k$  유전체 층(28) 상의 덮개층(32), 비아(via)(25)를 통하고 층들(26, 28 및 30)로 둘러싸인 도전층(30), 덮개층(32) 상의 낮은  $k$  장벽층(34), 낮은  $k$  장벽층(34) 상의 낮은  $k$  유전체 층(36), 및 도전층(30) 상에 있고 층들(34, 36)에 둘러싸인 비아(38)를 포함하는 반도체 디바이스(10)를 도시한다. 반도체 기판(12)은, 반도체가 실리콘이나 다른 반도체 재료의 다른 형태의 반도체 기판일 수 있는 SOI 기판이 바람직하다. 게이트(20)는 실리콘이나 바람직하지만, 금속과 같은 다른 재료들 또는 상이한 층들의 합성일 수 있다. 접촉(25)은 텅스텐이 바람직하지만, 다른 형태의 도전성 재료일 수 있다. 비아(38)는 구리가 바람직하지만, 다른 도전성 재료일 수 있다. 도전층(30)은 구리가 바람직하지만, 다른 도전성 재료일 수 있다. 덮개층(32)은 TEOS(tetraethylorthosilicate)를 사용하여 형성된 산화물이 바람직하지만, 다른 유전체 재료들일 수 있다. 유전체(24)는 층들의 합성이며, 상부층은 SiCOH 또는 플루오린 및 TEOS(FTEOS)를 사용하여 형성된 산화물이 바람직하다. CMP 공정은, CMP 프로세

성 후에 층(24)의 표면 상의 재료가 변경될 수 있도록 유전체 층(24)에 적용된다. CMP 프로세싱을 수행하기 전에 층(24) 상의 바람직한 재료 조합은 실리콘 리치 옥사이드(silicon rich oxide), 실리콘 리치 옥시나이트라이드(silicon rich oxynitride), 산화 TEOS이며, 이로 인해 디바이스(10)가 수행되는 웨이퍼에 걸쳐 층(24)의 상부 표면이 동일하지 않게 된다. 반도체 디바이스(10)는, 낮은 k 장벽층(26)과 낮은 K 유전체(28)의 합성층 및 낮은 k 장벽층(34)과 낮은 K 유전체 층(36)의 합성층을 형성하는 방법 이외의 종래 수단에 의해 형성될 수 있는 종래의 구조이다.

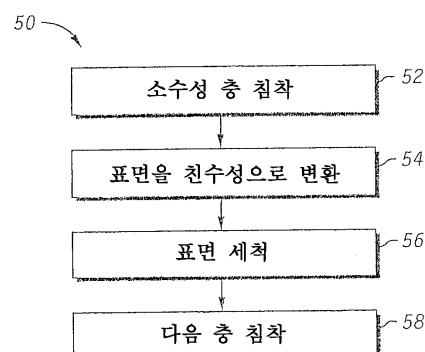

[0010] 이들 합성층들을 형성하는 방법은 도 2의 흐름도에 도시된다. 흐름도(50)는 단계들(52, 54, 56 및 58)을 포함한다. 단계(52)에서, 낮은 k 장벽층들(26, 34)의 고유한 성질인 소수성 표면을 갖는 층이 침착된다. 장벽층들(26 및 34)은 SiCN이 바람직하다. 낮은 K 유전체 층들(28, 36)은 SiCOH가 바람직하다. SiCN은 소수성 표면을 갖는 특성을 갖는다. 또한 SiCN은 그의 표면 상에 입자들을 갖는 것으로 알려져 있다. 스크러브 세정은 입자들 모두를 제거하지는 않는 것으로 알려져 있다. 세정이 완전히 효과적이지 않는다는 하나의 가능한 이유는 침착된 SiCN 층의 표면이 소수성이라는 것이다. 또한, 스크러브 세정은, 새로운 형태의 결합을 생성하여 SiCN 구조를 손상시키는 것으로 알려져 있다. 단계(54)는 SiCN 층의 표면을 소수성에서 친수성으로 변환한다. 이것은 산소 플라즈마에 의해 성취된다. SiCN의 침착 및 SiCN 층의 후속 플라즈마 처리는 인시츄(in situ)로 수행되는 것이 바람직하다. SiCN은 플라즈마 침착이기 때문에, 후속 산소 플라즈마 단계는, 침착 챔버에서 웨이퍼들을 제거하지 않고 쉽게 수행될 수 있다. 따라서, 층(26)이 침착되고, 그후 동일한 챔버에서 처리된다. 동일한 방법으로, 침착 및 도전체(30)의 CMP 프로세싱 후에, 층(34)이 침착되고 동일한 챔버에서 처리된다.

[0011] 단계(56)는 플라즈마 처리된 층의 표면의 스크러브를 수행하는 것이다. 따라서, 층(26)은, 층(26)이 산소 플라즈마로 처리된 후에 스크러브 세정으로 처리된다. 또한, 이것은 층(34)에 대해서도 마찬가지이다. 스크러브 세정은 수계 세정제(a water-based clean)이다. 물은 탈이온화되는 것이 바람직하며, 또한 암모늄 하이드로옥사이드(ammonium hydroxide)를 포함하는 것이 바람직하다. 이것은 스크러빙 세정과 같은 수계 세정제를 위한 통상의 혼합물이다.

[0012] 단계(58)는 다음 층의 침착을 수행하며, 다음 층은 낮은 k 장벽층(26) 상의 유전체 층(28) 및 장벽층(34) 상의 낮은 K 유전체 층(36)이다. 단계들(52-58)의 결합은 낮은 K 유전체로서 유용한 합성층을 완성하기 위해 결합된다.

[0013] 장벽층의 플라즈마 침착이 수율 감소 결합들을 일으킬 수 있는 장벽의 표면 상에 입자들을 생기게 하고, 이들 입자는 스크러브에 의해 효과적으로 제거되지 않는데, 장벽층의 표면이 소수성인가 때문이며, 장벽층 표면의 사후-침착 플라즈마 처리가 장벽층의 표면을 친수성으로 변환하여, 새로운 결합 형태를 후속으로 생성하지 않고 스크러브가 입자들을 제거하는데 효과적이라는 것이 이러한 방법의 이점에 대한 하나의 이론이다. 임의의 경우에, 공정은 수율에서 상당한 개선을 가져온다.

[0014] 명세서에서, 본 발명은 특정 실시예들을 참조하여 설명된다. 그러나, 청구 범위에 설명된 본 발명의 범위를 벗어나지 않고 다양한 수정들 및 변경들이 이루어질 수 있다는 것을 당업자는 이해한다. 예를 들면, 수계 세정제 다음의 플라즈마 처리에 이로운 다른 유전체 및 장벽 재료들이 사용될 수 있다. 다른 물질은 침착되는 소수성일 수 있고 플라즈마 처리에 의해 친수성으로 변환될 수 있다. 플라즈마 처리는 산소 이외에 의한 것일 수 있다. 낮은 K 물질은 SiCN 및 SiCOH 이외의 것일 수 있으며, 플라즈마 대신에 회전될 수 있다. 수계 세정제는 반드시 스크러브 공정일 필요는 없지만, 스크러버(scrubber)를 필요로 하지 않는 수계 용액을 사용하는 것이 간단하다. 따라서, 명세서 및 도면들은 제한적 의미라기 보다는 예시적인 것으로 간주되며, 모든 수정들은 본 발명의 범위 내에 포함되는 것으로 의도된다.

[0015] 이점들, 다른 장점들 및 문제점에 대한 해결책들은 특정 실시예들에 관하여 상술되었다. 그러나, 이점들, 장점들, 문제점들에 대한 해결책들, 및 임의의 이점들, 문제점들에 대한 해결책들이 유발하거나 공표되도록 할 수 있는 임의의 요소(들)는 중대하고, 요구되거나 필수적인 특징 또는 임의의 또는 모든 청구항들의 요소로서 해석되지 않는다. 명세서에 사용된 바와 같이, 용어들 "포함하다", "포함하는" 또는 그의 임의의 다른 변경은 배타적이지 않은 포함을 커버하도록 의도되어, 요소들의 리스트를 포함하는 공정, 방법, 물품 또는 장치가 그러한 요소들만을 포함하지 않고, 열거되지 않거나 그러한 공정, 방법, 물품 또는 장치에 내재된 다른 요소들을 포함할 수 있다.

## 도면의 간단한 설명

[0005] 도 1은 본 발명의 실시예에 따라 제조된 반도체 디바이스 구조의 단면도.

[0006]

도 2는 도 1의 디바이스 제조시에 사용되는 본 발명의 실시예에 따른 공정의 흐름도.

## 도면

### 도면1

### 도면2