(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7534412号**

**(P7534412)**

(45)発行日 令和6年8月14日(2024.8.14)

(24)登録日 令和6年8月5日(2024.8.5)

(51)国際特許分類

|         |                  |     |         |      |         |

|---------|------------------|-----|---------|------|---------|

| G 0 9 F | 9/30 (2006.01)   | F I | G 0 9 F | 9/30 | 3 3 8   |

| G 0 9 F | 9/00 (2006.01)   |     | G 0 9 F | 9/00 | 3 4 6 Z |

| G 0 9 G | 3/20 (2006.01)   |     | G 0 9 G | 3/20 | 6 2 1 M |

| G 1 1 C | 19/28 (2006.01)  |     | G 0 9 G | 3/20 | 6 2 2 B |

| H 0 1 L | 21/8234(2006.01) |     | G 0 9 G | 3/20 | 6 2 2 E |

請求項の数 14 (全55頁) 最終頁に続く

(21)出願番号 特願2022-539718(P2022-539718)

(86)(22)出願日 令和2年6月4日(2020.6.4)

(65)公表番号 特表2023-535853(P2023-535853)

A)

(43)公表日 令和5年8月22日(2023.8.22)

(86)国際出願番号 PCT/CN2020/094316

(87)国際公開番号 WO2021/243638

(87)国際公開日 令和3年12月9日(2021.12.9)

審査請求日 令和5年5月30日(2023.5.30)

(73)特許権者 510280589

京東方科技集團股 ふん 有限公司

BOE TECHNOLOGY GROU

P CO., LTD.

中華人民共和国 100015 北京市朝陽

區酒仙橋路 10 號

No. 10 Jiuxianqiao R

d., Chaoyang Distri

ct, Beijing 100015,

CHINA

(73)特許権者 511121702

成都京東方光電科技有限公司

CHENGDU BOE OPTOELE

CTRONICS TECHNOLOGY

CO., LTD.

最終頁に続く

(54)【発明の名称】 表示基板、その製作方法、及び表示装置

**(57)【特許請求の範囲】****【請求項 1】**

表示基板であって、ベースに設けられている走査駆動回路及び表示領域を含み、前記走査駆動回路は、複数のシフトレジスタユニットを含み、前記複数のシフトレジスタユニットのうち、少なくとも一つのシフトレジスタユニットは、信号出力線及び出力回路を含み、前記出力回路は、出力トランジスタ及び出力リセットトランジスタを含み、前記信号出力線は、第1方向に沿って延在される第1出力線部分を含み、

前記第1出力線部分は、信号線の重なり領域に設けられた複数の第1信号線ピアホールを介して前記出力トランジスタの第2電極に結合され、前記第1出力線部分は、前記信号線の重なり領域に設けられた複数の第2信号線ピアホールを介して前記出力リセットトランジスタの第2電極に結合され、前記複数の第1信号線ピアホールが第1方向に沿って順次に配列され、前記複数の第2信号線ピアホールが第1方向に沿って順次に配列され、

前記信号線の重なり領域は、第1信号線の重なり領域及び第2信号線の重なり領域を含み、前記第1信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力トランジスタの第2電極が含まれる第1ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、前記第2信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力リセットトランジスタの第2電極が含まれる第2ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、

第1方向に沿って順次に配列された複数つの第1信号線ピアホールのうちの1番目の第1信号線ピアホールと最後の一つの第1信号線ピアホールとの第1方向での距離と第3長

さとの割合が第1所定割合であり、前記第3長さが、前記第1信号線の重なり領域の第1方向での長さであり、

第1方向に沿って順次に配列された複数の第2信号線ピアホールのうちの1番目の第2信号線ピアホールと最後の一つの第2信号線ピアホールとの第1方向での距離と第4長さとの割合が第2所定割合であり、前記第4長さが、前記第2信号線の重なり領域の第1方向での長さであり、

前記第1所定割合が0.05以上かつ0.9以下であり、

前記第2所定割合が0.05以上かつ0.9以下であり、

前記出力トランジスタのアクティブ層及び前記出力リセットトランジスタのアクティブ層は、第1方向に沿って配列され、前記出力トランジスタのアクティブ層の前記第1方向での長さを第1長さとして、前記出力リセットトランジスタのアクティブ層の前記第1方向での長さを第2長さとして、前記第1長さと前記第2長さとの和が出力アクティブ長さであり、

前記出力トランジスタのアクティブ層の第2方向に沿う最小の幅と、前記出力リセットトランジスタのアクティブ層の第2方向に沿う最小の幅とのうち、小さいものを出力アクティブ幅とし、前記第1方向と前記第2方向は互いに交差し、

前記出力アクティブ長さと前記出力アクティブ幅との割合が所定割合の範囲内にあり、前記所定割合の範囲が3以上かつ11以下であり、

または、

前記出力アクティブ幅が所定の幅の範囲内にあり、

前記所定の幅の範囲が12μm以上かつ45μm以下である、表示基板。

### 【請求項2】

前記出力トランジスタのアクティブ層及び前記出力リセットトランジスタのアクティブ層が一つの連続した第1半導体層により形成され、前記第1半導体層が第1方向に沿って延在され、

前記第1半導体層の第1方向での長さが出力アクティブ長さであり、

前記第1半導体層の第2方向での最小の長さが前記出力アクティブ長さである、請求項1に記載の表示基板。

### 【請求項3】

前記少なくとも一つのシフトレジスタユニットは、第1トランジスタをさらに含み、

前記第1トランジスタは、第1アクティブパターンを含み、前記第1アクティブパターンが第2方向に沿って延在され、

前記第1トランジスタは、前記出力回路の表示領域から離れた側に位置しており、

または、

前記少なくとも一つのシフトレジスタユニットは、第2トランジスタ及び第3トランジスタをさらに含み、前記第2トランジスタの第2電極が前記第3トランジスタの第2電極に結合され、

前記第2トランジスタのゲート電極の前記ベースでの正投影と、前記第3トランジスタのゲート電極の前記ベースでの正投影との間の第2方向での最大距離が第3所定距離であり、

前記第2トランジスタ及び前記第3トランジスタは、前記出力回路の表示領域から離れた側に位置しており、

前記第3所定距離が14μm以上かつ50μm以下であり、

または、

前記少なくとも一つのシフトレジスタユニットは、第1トランジスタ、第2トランジスタ及び第1コンデンサをさらに含み、

前記第1トランジスタの第2電極及び前記第2トランジスタの第1電極がそれぞれ前記第1コンデンサの第2極板に結合され、前記第1トランジスタのゲート電極が前記第1コンデンサの第1極板に結合され、

前記第1トランジスタ、前記第1コンデンサ及び前記第2トランジスタが第1方向に沿

10

20

30

40

50

つて順次に配列され、

前記第1トランジスタ、前記第1コンデンサ及び前記第2トランジスタが、前記出力回路の表示領域から離れた側に位置しており、

または、

前記走査駆動回路は、第1電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、出力リセットコンデンサをさらに含み、前記出力リセットコンデンサの第1極板が前記出力リセットトランジスタのゲート電極に結合され、前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、

前記出力リセットコンデンサの第2極板の第2方向での最大の幅が第1所定の幅であり、

前記出力リセットコンデンサの第2極板の第1方向での最大の長さが第2所定の長さであります、

10

前記出力リセットコンデンサは前記出力回路の表示領域から離れた側に位置しております、

前記出力リセットコンデンサの第2極板の前記ベースでの正投影が前記出力リセットコンデンサの第1極板の前記ベースでの正投影内にあり、

前記第1所定の幅が $3\text{ }\mu\text{m}$ 以上かつ $60\text{ }\mu\text{m}$ 以下であり、前記第2所定の長さが $3\text{ }\mu\text{m}$ 以上かつ $20\text{ }\mu\text{m}$ 以下であり、

または、

前記第1電圧信号線が第1方向に沿って延在され、前記第1電圧信号線は前記出力リセットコンデンサの表示領域から離れた側に位置している、請求項1に記載の表示基板。

#### 【請求項4】

20

前記出力トランジスタ及び前記出力リセットトランジスタが第1方向に沿って配列され、前記走査駆動回路は、第2電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、出力リセットコンデンサをさらに含み、

前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、

前記出力トランジスタの第1電極が第2電圧信号線に結合され、前記出力リセットトランジスタの第1電極が前記出力リセットコンデンサの第2極板に結合され、

前記出力トランジスタ及び前記出力リセットトランジスタが前記第2電圧信号線の表示領域から離れた側に位置している、請求項3に記載の表示基板。

#### 【請求項5】

30

前記出力トランジスタのゲート電極は、少なくとも一つの出力ゲート電極パターンを含み、前記出力トランジスタの第1電極は、少なくとも一つの第1電極パターンを含み、前記出力トランジスタの第2電極は、少なくとも一つの第2電極パターンを含み、

前記出力ゲート電極パターンは、隣接する前記第1電極パターンと前記第2電極パターンとの間に位置しており、

前記第1電極パターン、前記出力ゲート電極パターン及び前記第2電極パターンはいずれも第2方向に沿って延在されており、

または、

前記出力リセットトランジスタのゲート電極は、少なくとも一つの出力リセットゲート電極パターンを含み、前記出力リセットトランジスタの第1電極は、少なくとも一つの第3電極パターンを含み、前記出力リセットトランジスタの第2電極は、少なくとも一つの第4電極パターンを含み、

40

前記出力リセットゲート電極パターンは、隣接する前記第3電極パターンと前記第4電極パターンとの間に位置しており、

前記第3電極パターン、前記出力リセットゲート電極パターン及び前記第4電極パターンはいずれも第2方向に沿って延在され、

前記出力リセットトランジスタのうち、前記出力トランジスタのゲート電極に最も近接する前記第4電極パターンが前記出力トランジスタの第2電極パターンとして兼用される、請求項4に記載の表示基板。

#### 【請求項6】

前記出力トランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なく

50

とも二つの第1導電部分及び少なくとも一つの第1チャネル部分を含み、それぞれの前記第1チャネル部分は二つの隣接する前記第1導電部分の間に設けられており、

前記第1チャネル部分が前記出力ゲート電極パターンに一対一対応され、各前記第1チャネル部分の前記ベースでの正投影が、いずれも対応する前記出力ゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力トランジスタのうちの一部の前記第1導電部分が前記第1電極パターンに一対一対応され、前記第1電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第1重なり領域を有し、前記第1電極パターンは前記第1重なり領域に設けられている少なくとも一つの第1ビアホールを介して対応する前記第1導電部分に結合され、

前記出力トランジスタのうちの他の一部の前記第1導電部分が前記第2電極パターンに一対一対応され、前記第2電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第2重なり領域を有し、前記第2電極パターンは前記第2重なり領域に設けられている少なくとも一つの第2ビアホールを介して対応する前記第1導電部分に結合される、請求項5に記載の表示基板。

#### 【請求項7】

前記出力リセットトランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第2導電部分及び少なくとも一つの第2チャネル部分を含み、それぞれの前記第2チャネル部分は二つの隣接する前記第2導電部分の間に設けられており、

前記第2チャネル部分は、前記出力リセットゲート電極パターンに一対一対応され、各前記第2チャネル部分の前記ベースでの正投影は、いずれも対応する前記出力リセットゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力リセットトランジスタのうちの一部の前記第2導電部分が前記第3電極パターンに一対一対応され、前記第3電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第3重なり領域を有し、前記第3電極パターンは、前記第3重なり領域に設けられている少なくとも一つの第3ビアホールを介して対応する前記第2導電部分に結合され、

前記出力リセットトランジスタのうちの他の一部の前記第2導電部分が前記第4電極パターンに一対一対応され、前記第4電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第4重なり領域を有し、前記第4電極パターンは、前記第4重なり領域に設けられている少なくとも一つの第4ビアホールを介して対応する前記第2導電部分に結合される、請求項5に記載の表示基板。

#### 【請求項8】

前記走査駆動回路は第2電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタをさらに含み、

前記第2電圧信号線が電極導電接続部に結合され、前記電極導電接続部が第2方向に沿って延在され、前記少なくとも一つの第1電極パターンは第1方向に沿って順次に配列され、

前記電極導電接続部が前記出力トランジスタの第1電極に含まれる1番目の第1電極パターンに結合され、

前記第4トランジスタの第1電極が前記電極導電接続部に結合され、

前記第4トランジスタのゲート電極の前記ベースでの正投影と、前記電極導電接続部の前記ベースでの正投影との間の第1方向での最小距離が第4所定距離であり、

前記第4所定距離が $1 \mu m$ 以上かつ $5 \mu m$ 以下である、請求項5に記載の表示基板。

#### 【請求項9】

前記少なくとも一つのシフトレジスタユニットは、第4トランジスタ及び第5トランジスタをさらに含み、

前記第4トランジスタのゲート電極が前記第5トランジスタのゲート電極に結合され、

前記第4トランジスタのゲート電極及び前記第5トランジスタのゲート電極が第1ゲート金属パターンに含まれ、前記第1ゲート金属パターンが第2方向に沿って延在され、

10

20

30

40

50

前記走査駆動回路は第1クロック信号線をさらに含み、前記第5トランジスタのゲート電極が前記第1クロック信号線に結合され、

前記第1クロック信号線は第1方向に沿って延在され、前記第1クロック信号線は前記第5トランジスタの表示領域から離れた側に位置している、請求項1に記載の表示基板。

**【請求項10】**

前記少なくとも一つのシフトレジスタユニットは、第1トランジスタ、第4トランジスタ、第5トランジスタ、第6トランジスタ及び出力コンデンサをさらに含み、

前記第5トランジスタの第1電極が入力信号端に結合され、前記第5トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第6トランジスタのゲート電極は、互いに結合される第1ゲート電極パターン及び第2ゲート電極パターンを含み、

前記第1ゲート電極パターン及び前記第2ゲート電極パターンがそれぞれ前記出力コンデンサの第1極板に結合され、前記出力コンデンサの第1極板が前記出力トランジスタのゲート電極に結合され、

前記第6トランジスタの第1電極が第4トランジスタのゲート電極に結合され、前記第6トランジスタの第2電極が前記第4トランジスタの第2電極に結合され、前記出力コンデンサの第2極板が前記第1トランジスタの第1電極に結合され、

前記第4トランジスタ、前記第6トランジスタ及び前記第1トランジスタが前記第1方向に沿って順次に配列され、

前記第5トランジスタ、前記第6トランジスタ及び前記第1トランジスタが前記第1方向に沿って順次に配列され、

前記出力コンデンサは、前記第6トランジスタと前記出力回路との間に位置している、請求項1に記載の表示基板。

**【請求項11】**

前記少なくとも一つのシフトレジスタユニットは、第2トランジスタ、第1トランジスタ、第6トランジスタ、第7トランジスタ及び第8トランジスタをさらに含み、

前記第7トランジスタのアクティブ層及び前記第8トランジスタのアクティブ層が一つの連続した第2半導体層により形成され、前記第2半導体層が第1方向に沿って延在され、

前記第7トランジスタのアクティブ層は、第1方向に沿って順次に設置される1番目の第9導電部分、第9チャネル部分及び2番目の第9導電部分を含み、

前記2番目の第9導電部分が1番目の第10導電部分として兼用され、

前記第8トランジスタのアクティブ層は、第1方向に沿って順次に設置される1番目の第10導電部分、第10チャネル部分及び2番目の第10導電部分を含み、

前記1番目の第9導電部分が前記第7トランジスタの第2電極として用いられ、前記2番目の第9導電部分が前記第7トランジスタの第1電極として用いられ、前記2番目の第10導電部分が前記第8トランジスタの第1電極として用いられ、前記第7トランジスタの第1電極が前記第8トランジスタの第2電極として兼用され、

前記第7トランジスタのゲート電極が出力コンデンサの第2極板に結合され、前記第7トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第8トランジスタのゲート電極が前記第1トランジスタのゲート電極に結合され、

前記第8トランジスタの第1電極が第1電圧信号線に結合され、

前記第1電圧信号線が第1方向に沿って延在され、

前記第6トランジスタ、前記第7トランジスタ、前記第8トランジスタ及び前記第2トランジスタは、第1方向に沿って順次に配列され、

前記走査駆動回路は第2クロック信号線をさらに含み、前記第2トランジスタのゲート電極及び第7トランジスタのゲート電極がそれぞれ前記第2クロック信号線に結合され、

前記第2クロック信号線が第1方向に沿って延在され、前記第2クロック信号線が前記第2トランジスタの表示領域から離れた側に位置している、請求項1に記載の表示基板。

**【請求項12】**

前記走査駆動回路は、第2電圧信号線及び信号出力線をさらに含み、

10

20

30

40

50

前記信号出力線は、第1出力線部分及び少なくとも一つの第2出力線部分を含み、前記第2電圧信号線及び前記第1出力線部分がいずれも第1方向に沿って延在され、前記第1出力線部分が前記第2電圧信号線と前記出力回路との間に位置しており、前記第2出力線部分が第2方向に沿って延在され、

前記第2出力線部分が表示領域のうち、画素回路に発光制御信号を提供することに用いられ、

前記第1出力線部分及び前記出力回路が前記第2電圧信号線の前記表示領域から離れた側に位置しており、

または、

前記走査駆動回路は、第1電圧信号線、第2電圧信号線、第1クロック信号線及び第2クロック信号線をさらに含み、

前記第1電圧信号線、前記第2電圧信号線、前記第1クロック信号線及び前記第2クロック信号線がいずれも第1方向に沿って延在され、

前記第1電圧信号線の前記ベースでの正投影、前記第1クロック信号線の前記ベースでの正投影及び前記第2クロック信号線の前記ベースでの正投影がいずれも前記シフトレジスタユニットの前記ベースでの正投影の前記表示領域から離れた側に位置しており、

前記第2電圧信号線の前記ベースでの正投影は、前記シフトレジスタユニットの前記表示領域に近い側に位置している、

または、

前記信号出力線は、少なくとも一つの第2出力線部分をさらに含み、前記第2出力線部分が前記第1出力線部分に結合され、前記第2出力線部分が前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられる、請求項1に記載の表示基板。

### 【請求項13】

前記走査駆動回路は、第1電圧信号線、第2電圧信号線、第1クロック信号線、第2クロック信号線及び信号出力線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、第1コンデンサ、出力コンデンサ、出力リセットコンデンサ、第1トランジスタ、第2トランジスタ、第3トランジスタ、第4トランジスタ、第5トランジスタ、第6トランジスタ、第7トランジスタ及び第8トランジスタをさらに含み、前記信号出力線は、少なくとも一つの第2出力線部分をさらに含み、

前記出力トランジスタのゲート電極が前記出力コンデンサの第1極板に結合され、前記出力トランジスタの第1電極が第2電圧信号線に結合され、前記出力トランジスタの第2電極が前記信号出力線に結合され、

前記出力リセットトランジスタのゲート電極が前記出力リセットコンデンサの第1極板に結合され、前記出力リセットトランジスタの第1電極が前記出力リセットコンデンサの第2極板に結合され、前記出力リセットトランジスタの第2電極が前記信号出力線に結合され、

前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、前記出力コンデンサの第2極板が前記第7トランジスタのゲート電極に結合され、

前記第1トランジスタの第1電極が前記出力コンデンサの第2極板に結合され、前記第1トランジスタの第2電極及び前記第2トランジスタの第1電極がそれぞれ前記第1コンデンサの第2極板に結合され、前記第1トランジスタのゲート電極が前記第1コンデンサの第1極板に結合され、

前記第2トランジスタのゲート電極が前記第2クロック信号線に結合され、前記第2トランジスタの第2電極が前記第3トランジスタの第2電極に結合され、

前記第3トランジスタのゲート電極が前記出力トランジスタのゲート電極に結合され、

前記第3トランジスタの第1電極が前記出力リセットコンデンサの第1極板に結合され、

前記第4トランジスタのゲート電極が前記第5トランジスタのゲート電極に結合され、

前記第4トランジスタの第1電極が前記出力トランジスタの第1電極に結合され、前記第4トランジスタの第2電極が前記第6トランジスタの第2電極に結合され、

10

20

30

40

50

前記第5トランジスタのゲート電極が前記第1クロック信号線に結合され、前記第5トランジスタの第1電極が入力信号端に結合され、第5トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第6トランジスタの第1電極が第4トランジスタのゲート電極に結合され、前記第6トランジスタの第2電極が前記第4トランジスタの第2電極に結合され、

前記第8トランジスタのゲート電極が前記第1トランジスタのゲート電極に結合され、前記第8トランジスタの第1電極が第1電圧信号線に結合され、

前記第2出力線部分は、前記第1出力線部分に結合され、前記第2出力線部分は前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられ、

第2電圧信号線が前記シフトレジスタユニットの表示領域に近い側に設けられており、

前記第1電圧信号線、前記第1クロック信号線及び前記第2クロック信号線が、前記シフトレジスタユニットの表示領域から離れた側に設けられており、

前記表示領域に近づいてくる方向に沿って、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、もしくは、前記表示領域に近づいてくる方向に沿って、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列され、

前記走査駆動回路は、第1初期信号線及び第2初期信号線をさらに含み、

前記表示領域に近づいてくる方向に沿って、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列される場合、

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、または

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列される場合、

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列され、または

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列され、

前記出力トランジスタ及び前記出力リセットトランジスタは前記出力コンデンサと前記第1出力線部分との間に位置しており、前記出力トランジスタ及び前記出力リセットトランジスタが前記第1方向に沿って順次に配列され、

第1方向に沿って、前記第5トランジスタ、前記第6トランジスタ、前記第7トランジスタ、前記第8トランジスタ、前記第1トランジスタ、前記第1コンデンサ、前記第2トランジスタ及び前記出力リセットトランジスタが順次に配列され、

前記第5トランジスタ、前記第4トランジスタ、前記第6トランジスタ、前記第7トランジスタ及び前記第8トランジスタが前記出力コンデンサと前記第1電圧信号線との間に位置しており、

前記第5トランジスタのゲート電極及び前記第4トランジスタのゲート電極が第1ゲート金属パターンに含まれ、前記第1ゲート金属パターンが前記第2方向に沿って延在される、請求項1に記載の表示基板。

#### 【請求項14】

前記表示基板は、前記ベースに設けられる複数行の画素回路をさらに含み、前記画素回路は発光制御端を含み、

前記シフトレジスタユニットが少なくとも一行の前記画素回路に対応され、

10

20

30

40

50

前記シフトレジスタユニットの信号出力線が前記少なくとも一行の画素回路の発光制御端に結合されて、前記少なくとも一行の画素回路の発光制御端に発光制御信号を提供することに用いられる、請求項1に記載の表示基板。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、表示技術分野に関し、特に、表示基板、その製作方法及び表示装置に関する。

**【背景技術】**

**【0002】**

アクティブマトリックス有機発光ダイオード(Active-Matrix Organic Light-Emitting Diode、AMOLED)表示パネルは、低い消費電力、低い製造コスト、広い色域などのメリットを持ち、様々な分野で幅広く適用されている。

AMOLED表示パネルは、表示領域に位置する画素回路及び周辺領域に位置する走査駆動回路を含み、前記画素回路は、アレイで分布されている複数のサブ画素回路を含み、前記走査駆動回路は複数のシフトレジスタユニットを含み、各シフトレジスタユニットは、対応するサブ画素回路に発光制御信号を提供することに用いられる。前記走査駆動回路がAMOLED表示パネルの周辺領域に設置されているので、走査駆動回路の配列方式がAMOLED表示パネルの額縁の幅を決めるようになっている。

**【発明の概要】**

**【課題を解決するための手段】**

**【0003】**

第1態様において、本開示の実施例には、表示基板であって、ベースに設けられている走査駆動回路及び表示領域を含み、前記走査駆動回路は、複数のシフトレジスタユニットを含み、前記複数のシフトレジスタユニットのうち、少なくとも一つのシフトレジスタユニットは、信号出力線及び出力回路を含み、前記出力回路は、出力トランジスタ及び出力リセットトランジスタを含み、

前記信号出力線は、第1方向に沿って延在される第1出力線部分を含み、

前記第1出力線部分は、信号線の重なり領域に設けられた複数の第1信号線ビアホールを介して前記出力トランジスタの第2電極に結合され、前記第1出力線部分は、前記信号線の重なり領域に設けられた複数の第2信号線ビアホールを介して前記出力リセットトランジスタの第2電極に結合され、前記複数の第1信号線ビアホールが第1方向に沿って順次に配列され、前記複数の第2信号線ビアホールが第1方向に沿って順次に配列され、

前記信号線の重なり領域は、第1信号線の重なり領域及び第2信号線の重なり領域を含み、前記第1信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力トランジスタの第2電極が含まれる第1ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、前記第2信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力リセットトランジスタの第2電極が含まれる第2ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、

第1方向に沿って順次に配列されるいずれか二つの第1信号線ビアホールの第1方向での最大距離と第3長さとの割合が第1所定割合であり、二つの隣接する第1信号線ビアホールの間の第1方向での最小距離が第1所定距離であり、前記第3長さが、前記第1信号線の重なり領域の第1方向での長さであり、

第1方向に沿って順次に配列されるいずれか二つの第2信号線ビアホールの第1方向での最大距離と第4長さとの割合が第2所定割合であり、二つの隣接する第2信号線ビアホールの間の第1方向での最小距離が第2所定距離であり、前記第4長さが、前記第2信号線の重なり領域の第1方向での長さであり、

前記第1所定割合が0.05以上かつ0.9以下であり、

前記第1所定距離が1.5μm以上かつ4.5μm以下であり、

前記第2所定割合が0.05以上かつ0.9以下であり、

10

20

30

40

50

前記第2所定距離が $1.5\mu m$ 以上かつ $6.5\mu m$ 以下である、表示基板を提供する。

**【0004】**

選択的に、前記出力トランジスタのアクティブ層及び前記出力リセットトランジスタのアクティブ層は、第1方向に沿って配列され、前記出力トランジスタのアクティブ層の前記第1方向での長さを第1長さとして、前記出力リセットトランジスタのアクティブ層の前記第1方向での長さを第2長さとして、前記第1長さと前記第2長さとの和が出力アクティブ長さであり、

前記出力トランジスタのアクティブ層の第2方向に沿う最小の幅と、前記出力リセットトランジスタのアクティブ層の第2方向に沿う最小の幅とのうち、小さいものを出力アクティブ幅とし、前記第1方向と前記第2方向は互いに交差する。

10

**【0005】**

選択的に、前記出力アクティブ長さと前記出力アクティブ幅との割合が所定割合の範囲内にあり、

前記所定割合の範囲が3以上かつ11以下である。

**【0006】**

選択的に、前記出力アクティブ幅が所定の幅の範囲内にあり、

前記所定の幅の範囲が $1.2\mu m$ 以上かつ $4.5\mu m$ である。

**【0007】**

選択的に、前記出力トランジスタのアクティブ層及び前記出力リセットトランジスタのアクティブ層が一つの連続した第1半導体層により形成され、前記第1半導体層が第1方向に沿って延在され、

20

前記第1半導体層の第1方向での長さが出力アクティブ長さであり、

前記第1半導体層の第2方向での最小の長さが前記出力アクティブ長さである。

**【0008】**

選択的に、前記少なくとも一つのシフトレジスタユニットは、第1トランジスタをさらに含み、

前記第1トランジスタは、第1アクティブパターンを含み、前記第1アクティブパターンが第2方向に沿って延在され、

前記第1トランジスタは、前記出力回路の表示領域から離れた側に位置している。

30

**【0009】**

選択的に、前記少なくとも一つのシフトレジスタユニットは、第2トランジスタ及び第3トランジスタをさらに含み、前記第2トランジスタの第2電極が前記第3トランジスタの第2電極に結合され、

前記第2トランジスタのゲート電極の前記ベースでの正投影と、前記第3トランジスタのゲート電極の前記ベースでの正投影との間の第2方向での最大距離が第3所定距離であり、

前記第2トランジスタ及び前記第3トランジスタは、前記出力回路の表示領域から離れた側に位置している。

**【0010】**

選択的に、前記第3所定距離が $1.4\mu m$ 以上かつ $5.0\mu m$ 以下である。

40

**【0011】**

選択的に、前記少なくとも一つのシフトレジスタユニットは、第1トランジスタ、第2トランジスタ及び第1コンデンサをさらに含み、

前記第1トランジスタの第2電極及び前記第2トランジスタの第1電極がそれぞれ前記第1コンデンサの第2極板に結合され、前記第1トランジスタのゲート電極が前記第1コンデンサの第1極板に結合され、

前記第1トランジスタ、前記第1コンデンサ及び前記第2トランジスタが第1方向に沿って順次に配列され、

前記第1トランジスタ、前記第1コンデンサ及び前記第2トランジスタが、前記出力回路の表示領域から離れた側に位置している。

50

**【 0 0 1 2 】**

選択的に、前記走査駆動回路は、第1電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、出力リセットコンデンサをさらに含み、前記出力リセットコンデンサの第1極板が前記出力リセットトランジスタのゲート電極に結合され、前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、

前記出力リセットコンデンサの第2極板の第2方向での最大の幅が第1所定の幅であり、前記出力リセットコンデンサの第2極板の第1方向での最大の長さが第2所定の長さであり、

前記出力リセットコンデンサは前記出力回路の表示領域から離れた側に位置しており、

前記出力リセットコンデンサの第2極板の前記ベースでの正投影が前記出力リセットコンデンサの第1極板の前記ベースでの正投影内にある。10

**【 0 0 1 3 】**

選択的に、前記第1所定の幅が $3\text{ }\mu\text{m}$ 以上かつ $60\text{ }\mu\text{m}$ 以下であり、前記第2所定の長さが $3\text{ }\mu\text{m}$ 以上かつ $20\text{ }\mu\text{m}$ 以下である。

**【 0 0 1 4 】**

選択的に、前記第1電圧信号線が第1方向に沿って延在され、前記第1電圧信号線は前記出力リセットコンデンサの表示領域から離れた側に位置している。

**【 0 0 1 5 】**

選択的に、前記出力トランジスタ及び前記出力リセットトランジスタが第1方向に沿って配列され、前記走査駆動回路は、第2電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、出力リセットコンデンサをさらに含み、20

前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、

前記出力トランジスタの第1電極が第2電圧信号線に結合され、前記出力リセットトランジスタの第1電極が前記出力リセットコンデンサの第2極板に結合され、

前記出力トランジスタ及び前記出力リセットトランジスタが前記第2電圧信号線の表示領域から離れた側に位置している。

**【 0 0 1 6 】**

選択的に、前記出力トランジスタのゲート電極は、少なくとも一つの出力ゲート電極パターンを含み、前記出力トランジスタの第1電極は、少なくとも一つの第1電極パターンを含み、前記出力トランジスタの第2電極は、少なくとも一つの第2電極パターンを含み、30

前記出力ゲート電極パターンは、隣接する前記第1電極パターンと前記第2電極パターンとの間に位置しており、

前記第1電極パターン、前記出力ゲート電極パターン及び前記第2電極パターンはいずれも第2方向に沿って延在されている。

**【 0 0 1 7 】**

選択的に、前記出力リセットトランジスタのゲート電極は、少なくとも一つの出力リセットゲート電極パターンを含み、前記出力リセットトランジスタの第1電極は、少なくとも一つの第3電極パターンを含み、前記出力リセットトランジスタの第2電極は、少なくとも一つの第4電極パターンを含み、

前記出力リセットゲート電極パターンは、隣接する前記第3電極パターンと前記第4電極パターンとの間に位置しており、40

前記第3電極パターン、前記出力リセットゲート電極パターン及び前記第4電極パターンはいずれも第2方向に沿って延在され、

前記出力リセットトランジスタのうち、前記出力トランジスタのゲート電極に最も近接する前記第4電極パターンが前記出力トランジスタの第2電極パターンとして兼用される。

**【 0 0 1 8 】**

選択的に、前記出力トランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第1導電部分及び少なくとも一つの第1チャネル部分を含み、それぞれの前記第1チャネル部分は二つの隣接する前記第1導電部分の間に設けられており、

前記第1チャネル部分が前記出力ゲート電極パターンに一対一対応され、各前記第1チ50

ヤネル部分の前記ベースでの正投影が、いずれも対応する前記出力ゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力トランジスタのうちの一部の前記第1導電部分が前記第1電極パターンに一対一対応され、前記第1電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第1重なり領域を有し、前記第1電極パターンは前記第1重なり領域に設けられている少なくとも一つの第1ビアホールを介して対応する前記第1導電部分に結合され、

前記出力トランジスタのうちの他の一部の前記第1導電部分が前記第2電極パターンに一対一対応され、前記第2電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第2重なり領域を有し、前記第2電極パターンは前記第2重なり領域に設けられている少なくとも一つの第2ビアホールを介して対応する前記第1導電部分に結合される。

#### 【0019】

選択的に、前記出力リセットトランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第2導電部分及び少なくとも一つの第2チャネル部分を含み、それぞれの前記第2チャネル部分は二つの隣接する前記第2導電部分の間に設けられており、

前記第2チャネル部分は、前記出力リセットゲート電極パターンに一対一対応され、各前記第2チャネル部分の前記ベースでの正投影は、いずれも対応する前記出力リセットゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力リセットトランジスタのうちの一部の前記第2導電部分が前記第3電極パターンに一対一対応され、前記第3電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第3重なり領域を有し、前記第3電極パターンは、前記第3重なり領域に設けられている少なくとも一つの第3ビアホールを介して対応する前記第2導電部分に結合され、

前記出力リセットトランジスタのうちの他の一部の前記第2導電部分が前記第4電極パターンに一対一対応され、前記第4電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第4重なり領域を有し、前記第4電極パターンは、前記第4重なり領域に設けられている少なくとも一つの第4ビアホールを介して対応する前記第2導電部分に結合される。

#### 【0020】

選択的に、前記走査駆動回路は第2電圧信号線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタをさらに含み、

前記第2電圧信号線が電極導電接続部に結合され、前記電極導電接続部が第2方向に沿って延在され、前記少なくとも一つの第1電極パターンは第1方向に沿って順次に配列され、

前記電極導電接続部が前記出力トランジスタの第1電極に含まれる1番目の第1電極パターンに結合され、

前記第4トランジスタの第1電極が前記電極導電接続部に結合され、

前記第4トランジスタのゲート電極の前記ベースでの正投影と、前記電極導電接続部の前記ベースでの正投影との間の第1方向での最小距離が第4所定距離である。

#### 【0021】

選択的に、前記第4所定距離が $1\text{ }\mu\text{m}$ 以上かつ $5\text{ }\mu\text{m}$ 以下である。

#### 【0022】

選択的に、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタ及び第5トランジスタをさらに含み、

前記第4トランジスタのゲート電極が前記第5トランジスタのゲート電極に結合され、

前記第4トランジスタのゲート電極及び前記第5トランジスタのゲート電極が第1ゲート金属パターンに含まれ、前記第1ゲート金属パターンが第2方向に沿って延在される。

#### 【0023】

10

20

30

40

50

選択的に、前記走査駆動回路は第1クロック信号線をさらに含み、前記第5トランジスタのゲート電極が前記第1クロック信号線に結合され、

前記第1クロック信号線は第1方向に沿って延在され、前記第1クロック信号線は前記第5トランジスタの表示領域から離れた側に位置している。

#### 【0024】

選択的に、前記少なくとも一つのシフトレジスタユニットは、第1トランジスタ、第4トランジスタ、第5トランジスタ、第6トランジスタ及び出力コンデンサをさらに含み、

前記第5トランジスタの第1電極が入力信号端に結合され、前記第5トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第6トランジスタのゲート電極は、互いに結合される第1ゲート電極パターン及び第2ゲート電極パターンを含み、10

前記第1ゲート電極パターン及び前記第2ゲート電極パターンがそれぞれ前記出力コンデンサの第1極板に結合され、前記出力コンデンサの第1極板が前記出力トランジスタのゲート電極に結合され、

前記第6トランジスタの第1電極が第4トランジスタのゲート電極に結合され、前記第6トランジスタの第2電極が前記第4トランジスタの第2電極に結合され、前記出力コンデンサの第2極板が前記第1トランジスタの第1電極に結合され、

前記第4トランジスタ、前記第6トランジスタ及び前記第1トランジスタが前記第1方向に沿って順次に配列され、20

前記第5トランジスタ、前記第6トランジスタ及び前記第1トランジスタが前記第1方向に沿って順次に配列され、

前記出力コンデンサは、前記第6トランジスタと前記出力回路との間に位置している。

#### 【0025】

選択的に、前記少なくとも一つのシフトレジスタユニットは、第2トランジスタ、第1トランジスタ、第6トランジスタ、第7トランジスタ及び第8トランジスタをさらに含み、

前記第7トランジスタのアクティブ層及び前記第8トランジスタのアクティブ層が一つの連続した第2半導体層により形成され、前記第2半導体層が第1方向に沿って延在され、

前記第7トランジスタのアクティブ層は、第1方向に沿って順次に設置される1番目の第9導電部分、第9チャネル部分及び2番目の第9導電部分を含み、30

前記2番目の第9導電部分が1番目の第10導電部分として兼用され、

前記第8トランジスタのアクティブ層は、第1方向に沿って順次に設置される1番目の第10導電部分、第10チャネル部分及び2番目の第10導電部分を含み、

前記1番目の第9導電部分が前記第7トランジスタの第2電極として用いられ、前記2番目の第9導電部分が前記第7トランジスタの第1電極として用いられ、前記2番目の第10導電部分が前記第8トランジスタの第1電極として用いられ、前記第7トランジスタの第1電極が前記第8トランジスタの第2電極として兼用され、

前記第7トランジスタのゲート電極が出力コンデンサの第2極板に結合され、前記第7トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、40

前記第8トランジスタのゲート電極が前記第1トランジスタのゲート電極に結合され、前記第8トランジスタの第1電極が第1電圧信号線に結合され、

前記第1電圧信号線が第1方向に沿って延在され、

前記第6トランジスタ、前記第7トランジスタ、前記第8トランジスタ及び前記第2トランジスタは、第1方向に沿って順次に配列される。

#### 【0026】

選択的に、前記走査駆動回路は第2クロック信号線をさらに含み、前記第2トランジスタのゲート電極及び第7トランジスタのゲート電極がそれぞれ前記第2クロック信号線に結合され、

前記第2クロック信号線が第1方向に沿って延在され、前記第2クロック信号線が前記第2トランジスタの表示領域から離れた側に位置している。

#### 【0027】

10

20

30

40

50

選択的に、前記走査駆動回路は、第2電圧信号線及び信号出力線をさらに含み、前記信号出力線は、第1出力線部分及び少なくとも一つの第2出力線部分を含み、前記第2電圧信号線及び前記第1出力線部分がいずれも第1方向に沿って延在され、前記第1出力線部分が前記第2電圧信号線と前記出力回路との間に位置しており、前記第2出力線部分が第2方向に沿って延在され、前記第2出力線部分が表示領域のうち、画素回路に発光制御信号を提供することに用いられ、前記第1出力線部分及び前記出力回路が前記第2電圧信号線の前記表示領域から離れた側に位置している。

## 【0028】

10

選択的に、前記走査駆動回路は、第1電圧信号線、第2電圧信号線、第1クロック信号線及び第2クロック信号線をさらに含み、前記第1電圧信号線、前記第2電圧信号線、前記第1クロック信号線及び前記第2クロック信号線がいずれも第1方向に沿って延在され、前記第1電圧信号線の前記ベースでの正投影、前記第1クロック信号線の前記ベースでの正投影及び前記第2クロック信号線の前記ベースでの正投影がいずれも前記シフトレジスタユニットの前記ベースでの正投影の前記表示領域から離れた側に位置しており、前記第2電圧信号線の前記ベースでの正投影は、前記シフトレジスタユニットの前記表示領域に近い側に位置している。

## 【0029】

20

選択的に、前記信号出力線は、少なくとも一つの第2出力線部分をさらに含み、前記第2出力線部分が前記第1出力線部分に結合され、前記第2出力線部分が前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられる。

## 【0030】

30

選択的に、前記走査駆動回路は、第1電圧信号線、第2電圧信号線、第1クロック信号線、第2クロック信号線及び信号出力線をさらに含み、前記少なくとも一つのシフトレジスタユニットは、第1コンデンサ、出力コンデンサ、出力リセットコンデンサ、第1トランジスタ、第2トランジスタ、第3トランジスタ、第4トランジスタ、第5トランジスタ、第6トランジスタ、第7トランジスタ及び第8トランジスタをさらに含み、前記信号出力線は、少なくとも一つの第2出力線部分をさらに含み、

前記出力トランジスタのゲート電極が前記出力コンデンサの第1極板に結合され、前記出力トランジスタの第1電極が第2電圧信号線に結合され、前記出力トランジスタの第2電極が前記信号出力線に結合され、

前記出力リセットトランジスタのゲート電極が前記出力リセットコンデンサの第1極板に結合され、前記出力リセットトランジスタの第1電極が前記出力リセットコンデンサの第2極板に結合され、前記出力リセットトランジスタの第2電極が前記信号出力線に結合され、

前記出力リセットコンデンサの第2極板が前記第1電圧信号線に結合され、前記出力コンデンサの第2極板が前記第7トランジスタのゲート電極に結合され、

前記第1トランジスタの第1電極が前記出力コンデンサの第2極板に結合され、前記第1トランジスタの第2電極及び前記第2トランジスタの第1電極がそれぞれ前記第1コンデンサの第2極板に結合され、前記第1トランジスタのゲート電極が前記第1コンデンサの第1極板に結合され、

前記第2トランジスタのゲート電極及び第7トランジスタのゲート電極がそれぞれ前記第2クロック信号線に結合され、前記第2トランジスタの第2電極が前記第3トランジスタの第2電極に結合され、

前記第3トランジスタのゲート電極が前記出力トランジスタのゲート電極に結合され、前記第3トランジスタの第1電極が前記出力リセットコンデンサの第1極板に結合され、前記第4トランジスタのゲート電極が前記第5トランジスタのゲート電極に結合され、

40

50

前記第4トランジスタの第1電極が前記出力トランジスタの第1電極に結合され、前記第4トランジスタの第2電極が前記第6トランジスタの第2電極に結合され、

前記第5トランジスタのゲート電極が前記第1クロック信号線に結合され、前記第5トランジスタの第1電極が入力信号端に結合され、第5トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第6トランジスタの第1電極が第4トランジスタのゲート電極に結合され、前記第6トランジスタの第2電極が前記第4トランジスタの第2電極に結合され、

前記第7トランジスタのゲート電極が出力コンデンサの第2極板に結合され、前記第7トランジスタの第1電極が前記第8トランジスタの第2電極として兼用され、前記第7トランジスタの第2電極が前記第6トランジスタのゲート電極に結合され、

前記第8トランジスタのゲート電極が前記第1トランジスタのゲート電極に結合され、前記第8トランジスタの第1電極が第1電圧信号線に結合され、

前記第2出力線部分は、前記第1出力線部分に結合され、前記第2出力線部分は前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられる。

#### 【0031】

選択的に、第2電圧信号線が前記シフトレジスタユニットの表示領域に近い側に設けられており、

前記第1電圧信号線、前記第1クロック信号線及び前記第2クロック信号線が、前記シフトレジスタユニットの表示領域から離れた側に設けられており、

前記表示領域に近づいてくる方向に沿って、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、もしくは、前記表示領域に近づいてくる方向に沿って、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列される。

#### 【0032】

選択的に、前記走査駆動回路は、第1初期信号線及び第2初期信号線をさらに含み、

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列される。

#### 【0033】

選択的に、前記出力トランジスタ及び前記出力リセットトランジスタは前記出力コンデンサと前記第1出力線部分との間に位置しており、前記出力トランジスタ及び前記出力リセットトランジスタが前記第1方向に沿って順次に配列され、

第1方向を沿って、前記第5トランジスタ、前記第6トランジスタ、前記第7トランジスタ、前記第8トランジスタ、前記第1トランジスタ、前記第1コンデンサ、前記第2トランジスタ及び前記出力リセットトランジスタが順次に配列され、

前記第5トランジスタ、前記第4トランジスタ、前記第6トランジスタ、前記第7トランジスタ及び前記第8トランジスタが前記出力コンデンサと前記第1電圧信号線との間に位置しており、

前記第5トランジスタのゲート電極及び前記第4トランジスタのゲート電極が第1ゲート金属パターンに含まれ、前記第1ゲート金属パターンが前記第2方向に沿って延在され

10

20

30

40

50

る。

【0034】

選択的に、前記表示基板は、前記ベースに設けられる複数行の画素回路をさらに含み、前記画素回路は発光制御端を含み、

前記シフトレジスタユニットが少なくとも一行の前記画素回路に対応され、

前記シフトレジスタユニットの信号出力線が前記少なくとも一行の画素回路の発光制御端に結合されて、前記少なくとも一行の画素回路の発光制御端に発光制御信号を提供することに用いられる。

【0035】

第2態様において、本開示の実施例では、表示基板の製作方法であって、前記表示基板の製作方法は、ベース上に走査駆動回路を製作することを含み、前記走査駆動回路は、複数のシフトレジスタユニットを含み、前記複数のシフトレジスタユニットのうち、少なくとも一つのシフトレジスタユニットは、出力回路を含み、前記出力回路は、出力トランジスタ及び出力リセットトランジスタを含み、

前記表示基板の製作方法は、

前記ベース上に半導体層を製作し、前記半導体層にパターニング工程を行って、出力トランジスタのアクティブ層及び出力リセットトランジスタのアクティブ層を形成することと、

前記半導体層の前記ベースに背く一面に第1ゲート金属層を製作し、前記第1ゲート金属層にパターニング工程を行って、前記出力トランジスタのゲート電極及び前記出力リセットトランジスタのゲート電極を形成することと、

前記出力トランジスタのゲート電極及び前記出力リセットトランジスタのゲート電極をマスクとして、半導体層のうち、前記ゲート電極により被覆されていない部分に対してドーピングを行って、前記半導体層のうち、前記ゲート電極により被覆されていない部分を導電部分として形成し、前記半導体層のうち、前記ゲート電極により被覆されている部分をチャネル部分として形成することと、

前記第1ゲート金属層の前記半導体層に背く一面に第2ゲート金属層を設け、前記第2ゲート金属層にパターニング工程を行って、第1方向に沿って延在される第1出力線部分を含む信号出力線を形成することと、

前記第2ゲート金属層の前記第1ゲート金属層に背く一面に第1絶縁層を設けることと、

前記第1絶縁層と前記第1出力線とが部分的に重なる領域に、前記第1絶縁層を貫通する複数の第1信号線ビアホール及び複数の第2信号線ビアホールを製作することと、

前記第1絶縁層の前記第2ゲート金属層に背く一面にソース・ドレイン金属層を製作し、前記ソース・ドレイン金属層にパターニング工程を行って、第1ソース・ドレイン金属パターン及び第2ソース・ドレイン金属パターンを形成することと、を含み、

前記第1ソース・ドレイン金属パターンが前記出力トランジスタの第2電極を含み、前記第2ソース・ドレイン金属パターンが前記出力リセットトランジスタの第2電極を含んでいることで、前記第1出力線部分が前記複数の第1信号線ビアホールを介して前記出力トランジスタの第2電極に結合され、かつ前記第1出力線部分が前記複数の第2信号線ビアホールを介して前記出力リセットトランジスタの第2電極に結合され、

前記信号出力線は、第1方向に沿って延在される第1出力線部分を含み、

前記複数の第1信号線ビアホールが第1方向に沿って順次に配列され、前記複数の第2信号線ビアホールが第1方向に沿って順次に配列され、

第1方向に沿って順次に配列されるいずれか二つの第1信号線ビアホールの第1方向での最大距離と第3長さとの割合が第1所定割合であり、二つの隣接する第1信号線ビアホールの間の第1方向での最小距離が第1所定距離であり、

第1方向に沿って順次に配列されるいずれか二つの第2信号線ビアホールの第1方向での最大距離と第4長さとの割合が第2所定割合であり、二つの隣接する第2信号線ビアホールの間の第1方向での最小距離が第2所定距離であり、

前記第3長さは、前記第1信号線の重なり領域の第1方向での長さであり、前記第4長

10

20

30

40

50

さは、前記第2信号線の重なり領域の第1方向での長さであり、

前記第1所定割合は、0.05以上かつ0.9以下であり、

前記第1所定距離は、1.5μm以上かつ4.5μm以下であり、

前記第2所定割合は、0.05以上かつ0.9以下であり、

前記第2所定距離は、1.5μm以上かつ6.5μm以下である、表示基板の製作方法を

提供する。

**【0036】**

選択的に、前記出力トランジスタのアクティブ層の前記第1方向での長さを第1長さとして、前記出力リセットトランジスタのアクティブ層の前記第1方向での長さを第2長さとして、前記第1長さと前記第2長さとの和が出力アクティブ長さであり、

10

前記出力トランジスタのアクティブ層の第2方向に沿う最小の幅と、前記出力リセットトランジスタのアクティブ層の第2方向に沿う最小の幅とのうち、小さいものを出力アクティブ幅とし、前記第1方向と前記第2方向は互いに交差する。

**【0037】**

選択的に、前記出力アクティブ長さと前記出力アクティブ幅との割合が所定割合の範囲内にあり、

前記所定割合の範囲が3以上かつ1.1以下である。

**【0038】**

選択的に、前記出力アクティブ幅が所定の幅の範囲内にあり、

20

前記所定の幅の範囲が1.2μm以上かつ4.5μm以下である。

**【0039】**

第3態様において、本開示の実施例では、上記の表示基板を含む表示装置をさらに提供する。

**【図面の簡単な説明】****【0040】**

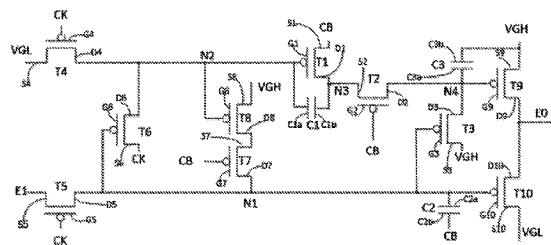

**【図1】**本開示の実施例に記載の表示基板に含まれる少なくとも一つのシフトレジスタユニットの少なくとも一実施例の回路図である。

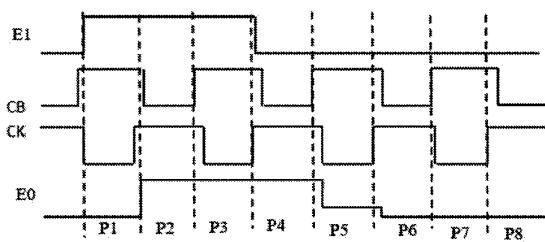

**【図2A】**図1に示されるシフトレジスタユニットの少なくとも一実施例の動作シーケンス図である。

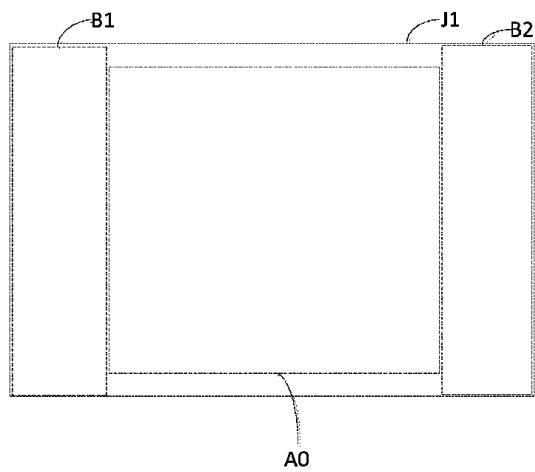

**【図2B】**本開示の少なくとも一実施例に記載の表示基板の領域区画の概略図である。

30

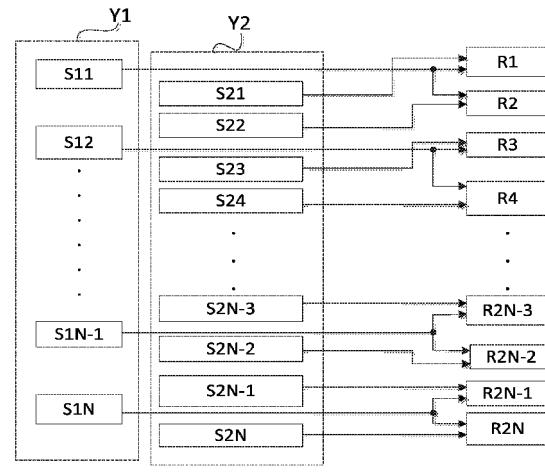

**【図2C】**本開示の少なくとも一実施例に記載の表示基板に含まれる走査駆動回路と画素回路との間の接続関係の概略図である。

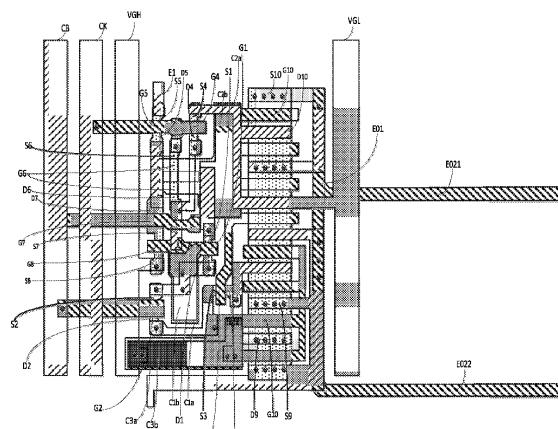

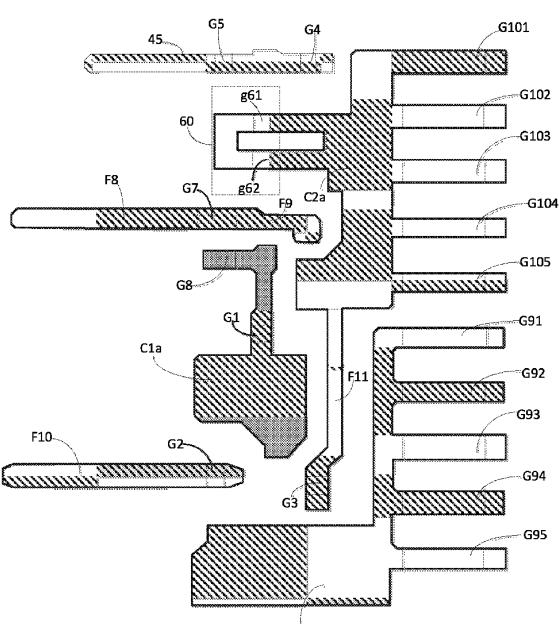

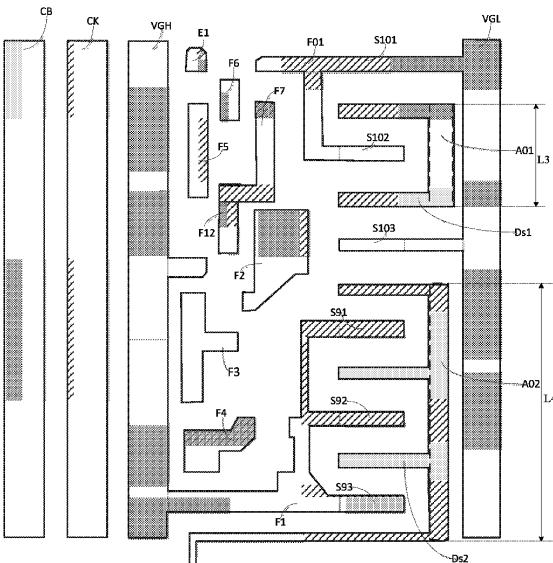

**【図2D】**本開示の少なくとも一実施例に係るシフトレジスタユニットの一レイアウト概略図である。

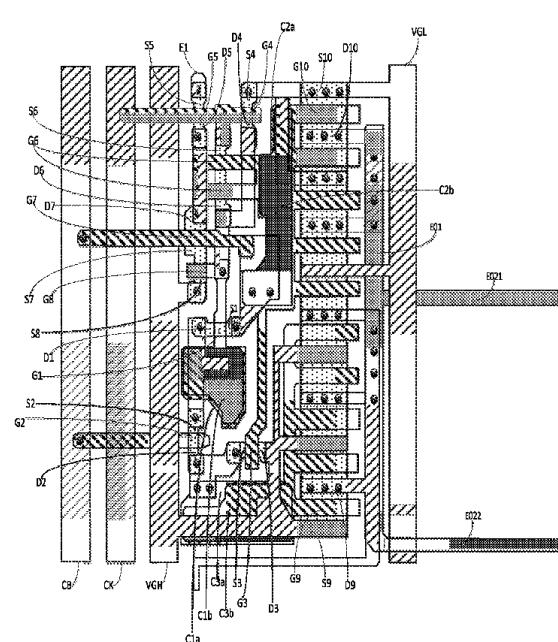

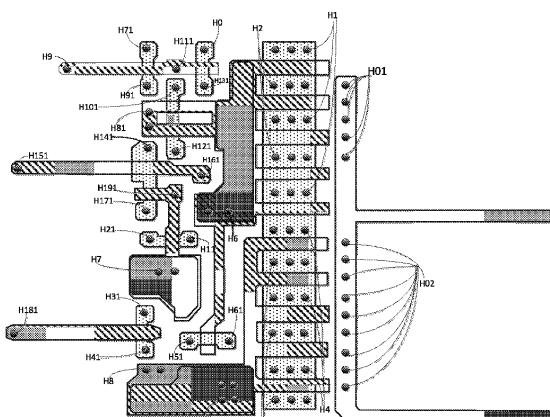

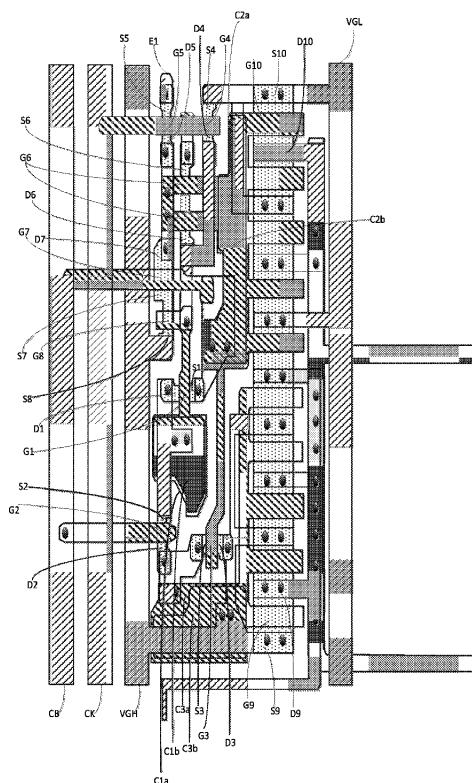

**【図3A】**本開示の少なくとも一実施例に係るシフトレジスタユニットの他のレイアウト概略図である。

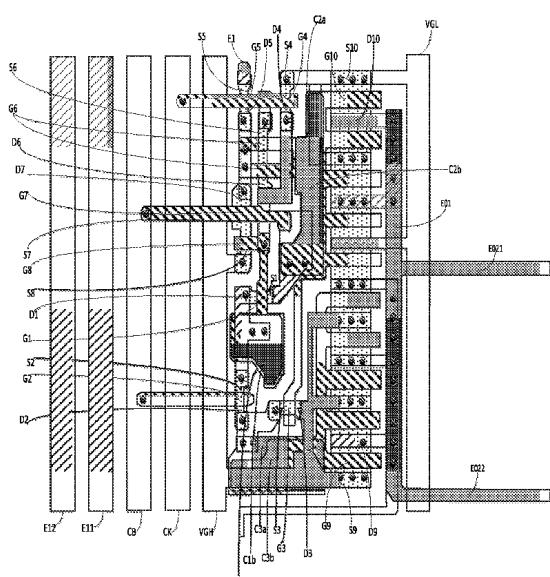

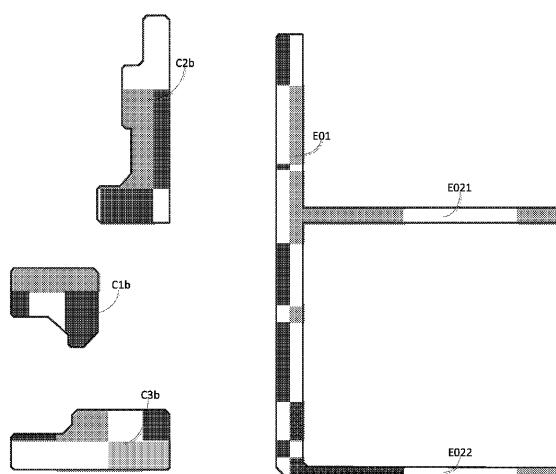

**【図3B】**本開示の少なくとも一実施例に係るシフトレジスタユニットの更なる他のレイアウト概略図である。

**【図4】**図3Aに基づいた、第1方向に沿って順次に配列される1番目の第1信号線ビアホールと最後の一つの第1信号線ビアホールとの第1方向での最大距離K1及び第1方向に沿って順次に配列される1番目の第2信号線ビアホールと最後の一つの第2信号線ビアホールとの第1方向での最大距離K2を示した概略図である。

40

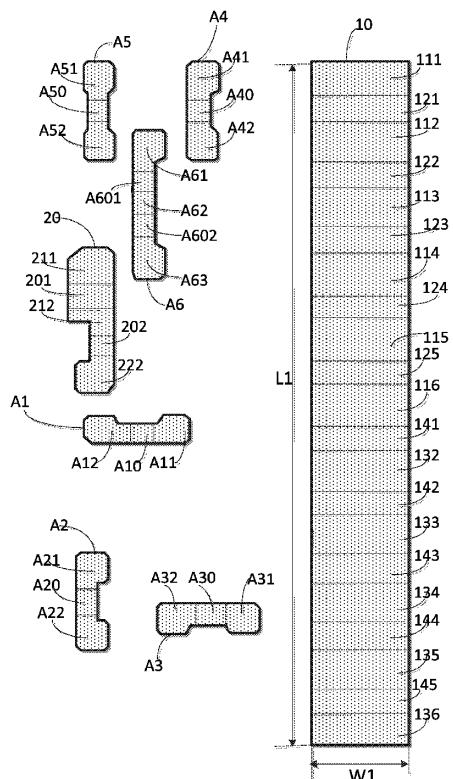

**【図5】**本開示の少なくとも一実施例に係るシフトレジスタユニットのうちのアクティブ層の概略図である。

**【図6】**本開示の少なくとも一実施例に係るシフトレジスタユニットのうちの第1ゲート金属層の概略図である。

**【図7】**本開示の少なくとも一実施例に係るシフトレジスタユニットのうちの第2ゲート金属層の概略図である。

**【図8】**本開示の少なくとも一実施例に係るシフトレジスタユニットに用いられるビアホールの概略図である。

50

【図9】本開示の少なくとも一実施例に係るシフトレジスタユニットのうちのソース・ドレイン金属層の概略図である。

【図10】図3Aのソース・ドレイン金属層の概略図である。

【図11】本開示の少なくとも一実施例に係るシフトレジスタユニットの更なる他のレイアウト概略図である。

【発明を実施するための形態】

【0041】

以下、本開示の実施例の図面を参照しながら、本開示の実施例の技術案を明確かつ完全に説明する。明らかなように、説明される実施例は本開示の一部の実施例に過ぎず、全ての実施例ではない。説明される本開示の実施例に基づいて、当業者が創造的な努力をせずに想到し得るほかの実施例は、すべて本開示の特許範囲に属する。

10

【0042】

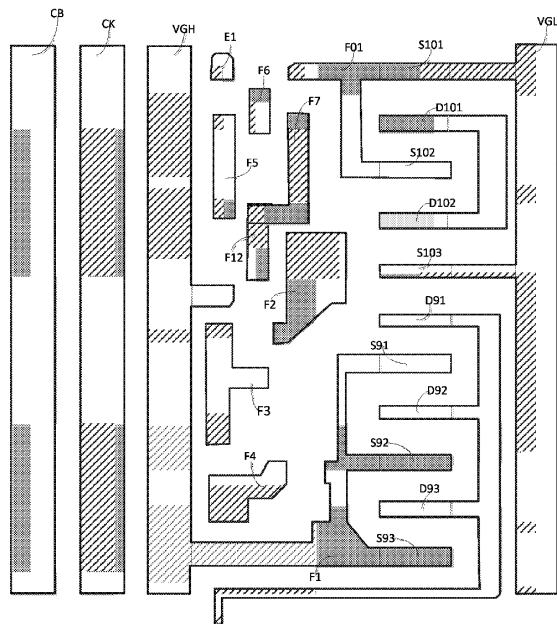

図1に示すように、本開示の少なくとも一実施例は、表示基板を提供し、前記表示基板は表示基板の周辺領域に位置する走査駆動回路を含み、前記走査駆動回路は、第1電圧信号線VGH、第2電圧信号線VGL、第1クロック信号線CK、第2クロック信号線CB及び信号出力線E0を含み、前記走査駆動回路は、複数のシフトレジスタユニットをさらに含み、

20

図1に示すように、前記複数のシフトレジスタユニットのうち、少なくとも一つのシフトレジスタユニットの少なくとも一実施例は、第1コンデンサC1、出力コンデンサC2、出力リセットコンデンサC3、出力トランジスタT10、出力リセットトランジスタT9、第1トランジスタT1、第2トランジスタT2、第3トランジスタT3、第4トランジスタT4、第5トランジスタT5、第6トランジスタT6、第7トランジスタT7及び第8トランジスタT8を含み、

前記出力トランジスタT10のゲート電極G10は、前記出力コンデンサC2の第1極板C2aに結合され、前記出力トランジスタT10の第1電極S10は、第2電圧信号線VGLに結合され、前記出力トランジスタT10の第2電極D10は、前記信号出力線E0に結合され、

前記出力リセットトランジスタT9のゲート電極G9は、前記出力リセットコンデンサC3の第1極板C3aに結合され、前記出力リセットトランジスタT9の第1電極S9は、前記出力リセットコンデンサC3の第2極板C3bに結合され、前記出力リセットトランジスタT9の第2電極D9は、前記信号出力線E0に結合され、

30

前記出力リセットコンデンサC3の第2極板C3bが前記第1電圧信号線VGHに結合され、前記出力コンデンサC2の第2極板C2bが第2クロック信号線CBに結合され、

前記第1トランジスタT1の第1電極S1が前記第2クロック信号線CBに結合され、前記第1トランジスタT1の第2電極D1及び前記第2トランジスタT2の第1電極S2がそれぞれ前記第1コンデンサC1の第2極板C1bに結合され、前記第1トランジスタT1のゲート電極G1が前記第1コンデンサC1の第1極板C1aに結合され、

前記第2トランジスタT2のゲート電極G2及び第7トランジスタT7のゲート電極G7は、それぞれ前記第1クロック信号線CKに結合され、前記第2トランジスタT2の第2電極D2は、前記第3トランジスタT3の第2電極D3に結合され、前記第2トランジスタT2の第1電極S2は、前記第1コンデンサの第2極板C1bに結合され、

40

前記第3トランジスタT3のゲート電極G3は、前記出力トランジスタT10のゲート電極G10に結合され、前記第3トランジスタT3の第1電極S3は、前記第1電圧信号線VGHに結合され、

前記第4トランジスタT4のゲート電極G4及び前記第5トランジスタT5のゲート電極G5は、いずれも第1クロック信号線CKに結合され、前記第4トランジスタT4の第1電極S4及び前記出力トランジスタT10の第1電極S10は、いずれも第2電圧信号線VGLに結合され、前記第4トランジスタT4の第2電極D4は、前記第6トランジスタT6の第2電極D6に結合され、

前記第5トランジスタT5のゲート電極G5は、前記第1クロック信号線CKに結合さ

50

れ、第5トランジスタT5の第2電極D5は、前記第6トランジスタT6のゲート電極G6に結合され、前記第5トランジスタT5の第1電極S5は、入力信号端E1に結合され、

前記第6トランジスタT6の第1電極S1及び第4トランジスタT4のゲート電極G4は、いずれも第1クロック信号線CKに結合され、前記第6トランジスタT6の第2電極D6は、前記第4トランジスタT4の第2電極D4に結合され、前記第6トランジスタT6のゲート電極G6は、第5トランジスタの第2電極D1に結合され、

前記第7トランジスタT7のゲート電極G7及び出力コンデンサCBの第2極板C2bは、いずれも第2クロック信号線CBに結合され、前記第7トランジスタT7の第1電極S7は、前記第8トランジスタT8の第2電極D8に結合され、前記第7トランジスタT7の第2電極D7は、前記第6トランジスタT6のゲート電極G6に結合され、

前記第8トランジスタT8のゲート電極G8は、前記第1トランジスタT1のゲート電極G1に結合され、前記第8トランジスタT8の第1電極S8は、第1電圧信号線VGHに結合される。

#### 【0043】

図1に示されるシフトレジスタユニットの少なくとも一実施例では、全てのトランジスタはいずれもp型トランジスタであるが、これに限らない。

#### 【0044】

本開示の少なくとも一実施例では、図1に示されるシフトレジスタユニットの少なくとも一実施例は、発光制御走査駆動回路であってもよいが、これに限らない。

#### 【0045】

本開示の少なくとも一実施例では、トランジスタの第1電極はソース電極であってもよく、トランジスタの第2電極はドレイン電極であってもよく、もしくは、トランジスタの第1電極はドレイン電極であってもよく、トランジスタの第2電極はソース電極であってもよく。

#### 【0046】

図1において、符号N1は第1ノードであり、符号N2は第2ノードであり、符号N3は第3ノードであり、符号N4は第4ノードである。

#### 【0047】

図1に示した少なくとも一実施例では、第1電圧信号線VGHは高電圧Vghを提供することができ、第2電圧信号線VGLは低電圧Vglを提供することができるが、これに限らない。

#### 【0048】

図2Aに示すように、本開示の図1に示されるシフトレジスタユニットの少なくとも一実施例において、動作する時に、

第1段階P1で、E1がハイレベルを提供し、CKがローレベルを提供し、CBがハイレベルを提供し、T5及びT4がオンとなり、N1の電位がハイレベルで、T6はオフとなり、N2の電位はローレベルであるので、T7、T3及びT10がオフとなり、T8及びT1がオンとなり、この時、N3の電位がハイレベルであり、CBがハイレベルを提供するので、T2がオフとなり、コンデンサの両端の電圧が突然に変化しないので、N4の電位が、前フレームのハイレベルに保持されて、T9がオフとなり、E0から出力される発光制御信号の電位が、前フレームのローレベルに保持され、

第2段階P2で、E1及びCKがいずれもハイレベルを提供し、CBがローレベルを提供し、T5、T6及びT4がいずれもオフとなり、N1の電位がハイレベルに保持され、N2の電位がローレベルに保持され、T7、T8及びT1がいずれもオンとなり、N3の電位がハイレベルからローレベルに変化し、T2がオンとなり、N4の電位がローレベルであり、T9がオンとなり、E0がハイレベルを出力し、T3及びT10がいずれもオフとなり、

第3段階P3で、E1及びCBがいずれもハイレベルを提供し、CKがローレベルを提供し、T5及びT4がいずれもオンとなり、N1の電位がハイレベルであり、N2の電位がローレベルであり、T6及びT7がいずれもオフとなり、T8及びT1がいずれもオン

10

20

30

40

50

となり、N<sub>3</sub>の電位が前の段階のローレベルからハイレベルに変化し、T<sub>2</sub>がオフとなり、N<sub>4</sub>の電位がローレベルに保持され、T<sub>9</sub>がオンとなり、E<sub>0</sub>がハイレベルを出力し、T<sub>3</sub>及びT<sub>10</sub>がいずれもオフとなり。

第4段階P<sub>4</sub>で、E<sub>1</sub>及びC<sub>B</sub>がいずれもローレベルを提供し、C<sub>K</sub>がハイレベルを提供し、T<sub>5</sub>及びT<sub>4</sub>がいずれもオフとなり、N<sub>1</sub>の電位がハイレベルであり、T<sub>6</sub>がオフとなり、N<sub>2</sub>の電位がローレベルに保持され、T<sub>7</sub>、T<sub>8</sub>及びT<sub>1</sub>がいずれもオンとなり、N<sub>3</sub>の電圧がローレベルにジャンプし、T<sub>2</sub>がオンとなり、N<sub>4</sub>の電位がローレベルであり、T<sub>9</sub>がオンとなり、E<sub>0</sub>がハイレベルを出力し、T<sub>3</sub>及びT<sub>10</sub>がいずれもオフとなり。

第5段階P<sub>5</sub>で、E<sub>1</sub>及びC<sub>K</sub>がいずれもローレベルを提供し、C<sub>B</sub>がハイレベルを提供し、T<sub>5</sub>、T<sub>6</sub>及びT<sub>4</sub>がいずれもオンとなり、N<sub>1</sub>の電位及びN<sub>2</sub>の電位はいずれもローレベルであり、T<sub>7</sub>がオフとなり、T<sub>7</sub>及びT<sub>1</sub>がいずれもオンとなり、N<sub>3</sub>の電圧がハイレベルに変化し、T<sub>2</sub>がオフとなり、T<sub>3</sub>がオンとなり、N<sub>4</sub>の電圧がハイレベルに変化し、T<sub>9</sub>がオフとなり、T<sub>10</sub>がオンとなり、E<sub>0</sub>がローレベルを出力し、

第6段階P<sub>6</sub>で、E<sub>1</sub>及びC<sub>B</sub>信号はローレベルであり、C<sub>K</sub>はハイレベルであり、T<sub>1</sub>、T<sub>3</sub>がオフとなり、ノードN<sub>1</sub>がローレベルを保持され、T<sub>2</sub>がオンとなり、N<sub>2</sub>ノードの電圧はハイレベルであり、T<sub>4</sub>、T<sub>5</sub>がオンとなり、T<sub>6</sub>がオフとなり、N<sub>3</sub>ノードはハイレベルであり、T<sub>7</sub>、T<sub>8</sub>がオンとなり、N<sub>4</sub>ノードはハイレベルであり、T<sub>9</sub>がオフとなり、T<sub>10</sub>はオンとなり、E<sub>0</sub>がローレベルを出力する。

#### 【0049】

第7段階P<sub>7</sub>で、E<sub>1</sub>及びC<sub>K</sub>がいずれもローレベルを提供し、C<sub>B</sub>がハイレベルを提供し、T<sub>5</sub>、T<sub>6</sub>及びT<sub>4</sub>がいずれもオンとなり、N<sub>1</sub>の電位及びN<sub>2</sub>の電位はいずれもローレベルであり、T<sub>7</sub>がオフとなり、T<sub>8</sub>及びT<sub>1</sub>がいずれもオンとなり、N<sub>3</sub>の電位はハイレベルであり、T<sub>2</sub>がオフとなり、T<sub>3</sub>がオンとなり、N<sub>4</sub>の電位はハイレベルであり、T<sub>9</sub>がオフとなり、T<sub>10</sub>がオンとなり、E<sub>0</sub>がローレベルを出力し、

#### 【0050】

第8段階P<sub>8</sub>で、E<sub>1</sub>及びC<sub>B</sub>がいずれもローレベルを提供し、C<sub>K</sub>がハイレベルを提供し、T<sub>5</sub>及びT<sub>4</sub>がいずれもオフとなり、N<sub>1</sub>の電位がローレベルに保持され、T<sub>6</sub>がオンとなり、N<sub>2</sub>の電位はハイレベルであり、T<sub>7</sub>がオンとなり、T<sub>8</sub>及びT<sub>1</sub>がいずれもオフとなり、N<sub>3</sub>の電位はハイレベルであり、T<sub>2</sub>及びT<sub>3</sub>がいずれもオンとなり、N<sub>4</sub>の電圧はハイレベルであり、T<sub>9</sub>がオフとなり、T<sub>10</sub>がオンとなり、E<sub>0</sub>がローレベルを出力し、

前記第6段階の後、次のフレームでE<sub>1</sub>が入力信号を受信するまで、T<sub>3</sub>が持続的にオンとなり、T<sub>9</sub>が持続的にオフとなり、T<sub>5</sub>が周期的にC<sub>2</sub>に充電し、N<sub>1</sub>の電位がローレベルに保持され、T<sub>10</sub>が持続的にオンとなり、E<sub>0</sub>がローレベルを出力する。

#### 【0051】

図2Bに示すように、符号J<sub>1</sub>は表示基板であり、符号A<sub>0</sub>は表示領域であり、符号B<sub>1</sub>は第1周辺領域であり、符号B<sub>2</sub>は第2周辺領域である。

#### 【0052】

前記表示基板J<sub>1</sub>の表示領域A<sub>0</sub>に複数本の発光制御線、複数本のゲート線と複数本のデータ線、及び、前記複数本のゲート線と前記複数本のデータ線が交差して限定した複数のサブ画素は設けられていてもよく、

第1周辺領域B<sub>1</sub>及び/または第2周辺領域B<sub>2</sub>に走査駆動回路が設けられていてもよく、前記走査駆動回路は、複数のシフトレジスタユニットを含み、

前記走査駆動回路に含まれる複数のシフトレジスタユニットのうち、各前記シフトレジスタユニットの信号出力線は、それぞれA本の発光制御線に結合されて、対応する発光制御線に発光制御信号を提供することに用いられてもよい。

#### 【0053】

ここで、Aは、正の整数であってもよい。実際の操作において、Aは1、2、3、4であってもよく、または他の正の整数であってもよく、Aの値は実際の状態によって選択し

10

20

30

40

50

てもよい。

#### 【0054】

具体的に実施する時に、前記発光制御線は、相応する行の画素回路の発光制御端に結合される。

選択的に、前記表示基板は、前記ベースに設けられる複数行の画素回路をさらに含み、前記画素回路は発光制御端を含み、

前記走査駆動回路に含まれる前記シフトレジスタユニットは少なくとも一行の前記画素回路に対応され、

前記シフトレジスタユニットの信号出力線は、前記少なくとも一行の画素回路の発光制御端に結合されて、前記少なくとも一行の画素回路の発光制御端に発光制御信号を提供することに用いられる。

#### 【0055】

本開示の少なくとも一実施例では、前記画素回路が表示基板の有効表示領域に設けられてもよく、前記走査駆動回路が表示基板の周辺領域に設けられてもよい。

#### 【0056】

図2Cに示すように、符号Y1は走査駆動回路であり、符号S11は前記走査駆動回路S1に含まれる第1段シフトレジスタユニットであり、符号S12は前記走査駆動回路S1に含まれる第2段シフトレジスタユニットであり、符号S1N-1は前記走査駆動回路S1に含まれる第N-1段シフトレジスタユニットであり、符号S1Nは前記走査駆動回路S1に含まれる第N段シフトレジスタユニットであり、Nは3より大きい整数であり、

図2Cにおいて、符号R1は第1行画素回路であり、符号R2は第2行画素回路であり、符号R3は第3行画素回路であり、符号R4は第4行画素回路であり、符号R2N-3は第2N-3行画素回路であり、符号R2N-2は第2N-2行画素回路であり、符号R2N-1は第2N-1行画素回路であり、符号R2Nは第2N行画素回路であり、

S11がR1及びR2に発光制御信号を提供し、S12がR3及びR4に発光制御信号を提供し、S1N-1がR2N-3及びR2N-2に発光制御信号を提供し、S1NがR2N-1及びR2Nに発光制御信号を提供し、

図2Cに示すように、周辺領域において、前記表示基板は、ゲート電極駆動回路をさらに含んでもよく、前記ゲート電極駆動回路は、複数段のゲート電極駆動ユニットを含み、前記ゲート電極駆動ユニットは画素行に一対一対応されて、相応する行の画素に、相応のゲート電極駆動信号を提供することに用いられてもよく、

図2Cにおいて、符号Y2はゲート電極駆動回路であり、符号S21はゲート電極駆動回路に含まれる第1行ゲート電極駆動ユニットであり、符号S22はゲート電極駆動回路に含まれる第2行ゲート電極駆動ユニットであり、符号S23はゲート電極駆動回路に含まれる第3行ゲート電極駆動ユニットであり、符号S24はゲート電極駆動回路に含まれる第4行ゲート電極駆動ユニットであり、符号S2N-3はゲート電極駆動回路に含まれる第2N-3行ゲート電極駆動ユニットであり、符号S2N-2はゲート電極駆動回路に含まれる第2N-2行ゲート電極駆動ユニットであり、符号S2N-1はゲート電極駆動回路に含まれる第2N-1行ゲート電極駆動ユニットであり、符号S2Nはゲート電極駆動回路に含まれる第2N行ゲート電極駆動ユニットである。

#### 【0057】

図2Dに示した少なくとも一実施例では、第1電圧信号線VGHが高電圧信号Vghを提供し、第2電圧信号線VGLが低電圧信号Vglを提供し、

図2Dに示すように、VGL、VGH、CK及びCBは表示領域から離れていく方向に沿って配列され、VGH、VGL、CK及びCBが第1方向に延在され、

図1及び図2Dに示すように、シフトレジスタユニットの少なくとも一実施例は、第1コンデンサC1、出力コンデンサC2、出力リセットコンデンサC3、出力トランジスタT10、出力リセットトランジスタT9、第1トランジスタT1、第2トランジスタT2、第3トランジスタT3、第4トランジスタT4、第5トランジスタT5、第6トランジスタT6、第7トランジスタT7及び第8トランジスタT8を含み、前記シフトレジスタ

10

20

30

40

50

ユニットの該実施例は、VGHとVGLとの間に設置され、

T10及びT9は第1方向に沿って配列され、

C2は、T10のVGLから離れた側に設けられ、T5、T6及びT4は、C2及びVGHとの間に設けられ、

T1及びT3は、T9のVGLから離れた側に設けられ、C1は、T3のT9から離れた側に設けられ、T8及びT2は、C1のT8から離れた側に設けられ、

T5、T7、T8、T2及びC3が第1方向に沿って順次に配列され、T6、C1及びC3が第1方向に沿って順次に配列され、C2、T1、T3及びC3が第1方向に沿って順次に配列され、

T1は、第1アクティブパターンを含み、T1の第1アクティブパターンが縦方向に配列されて、T2及びT3との間に緊密に配列されることに不利であり、

C3の第2極板C3bの横方向での幅が長くて、シフトレジスタユニットの第2方向での幅を狭めることに不利である。

#### 【0058】

図2Dにおいて、符号E01は信号出力線の第1出力線部分であり、符号E021は信号出力線の1番目の第2出力線部分であり、符号E022は信号出力線の2番目の第2出力線部分であり、E01が第1方向に沿って配列され、E021が第2方向に沿って配列され、E01、E021及びE022は、互いに結合され、第1方向及び第2方向は互いに交差され、E01は、VGLと出力回路（前記出力回路は前記出力トランジスタT10及び前記出力リセットトランジスタT9を含む）との間に設けられ、E021及びE022が第2方向に沿って表示領域へと延在されて、表示領域に位置している画素回路に発光制御信号を提供することを便利にする。

#### 【0059】

図2Dに示すように、S7がD8として兼用される。

#### 【0060】

図2D及び図3Aにおいて、符号G1はT1のゲート電極であり、符号S1はT1の第1電極であり、符号D1はT1の第2電極であり、符号G2はT2のゲート電極であり、符号S2はT2の第1電極であり、符号D2はT2の第2電極であり、符号G3はT3のゲート電極であり、符号S3はT3の第1電極であり、符号D3はT3の第2電極であり、符号G4はT4のゲート電極であり、符号S4はT4の第1電極であり、符号D4はT4の第2電極であり、符号G5はT5のゲート電極であり、符号S5はT5の第1電極であり、符号D5はT5の第2電極であり、符号G6はT6のゲート電極であり、符号S6はT6の第1電極であり、符号D6はT6の第2電極であり、符号G7はT7のゲート電極であり、符号S7はT7の第1電極であり、符号D7はT7の第2電極であり、符号G8はT8のゲート電極であり、符号S8はT8の第1電極であり、符号G9はT9のゲート電極であり、符号S9はT9の第1電極であり、符号D9はT9の第2電極であり、符号G10はT10のゲート電極であり、符号S10はT10の第1電極であり、符号D10はT10の第2電極である。

#### 【0061】

図2Dに示した少なくとも一実施例では、第1方向は上から下に向かう垂直方向であつてもよく、第2方向は右から左に向かう水平方向であつてもよいが、これに限らない。実際の操作において、第1方向は、下から上に向かう垂直方向であつてもよく、第2方向は、左から右に向かう水平方向であつてもよく、もしくは、前記第1方向は他の方向であつてもよく、前記第2方向は他の方向であつてもよい。

#### 【0062】

図2Dに示されるゲート電極駆動回路のレイアウト方式において、T9のアクティブ層及びT9のアクティブ層は一つの連続した第1半導体層により形成され、前記第1半導体層の第1方向での長さが短くて、シフトレジスタユニット全体の縦方向での空間が小さく、そのため、横方向でのシフトレジスタユニットの幅が大きくて、シフトレジスタユニットのうちの素子が水平方向で緊密に配列されることに不利で、表示基板の狭額縫化の発展

10

20

30

40

50

に不利である。

**【 0 0 6 3 】**

図 2 D に示されるシフトレジスタユニットは走査駆動回路に含まれる第 n 段シフトレジスタユニットであってもよく、n は正の整数である。

**【 0 0 6 4 】**

上記の問題点に基づいて、本開示の発明者は、研究を通じて、シフトレジスタユニットのうちの各トランジスタのレイアウト方式を調整することにより、シフトレジスタユニットの占有面積を減らすことで、表示基板の額縁の幅を縮めることができたことを発見した。

**【 0 0 6 5 】**

図 3 A に示されるレイアウト方式において、第 1 電圧信号線 V G H が高電圧信号 V g h を提供し、第 2 電圧信号線 V G L が低電圧信号 V g l を提供し、本開示の少なくとも一実施例では、シフトレジスタユニットは、V G H と V G L との間に設置される。

**【 0 0 6 6 】**

図 3 A において、符号 E 0 1 は信号出力線の第 1 出力線部分であり、符号 E 0 2 1 は信号出力線の 1 番目の第 2 出力線部分であり、符号 E 0 2 2 は信号出力線の 2 番目の第 2 出力線部分であり、E 0 1 が第 1 方向に沿って配列され、E 0 2 1 が第 2 方向に沿って配列され、E 0 1 、E 0 2 1 及び E 0 2 2 は、互いに結合され、第 1 方向及び第 2 方向は互いに交差する。図 3 A に示すように、E 0 1 が V G L と前記出力回路との間に設けられており、E 0 2 1 及び E 0 2 2 が第 2 方向に沿って表示領域へと延在されて、表示領域に位置している画素回路に発光制御信号を提供することを便利にする。

**【 0 0 6 7 】**

例えば、図 3 A に示されるレイアウト方式において、第 1 方向は上から下に向かう垂直方向であってもよく、第 2 方向は右から左に向かう水平方向であってもよいが、これに限らない。

**【 0 0 6 8 】**

図 3 A に示されるシフトレジスタユニットは、走査駆動回路に含まれる第 n 段シフトレジスタユニットであってもよく、n は正の整数である。

**【 0 0 6 9 】**

図 1 及び図 3 A に示すように、シフトレジスタユニットの少なくとも一実施例は、第 1 コンデンサ C 1 、出力コンデンサ C 2 、出力リセットコンデンサ C 3 、出力トランジスタ T 1 0 、出力リセットトランジスタ T 9 、第 1 トランジスタ T 1 、第 2 トランジスタ T 2 、第 3 トランジスタ T 3 、第 4 トランジスタ T 4 、第 5 トランジスタ T 5 、第 6 トランジスタ T 6 、第 7 トランジスタ T 7 及び第 8 トランジスタ T 8 を含み、図 3 A に示すように、出力回路 O 1 は、前記出力トランジスタ T 1 0 及び前記出力リセットトランジスタ T 9 を含み、

前記出力トランジスタ T 1 0 のゲート電極 G 1 0 は、前記出力コンデンサ C 2 の第 1 極板 C 2 a に結合され、前記出力トランジスタ T 1 0 の第 1 電極 S 1 0 は、第 2 電圧信号線 V G L に結合され、前記出力トランジスタ T 1 0 の第 2 電極 D 1 0 は、信号出力線に含まれる第 1 出力線部分 E 0 1 に結合され、

前記出力リセットトランジスタ T 9 のゲート電極 G 9 は、前記出力リセットコンデンサ C 3 の第 1 極板 C 3 a に結合され、前記出力リセットトランジスタ T 9 の第 1 電極 S 9 は、前記出力リセットコンデンサ C 3 の第 2 極板 C 3 b に結合され、前記出力リセットトランジスタ T 9 の第 2 電極 D 9 は、前記信号出力線に含まれる第 1 出力線部分 E 0 1 に結合される。

**【 0 0 7 0 】**

図 3 A に示されるゲート電極駆動回路のレイアウト方式において、T 9 のアクティブ層及び T 1 0 のアクティブ層は、一つの連続した第 1 半導体層により形成されてもよく、前記第 1 半導体層の第 1 方向での長さを引き上げて、シフトレジスタユニットに含まれる他の素子が縦方向で余裕になる空間を利用して、横方向でのシフトレジスタユニットの幅を狭めて、シフトレジスタユニットのうちの素子が水平方向で緊密に配列されることに有利

10

20

30

40

50

で、表示基板の狭額縫化の発展に有利であるようにする。

#### 【0071】

図3Aに示すように、上記構成のシフトレジスタユニットを表示基板の周辺領域にレイアウトを行う場合、表示基板の表示領域から離れていく方向に沿って、第2電圧信号線VGL、第1電圧信号線VGH、第1クロック信号線CK及び第2クロック信号線CBを順次に配列し、第2電圧信号線VGL、第1電圧信号線VGH、第1クロック信号線CK及び第2クロック信号線CBはいずれも第1方向に沿って延在され、

図3Aに示すように、第1コンデンサC1、出力コンデンサC2、出力リセットコンデンサC3、出力トランジスタT10、出力リセットトランジスタT9、第1トランジスタT1、第2トランジスタT2、第3トランジスタT3、第4トランジスタT4、第5トランジスタT5、第6トランジスタT6、第7トランジスタT7及び第8トランジスタT8がいずれもVGHとVGLとの間に設置され、第1半導体層の第1方向で引き上げた長さを利用するため、T5、T6、T4、T7及びT8をいずれも上方に移動して、

T1は、第1アクティブパターンを含み、かつT1の第1アクティブパターンが第2方向に沿って延在されるように設け、T1をT8とC1との間に設け、T8、T1及びC1は第1方向に沿って順次に配列されることで、T8とC1との間の空間を利用してT1を設けて、T2及びT3との間の配列がより緊密にすることができ（前記第2トランジスタT2の第2電極D2が前記第3トランジスタT3の第2電極D2に結合されるので、配線の便宜上、T2及びT3を近く設けることが必要である）、シフトレジスタユニットの占める第2方向での幅をさらに狭めることができ、

そのうえ、図3Aに示されるレイアウト方式において、C1の形状と、T1、T2及びT3の配列される位置とがさらに契合し、T1、T2及びT3の間の空間を利用してC1の極板を設け、

図3Aに示されるレイアウト方式において、C3の第2極板C3bの第2方向での幅を小さく設置し、C3の第2極板C3bの第1方向での長さを大きく設置して、C3の極板の面積を確保することを前提に、C3の極板の占める第2方向での幅を狭め、

図3Aに示すように、C3の第2極板C3bのベースでの正投影がC3の第1極板C3aのベースでの正投影内にある。

#### 【0072】

また、図3A及び図6（図6は図3Aの第1ゲート金属層の概略図である）に示すように、T6のゲート電極G6は、互いに結合される第1ゲート電極パターンG61及び第2ゲート電極パターンG62を含んで、T6をダブルゲート構造として形成する。

#### 【0073】

ダブルゲート構造の設計の目的としては、第2段階P2で、走査駆動回路に含まれるシフトレジスタユニットが高電圧信号Vghを出力する時に、T10が完全にオフとなるべき、T10のゲート電極に印加されるハイレベルがT8のソース電極から入力され、したがって、第2段階P2で、必ずT8がオンとなるように確保し、即ち、第2ノードN2の電位が低電圧にされる必要である一方、第2段階P2で、T6のゲート電極の電位が高電圧になっているので、第2ノードN2の電位上昇をもたらすT6の漏電がないように、設置T6をオフにし易くさせるダブルゲート設計を採用してT6を設定することにある。

#### 【0074】

本開示の少なくとも一実施例では、前記第1方向と前記第2方向は互いに交差され、例えば、前記第1方向が前記第2方向に垂直してもよいが、これに限らない。

#### 【0075】

具体的に、前記第2方向と前記第1方向とが互いに交差する夾角は、実際の必要に応じて設けてもよく、例示として、前記第2方向は前記第1方向に垂直である。

#### 【0076】

本開示の少なくとも一実施例では、第1クロック信号線CBの位置及び前記第2クロック信号線CKの位置は互いに交換してもよいが、これに限らない。

#### 【0077】

10

20

30

40

50

図3Aに示されるレイアウト方式において、図5に示すように（図5は図3Aのアクティブ層の概略図である）、第1半導体層10の第1方向での長さは出力アクティブ長さL1であり、前記第1半導体層10の第2方向での最小の幅は出力アクティブ幅W1であり、前記出力アクティブ長さL1は、第1所定の長さであり、

前記出力アクティブ長さL1及び前記出力アクティブ幅W1の割合が所定割合の範囲内にあり、

前記出力アクティブ幅W1は所定の幅の範囲にあり、

本開示の少なくとも一実施例前記出力アクティブ長さL1を上げることで、シフトレジスタユニットのうち、出力回路以外の素子はL1が大きくなつて縦方向で余裕になる空間を利用してレイアウトを行うことができ、その上シフトレジスタユニットの占める横方向の空間を縮めることができ、かつ本開示の少なくとも一実施例では、前記出力アクティブ幅W1を減らすことができ、水平方向での空間を省き、残すべきところを、シフトレジスタユニットのうち、出力回路以外の素子が利用してレイアウトを行うことができるようになり、シフトレジスタユニットの占める横方向の空間も縮めることができる。

#### 【0078】

本開示の少なくとも一実施例では、前記所定割合の範囲は、3以上かつ11以下であつてもよいが、これに限らない。

#### 【0079】

本開示の少なくとも一実施例では、前記所定の幅の範囲は、12μm以上かつ45μm以下でもよいが、これに限らない。

#### 【0080】

本開示の少なくとも一実施例では、前記第1所定の長さは、50μm以上かつ130μm以下でもよいが、これに限らない。

#### 【0081】

図3A及び図8に示すように、前記第1出力線部分E01は、信号線の重なり領域に設けられた複数の第1信号線ビアホールH01を介して前記出力トランジスタT10の第2電極D10に結合され、前記第1出力線部分E01は、前記信号線の重なり領域に設けられた複数の第2信号線ビアホールH02を介して前記出力リセットトランジスタT9の第2電極D9に結合され、前記複数の第1信号線ビアホールH01は第1方向に沿つて順次に配列され、前記複数の第2信号線ビアホールH02が第1方向に沿つて順次に配列され、

図4及び図10（図10は図3Aのソース・ドレイン金属層の概略図であり、図10に第1ソース・ドレイン金属パターンDs1及び第2ソース・ドレイン金属パターンDs2を示す）に示すように、前記信号線の重なり領域は、第1信号線の重なり領域A01及び第2信号線の重なり領域A02を含み、前記第1信号線の重なり領域A01は、前記第1出力線部分E01の前記ベースでの正投影と、前記出力トランジスタT10の第2電極D10が含まれる第1ソース・ドレイン金属パターンDs1の前記ベースでの正投影との重なり領域であり、前記第2信号線の重なり領域A02は、前記第1出力線部分E01の前記ベースでの正投影と、前記出力リセットトランジスタT9の第2電極D9が含まれる第2ソース・ドレイン金属パターンDs2の前記ベースでの正投影との重なり領域であり、

図4及び図10に示すように、第1方向に沿つて順次に配列される1番目の第1信号線ビアホールと最後の一つの第1信号線ビアホールとの第1方向での最大距離K1と、第3長さL3との割合は、第3所定割合であり、二つの隣接する第1信号線ビアホールの間の第1方向での最小距離は、第1所定距離であり、前記第3長さL3は、前記第1信号線の重なり領域A01の第1方向での長さであり、

第1方向に沿つて順次に配列される1番目の第2信号線ビアホールと最後の一つの第2信号線ビアホールとの第1方向での最大距離K2と、第4長さL4との割合は、第4所定割合であり、二つの隣接する第2信号線ビアホールの間の第1方向での最小距離は、第2所定距離であり、前記第4長さL4は、前記第2信号線の重なり領域A02の第1方向での長さである。

#### 【0082】

10

20

30

40

50

本開示の少なくとも一実施例では、前記第1信号線ピアホールの数及び前記第2信号線ピアホールの数は実際の状態によって選択してもよい。

#### 【0083】

本開示の少なくとも一実施例では、第1方向に沿って順次に配列されるいずれか二つの第1信号線ピアホールの第1方向での最大距離というのは、いずれか二つの第1信号線ピアホールのベースでの正投影の周辺との間の第1方向での最大距離であり、

第1方向に沿って順次に配列される1番目の第1信号線ピアホールと最後の一つの第1信号線ピアホールとの第1方向での最大距離K1というのは、前記1番目の第1信号線ピアホールのベースでの正投影の周辺と、前記最後の一つの第1信号線ピアホールのベースでの正投影の周辺との間の第1方向での最大距離であり、

二つの隣接する第1信号線ピアホールの間の第1方向での最小距離K01とは、二つの隣接する第1信号線ピアホールのベースでの正投影の周辺の第1方向での最小距離であり、

第1方向に沿って順次に配列される1番目の第2信号線ピアホールと最後の一つの第2信号線ピアホールとの第1方向での最大距離K2というのは、前記1番目の第2信号線ピアホールのベースでの正投影の周辺と、前記最後の一つの第2信号線ピアホールのベースでの正投影の周辺との間の第1方向での最大距離であり、

第1方向に沿って順次に配列されるいずれか二つの第2信号線ピアホールの第1方向での最大距離というのは、いずれか二つの第2信号線ピアホールのベースでの正投影の周辺との間の第1方向での最大距離であり、

二つの隣接する第2信号線ピアホールの間の第1方向での最小距離K02というのは、二つの隣接する第2信号線ピアホールのベースでの正投影の周辺の第1方向での最小距離である。

#### 【0084】

本開示の少なくとも一実施例では、前記第1所定割合は0.05以上かつ0.9以下であってもよいが、これに限らず、

前記第1所定距離は、1.5μm以上かつ4.5μm以下であってもよいが、これに限らず、

前記第2所定割合は、0.05以上かつ0.9以下であってもよいが、これに限らず、

前記第2所定距離は、1.5μm以上かつ6.5μm以下であってもよいが、これに限らない。

#### 【0085】

図3A、図4及び図10に示すように、T10のアクティブ層及びT9のアクティブ層が縦方向で長められるので、それに伴い、第3長さL3及び第4長さL4が長くなり、これにより複数の第1信号線ピアホールH01が第1信号線の重なり領域A01に均一に配列され得、かつ上から下の1番目の第1信号線ピアホールと上から下の最後の一つの第1信号線ピアホールとの第1方向での最大距離K1と、第3長さL3との割合は、第3所定割合であり、前記複数の第1信号線ピアホールH01が前記第1信号線の重なり領域A01にできるだけ張り詰め得、出力トランジスタT10の第2電極D10をより良好にE01に結合させることができ、

図3A、図4及び図10に示すように、T10のアクティブ層及びT9のアクティブ層が縦方向で長められるので、それに伴い、第3長さL3及び第4長さL4が長くなり、これにより複数の第2信号線ピアホールH02が第2信号線の重なり領域A02に均一に配列され得、かつ上から下の1番目の第2信号線ピアホールと上から下の最後の一つの第2信号線ピアホールとの第1方向での最大距離K2と、第4長さL4との割合が第4所定割合であり、前記複数の第2信号線ピアホールH02が前記第2信号線の重なり領域A02にできるだけ張り詰め得、出力リセットトランジスタT9の第2電極D9をより良好にE01に結合させることができる。

#### 【0086】

本開示の少なくとも一実施例では、前記第3所定割合は、0.05以上かつ0.9以下であってもよく、前記第4所定割合は、0.05以上かつ0.9以下であってもよいが、

10

20

30

40

50

これに限らない。

#### 【0087】

本開示の少なくとも一実施例に記載の表示基板は、ベースに設けられている走査駆動回路及び表示領域を含み、前記走査駆動回路は、複数のシフトレジスタユニットを含み、前記複数のシフトレジスタユニットのうち、少なくとも一つのシフトレジスタユニットは、信号出力線及び出力回路を含み、前記出力回路は、出力トランジスタ及び出力リセットトランジスタを含み、

前記信号出力線は、第1方向に沿って延在される第1出力線部分を含み、

前記第1出力線部分は、信号線の重なり領域に設けられた複数の第1信号線ビアホールを介して前記出力トランジスタの第2電極に結合され、前記第1出力線部分は、前記信号線の重なり領域に設けられた複数の第2信号線ビアホールを介して前記出力リセットトランジスタの第2電極に結合され、前記複数の第1信号線ビアホールが第1方向に沿って順次に配列され、前記複数の第2信号線ビアホールが第1方向に沿って順次に配列され、

前記信号線の重なり領域は、第1信号線の重なり領域及び第2信号線の重なり領域を含み、前記第1信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力トランジスタの第2電極が含まれる第1ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、前記第2信号線の重なり領域は、前記第1出力線部分の前記ベースでの正投影と、前記出力リセットトランジスタの第2電極が含まれる第2ソース・ドレイン金属パターンの前記ベースでの正投影との重なり領域であり、

第1方向に沿って順次に配列されるいずれか二つの第1信号線ビアホールの第1方向での最大距離と第3長さとの割合が第1所定割合であり、二つの隣接する第1信号線ビアホールの間の第1方向での最小距離が第1所定距離であり、前記第3長さが、前記第1信号線の重なり領域の第1方向での長さであり、

第1方向に沿って順次に配列されるいずれか二つの第2信号線ビアホールの第1方向での最大距離と第4長さとの割合が第2所定割合であり、二つの隣接する第2信号線ビアホールの間の第1方向での最小距離が第2所定距離であり、前記第4長さが、前記第2信号線の重なり領域の第1方向での長さであり、

前記第1所定割合が0.05以上かつ0.9以下であり、

前記第1所定距離が1.5μm以上かつ4.5μm以下であり、

前記第2所定割合が0.05以上かつ0.9以下であり、

前記第2所定距離が1.5μm以上かつ6.5μm以下である。

#### 【0088】

選択的に、前記出力トランジスタのアクティブ層及び前記出力リセットトランジスタのアクティブ層は、第1方向に沿って配列され、前記出力トランジスタのアクティブ層の前記第1方向での長さを第1長さとして、前記出力リセットトランジスタのアクティブ層の前記第1方向での長さを第2長さとして、前記第1長さと前記第2長さとの和が出力アクティブ長さであり、

前記出力トランジスタのアクティブ層の第2方向に沿う最小の幅と、前記出力リセットトランジスタのアクティブ層の第2方向に沿う最小の幅とのうち、小さいものを出力アクティブ幅とし、前記第1方向と前記第2方向は互いに交差する。

#### 【0089】

本開示の少なくとも一実施例では、前記出力アクティブ長さと前記出力アクティブ幅との割合が所定割合の範囲内にあり、前記所定割合の範囲は、3以上かつ1.1以下であってもよいが、これに限らない。

#### 【0090】

本開示の少なくとも一実施例において、前記出力アクティブ長さを上げることで、シフトレジスタユニットのうち、出力回路以外の素子が出力アクティブ長さが大きくなつて縦方向で余裕になる空間を利用してレイアウトを行うことができ、その上、シフトレジスタユニットの占める横方向の空間を縮めることができる。しかも、本開示の少なくとも一実施例では、出力トランジスタのアクティブ層及び出力リセットトランジスタのアクティブ

10

20

30

40

50

層が縦方向で長められるので、それに伴い、第3長さ及び第4長さが長くなり、これにより複数の第1信号線ビアホールが第1信号線の重なり領域に均一に配列され得、かついずれか二つの第1信号線ビアホールの第1方向での最大距離と、第3長さとの割合が第1所定割合であり、前記複数の第1信号線ビアホールが前記第1信号線の重なり領域にできるだけ張り詰め得、出力トランジスタの第2電極をより良好に第1出力線部分に結合させることができ、

図3A、図4及び図10に示すように、出力トランジスタのアクティプ層及び出力リセットトランジスタのアクティプ層が縦方向で長められるので、それに伴い、第3長さ及び第4長さが長くなり、これにより複数の第2信号線ビアホールが第2信号線の重なり領域に均一に配列され得、かつ上から下のいずれか二つの第2信号線ビアホールの第1方向での最大距離と、第4長さとの割合が第2所定割合であり、前記複数の第2信号線ビアホールが前記第2信号線の重なり領域にできるだけ張り詰め得、出力リセットトランジスタの第2電極をより良好に第1出力線部分に結合させることができる。

10

#### 【0091】

本開示の少なくとも一実施例では、前記出力アクティプ幅は、所定の幅の範囲にあってもよい。

#### 【0092】

本開示の少なくとも一実施例では、前記出力アクティプ幅を減らすことができ、水平方向での空間を省き、残すべきところを、シフトレジスタユニットのうち、出力回路以外の素子が利用してレイアウトを行うことができるようにして、シフトレジスタユニットの占める横方向の空間を縮めることもできる。

20

#### 【0093】

選択的に、図3A及び図5に示すように、前記出力トランジスタT10のアクティプ層及び前記出力リセットトランジスタT9のアクティプ層は一つの連続した第1半導体層により形成されてもよく、前記第1半導体層は第1方向10に沿って延在され、

図5に示すように、前記第1半導体層10の第1方向での長さは出力アクティプ長さL1であり、

前記第1半導体層10の第2方向での最小長さは、前記出力アクティプ長さW1であり。

#### 【0094】

図3Aに示すように、前記出力トランジスタT10及び前記出力リセットトランジスタT9は第1方向に沿って順次に配列されているが、これに限らず、実際の操作において、出力リセットトランジスタT9及び出力トランジスタT10は第1方向に沿って順次に配列するように設置されてもよい。

30

#### 【0095】

本開示の少なくとも一実施例では、出力リセットトランジスタT9は無効の発光制御信号を提供することに用いられ、出力トランジスタT10は有效の発光制御信号を提供することに用いられる。

#### 【0096】

本開示の少なくとも一実施例では、前記有效の発光制御信号は画素回路のうち、発光制御トランジスタをオンとすることができますの電圧信号であってもよく（前記発光制御トランジスタのゲート電極は、前記発光制御線に結合され）、前記無効の発光制御信号は、前記発光制御トランジスタをオフとすることができますの電圧信号であってもよい。

40

#### 【0097】

具体的に、前記表示基板の表示領域は、複数のサブ画素を含み、前記複数のサブ画素のうち、少なくとも一つのサブ画素は、画素駆動回路を含み、前記画素駆動回路は、トランジスタ、ゲート線、発光制御線及びデータ線を含み、前記走査駆動回路に含まれるシフトレジスタユニットは、少なくとも一本の発光制御線に対応してもよく、各前記シフトレジスタユニットの信号出力線は、対応する少なくとも一本の発光制御線に結合されて、対応する発光制御線に発光制御信号を提供することに用いられる。

#### 【0098】

本開示の少なくとも一実施例では、前記出力トランジスタのアクティブ層及び前記リセットトランジスタのアクティブ層は一つの連続した第1半導体層により形成されてもよく、

前記出力トランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第1導電部分及び少なくとも一つの第1チャネル部分を含んでもよく、それぞれの前記第1チャネル部分は二つの隣接する前記第1導電部分の間に設けられており、

前記出力リセットトランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第2導電部分及び少なくとも一つの第2チャネル部分を含んでもよく、それぞれの前記第2チャネル部分は二つの隣接する前記第2導電部分の間に設けられており、

前記出力トランジスタのアクティブ層で前記出力リセットトランジスタのアクティブ層との距離が最も近い第1導電部分は、前記出力リセットトランジスタのうちの第2導電部分として兼用されてもよく、これにより前記出力トランジスタ及び出力リセットトランジスタのレイアウト空間をさらに縮めることができ、前記表示基板の狭額縁化を実現することに有利であるようにする。

#### 【0099】

図5に示すように、前記出力トランジスタT10のアクティブ層及び前記出力リセットトランジスタT9のアクティブ層は一つの連続した第1半導体層により形成されてもよく、

前記出力トランジスタT10のアクティブ層は、第1方向に沿って対向して設けられる1番目の第1導電部分111、2番目の第1導電部分112、3番目の第1導電部分113、4番目の第1導電部分114、5番目の第1導電部分115及び6番目の第1導電部分116を含み、前記出力トランジスタT10のアクティブ層は、1番目の第1チャネル部分121、2番目の第1チャネル部分122、3番目の第1チャネル部分123、4番目の第1チャネル部分124及び5番目の第1チャネル部分125をさらに含み、

前記1番目の第1チャネル部分121は、前記1番目の第1導電部分111と前記2番目の第1導電部分112との間に設けられており、前記2番目の第1チャネル部分122は、前記2番目の第1導電部分112と前記3番目の第1導電部分113との間に設けられており、

前記3番目の第1チャネル部分123は、前記3番目の第1導電部分113及び前記2番目の第4導電部分114との間に設けられており、前記4番目の第1チャネル部分124は、前記4番目の第1導電部分114と前記5番目の第1導電部分115との間に設けられており、前記5番目の第1チャネル部分125は、前記5番目の第1導電部分115と前記6番目の第1導電部分116との間に設けられており、

前記6番目の第1導電部分116は、前記出力リセットトランジスタT9のアクティブ層に含まれる1番目の第2導電部分として兼用され、

前記出力リセットトランジスタT9のアクティブ層は、第1方向に沿って対向して設けられる2番目の第2導電部分132、3番目の第2導電部分133、4番目の第2導電部分134、5番目の第2導電部分135及び6番目の第2導電部分136をさらに含み、前記出力リセットトランジスタT9のアクティブ層は、1番目の第2チャネル部分141、2番目の第2チャネル部分142、3番目の第2チャネル部分143、4番目の第2チャネル部分144及び5番目の第2チャネル部分145をさらに含み、

前記1番目の第2チャネル部分141は、1番目の第2導電部分と2番目の第2導電部分132との間に設けられており、前記2番目の第2チャネル部分142は、前記2番目の第2導電部分132と3番目の第2導電部分133との間に設けられており、前記3番目の第2チャネル部分143は、3番目の第2導電部分133と4番目の第2導電部分134との間に設けられており、前記4番目の第2チャネル部分144は、前記4番目の第2導電部分134と5番目の第2導電部分135との間に設けられている、前記5番目の第2チャネル部分145は、前記5番目の第2導電部分135と6番目の第2導電部分136との間に設けられている。

#### 【0100】

前記出力トランジスタT10及び前記出力リセットトランジスタT9において、各トランジ

10

20

30

40

50

ンジスタのチャネル部分の両側の導電部分は、それぞれ対応して、該トランジスタの第1電極、第2電極としてもよく、もしくはそれぞれ該トランジスタの第1電極、該トランジスタの第2電極に結合されてもよく、これによりT10及びT9が6番目の第1導電部分116を介して電気的接続を実現可能にする。

#### 【0101】

前記第1半導体層10を製作する時に、例示として、まず、第1半導体材料層を形成した後に、出力トランジスタT10のゲート電極G10及び出カリセットトランジスタT9のゲート電極G9を形成してから、前記第1半導体材料層のうち、各トランジスタのゲート電極により被覆されていない部分が前記導電部分として形成されるよう、前記第1半導体材料層のうち、各トランジスタにより被覆されている部分が前記チャネル部分として形成されるように、出力トランジスタT10のゲート電極G10及び出カリセットトランジスタT9のゲート電極G9をマスクとして、第1半導体材料層のうち、各トランジスタのゲート電極により被覆されていない部分に対してドーピングを行ってもよい。

10

#### 【0102】

上記の表示基板の具体的な構成によって、本開示の少なくとも一実施例に記載の表示基板において、シフトレジスタユニットのうち、前記出力トランジスタT10及び出カリセットトランジスタT9が前記第1方向に沿って配列され得、シフトレジスタユニットの占める第2方向での面積を縮め、前記表示基板を狭額縁化の発展要求にさらに符合させることができる。

#### 【0103】

具体的に、前記出力トランジスタのゲート電極は、少なくとも一つの出力ゲート電極パターンを含んでもよく、前記出力トランジスタの第1電極は、少なくとも一つの第1電極パターンを含み、前記出力トランジスタの第2電極は、少なくとも一つの第2電極パターンを含み、

20

前記出力ゲート電極パターンは、隣接する前記第1電極パターンと前記第2電極パターンとの間に位置しており、

前記第1電極パターン、前記出力ゲート電極パターン及び前記第2電極パターンはいずれも第2方向に沿って延在されている。

#### 【0104】

具体的に、前記出カリセットトランジスタのゲート電極は、少なくとも一つの出カリセットゲート電極パターンを含んでもよく、前記出カリセットトランジスタの第1電極は、少なくとも一つの第3電極パターンを含み、前記出カリセットトランジスタの第2電極は、少なくとも一つの第4電極パターンを含み、

30

前記出カリセットゲート電極パターンは、隣接する前記第3電極パターンと前記第4電極パターンとの間に位置しており、

前記第3電極パターン、前記出カリセットゲート電極パターン及び前記第4電極パターンはいずれも第2方向に沿って延在され、

前記出カリセットトランジスタのうち、前記出力トランジスタのゲート電極に最も近接する前記第4電極パターンが前記出力トランジスタの第2電極パターンとして兼用される。

#### 【0105】

具体的に実施する時に、前記出カリセットゲート電極パターンの数量、前記第1電極パターンの数量、前記第2電極パターンの数量、前記出力ゲート電極パターンの数量、前記第3電極パターンの数量及び前記第4電極パターンの数量は、実際の必要に応じて設けられてもよい。例示として、図6及び図9に示すように、前記出力ゲート電極パターンの数量及び前記出カリセットゲート電極パターンの数量は、五つであってもよく、第1電極パターンの数量は、三つであってもよく、第2電極パターンの数量は、三つであってもよく、第3電極パターンの数量は、三つであってもよく、前記第4電極パターンの数量は、三つであってもよいが、これに限らない。

40

#### 【0106】

また、前記出力トランジスタの第2電極及び出カリセットトランジスタの第2電極はい

50

ずれも信号出力線に結合されるので、出力トランジスタ及び出カリセットトランジスタをレイアウトを行う時に、前記出カリセットトランジスタのうち、前記出力トランジスタのゲート電極に最も近接する前記第4電極パターンが前記出力トランジスタの第2電極パターンとして兼用されてもよく、これにより、出力トランジスタ及び出カリセットトランジスタのレイアウト空間をさらに縮めることができ、表示基板の狭額縁化を実現することに有利であるようにする。

#### 【0107】

図3A及び図6に示すように、いくつの実施例では、前記出力トランジスタT10のゲート電極は、第1出力ゲート電極パターンG101、第2出力ゲート電極パターンG102、第3出力ゲート電極パターンG103、第4出力ゲート電極パターンG104及び第5出力ゲート電極パターンG105を含んでもよく、

前記出カリセットトランジスタT9のゲート電極は、第1出カリセットゲート電極パターンG91、第2出カリセットゲート電極パターンG92、第3出カリセットゲート電極パターンG93、第4出カリセットゲート電極パターンG94及び第5出カリセットゲート電極パターンG95を含んでもよく、

第1出力ゲート電極パターンG101、第2出力ゲート電極パターンG102、第3出力ゲート電極パターンG103、第4出力ゲート電極パターンG104及び第5出力ゲート電極パターンG105が第1方向に沿って順次に配列され、

第1出カリセットゲート電極パターンG91、第2出カリセットゲート電極パターンG92、第3出カリセットゲート電極パターンG93、第4出カリセットゲート電極パターンG94及び第5出カリセットゲート電極パターンG95が第1方向に沿って順次に配列され、

第1出力ゲート電極パターンG101、第2出力ゲート電極パターンG102、第3出力ゲート電極パターンG103、第4出力ゲート電極パターンG104及び第5出力ゲート電極パターンG105がいずれも第2方向に沿って延在され、第1方向と第2方向は互いに交差され、

第1出力ゲート電極パターンG101、第2出力ゲート電極パターンG102、第3出力ゲート電極パターンG103、第4出力ゲート電極パターンG104及び第5出力ゲート電極パターンG105が互いに結合され、

第1出カリセットゲート電極パターンG91、第2出カリセットゲート電極パターンG92、第3出カリセットゲート電極パターンG93、第4出カリセットゲート電極パターンG94及び第5出カリセットゲート電極パターンG95がいずれも第2方向に沿って延在され、

第1出カリセットゲート電極パターンG91、第2出カリセットゲート電極パターンG92、第3出カリセットゲート電極パターンG93、第4出カリセットゲート電極パターンG94及び第5出カリセットゲート電極パターンG95が互いに結合され、

図9に示すように、前記出力トランジスタT10の第1電極S10は、1番目の第1電極パターンS101、2番目の第1電極パターンS102及び3番目の第1電極パターンS103を含み、

前記出力トランジスタT10の第2電極D10は、1番目の第2電極パターンD101及び2番目の第2電極パターンD102を含み、

前記出カリセットトランジスタT9の第1電極S9は、1番目の第3電極パターンS91、2番目の第3電極パターンS92及び3番目の第3電極パターンS93、

前記出カリセットトランジスタT9の第2電極D9は、1番目の第4電極パターンD91、2番目の第4電極パターンD92及び3番目の第4電極パターンD93を含み、

1番目の第4電極パターンD91が前記出力トランジスタT10に含まれる3番目の第2電極パターンとして兼用され、

図3A～図10に示すように、S101がVGLに結合され、S101がS102に結合され、S103がVGLに結合され、S91、S92及びS93がそれぞれ第1導電接続部F1に結合され、前記第1導電接続部F1が前記第1電圧信号線VGHに結合され、

10

20

30

40

50

図3A～図10に示すように、前記第1出力線部分E01が信号線の重なり領域に設けられた複数の第1信号線ビアホールH01を介してそれぞれD101及びD102に結合され、前記第1出力線部分E01は、信号線の重なり領域に設けられた複数の第2信号線ビアホールH02を介してそれぞれD91、D92及びD93に結合され、

前記複数の第1信号線ビアホールH01が第1方向に沿って順次に配列され、前記複数の第2信号線ビアホールH02が第1方向に沿って順次に配列される。

#### 【0108】

具体的に実施する時に、前記出力トランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第1導電部分及び少なくとも一つの第1チャネル部分を含んでもよく、それぞれの前記第1チャネル部分は、二つの隣接する前記第1導電部分の間に設けられており、

前記第1チャネル部分は、前記出力ゲート電極パターンに一対一対応され、各前記第1チャネル部分の前記ベースでの正投影は、いずれも対応する前記出力ゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力トランジスタのうちの一部の前記第1導電部分が前記第1電極パターンに一対一対応され、前記第1電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第1重なり領域を有し、前記第1電極パターンは前記第1重なり領域に設けられている少なくとも一つの第1ビアホールを介して対応する前記第1導電部分に結合され、

前記出力トランジスタのうちの他の一部の前記第1導電部分が前記第2電極パターンに一対一対応され、前記第2電極パターンの前記ベースでの正投影と、対応する前記第1導電部分の前記ベースでの正投影とが第2重なり領域を有し、前記第2電極パターンは前記第2重なり領域に設けられている少なくとも一つの第2ビアホールを介して対応する前記第1導電部分に結合される。

#### 【0109】

具体的に実施する時に、前記出力リセットトランジスタのアクティブ層は、第1方向に沿って対向して設けられる少なくとも二つの第2導電部分及び少なくとも一つの第2チャネル部分を含み、それぞれの前記第2チャネル部分は二つの隣接する前記第2導電部分の間に設けられており、

前記第2チャネル部分は、前記出力リセットゲート電極パターンに一対一対応され、各前記第2チャネル部分の前記ベースでの正投影は、いずれも対応する前記出力リセットゲート電極パターンの前記ベースでの正投影の内部に位置しており、

前記出力リセットトランジスタのうちの一部の前記第2導電部分が前記第3電極パターンに一対一対応され、前記第3電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第3重なり領域を有し、前記第3電極パターンは、前記第3重なり領域に設けられている少なくとも一つの第3ビアホールを介して対応する前記第2導電部分に結合され、

前記出力リセットトランジスタのうちの他の一部の前記第2導電部分が前記第4電極パターンに一対一対応され、前記第4電極パターンの前記ベースでの正投影と、対応する前記第2導電部分の前記ベースでの正投影とが第4重なり領域を有し、前記第4電極パターンは、前記第4重なり領域に設けられている少なくとも一つの第4ビアホールを介して対応する前記第2導電部分に結合される。

#### 【0110】

図5、図6、図8及び図9に示すように、1番目の第1チャネル部分121が第1出力ゲート電極パターンG101に対応され、2番目の第1チャネル部分122が第2出力ゲート電極パターンG102に対応され、3番目の第1チャネル部分123が第3出力ゲート電極パターンG103に対応され、4番目の第1チャネル部分124が第4出力ゲート電極パターンG104に対応され、5番目の第1チャネル部分125が第5出力ゲート電極パターンG105に対応され、

1番目の第1チャネル部分121のベースでの正投影は、第1出力ゲート電極パターン

10

20

30

40

50

G 1 0 1 のベースでの正投影の内部に位置しており、

2 番目の第 1 チャネル部分 1 2 2 のベースでの正投影は、第 2 出力ゲート電極パターン G 1 0 2 のベースでの正投影の内部に位置しており、

3 番目の第 1 チャネル部分 1 2 3 のベースでの正投影は、第 3 出力ゲート電極パターン G 1 0 3 のベースでの正投影の内部に位置しており、

4 番目の第 1 チャネル部分 1 2 4 のベースでの正投影は、第 4 出力ゲート電極パターン G 1 0 4 のベースでの正投影の内部に位置しており、

5 番目の第 1 チャネル部分 1 2 5 のベースでの正投影は、第 5 出力ゲート電極パターン G 1 0 5 のベースでの正投影の内部に位置しており、

1 番目の第 1 導電部分 1 1 1 が 1 番目の第 1 電極パターン S 1 0 1 に対応され、2 番目の第 1 導電部分 1 1 2 が 1 番目の第 2 電極パターン D 1 0 1 に対応され、3 番目の第 1 導電部分 1 1 3 が 2 番目の第 1 電極パターン S 1 0 2 に対応され、4 番目の第 1 導電部分 1 1 4 が 2 番目の第 2 電極パターン D 1 0 2 に対応され、5 番目の第 1 導電部分 1 1 5 が 3 番目の第 1 電極パターン S 1 0 3 に対応され、6 番目の第 1 導電部分 1 1 6 が 1 番目の第 4 電極パターン D 9 1 に対応され、

前記 6 番目の第 1 導電部分 1 1 6 は、前記出力リセットトランジスタ T 9 のアクティブ層に含まれる 1 番目の第 2 導電部分として兼用され、

1 番目の第 2 チャネル部分 1 4 1 が第 1 出力リセットゲート電極パターン G 9 1 に対応され、2 番目の第 2 チャネル部分 1 4 2 が第 2 出力リセットゲート電極パターン G 9 2 に対応され、3 番目の第 2 チャネル部分 1 4 3 が第 3 出力リセットゲート電極パターン G 9 3 に対応され、4 番目の第 2 チャネル部分 1 4 4 が第 4 出力リセットゲート電極パターン G 9 4 に対応され、5 番目の第 2 チャネル部分 1 4 5 が第 5 出力リセットゲート電極パターン G 9 5 に対応され、

1 番目の第 2 チャネル部分 1 4 1 のベースでの正投影は、第 1 出力リセットゲート電極パターン G 9 1 のベースでの正投影の内部に位置しており、

2 番目の第 2 チャネル部分 1 4 2 のベースでの正投影は、第 2 出力リセットゲート電極パターン G 9 2 のベースでの正投影の内部に位置しており、

3 番目の第 2 チャネル部分 1 4 3 のベースでの正投影は、第 3 出力リセットゲート電極パターン G 9 3 のベースでの正投影の内部に位置しており、

4 番目の第 2 チャネル部分 1 4 4 のベースでの正投影は、第 4 出力リセットゲート電極パターン G 9 4 のベースでの正投影の内部に位置しており、

5 番目の第 2 チャネル部分 1 4 5 のベースでの正投影は、第 5 出力リセットゲート電極パターン G 9 5 のベースでの正投影の内部に位置しており、

2 番目の第 2 導電部分 1 3 2 が 1 番目の第 3 電極パターン S 9 1 に対応され、3 番目の第 2 導電部分 1 3 3 が 2 番目の第 4 電極パターン D 9 2 に対応され、4 番目の第 2 導電部分 1 3 4 が 2 番目の第 3 電極パターン S 9 2 に対応され、5 番目の第 2 導電部分 1 3 5 が 3 番目の第 4 電極パターン D 9 3 に対応され、6 番目の第 2 導電部分 1 3 6 が 3 番目の第 3 電極パターン S 9 3 に対応され、

S 1 0 1 のベースでの正投影と、1 番目の第 1 導電部分 1 1 1 のベースでの正投影との間に 1 番目の第 1 重なり領域を有し、S 1 0 2 のベースでの正投影と、3 番目の第 1 導電部分 1 1 3 のベースでの正投影との間に 2 番目の第 1 重なり領域を有し、S 1 0 3 のベースでの正投影と、5 番目の第 1 導電部分 1 1 5 のベースでの正投影との間に 3 番目の第 1 重なり領域を有し、S 1 0 1 は、1 番目の第 1 重なり領域に設けられている第 1 ビアホール H 1 を介して 1 番目の第 1 導電部分 1 1 1 に結合され、S 1 0 2 は、2 番目の第 1 重なり領域に設けられている第 1 ビアホール H 1 を介して 3 番目の第 1 導電部分 1 1 3 に結合され、S 1 0 3 は、3 番目の第 1 重なり領域に設けられている第 1 ビアホール H 1 を介して 5 番目の第 1 導電部分 1 1 5 に結合され、

D 1 0 1 のベースでの正投影と、2 番目の第 1 導電部分 1 1 2 のベースでの正投影との間に存在 1 番目の第 2 重なり領域を有し、D 1 0 2 のベースでの正投影と、4 番目の第 1 導電部分 1 1 4 との間に 2 番目の第 2 重なり領域を有し、D 1 0 1 は、1 番目の第 2 重な

10

20

30

40

50

り領域に設けられている第2ビアホールH2を介して2番目の第1導電部分112に結合され、D102は、2番目の第2重なり領域に設けられている第2ビアホールH2を介して4番目の第1導電部分114に結合され、

D91のベースでの正投影と、1番目の第2導電部分131のベースでの正投影との間に1番目の第4重なり領域を有し、D92のベースでの正投影と、3番目の第2導電部分133のベースでの正投影との間に2番目の第4重なり領域を有し、D93のベースでの正投影と、5番目の第2導電部分135との間に3番目の第4重なり領域を有し、D91は、1番目の第4重なり領域に設けられている第4ビアホールH4を介して1番目の第2導電部分131に結合され、D92は、2番目の第4重なり領域に設けられている第4ビアホールH4を介して3番目の第2導電部分133に結合され、D93は、3番目の第4重なり領域に設けられている第4ビアホールH4を介して5番目の第2導電部分133に結合され、

S91のベースでの正投影と、2番目の第2導電部分132のベースでの正投影との間に1番目の第3重なり領域を有し、S92のベースでの正投影と、4番目の第2導電部分134のベースでの正投影との間に2番目の第3重なり領域を有し、S93のベースでの正投影と、6番目の第2導電部分136のベースでの正投影との間に3番目の第3重なり領域を有し、S91は、1番目の第3重なり領域に設けられている第3ビアホールH3を介して2番目の第2導電部分132に結合され、S92は、2番目の第3重なり領域に設けられている第3ビアホールH3を介して4番目の第2導電部分134に結合され、S93は、3番目の第3重なり領域に設けられている第3ビアホールH3を介して6番目の第2導電部分136に結合される。

#### 【0111】

本開示の少なくとも一実施例では、第1ビアホールの数量、第2ビアホールの数量、第3ビアホールの数量及び第4ビアホールの数量は、実際の必要に応じて設けてもよい。

#### 【0112】

図3Aに示されるレイアウト方式において、第1ビアホールの数量、第2ビアホールの数量、第3ビアホールの数量はいずれも三つであるが、実際の操作において、以上の各ビアホールの数量は実際の状態によって選択してもよく、例えば、図11に示すように、他のレイアウト方式において、第1ビアホールの数量、第2ビアホールの数量、第3ビアホールの数量はいずれも二つであってもよく、図11に示されるレイアウト方式において、第1半導体層の第1方向での長さがより長く（図3Aに示されるレイアウト方式に比べ）、第1半導体層の第2方向での幅がより狭く（図3Aに示されるレイアウト方式に比べ）、シフトレジスタユニットの占める第2方向での幅を狭めることに寄与し、狭額縁の実現に有利である。

#### 【0113】

上記の実施例に係る表示基板において、第1半導体層10を利用して出力リセットトランジスタT9のアクティブ層及び出力トランジスタT10のアクティブ層を形成して、T9及びT10の占める第2方向での空間を小さくするのみならず、出力リセットトランジスタT9のアクティブ層及び出力トランジスタT10のアクティブ層の第1方向でのサイズを大きくすることで、T9のチャネルの幅及びT10のチャネルの幅を確保し、これによりT9の動作性能及びT10の動作性能を確保する上に、表示基板の額縁の幅を縮めることができる。

#### 【0114】

本開示の少なくとも一実施例では、図5は、図3Aのアクティブ層の概略図であり、図6は、図3Aの第1ゲート金属層の概略図であり、図7は、図3Aの第2ゲート金属層の概略図であり、図8は、順次にアクティブ層、第1ゲート金属層及び第2ゲート金属層を設置した後に製作したビアホールの概略図であり、図9は図3Aのソース・ドレイン金属層の概略図である。

#### 【0115】

具体的に実施する時に、ベース上に順次にアクティブ層、第1ゲート金属層、第2ゲー

10

20

30

40

50

ト金属層、ビアホール及びソース・ドレイン金属層を設置して表示基板を形成する。

**【0116】**

本開示の少なくとも一実施例では、前記少なくとも一つのシフトレジスタユニットは、出力トランジスタ及び出力リセットトランジスタに加えて、複数のトランジスタも含んでもよく、各トランジスタのチャネル部分の両側の導電部分は、対応に該トランジスタの第1電極及び第2電極それぞれにしてもよいか、もしくは該トランジスタの第1電極及び該トランジスタの第2電極それぞれに結合されてもよい。

**【0117】**

図3A～図9に示すように、S91、S92及びS93がそれぞれ第1導電接続部F1に結合され、前記第1導電接続部F1が前記第1電圧信号線VGHに結合され、

10

前記第1導電接続部F1のベースでの正投影と、前記出力リセットコンデンサC3の第2極板C3bのベースでの正投影との間に第5重なり領域を有し、前記第1導電接続部F1が前記第5重なり領域に設けられている第5ビアホールH5を介して前記出力リセットコンデンサC3の第2極板C3bに結合される。

**【0118】**

具体的に実施する時に、前記少なくとも一つのシフトレジスタユニットは、第1トランジスタをさらに含んでもよく、

前記第1トランジスタは、第1アクティブパターンを含み、前記第1アクティブパターンが第2方向に沿って延在され、

20

前記第1トランジスタは、前記出力回路の表示領域から離れた側に位置している。

図1、図3A～図9に示すように、前記少なくとも一つのシフトレジスタユニットは、第1トランジスタT1をさらに含んでもよく、

前記第1トランジスタT1は、第1アクティブパターンA1を含み、前記第1アクティブパターンA1が第2方向に沿って延在され、

前記第1トランジスタT1は、前記出力回路O1の表示領域から離れた側に位置している。

**【0119】**

本開示の少なくとも一実施例では、T1のうち、第1アクティブパターンA1を第2方向に沿って延在されるように設置して、T2及びT8がより緊密に設置されて、横方向の空間を節約することができる。

30

**【0120】**

図3A～図9に示すように、前記第1トランジスタT1は、第1アクティブパターンA1を含み、前記第1アクティブパターンA1は、第2方向に沿って順次に配列される1番目の第3導電部分A11、第3チャネル部分A10及び2番目の第3導電部分A12を含み、

1番目の第3導電部分A11が第1トランジスタT1の第1電極S1として兼用され、2番目の第3導電部分A12が第1トランジスタT1の第2電極D1として兼用され、

前記第1トランジスタT1の第1電極S1は、第1接続ビアホールH11を介して第2導電接続部F2に結合され、前記第2導電接続部F2のベースでの正投影と、前記出力コンデンサC2の第2極板C2bのベースでの正投影との間に第6重なり領域を有し、前記第2導電接続部F2は、前記第6重なり領域に設けられている第6ビアホールH6を介して前記出力コンデンサC2の第2極板C2bに結合され、

40

T1の第2電極D1は、第2接続ビアホールH21を介して第3導電接続部F3に結合され、前記第3導電接続部F3のベースでの正投影と、C1の第2極板C1bのベースでの正投影との間に第7重なり領域を有し、F3は、第7重なり領域に設けられている第7ビアホールH7を介してC1の第2極板C1bに結合され、

T1のゲート電極G1は、C1の第1極板C1aに結合され、T1のゲート電極G1は、T8のゲート電極G8にも結合される。

**【0121】**

図3Aに示すように、前記出力コンデンサC2の極板のT4とT10との間の部分の第

50

2方向での幅が狭くなり、C2の極板のT7とT10との間の部分の第2方向での幅も狭くなつて、第2方向での空間を省き、残すべきところが他の素子のレイアウトに用いられるようとする。しかも、図3Aに示すように、第1方向におけるC2の極板の長さも長くなつて、C2の極板の面積を確保する。

#### 【0122】

本開示の少なくとも一実施例では、図1、図3A～図9に示すように、前記少なくとも一つのシフトレジスタユニットは、第2トランジスタT2及び第3トランジスタT3をさらに含んでもよく、

前記第2トランジスタT2のゲート電極G2の前記ベースでの正投影と、前記第3トランジスタT3のゲート電極G3の前記ベースでの正投影との間の第2方向での最大距離が第3所定距離であり、10

前記第2トランジスタT2及び前記第3トランジスタT3が前記出力回路の表示領域から離れた側に位置しており、

前記第2トランジスタT2の第2電極D2は、前記第3トランジスタT3の第2電極D3に結合される。10

#### 【0123】

本開示の少なくとも一実施例では、前記第3所定距離は、14μm以上かつ50μm以下であつてもよいが、これに限らない。

#### 【0124】

具体的に実施する時に、前記第2トランジスタT2の第2電極D2が前記第3トランジスタT3の第2電極D2に結合されるので、配線の便宜上、T2及びT3を近く設置することが必要であり、かつT2及びT3を近く設置することは、シフトレジスタユニットの占める第2方向での幅を狭めることに寄与することができる。20

#### 【0125】

本開示の少なくとも一実施例では、前記第2トランジスタT2のゲート電極G2の前記ベースでの正投影と、前記第3トランジスタT3のゲート電極G3の前記ベースでの正投影との間の第2方向での最大距離が第3所定距離より短いということは、G2のベースでの正投影の周辺と、G3のベースでの正投影の周辺との間の第2方向での最大距離が第3所定距離より短いことである。

#### 【0126】

図3A～図9に示すように、第2トランジスタT2は、第2アクティブパターンを含み、前記第2アクティブパターンA2は、第1方向に沿つて順次に配列される1番目の第4導電部分A21、第4チャネル部分A20及び2番目の第4導電部分A22を含み、30

1番目の第4導電部分A21が第2トランジスタT2の第1電極S2として兼用され、2番目の第4導電部分A22が第2トランジスタT2の第2電極D2として兼用され、

第2トランジスタT2の第1電極S2は、第3接続ビアホールH31を介して前記第3導電接続部F3に結合され、前記第3導電接続部F3のベースでの正投影と、C1の第2極板C1bのベースでの正投影との間に第7重なり領域を有し、F3は、第7重なり領域に設けられている第7ビアホールH7を介してC1の第2極板C1bに結合されて、第2トランジスタT2の第1電極S2がC1の第2極板C1bに結合され、40

第2トランジスタT2の第2電極D2は、第4接続ビアホールH41を介して第4導電接続部F4に結合され、

第3トランジスタT3は、第3アクティブパターンA3を含み、

前記第3アクティブパターンA3は、第2方向に沿つて順次に配列される1番目の第5導電部分A31、第5チャネル部分A30及び2番目の第5導電部分A32を含み、

1番目の第5導電部分A31が第3トランジスタT3の第1電極S3として兼用され、2番目の第5導電部分A32が第3トランジスタT3の第2電極D3として兼用され、

第3トランジスタT3の第1電極S3は、第5接続ビアホールH51を介してそれぞれS91、S92及びS93に結合され、50

第3トランジスタT3の第2電極D3は、第6接続ビアホールH61を介して第4導電

接続部 F 4 に結合される。

**【 0 1 2 7 】**

選択的に、前記少なくとも一つのシフトレジスタユニットは、第 1 トランジスタ、第 2 トランジスタ及び第 1 コンデンサを含んでもよく、ここで、

前記第 1 トランジスタの第 2 電極及び前記第 2 トランジスタの第 1 電極は、それぞれ前記第 1 コンデンサの第 2 極板に結合され、前記第 1 トランジスタのゲート電極は、前記第 1 コンデンサの第 1 極板に結合され、

前記第 1 トランジスタ、前記第 1 コンデンサ及び前記第 2 トランジスタが第 1 方向に沿って順次に配列され、

前記第 1 トランジスタ、前記第 1 コンデンサ及び前記第 2 トランジスタは、前記出力回路の表示領域から離れた側に位置している。 10

**【 0 1 2 8 】**

図 1、図 3 A ~ 図 9 に示すように、前記少なくとも一つのシフトレジスタユニットは、第 1 トランジスタ T 1、第 2 トランジスタ T 2 及び第 1 コンデンサ C 1 をさらに含んでもよく、ここで、

前記第 1 トランジスタ T 1 の第 2 電極 D 1 及び前記第 2 トランジスタ T 2 の第 1 電極 D 2 は、それぞれ前記第 1 コンデンサ C 1 の第 2 極板 C 1 b に結合され、前記第 1 トランジスタ T 1 のゲート電極 G 1 は、前記第 1 コンデンサ C 1 の第 1 極板 C 1 a に結合され、

前記第 1 トランジスタ T 1、前記第 1 コンデンサ C 1 及び前記第 2 トランジスタ T 2 が第 1 方向に沿って順次に配列され、 20

前記第 1 トランジスタ T 1、前記第 1 コンデンサ C 1 及び前記第 2 トランジスタ T 2 は、前記出力回路 O 1 の表示領域から離れた側に位置している。

**【 0 1 2 9 】**

本開示の少なくとも一実施例では、C 1 は、T 1 と T 2 との間に位置しており、かつ T 1、T 2 及び T 3 の配列される位置が C 1 の極板の形状に互いに契合して、T 1、T 2、T 3 及び C 1 がさらに緊密に配列される。具体的に実施する時に、図 1、図 3 A - 図 9 に示すように、前記走査駆動回路は、第 1 電圧信号線 V G H をさらに含んでもよく、前記少くとも一つのシフトレジスタユニットは、出力リセットコンデンサ C 3 をさらに含んでもよく、前記出力リセットコンデンサ C 3 の第 1 極板 C 3 a は、前記出力リセットトランジスタ T 9 のゲート電極 G 9 に結合され、前記出力リセットコンデンサ C 3 の第 2 極板 C 3 b は、前記第 1 電圧信号線 V G H に結合され、 30

前記出力リセットコンデンサ C 3 の第 2 極板 C 3 b の第 2 方向での最大の幅が第 1 所定の幅であり、前記出力リセットコンデンサ C 3 の第 2 極板 C 3 b の第 1 方向での最大長さが第 2 所定の長さであり、

前記出力リセットコンデンサ C 3 は、前記出力回路 O 1 の表示領域から離れた側に位置しており、

前記出力リセットコンデンサ C 3 の第 2 極板 C 3 b の前記ベースでの正投影は、前記出力リセットコンデンサ C 3 の第 1 極板 C 3 a の前記ベースでの正投影内にある。

**【 0 1 3 0 】**

本開示の少なくとも一実施例では、前記第 1 所定の幅は、3 μm 以上かつ 60 μm 以下であってもよく、前記第 2 所定の長さは、3 μm 以上かつ 20 μm 以下であってもよいが、これに限らない。 40

**【 0 1 3 1 】**

選択的に、図 3 A に示すように、前記第 1 電圧信号線 V G H が第 1 方向に沿って延在され、前記第 1 電圧信号線 V G H は、前記出力リセットコンデンサ C 3 の表示領域から離れた側に位置している。

**【 0 1 3 2 】**

本開示の少なくとも一実施例では、C 3 の第 2 極板 C 3 b の第 2 方向での幅を小さく設定して、第 2 方向でのシフトレジスタユニットの幅を狭め、かつ C 3 の極板の面積を確保するために、C 3 の第 2 極板 C 3 b の第 1 方向での長さを大きく設定する。 50

**【0133】**

図3A～図9に示すように、C3の第1極板C3aがT9のゲート電極G9に結合され、C3の第1極板C3aのベースでの正投影と、前記第4導電接続部F4のベースでの正投影との間に第8重なり領域を有し、C3aは、前記第8重なり領域に設けられている第8ピアホールH8を介して前記第4導電接続部F4に結合されて、C3aが第2トランジスタT2の第2電極D2に結合され、

S91、S92及びS93がそれぞれ第1導電接続部F1に結合され、前記第1導電接続部F1が前記第1電圧信号線VGHに結合され、

前記第1導電接続部F1のベースでの正投影と、前記出力リセットコンデンサC3の第2極板C3bのベースでの正投影との間に第5重なり領域を有し、前記第1導電接続部F1は、前記第5重なり領域に設けられている第5ピアホールH5を介して前記出力リセットコンデンサC3の第2極板C3bに結合されて、C3bがS91、S92及びS93それぞれに結合される。

10

**【0134】**

本開示の少なくとも一実施例では、図3A～図9に示すように、前記出力トランジスタT10及び前記出力リセットトランジスタT9は、第1方向に沿って配列され、前記走査駆動回路は、第2電圧信号線VGLをさらに含み、前記少なくとも一つのシフトレジスタユニットは、出力リセットコンデンサC3をさらに含み、

前記出力リセットコンデンサC3の第2極板C3bは、前記第1電圧信号線VGHに結合され、

20

前記出力トランジスタT10の第1電極S10は、第2電圧信号線VGLに結合され、前記出力リセットトランジスタT9の第1電極S9は、前記出力リセットコンデンサC3の第2極板C3bに結合され、

前記出力トランジスタT10及び前記出力リセットトランジスタT9は、前記第2電圧信号線VGLの表示領域から離れた側に位置している。

30

**【0135】**

選択的に、前記走査駆動回路は、第2電圧信号線をさらに含んでもよく、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタをさらに含んでもよく、

前記第2電圧信号線は、電極導電接続部に結合され、前記電極導電接続部は、第2方向に沿って延在され、前記少なくとも一つの第1電極パターンは、第1方向に沿って順次に配列され、

前記電極導電接続部は、前記出力トランジスタの第1電極に含まれる1番目の第1電極パターンに結合され、

前記第4トランジスタの第1電極は、前記電極導電接続部に結合され、

前記第4トランジスタのゲート電極の前記ベースでの正投影と、前記電極導電接続部の前記ベースでの正投影との間の第1方向での最小距離は、第4所定距離である。

**【0136】**

本開示の少なくとも一実施例では、前記第4トランジスタのゲート電極の前記ベースでの正投影と、前記電極導電接続部の前記ベースでの正投影との間の第1方向での最小距離というのは、第4トランジスタのゲート電極のベースでの正投影の周辺と、電極導電接続部のベースでの正投影の周辺との間の第1方向での最小距離である。

40

**【0137】**

本開示の少なくとも一実施例では、前記第4所定距離は、1μm以上かつ5μm以下であってもよいが、これに限らない。

本開示の少なくとも一実施例では、出力アクティブ長さを上げるとともに、第4トランジスタを上方に移動し、第4トランジスタのゲート電極と電極導電接続部との第1方向での距離を短く保持することで、出力アクティブ長さを上げることにより第1方向で余裕になる空間を利用してシフトレジスタユニットに含まれる出力回路以外の他の素子をレイアウトし、その上シフトレジスタユニットの第2方向での幅を狭めることができる。

**【0138】**

50

図3A～図9に示すように、前記走査駆動回路は、第2電圧信号線VGLをさらに含んでもよく、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタT4をさらに含んでもよく、

前記第2電圧信号線VGLは、電極導電接続部F01に結合され、前記電極導電接続部F01は、第2方向に沿って延在され、前記出力トランジスタT10の第1電極S10に含まれる1番目の第1電極パターンS101、2番目の第1電極パターンS102及び3番目の第1電極パターンS103は第1方向に沿って順次に配列され、

前記電極導電接続部F01は、前記1番目の第1電極パターンS101に結合され、

前記第4トランジスタT4の第1電極S4は、電極接続ビアホールH0を介して前記電極導電接続部F01に結合され、

前記第4トランジスタT4のゲート電極G4の前記ベースでの正投影と、前記電極導電接続部F01の前記ベースでの正投影との間の第1方向での最小距離が第4所定距離とされ、S101を上方に移動するとともに、T4も上方に移動するようとする。

#### 【0139】

図5に示すように、第4トランジスタT4は、第4アクティブパターンA4を含み、

前記第4アクティブパターンA4は、第1方向に沿って順次に配列される1番目の第6導電部分A41、第6チャネル部分A40及び2番目の第6導電部分A42を含み、

1番目の第6導電部分A41が第4トランジスタT4の第1電極S4として兼用され、2番目の第6導電部分A42が第4トランジスタT4の第2電極D4として兼用される。

#### 【0140】

本開示の少なくとも一実施例では、前記少なくとも一つのシフトレジスタユニットは、第4トランジスタ及び第5トランジスタをさらに含んでもよく、

前記第4トランジスタのゲート電極は、前記第5トランジスタのゲート電極に結合され、

前記第4トランジスタのゲート電極及び前記第5トランジスタのゲート電極は、第1ゲート金属パターンに含まれ、前記第1ゲート金属パターンは、第2方向に沿って延在される。

#### 【0141】

具体的に実施する時に、前記第4トランジスタ及び前記第5トランジスタは並べて設置されてもよく、第4トランジスタを上方に移動するとともに、第5トランジスタも上方に移動する。

選択的に、前記走査駆動回路は、第1クロック信号線をさらに含んでもよく、前記第5トランジスタのゲート電極は、前記第1クロック信号線に結合され、

前記第1クロック信号線は第1方向に沿って延在され、前記第1クロック信号線は前記第5トランジスタの表示領域から離れた側に位置している。

#### 【0142】

図1、図3A～図9に示すように、前記少なくとも一つのシフトレジスタユニットは第4トランジスタT4及び第5トランジスタT5をさらに含んでもよく、前記走査駆動回路は、第1クロック信号線CKをさらに含んでもよく、

前記第4トランジスタT4のゲート電極G4は、前記第5トランジスタT5のゲート電極G5に結合され、

前記第4トランジスタT4のゲート電極G4及び前記第5トランジスタT5のゲート電極G5は第1ゲート金属パターン45に含まれ、前記第1ゲート金属パターン45は、第2方向に沿って延在され、

前記第5トランジスタT5のゲート電極G5は、前記第1クロック信号線CKに結合され、

前記第1クロック信号線CKは、第1方向に沿って延在され、前記第1クロック信号線CKは、前記第5トランジスタT5の表示領域から離れた側に位置している。

#### 【0143】

図3A～図9に示すように、前記第1ゲート金属パターン45のベースでの正投影と、前記第1クロック信号線CKのベースでの正投影との間に第9重なり領域を有し、前記第

10

20

30

40

50

1 ゲート金属パターン 4 5 は、前記第 9 重なり領域に設けられている第 9 ピアホール H 9 を介して前記第 1 クロック信号線 C K に結合される。

T 5 の第 1 電極 S 5 は、第 7 接続ピアホール H 7 1 を介して入力信号端 E 1 に結合される。

#### 【 0 1 4 4 】

図 5 に示すように、第 5 トランジスタ T 5 は、第 5 アクティブパターン A 5 を含み、前記第 5 アクティブパターン A 5 は、第 1 方向に沿って順次に配列される 1 番目の第 7 導電部分 A 5 1、第 7 チャネル部分 A 5 0 及び 2 番目の第 7 導電部分 A 5 2 を含み、1 番目の第 7 導電部分 A 5 1 が第 5 トランジスタ T 5 の第 1 電極 S 5 として兼用され、2 番目の第 7 導電部分 A 5 2 が第 5 トランジスタ T 5 の第 2 電極 D 5 として兼用される。

#### 【 0 1 4 5 】

具体的に実施する時に、図 1、図 3 A ~ 図 9 に示すように、前記少なくとも一つのシフトレジスタユニットは、第 1 トランジスタ T 1、第 4 トランジスタ T 4、第 5 トランジスタ T 5、第 6 トランジスタ T 6 及び出力コンデンサ C 2 をさらに含んでもよく、

前記第 5 トランジスタ T 5 の第 2 電極 D 5 は、前記第 6 トランジスタ T 6 のゲート電極 G 6 に結合され、前記第 5 トランジスタ T 5 の第 1 電極 S 1 は、入力信号端 E 1 に結合され、

前記第 6 トランジスタ T 6 のゲート電極 G 6 は、互いに結合される第 1 ゲート電極パターン g 6 1 及び第 2 ゲート電極パターン g 6 2 を含み、

前記第 1 ゲート電極パターン g 6 1 及び前記第 2 ゲート電極パターン g 6 2 は、それぞれ前記出力コンデンサ C 2 の第 1 極板 C 2 a に結合され、前記出力コンデンサ C 2 の第 1 極板 C 2 a は、前記出力トランジスタ T 1 0 のゲート電極 S 1 0 に結合され、

前記第 6 トランジスタ T 6 の第 1 電極 S 6 は、第 4 トランジスタ T 4 のゲート電極 G 4 に結合され、前記第 6 トランジスタ T 6 の第 2 電極 D 6 は、前記第 4 トランジスタ T 4 の第 2 電極 D 4 に結合され、前記出力コンデンサ C 2 の第 2 極板 C 2 b は、前記第 1 トランジスタ T 1 の第 1 電極 S 1 に結合され、

前記第 4 トランジスタ T 4、前記第 6 トランジスタ T 6 及び前記第 1 トランジスタ T 1 が前記第 1 方向に沿って順次に配列され、

前記第 5 トランジスタ T 5、前記第 6 トランジスタ T 6 及び前記第 1 トランジスタ T 1 が前記第 1 方向に沿って順次に配列され、

前記出力コンデンサ C 2 は、前記第 6 トランジスタ T 6 と前記出力回路 O 1 との間に位置している。

#### 【 0 1 4 6 】

図 5 に示すように、第 6 トランジスタ T 6 は、第 6 アクティブパターン A 6 を含み、前記第 6 アクティブパターン A 6 は、第 1 方向に沿って順次に配列される 1 番目の第 8 導電部分 A 6 1、1 番目の第 8 チャネル部分 A 6 0 1、2 番目の第 8 導電部分 A 6 2、2 番目の第 8 チャネル部分 A 6 0 2 及び 3 番目の第 8 導電部分 A 6 3 を含み、

1 番目の第 8 導電部分 A 6 1 が第 6 トランジスタ T 6 の第 1 電極 S 6 として兼用され、3 番目の第 8 導電部分 A 6 3 が第 6 トランジスタ T 6 の第 2 電極 D 6 として兼用される。

#### 【 0 1 4 7 】

図 3 A ~ 図 9 に示すように、T 6 のゲート電極は、第 2 ゲート金属パターン 6 0 に含まれ、前記第 2 ゲート金属パターン 6 0 は U 形であって、T 6 のゲート電極が互いに結合される第 1 ゲート電極パターン g 6 1 及び第 2 ゲート電極パターン g 6 2 を含むようにし、

前記第 2 ゲート金属パターン 6 0 は、第 8 接続ピアホール H 8 1 を介して第 5 導電接続部 F 5 に結合され、

T 5 の第 2 電極 D 5 は、第 9 接続ピアホール H 9 1 を介して前記第 5 導電接続部 F 5 に結合されて、T 5 の第 2 電極 D 5 が T 6 のゲート電極に含まれる互いに結合される第 1 ゲート電極パターン g 6 1 及び第 2 ゲート電極パターン g 6 2 それぞれに結合されるようにし、

T 6 の第 1 電極 S 6 は、第 1 0 接続ピアホール H 1 0 1 を介して第 6 導電接続部 F 6 に

10

20

30

40

50

結合され、第1ゲート金属パターン45は、第11接続ビアホールH111を介して前記第6導電接続部F6に結合され、

T6の第2電極D6は、第12接続ビアホールH121を介して第7導電接続部F7に結合され、T4の第2電極D4は、第13接続ビアホールH131を介して前記第7導電接続部F7に結合されて、T6の第2電極D6がT4の第2電極D4に結合されるようとする。

#### 【0148】

本開示の少なくとも一実施例では、図1、図3A～図9に示すように、前記少なくとも一つのシフトレジスタユニットは、第2トランジスタT2、第1トランジスタT1、第6トランジスタT6、第7トランジスタT7及び第8トランジスタT8をさらに含んでもよく、ここで、

図5に示すように、前記第7トランジスタT7のアクティブ層及び前記第8トランジスタT8のアクティブ層は、一つの連続した第2半導体層20により形成されてもよく、前記第2半導体層20が第1方向に沿って延在され、

前記第7トランジスタT7のアクティブ層は、第1方向に沿って順次に設置される1番目の第9導電部分211、第9チャネル部分201及び2番目の第9導電部分212を含み、

前記2番目の第9導電部分212が1番目の第10導電部分として兼用され、

前記第8トランジスタT8のアクティブ層は、第1方向に沿って順次に設置される1番目の第10導電部分、第10チャネル部分202及び2番目の第10導電部分222を含み、

前記1番目の第9導電部分211は、前記第7トランジスタT7の第2電極D7として用いられ、前記2番目の第9導電部分212は、前記第7トランジスタT7の第1電極S7として用いられ、前記2番目の第10導電部分222は、前記第8トランジスタT8の第1電極S8として用いられ、前記第7トランジスタT7の第1電極S7が前記第8トランジスタT8の第2電極D8として兼用され、

前記第7トランジスタT7のゲート電極G7は、出力コンデンサC2の第2極板C2bに結合され、前記第7トランジスタT7の第2電極D7は、前記第6トランジスタT6のゲート電極G6に結合され、

前記第8トランジスタT8のゲート電極G8は、前記第1トランジスタT1のゲート電極G1に結合され、前記第8トランジスタT8の第1電極S8は、第1電圧信号線VGHに結合され、

前記第1電圧信号線VGHが第1方向に沿って延在され、

前記第6トランジスタT6、前記第7トランジスタT7、前記第8トランジスタT8及び前記第2トランジスタT2は、第1方向に沿って順次に配列される。

本開示の少なくとも一実施例では、出力アクティブ長さを上げるのに伴い、T5、T4、T6、T7及びT8がいずれも上方に移動され、第1方向で余裕になる空隙を利用して、シフトレジスタユニットの占める第2方向での幅を狭める。

#### 【0149】

また、前記第7トランジスタT7の第1電極S7が前記第8トランジスタT8の第2電極D8として兼用され、即ち、本開示の少なくとも一実施例に記載の表示基板において、第7トランジスタT7及び第8トランジスタT8において、第2半導体層20に含まれる2番目の第9導電部分212を介して直接的に結合されることができ、T7及びT8の第1方向で占める面積を縮める。

#### 【0150】

選択的に、図1、図3A～図9に示すように、前記走査駆動回路は、第2クロック信号線CBをさらに含んでもよく、前記第2トランジスタT2のゲート電極G2及び第7トランジスタT7のゲート電極G7は、それぞれ前記第2クロック信号線CBに結合され、

前記第2クロック信号線CBが第1方向に沿って延在され、前記第2クロック信号線CBは、前記第2トランジスタT2の表示領域から離れた側に位置している。

10

20

30

40

50

**【 0 1 5 1 】**

図3A～図9に示すように、T7の第2電極D7は、第14接続ビアホールH141を介して前記第5導電接続部F5に結合されて、T7の第2電極D7がT6のゲート電極G6に結合され、

T7のゲート電極G7は、それぞれ第8導電接続部F8及び第9導電接続部F9に結合され、

F8は、第15接続ビアホールH151を介して第2クロック信号線CBに結合され、

F9は、第16接続ビアホールH161を介して第2導電接続部F2に結合されて、T7のゲート電極G7がC2の第2極板C2bに結合され、

T8の第1電極S8は、第17接続ビアホールH171を介して前記第1電圧信号線VGHに結合され、

T8のゲート電極G8は、T1のゲート電極G1及びC1の第1極板C1aそれぞれに結合される。

図3A～図9に示すように、T2のゲート電極G2は、第10導電接続部F10に結合され、前記第10導電接続部F10は、第18接続ビアホールH181を介して前記第2クロック信号線CBに結合される。

**【 0 1 5 2 】**

図6に示すように、T3のゲート電極G3は、第11導電接続部F11を介して出力コンデンサC2の第1極板C2Aに結合され得る。

**【 0 1 5 3 】**

図9に示すように、G8は、第19接続ビアホールH191を介して第12導電接続部F12に結合され、前記第12導電接続部F12は、第12接続ビアホールH121を介してT6の第2電極D6に結合される。

選択的に、前記走査駆動回路は、第2電圧信号線及び信号出力線をさらに含んでもよく、前記信号出力線は、第1出力線部分及び少なくとも一つの第2出力線部分を含み、

前記第2電圧信号線及び前記第1出力線部分は、いずれも第1方向に沿って延在され、前記第1出力線部分は、前記第2電圧信号線と前記出力回路との間に位置しており、

前記第2出力線部分は、第2方向に沿って延在され、

前記第2出力線部分は、表示領域のうち、画素回路に発光制御信号を提供することに用いられ、

前記第1出力線部分及び前記出力回路は、前記第2電圧信号線の前記表示領域から離れた側に位置している。

**【 0 1 5 4 】**

図3Aに示されるレイアウト方式において、前記信号出力線は二つの第2出力線部分を含み、具体的に実施する時に、前記信号出力線に含まれる第2出力線部分の数は実際の状態に応じて選択されてもよい。

**【 0 1 5 5 】**

具体的に実施する時に、前記走査駆動回路は、第1電圧信号線、第2電圧信号線、第1クロック信号線及び第2クロック信号線をさらに含んでもよく、

前記第1電圧信号線、前記第2電圧信号線、前記第1クロック信号線及び前記第2クロック信号線は、いずれも第1方向に沿って延在され、

前記第1電圧信号線の前記ベースでの正投影、前記第1クロック信号線の前記ベースでの正投影及び前記第2クロック信号線の前記ベースでの正投影がいずれも前記シフトレジスタユニットの前記ベースでの正投影の前記表示領域から離れた側に位置しており、

前記第2電圧信号線の前記ベースでの正投影は、前記シフトレジスタユニットの前記表示領域に近い側に位置している。

**【 0 1 5 6 】**

本開示の少なくとも一実施例では、前記信号出力線は、少なくとも一つの第2出力線部分を含んでもよく、前記第2出力線部分が前記第1出力線部分に結合され、前記第2出力線部分が前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御

10

20

30

40

50

信号を提供することに用いられる。

【0157】

具体的に、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線の具体的な位置は、実際の必要に応じて設置されてもよく、例示として、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線をいずれも前記表示基板の周辺の箇所に設置して、すなわち、前記第1電圧信号線の前記ベースでの正投影、前記第1クロック信号線の前記ベースでの正投影及び前記第2クロック信号線の前記ベースでの正投影がいずれも前記シフトレジスタユニットの前記ベースでの正投影の前記表示基板の表示領域から離れた側に位置され、このようにして、前記シフトレジスタユニットをレイアウトする時に、前記シフトレジスタユニットのうち、各トランジスタと前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線との間に過多のオーバーラップが発生することを避けることで、前記シフトレジスタユニットの動作性能を高めることにさらに寄与する。

【0158】

また、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線をいずれも前記第1方向に沿って延在されるように設置することで、前記表示基板の狭額縁化の実現にさらに寄与する。

【0159】

本開示の少なくとも一実施例では、前記第1クロック信号線から出力の第1クロック信号及び前記第2クロック信号線から出力の第2クロック信号の位相が互いに反してもよいが、これに限らない。

具体的に実施する時に、図1及び図3Aに示すように、前記走査駆動回路は、第1電圧信号線VGH、第2電圧信号線VGL、第1クロック信号線CK、第2クロック信号線CB及び信号出力線を含んでもよく、前記少なくとも一つのシフトレジスタユニットは、第1コンデンサC1、出力コンデンサC2、出力リセットコンデンサC3、第1トランジスタT1、第2トランジスタT2、第3トランジスタT3、第4トランジスタT4、第5トランジスタT5、第6トランジスタT6、第7トランジスタT7、第8トランジスタT8、出力リセットトランジスタT9及び出力トランジスタT10をさらに含んでもよく、

前記信号出力線は、第1出力線部分E01、1番目の第2出力線部分E021及び2番目の第2出力線部分E022を含み、

第1出力線部分E01、1番目の第2出力線部分E021及び2番目の第2出力線部分E022は、互いに結合され、

前記第1出力線部分E01は、第1方向に沿って延在され、前記1番目の第2出力線部分E021及び前記2番目の第2出力線部分E022は、互いに結合されかつ第2方向に沿って延在され、

前記出力トランジスタT10及び前記出力リセットトランジスタT9が第1方向に沿って配列され、

前記出力トランジスタT10のゲート電極G10は、前記出力コンデンサC2の第1極板C2aに結合され、前記出力トランジスタT10の第1電極S10は、第2電圧信号線VGLに結合され、前記出力トランジスタT10の第2電極D10は、前記第1出力線部分E01に結合され、

前記出力リセットトランジスタT9のゲート電極G9は、前記出力リセットコンデンサC3の第1極板C3aに結合され、前記出力リセットトランジスタT9の第1電極S9は、前記出力リセットコンデンサC3の第2極板C3bに結合され、前記出力リセットトランジスタT9の第2電極D9は、前記第1出力線部分E01に結合され、

前記出力リセットコンデンサC3の第2極板C3bは、前記第1電圧信号線VGHに結合され、前記出力コンデンサC2の第2極板C2bは、前記第7トランジスタT7のゲート電極G7に結合され、

前記第1トランジスタT1の第1電極S1は、前記出力コンデンサC2の第2極板C2bに結合され、前記第1トランジスタT1の第2電極D1及び前記第2トランジスタT2

10

20

30

40

50

の第1電極D2は、それぞれ前記第1コンデンサC1の第2極板C1bに結合され、前記第1トランジスタT1のゲート電極G1は、前記第1コンデンサC1の第1極板C1aに結合され、

前記第2トランジスタT2のゲート電極G2及び第7トランジスタT7のゲート電極G7は、それぞれ前記第2クロック信号線CBに結合され、前記第2トランジスタT2の第2電極D2は、前記第3トランジスタT3の第2電極D3に結合され、

前記第3トランジスタT3のゲート電極G3は、前記出力トランジスタT10のゲート電極G10に結合され、前記第3トランジスタT3の第1電極S3は、前記出力リセットコンデンサC3の第1極板C3aに結合され、

前記第4トランジスタT4のゲート電極G4は、前記第5トランジスタT5のゲート電極G5に結合され、前記第4トランジスタT4の第1電極S4は、前記出力トランジスタT10の第1電極S10に結合され、前記第4トランジスタT4の第2電極D4は、前記第6トランジスタT6の第2電極D6に結合され、

前記第5トランジスタT5のゲート電極G5は、前記第1クロック信号線CKに結合され、第5トランジスタT5の第2電極D5は、前記第6トランジスタT6のゲート電極G6に結合され、前記第5トランジスタT5の第1電極S5は、入力信号端E1に結合され、

前記第6トランジスタT6の第1電極S6は、第4トランジスタT4のゲート電極G4に結合され、前記第6トランジスタT6の第2電極D6は、前記第4トランジスタT4の第2電極D4に結合され、

前記第7トランジスタT7のゲート電極G7は、出力コンデンサC2の第2極板C2bに結合され、前記第7トランジスタT7の第1電極S7が前記第8トランジスタG8の第2電極D8として兼用され、前記第7トランジスタT7の第2電極D7は、前記第6トランジスタG6のゲート電極G6に結合され、

前記第8トランジスタT8のゲート電極G8は、前記第1トランジスタT1のゲート電極G1に結合され、前記第8トランジスタT8の第1電極S8は、第1電圧信号線VGHに結合され、

前記1番目の第2出力線部分E021は、前記第1出力線部分E01に結合され、前記1番目の第2出力線部分E022は前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられ、

前記2番目の第2出力線部分E022は、前記第1出力線部分E01に結合され、前記2番目の第2出力線部分E022は前記表示領域まで延在されて、前記表示領域に位置している画素回路に発光制御信号を提供することに用いられる。

#### 【0160】

具体的に実施する時に、第2電圧信号線は、前記シフトレジスタユニットの表示領域に近い側に設けられてもよく、

前記第1電圧信号線、前記第1クロック信号線及び前記第2クロック信号線は、前記シフトレジスタユニットの表示領域から離れた側に設けられており、

前記表示領域に近づいてくる方向に沿って、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、もしくは、前記表示領域に近づいてくる方向に沿って、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列される。

#### 【0161】

本開示の少なくとも一実施例では、前記走査駆動回路は、第1初期信号線及び第2初期信号線をさらに含んでもよく、

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第1クロック信号線、前記第2クロック信号線及び前記第1電圧信号線が順次に配列され、

10

20

30

40

50

前記表示領域に近づいてくる方向に沿って、前記第2初期信号線、前記第1初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列され、

前記表示領域に近づいてくる方向に沿って、前記第1初期信号線、前記第2初期信号線、前記第2クロック信号線、前記第1クロック信号線及び前記第1電圧信号線が順次に配列される。

#### 【0162】

図3Bに示すように、図3Aに示されるシフトレジスタユニットの少なくとも一実施例を基にして、前記シフトレジスタユニットの少なくとも一実施例は、第1初期信号線E11及び第2初期信号線E12をさらに含み、

前記第1初期信号線E11及び前記第2初期信号線E12はいずれも第1方向に沿って延在されてもよく、

図3Bに示すように、E12、E11、CB、CK、VGHは、表示領域に近づいてくる方向に沿って、順次に配列される。

実際の操作において、E11の位置及びE12の位置は互に取り換えるてもよく、即ち、E11、E12、CB、CK、VGHは、表示領域に近づいてくる方向に沿って、順次に配列される。

#### 【0163】