(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5190414号

(P5190414)

(45) 発行日 平成25年4月24日(2013.4.24)

(24) 登録日 平成25年2月1日(2013.2.1)

|                |           |              |   |

|----------------|-----------|--------------|---|

| (51) Int.Cl.   | F 1       |              |   |

| HO 1 L 21/822  | (2006.01) | HO 1 L 27/04 | D |

| HO 1 L 27/04   | (2006.01) | HO 1 L 21/82 | L |

| HO 1 L 21/82   | (2006.01) | HO 1 L 21/88 | Z |

| HO 1 L 21/3205 | (2006.01) |              |   |

| HO 1 L 21/768  | (2006.01) |              |   |

請求項の数 12 (全 17 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-127377 (P2009-127377)  |

| (22) 出願日  | 平成21年5月27日 (2009.5.27)        |

| (65) 公開番号 | 特開2010-278104 (P2010-278104A) |

| (43) 公開日  | 平成22年12月9日 (2010.12.9)        |

| 審査請求日     | 平成22年8月31日 (2010.8.31)        |

|           |                                             |

|-----------|---------------------------------------------|

| (73) 特許権者 | 000005821<br>パナソニック株式会社<br>大阪府門真市大字門真1006番地 |

| (74) 代理人  | 110001427<br>特許業務法人前田特許事務所                  |

| (74) 代理人  | 100077931<br>弁理士 前田 弘                       |

| (74) 代理人  | 100110939<br>弁理士 竹内 宏                       |

| (74) 代理人  | 100110940<br>弁理士 嶋田 高久                      |

| (74) 代理人  | 100113262<br>弁理士 竹内 祐二                      |

| (74) 代理人  | 100115059<br>弁理士 今江 克実                      |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1配線層と、前記第1配線層の上側又は下側に形成された第2配線層とを半導体基板上に備えており、

前記第1配線層は複数の第1配線ブロックを含み、当該各第1配線ブロックには、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線と、前記第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線とが配置されており、

前記第2配線層は、前記複数の第1配線ブロックのうちの互いに隣り合う一対の第1配線ブロックにおける前記第1配線同士を電気的に接続する第3配線と、前記一対の第1配線ブロックにおける前記第2配線同士を電気的に接続する第4配線とを含み、

前記第2配線層は、前記第3配線及び前記第4配線がそれぞれ配置された複数の第2配線ブロックを含むことを特徴とする半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置において、

前記一対の第1配線ブロックのうちの一方の第1配線ブロックにおける前記第1配線及び前記第2配線の配置の仕方と、前記一対の第1配線ブロックのうちの他方の第1配線ブロックにおける前記第1配線及び前記第2配線の配置の仕方が異なっていることを特徴とする半導体装置。

## 【請求項 3】

請求項1又は2に記載の半導体装置において、

10

20

前記第3配線及び前記第4配線はそれぞれ二方向以上に延びることを特徴とする半導体装置。

【請求項4】

請求項1～3のいずれか1項に記載の半導体装置において、

前記第1配線の抵抗と前記第3配線の抵抗とは異なっており、

前記第2配線の抵抗と前記第4配線の抵抗とは異なっていることを特徴とする半導体装置。

【請求項5】

請求項1～4のいずれか1項に記載の半導体装置において、

前記第1配線と前記第3配線とは第1コンタクトを介して電気的に接続されており、

前記第2配線と前記第4配線とは第2コンタクトを介して電気的に接続されていることを特徴とする半導体装置。

【請求項6】

請求項1～5のいずれか1項に記載の半導体装置において、

前記第1配線及び前記第2配線のそれぞれはリング状に形成されていることを特徴とする半導体装置。

【請求項7】

請求項1～5のいずれか1項に記載の半導体装置において、

前記第1配線及び前記第2配線のそれぞれは渦巻き状に形成されていることを特徴とする請求項1記載の半導体装置。

10

【請求項8】

請求項1～7のいずれか1項に記載の半導体装置において、

前記第1配線層における前記複数の第1配線ブロック同士の間に信号配線が配置されていることを特徴とする半導体装置。

20

【請求項9】

請求項1～8のいずれか1項に記載の半導体装置において、

前記半導体基板の平面形状は方形状であり、

前記複数の第1配線ブロックは、前記半導体基板の各辺が延びる方向に配列されていることを特徴とする半導体装置。

30

【請求項10】

請求項1～8のいずれか1項に記載の半導体装置において、

前記半導体基板の平面形状は方形状であり、

前記複数の第1配線ブロックは、前記半導体基板の各辺が延びる方向に対して斜め方向に配列されていることを特徴とする半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記半導体基板の平面形状は正方形状であり、

前記複数の第1配線ブロックは、前記半導体基板の各辺が延びる方向に対して45度の方向に配列されていることを特徴とする半導体装置。

40

【請求項12】

請求項1～11のいずれか1項に記載の半導体装置において、

前記第3配線及び前記第4配線のそれぞれはリング状に形成されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路の配線構造に関し、詳しくは、半導体集積回路の電源配線の配線構造に関する。

【背景技術】

【0002】

50

半導体集積回路の電源配線が複数配線層に亘って形成される場合、通常、電源配線はメッシュ状又はそれに準じた形状の配線構造を有している。この場合、信号配線がノイズの影響を受けにくくするために、信号配線の横方向及び上下方向は電源配線によってシールドされる（例えば特許文献1参照）。

【0003】

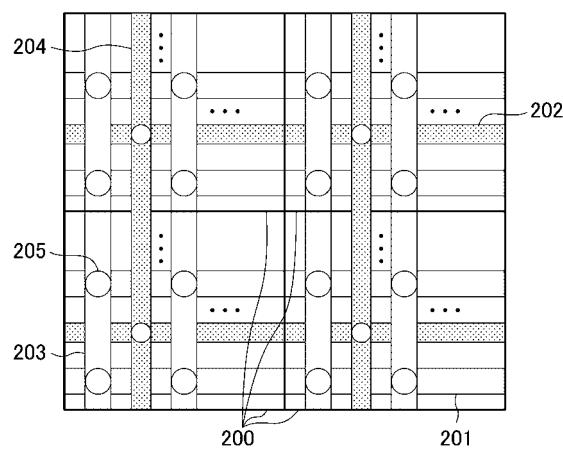

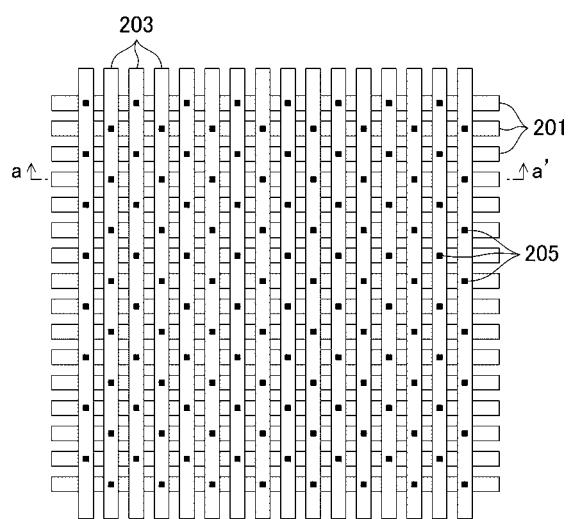

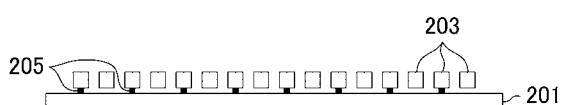

図14は、従来例に係る半導体装置における信号配線及び電源配線の配置例を示す図である。図14において、「200」はメモリコア、「201」はn層目メモリコア用電源配線、「202」はn層目信号配線、「203」は(n+1)層目メモリコア用電源配線、「204」は(n+1)層目信号配線、「205」は配線層間コンタクトである。図14に示す従来例においては、n層目と(n+1)層目とを用いてチップ全体にメッシュ状の電源配線が配置されている。尚、n層目及び(n+1)層目のそれぞれにおいて個々の電源配線は所定の方向に一次元的に延びている。

10

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005-332903号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、メッシュ状に広がる電源配線網において電流は周縁部から中心部に向けて供給される。また、半導体集積回路の内部各点において、当該各点に位置するセルが電源配線網から電流を受け取って消費する。従って、半導体集積回路の内部各点において電流が消費されることにより、チップの中心部に向かって電源配線網における電圧ドロップ（電圧降下）が大きくなる。すなわち、半導体集積回路の周縁部では電源配線網上の電圧が高く、半導体集積回路の中心部に向かうにつれて電源配線網上の電圧が低くなる。

20

【0006】

従って、前述の従来例に係る単純なメッシュ構造を持つ電源配線においては、n層目と(n+1)層目との間で配線層の膜厚などが異なることに起因して抵抗が異なる場合には電圧降下に方向性が生じてしまう。すなわち、抵抗が高い配線層において電源配線が延びる方向に電圧降下が大きくなるという問題が生じる。

30

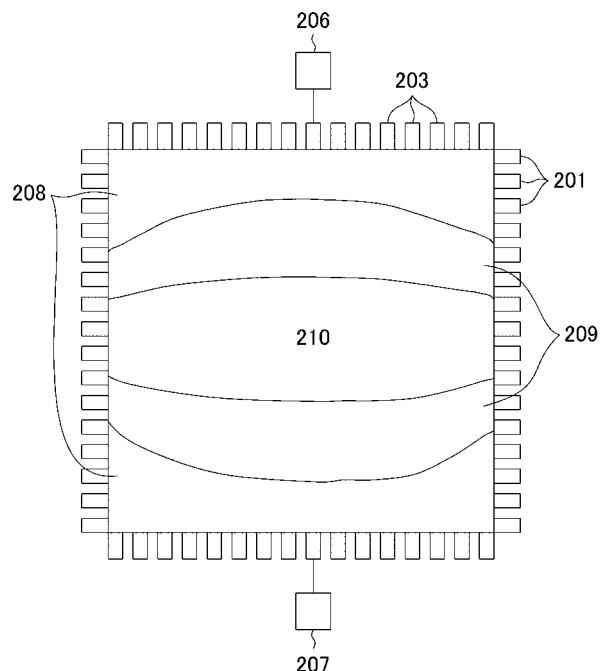

【0007】

図15及び図16は、図14に示す従来例の電源配線パターンを簡素化して模式的に示す上面図及び断面図である。また、図17は、図15に示す簡素化パターンに対して電源電圧を印加したときの配線抵抗による電圧降下例を示した図である。尚、図15～図17において、図14に示す従来例と同一の構成要素には同一の符号を付すことにより、重複する説明を省略する。

【0008】

図17に示すように、(n+1)層目メモリコア用電源配線203の両端にそれぞれ接続された電源供給パッド206及び207から電源電圧が印加されている。ここで、(n+1)層目メモリコア用電源配線（縦方向の配線）203の抵抗は、n層目メモリコア用電源配線（横方向の配線）201の抵抗よりも高く、その結果、(n+1)層目メモリコア用電源配線203の延びる方向に沿ってパターンの周縁部から中心部に向かうにつれて順次電圧降下が発生している。ここで、「208」は電圧降下がほとんどない領域、「209」は小さい電圧降下が発生している領域、「210」は大きい電圧降下が発生している領域である。

40

【0009】

尚、前述の電圧降下を防ぐために、電源供給パッド数を増やしたり、電源配線を太くするなどの対策を講じることも可能であるが、チップサイズの制約などから、このような対策にも限界がある。

【0010】

50

以上に鑑みて、本発明は、局所的な電圧降下を効果的に抑制できる電源配線構造を有した半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

前記の目的を達成するために、本発明に係る半導体装置は、第1配線層と、前記第1配線層の上側又は下側に形成された第2配線層とを半導体基板上に備えており、前記第1配線層は複数の第1配線ブロックを含み、当該各第1配線ブロックには、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線と、前記第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線とが配置されており、前記第2配線層は、前記複数の第1配線ブロックのうちの互いに隣り合う一対の第1配線ブロックにおける前記第1配線同士を電気的に接続する第3配線と、前記一対の第1配線ブロックにおける前記第2配線同士を電気的に接続する第4配線とを含む。

10

【0012】

本発明に係る半導体装置によると、第1配線層に設けられた第1配線及び第2配線のいずれも二方向以上に延びるため、従来例のように各配線層において電源配線が一方向のみに延びている場合と比較して、電圧降下に方向性が生じる事態を回避することができる。

【0013】

また、本発明に係る半導体装置によると、第1配線層に設けられた第1配線及び第2配線のいずれもが二方向以上に延びる配線として二次元的に形成されているため、従来例のように一方向のみに延びる配線として一次元的に形成された電源配線と比べて、各配線の抵抗値を低減することができる。

20

【0014】

従って、本発明に係る半導体装置によると、チップ内での局所的な電圧降下を効果的に抑制できる電源配線構造を実現することができる。

【0015】

尚、本発明に係る半導体装置において、電源電圧（Vdd）には複数の電圧があつてもよい。例えば、本発明に係る半導体装置において、第1配線層の各第1配線ブロックに、第1電位を持つ第1配線、及び第1電位と異なる第2電位を持つ第2配線に加えて、第1電位及び第2電位と異なる第3電位を持つ第3配線が配置されていてもよい。

30

【0016】

また、本発明に係る半導体装置において、前記一対の第1配線ブロックのうちの一方の第1配線ブロックにおける前記第1配線及び前記第2配線の配置の仕方と、前記一対の第1配線ブロックのうちの他方の第1配線ブロックにおける前記第1配線及び前記第2配線の配置の仕方が異なっていてもよい。このようにすると、第1配線と第2配線との間の抵抗差を解消することができる。

【0017】

また、本発明に係る半導体装置において、前記第2配線層は、前記第3配線及び前記第4配線がそれぞれ配置された複数の第2配線ブロックを含んでいてもよい。ここで、第1配線層の各第1配線ブロックと第2配線層の各第2配線ブロックとを互いにずらして配置してもよい。また、この場合、前記第3配線及び前記第4配線はそれぞれ二方向以上に延びていてもよい。このようにすると、従来例と比較して、前述の本発明の効果がより顕著に発揮される。

40

【0018】

また、本発明に係る半導体装置において、前記第1配線の抵抗と前記第3配線の抵抗とが異なっており、前記第2配線の抵抗と前記第4配線の抵抗とが異なっていると、言い換えると、第1配線層と第2配線層との間で抵抗が異なっていると、従来例と比較して、前述の本発明の効果がより顕著に発揮される。

【0019】

また、本発明に係る半導体装置において、前記第1配線と前記第3配線とは第1コンタクトを介して電気的に接続されており、前記第2配線と前記第4配線とは第2コンタクト

50

を介して電気的に接続されていてもよい。

【0020】

また、本発明に係る半導体装置において、前記第1配線及び前記第2配線のそれぞれはリング状に形成されていてもよい。このようにすると、前述の本発明の効果を確実に得ることができる。

【0021】

また、本発明に係る半導体装置において、前記第1配線及び前記第2配線のそれぞれは渦巻き状に形成されていてもよい。このようにすると、前述の本発明の効果を確実に得ることができる。また、前記第1配線及び前記第2配線のそれぞれをリング状に形成する場合と同様に、前記第1配線及び前記第2配線のそれぞれと前記第3配線及び前記第4配線のそれぞれとを電気的に接続するコンタクトを容易に配置することができる。さらに、前記第1配線及び前記第2配線のそれぞれをリング状に形成する場合と比べて、コンタクトを介すことなく広範囲に亘って各配線を延伸させることができるので、各配線のさらなる低抵抗化が可能となる。

10

【0022】

また、本発明に係る半導体装置において、前記第1配線層における前記複数の第1配線プロック同士の間に信号配線が配置されていてもよい。

【0023】

また、本発明に係る半導体装置において、前記複数の第1配線プロックは、前記半導体基板の各辺が延びる方向に配列されていてもよい。このようにすると、半導体基板の各辺が延びる方向（チップエッジ方向）における電圧降下を抑制できるので、チップ周縁部に電源供給パッドが均一に配置されている構成に対して有効である。

20

【0024】

また、本発明に係る半導体装置において、前記半導体基板の平面形状は方形状であり、前記複数の第1配線プロックは、前記半導体基板の各辺が延びる方向に対して斜め方向に配列されていてもよい。特に、前記半導体基板の平面形状は正方形状であり、前記複数の第1配線プロックは、前記半導体基板の各辺が延びる方向に対して45度の方向に配列されていてもよい。このようにすると、一般的な正方形状のチップにおいて、チップエッジ方向に対して45度方向における電圧降下を抑制できるので、チップコーナー部に電源供給パッドが多く配置されている構成に対して有効である。

30

【0025】

また、本発明に係る半導体装置において、前記第3配線及び前記第4配線のそれぞれはリング状に形成されていてもよい。このようにすると、前述の本発明の効果を確実に得ることができる。

【発明の効果】

【0026】

本発明によると、電圧降下に方向性が生じる事態を回避することができるため、半導体装置内での局所的な電圧降下を効果的に抑制できるので、半導体装置を安定的に動作させることができると共にチップ面積を削減することができる。

40

【図面の簡単な説明】

【0027】

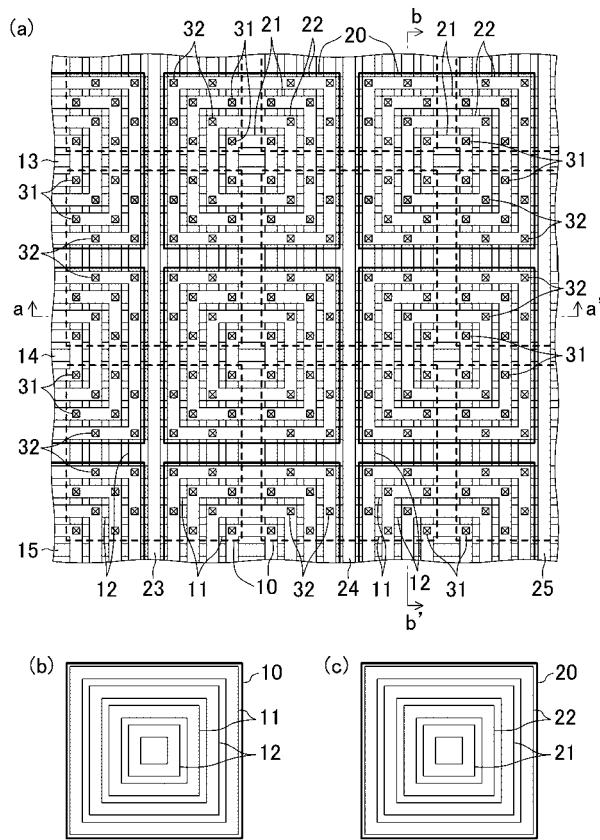

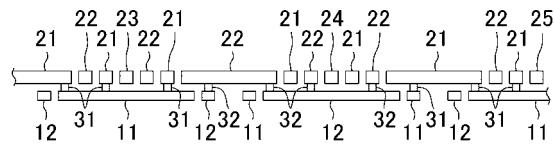

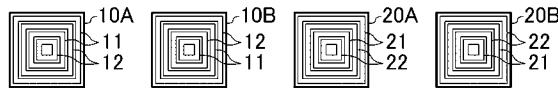

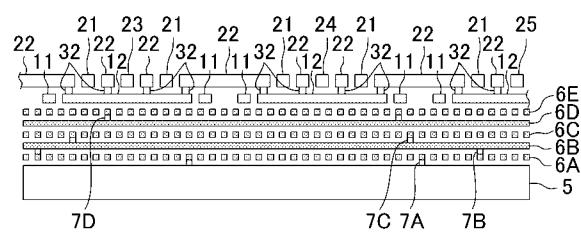

【図1】図1(a)は本発明の第1の実施形態に係る半導体装置の平面図であり、図1(b)は本発明の第1の実施形態に係る半導体装置における下側の配線層の配線プロックを示す図であり、図1(c)は本発明の第1の実施形態に係る半導体装置における上側の配線層の配線プロックを示す図である。

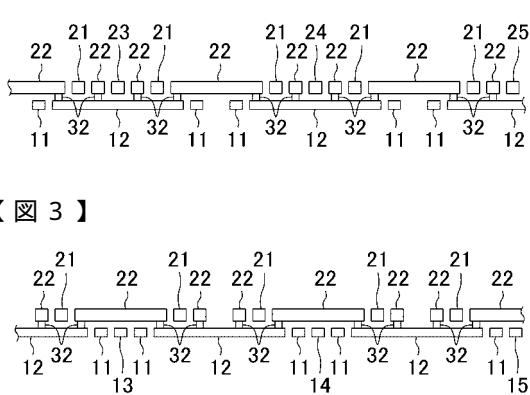

【図2】図2は図1(a)のa-a'線における断面図である。

【図3】図3は図1(a)のb-b'線における断面図である。

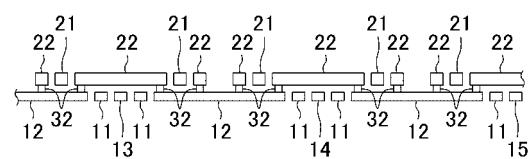

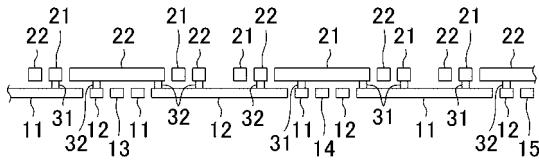

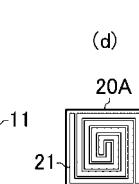

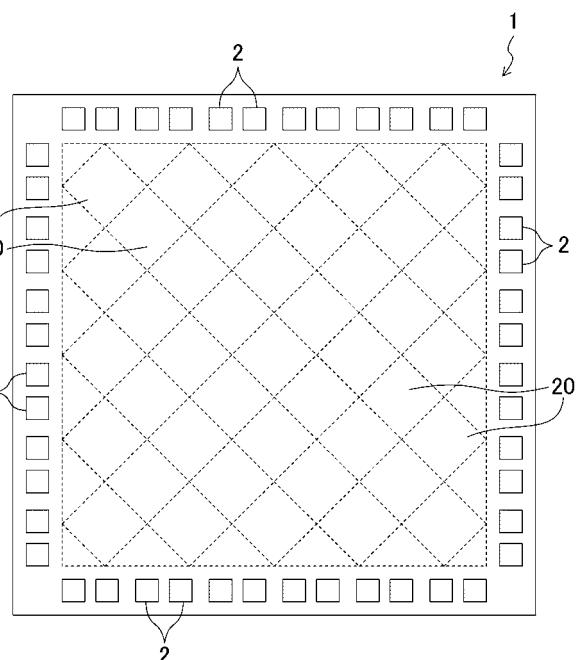

【図4】図4(a)は本発明の第1の実施形態の変形例に係る半導体装置の平面図であり、図4(b)及び(c)は本発明の第1の実施形態の変形例に係る半導体装置における下側の配線層の配線プロックを示す図であり、図4(d)及び(e)は本発明の第1の実施

50

形態の変形例に係る半導体装置における上側の配線層の配線ブロックを示す図である。

【図5】図4(a)のa-a'線における断面図である。

【図6】図4(a)のb-b'線における断面図である。

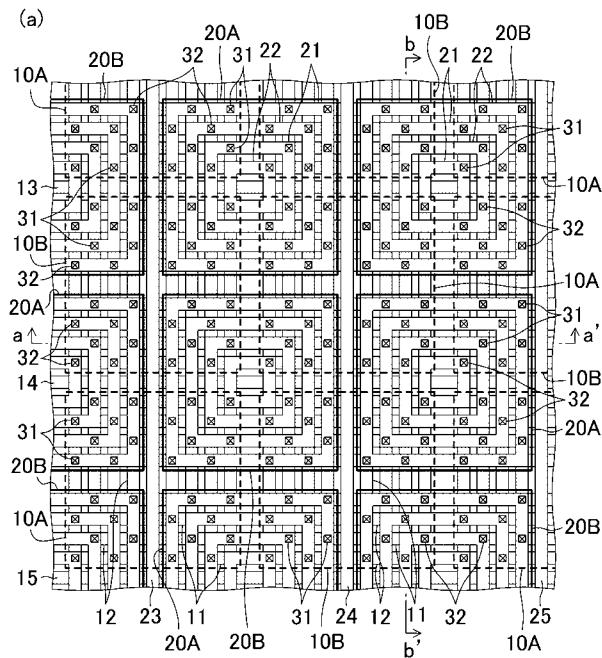

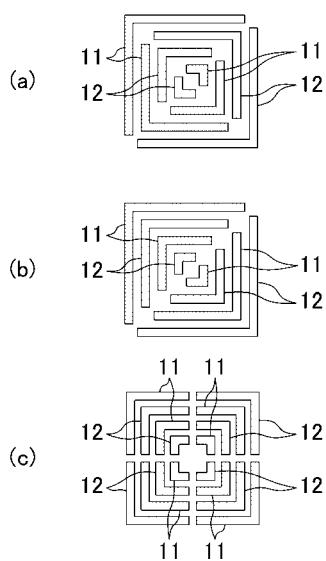

【図7】図7(a)は本発明の第2の実施形態に係る半導体装置の平面図であり、図7(b)は本発明の第2の実施形態に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図7(c)は本発明の第2の実施形態に係る半導体装置における上側の配線層の配線ブロックを示す図である。

【図8】図8(a)は本発明の第2の実施形態の変形例に係る半導体装置の平面図であり、図8(b)及び(c)は本発明の第2の実施形態の変形例に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図8(d)及び(e)は本発明の第2の実施形態の変形例に係る半導体装置における上側の配線層の配線ブロックを示す図である。10

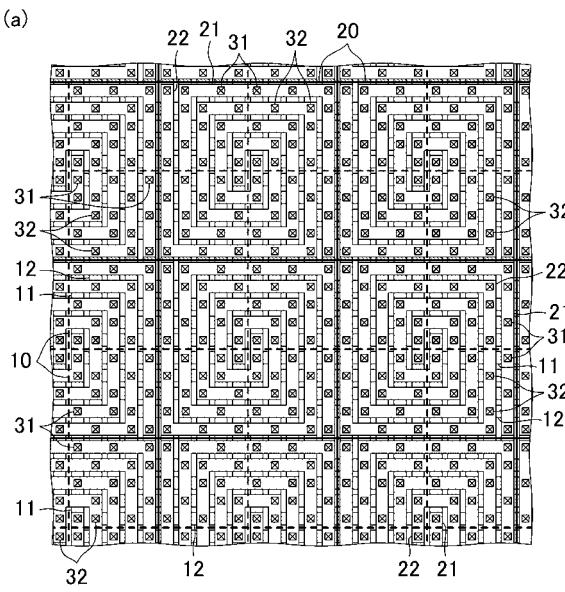

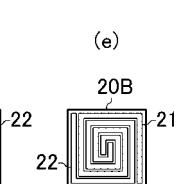

【図9】図9は、本発明の各実施形態(その変形例を含む)の配線ブロックの半導体チップ内での配置の一例を示す平面図である。

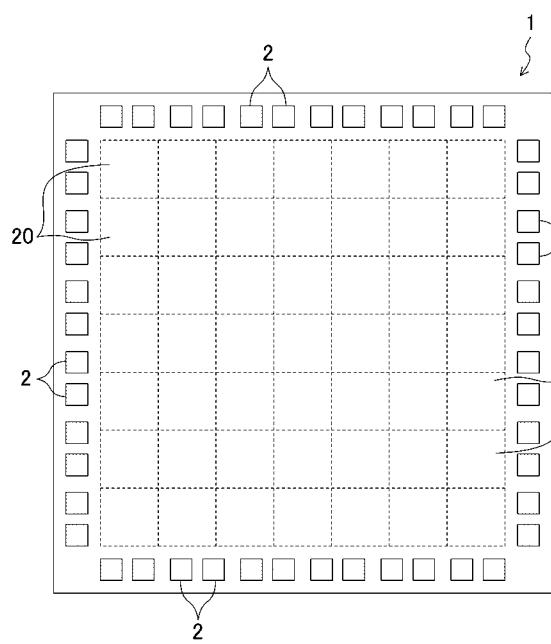

【図10】図10は、本発明の各実施形態(その変形例を含む)の配線ブロックの半導体チップ内での配置の他例を示す平面図である。

【図11】図11は、本発明の各実施形態(その変形例を含む)の第1配線層及び第2配線層よりも下層に設けられた他の配線層の構造例を示す断面図である。

【図12】図12は、本発明の各実施形態(その変形例を含む)の電源配線及び接地配線として、二方向に延びる配線を配置した例を示す平面図である。

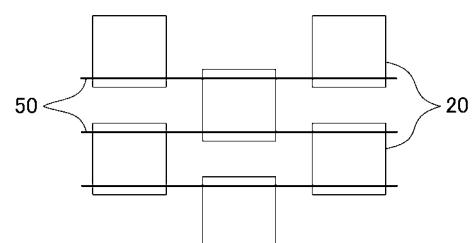

【図13】図13は、下層配線層に一方向に延びるように設けられた電源配線(又は接地配線)によって、上層配線層において千鳥状に配列された配線ブロックにおける電源配線同士(又は接地配線同士)を電気的に接続している様子を模式的に示す平面図である。20

【図14】図14は、従来例に係る半導体装置における信号配線及び電源配線の配置例を示す図である。

【図15】図15は、図14に示す従来例の電源配線パターンを簡素化して模式的に示す上面図である。

【図16】図16は、図14に示す従来例の電源配線パターンを簡素化して模式的に示す断面図である。

【図17】図17は、図15に示す簡素化パターンに対して電源電圧を印加したときの配線抵抗による電圧降下例を示した図である。30

【発明を実施するための形態】

【0028】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置について、図面を参照しながら説明する。

【0029】

図1(a)は第1の実施形態に係る半導体装置の平面図であり、図1(b)は第1の実施形態に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図1(c)は第1の実施形態に係る半導体装置における上側の配線層の配線ブロックを示す図である。また、図2は図1(a)のa-a'線における断面図であり、図3は図1(a)のb-b'線における断面図である。40

【0030】

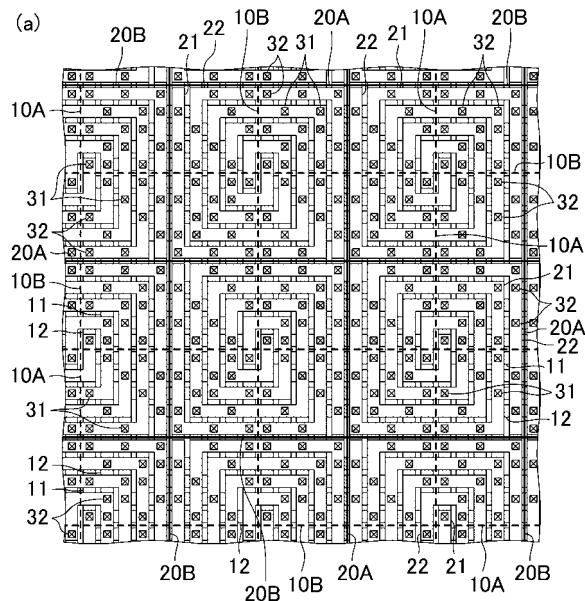

図1(a)に示すように、本実施形態の半導体装置においては、半導体基板(図示省略)の上側に複数の第1配線ブロック10(図中の点線枠内)を有する第1配線層が設けられていると共に、第1配線層の上側に複数の第2配線ブロック20(図中の実線枠内)を有する第2配線層が設けられている。ここで、複数の第1配線ブロック10及び複数の第2配線ブロック20は行列状に配列されていると共に、各第1配線ブロック10と各第2配線ブロック20とは互いにずらして配置されている。具体的には、2×2の行列状に隣接する4つの第1配線ブロック10の集合体の中心が1つの第2配線ブロック20内の中心と一致するように各ブロックが配置されている。言い換えれば、2×2の行列状に隣接

する4つの第2配線ブロック20の集合体の中心が1つの第1配線ブロック10内の中心と一致するように各ブロックが配置されている。尚、後述する他の実施形態及び変形例においても、各ブロックの配置は同様である。

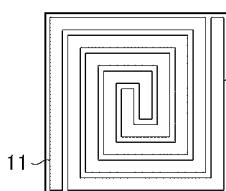

【0031】

また、図1(b)に示すように、各第1配線ブロック10には、電源配線と接地配線とが交互に配置されてなる4重構造のリング状配線が設けられている。具体的には、外側から順にそれぞれリング状の電源配線11、接地配線12、電源配線11及び接地配線12が設けられている。ここで、各電源配線11には電源電圧が印加されており、各接地配線12には接地電圧が印加されている。

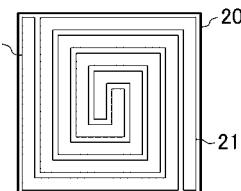

【0032】

また、図1(c)に示すように、各第2配線ブロック20には、電源配線と接地配線とが交互に配置されてなる4重構造のリング状配線が設けられている。具体的には、外側から順にそれぞれリング状の接地配線22、電源配線21、接地配線22及び電源配線21が設けられている。ここで、各電源配線21には電源電圧が印加されており、各接地配線22には接地電圧が印加されている。

【0033】

また、図1(a)、図2及び図3に示すように、各第1配線ブロック10の電源配線11は第1コンタクト31を介して各第2配線ブロック20の電源配線21と電気的に接続されており、各第1配線ブロック10の接地配線12は第2コンタクト32を介して各第2配線ブロック20の接地配線22と電気的に接続されている。ここで、各第1配線ブロック10と各第2配線ブロック20とは互いにずらして配置されているため、隣り合う一対の第1配線ブロック10における電源配線11同士が第2配線ブロック20の電源配線21を介して電気的に接続されると共に、隣り合う一対の第1配線ブロック10における接地配線12同士が第2配線ブロック20の接地配線22を介して電気的に接続される。同様に、隣り合う一対の第2配線ブロック20における電源配線21同士が第1配線ブロック10の電源配線11を介して電気的に接続されると共に、隣り合う一対の第2配線ブロック20における接地配線22同士が第1配線ブロック10の接地配線12を介して電気的に接続される。これによって、チップ全体に亘って電源配線網及び接地配線網が形成される。

【0034】

さらに、図1(a)、図2及び図3に示すように、第1配線層における複数の第1配線ブロック10同士の間には、電源配線11及び接地配線12とは異なり一方向に延びる信号配線13～15が配置されていると共に、第2配線層における複数の第2配線ブロック20同士の間には、電源配線21及び接地配線22とは異なり一方向に延びる信号配線23～25が配置されている。すなわち、本実施形態においては、電源配線及び接地配線とは異なる信号配線についても第1配線層及び第2配線層を用いて形成されている。

【0035】

本実施形態においては、第1配線層の各配線11～15として、例えば厚さ0.3μm程度の銅配線を用い、第2配線層の各配線21～25として、例えば第1配線層の各配線11～15の厚さの5倍の厚さ1.5μm程度の銅配線を用いている。ここで、第1配線層及び第2配線層のいずれにおいても、配線幅は例えば10μm程度であり、配線間隔は例えば2.5μm程度である。すなわち、第1配線層の各配線11～15の抵抗は、第2配線層の各配線21～25の抵抗の約5倍である。

【0036】

以上に説明した本実施形態によると、第1配線層に設けられた電源配線11及び接地配線12のいずれもリング状に形成されているため、従来例のように各配線層において電源配線や接地配線が一方向のみに延びている場合と比較して、電圧降下に方向性が生じる事態を回避することができる。特に、本実施形態のように第1配線層と第2配線層との間で抵抗が異なっている場合、従来例と比べて前述の効果は顕著である。

【0037】

10

20

30

40

50

また、本実施形態によると、第1配線層に設けられた電源配線11及び接地配線12のいずれもが二方向以上に延びる配線として二次元的に形成されているため、従来例のように一方向のみに延びる配線として一次元的に形成された電源配線や接地配線と比べて、各ブロック内の単位面積当たりの抵抗値を約20%程度低減することができる。

【0038】

従って、本実施形態によると、チップ内での局所的な電圧降下を効果的に抑制できる電源配線構造を実現することができる。すなわち、半導体装置内での局所的な電圧降下を効果的に抑制できるので、半導体装置を安定的に動作させることができると共にチップ面積を削減することができる。

【0039】

また、本実施形態によると、第2配線層に設けられた電源配線21及び接地配線22のいずれもリング状に形成されているため、従来例と比較して、前述の本実施形態の効果がより顕著に発揮される。

【0040】

尚、第1の実施形態において、各第1配線ブロック10における電源配線11及び接地配線12の配置順を入れ替えると共に、各第2配線ブロック20における電源配線21及び接地配線22の配置順を入れ替えてよい。また、各第1配線ブロック10及び各第2配線ブロック20に4重構造のリング状配線を設けたが、これに代えて、2重、3重又は5重以上の構造のリング状配線を設けてよい。さらに、各第1配線ブロック10及び各第2配線ブロック20に設けるリング状配線の構造が互いに異なっていてもよい。

【0041】

また、第1の実施形態において、図示はしていないが、第1配線層の信号配線13～15のそれぞれに、第1配線層の下側の基板若しくは配線層又は第1配線層の上側の第2配線層又はパッドとの電気的接続を行うためのコンタクトが形成されていてもよい。また、第2配線層の信号配線23～25のそれぞれに、第2配線層の下側の基板若しくは第1配線層等の配線層又は第2配線層の上側のパッドとの電気的接続を行うためのコンタクトが形成されていてもよい。

【0042】

また、第1の実施形態において、第1配線層における複数の第1配線ブロック10同士の間に信号配線13～15を配置すると共に、第2配線層における複数の第2配線ブロック20同士の間に信号配線23～25を配置した。しかし、これに代えて、信号配線13～15、23～25を配置しなくてもよい。言い換えると、第1配線層には電源配線11及び接地配線12のみを配置し、第2配線層には電源配線21及び接地配線22のみを配置してもよい。このようにすると、各配線層の全体に電源配線及び接地配線を無駄なく設けることができるので、信号配線13～15、23～25を配置する場合と比べて、電源配線及び接地配線の抵抗値をさらに約5%程度低減することができる。

【0043】

(第1の実施形態の変形例)

以下、本発明の第1の実施形態の変形例に係る半導体装置について、図面を参照しながら説明する。

【0044】

図4(a)は第1の実施形態の変形例に係る半導体装置の平面図であり、図4(b)及び(c)は第1の実施形態の変形例に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図4(d)及び(e)は第1の実施形態の変形例に係る半導体装置における上側の配線層の配線ブロックを示す図である。また、図5は図4(a)のa-a'線における断面図であり、図6は図4(a)のb-b'線における断面図である。

【0045】

尚、図4(a)～(e)、図5及び図6において、図1(a)～(c)、図2及び図3に示す第1の実施形態と同一の構成要素には同一の符号を付すことにより、重複する説明を省略する。

10

20

30

40

50

## 【0046】

本変形例が第1の実施形態と異なっている第1の点は、図4(a)～(c)に示すように、第1配線ブロック10として、電源配線11及び接地配線12の配置順が異なる2種類の第1配線ブロック10A及び10Bが交互に隣り合うように配列されていることである。ここで、第1配線ブロック10Aには、外側から順にそれぞれリング状の電源配線11、接地配線12、電源配線11及び接地配線12が配置されてなる4重構造のリング状配線が設けられている。また、第1配線ブロック10Bには、外側から順にそれぞれリング状の接地配線12、電源配線11、接地配線12及び電源配線11が配置されてなる4重構造のリング状配線が設けられている。

## 【0047】

10

また、本変形例が第1の実施形態と異なっている第2の点は、図4(a)、(d)及び(e)に示すように、第2配線ブロック20として、電源配線21及び接地配線22の配置順が異なる2種類の第2配線ブロック20A及び20Bが交互に隣り合うように配列されていることである。ここで、第2配線ブロック20Aには、外側から順にそれぞれリング状の電源配線21、接地配線22、電源配線21及び接地配線22が配置されてなる4重構造のリング状配線が設けられている。また、第2配線ブロック20Bには、外側から順にそれぞれリング状の接地配線22、電源配線21、接地配線22及び電源配線21が配置されてなる4重構造のリング状配線が設けられている。

## 【0048】

20

以上に述べた本変形例によると、第1の実施形態と同様の効果に加えて、次のような効果が得られる。すなわち、隣り合う第1配線ブロック10A及び10B同士の間で電源配線11及び接地配線12の配置順を逆にしているため、電源配線11と接地配線12との間の抵抗差を解消することができる。また、隣り合う第2配線ブロック20A及び20B同士の間で電源配線21及び接地配線22の配置順を逆にしているため、電源配線21と接地配線22との間の抵抗差を解消することができる。

## 【0049】

## (第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置について、図面を参照しながら説明する。

## 【0050】

30

図7(a)は第2の実施形態に係る半導体装置の平面図であり、図7(b)は第2の実施形態に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図7(c)は第2の実施形態に係る半導体装置における上側の配線層の配線ブロックを示す図である。尚、図7(a)～(c)において、図1(a)～(c)に示す第1の実施形態と同一の構成要素には同一の符号を付すことにより、重複する説明を省略する。

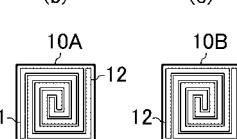

## 【0051】

本実施形態が第1の実施形態と異なる点は、図7(a)～(c)に示すように、各第1配線ブロック10には、それぞれ渦巻き状を有する電源配線11及び接地配線12が1つずつ設けられていると共に、各第2配線ブロック20には、それぞれ渦巻き状を有する電源配線21及び接地配線22が1つずつ設けられていることである。

40

## 【0052】

以上に述べた本実施形態によると、第1の実施形態と同様の効果に加えて、次のような効果が得られる。すなわち、電源配線11及び接地配線12並びに電源配線21及び接地配線22のそれぞれをリング状に形成する場合と同様に、電源配線11及び接地配線12のそれぞれと電源配線21及び接地配線22のそれぞれとを電気的に接続するコンタクトを容易に配置することができる。また、電源配線11及び接地配線12並びに電源配線21及び接地配線22のそれぞれをリング状に形成する場合と比べて、電源配線11及び接地配線12並びに電源配線21及び接地配線22をそれぞれ渦巻き状配線として形成しているため、コンタクト31及び32を介することなく広範囲に亘って各配線を延伸させることができるので、各配線のさらなる低抵抗化が可能となる。

50

## 【0053】

尚、第2の実施形態において、各第1配線ブロック10における電源配線11及び接地配線12の配置順を入れ替えると共に、各第2配線ブロック20における電源配線21及び接地配線22の配置順を入れ替てもよい。また、渦巻き状配線である電源配線11、接地配線12、電源配線21及び接地配線22のそれぞれの巻き数は特に限定されないことは言うまでもない。さらに、各第1配線ブロック10及び各第2配線ブロック20に設ける渦巻き状配線の構造が互いに異なっていてもよい。

## 【0054】

また、第2の実施形態において、各第1配線ブロック10及び各第2配線ブロック20のいずれにも渦巻き状配線を設けたが、これに代えて、各第1配線ブロック10には電源配線11及び接地配線12として、第1の実施形態と同様のリング状配線を設けると共に、各第2配線ブロック20には電源配線21及び接地配線22として、本実施形態と同様の渦巻き状配線を設けてもよい。或いは、各第1配線ブロック10には電源配線11及び接地配線12として、本実施形態と同様の渦巻き状配線を設けると共に、各第2配線ブロック20には電源配線21及び接地配線22として、第1の実施形態と同様のリング状配線を設けてもよい。

10

## 【0055】

また、第2の実施形態において、第1配線層における第1配線ブロック10A及び10Bの間に信号配線を配置すると共に、第2配線層における第2配線ブロック20A及び20Bの間に信号配線を配置してもよい。

20

## 【0056】

(第2の実施形態の変形例)

以下、本発明の第2の実施形態の変形例に係る半導体装置について、図面を参照しながら説明する。

## 【0057】

図8(a)は第2の実施形態の変形例に係る半導体装置の平面図であり、図8(b)及び(c)は第2の実施形態の変形例に係る半導体装置における下側の配線層の配線ブロックを示す図であり、図8(d)及び(e)は第2の実施形態の変形例に係る半導体装置における上側の配線層の配線ブロックを示す図である。

30

## 【0058】

尚、図8(a)～(e)において、図1(a)～(c)に示す第1の実施形態及び図7(a)～(c)に示す第2の実施形態と同一の構成要素には同一の符号を付すことにより、重複する説明を省略する。

## 【0059】

本変形例が第2の実施形態と異なっている第1の点は、図8(a)～(c)に示すように、第1配線ブロック10として、それぞれ渦巻き状配線である電源配線11及び接地配線12の配置の仕方が異なる2種類の第1配線ブロック10A及び10Bが交互に隣り合うように配列されていることである。

## 【0060】

また、本変形例が第2の実施形態と異なっている第2の点は、図8(a)、(d)及び(e)に示すように、第2配線ブロック20として、それぞれ渦巻き状配線である電源配線21及び接地配線22の配置の仕方が異なる2種類の第2配線ブロック20A及び20Bが交互に隣り合うように配列されていることである。

40

## 【0061】

以上に述べた本変形例によると、第2の実施形態と同様の効果に加えて、次のような効果が得られる。すなわち、隣り合う第1配線ブロック10A及び10B同士の間で電源配線11及び接地配線12の配置の仕方を変えているため、電源配線11と接地配線12との間の抵抗差を解消することができる。また、隣り合う第2配線ブロック20A及び20B同士の間で電源配線21及び接地配線22の配置の仕方を変えているため、電源配線21と接地配線22との間の抵抗差を解消することができる。

50

## 【0062】

尚、前記各実施形態（それぞれの変形例を含む：以下同じ）において、電源電圧には複数の電圧があつてもよい。言い換えると、各配線層の各配線ブロックに、異なる2種類以上の電源電圧がそれぞれ印加される2種類以上の電源配線を設けてもよい。

## 【0063】

また、前記各実施形態において、各配線ブロックのサイズは特に限定されるものではないが、例えば約100μmから約400μmまでのサイズで形成してもよい。但し、コンタクト抵抗が高い場合には、コンタクト抵抗の影響を少なくするために、ある程度大きいブロックサイズとすることが望ましい。一方、コンタクト抵抗が低い場合には、複数のリング状配線又は渦巻き状配線等を配置できる限りにおいて小さいブロックサイズとしてもよい。

10

## 【0064】

図9は、前記各実施形態の配線ブロック（具体的には上層配線層である第2配線層の第2配線ブロック）の半導体チップ内での配置の一例を示す平面図である。図9に示すように、方形状の半導体チップ1の周縁部には複数のパッド2が配置されており、パッド2の配置領域の内側に、複数の第2配線ブロック20が半導体チップ1（つまり半導体基板）の各辺が伸びる方向に配列されている。すなわち、各第2配線ブロック20はチップエッジ方向と同じ方向に沿って配置されている。このようにすると、チップエッジ方向における電圧降下を抑制できるので、チップ周縁部に電源供給パッドが均一に配置されている構成に対して有効である。

20

## 【0065】

図10は、前記各実施形態の配線ブロック（具体的には上層配線層である第2配線層の第2配線ブロック）の半導体チップ内での配置の他例を示す平面図である。図10に示すように、正方形状の半導体チップ1の周縁部には複数のパッド2が配置されており、パッド2の配置領域の内側に、複数の第2配線ブロック20が半導体チップ1（つまり半導体基板）の対角線方向、つまりチップエッジ方向に対して45度の方向に配列されている。このようにすると、チップエッジ方向に対して45度方向（チップ対角線方向）における電圧降下を抑制できるので、チップコーナー部に電源供給パッドが多く配置されている構成に対して有効である。尚、この場合、チップエッジに沿って、途中で切断された第2配線ブロック20が配列されるものの、当該第2配線ブロック20における電源配線21及び接地配線22はそれぞれコンタクト31及び32を介して、第1配線層（下層配線層）の電源配線11及び接地配線12と電気的に接続されるので、チップ全体に亘って有効な電源配線網及び接地配線網が形成される。また、図10においては、半導体チップ1が正方形である場合を示したが、半導体チップ1が長方形である場合には、複数の第2配線ブロック20を半導体チップ1（つまり半導体基板）の対角線方向、つまりチップエッジ方向に対して斜め方向に配列すればよい。

30

## 【0066】

尚、図9及び図10において、図示は省略しているが、下層配線層である第1配線層の第1配線ブロック10についても、チップエッジ方向と同じ方向に沿って配列してもよいし、又はチップエッジ方向に対して斜め方向に配列してもよいことは言うまでもない。

40

## 【0067】

また、図9及び図10において、第2配線ブロックが設けられる第2配線層（上層配線層）がパッドと同じチップ最上層である場合を示したが、第2配線層がパッドの直下の配線層であつてもよいし、又は第2配線層とチップ最上層との間にさらに他の配線層が介在していてもよい。

## 【0068】

また、図9及び図10において、半導体チップ1の周縁部にパッド2を配置する場合を示したが、これに代えて、半導体チップ1の全面にパッド（エリアパッド）を配置してもよい。

## 【0069】

50

図11は、前記各実施形態の第1配線層及び第2配線層よりも下層に設けられた他の配線層の構造例を示す断面図である。尚、図11において、図1(a)～(c)、図2及び図3に示す第1の実施形態、図4(a)～(e)、図5及び図6に示す第1の実施形態の変形例、図7(a)～(c)に示す第2の実施形態、又は図8(a)～(e)に示す第2の実施形態の変形例と同一の構成要素には同一の符号を付すことにより、重複する説明を省略する。図11に示すように、電源配線11及び接地配線12が設けられた第1配線層の下側には、電源配線11及び接地配線12よりも配線加工寸法が微細な5層の配線層6A、6B、6C、6D及び6Eが下から順次形成されている。尚、配線層6A～6Eは、トランジスタ等が形成された半導体基板5上に形成されている。また、半導体基板5と配線層6Aとはコントラクト7Aによって電気的に接続されており、配線層6Aと配線層6Bとはコントラクト7Bによって電気的に接続されており、配線層6Bと配線層6Cとはコントラクト7Cによって電気的に接続されており、配線層6Dと配線層6Eとはコントラクト7Dによって電気的に接続されている。

10

#### 【0070】

尚、前記各実施形態において、第1配線層の各配線11～15及び第2配線層の各配線21～25として共に銅配線を用いたが、これに代えて、第1配線層には銅配線を用いる一方、第2配線層にはアルミニウム配線を用いてもよい。この場合、第2配線層に用いるアルミニウム配線はワイヤボンディングに形成されたアルミニウム配線であって、少なくともこの第2配線層に前記各実施形態の電源配線構造を適用することによって、前記各実施形態と同様の効果として、電圧降下に方向性が生じることのない低抵抗の電源配線網及び接地配線網を実現することができる。

20

#### 【0071】

また、前記各実施形態において、配線ブロック10及び20の形状を方形（例えば正方形）に設定したが、配線ブロック10及び20の形状は特に限定されるものではない。配線ブロック10及び20の形状として、例えば三角形、六角形、八角形等の任意の形状を採用した場合にも、各ブロック形状に応じたリング状配線又は渦巻き状配線等を設けることにより、前記各実施形態と同様の効果として、電圧降下に方向性が生じることのない低抵抗の電源配線網及び接地配線網を実現することができる。また、配線ブロック10及び20の形状として、複数の形状を同時に使用してもよいし、配線ブロック10及び20のそれぞれの形状が互いに異なっていてもよい。

30

#### 【0072】

また、前記各実施形態において、配線ブロック10及び20に配置される電源配線11及び接地配線12並びに電源配線21及び接地配線22として、リング状配線又は渦巻き状配線等を配置したが、電源配線11及び接地配線12並びに電源配線21及び接地配線22として配置可能な配線は、少なくとも二方向以上に延びる配線であれば、特に限定されるものではない。図12(a)～(c)はそれぞれ、電源配線11及び接地配線12として、二方向に延びる配線を配置した例を示す平面図である。

#### 【0073】

また、前記各実施形態において、下層配線層である第1配線層に複数の配線ブロック10を行列状に配列すると共に上層配線層である第2配線層に複数の配線ブロック20を行列状に配列した。しかし、これに代えて、例えば図13に示すように、上層配線層である第2配線層に複数の配線ブロック20を千鳥状に配列すると共に、下層配線層である第1配線層に電源配線（又は接地配線）50を一方向に延びるように設けて、部分的に隣り合う配線ブロック20における電源配線同士（又は接地配線同士）を電源配線（又は接地配線）50によって電気的に接続してもよい。すなわち、下層配線層である第1配線層には配線ブロックを設けなくてもよい。逆に、下層配線層である第1配線層に複数の配線ブロック10を千鳥状に配列すると共に、上層配線層である第2配線層に電源配線（又は接地配線）を一方向に延びるように設けて、当該一方向に延びる電源配線（又は接地配線）によって、部分的に隣り合う配線ブロック10における電源配線同士（又は接地配線同士）を電気的に接続してもよい。すなわち、上層配線層である第2配線層には配線ブロックを

40

設けなくてもよい。

### 【産業上の利用可能性】

【 0 0 7 4 】

本発明は、半導体装置内の局所的な電圧降下を効果的に抑制できるものであり、これによって、半導体装置を安定的に動作させることができると共にチップ面積を削減することができるので、有用である。

## 【 符号の説明 】

〔 0 0 7 5 〕

1 半導体チップ

2 パッド

5 半導体基板

6 A、6 B、6 C、6 D、6 E 配線層

7 A、7 B、7 C、7 D コンタクト

10、10 A、10 B 第1配線ブロック

11 電源配線

12 接地配線

13 ~ 15 信号配線

20、20 A、20 B 第2配線ブロック

21 電源配線

22 接地配線

23 ~ 25 信号配線

31 第1コンタクト

32 第2コンタクト

50 電源配線（又は接地配線）

【 图 1 】

【圖 2】

〔 図 3 〕

【図4】

【図5】

【 6 】

(b)

【図7】

(b)

(c)

【図8】

(b)

2)

(d)

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

【図17】

【図16】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 23/522 (2006.01)

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 平野 博茂

大阪府門真市大字門真1006番地 パナソニック株式会社内

(72)発明者 太田 行俊

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 瀧内 健夫

(56)参考文献 特開2004-273844 (JP, A)

特開2008-270319 (JP, A)

特開2009-054702 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/822

H 01 L 21/3205

H 01 L 21/768

H 01 L 21/82

H 01 L 23/522

H 01 L 27/04