(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2007-0093371

(43) 공개일자 2007년09월18일

(51) Int. Cl.

H01L 29/786(2006.01) H01L 21/268(2006.01)

(21) 출원번호 10-2007-0024661

(22) 출원일자 2007년03월13일

심사청구일자 없음

(30) 우선권주장

JP-P-2006-00067270 2006년03월13일 일본(JP)

JP-P-2006-00344129 2006년12월21일 일본(JP)

(71) 출원인

소니 가부시끼가이샤

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

후지노 토시오

일본국 108-0075 도쿄도 미나토구 코난 1-7-1 소

니가부시끼가이샤내

마치다 아키오

일본국 108-0075 도쿄도 미나토구 코난 1-7-1 소

니가부시끼가이샤내

코노 타다히로

일본국 108-0075 도쿄도 미나토구 코난 1-7-1 소

니가부시끼가이샤내

(74) 대리인

김학수, 문경진

전체 청구항 수 : 총 8 항

(54) 반도체 박막의 결정화 방법

## (57) 요 약

형상 정밀도(形狀精度)가 양호하고 또한 양질인 결정립(結晶粒; 결정 입자)을 규칙적으로 배열시키는 것이 가능한 반도체 박막의 결정화 방법을 제공한다.

반도체 박막(薄膜)(3)에 대해서 레이저광(Lh)(에너지 빔)을 소정(所定; 미리 정해진) 속도로 주사(走査)시키면서 연속 조사(照射)하는 것에 의해, 반도체 박막(3)을 레이저광(Lh)의 주사에 따라서 결정화시키는 반도체 박막(3)의 결정화 방법에 있어서, 반도체 박막(3)을 완전 용융(溶融)시킴과 동시에, 레이저광(Lh)의 주사 중심이 레이저광(Lh)의 주사에 수반하여 마지막에 결정화되도록 레이저광(Lh)의 조사 조건을 설정하는 것을 특징으로 하고 있다.

대표도 - 도3

## 특허청구의 범위

### 청구항 1

반도체 박막(薄膜)에 대해서 에너지 빔을 소정(所定; 미리 정해진) 속도로 주사(走査)시키면서 연속 조사(照射)하는 것에 의해, 해당(當該) 반도체 박막을 결정화(結晶化)시키는 반도체 박막의 결정화 방법에 있어서, 상기 반도체 박막을 완전 용융(熔融)시킴과 동시에, 상기 에너지 빔의 주사 중심이 해당 에너지 빔의 주사에 따라서 마지막(最後)에 결정화되도록, 해당 에너지 빔의 조사 조건을 설정(設定)하는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 2

제1항에 있어서,

상기 주사 중심에, 상기 주사 방향에 따른 일련의 결정립계(結晶粒系)를 설치(設)하는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 3

제1항에 있어서,

상기 주사 중심에 겹치(重)지 않는 소정 피치를 유지(保)해서 상기 에너지 빔을 평행하게 주사시키는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 4

제3항에 있어서,

상기 소정 피치는, 인접하는 상기 에너지 빔의 주사 위치에 형성된 결정립의 결정성(性)이 계승(引繼)되는 범위에 설정되는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 5

제4항에 있어서,

상기 주사 중심에, 상기 주사 방향에 따른 일련의 결정립계를 설치함과 동시에, 해당 결정립계의 사이에 상기 에너지 빔의 주사 방향과 반대(逆) 방향으로 볼록(凸)하게 되는 초승달 형상(三日月狀; semi-crescent form)의 결정립을 배열(配列)하는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 6

제1항에 있어서,

상기 에너지 빔의 빔 프로파일을 가우시안 커브(Gaussian curve)로 하는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 7

제1항에 있어서,

상기 에너지 빔을 스포트 빔으로 해서 이용하는 것을 특징으로 하는 반도체 박막의 결정화 방법.

### 청구항 8

제1항에 있어서,

상기 에너지 빔은, 반도체 레이저 발진기(發振器)로부터 발진되는 레이저광인 것을 특징으로 하는 반도체 박막의 결정화 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <12> 본 발명은, 에너지 빔의 조사(照射)에 의해 반도체 박막을 결정화(結晶化)시키는 방법에 관한 것이다.

- <13> 액정(液晶) 표시 장치나 유기 전계 발광소자(有機電界發光素子)를 이용한 유기(EL) 표시 장치와 같은 플랫형(型)의 표시 장치에서는, 복수(複數) 화소의 액티브 매트릭스 표시를 행하기 위한 스위칭 소자로서, 박막 트랜지스터(thin film transistor : TFT)를 이용하고 있다.

- <14> 박막 트랜지스터에는, 다결정 실리콘(poly-Si)을 활성 영역에 이용한 TFT(다결정 실리콘 TFT)와 비정질(非晶質) 실리콘(아몰퍼스(amorphous) Si)을 활성 영역에 이용한 TFT(비정질 실리콘 TFT)가 있다.

- <15> 이 중, 다결정 실리콘 TFT는, 비정질 실리콘 TFT와 비교해서 캐리어의 이동도(移動度)가 10배(倍)에서 100배정도 크고, 온(on) 전류의 열화(劣化; degradation)도 작다고 하는 특징이 있다. 이 때문에, 다결정(多結晶) 실리콘 TFT는, 상기 표시 장치의 스위칭 소자로서 매우 뛰어난 특성을 가지고 있을 뿐만 아니라, 각종 논리 회로(예를 들면, 도미노 논리 회로, CMOS 트랜스미션 게이트 회로)나 이들을 이용한 멀티플렉서, EPROM, EEPROM, CCD, RAM를 구성하는 스위칭 소자로서도 주목되고 있다.

- <16> 이와 같은 다결정 실리콘 TFT의 제조 기술로서, 대개 600°C이하의 저온 프로세스만을 이용하는, 이를바 저온 폴리 실리콘 프로세스가 개발되어, 기판(基板)의 저(低)코스트화(化)가 실현되어 있다.

- <17> 저온 폴리 실리콘 프로세스에서는, 발진(發振) 시간이 극단시간인 펄스 레이저를 이용해서 비정질 실리콘막의 결정화를 행하는 펄스 레이저 결정화 기술이 널리 사용되고 있다. 펄스 레이저 결정화 기술이란, 기판위의 실리콘 박막에 고출력의 펄스 레이저광을 조사하는 것에 의해 순식간(瞬時)에 용융(溶融)시키고, 이것이 응고하는 과정에서 결정화하는 성질을 이용하는 기술이다.

- <18> 예를 들면, 액시머 레이저를 이용한 저온 폴리 실리콘 프로세스에서는, 라인(line) 모양(狀)으로 정형(整形)된 레이저광을, 조금씩 이동시켜서 대부분을 중복시키면서 비정질 실리콘막에 대해서 펄스 조사하고, 동일(同一) 개소(箇所)에 10~20회(回)의 레이저 광 조사를 행한다. 이전에 의해, 활성 영역의 전면에서 결정립(結晶粒; crystal grains) 지름(徑)이 균일화된 다결정이 얻어지도록 하고 있다.

- <19> 또, SLS(Sequential Lateral solidification) 방식의 결정화에 의해 결정립의 위치의 제어를 행하는 방법이 제안되어 있다. 예를 들면, 위상 시프트 마스크를 거쳐서 액시머 레이저광의 위상을 공간적으로 변조함으로써, 조사하는 레이저광에 에너지 밀도 구배(句配; gradient)를 갖게 하고, 이것에 의해서 결정립의 위치 제어를 행하는 방법도 제안되어 있다(하기(下記) 비특허 문헌 1 참조).

- <20> 또, 이와 같은 라인 모양의 레이저광을 이용한 방법 이외에도, Ar가스 등의 스포트 빔 레이저를 이용해서, 폭발적(爆發的) 결정화시키는 것에 의해, 비교적 작은 입경(粒徑; 입자 지름)의 결정을 배열시키는 방법도 제안되어 있다.

- <21> [비특허 문헌 1] 「표면 과학 21」, 2000년, vol. 1, No. 5, p. 278-287.

#### 발명이 이루고자 하는 기술적 과제

- <22> 근년(近年; 최근)에, 상술한 플랫 패널형의 표시 장치에서는, 동영상(動畫; moving image) 특성이나 콘트라스트 특성을 더욱더 향상시키는 것을 목적으로 해서 하이프레임 레이트(high frame-rate)의 액정 디스플레이의 개발이 진행되고, 또 유기 EL디스플레이 등의 자발광형(自發光型; self emitting)의 디스플레이 등의 새로운 표시 장치의 개발도 진행되고 있다. 이것에 따라서, 이와 같은 표시 장치에 대응 가능한 스위칭 소자로서, 급격하게

큰 전류를 흐르게 하더라도 특성 열화가 없고, 또 각 스위칭 소자의 특성 편차(variation)가 작은 TFT의 개발이 요구되고 있다.

<23> 그런데, 상술한 종래의 저온 폴리 실리콘 프로세스에 의해 얻어진 다결정 실리콘 TFT는, 비교적 큰 전류를 흐르게 하기 쉬운 특성으로서 캐리어의 이동도도 크고 특성 열화도 작은 것이 매우 유리한 반면, 비정질 실리콘 TFT와 비교해서 소자 사이의 특성, 특히 초기의 임계값(threshold) 전압이나 온 전류의 편차가 크다. 그리고, 이와 같은 다결정 실리콘 TFT에서의 소자 사이의 특성 편차는, 다결정 실리콘 TFT를 스위칭 소자로 한 표시 장치에서의 휘도 열룩(輝度斑; uneven brightness)의 발생 요인으로 된다.

<24> 여기서, 이상과 같은 다결정 실리콘 TFT에서의 소자 사이의 특성 편차는, 다결정 실리콘 TFT의 채널부에서, 채널 방향(전자가 흐르는 방향)에 존재하는 결정립계(結晶粒界; 결정 입자 경계)의 수(數)의 편차에 의존한다. 이 때문에, 결정립계의 수가 적은 범위에서는, 결정립계의 얼마 안 되는 수의 차이(違; difference)로도 큰 TFT 소자의 편차를 낳(生)는다. 한편, 결정립계의 수가 증가해 감에 따라, 채널부의 결정립계 수가 다소(多少) 다르더라도 TFT 소자의 편차는 작게 억제된다. 따라서, 다결정 실리콘 TFT에서의 특성 편차를 작게 억제하기 위해서는, 형상(形狀)이 고른(uniform) 비교적 작은 사이즈의 결정을 규칙적으로 배치한 다결정 실리콘막을 형성하는 것이 중요해진다.

<25> 그렇지만, 상술한 펠스 레이저 결정화 기술에 널리 사용되고 있는 엑시머 레이저는, 가스 레이저이기 때문에 펠스 사이의 에너지 안정성이 낮다. 이 때문에, 상술한 바와 같이 동일 개소에 10~20회의 레이저 광조사를 행함으로써, 결정립 지름이 균일화(均一化; uniform)된 다결정이 얻어지도록 하고 있지만, 얻어지는 결정립 지름의 균일성은 불충분하다. 또, 엑시머 레이저는 장치 단가가 비싸고, 레이저 투브(발진기)의 교환에 의한 러닝 코스트(running costs)도 비싸다. 또, 상술한 바와 같이 수십회 정도의 되풀이(繰返; 반복) 조사가 필요하기 때문에, 스루풋(throughput)도 낮으므로, 제품의 제조 코스트를 내릴 수 없다고 하는 문제를 안고(抱; 포함하고) 있다.

<26> 또, 결정립 지름의 균일화가 불충분하다라고 하는 문제는, 상기 특히 문헌 1에 기재된 위상 시프트 마스크를 이용한 방법으로서도 마찬가지이다. 게다가, 이와 같은 방법이라면, 위상 시프트 마스크의 제작(作製)에도 비싼 코스트를 요(要)하고, 기판의 대형화가 곤란하다고 하는 문제도 더(加; add)해진다.

<27> 또, Ar가스 등의 스포트 빔 레이저를 이용한 폭발적 결정화 방법은, 고상 전이(固相轉移)에 의한 재 결정화법이기 때문에, 형성된 결정의 질이 나쁘고, 충분한 캐리어의 이동도를 얻을 수가 없다.

<28> 그래서 본 발명은, 형상 정밀도(精度)가 양호하고 또한 양질인 결정립을 규칙적으로 배열시키는 것에 의해, 정밀도 양호한 높은 캐리어 이동도를 나타내는 결정 영역(結晶領域)을 형성하는 것이 가능한 반도체 박막의 결정화 방법을 제공하는 것을 목적으로 한다.

### 발명의 구성 및 작용

<29> 이와 같은 목적을 달성하기 위한 본 발명은, 반도체 박막에 대해서 에너지 빔을 소정속도로 주사시키면서 연속 조사하는 것에 의해, 반도체 박막을 결정화시키는 반도체 박막의 결정화 방법이다. 이 때, 반도체 박막을 완전 용융시킴과 동시에, 에너지 빔의 중심 위치가 해당 에너지 빔의 주사에 따라서 마지막(最後)에 결정화되도록, 해당 에너지 빔의 조사 조건을 설정하는 것을 특징으로 하고 있다.

<30> 이와 같은 반도체 박막의 결정화 방법에서는, 에너지 빔의 주사 방향을 향해 주사 중심 측에 잡아당겨지는(引張; pulled) 상태로 불록(凸)하게 되는 형상의 결정립이 해당 주사 방향에 규칙적으로 배열된 다결정화가 행해진다. 이 결정립의 형상이나 배열 간격은, 에너지 빔의 주사 속도나 조사 에너지 등의 조사 조건에 의해 양호하게 제어된다. 게다가, 에너지 빔의 조사에 의해 반도체 박막을 완전 용해시켜, 액상 성장(液相成長)에 의해 재결정화(再結晶化) 시켜서 얻어진 결정립이므로, 결정의 질도 양호하다.

<31> [발명을 실시하기 위한 최량의 형태]

<32> 이하, 본 발명의 실시의 형태를 도면에 의거해서 상세하게 설명한다. 또, 이하의 실시 형태에서는, 반도체 박막의 결정화 방법, 이 결정화 방법을 이용한 박막 반도체 장치의 제조 방법을 이 순(順)으로 설명한다.

<33> <반도체 박막의 결정화 방법>

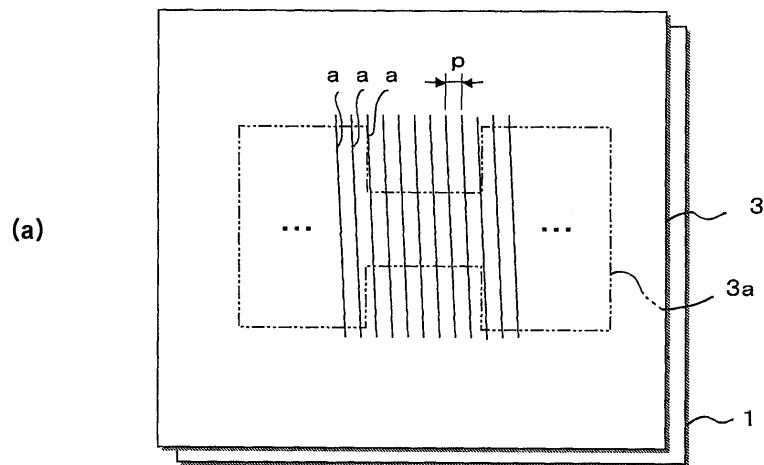

<34> 먼저, 도 1에 도시하는 바와 같이, 박막 반도체 장치를 형성하는 기판(1)을 준비한다. 이 기판(1)으로서는, 실리콘 기판을 비롯해서, 비정질 기판의 유리(glass)나 플라스틱 기판 등의 저융점(低融點) 기판, 석영, 사파이어

기판, 나아가서는 알루미늄이나 스텐레스 등의 금속 기판 등을 이용한다. 또, 이 기판(1)의 1 주면(正面) 상에는, 여기서의 도시는 생략한, 산화막(酸化膜)이나 질화막(窒化膜) 등 절연막(絕緣膜)을 기판(1)에의 열전도(熱傳導)를 방지하기 위한 버퍼층(buffer layer)으로서 설치(設; form)해도 좋고, 또 각종 금속막 등을 설치해도 좋다.

<35> 다음에, 이 기판(1) 상에, 비정질의 반도체 박막(3)을 형성한다. 여기서는, 예로서 PE-CVD(plasma enhancement-chemical vapor deposition) 법에 의한 비정질 실리콘으로 이루어지는 반도체 박막(3)의 형성을 행한다. 이와 같이 해서 얻어진 반도체 박막(3)은, 다량의 수소가 함유(含有)된, 이를바 수소화 비정질 실리콘(a-Si : H)으로 이루어진다. 또, 여기서 형성하는 반도체 박막(3)의 막두께(膜厚)는, 예를 들면 막두께 20nm~100nm인 것으로 한다.

<36> 또한, 반도체 박막(3)의 형성은, 성막(成膜; film-forming) 온도를 낮게 억제할 수 있는 방법이면 상술한 PE-CVD법에 한정되는 것은 아니며, 도포법(塗布法; coating method)에 의해서 행해도 좋다. 이 경우, 폴리실란화합물을 용매에 섞은(混) 혼합물을, 기판(1) 상에 도포 성막하고, 그 후, 건조, 어닐링(annealing)을 행(施)하는 것에 의해 반도체 박막(3)을 형성한다. 그리고, 앞서의 PE-CVD법이나, 여기서 나타낸 도포법 등의 성막 온도가 낮게 억제된 성막 방법에서는, 어느 경우에도 성막 조건에 의해 다소의 변동은 있지만, 0.5atoms%~15atoms%정도의 수소를 함유한 수소화 비정질 실리콘(a-Si : H)으로 이루어지는 반도체 박막(3)이 얻어진다.

<37> 그 후, 필요에 따라서 반도체 박막(3) 중(中)의 과잉(過剩) 수소이온을 이탈(離脫)시키기 위한, 이를바 수소 빼기(水素拔; dehydrogenation; 탈수소화)어닐링 처리를 행한다. 이와 같은 수소 빼기 어닐링 처리로서는, 예를 들면 400°C 부터 600°C의 로(爐)어닐링을 행한다. 다만, 다음에 행하는 결정화를 위한 어닐링 처리가, 반도체 박막(3) 중에서 수소이온을 가스화(化) 팽창시키는 일 없이 레이저광의 조사부로부터 잉여(剩餘; excess) 수소를 제거하도록, 조사 에너지를 조정해서 행해지는 경우에는, 수소 빼기 어닐링 처리를 생략해도 좋다.

<38> 이상(以上)의 이후(後)에, 반도체 박막(3)에 설정한 활성 영역에, 에너지 빔으로서 레이저광(Lh)을 조사하는 결정화 공정을 행한다.

<39> 레이저광(Lh)으로서는, 예를 들면, Ga-N레이저(파장 405nm), Kr레이저(파장 413nm), Ar레이저(파장 488nm, 514.5nm), Nd : YAG 레이저(파장 1.06μm)의 제2 고조파(高調波)(532nm)나 제3 고조파(355nm), Nd : YLF레이저(파장 1.05μm)의 제2 고조파(524nm)나 제3 고조파(349nm), 또는 Yb : YAG 레이저(파장 1.03μm)의 제2 고조파(515nm)나 제3 고조파(344nm) 등을 이용할 수가 있다. 그 밖에도, Ti : Sapphire레이저의 기본파(792nm) 또는 제2 고조파(396nm)를 이용해도 좋다.

<40> 여기에서는, 반도체 박막(3)에 대해서 소정의 속도로 한쪽(一方; one)의 주사 방향(y)에 레이저광(Lh)을 주사시키면서 조사한다. 그리고 특히, 레이저광(Lh)의 조사에 의해서 반도체 박막(3)이 그의 깊이(深) 방향에서 완전 용융 되도록, 반도체 박막(3)의 막두께에 맞추어(合; conformity) 레이저광(Lh)의 조사 조건을 설정하는 것이 중요하다.

<41> 이 때문에, 반도체 박막(3)에 조사하는 레이저광(Lh)의 파장은, 반도체 박막(3)의 막두께와 그 흡수 계수에 의거하여, 반도체 박막(3)의 표면층에서만 흡수되지 않고 깊이 방향 전역에 걸쳐서 흡수될 정도로, 비교적 흡수 계수가 작아지는 파장이 선택된다. 즉, 두께 50nm의 비정질 실리콘으로 이루어지는 반도체 박막(3)을 예를 들면, 파장 350nm~470nm의 레이저광이 바람직하게 이용된다. 이와 같은 파장의 레이저광(Lh)의 발진원(發振源; oscillation source)으로서는, 예를 들면 GaN계의 화합물 반도체 레이저 발진기(器), 또 YAG 레이저 발진기가 대응한다.

<42> 이상과 같은 레이저광(Lh)의 파장 이외의 조사 조건으로서, 레이저광(Lh)을 조사하는 대물 렌즈의 개구수(NA), 레이저광(Lh)의 주사 속도나 조사 에너지 등을 조정하는 것에 의해서도, 반도체 박막(3)을 깊이 방향에서 완전 용융시킨 결정화가 행해지도록 할 수가 있다. 그리고, 비정질의 반도체 박막(3)에 일정 강도(強度) 이상의 레이저광(Lh)을 조사하는 것에 의해 반도체 박막(3)을 완전하게 용융시키는 것이다.

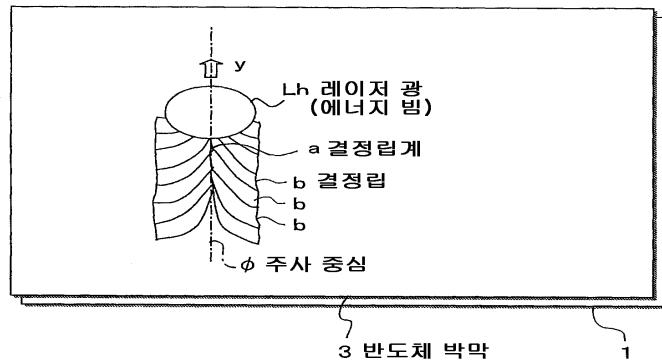

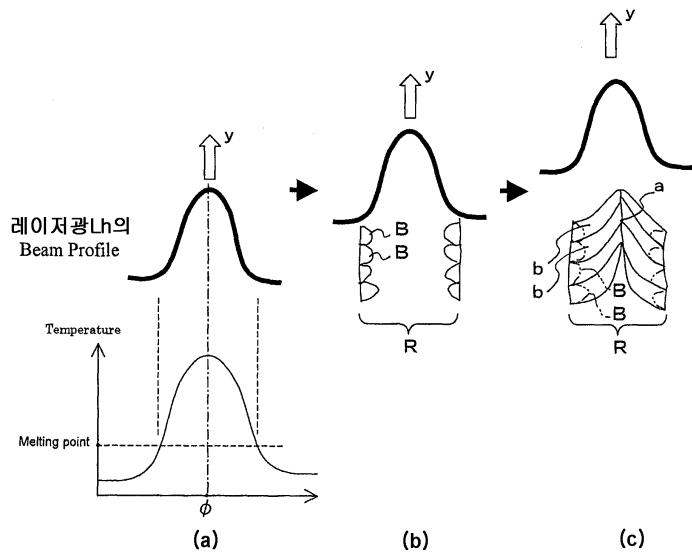

<43> 또 이 결정화 공정에서는, 이상과 같이 선택된 파장의 레이저광(Lh)을, 빔 프로파일이 가우시안 형상(Gaussian form)의 스포트 빔으로서 이용하는 것으로 한다. 이것에 의해, 도 2의 (a)에 도시하는 바와 같이, 레이저광(Lh)의 조사 부분의 온도는, 레이저광(Lh)의 빔 프로파일(Beam Profile)의 가우시안 형상에 대응하고, 레이저광(Lh)의 주사 중심(ψ)에서 가장 높고, 양단(兩端)에서 가장 낮아진다.

<44> 그 때문에, 도 2의 (b)에 도시하는 바와 같이, 레이저광(Lh)을 주사 방향(y)으로 주사하면서 조사하는 것에 의해, 반도체 박막(3)이 완전 용융된 주사로(走査路)(R)에서, 주사 중심(ψ)과 떨어진(離) 면 위치(레이저광의 주

사로(R)의 양측단)로부터 결정 응고가 개시되고, 주사로(R)의 양측단에 일정 수(一定數)의 결정의 종(種)(B)이 발생한다.

<45> 그리고, 도 2의 (c)에 도시하는 바와 같이, 더욱 더 레이저광(Lh)의 주사를 진행시키는 것에 의해, 결정의 종(B)이 주사 방향(y)에 향해서 주사 중심(ψ)축에 잡아당겨지는 상태로 응고가 진행되고, 주사 중심(ψ)이 마지막에 결정화된다. 이 때, 주사 중심(ψ)에서 응고가 회합(會合)하도록, 상술한 조사 조건의 범위에서 더욱 더 레이저광(Lh)의 주사 속도 및 출력을 조정해도 좋다. 이것에 의해, 주사 중심(ψ)으로부터 주사로(R)의 양측에 향해 끝이 넓게(未廣) 넓어지는 반초승달 모양(半三日月狀; semi-crescent form), 즉 초승달을 선대칭(線對稱)이 되는 선으로 2 분할한 형상의 결정립(b)을 얻는다. 또 응고가 회합하는 주사 중심(ψ)에는, 주사 방향(y)에 따른 일련의 결정립계(a)를 형성한다.

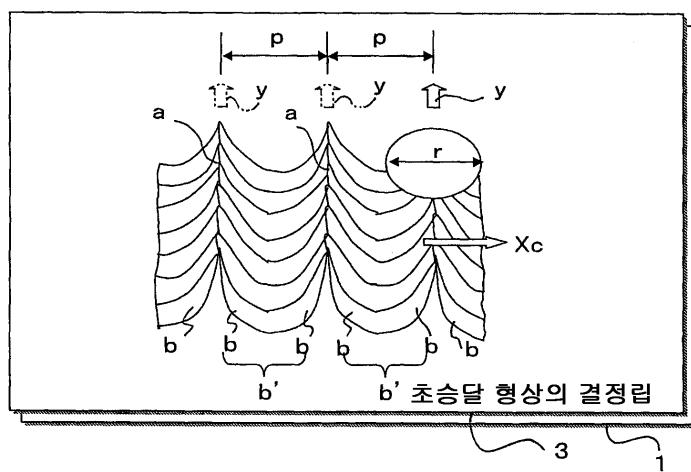

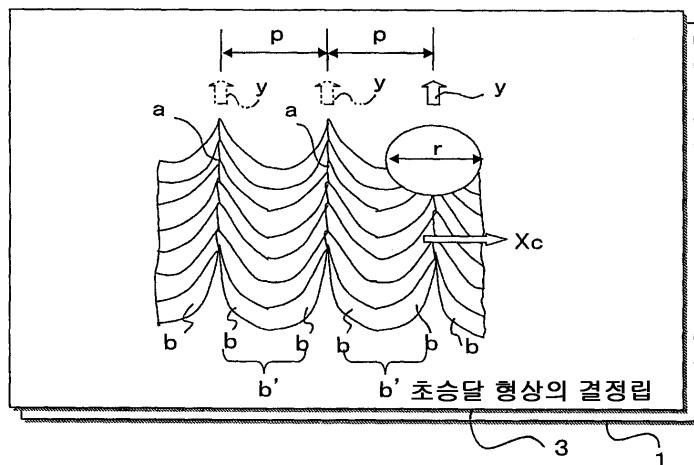

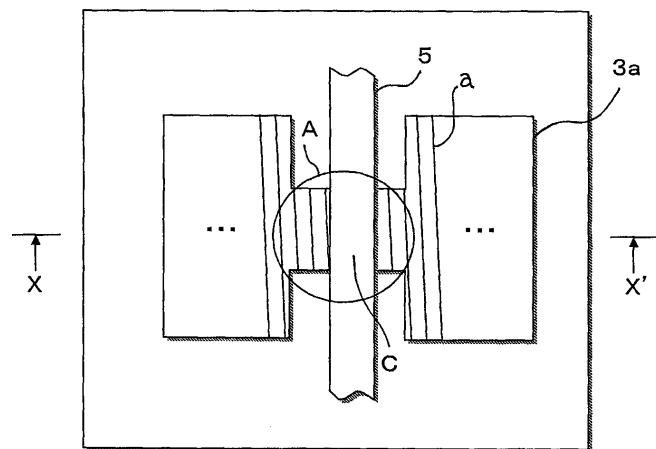

<46> 또한, 도 3에 도시하는 바와 같이, 이 결정화 공정에서는, 기판(1)상의 반도체 박막(3)에 대해서, 레이저광(Lh)을 소정의 피치(p)를 유지(保; kept)해서 평행(平行; parallel)하게 주사시킨다. 이 때, 각 주사에서의 주사 방향(y)은, 일정(一定) 방향인 것으로 한다.

<47> 레이저광(Lh)를 주사시키는 피치(p)는, 주사 중심(ψ)이 인접하는 레이저광(Lh)의 주사로(R)와 겹쳐(重; overlap)지는 일 없이, 또 인접하는 레이저광(Lh)의 주사 위치에 형성된 결정립(b)의 결정성을 계승(引繼; take over)해서 응고가 진행되는 범위에 설정되는 것으로 한다. 이 때문에, 피치(p)는, 대체로 레이저광(Lh)의 직경(r)으로 한 경우, 대체로  $r/2 < p \leq [1.5 \times r]$ 의 범위이고, 레이저광(Lh)의 직경(r)과 동일한 정도의 피치(p)로 일정의 주사 방향(y)에 레이저광(Lh)을 주사시키는 것이 바람직하다.

<48> 이것에 의해, 앞(先)의 레이저광(Lh)의 주사로 형성된 반초승달 모양의 결정립(b)이 종(種)이 되고, 이 주사에 인접시킨 레이저광(Lh)의 주사에서의 결정화가 진행된다. 또, 소정의 피치(p)로 결정립계(a)가 설치(設)되도록 반도체 박막(3)의 다결정화가 진행된다. 그리고, 결정립계(a-a) 사이에는, 반초승달 모양의 결정립(b)을 합체(合體; combining)시킨 초승달 형상의 결정립(b')이 결정립계(a)의 연장 설치(延設; extension) 방향을 따라서 배열 형성된다. 이 결정립(b')은, 레이저광(Lh)의 주사 방향(y)과 반대 방향에 볼록(凸)하게 되는 초승달 형상이 된다.

<49> 여기서, 레이저광(Lh)을 평행하게 주사시키는 피치(p)(즉 결정립계 (a)의 피치인 주기)는, 다음에 설명하는 박막 반도체 장치의 채널부에 설치되는 결정립계(a)의 갯수(本數)를 규정하는 중요한 팩터(factor; 요인)로 된다. 즉, 이후에 자세하게 설명하는 바와 같이, 박막 반도체 장치의 채널부에 설치되는 결정립계(a)의 갯수(周期數)는, 캐리어 이동도를 유지할 수 있는 범위에서 트랜지스터 특성의 편차를 균일화할 수 있을 정도로 많이 설정되는 것이 바람직하지만, 또 여기서는 프로세스의 택트 타임(tact time)을 손상(損; impeding)시키지 않는 범위에서 보다 많은 갯수의 결정립계(a)가 채널부에 설치되도록, 박막 반도체 장치의 설계에 맞추어 피치(p)가 설정되어 있는 것으로 한다. 그리고, 이 피치(p)에 맞추어, 피치(p)방향(주사 방향(y)과 수직인 방향)에서의 레이저광(Lh)의 스포트 지름(r)이 설정되는 것으로 한다.

<50> 구체적으로는, 이후(後)의 실시예에서도 설명하는 바와 같이, 채널부에는, 채널폭 방향으로 연장 설치된 결정립계(a)가 25개 정도 설치되도록, 채널 길이(長)에 맞추어 피치(p)가 설정되는 것이 바람직하다.

<51> 또, 상술한 결정화 공정에서는, 레이저광(Lh)의 조사에 의해서 형성되는 결정립계(a)의 특성을 일정화 시키는 것이 지극히 중요하다. 결정립계(a)의 특성을 일정화하는 요인(要因; factor)으로서는, 각 조사 위치에서의 레이저의 조사 에너지 밀도가 일정한 것, 주사 속도가 일정한 것, 레이저광(Lh)의 피치(p)가 일정한 것, 반도체 박막(3)의 막두께가 균일한 것 등이 요구된다.

<52> 또, 레이저광(Lh)의 조사 에너지 밀도를 일정하게 하기 위해서, 적어도 활성 영역에 대해서 레이저광(Lh)을 조사하고 있는 동안에 있어서는, 레이저광(Lh)이 연속 발진된 상태로 되어 있는 것이 바람직하다. 여기서, 연속 발진이라 함은, 반도체 박막(3)의 온도가 저하하지 않는 범위의 휴지(休止; pause)(예를 들면 50ns이하의 휴지)가 있는 경우도 포함하는 것으로 한다. 또, 레이저광(Lh)의 조사 에너지 밀도를 일정하게 해서 상술한 조사를 행하기 위해서는, 에너지의 피드백 기능이나 포커스 서보 기능을 구비한 레이저광의 조사 장치를 이용하는 것이 바람직하다. 에너지의 피드백 기능이나 포커스 서보 기능은 패디스크 등의 컷팅 머신(cutting machines) 등에서 사용되는 공지(公知)의 기술로 구축되는 것이 가능하다.

<53> 또, 반도체 박막(3)에 대한 레이저광(Lh)의 조사는, 레이저 조사의 주사 속도가 일정하게 되는 영역에서 설정한다.

<54> 그리고, 반도체 박막(3)에 대한 레이저광(Lh)의 조사 위치의 이동은 상대적으로 좋고, 고정된 레이저광의 조사

위치에 대해서 반도체 박막이 형성된 기판측을 이동시켜도 좋고, 고정된 기판에 대해서 레이저광의 조사 위치를 이동시켜도 좋다. 또, 기판(1)과 레이저광의 조사 위치와의 양쪽(良方 ; both)을 이동시켜도 좋다.

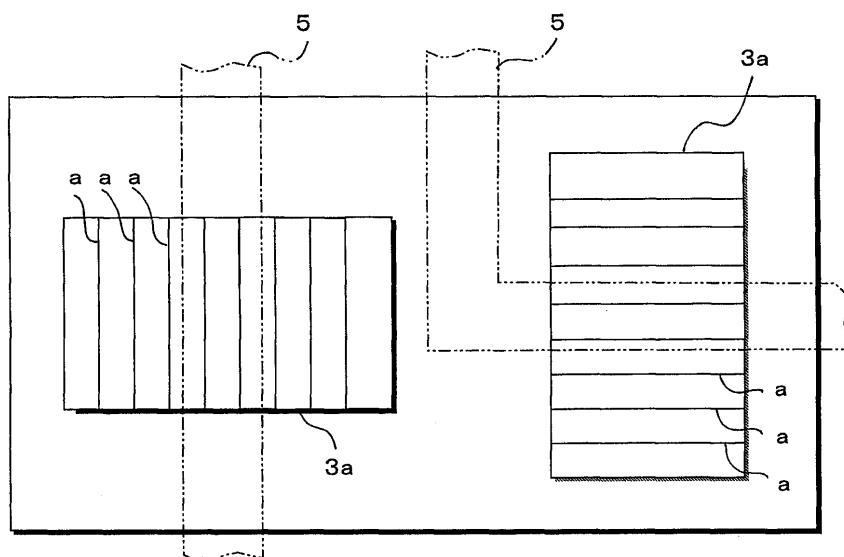

<55> 또, 상술한 결정화 공정에서의 레이저광(Lh)의 평행한 주사는, 하나의 레이저 발진기를 이용해서 순차(順次) 행해도 좋고, 복수의 레이저 발진기를 이용해서 행해도 좋다. 또, 표시 장치를 구동하기 위한 박막 트랜지스터의 제작을 생각한 경우, 복수의 활성 영역에 대해서 동시에 행해지는 것이 바람직하다. 다시말해, 기판(1)의 표면측에 설정 배열된 복수의 활성 영역에 대해서 레이저광(La)을 동시에 다점(多点) 조사하는 것에 의해, 복수의 활성 영역에 대해서 결정화 공정을 동시에 행할 수 있는 것이, 생산성을 고려한 경우에는 바람직한 방법이다.

<56> 이와 같은 레이저광(Lh)의 다점 조사를 실현하기 위해서는, 레이저광의 발진원으로서 반도체 레이저 발진기가 매우 적합(好適; appropriately)하게 이용된다. 반도체 레이저 발진기는, 액시머 레이저나 YAG 레이저 등의 다른(他) 레이저 발진기와 비교해서 매우 소형이기 때문에, 하나의 장치 내에 복수 배치가 가능하며, 또한 연속 조사로 정격(定格) 200mW의 출력이 가능하다.

<57> 반도체 레이저 발진기를 이용하는 것에 의해, 대면적화(大面積化)에 대응해서 반도체 레이저의 갯수를 늘림으로써 기판 사이즈에 대해서 유연(柔軟)하게 장치 설계가 대응하는 것이 가능하게 된다. 이 때문에, 대형 기판상에 같은(同) 성능의 트랜지스터를 다수 늘어놓은 구조를 얻을 수 있고, 연구 레벨로 보고가 있는 바와 같은 마스크를 이용해서 입계(粒界)를 제어하는 방법에 비해 대면적으로 균일한 특성의 트랜지스터를 형성하는 것에 유리하다.

<58> 또, 이상의 결정화 공정은, 불활성 가스 분위기 중에 한정되지 않고, 대기 분위기 중에서 행해져도 좋다. 대기 분위기 중에서 행하는 것에 의해, 장치 전체의 대형화가 방지된다.

<59> 이상 설명한 결정화 방법에 의하면, 레이저광(Lh)의 주사 방향(y)에 향해 주사 중심( $\Psi$ )측에 잡아 당겨지는 상태로 보록(凸)하게 되는 형상의 결정립(b)이, 해당 주사 방향(y)으로 규칙적으로 배열된 다결정화가 행해진다. 이 결정립(b)의 형상이나 배열 간격은, 레이저광(Lh)의 파장, 주사 속도, 조사 에너지 등의 조사 조건에 의해 양호하게 제어할 수가 있다. 게다가, 결정립(b)은, 레이저광(Lh)의 조사에 의해서 반도체 박막(3)을 완전 용융시키고, 액상(液相)성장에 의해 재결정화(再結晶化)시켜서 얻어진 결정립이기 때문에, 결정의 질(質)도 양호하다.

<60> 또, 레이저광(Lh)을 주사시키는 피치(p)를 조정하는 것에 의해, 인접하는 레이저광(Lh)의 주사 위치에 형성된 결정립(b)의 결정성을 계승해서 응고를 진행시키고, 피치(p)로 배치된 결정립계(a-a)사이에 반초승달 모양의 결정립(b)을 합체시킨 초승달 형상의 결정립(b')을 형성 할 수가 있다. 이것에 의해, 주사 방향(y)과 대략(略) 수직인 방향에도 규칙적으로 결정립(b')을 배열시키는 것이 가능하다.

<61> 따라서, 형상 정밀도가 양호하고 또한 양질인 결정립이 규칙적으로 배열되는 것에 의해, 높은 캐리어 이동도가 고정밀도로 제어된 다결정성 영역을 반도체 박막에 형성하는 것이 가능하다.

#### <박막 반도체 장치의 제조 방법>

<63> 다음에, 이상과 같은 결정화 방법에 계속(繼)해서 행해지는 박막 반도체 장치의 제조 방법을 설명한다. 여기서는, 동일한 기판(1)상에 복수의 박막 트랜지스터 TFT를 설치해서 이루어지는 반도체 장치의 제조 방법을 설명한다. 또한, 도면에서는, 주로 하나의 박막 트랜지스터 형성 부분만을 도시한다.

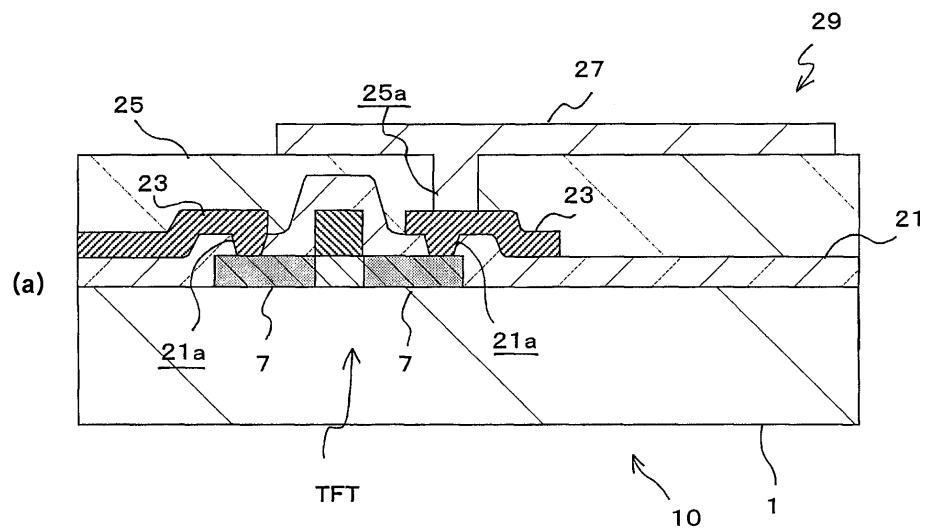

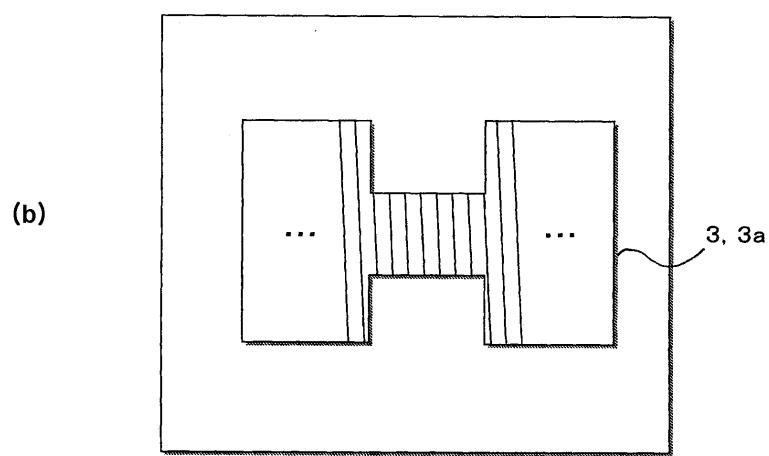

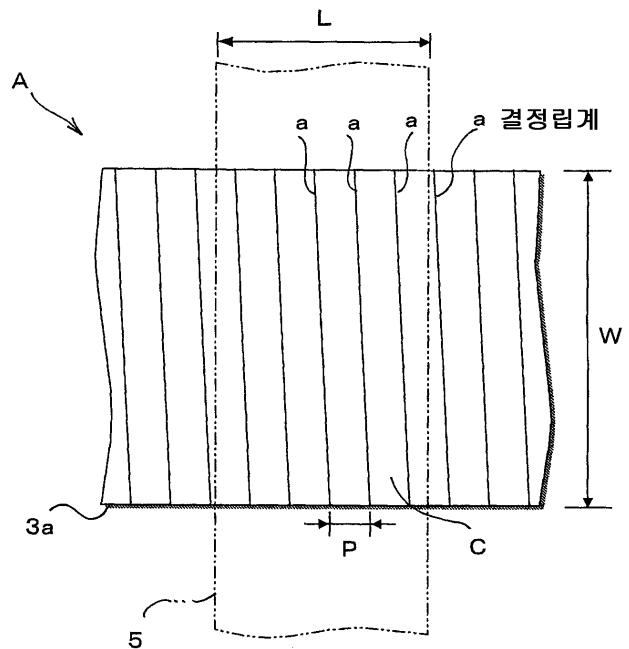

<64> 먼저, 도 4의 (a)에 도시하는 바와 같이, 기판(1)상의 반도체 박막(3)에 설정한 각 활성 영역(3a)의 전면(全面)을, 상술한 결정화 방법에 의해서 선택적으로 결정화한다. 그리고, 각각의 활성 영역(3a) 내에, 활성 영역(3a)을 가로지르는(橫切) 상태에서 결정립계(a)를 평행하게 배열시킨다. 이 결정립계(a)는, 상술한 바와 같이 소정의 피치(p)로 배열된다.

<65> 다음에, 도 4의 (b)에 도시하는 바와 같이, 결정화시킨 활성 영역(3a)을 남기는(殘) 바와 같은 소정 형상으로 반도체 박막(3)을 패턴 에칭하고, 각 활성 영역(3a)을 소정 형상의 섬 모양(島狀)으로 분할해서 소자(素子) 분리한다. 이 경우, 도시한 바와 같이, 활성 영역(3a) 주위에 결정화시키고 있지 않은 반도체박막(3) 부분이 남지 않도록, 반도체 박막(3)을 패턴 에칭 해도 좋다. 또, 활성 영역(3a)의 주위에 결정화시키고 있지 않은 반도체 박막(3) 부분이 남도록, 반도체 박막(3)을 패턴 에칭해도 좋다. 이 경우, 섬 모양으로 패터닝된 영역내의 결정화된 영역 모두가 활성 영역으로 되고, 그 주위에 남겨진 비결정 영역은 분리 영역으로 된다. 또한, 이와 같은 반도체 박막(3)의 패턴 에칭은, 상술한 결정화 공정 전에 행해도 좋다. 이 경우, 활성 영역(3a)의 예정으

로 되는 영역을 포함하는 섬 모양으로 패터닝된 각 반도체 박막(3)에 대해서, 상술한 결정화 공정이 행해지게 된다.

<66> 다음에, 패터닝된 활성 영역(3a)을 덮는(覆; cover) 상태에서 기판(1)의 상부에 게이트 절연막(도시생략)을 형성한다. 이 게이트 절연막은, 산화 실리콘이나 질화 실리콘으로 이루어지는 것으로 좋고, 통상의 PE-CVD에 의한 공지의 방법으로 성막가능하며, 그 밖에도 도포형 절연층으로서 공지의 SOG 등의 성막을 행해도 좋다. 또한, 이 게이트 절연막의 형성은, 반도체 박막(3)을 패턴 예칭 하기 전에 행해도 좋다.

<67> 다음에, 도 5에 도시하는 바와 같이, 섬 모양으로 분할한 각 활성 영역(3a)의 중앙부를 가로지르는 형상의 게이트 전극(5)을, 게이트 절연막 상에 형성한다. 여기서는, 결정립계(a)의 연장 설치 방향을 따라서, 게이트 전극(5)을 형성하는 것이 중요하다. 도 5에서의 A부의 확대도를 도 6에 도시한다.

<68> 이들 도면에 도시하는 바와 같이, 게이트 전극(5)은, 활성 영역(3a)에서 소정의 폭(W)으로 설계된 부분을 가로지르도록 설치되어 있고, 게이트 전극(5)이 가로지르는 부분의 활성 영역(3a)의 폭이 채널 폭(W)으로 된다. 다시 말해, 결정립계(a)는, 게이트 전극(5) 하부의 채널부(C)를, 채널 폭(W)의 방향으로 가로지르는 상태로 설치되게 된다.

<69> 또, 게이트 전극(5)의 선폭(線幅)(즉 채널 길이(L)에 대응한다)은, 여기서 형성하는 박막 트랜지스터의 규격에 의거하여 설계되어 있으며, 그의 하부에 소정 갯수의 결정립계(a)가 채널부(C)를 채널 폭(W) 방향으로 가로지르도록 배치되어 설정되어 있는 것으로 한다. 그리고, 동일 특성의 박막 트랜지스터이면, 채널부(C)에는, 대략 동일 갯수의 결정립계(a)가 설치되어 있는 것이 중요하다. 여기서 대략 동일 개수라 함은, 소정 갯수에 대해서  $\pm 1$ 개의 범위인 것이 바람직하다.

<70> 채널부(C)에 설치되는 결정립계(a)의 수는, 소정 갯수에 대한 실제의 갯수의 비율의 편차가 작을 수록, 박막 트랜지스터의 특성 편차를 균일화할 수 있다. 이 때문에, 채널부(C)에 설치되는 결정립계(a)의 갯수는 2개 이상으로 많은 쪽이 좋다. 구체적으로는, 이후의 실시예에서도 설명하는 바와 같이, 채널부(C)에는, 채널 폭(W) 방향으로 연장설치 된 결정립계(a)가 25개 정도 설치되도록, 채널 길이(L)에 맞추어 피치(p)가 설정되는 것이 바람직하다. 다만, 채널부(C)에서 채널 길이(L)방향을 가로지르는 결정립계(a)가 많을 수록, 채널 길이(L)방향에서의 캐리어 이동도가 낮아지기 때문에, 캐리어 이동도가 어느 정도 높게 유지되는 범위에서 결정립계(a)의 갯수가 많을 수록 좋다.

<71> 또 이상과 같이, 각 활성 영역(3a)에 설치된 결정립계(a)에 대해서 소정 상태로 해서 게이트 전극(5)을 형성하는 것이 중요하다. 이 때문에, 앞서의 결정화 공정에서는, 도 7에 도시하는 바와 같이, 게이트 전극(5)의 배선 방향에 맞추어 각각의 활성 영역(3a)에서의 레이저광(Lh)의 주사 방향을 설정하고, 결정립계(a)의 연장설치 방향을 게이트 전극(5)의 배선 방향에 일치시키는 것으로 한다.

<72> 이상의 게이트 전극(5)을 형성하려면, 먼저, 스퍼터법 또는 증착법에 의해, 예를 들면 알루미늄으로 이루어지는 전극 재료층을 성막하고, 다음에 리소그래피법에 의해서 이 전극 재료층 상에 레지스트 패턴을 형성한다. 그 후, 이 레지스터 패턴을 마스크로 이용해서 전극 재료층을 예칭하는 것에 의해, 게이트 전극(5)을 패턴 형성한다.

<73> 또한, 게이트 전극(5)의 형성은, 이와 같은 수순(手順; procedure)에 한정되는 것은 아니며, 예를 들면 금속 미립자(微粒子)를 도포해서 인쇄하는 수법(手法)으로 해도 좋다. 또, 게이트 전극(5)을 형성할 때의 전극 재료층의 예칭에서는, 계속해서 게이트 절연막을 예칭해도 좋다.

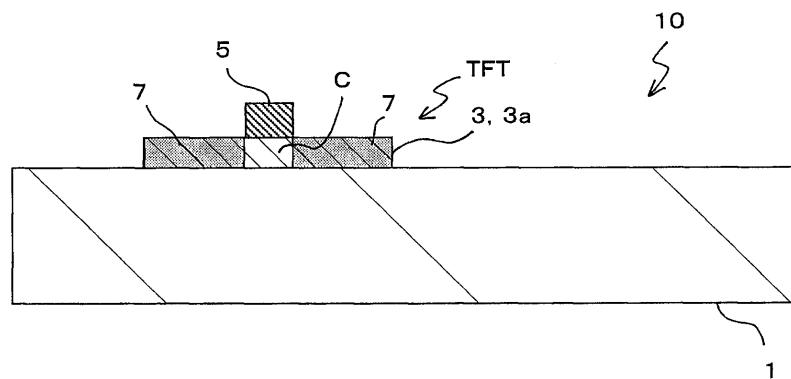

<74> 다음에, 도 8의 단면도에 도시하는 바와 같이, 게이트 전극(5)을 마스크로 이용한 이온 임플란테이션(implantation; 주입)과 그 후의 어닐링 처리에 의해, 활성 영역(3a)에 자기 정합적(自己整合的)으로 불순물이 도입된 소스·드레인(7)을 형성한다. 또한, 도 8은, 도 5에서의 X-X' 방향의 단면에 대응하고 있다.

<75> 이것에 의해, 게이트 전극(5)의 하부에는 결정화된 활성 영역(3a)에서 불순물이 도입되지 않는 부분으로 이루어지는 채널부(C)가 형성된다. 이들 소스·드레인(7) 및 게이트 전극(5)의 하부의 채널부(C)는, 반도체 박막(3)을 결정화시킨 다결정 실리콘으로 구성되기 때문에, 이상에 의해서 다결정 실리콘 박막을 이용한 톱 게이트(top gate)형(型)의 박막 트랜지스터 TFT(즉, 다결정 실리콘 TFT)가 동일 기판(1) 상에 복수 설치된 박막 반도체 장치(10)가 얻어진다.

<76> 그리고, 이와 같은 박막 트랜지스터 TFT를 스위칭 소자로서 이용한 표시 장치로서, 예를 들면 액정표시 장치를 제작하는 경우에는, 이하의 공정을 더 행한다.

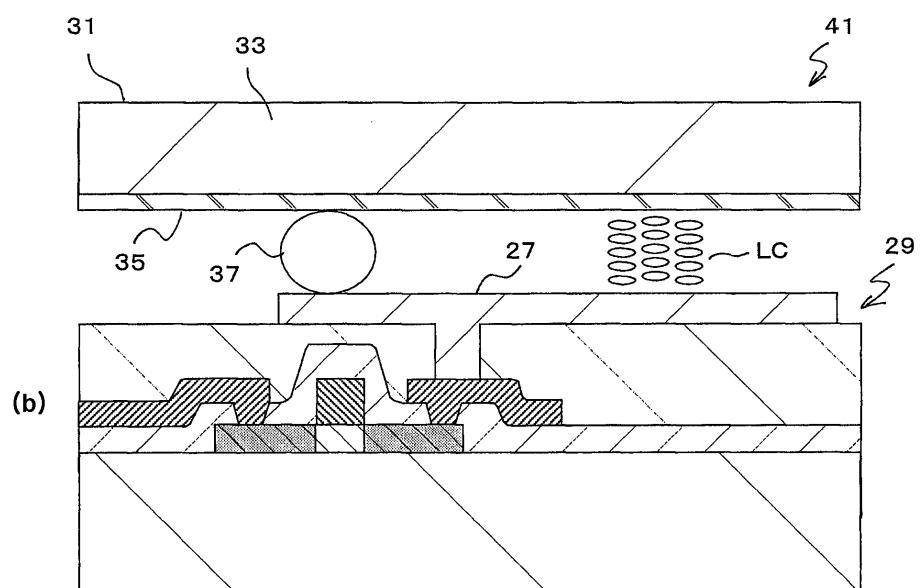

- <77> 먼저, 도 9의 (a)에 도시하는 바와 같이, 박막 반도체 장치(10)의 기판(1) 상에, 박막 트랜지스터 TFT를 덮는 상태에서 충간 절연막(21)을 형성한다. 다음에, 이 충간 절연막(21)에 박막 트랜지스터 TFT의 소스·드레인(7)에 도달하는 접속 구멍(21a)을 형성한다. 그리고, 이 접속 구멍(21a)을 거쳐서 소스·드레인(7)에 접속된 배선(23)을, 충간 절연막(21) 상에 형성한다.

- <78> 그 다음에, 배선(23)을 덮는 상태에서 평탄화(平坦化) 절연막(25)을 형성하고, 배선(23)에 도달하는 접속 구멍(25a)를 평탄화 절연막(25)에 형성한다. 다음에, 이 접속 구멍(25a)과 배선(23)을 거쳐서 소스·드레인(7)에 접속된 화소 전극(27)을, 평탄화 절연막(25) 상에 형성한다. 이 화소 전극(27)은, 액정 표시 장치의 표시 타입에 따라서 투명 전극 또는 반사 전극으로서 형성한다. 또한, 도면은 1화소의 요부 단면(要部斷面)으로 되어 있다.

- <79> 그 후, 여기서의 도시는 생략했지만, 화소 전극(27)을 덮는 배향막(配向膜; orientation film)을 평탄화 절연막 상에 형성하고, 구동 기판(29)을 완성시킨다.

- <80> 한편, 도 9의 (b)에 도시하는 바와 같이, 구동 기판(29)에 대향 배치시키는 대향 기판(31)을 준비한다. 이 대향 기판(31)은, 투명 기판(33) 상에 공통 전극(35)을 설치하고, 또 여기서의 도시를 생략한 배향막으로 공통 전극(35)을 덮어서 이루어진다. 또한, 공통 전극(35)은 투명 전극으로 이루어지는 것으로 한다.

- <81> 그리고, 구동 기판(29)과 대향 기판(31)을, 화소 전극(27)과 공통 전극(35)을 서로 마주보게(向合) 한 상태에서, 스페이서(37)를 거쳐서 대향(對向; face-to-face relation) 배치한다. 그리고, 스페이서(37)에 의해서 소정 간격으로 유지된 기판(29, 31) 사이에 액정상(液晶相)(LC)을 충전 봉지(充填封止; sealedly packing)하고, 액정표시 장치(41)를 완성시킨다.

- <82> 또한, 상기 구성의 구동 기판(29)을 이용해서 유기 EL표시 장치를 제작하는 경우에는, 구동 기판(29)에 설치된 화소 전극을 양극(陽極)(또는 음극(陰極))으로 하고, 이 화소 전극 상에 정공 주입층(正孔注入層), 발광층, 전자 수송층(電子輸送層) 등의 필요 기능을 가지는 유기층을 적층시키고, 또 유기층 상에 공통 전극을 음극(또는 양극)으로서 형성하는 것으로 한다.

- <83> 이상 설명한 본 실시형태의 결정화 방법을 이용해서 얻어진 박막 반도체 장치(10)는, 도 5 및 도 6을 참조하면, 게이트 전극(5)을 따라서 연장설치된 결정립계(a)가, 채널부(C)를 가로지름과 동시에 채널 길이(L)방향으로 주기적으로 배치된 구성으로 함으로써, 채널부(C)를 통과하는 캐리어는, 반드시 소정 피치(p)로 배치된 결정립계(a)를 가로질러서 이동하게 된다. 이 때문에, 이 피치(p)를 제어하는 것에 의해, 박막 반도체 장치(1)에서의 박막 트랜지스터 TFT의 트랜지스터 특성(캐리어 이동도)을 정밀도 양호하게 제어하는 것이 가능하게 된다. 그리고, 피치(p)의 크기나 채널부(C)에 배치되는 결정립계(a)의 수를 일치시킴으로써, 복수의 소자에서의 캐리어 이동도의 편차가 억제된다. 다시말해, 이 박막 반도체 장치(10)에서는, 도 3에 도시하는 바와 같이, 캐리어는 이동 방향(Xc)에 결정립계(a)를 가로지르도록 이동하는 것이다. 그리고, 이 결정립계(a)는, 결정화시(際)에 마지막에 응고하는 부분이고 불순물이 집중되어 있기 때문에, 반초승달 모양의 결정립(b)의 주사 방향(y) 사이의 결정립계보다도 명확한 입계가 되어 있다. 이 때문에, 이와 같은 명확한 결정립계(a)를 소정 개수만큼 가로지르도록 캐리어가 이동하는 것에 의해, 이동 방향(Xc)과 수직인 방향(즉 주사 방향(y))을 채널 길이(L)방향으로서 설계된 트랜지스터와 비교해서, 박막 트랜지스터 TFT의 트랜지스터 특성(캐리어 이동도)이 정밀도 양호하게 제어되는 것이다.

- <84> 게다가, 결정립계(a-a) 사이의 결정 상태는, 결정립계(a-a) 사이에 걸치는 크기의 결정립(b')이 결정립계(a)에 따라 배열되어 있다. 이 때문에, 비정질의 영역을 포함하지 않고 소자 특성의 열화가 억제된다. 또, 결정립계(a-a) 사이에서는, 캐리어가 결정립(b' - b') 사이의 입계를 통과하는 일이 없기 때문에, 채널 길이(L)방향의 캐리어 이동도가 높게 유지된다.

- <85> 따라서, 이와 같은 박막 반도체 장치에 형성된 각 박막 트랜지스터 TFT를 화소의 스위칭 소자로서 이용해서 표시 장치를 구성하는 것에 의해, 표시부에서의 휙도 얼룩이나 색 얼룩(色斑; color shading)을 방지하는 것이 가능하게 된다.

- <86> 또한, 상술한 실시형태에서는, 도 3을 이용해서 설명한바와 같이, 레이저광(Lh)을 주사시키는 피치(p)를, 주사 중심(Ψ)이 인접하는 레이저광(Lh)의 주사로(R)에 겹쳐지는 일 없고, 또 인접하는 레이저광(Lh)의 주사 위치에 형성된 결정립(b)의 결정성을 계승하여 응고가 진행되는 범위에 설정하는 것으로, 피치(p)로 배치된 결정립계(a-a) 사이에 걸치는 입경의 결정립(b')이 결정립계(a)의 연장설치 방향으로 배열되도록 반도체 박막을 다결정화시키는 방법을 설명했다. 그렇지만 본 발명으로서는, 인접하는 레이저광(Lh)의 주사 위치에 형성된 결정립

(b)의 결정성을 계승하지 않고 응고가 진행되도록, 레이저광(Lh)을 주사시키는 피치(p)를 설정해도 좋다. 이 경우에는, 소정 피치(p)로 설치된 결정립계(a-a) 사이에, 결정립(b), 비정질부, 결정립(b)이 이 순(順)으로 주기적으로 설치되도록, 반도체 박막(3)의 다결정화가 행해진다. 이와 같은 결정화로서도, 소정 피치(p)의 결정립계(a-a) 사이에, 규칙적으로 결정립계(b)를 배열한 결정화가 행해진다. 또, 반도체 박막을 완전 용융시켜 액상 성장시켜서 얻어진 결정립(b)이기 때문에, 결정의 질도 양호하다.

<87> 그리고, 이와 같은 비정질부(非晶質部)를 남겨서 결정화된 활성 영역으로서도, 상술한 실시형태와 마찬가지로 결정립계(a)에 따라서 게이트 전극을 설치한 구성으로 하는 것에 의해, 결정립계(a)의 피치(p)에 의해 트랜지스터 특성의 정밀도를 고정밀도로 제어하고, 특성 편차가 작은 박막 트랜지스터 TFT를 얻는 것이 가능하다.

<88> 또, 상술한 실시 형태에서는, 본 발명의 다결정화 방법을 적용해서 박막 트랜지스터를 구비한 박막 반도체 장치를 제작하는 방법을 설명했다. 그렇지만, 본 발명의 다결정화 방법은 박막 트랜지스터의 제조 방법에의 적용에 한정되는 것은 아니며, 다른 전자 소자의 제조 방법에도 적용 가능하다. 어느 경우로서도, 결정립계(a)를 가로지르는 방향으로 전류를 흐르게 하도록 설정하는 것에 의해, 특성 정밀도가 양호한 전자 소자를 얻을 수가 있다.

<89> 또, 이상의 실시형태에서 예시한 재료, 원료, 프로세스, 및 수치 등은 어디까지나 1예에 불과하며, 필요에 따라서 이들과 다른 재료, 원료, 프로세스, 및 수치를 이용해도 좋다.

<90> [실시예]

<91> 이하, 본 발명의 실시예를 도 3에 의거하여 설명한다.

<92> <실시예 1>

<93> 먼저, 석영 유리 기판 상에, 플라스마 CVD법에 의해서 막두께 120nm의 산화 실리콘막을 성막해서 이것을 기판(1)으로 했다. 이 기판(1) 상에, 플라스마 CVD법에 의해서 막두께 50nm의 비정질 실리콘으로 이루어지는 반도체 박막(3)을 성막했다. 다음에, 반도체 박막(3) 중의 과잉 수소 이온을 이탈시키기 위해서, 진공중에서 500°C, 1시간의 어닐링 처리(수소 빼기 어닐링 처리)를 행했다.

<94> 그 후, 이 반도체 박막(3)에 대해서, 직경  $r=$  약 500nm, 기판면에서의 조사 에너지(판면(板面) 조사 에너지) 12mW, 대물렌즈의 실효 NA=0.8의 GaN 스폿 빔 레이저광(Lh)을, 일정한 주사 방향(y)에 평행하게 주사시키면서 조사했다. 이 때, 실시예 1에서는, 이 레이저광(Lh)을, 피치(p)=400nm의 간격을 두고 주사 방향(y)으로 주사 속도(v)=1m/s로 평행하게 주사시키면서 조사했다. 또한, 반도체 박막(3)에 대한 레이저광(Lh)의 조사는, 항상 포커스 서보를 가하고, 주사시에 초점이 벗어나지 않도록 했다. 또 조사 에너지가 일정하게 되도록 조사 빔의 일부를 모니터 해서 에너지의 변동이 없도록 했다.

<95> 이와 같은 레이저광(Lh)의 조사에 의한 결정화를 행한 영역을, 주사형 전자현미경(SEM)으로 관찰한 바, 피치(주기) p=400nm로 설치된 일련의 결정립계(a-a) 사이에, 주사 방향(y)과 반대(逆)방향에 볼록(凸)하게 되는 균일한 초승달 형상의 결정립(b')이 규칙적으로 배열된 다결정 영역이 얻어지는 것이 확인되었다.

<96> <실시예 2>

<97> 실시예 1에서의 레이저광(Lh)의 조사 조건을, 대물렌즈의 실효 NA=0.4, 피치(p)=600nm, 주사 방향(y)으로의 주사 속도(v)=3m/s로 변경한 것 이외는, 실시예 1과 마찬가지로 행했다.

<98> 이와 같은 레이저광(Lh)의 조사에 의한 결정화를 행한 영역을, 주사형 전자현미경(SEM)으로 관찰한 바, 피치(주기)(p)=600nm로 설치된 일련의 결정립계(a-a) 사이에, 주사 방향(y)과 반대방향에 볼록(凸)하게 되는 균일한 초승달 형상의 결정립(b')이 규칙적으로 배열된 다결정 영역이 얻어지는 것이 확인되었다.

<99> <실시예 3-1, 실시예 3-2>

<100> 실시예 1과 같이 해서 다결정화한 영역을 이용해서, 하기(下記)표 1에 나타내는 바와 같이, 채널 길이(게이트 선폭)(L)=10μm, 20μm, 채널폭(W)=50μm의 각 박막 트랜지스터를 제작했다. 본 실시예 3의 각 박막 트랜지스터에서는, 도 5에 도시한 바와 같이, 결정립계(a)와 평행하게 게이트 배선(5)을 설치했다. 이것에 의해, 도 3에 도시한 바와 같이, 결정화시에 마지막에 응고하는 부분이고 불순물이 집중되어 있는 결정립계(a)를 가로지르는 이동 방향(Xc)에 캐리어를 이동시키는 구조으로 했다. 또, 실시예 3-1, 실시예 3-2의 각 박막 트랜지스터에서의 채널부의 결정립계(a)의 갯수는, 약 25개, 약 50개로 된다.

&lt;101&gt;

[표 1]

|         | 채널 길이<br>$L$     | 채널폭<br>$W$       | 결정립계(a)의 수<br>(주기수) | 온 전류 편차<br>$\pm \sigma$ | $V_{th}$ 편차 | 이동도<br>( $\text{cm}^2/\text{Vs}$ ) |

|---------|------------------|------------------|---------------------|-------------------------|-------------|------------------------------------|

| 실시예 3-1 | $10 \mu\text{m}$ | $50 \mu\text{m}$ | 25 개                | $\pm 1.9\%$             | 0. 08V      | 26                                 |

| 실시예 3-2 | $20 \mu\text{m}$ |                  | 50 개                | $\pm 1.3\%$             | 0. 06V      | 26                                 |

GaN레이저; NA=0.8 결정립계(a)의 피치(주기)(p)=400nm

&lt;102&gt;

&lt;103&gt;

제작한 각 박막 트랜지스터에 대한 온 전류의 편차를 측정했다. 그 결과를 상기 표 1에 아울러(合) 나타낸다. 표 1에 나타내는 바와 같이, 실시예 3-1에서는 온 전류 편차  $\sigma = \pm 1.9\%$ , 실시예 3-2에서는 온 전류 편차  $\sigma = \pm 1.3\%$ 로 억제되어 있다.

&lt;104&gt;

또, 임계값( $V_{th}$ )의 편차  $\sigma$ 도, 실시예 3-1에서는 0.08V, 실시예 3-2에서는 0.06V에 억제되어 있다. 이것에 의해, 본 발명을 적용해서 다결정화 시킨 반도체 박막으로 채널부를 구성하는 것에 의해, 트랜지스터 특성을 고정밀도로 제어하는 것이 가능한 것으로 확인되었다. 특히 온 전류 편차  $\sigma = 3\%$ 이내로 억제됨으로써, 유기 전계 발광소자를 이용한 표시 장치에서의 화소 전극의 스위칭 소자로서, 이 박막 트랜지스터를 이용한 경우로서도, 휴도 편차가 시인(視認)되지 않을 정도로 충분히 억제되는 것이 확인되었다.

&lt;105&gt;

또, 실시예 3-1과 실시예 3-2와의 비교에 의하면, 결정립계(a)의 갯수가 많은 만큼, 온 전류 및 임계값의 편차가 작고, 특성 정밀도가 양호한 박막 트랜지스터가 얻어지는 것이 확인되었다. 또 이 때의 FET 이동도(캐리어의 이동도)는, 실시예 3-1, 3-2 모두  $26 \text{ cm}^2/\text{Vs}$ 이며, 화소 스위치로서 충분히 양호한 트랜지스터 특성이 얻어지는 것도 확인되었다.

&lt;106&gt;

&lt;실시예 4-1, 실시예 4-2&gt;

&lt;107&gt;

실시예 2와 같이 해서 다결정화한 영역을 이용해서, 하기 표 2에 나타내는 바와 같이, 채널 길이(게이트 선 폭)( $L$ )= $10 \mu\text{m}$ ,  $20 \mu\text{m}$ , 채널폭( $W$ )= $50 \mu\text{m}$ 의 각 박막 트랜지스터를 제작했다. 본 실시예 4의 각 박막 트랜지스터에서도, 도 5에 도시한 바와 같이, 결정립계(a)와 평행하게 게이트 배선(5)을 설치하고, 도 3에 도시하는 바와 같이 결정화 시에 마지막에 응고하는 부분이고 불순물이 집중되어 있는 결정립계(a)를 가로지르는 이동 방향( $X_c$ )에 캐리어를 이동시키는 구조으로 한 것은, 실시예 3과 마찬가지이다.

&lt;108&gt;

또, 실시예 4-1, 실시예 4-2의 각 박막 트랜지스터에서의 채널부의 결정립계(a)의 갯수는, 약 17개, 약 33개로 된다. 또한, 온 오프(off) 특성 향상이나 편차를 낮게 억제하기 위해서, 본 제4 실시예에서는 프로세스로 변경을 가하고 있다.

&lt;109&gt;

[표 2]

|         | 채널 길이<br>$L$     | 채널폭<br>$W$       | 결정립계(a)의 수<br>(주기수) | 온 전류 편차<br>$\pm \sigma$ | $V_{th}$ 편차 | 이동도<br>( $\text{cm}^2/\text{Vs}$ ) |

|---------|------------------|------------------|---------------------|-------------------------|-------------|------------------------------------|

| 실시예 4-1 | $10 \mu\text{m}$ | $50 \mu\text{m}$ | 17 개                | $\pm 0.94\%$            | 0. 10V      | 18                                 |

| 실시예 4-2 | $20 \mu\text{m}$ |                  | 33 개                | $\pm 0.56\%$            | 0. 06V      | 18                                 |

GaN레이저; NA=0.4 결정립계(a)의 피치(주기)(p)=600nm (단 프로세스 개선있음)

&lt;110&gt;

제작한 각 박막 트랜지스터에 대한 온 전류의 편차를 측정했다. 그 결과를 상기 표 2에 아울러 나타낸다. 표 2에 나타내는 바와 같이, 실시예 4-1에서는 온 전류 편차  $\sigma = \pm 0.94\%$ , 실시예 4-2에서는 온 전류 편차  $\sigma = \pm 0.56\%$ 로 억제되어 있다. 또, 임계값( $V_{th}$ )의 편차  $\sigma$ 도, 실시예 4-1에서는 0.10V, 실시예 4-2에서는 0.06V에 억제되어 있다.

&lt;112&gt;

이것에 의해, NA=0.4에서도 마찬가지로 본 발명을 적용해서 다결정화시킨 반도체 박막으로 채널부를 구성하는 것에 의해, 트랜지스터 특성을 고정밀도로 제어하는 것이 가능하다는 것이 확인되었다. 특히 온 전류 편차  $\sigma = 3\%$ 이내로 억제됨으로써, 유기 전계(有機電界) 발광소자를 이용한 표시 장치에서의 화소 전극의 스위칭 소자로서, 이 박막 트랜지스터를 이용한 경우로서도, 휴도 편차가 시인되지 않을 정도로 충분히 억제되는 것도 확인되었다.

&lt;113&gt;

또, 실시예 4-1과 실시예 4-2와의 비교에 의해, 결정립계(a)의 갯수가 많을 수록, 온 전류의 편차가 작고, 즉

특성 정밀도가 양호한 박막 트랜지스터가 얻어지는 것이 확인되었다. 또 이 때의 FET 이동도(캐리어의 이동도)는, 실시예 4-1, 4-2 모두  $18\text{cm}^2/\text{Vs}$ 이며, 화소 스위치로서 충분히 양호한 트랜지스터 특성이 얻어지는 것도 확인되었다.

<114> <비교 예>

<115> 종래 구성의 엑시머 레이저를 이용한 결정화 공정을 적용해서 복수의 박막 트랜지스터를 형성했다.

<116> 먼저, 실시예 1과 마찬가지 반도체 박막(3)을 성막한 후, KrF의 엑시머 레이저를, 광학적으로 단축(短軸) 방향의 폭  $400\mu\text{m}$ , 장축(長軸) 방향의 길이  $100\text{mm}$ 의 라인 빔으로 가공하고, 1펄스마다 단축 방향으로  $8\mu\text{m}$ 의 퍼치로 조사 위치를 어긋나게 하고, 나머지의 영역은 겹치도록 레이저를 조사했다. 이 때에 짧은 축에 평행한 단면에서 평가한 에너지 프로파일은, 톱 햇형(top hat form; 사다리꼴형)으로 조정되어 있다.

<117> 상기 조건으로 조사를 행한 경우, 같은 영역에는 약 50쇼트(shot)의 펄스 레이저가 조사되게 된다. 조사 레이저는 1펄스가  $25\text{ns}$ 이고,  $310\text{ mJ/cm}^2$ 상당의 에너지 밀도로 되도록 아테네이터(attenuator; 감쇠기)를 이용해서 조정했다.

<118> 이와 같은 레이저광(Lh)의 조사에 의한 결정화를 행한 영역을, 주사형 전자현미경(SEM)으로 관찰한 바, 한 변이 약  $250\text{nm}$ 의 사각형 모양(四角形狀; square-shaped)의 결정립이 격자 모양으로 규칙적으로 배열된 다결정 영역이 얻어지고 있는 것이 확인되었다.

<119> 상기 다결정화한 영역을 이용해서, 하기 표 3에 나타내는 채널 길이(케이트 선폭)(L)= $20\mu\text{m}$ 의 박막 트랜지스터를 제작했다. 또한, 각 박막 트랜지스터의 채널폭(W)= $50\mu\text{m}$ 로 했다.

<120> [표 3]

|         | 조사 에너지 빔       | 온 전류 편차 $\pm\sigma$ | V <sub>th</sub> 편차 | 이동도 ( $\text{cm}^2/\text{Vs}$ ) |

|---------|----------------|---------------------|--------------------|---------------------------------|

| 실시예 3-2 | GaN레이저; NA=0.8 | $\pm 1.3\%$         | 0.06V              | 26                              |

| 실시예 4-2 | GaN레이저; NA=0.4 | $\pm 0.56\%$        | 0.06V              | 18                              |

| 비교예     | 엑시머 레이저        | $\pm 6.2\%$         | 0.31V              | 155                             |

채널 길이(L)= $20\mu\text{m}$ , 채널폭(W)= $50\mu\text{m}$ (단, NA=0.4는 프로세스 개선있음)

<121>

<122> 제작한 각 박막 트랜지스터에 대한 온 전류의 편차 등을 측정했다. 그 결과를 상기 표 3에 아울러 나타낸다. 또한, 표 3에는, 비교예와 동일 규격(채널 길이 L= $20\mu\text{m}$ , 채널폭(W)= $50\mu\text{m}$ )의 각 실시예에 대한 결과를 아울러 나타냈다.

<123>

이 결과로부터, 본 발명을 적용해서 결정화시킨 반도체 박막을 이용한 실시예 3, 4의 박막 트랜지스터의 온 전류나 임계값(V<sub>t</sub>)의 편차는, 본 발명을 적용하지 않고 엑시머 레이저에 의해서 결정화시킨 반도체 박막을 이용한 비교예보다도, 훨씬 작은 것이 확인되었다. 또한, FET 이동도에 대해서는, 비교 예의 박막 트랜지스터 쪽이 높은 값을 나타내고 있지만, 본 발명을 적용한 실시예 3, 4의 값으로서도 화소 스위치로서 충분히 양호한 값이다.

### 발명의 효과

<124>

이상 설명한 바와 같이 본 발명의 반도체 박막의 결정화 방법에 의하면, 형상 정밀도가 양호하고 또한 양질인 결정립이 규칙적으로 배열되는 것에 의해, 높은 캐리어 이동도가 고정밀도로 제어된 다결정성 영역을 반도체 박막에 형성하는 것이 가능하다. 따라서, 이와 같이 해서 얻어진 다결정성(性) 영역을 이용하는 것에 의해, 특성 편차가 효과적으로 억제된 화소 스위칭 소자에 적합한(適) 박막 트랜지스터를 얻는 것이 가능하게 된다.

### 도면의 간단한 설명

<1>

도 1은 본 발명의 결정화 방법을 설명하는 평면도(그의 1),

<2>

도 2는 본 발명의 결정화 방법에 따르는 결정 성장을 설명하는 도면,

- <3> 도 3은 본 발명의 결정화 방법을 설명하는 평면도(그의 2),

- <4> 도 4는 본 발명의 결정화 방법을 이용한 박막 반도체 장치의 제조 방법을 설명하는 평면 공정도(그의 1),

- <5> 도 5는 본 발명의 결정화 방법을 이용한 박막 반도체 장치의 제조 방법을 설명하는 평면 공정도(그의 2),

- <6> 도 6은 도 5에서의 A부의 확대 평면도,

- <7> 도 7은 복수의 활성 영역의 결정화를 설명하는 평면도,

- <8> 도 8은 도 5에서의 X-X' 단면도,

- <9> 도 9는 박막 반도체 장치를 이용한 액정표시 장치의 제조 공정도.

- <10> [부호의 설명]

- <11> 3…반도체 박막, a…결정립계, b…결정립, b'…초승달 형상의 결정립, Lh…레이저광(에너지 빔), p…피치, y…주사 방향.

## 도면

### 도면1

### 도면2

도면3

## 도면4

## 도면5

도면6

도면7

도면8

## 도면9