(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4977310号

(P4977310)

(45) 発行日 平成24年7月18日(2012.7.18)

(24) 登録日 平成24年4月20日(2012.4.20)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/14

C

H01L 27/144 (2006.01)

H01L 27/14

K

H04N 5/32 (2006.01)

H04N 5/32

請求項の数 8 (全 8 頁)

(21) 出願番号

特願2004-167141 (P2004-167141)

(22) 出願日

平成16年6月4日(2004.6.4)

(65) 公開番号

特開2004-363614 (P2004-363614A)

(43) 公開日

平成16年12月24日(2004.12.24)

審査請求日

平成19年5月28日(2007.5.28)

(31) 優先権主張番号

10/457,322

(32) 優先日

平成15年6月6日(2003.6.6)

(33) 優先権主張国

米国(US)

(73) 特許権者

390041542

ゼネラル・エレクトリック・カンパニイ

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、リバーロード、1番

(74) 代理人

100137545

弁理士 荒川 智志

(74) 代理人

100105588

弁理士 小倉 博

(74) 代理人

100106541

弁理士 伊藤 信和

(74) 代理人

100129779

弁理士 黒川 俊久

最終頁に続く

(54) 【発明の名称】ソリッドステート放射線イメージヤの蓄積コンデンサアレイ

## (57) 【特許請求の範囲】

## 【請求項 1】

行及び列から成るイメージングアレイパターンで基板(105)上に配置され、各々が個別の薄膜スイッチングトランジスタ(130)に結合される個別のフォトセンサ(120)を含む複数のピクセル(110)と、

前記イメージングアレイパターンの第1の軸に沿って前記基板に対して第1のレベルで配置された複数の走査線(150)と、

を備えるイメージヤ(200)において、

前記イメージングアレイパターンのピクセルの各行が個別の走査線を有し、前記個別の走査線の各々が、前記イメージングアレイパターンでピクセルの個別の行に沿って配置された各ピクセルについて前記薄膜スイッチングトランジスタの個別のゲート電極(132)に結合されており、

前記イメージヤには、更に、前記イメージングアレイパターンの第2の軸に沿って前記基板に対して第2のレベルで配置された複数のデータ線(140)が設けられ、

前記イメージングアレイパターンのピクセルの各列が、対応するデータ線を有し、前記個別のデータ線の各々が、前記イメージングアレイパターンでピクセルの個別の列に沿って配置された各ピクセルについて、前記薄膜スイッチングトランジスタの個別の読み取り電極(136)に結合されており、

前記イメージヤには更に、前記基板上に配置され、各々が第1の電極(291)と、第2の電極(296)と、第1の電極及び第2の電極間に配置される誘電体とから構成される

10

20

複数のコンデンサ(241)を含む蓄積コンデンサアレイが設けられ、前記第1の電極が対応するフォトセンサと対応する薄膜スイッチングトランジスタとに結合され、複数の前記第2の電極がコンデンサ線形電極(251)に結合され、冗長性のために、隣接するコンデンサ線形電極間に結合される複数のブリッジ(271)を更に備えることを特徴とするイメージヤ(200)。

#### 【請求項2】

前記コンデンサ線形電極がコンデンサアレイの縁部に結合され、電圧バイアスが前記アレイの縁部に印加されることを特徴とする請求項1に記載のイメージヤ。

#### 【請求項3】

前記複数のデータ線と前記複数のブリッジの交点に対応する複数の交点の下に複数の電極を含むことを特徴とする請求項1又は2に記載のイメージヤ。 10

#### 【請求項4】

複数の交点(264)の下に複数の電極を更に備え、前記複数の交点が複数の前記データ線と複数の前記走査線との交点に対応することを特徴とする請求項1乃至3のいずれかに記載のイメージヤ。

#### 【請求項5】

前記イメージング装置がデータ読み取り動作中の過渡電流を最小にするよう、前記複数の線形電極が前記複数のデータ線に平行であることを特徴とする請求項1乃至4のいずれかに記載のイメージヤ。 20

#### 【請求項6】

前記複数の走査線の対応する1つの下に配置される前記線形電極の各1つが、冗長性のために2つの平行電極に分割されることを特徴とする請求項1乃至5のいずれかに記載のイメージヤ。

#### 【請求項7】

前記複数のデータ線が前記複数の走査線から電気的に絶縁していることを特徴とする請求項1乃至6のいずれかに記載のイメージヤ。

#### 【請求項8】

前記イメージヤがX線イメージヤである請求項1乃至7のいずれかに記載のイメージヤ。 30

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は一般的にイメージング装置に関し、より具体的にはソリッドステート放射線イメージヤの蓄積コンデンサアレイに関する。

#### 【背景技術】

#### 【0002】

ソリッドステート放射線イメージヤは通常、行及び列で配列された複数のピクセルを含む大型フラットパネルイメージング装置を備える。各ピクセルは通常、スイッチングトランジスタ(例えば薄膜電界効果トランジスタなど)によって2つの別個のアドレス線、走査線及びデータ線、に結合されるフォトダイオードなどのフォトセンサを有する。ピクセルの各行において、個別のスイッチングトランジスタは各々、トランジスタのゲート電極を通して共通走査線に結合される。ピクセルの各列において、トランジスタの読み取り電極(例えばトランジスタのソース電極など)はデータ線に結合される。公称動作中、放射線(X線線束など)はパルス化され、検査対象を透過するX線はイメージングアレイに入射する。放射線がシンチレータ材料に入射し、ピクセルフォトセンサが、シンチレータとのX線相互作用によって発生した光の量を(ダイオードの両端の電荷の変化によって)計測する。或いは、X線はフォトセンサに電子と正孔のペアを直接生成できる(通常「直接検知」と呼ばれる)。フォトセンサの電荷データは、ピクセルの行を連続的にイネーブルにし(走査線に信号を印加して、走査線に結合されるスイッチングトランジスタが導電性 40

を帯びることによる）、個別のデータ線を介してこのようにイネーブルになった個別のピクセルからの信号を読む（フォトダイオード電荷信号は導電スイッチングトランジスタを介してデータ線に結合され、データ線に結合される関連する読み取り電極に結合される）ことにより読み取られる。このようにして、所与のピクセルは、ピクセルに結合される走査線をイネーブルにすること、及びピクセルに結合されるデータ線で読み取ることを組合せることによりアドレスすることができる。

#### 【0003】

こうしたソリッドステート放射線イメージャに関する1つの問題は、ダイナミックレンジが制限されることである。処理可能な最大の信号レベルは、フォトダイオードの両端のバイアス電圧（通常1 - 10V）、及びフォトダイオードの静電容量（通常100マイクロメートルピッチにつき0.4 - 0.8 pF、平方ピッチに対応する）に比例する。ダイナミックレンジを増大させるためにバイアス又は静電容量を大きくすると、漏洩電流の増大又はより多くの点欠陥を含む様々な欠点がある。通常、X線用途において、最大X線信号レベルは、X線を通じてフォトダイオードに入射する光の量を低減することで増大することができる。かかる解決法の結果として得られる効果は、電子ノイズに対する感度がこれに応じて大きくなり、従って、最小信号レベルに関して逆効果となる。

【特許文献1】米国特許第6777685号

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0004】

従って、より大きなダイナミックレンジを可能にし、画像の画質を向上させるソリッド放射線イメージャの提供が望まれる。

#### 【課題を解決するための手段】

#### 【0005】

要約すると、本発明の1つの実施形態によれば、イメージャ用の蓄積コンデンサアレイが提供される。イメージャは、行及び列から成るイメージングアレイパターンで基板上に配置される複数のピクセルを含む。各ピクセルは、個別の薄膜スイッチングトランジスタに結合される個別のフォトセンサを含む。複数の走査線が、基板に対して第1のレベルでイメージングアレイパターンの第1の軸に沿って配置される。イメージングアレイパターンのピクセルの各行は、個別の走査線を有する。個別の走査線の各々は、薄膜スイッチングトランジスタの個別のゲート電極に結合され、各ピクセルがイメージングアレイパターンのピクセルの個別の行に沿って配置される。複数のデータ線が基板に対して第2のレベルでイメージングアレイパターンの第2の軸に沿って配置される。イメージングアレイパターンのピクセルの各列は対応するデータ線を有する。個別のデータ線の各々は、薄膜スイッチングトランジスタの個別の読み取り電極に結合され、各ピクセルがイメージングアレイのピクセルの個別の列に沿って配置される。複数のコンデンサを含む蓄積コンデンサアレイは、基板上に配置される。複数のコンデンサの各々は、第1の電極、第2の電極、及び第1の電極と第2の電極の間に配置される誘電体を含む。第1の電極は、対応するフォトセンサ及び対応する薄膜トランジスタに結合され、第2の電極はコンデンサ線形電極に結合される。

#### 【発明を実施するための最良の形態】

#### 【0006】

本発明のこれら及び他の特徴、態様、及び利点は、図面全体を通して同じ番号が同じ部分を表す添付図面を参照して以下の詳細な説明を読むとより理解される。

#### 【0007】

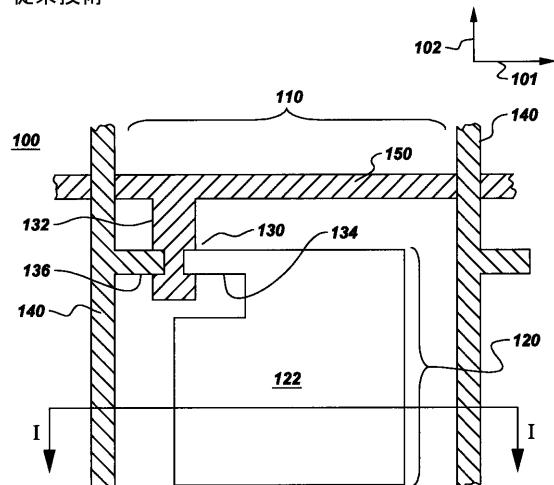

ソリッドステート放射線イメージャ100は、ピクセル110の行と列を成してマトリクス状のイメージングアレイパターンで配列された複数のピクセル110（その代表的な1つを図1Aに示す）を含む。限定ではなく例示の目的として、イメージャ100は、ピクセルの行が整列する第1の軸101と、ピクセルの列が整列する第2の軸102とを有する。各ピクセル110は、フォトセンサ120及び薄膜スイッチングトランジスタ13

10

20

30

40

50

0を含む。フォトセンサ120は通常、低ピクセル電極122から一部が構成されるフォトダイオードを含み、この低ピクセル電極は実質的に装置のアクティブ(すなわち感光性)領域と一致する。スイッチングトランジスタ130は通常、ゲート電極132、ドレイン電極134、及びソース電極(又は読み取り電極)136を有する薄膜電界効果トランジスタ(FET)を含む。イメージヤ100は更に、複数のデータ線140及び走査線150(総称してアドレス線と呼ばれる)を含む。少なくとも1つの走査線150は、イメージングアレイパターンのピクセルの各行について第1の軸101に沿って配置される。各走査線は、ピクセルの当該行におけるピクセルの個別のゲート電極132に結合される。少なくとも1つのデータ線140は、イメージングアレイパターンのピクセルの各列について第2の軸102に沿って配置され、ピクセルの当該列におけるピクセルの個別の読み取り電極136に結合される。

#### 【0008】

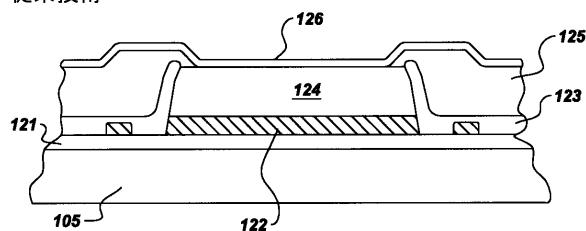

1つのピクセル110の部分断面図が図1Bに示されている。フォトダイオード120が基板105の上に配置される。第1の誘電体層121は通常、ピクセル電極122と基板105の間に配置される。フォトダイオード120は更に、イメージングアレイ上に配置される共通電極126に電気的に結合される感光材料本体124(通常アモルファスシリコンを含む)を含む。共通電極126は、インジウムスズ酸化物又は同様のものなどの光学的に透過性で導電性の材料を含む。第2の誘電体層123は、通常、窒化ケイ素又は同様のものなどを含み、感光材料本体124の側壁の一部上に延びてあり、第3の誘電体層125は、ポリイミド又は同様のものなどを含み、共通電極126とイメージングアレイの他の構成要素との間(第2の誘電体層123及び第3の誘電体層125のバイアを通る感光材料本体124への接点を除く)に配置される。

#### 【0009】

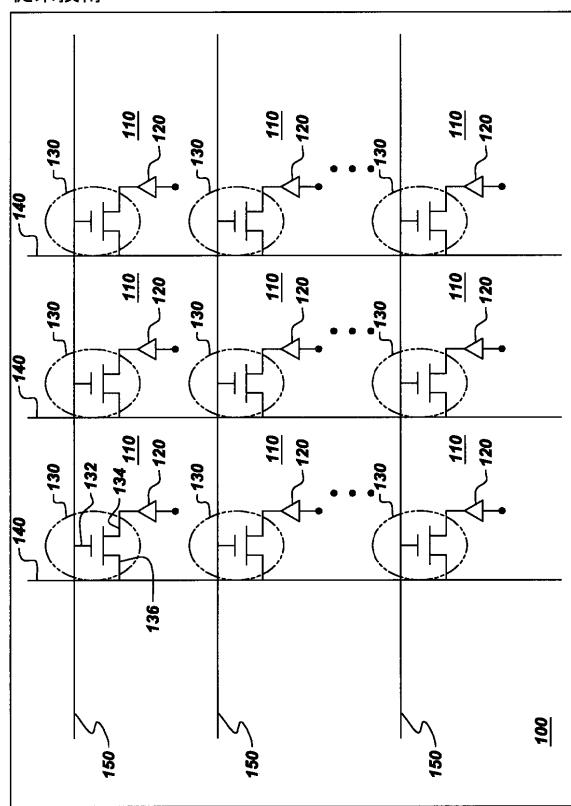

図2は、図1A-図1Bに示されるイメージヤ100の回路図である。図2は複数のピクセル110を示し、ここで各ピクセルは、フォトダイオードなどのフォトセンサ120と、ゲート電極132、ドレイン電極134、及びソース電極(又は読み取り電極)136を有するFETなどの薄膜スイッチングトランジスタ130とを含む。図2のイメージングアレイパターンはまた、複数のデータ線140及び走査線150を示す。

#### 【0010】

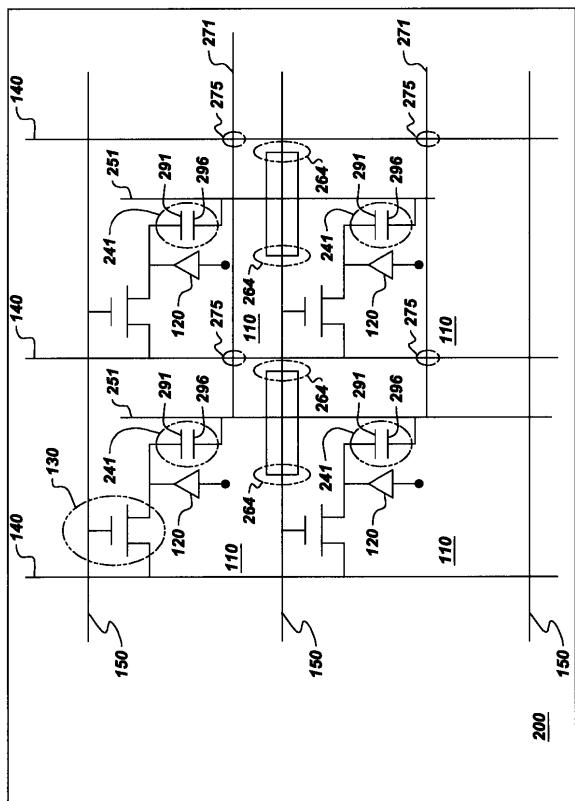

図3は、本発明の実施形態によるイメージヤ200の回路図である。イメージヤ200は、蓄積コンデンサアレイを含むことを除いては、図1A-図1B及び図2に示されるイメージヤ100と同様である。イメージヤ200は、行及び列を成してイメージングアレイパターンの基板上に配置される複数のピクセル110を含む。1つの実施形態において、基板は、シリコンに類似する熱膨張率を有するガラスである。各ピクセルは、個別の薄膜スイッチングトランジスタ130に結合される個別のフォトセンサ120を含む。

#### 【0011】

イメージヤ200は更に、複数の走査線150及び複数のデータ線140を含む。データ線及び走査線は、堆積された1つ又は複数の薄膜誘電体層により電気的に絶縁される。

#### 【0012】

イメージヤ200は更に、蓄積コンデンサアレイを含む。蓄積コンデンサアレイは、基板上に配置された複数のコンデンサ241を含む。各コンデンサ241は、第1の電極291、第2の電極296、及び第1の電極と第2の電極との間に配置された誘電体とを含む。

#### 【0013】

1つの実施形態において、誘電体は、薄膜トランジスタゲート誘電体層に用いられる薄膜と同じ窒化ケイ素の薄膜からなる。第1の電極291の各々は、対応するフォトセンサ120及び対応する薄膜スイッチングトランジスタ130にそれぞれ結合される。第2の電極296はコンデンサ線形電極251に結合される。1つの実施形態において、第2の電極はコンデンサ線形電極を含む。

#### 【0014】

10

20

30

40

50

コンデンサ線形電極はコンデンサアレイの縁部に結合される。この縁部をアレイの縁部と呼ぶ。アレイの縁部において、線形電極は、同じ金属によるか又は他の層に用いる金属によるかのいずれかにより全て共に結合される。更に縁部において、コンデンサ線形電極はフォトダイオード 120 用のバイアス電極に結合され、こうしてコンデンサとダイオードの間の平行な電気的構成が完成する。効果的に蓄積コンデンサを結合することで、バイアス電圧がアレイの縁部で印加され、これにより各ピクセルにおいてバイアス電圧を印加する必要が排除される。こうした配列によりピクセル充填率が最大限となする。

#### 【0015】

コンデンサアレイは更に、隣接するコンデンサ線形電極 251 の間に冗長のために結合される複数のブリッジ 271 を含む。例えば、線形電極が修復過程の間に幾つかの位置で切断され、その結果、電気的に絶縁される部分において、ブリッジは線形電極を共に結合したままの状態に確実に維持されることになる。冗長性を加えることにより、電気的に絶縁され又は浮動状態にある部分を有する確率は大幅に減少する。10

#### 【0016】

コンデンサアレイは更に、複数のデータ線と複数の走査線の交点及び複数のデータ線と複数のブリッジの交点に対応する複数の交点の下に複数の細い電極を含む。図 3 において、点 264 及び 275 が交点である。

#### 【0017】

イメージヤ 200 において、各蓄積コンデンサは、結合されるフォトダイオードよりも多くの電荷を蓄積するよう設計されており、これにより各ピクセルの電荷蓄積容量が増加すると共に、より薄いフォトダイオード（点欠陥）又は高バイアス電圧（高漏洩電流）を用いることに関連する問題が回避される。更に、かなりの量の電荷がコンデンサに蓄積されるので、所与の信号レベルがフォトダイオードの両端のバイアス変化をより小さくし、これはより低いラグを生じる。高い電荷蓄積容量は、ピクセルを飽和にすることなくフォトダイオードのゲインを最大にし、これにより電子ノイズに対する感度を低下させることができる。又、誘電体の堆積を均一に制御するのがより容易になるため、大面積イメージング装置全体のピクセル静電容量の均一性が改善される。20

#### 【0018】

更に、この特定の設計には他の利点がある。詳細には、複数のコンデンサ線形電極が複数のデータ線に平行であり、その結果、イメージヤによるデータ読み取り動作中の線形電極の過渡電流が最小となる。従って、走査線がバイアスされると、対応するピクセル及びコンデンサ電荷が、データ線及び対応する線形コンデンサ電極を通じて放電し、こうして各線形コンデンサ電極の過渡電流が低減する。過渡電流が低減することで多くの層に結合される電極及び導体の信頼性が改善され、大きな電流により有限線抵抗に起因する大きな過渡電圧偏位が発生することからイメージヤ性能が改善される。更に、蓄積コンデンサアレイは、イメージヤの任意のバイアス線が開放及び短絡に影響されないことを保証する。30

#### 【0019】

別の実施形態において、線形電極の各 1 つは複数の走査線の対応する 1 つの下に配置されて 2 つの平行電極に分割され、短絡の修復を成功させる確率が大きくなる。両交差点が短絡すると、短絡した交差点はレーザ又は他の方法で切断することができる。ライン 251 の電気的導通は影響を受けない。40

#### 【0020】

本発明の前述の実施形態は、コンデンサ電極の短絡及び過渡電流を最小限にする欠陥の少ないコンデンサアレイのための設計を含む、多くの利点を有し、従ってイメージヤの画質が向上する。

#### 【0021】

本発明のある特徴のみを本明細書で示して説明してきたが、当業者であれば多くの修正及び変更が行われるであろう。従って添付の請求項は、本発明の真の精神の範囲内にあるものとして、こうした修正及び変更の全てに及ぶことが意図される点を理解されたい。

#### 【図面の簡単な説明】

10

20

30

40

50

## 【0022】

【図1A】従来技術によるイメージャの部分の平面図。

【図1B】図1Aの線I - Iに沿った代表的なピクセルの部分断面図。

【図2】図1A - 図1Bに示すイメージャのイメージングアレイパターンの回路図。

【図3】本発明の1つの実施形態による蓄積コンデンサアレイを備えるイメージャの回路図。

## 【符号の説明】

## 【0023】

200 イメージャ

130 薄膜スイッチングトランジスタ

10

120 フォトセンサ

140 データ線

150 走査線

241 コンデンサ

251 コンデンサ線形電極

【図1A】

従来技術

【図1B】

従来技術

【図2】

従来技術

【図3】

---

フロントページの続き

(72)発明者 チー・アン・リー

アメリカ合衆国、ニューヨーク州、ニスカユナ、フォックス・ヒル・ドライブ、2186番

(72)発明者 ジョージ・エドワード・ポッシン

アメリカ合衆国、ニューヨーク州、ニスカユナ、アルゴンキン・ロード、2361番

(72)発明者 ダグラス・アルバゲリー

アメリカ合衆国、ニューヨーク州、クリフトン・パーク、クイーンズベリー・コート、1番

(72)発明者 ウィリアム・アンドリュー・ヘネシー

アメリカ合衆国、ニューヨーク州、スケネクタディ、グレゴリー・レーン、8015番

審査官 青鹿 喜芳

(56)参考文献 特開平05-315581(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14

H04N 5/32