**República Federativa do Brasil**

Ministério do Desenvolvimento, Indústria,

Comércio e Serviços

Instituto Nacional da Propriedade Industrial

---

**(11) BR 112017010750-3 B1**

**(22) Data do Depósito:** 30/09/2015

**(45) Data de Concessão:** 28/02/2023

**(54) Título:** DISPOSITIVO TRANSISTOR DE EFEITO DE CAMPO DE ALETAS (FINFET) E MÉTODO DE FABRICAÇÃO DO MESMO

**(51) Int.Cl.:** H01L 29/417; H01L 29/66; H01L 29/78.

**(30) Prioridade Unionista:** 24/11/2014 US 62/083,714; 30/03/2015 US 14/673,485.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** JEFFREY JUNHAO XU; STANLEY SEUNGCHUL SONG; VALDIMIR MACHKAOUTSAN; MUSTAFA BADAROGLU; JUNJING BAO; JOHN JIANHONG ZHU; DA YANG; CHOH FEI YEAP.

**(86) Pedido PCT:** PCT US2015053305 de 30/09/2015

**(87) Publicação PCT:** WO 2016/085570 de 02/06/2016

**(85) Data do Início da Fase Nacional:** 23/05/2017

**(57) Resumo:** A presente invenção se refere a um dispositivo semicondutor incluindo uma pilha de portas. O dispositivo semicondutor também inclui um contato envolvente disposto ao redor e substancialmente em contato com toda a área superficial de uma região fonte / dreno regenerada do dispositivo semicondutor próximo à pilha de portas.

**"DISPOSITIVO TRANSISTOR DE EFEITO DE CAMPO DE ALETAS

(FinFET) E MÉTODO DE FABRICAÇÃO DO MESMO"**

REFERÊNCIA CRUZADA A PEDIDOS RELACIONADOS

[0001] Este pedido reivindica o benefício sob 35 USC § 119 (e) ao Pedido de Patente US Provisório nº 62/083,714, intitulado "CONTACT WRAP AROUND STRUCTURE", depositado em 24 de novembro de 2014, em nome de Jeffrey Junhao XU, *et al.*, cuja divulgação é aqui expressamente incorporada por referência em sua totalidade.

ANTECEDENTES DA INVENÇÃO

CAMPO DA INVENÇÃO

[0002] Aspectos da presente invenção se referem a dispositivos semicondutores e, mais particularmente, a uma estrutura envolvente de contato.

ANTECEDENTES DA INVENÇÃO

[0003] À medida que a tecnologia do circuito integrado (IC) avança, as geometrias dos dispositivos são reduzidas. Reduzir a geometria e o "pitch" (espaçamento) entre os dispositivos pode fazer com que os dispositivos interfiram entre si em termos de operação adequada.

[0004] Dispositivos baseados em aletas são estruturas tridimensionais sobre a superfície de um substrato semicondutor. Um transistor baseado em aletas, que pode ser um transistor de efeito de campo de semicondutor de óxido metálico (MOSFET) baseado em aleta, pode ser referido como um FinFET. Um transistor de efeito de campo (FET) de nanofios é também uma estrutura tridimensional sobre a superfície de um substrato semicondutor. Um FET de nanofios inclui partes dopadas do nanofio que contatam uma região de canal e servem como as regiões de fonte e dreno do dispositivo. Um FET de nanofios também é um exemplo de um dispositivo MOSFET.

[0005] O desempenho dos dispositivos MOSFET pode ser afetado por numerosos fatores, incluindo o comprimento, a deformação e a resistência externa do canal. Um fator substancial que contribui para a resistência externa é a resistência de contato entre as regiões fonte / dreno e as camadas condutoras. As resistências de contato são um limitador do desempenho e dimensionamento de dispositivos para nodos de tecnologia avançada em que a geometria e "pitch" (espaçamento) entre os dispositivos são drasticamente reduzidos.

#### SUMÁRIO DA INVENÇÃO

[0006] Um dispositivo semicondutor inclui uma pilha de portas. O dispositivo semicondutor também inclui um contato envolvente disposto ao redor e que contata substancialmente toda a área de superfície de uma região de fonte / dreno regenerada do dispositivo semicondutor próximo à pilha de portas.

[0007] Um método para fabricar um dispositivo semicondutor incluindo uma estrutura envolvente de contato inclui regiões fonte / dreno regeneradas do dispositivo semicondutor. O método também inclui a substituição de uma porta simulada do dispositivo semicondutor por uma pilha de portas. O método pode ainda incluir a fabricação de um contato envolvente disposto ao redor e contatando substancialmente toda a área de superfície de uma região fronte / dreno regenerada do dispositivo semicondutor próximo à pilha de portas.

[0008] Um dispositivo semicondutor inclui uma pilha de portas. O dispositivo semicondutor também inclui meios para contatar substancialmente toda a área de superfície de uma região fonte / dreno regenerada do dispositivo semicondutor próximo à pilha de portas.

[0009] Isto delineou, de um modo bastante alargado, os recursos e as vantagens técnicas da presente invenção, a fim de que a descrição detalhada que segue possa ser melhor compreendida. Recursos e vantagens adicionais da invenção serão descritos abaixo. Deve ser apreciado pelos especialistas na técnica que esta descrição pode ser facilmente utilizada como base para modificar ou conceber outras estruturas para realizar os mesmos objetivos da presente invenção. Também deve ser percebido pelos especialistas na técnica que tais construções equivalentes não se afastam dos ensinamentos da invenção como estabelecido nas reivindicações anexas. Os novos recursos, que se crê serem características da invenção, tanto no que se refere à sua organização quanto ao método de operação, juntamente com outros objetivos e vantagens, serão melhor compreendidos a partir da descrição a seguir, quando considerada em ligação com as figuras anexas. Contudo, deve ser expressamente entendido que cada uma das figuras é proporcionada apenas para fins de ilustração e descrição e não se destina como uma definição dos limites da presente invenção.

#### BREVE DESCRIÇÃO DAS FIGURAS

[0010] Para uma compreensão mais completa de um aspecto da presente invenção, faz-se agora referência à descrição a seguir tomada em conjunto com os desenhos anexos.

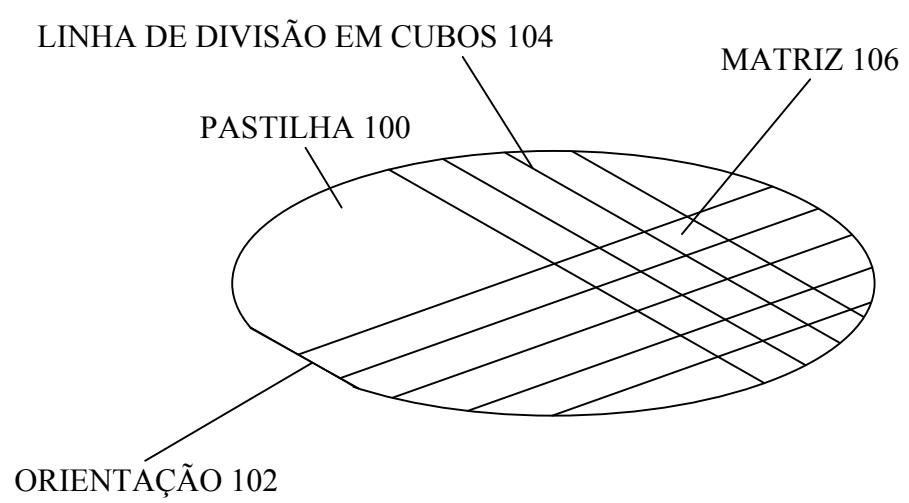

[0011] A FIGURA 1 ilustra uma vista em perspectiva de uma pastilha semicondutora em um aspecto da presente invenção.

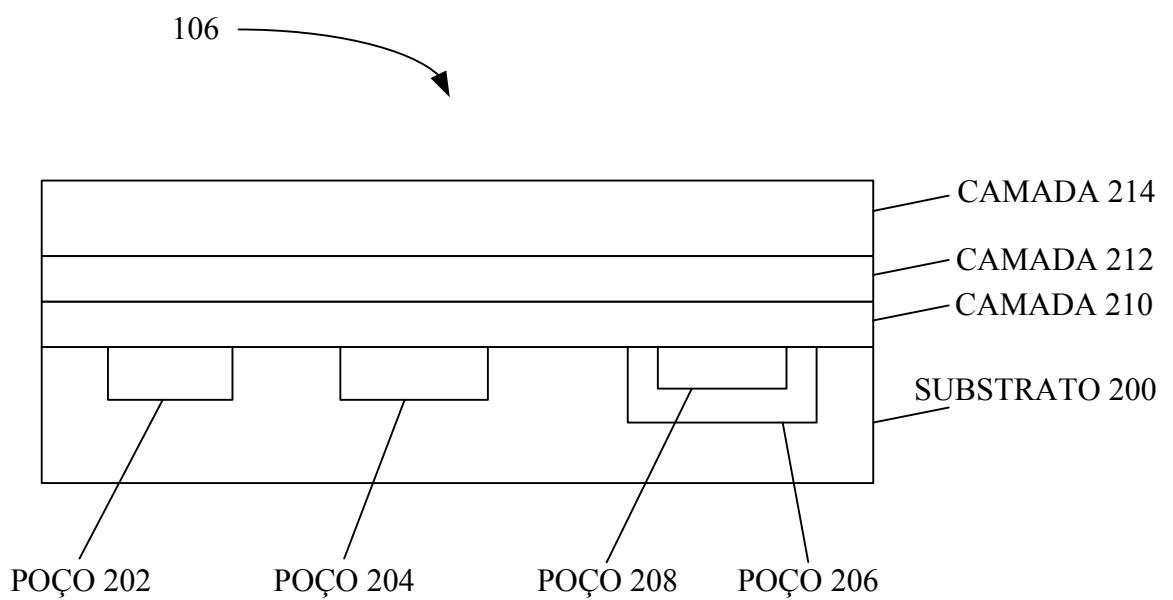

[0012] A FIGURA 2 ilustra uma vista em corte transversal de uma matriz de acordo com um aspecto da presente invenção.

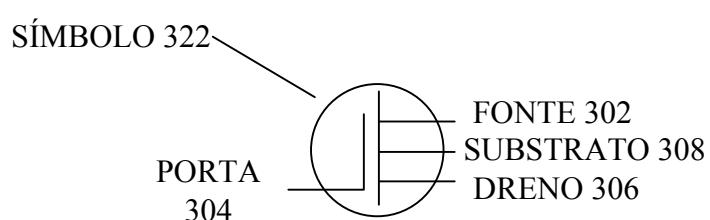

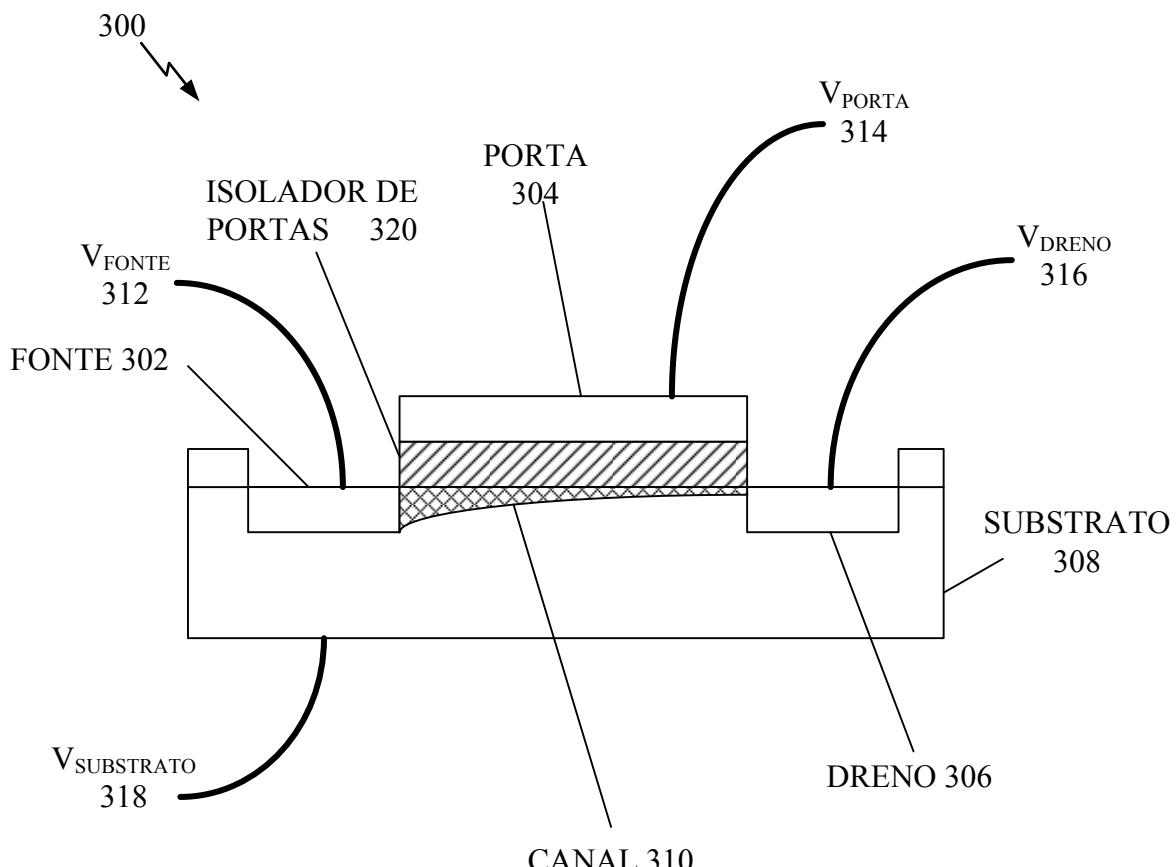

[0013] A FIGURA 3 ilustra uma vista em corte transversal de um dispositivo de transistor de efeito de campo de semicondutor de óxido metálico (MOSFET) em um aspecto da presente invenção.

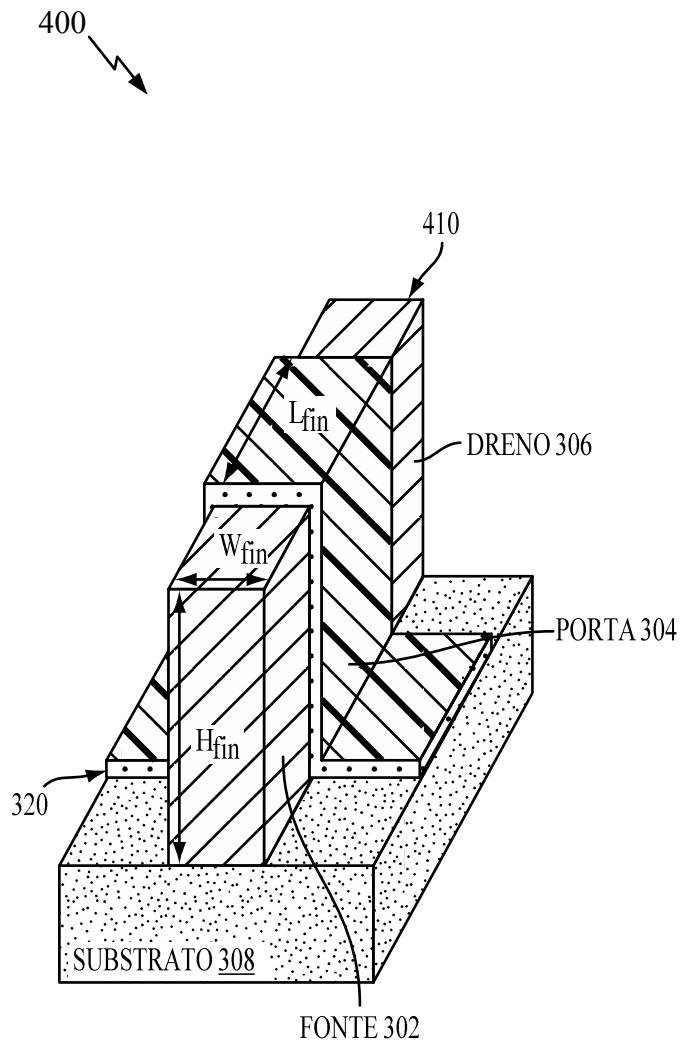

[0014] A FIGURA 4 ilustra um transistor de efeito de campo de aleta (FinFET) de acordo com um aspecto da presente invenção.

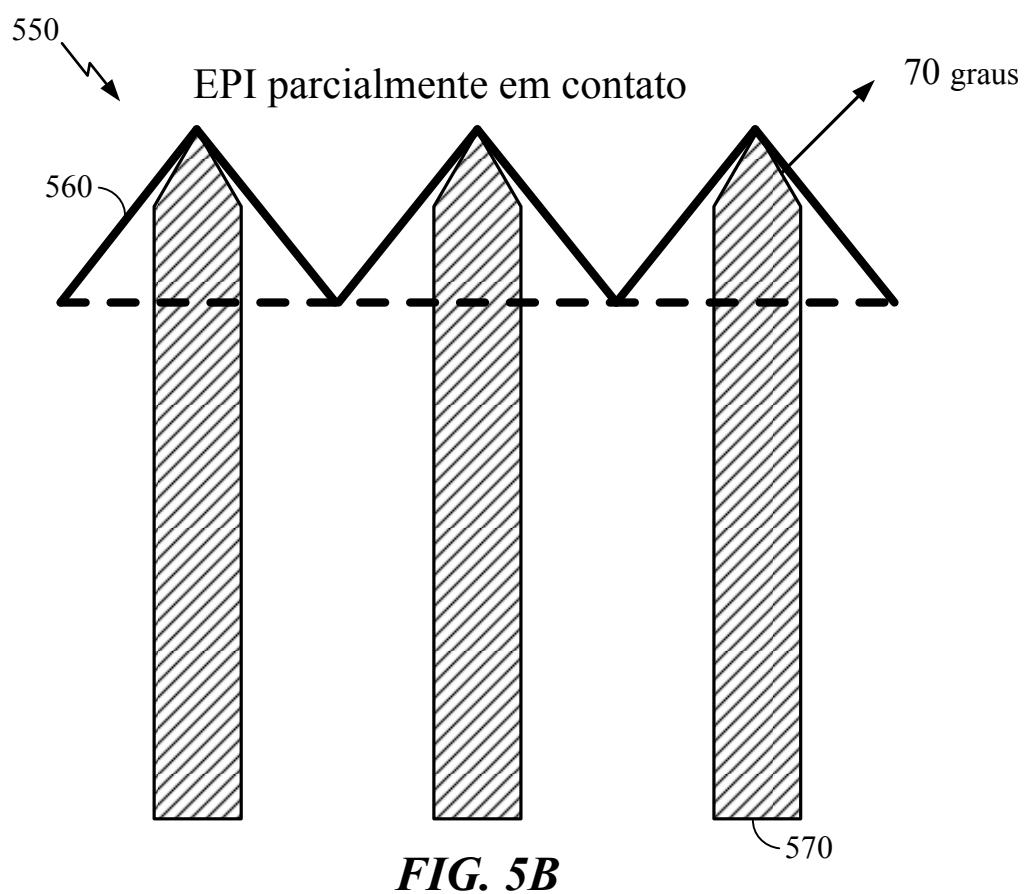

[0015] As FIGURAS 5A e 5B ilustram vistas em corte transversal de estruturas baseadas em aletas incluindo estruturas de contato convencionais.

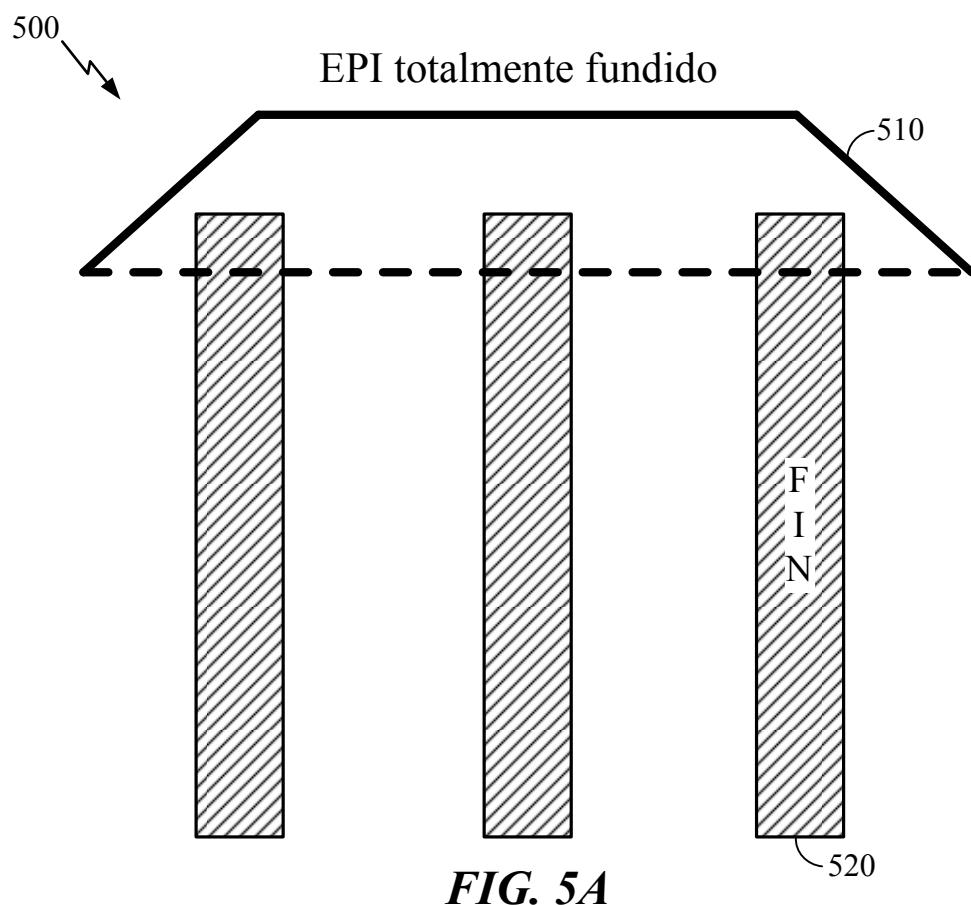

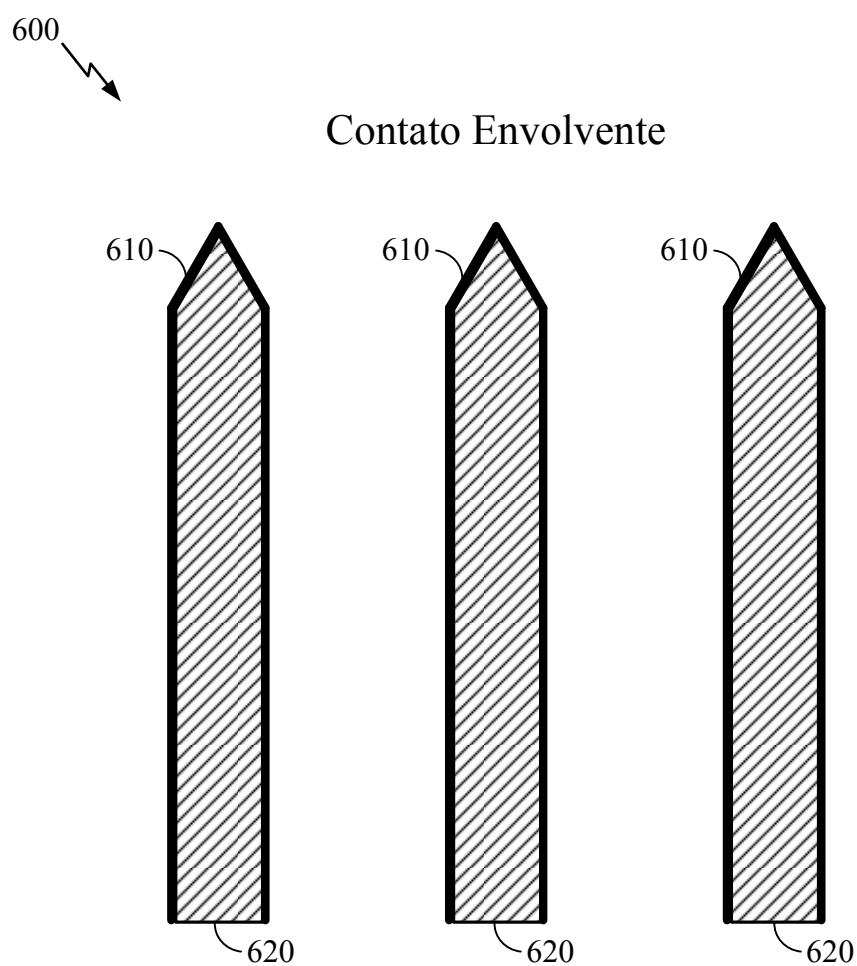

[0016] A FIGURA 6 ilustra uma vista em corte transversal de uma estrutura baseada em aleta que inclui um contato envolvente de acordo com um aspecto da presente invenção.

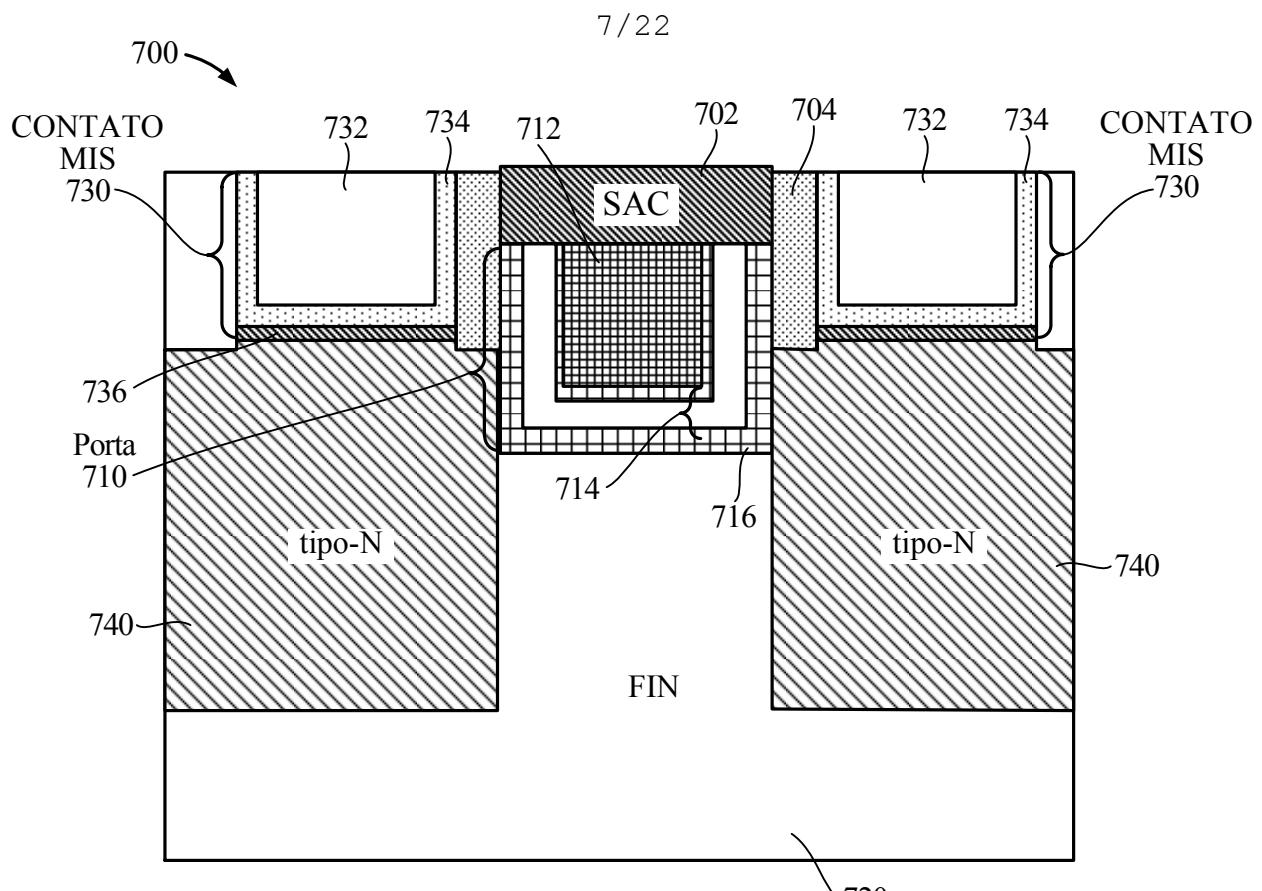

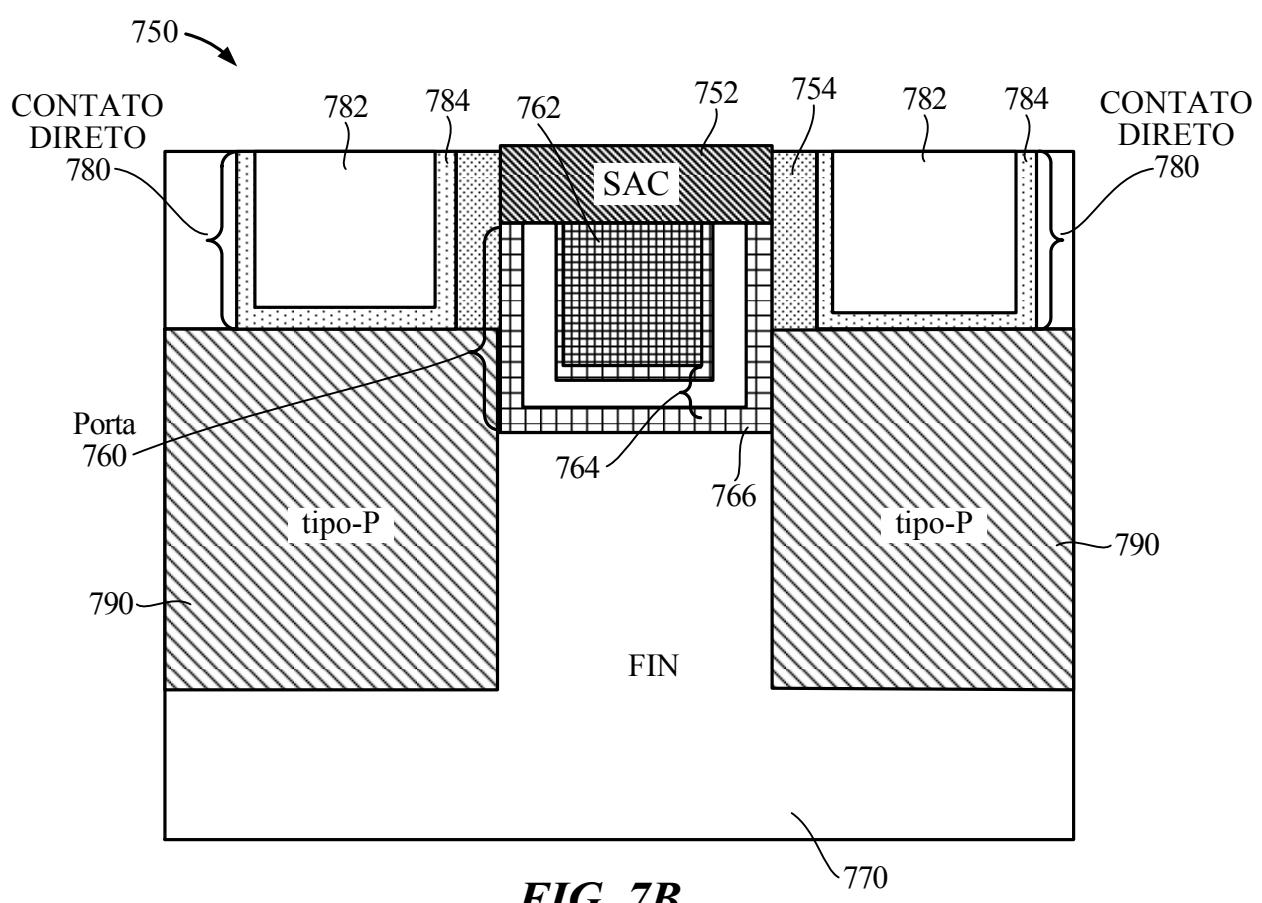

[0017] As FIGURAS 7A e 7B ilustram vistas em corte transversal de dispositivos de semicondutor de óxido metálico complementares (CMOS), incluindo um contato MIS ou um contato direto de acordo com um aspecto da presente invenção.

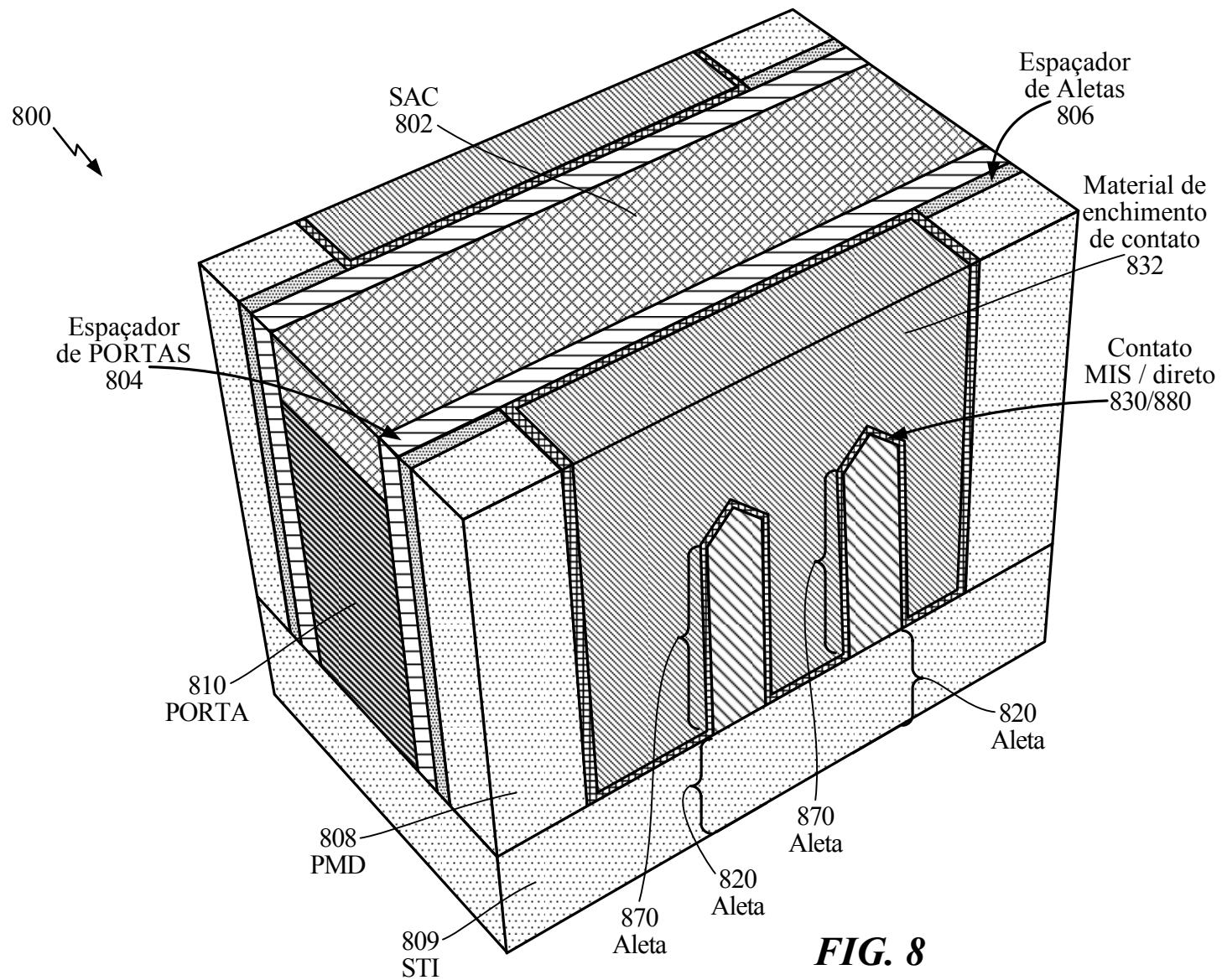

[0018] A FIGURA 8 ilustra uma vista em corte transversal de um dispositivo baseado em aletas que inclui uma estrutura envolvente de contato de acordo com um aspecto da presente divulgação.

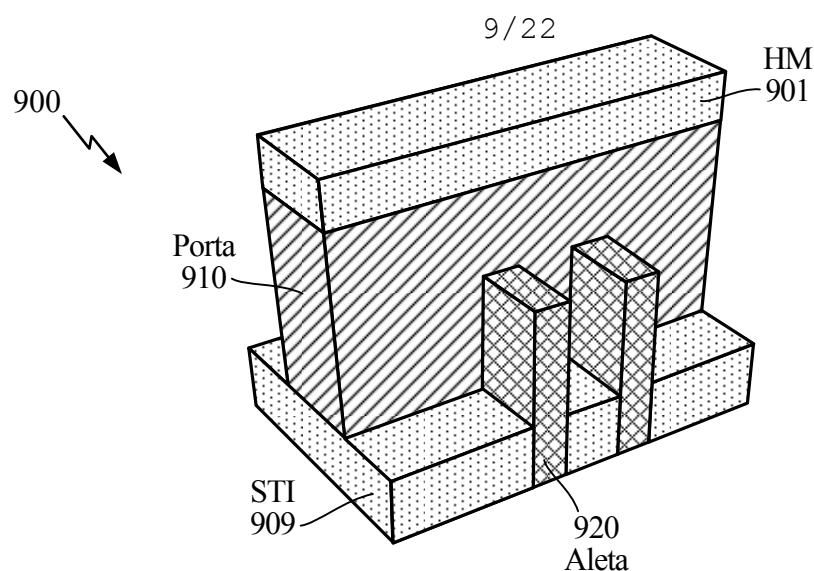

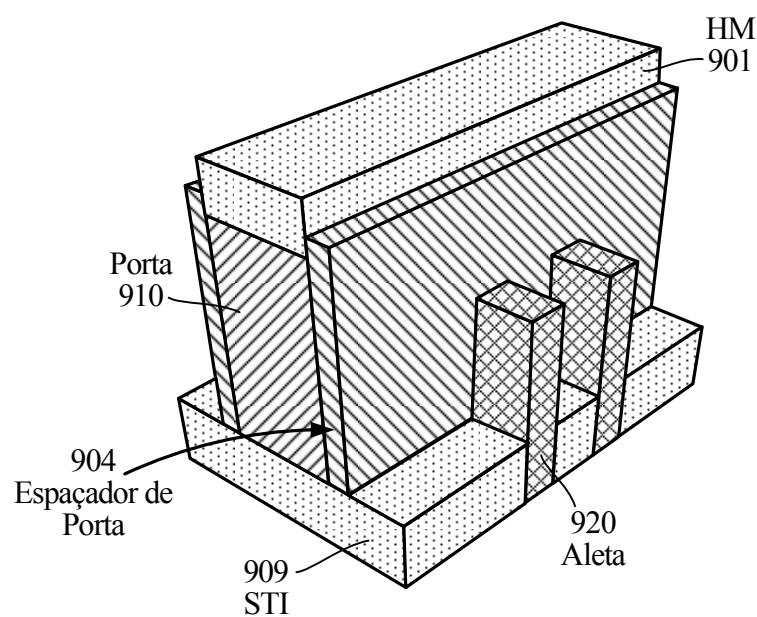

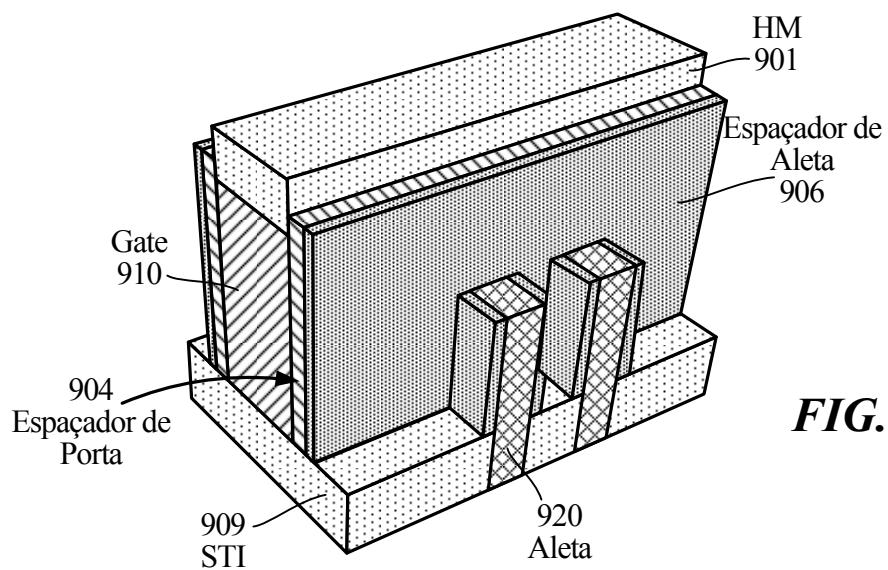

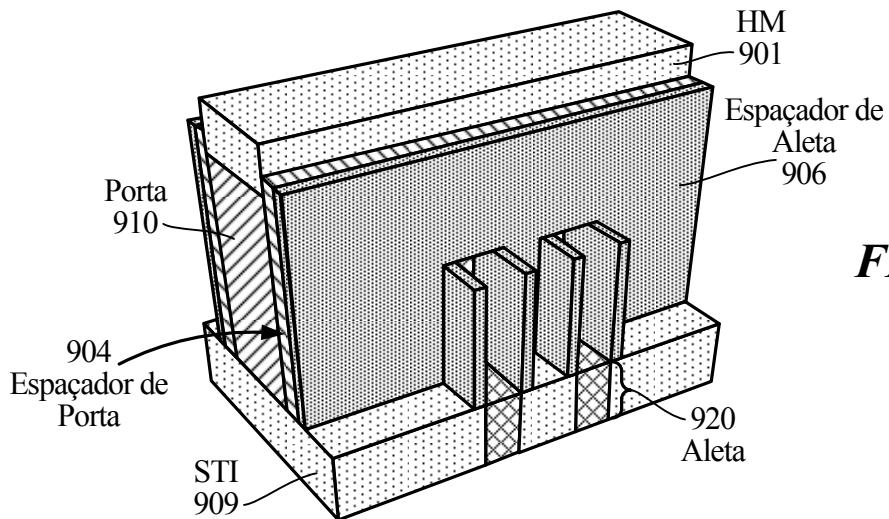

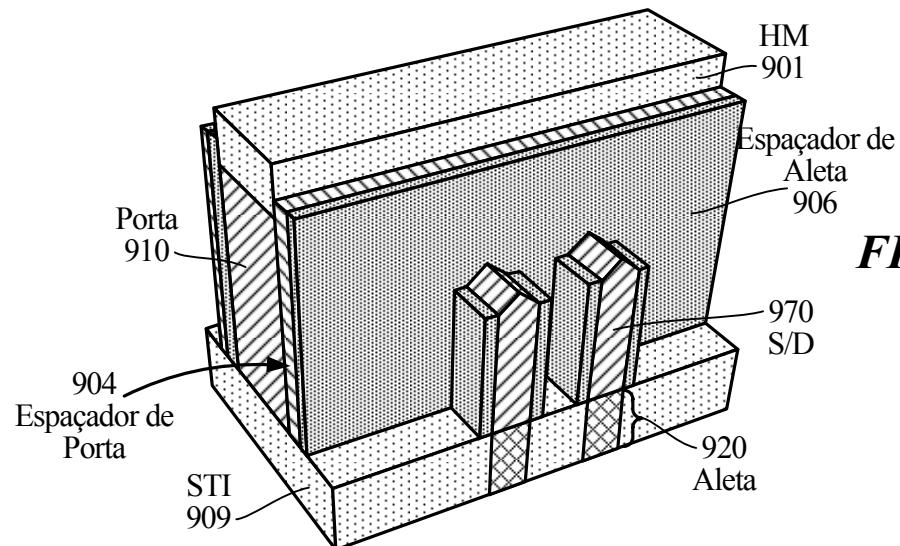

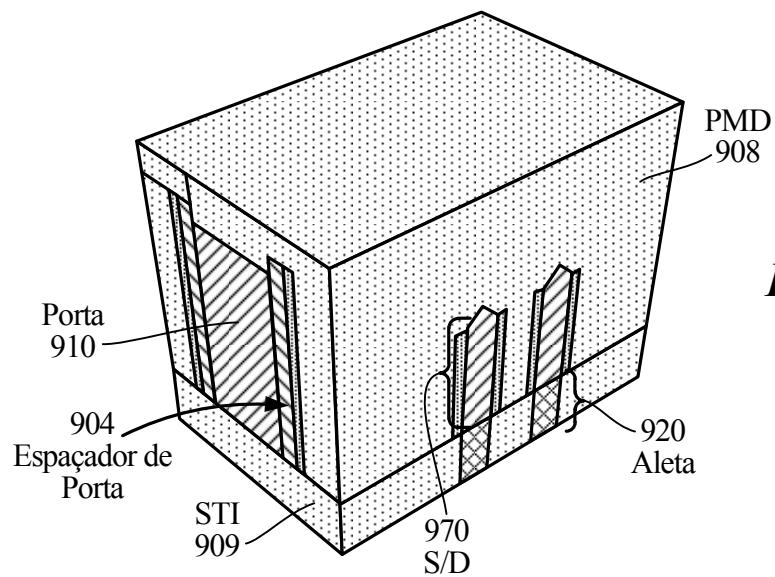

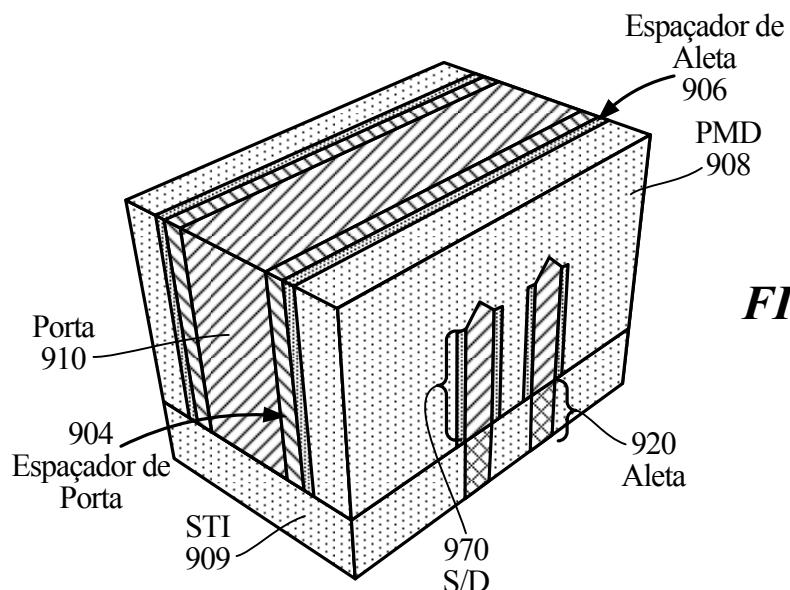

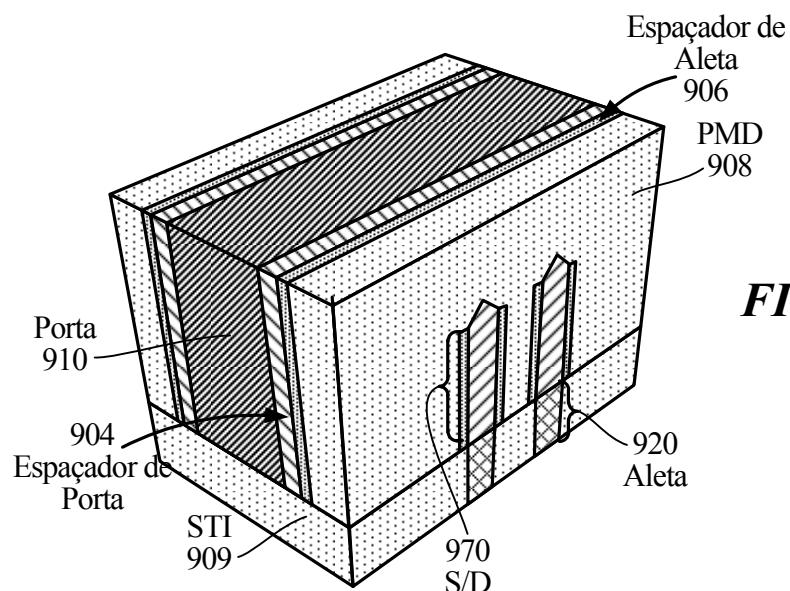

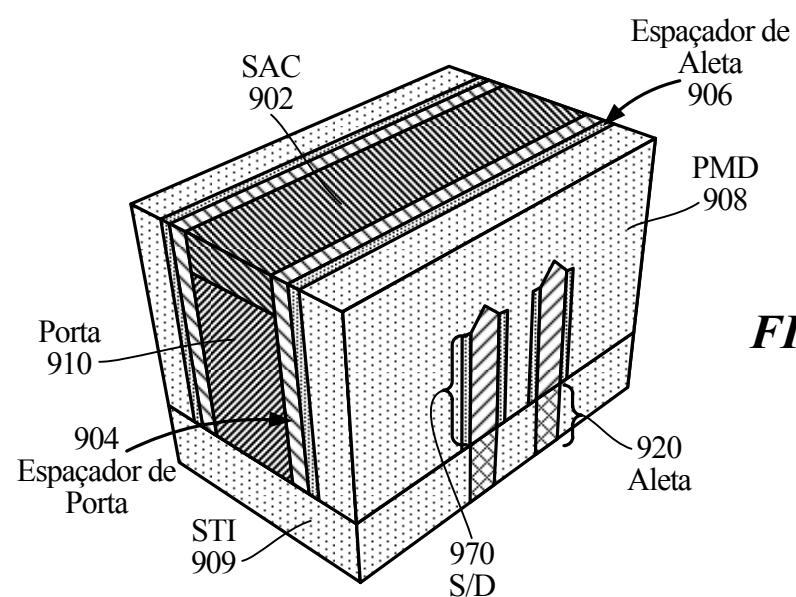

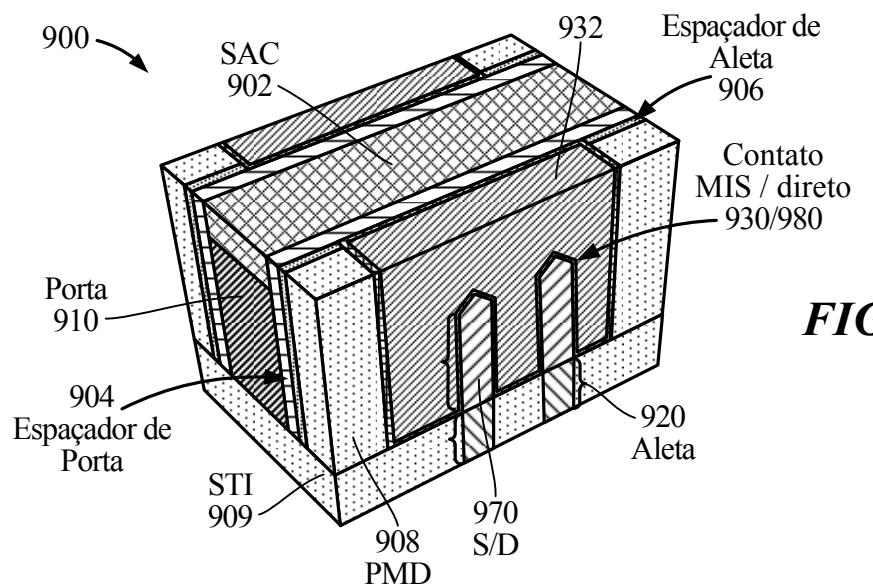

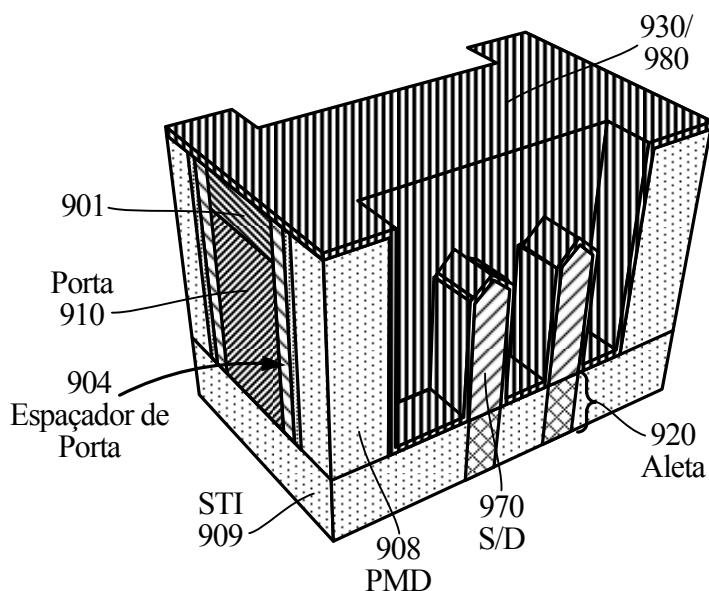

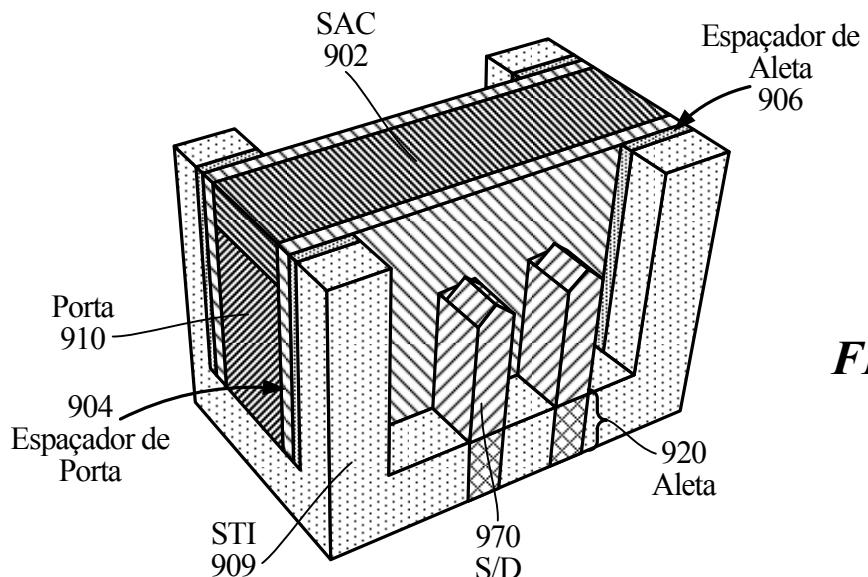

[0019] As FIGURAS 9A-9L são vistas em corte transversal que ilustram a formação de um dispositivo baseado em aletas incluindo contatos envolventes em um aspecto da presente invenção.

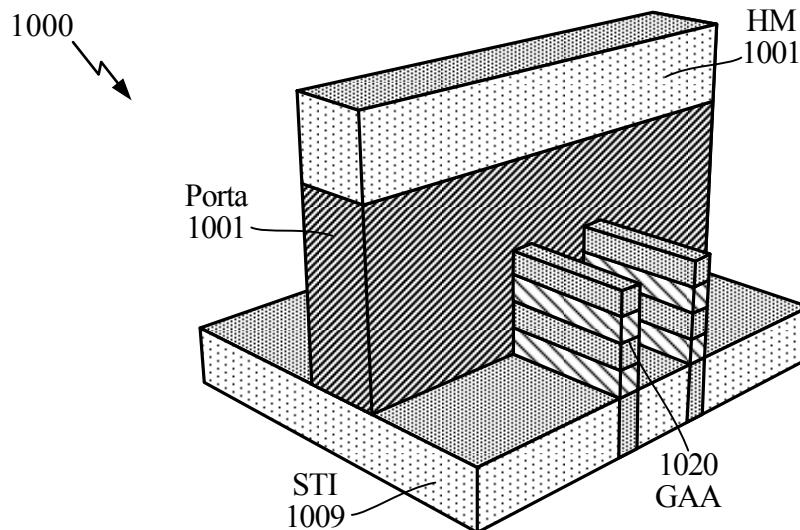

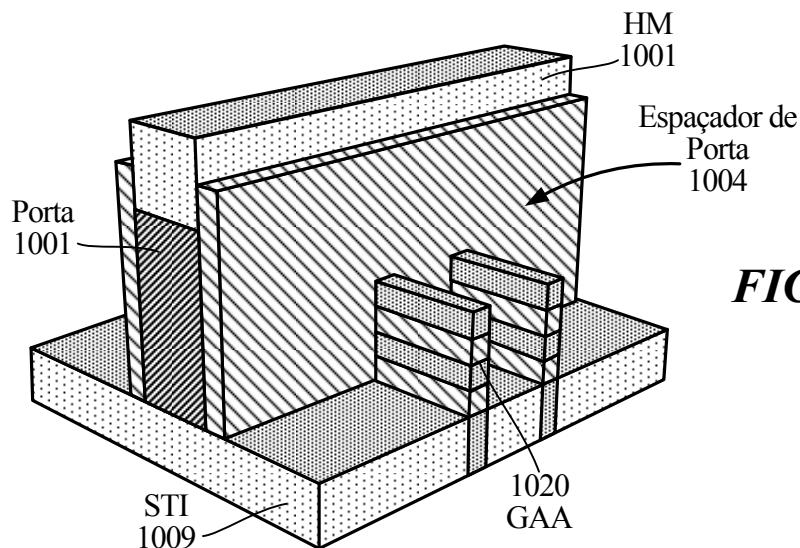

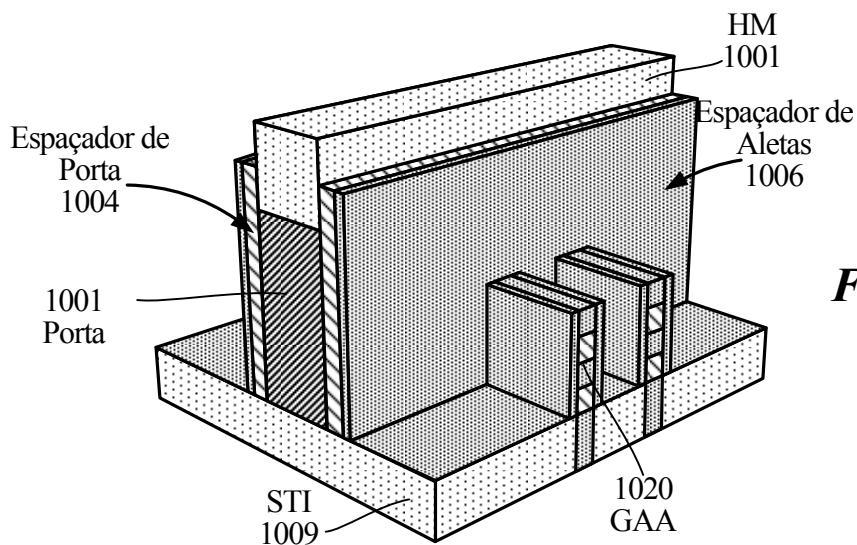

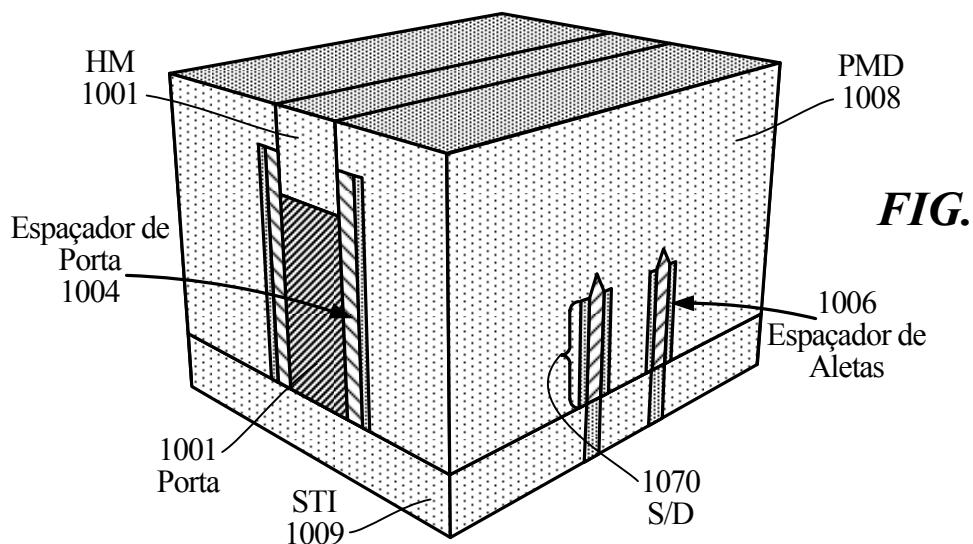

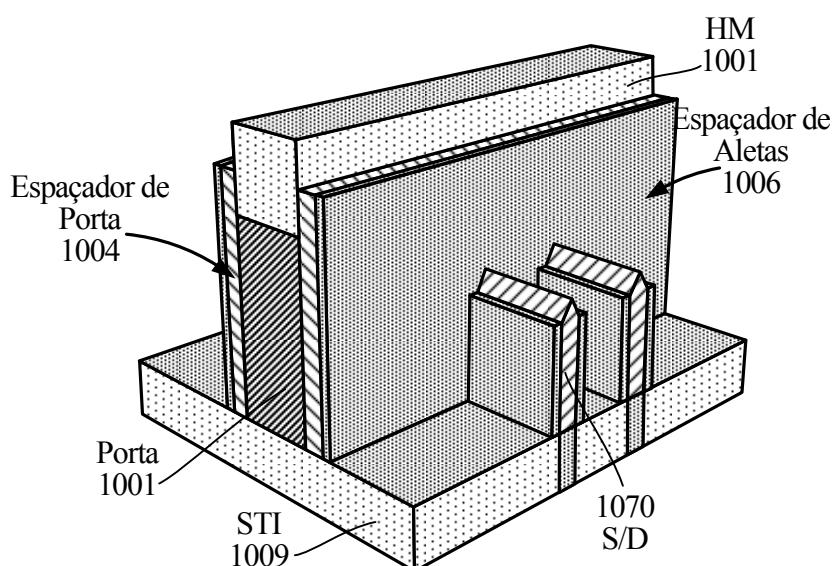

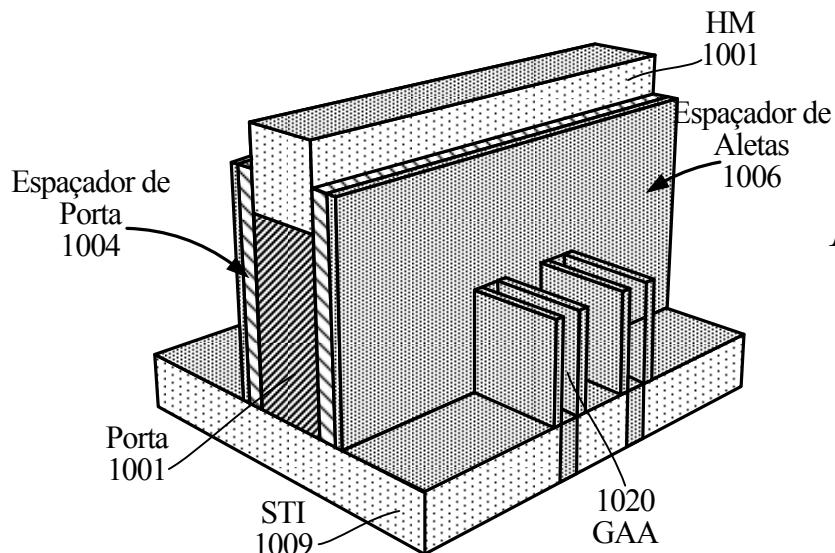

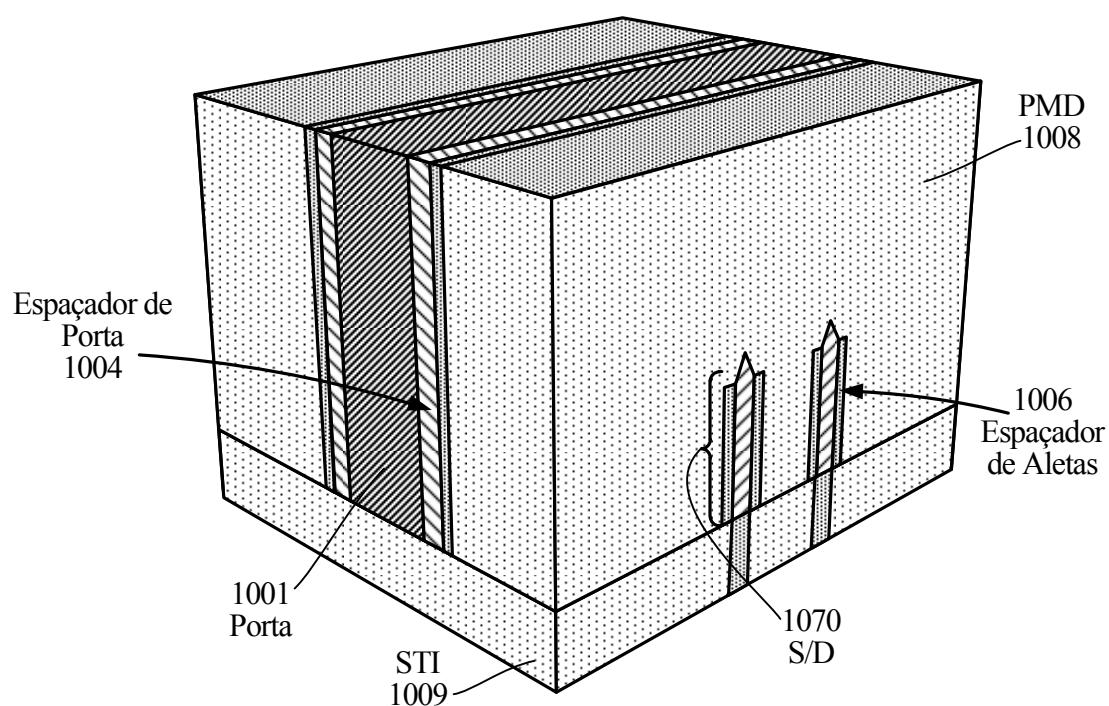

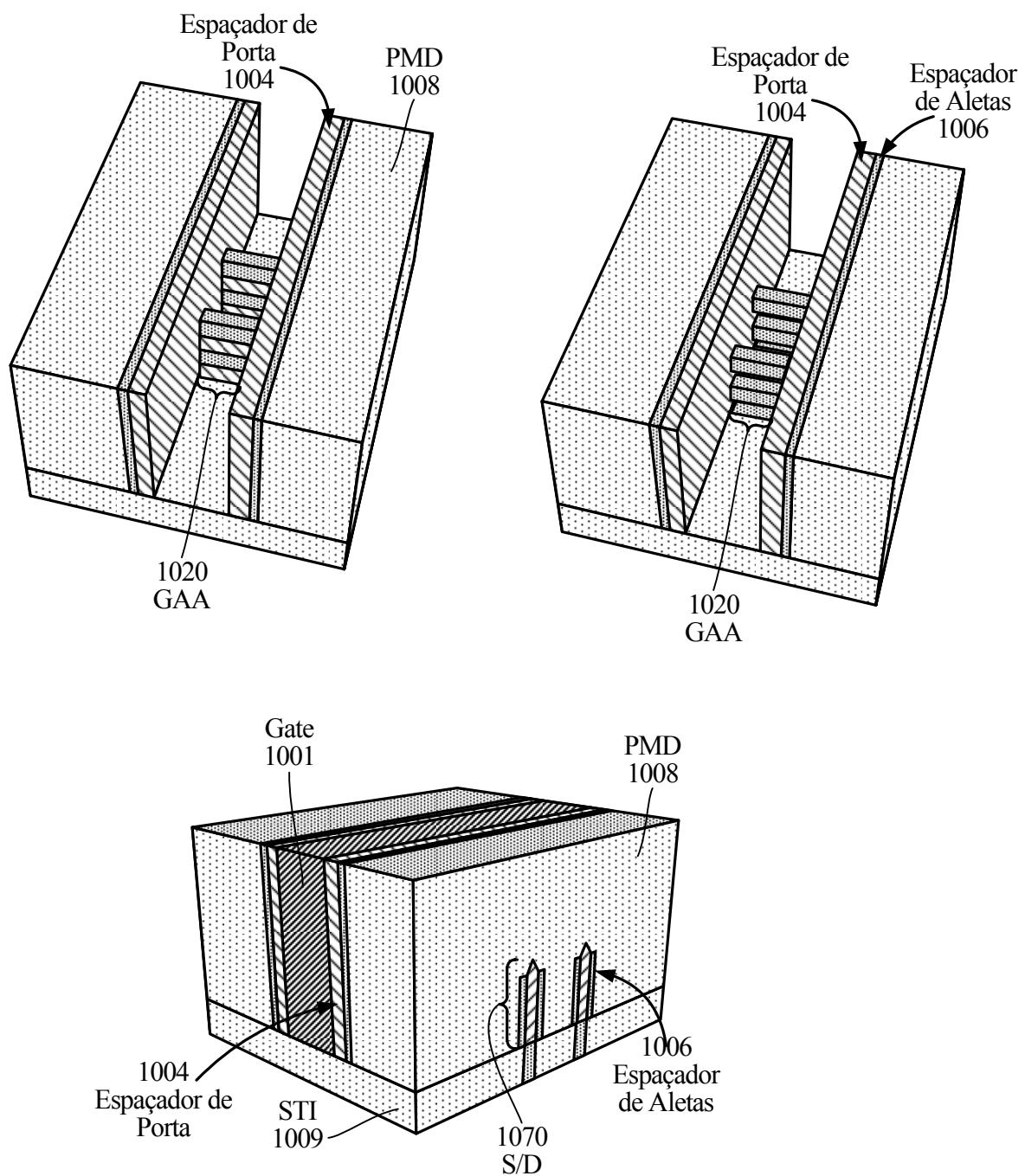

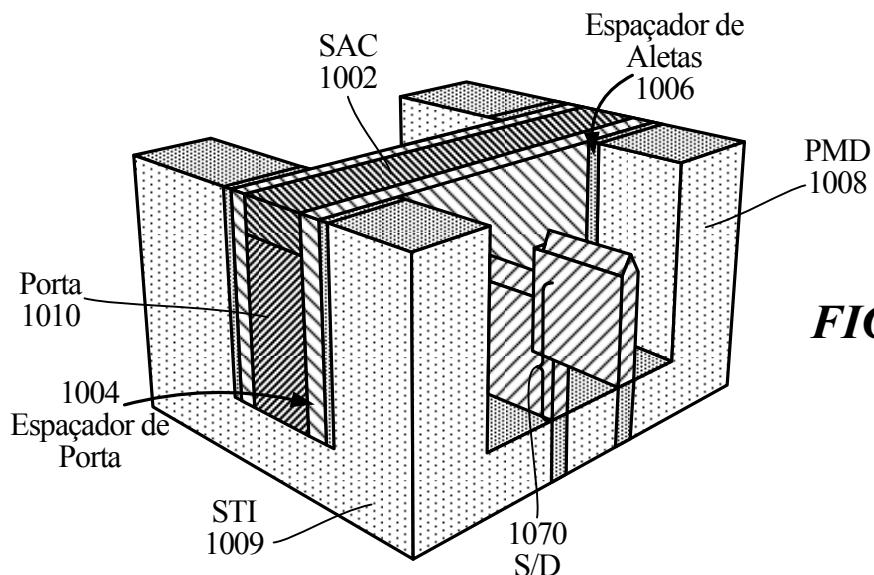

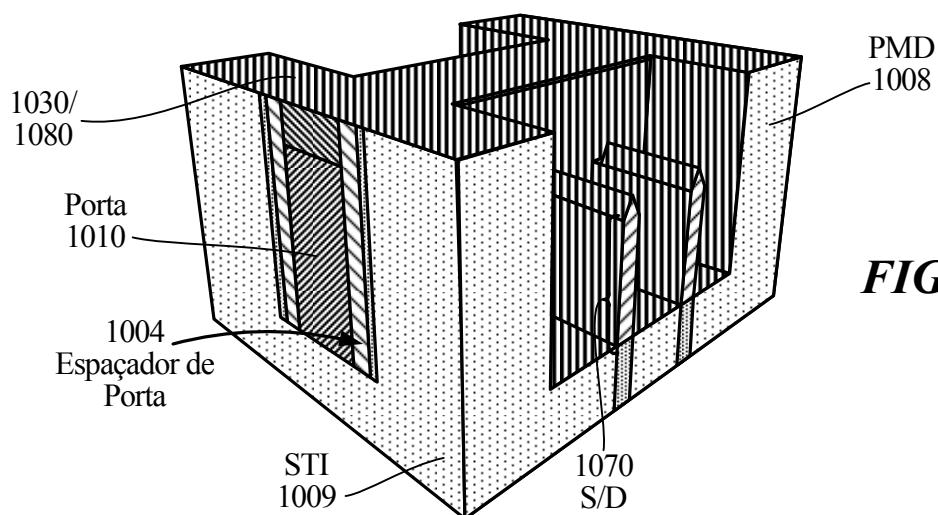

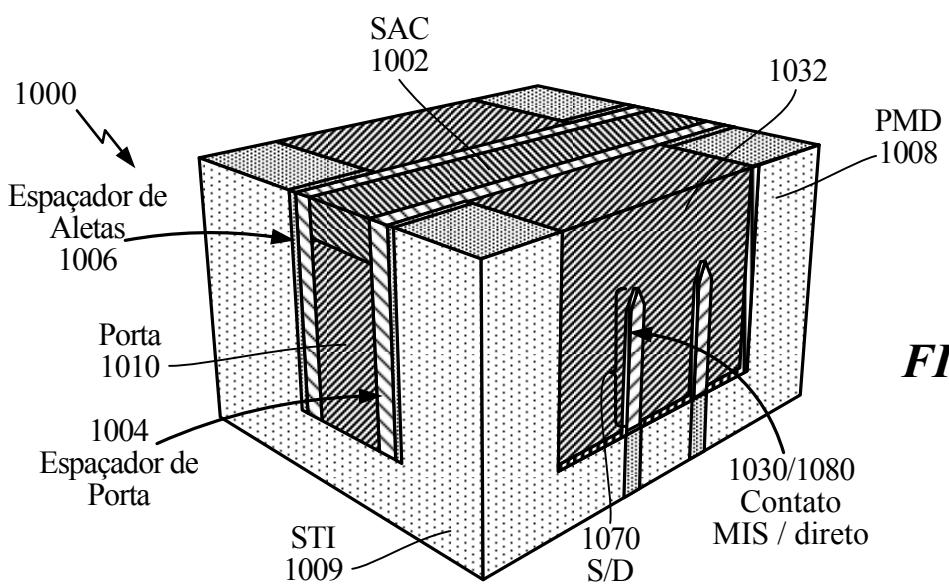

[0020] As FIGURAS 10A-10L são vistas em corte transversal que ilustram a formação de um dispositivo baseado em nanofios de uma porta circundante (GAA) incluindo contatos envolventes de acordo com aspectos da presente invenção.

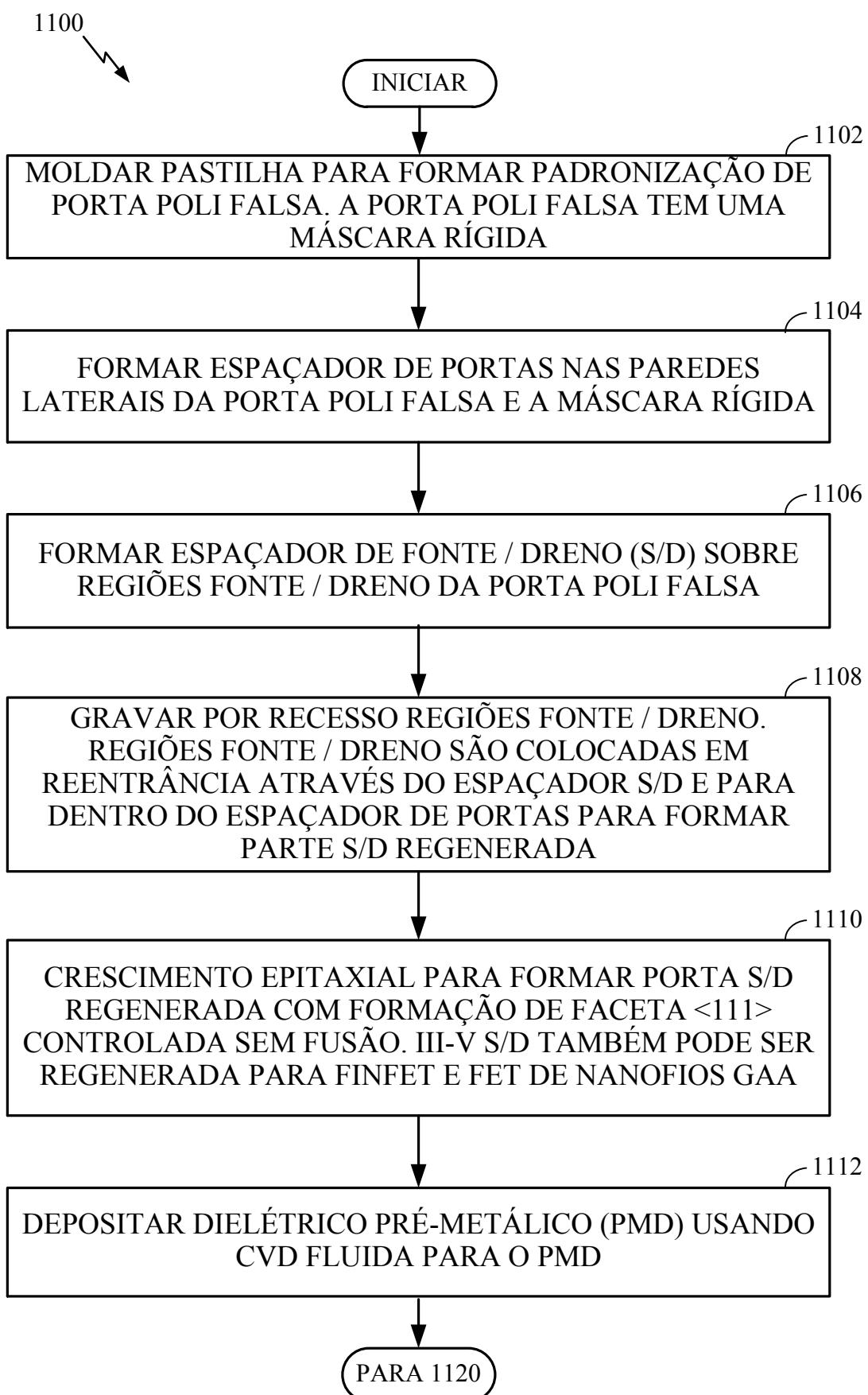

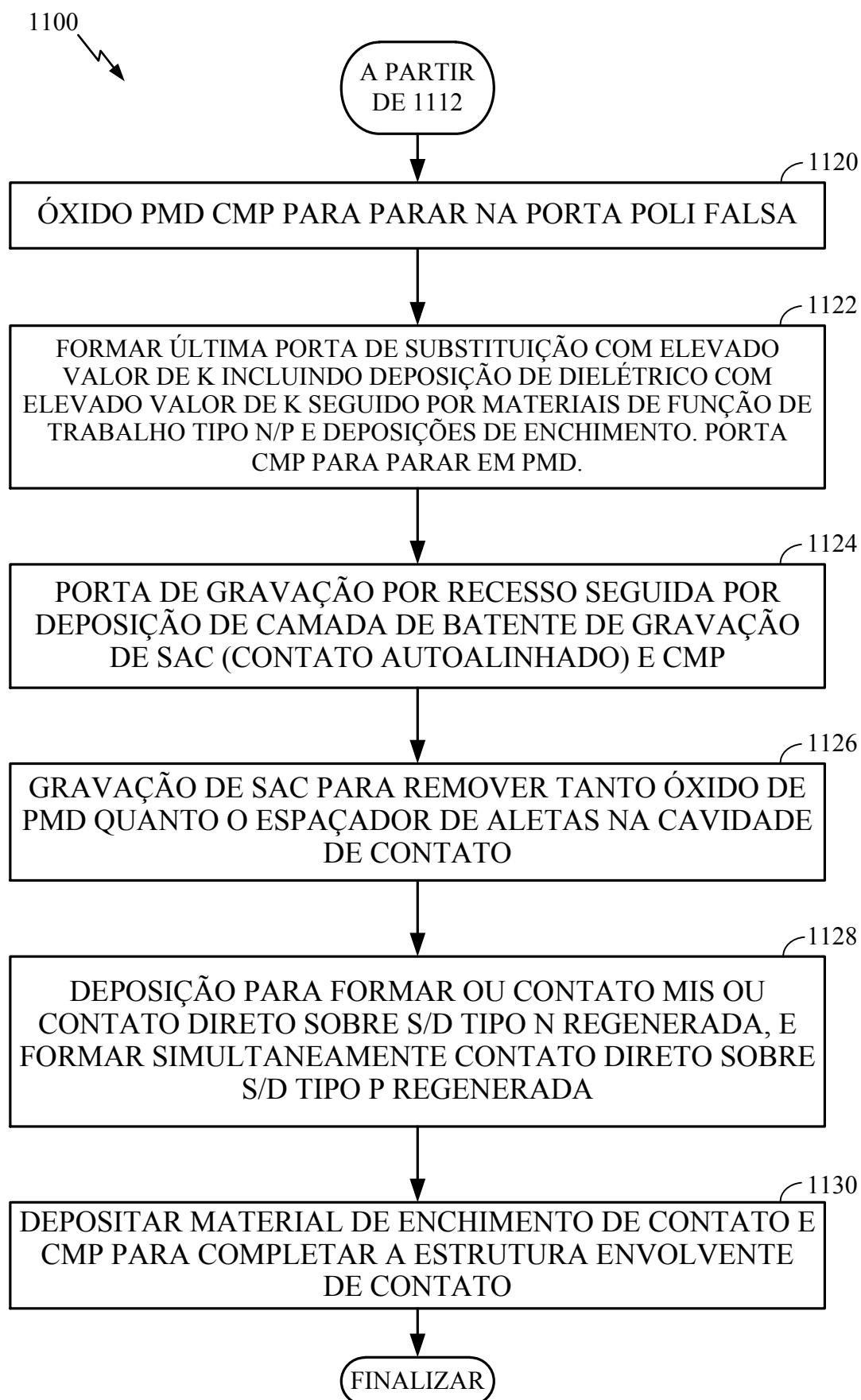

[0021] As FIGURAS 11A e 1B ilustram um método para fabricar um dispositivo semicondutor incluindo uma estrutura envolvente de contato de acordo com aspectos da presente invenção.

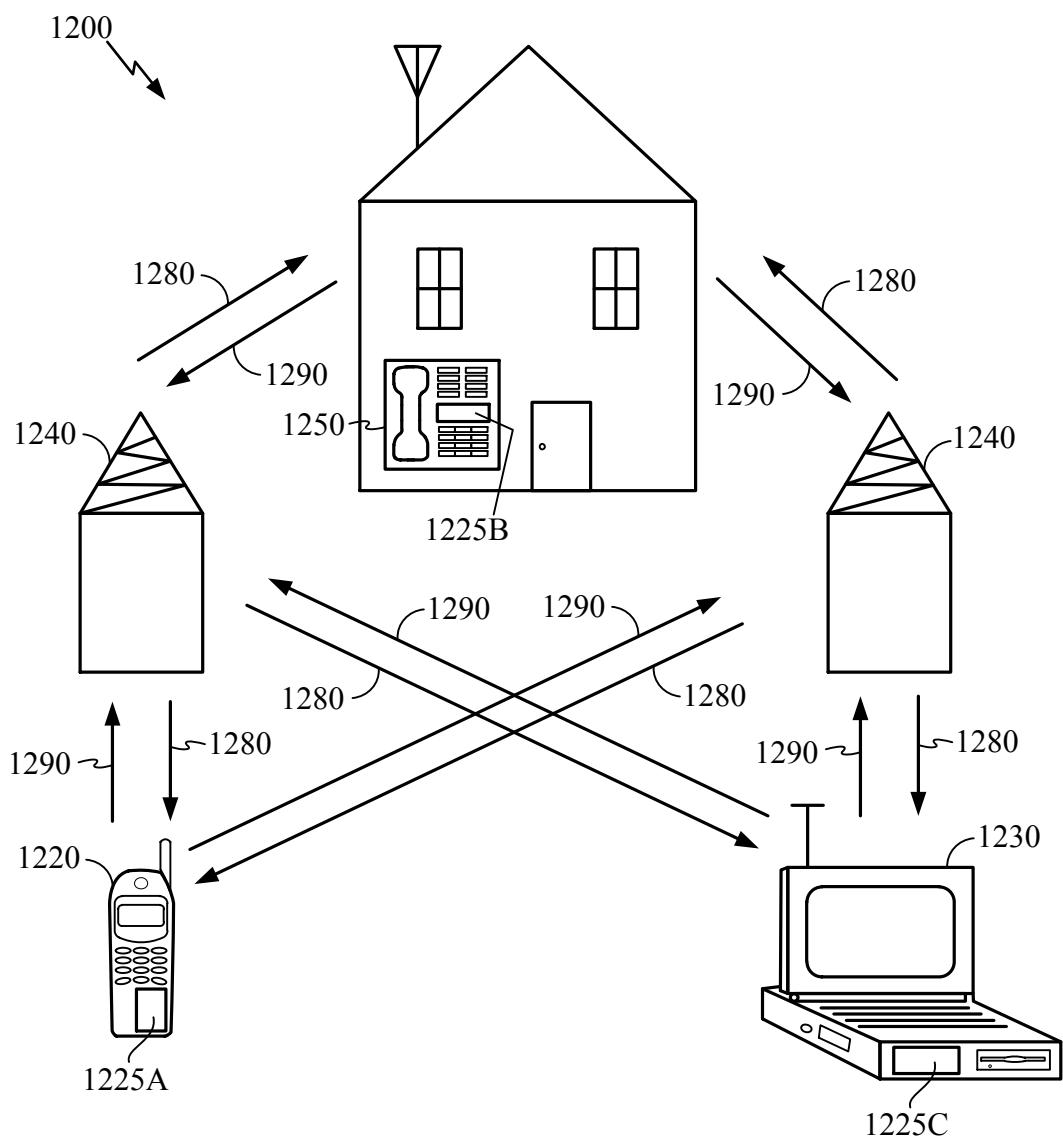

[0022] A FIGURA 12 é um diagrama em blocos que ilustra um sistema de comunicação sem fios exemplificativo, no qual aspectos da invenção podem ser usados vantajosamente.

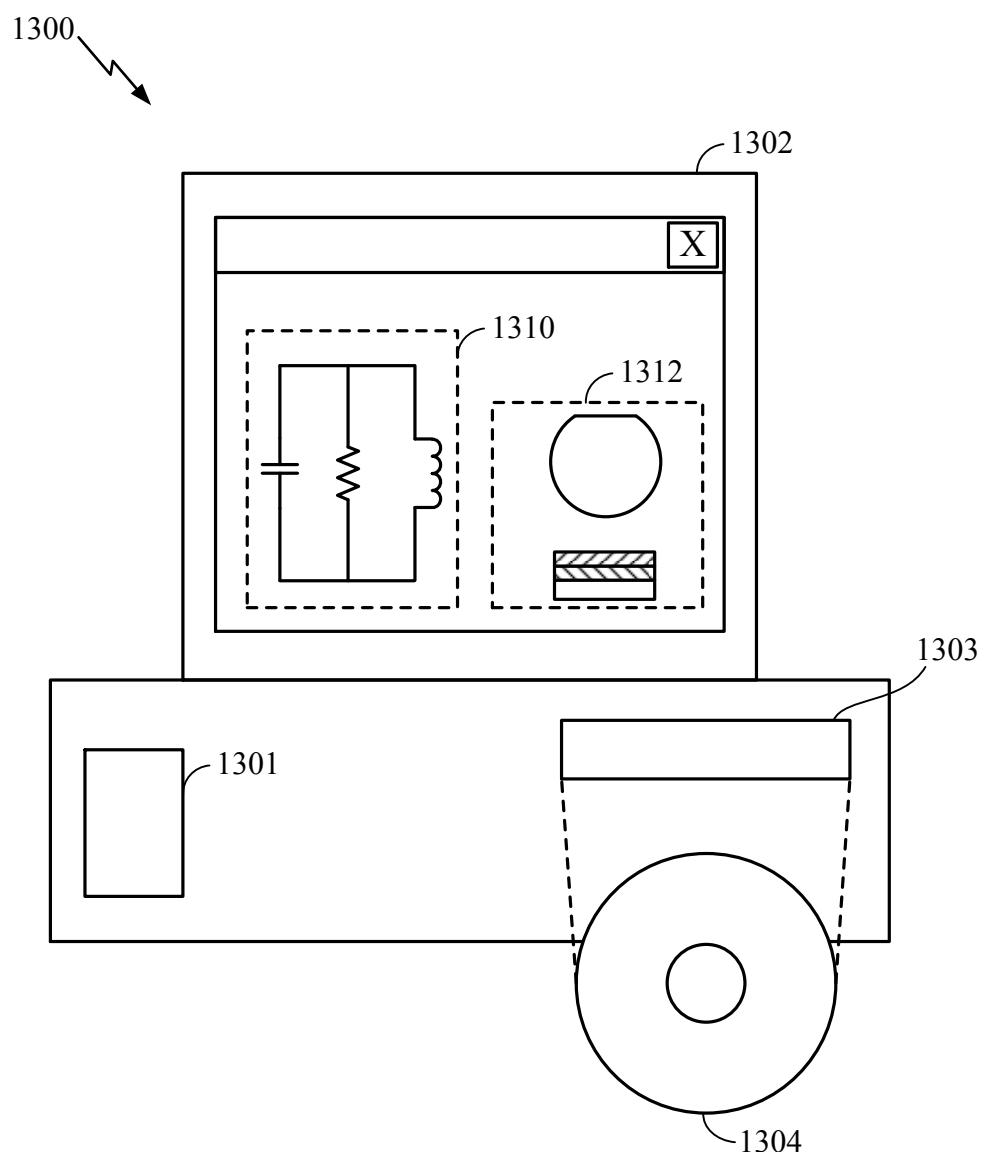

[0023] A FIGURA 13 é um diagrama em blocos que ilustra uma concepção de estação de trabalho utilizada para concepção de circuito, disposição e lógica de uma estrutura baseada em aleta de acordo com uma configuração.

#### DESCRIÇÃO DETALHADA DA INVENÇÃO

[0024] A descrição detalhada apresentada a seguir, em ligação com os desenhos anexos, pretende ser uma descrição de várias configurações e não se destina a representar as únicas configurações em que os conceitos aqui descritos podem ser praticados. A descrição detalhada inclui detalhes específicos com a finalidade de fornecer uma compreensão completa dos vários conceitos. Será evidente, no entanto, aos especialistas na técnica que estes conceitos podem ser praticados sem estes detalhes específicos. Em alguns casos, estruturas e componentes bem conhecidos são mostrados em diagrama em blocos para evitar obscurecer tais conceitos. Tal como aqui descrito, o uso do termo "e / ou" pretende representar um "OU inclusivo", e o uso do termo "ou" pretende representar um "OU exclusivo".

[0025] Processos de fabricação de semicondutores são frequentemente divididos em três partes: front-end-of-line (FEOL), middle-of-line (MOL) e back-end-of-line (BEOL). Os processos front-end-of-line incluem preparação de pastilhas, isolamento, formação de poços, padronização de portas, espaçadores e implantação de dopantes. Um

processo middle-of-line inclui a formação de contatos de porta e terminal. A formação de contatos de porta e terminal do processo middle-of-line, no entanto, é uma parte cada vez mais desafiadora do fluxo de fabricação, particularmente para a padronização de litografia. Os processos back-end-of-line incluem a formação de interligações e camadas dielétricas para acoplamento às regiões de fonte / dreno dos dispositivos FEOL utilizando contato não siliceto / não geminídeo. Estas interligações podem ser fabricadas com um processo de damasceno duplo utilizando materiais dielétricos intercamadas (ILD) depositados por deposição química a vapor enriquecida com plasma (PECVD).

[0026] À medida que a tecnologia de circuitos integrados (IC) avança, as geometrias do dispositivo são reduzidas. A geometria e "pitch" (espaçamento) entre dispositivos reduziram substancialmente em tecnologia lógica avançada. Por exemplo, em uma tecnologia lógica de sete (7) nanômetros, o espaçamento entre aletas é altamente dimensionado (por exemplo, 21 a 24 nanômetros) e o espaçamento entre portas de contato também é agressivamente reduzido (por exemplo, 39 a 45 nanômetros).

[0027] Os dispositivos baseados em aletas representam um avanço significativo na tecnologia de IC. Dispositivos baseados em aletas são estruturas tridimensionais sobre a superfície de um substrato semicondutor. Um transistor baseado em aletas, que pode ser um transistor de efeito de campo de semicondutor de óxido metálico (MOSFET), pode ser referido como um FinFET. Um transistor de efeito de campo de nanofios (FET) também representa um avanço significativo na tecnologia de IC. Um dispositivo com base em nanofios de porta circundante (GAA) é também uma estrutura tridimensional sobre a superfície de

um substrato semicondutor. Um dispositivo baseado em nanofios GAA inclui partes dopadas dos nanofios que contatam uma região de canal e servem como as regiões fonte e dreno do dispositivo. Um dispositivo baseado em nanofios GAA também é um exemplo de um dispositivo MOSFET.

[0028] O desempenho de dispositivos MOSFET pode ser afetado por numerosos fatores, incluindo o comprimento, tensão e resistência externa do canal. Um fator substancial que contribui para a resistência externa é uma resistência de contato entre as regiões fonte / dreno e as camadas condutoras (por exemplo, interligações condutoras). A resistência de contato é um limitador do desempenho e dimensionamento do dispositivo para nós de tecnologia avançada em que a geometria e "pitch" (espaçamento) entre os dispositivos são drasticamente reduzidos.

[0029] À medida que as geometrias do dispositivo são reduzidas e estruturas de dispositivos adicionais são adicionadas a um circuito integrado, a resistência de contato se torna um limitador substancial do desempenho e dimensionamento do dispositivo. Por exemplo, em nós de tecnologia avançada em que a geometria e o "pitch" (espaçamento) entre os dispositivos são dramaticamente reduzidos, a resistência de contato pode proibir o funcionamento adequado do dispositivo. Em particular, é desejada uma resistência de contato reduzida para continuar a suportar um desempenho e um dimensionamento de densidade melhorados do dispositivo para a tecnologia lógica avançada, tal como uma tecnologia lógica de sete (7) nanômetros. Nos dispositivos baseados em aletas, bem como nos dispositivos baseados em nanofios GAA, contudo, a geometria das aletas / portas e o espaçamento entre aletas / portas provoca uma substancial resistência de contato.

[0030] Vários aspectos da invenção proporcionam técnicas para fabricar uma estrutura envolvente de contato para dispositivos semicondutores. O fluxo de processo para a fabricação de semicondutores da estrutura envolvente de contato pode incluir processos front-of-line (FEOL), processos middle-of-line (MOL) e processos back-of-line (BEOL). Será entendido que o termo "camada" inclui película e não deve ser interpretado como indicando uma espessura vertical ou horizontal, a menos que indicado de outro modo. Como aqui descrito, o termo "substrato" ou pode referir-se a um substrato de uma pastilha cortada em cubos ou pode referir-se ao substrato de uma pastilha que não está cortada em cubos. Da mesma forma, os termos pastilha e matriz podem ser usados indistintamente, a menos que essa troca ponha a credulidade à prova.

[0031] Aspectos da presente invenção incluem um fluxo de integração inovador para formar contatos envolventes em aletas altamente dimensionadas com contatos metal-isolador-semicondutor (MIS) ou contatos diretos para reduzir drasticamente a resistência de contato. Aspectos adicionais da presente invenção também podem proporcionar um contato MIS ou um contato direto com a fonte / dreno de dispositivos à base de nanofios de porta circundante (GAA) e outro dispositivo semicondutor similar para reduzir a resistência de contato. Uma estrutura envolvente de contato, incluindo contatos envolventes, pode permitir operação dentro das geometrias de dispositivos reduzidas da tecnologia lógica avançada, tal como tecnologia lógica de sete (7) nanômetros e além. Uma estrutura envolvente de contato pode ser fabricada utilizando capacidades de processo e materiais existentes, ao mesmo tempo proporcionando uma substancial redução da resistência de contato.

[0032] A FIGURA 1 ilustra uma vista em perspectiva de uma pastilha semicondutora em um aspecto da presente invenção. Uma pastilha 100 pode ser uma pastilha semicondutora, ou pode ser um material de substrato com uma ou mais camadas de material semicondutor sobre uma superfície da pastilha 100. Quando a pastilha 100 é um material semicondutor, ela pode ser desenvolvida a partir de um cristal de semente utilizando o processo de Czochralski, em que o cristal de semente é mergulhado em um banho fundido de material semicondutor e lentamente girado e removido do banho. O material fundido então cristaliza sobre o cristal de semente na orientação do cristal.

[0033] A pastilha 100 pode ser um material composto, tal como arseneto de gálio (GaAs) ou nitreto de gálio (GaN), um material ternário tal como arseneto de índio-gálio (InGaAs), materiais quaternários ou qualquer material que possa ser um material de substrato para outros materiais semicondutores. Embora muitos dos materiais possam ser de natureza cristalina, também podem ser utilizados materiais policristalinos ou amorfos para a pastilha 100.

[0034] A pastilha 100, ou camadas que estão acopladas à pastilha 100, pode ser fornecida com materiais que tornam a pastilha 100 mais condutora. Por exemplo, e não a título de limitação, uma pastilha de silício pode ter fósforo ou boro adicionado à pastilha 100 para permitir que a carga eléctrica flua na pastilha 100. Estes aditivos são referidos como dopantes e proporcionam portadores de carga extra (ou elétrons ou buracos) dentro da pastilha 100 ou partes da pastilha 100. Seleccionando as áreas onde são fornecidos os portadores de carga extra, que tipo de portadores de carga são fornecidos e a quantidade (densidade) de portadores de carga adicionais na pastilha

100, podem ser formados diferentes tipos de dispositivos eletrônicos na ou sobre a pastilha 100.

[0035] A pastilha 100 tem uma orientação 102 que indica a orientação cristalina da pastilha 100. A orientação 102 pode ser uma borda plana da pastilha 100 como mostrado na FIG. 1, ou pode ser um entalhe ou outros sinais para ilustrar a orientação cristalina da pastilha 100. A orientação 102 pode indicar os índices de Miller para os planos da rede cristalina na pastilha 100.

[0036] Os índices de Miller formam um sistema de notação dos planos cristalográficos em redes de cristais. Os planos de rede podem ser indicados por três inteiros  $h$ ,  $k$  e  $\ell$ , que são os índices de Miller para um plano ( $hkl$ ) no cristal. Cada índice denota um plano ortogonal a uma direção ( $h$ ,  $k$ ,  $\ell$ ) na base dos vetores de rede recíprocos. Os inteiros são geralmente escritos em termos mais baixos (por exemplo, seu maior divisor comum deve ser 1). O índice de Miller 100 representa um plano ortogonal à direção  $h$ ; o índice 010 representa um plano ortogonal à direção  $k$  e o índice 001 representa um plano ortogonal a  $\ell$ . Para alguns cristais, são usados números negativos (escritos como uma barra sobre o índice) e para alguns cristais, como nitreto de gálio, mais de três números podem ser usados para descrever adequadamente os diferentes planos cristalográficos.

[0037] Uma vez que a pastilha 100 foi processada como desejado, a pastilha 100 é dividida ao longo das linhas de corte 104. As linhas de corte 104 indicam onde a pastilha 100 deve ser quebrada ou separada em pedaços. As linhas de corte 104 podem definir o contorno dos vários circuitos integrados que foram fabricados na pastilha 100.

[0038] Uma vez definidas as linhas de corte 104, a pastilha 100 pode ser serrada ou separada de outra forma

em pedaços para formar a matriz 106. Cada uma das matrizes 106 pode ser um circuito integrado com muitos dispositivos ou pode ser um único dispositivo eletrônico. O tamanho físico da matriz 106, que também pode ser referido como um chip ou um chip semicondutor, depende, pelo menos em parte, da capacidade de separar a pastilha 100 em certos tamanhos, bem como o número de dispositivos individuais que a matriz 106 é projetada para conter.

[0039] Uma vez que a pastilha 100 foi separada em uma ou mais matrizes 106, a matriz 106 pode ser montada na embalagem para permitir o acesso aos dispositivos e / ou circuitos integrados fabricados na matriz 106. A embalagem pode incluir embalagens individuais em linha, embalagens duplas em linha, embalagens de placas-mãe, acondicionamentos flip-chip, acondicionamentos pontilhados com índio ou outros tipos de dispositivos que proporcionam acesso à matriz 106. A matriz 106 também pode ser acessada diretamente através de ligação por arame, sondas ou outras ligações, sem montar a matriz 106 em uma embalagem separada.

[0040] A FIGURA 2 ilustra uma vista em corte transversal de uma matriz 106 de acordo com um aspecto da presente invenção. Na matriz 106, pode haver um substrato 200, que pode ser um material semicondutor e / ou pode atuar como um suporte mecânico para dispositivos eletrônicos. O substrato 200 pode ser um substrato semicondutor dopado, que tem portadores de carga de elétrons (designados por canal N) ou buracos (designados por canal P) presentes em todo o substrato 200. A dopagem subsequente do substrato 200 com íons / átomos portadores de carga pode alterar as capacidades de transporte de carga do substrato 200.

[0041] Dentro de um substrato 200 (por exemplo, um substrato semicondutor), podem existir poços 202 e 204, que podem ser a fonte e / ou dreno de um transístor de campo-efeito (FET), ou os poços 202 e / ou 204 podem ser estruturas de aleta de um FET estruturado em aleta (FinFET). Os poços 202 e / ou 204 podem também ser outros dispositivos (por exemplo, um resistor, um capacitor, um diodo ou outros dispositivos eletrônicos) dependendo da estrutura e outras características dos poços 202 e / ou 204 e da estrutura envolvente do substrato 200.

[0042] O substrato semicondutor pode também ter um poço 206 e um poço 208. O poço 208 pode estar completamente dentro do poço 206 e, em alguns casos, pode formar um transístor de junção bipolar (BJT). O poço 206 também pode ser utilizado como um poço de isolamento para isolar o poço 208 de campos elétricos e / ou magnéticos no interior da matriz 106.

[0043] As camadas (por exemplo, 210 a 214) podem ser adicionadas à matriz 106. A camada 210 pode ser, por exemplo, um óxido ou camada isolante que pode isolar os poços (por exemplo, 202-208) uns dos outros ou de outros dispositivos sobre a matriz 106. Em tais casos, a camada 210 pode ser dióxido de silício, um polímero, um dielétrico, ou outra camada eletricamente isolante. A camada 210 pode também ser uma camada de interligação, podendo nesse caso compreender um material condutor tal como cobre, tungstênio, alumínio, uma liga ou outros materiais condutores ou metálicos.

[0044] A camada 212 pode também ser uma camada dielétrica ou condutora, dependendo das características desejadas do dispositivo e / ou dos materiais das camadas (por exemplo, 210 e 214). A camada 214 pode ser uma camada encapsulante, que pode proteger as camadas (por exemplo,

210 e 212), bem como os poços 202-208 e o substrato 200, de forças externas. Por exemplo, e não a título de limitação, a camada 214 pode ser uma camada que protege a matriz 106 de danos mecânicos, ou a camada 214 pode ser uma camada de material que protege a matriz 106 de danos eletromagnéticos ou de radiação.

[0045] Os dispositivos eletrônicos concebidos sobre a matriz 106 podem compreender muitas características ou componentes estruturais. Por exemplo, a matriz 106 pode ser exposta a qualquer número de métodos para atribuir dopantes ao substrato 200, aos poços 202-208 e, se desejado, às camadas (por exemplo, 210-214). Por exemplo, e não a título de limitação, a matriz 106 pode ser exposta à implantação iônica, deposição de átomos dopantes que são conduzidos para uma estrutura cristalina através de um processo de difusão, deposição química a vapor, crescimento epitaxial ou outros métodos. Através do crescimento seletivo, seleção de material e remoção de partes das camadas (por exemplo, 210-214), e através de remoção seletiva, seleção de material e concentração de dopante do substrato 200 e dos poços 202-208, muitas estruturas e dispositivos eletrônicos diferentes podem ser formados dentro do âmbito da presente invenção.

[0046] Além disso, o substrato 200, os poços 202-208 e as camadas (por exemplo, 210-214) podem ser seletivamente removidos ou adicionados através de vários processos. A gravação química a úmido, planarização mecânica química (CMP), gravação por plasma, mascaramento de fotorresistência, processos damascênicos e outros métodos podem criar as estruturas e dispositivos da presente invenção.

[0047] A FIGURA 3 ilustra uma vista em corte transversal de um dispositivo de transistor de campo-efeito

de semicondutor de óxido metálico (MOSFET) 300 em um aspecto da presente invenção. O dispositivo MOSFET 300 pode ter quatro terminais de entrada. As quatro entradas são uma fonte 302, uma porta 304, um dreno 306 e um substrato 308. A fonte 302 e o dreno 306 podem ser fabricados como os poços 202 e 204 no substrato 308, ou podem ser fabricados como áreas acima do substrato 308, ou como parte das outras camadas sobre a matriz 106. Tais outras estruturas podem ser uma aleta ou outra estrutura que sobressai de uma superfície do substrato 308. Além disso, o substrato 308 pode ser o substrato 200 sobre a matriz 106, mas o substrato 308 também pode ser uma ou mais das camadas (por exemplo, 210-214) que são acopladas ao substrato 200.

[0048] O dispositivo MOSFET 300 é um dispositivo unipolar, uma vez que corrente elétrica é produzida por apenas um tipo de portador de carga (por exemplo, ou elétrons ou buracos) dependendo do tipo de MOSFET. O dispositivo MOSFET 300 opera controlando a quantidade de portadores de carga no canal 310 entre a fonte 302 e o dreno 306. Uma tensão Vfonte 312 é aplicada à fonte 302, uma tensão Vporta 314 é aplicada à porta 304, e uma tensão Vdreno 316 é aplicada ao dreno 306. Uma tensão Vsubstrato separada 318 também pode ser aplicada ao substrato 308, embora a tensão Vsubstrato 318 possa ser acoplada a uma dentre tensão Vfonte 312, tensão Vporta 314 ou tensão Vdreno 316.

[0049] Para controlar os portadores de carga no canal 310, a tensão Vporta 314 cria um campo elétrico no canal 310 quando a porta 304 acumula cargas. A carga oposta à que se acumula sobre a porta 304 começa a acumular-se no canal 310. O isolador de porta 320 isola as cargas acumuladas na porta 304 da fonte 302, do dreno 306 e do canal 310. A porta 304 e o canal 310, com o isolador de

porta 320 entre eles, criam um condensador, e à medida que a tensão Vporta 314 aumenta, os portadores de carga na porta 304, atuando como uma placa deste condensador, começam a acumular-se. Este acúmulo de cargas na porta 304 atrai os portadores de carga opostos para dentro do canal 310. Eventualmente, portadores de carga suficientes são acumulados no canal 310 para proporcionar um percurso eletricamente condutor entre a fonte 302 e o dreno 306. Esta condição pode ser referida como abrindo o canal do FET.

[0050] Alterando a tensão Vfonte 312 e a tensão Vdreno 316 e a sua relação com a tensão Vporta 314, a quantidade de tensão aplicada à porta 304 que abre o canal 310 pode variar. Por exemplo, a tensão Vfonte 312 é usualmente de um potencial mais elevado do que o da tensão Vdreno 316. Tornar o diferencial de tensão entre a tensão Vfonte 312 e a tensão Vdreno 316 maior irá mudar a quantidade da tensão Vporta 314 usada para abrir o canal 310. Além disso, um diferencial de tensão maior irá alterar a quantidade de força eletromotriz que move os portadores de carga através do canal 310, criando uma corrente maior através do canal 310.

[0051] O material do isolador de porta 320 pode ser óxido de silício, ou pode ser um material dielétrico ou outro com uma constante dielétrica ( $k$ ) diferente da do óxido de silício. Além disso, o isolador de porta 320 pode ser uma combinação de materiais ou diferentes camadas de materiais. Por exemplo, o isolador de porta 320 pode ser Óxido de Alumínio, Óxido de Hafnio, Nitreto de Óxido de Hafnio, Óxido de Zircônio ou laminados e / ou ligas destes materiais. Outros materiais para o isolador de porta 320 podem ser utilizados sem afastamento do âmbito da presente invenção.

[0052] Alterando o material para o isolador de porta 320 e a espessura do isolador de porta 320 (por exemplo, a distância entre a porta 304 e o canal 310), a quantidade de carga na porta 304 para abrir o canal 310 pode variar. Também é ilustrado um símbolo 322 mostrando os terminais do dispositivo MOSFET 300. Para os MOSFETs do canal N (utilizando elétrons como portadores de carga no canal 310), é aplicada uma seta ao terminal do substrato 308 no símbolo 322 que aponta para longe do terminal da porta 304. Para MOSFETs do tipo p (utilizando buracos como portadores de carga no canal 310), é aplicada uma seta ao terminal do substrato 308 no símbolo 322 que aponta para o terminal da porta 304.

[0053] A porta 304 pode também ser feita de materiais diferentes. Em alguns desenhos, a porta 304 é feita de silício policristalino, também referido como polissilício ou poli, que é uma forma condutora de silício. Embora referidos neste documento como "poli" ou "polissilício", metais, ligas ou outros materiais eletricamente condutores são contemplados como materiais apropriados para a porta 304, tal como descrito na presente descrição.

[0054] Em algumas concepções de MOSFET, pode ser desejado um material de elevado valor de  $k$  no isolador de porta 320 e, nessas concepções, podem ser usados outros materiais condutores. Por exemplo, e não a título de limitação, uma concepção de "porta de elevado valor de metal  $k$ " pode empregar um metal, tal como cobre, para o terminal da porta 304. Embora referidos como "metal", materiais policristalinos, ligas, ou outros materiais eletricamente condutores são contemplados como materiais apropriados para a porta 304, como descrito na presente invenção.

[0055] Para interligar-se ao dispositivo MOSFET 300, ou para interligar-se a outros dispositivos na matriz 106 (por exemplo, semicondutor), são utilizados traços ou camadas de interligação. Estes traços de interligação podem estar em uma ou mais camadas (por exemplo, 210-214), ou podem estar em outras camadas da matriz 106.

[0056] A FIGURA 4 ilustra um transistor de acordo com um aspecto da presente invenção. Um FET estruturado em aletas (FinFET 400) funciona de forma semelhante ao dispositivo MOSFET 300 descrito em relação à FIG. 3. Uma aleta 410 em um FinFET 400, contudo, é desenvolvida ou de outro modo acoplada ao substrato 308. O substrato 308 pode ser um substrato semicondutor ou outra camada de suporte semelhante, por exemplo, compreendendo uma camada de óxido, uma camada de nitreto, uma camada de óxido metálico ou uma camada de silício. A aleta 410 inclui a fonte 302 e o dreno 306. Uma porta 304 está disposta sobre a aleta 410 e sobre o substrato 308 através de um isolador de porta 320. Uma altura,  $H_{fin}$ , uma largura,  $W_{fin}$  e um comprimento,  $L_{fin}$ , representam as dimensões da aleta. Em uma estrutura FinFET, o tamanho físico do FinFET 400 pode ser menor do que a estrutura do dispositivo MOSFET 300 ilustrada na FIG. 3. Esta redução no tamanho físico permite mais dispositivos por unidade de área sobre a matriz 106.

#### ESTRUTURA ENVOLVENTE DE CONTATO

[0057] Os dispositivos baseados em aletas representam um avanço significativo na tecnologia de IC. Dispositivos baseados em aletas são estruturas tridimensionais sobre a superfície de um substrato semicondutor. Um transistor baseado em aletas, que pode ser um transistor de efeito de campo do semicondutor de óxido metálico baseado em aletas (MOSFET), pode ser referido como um FinFET. Um transistor de efeito de campo de nanofios

(FET) também representa um avanço significativo na tecnologia de IC. Um dispositivo com base em nanofios de porta circundante (GAA) é também uma estrutura tridimensional sobre a superfície de um substrato semicondutor. Um dispositivo baseado em nanofios GAA inclui partes dopadas dos nanofios que contatam uma região de canal e servem como as regiões fonte e dreno do dispositivo. Um dispositivo baseado em nanofios GAA também é um exemplo de um dispositivo MOSFET. Em uma configuração, é descrito um transistor de efeito de campo de nanofios (FET) de porta circundante.

[0058] O desempenho dos dispositivos MOSFET pode ser afetado por numerosos fatores, incluindo o comprimento, tensão e resistência externa do canal. Um fator substancial que contribui para a resistência externa é uma resistência de contato entre as regiões fonte / dreno e as camadas condutoras. A resistência de contato é um limitador do desempenho e dimensionamento do dispositivo para nós de tecnologia avançada em que a geometria e "pitch" (espaçamento) entre os dispositivos são drasticamente reduzidos.

[0059] À medida que as geometrias do dispositivo são reduzidas, e estruturas de dispositivos adicionais são adicionadas a um circuito integrado, a resistência de contato se torna um limitador substancial do desempenho e dimensionamento do dispositivo. Por exemplo, em nós de tecnologia avançada em que a geometria e o "pitch" (espaçamento) entre dispositivos são dramaticamente reduzidos, a resistência de contato pode proibir o funcionamento adequado do dispositivo. Em particular, é desejada uma resistência de contato reduzida para continuar a suportar o desempenho do dispositivo e o dimensionamento de densidade melhorados para a tecnologia lógica avançada,

tal como a tecnologia lógica de sete (7) nanômetros e além. Nos dispositivos baseados em aletas, bem como nos dispositivos baseados em nanofios de GAA, contudo, a geometria das aletas / portas, e o espaçamento entre as aletas / portas provoca uma substancial resistência de contato.

[0060] Vários aspectos da invenção proporcionam técnicas para fabricar uma estrutura envolvente de contato para dispositivos semicondutores. O fluxo de processo para a fabricação de semicondutores da estrutura envolvente de contato pode incluir processos front-end-of-line (FEOL), processos middle-of-line (MOL) e processos back-end-of-line (BEOL). Será entendido que o termo "camada" inclui película e não deve ser interpretado como indicando uma espessura vertical ou horizontal, a menos que indicado de outro modo. Como aqui descrito, o termo "substrato" ou pode referir-se a um substrato de uma pastilha cortada em cubos ou pode referir-se ao substrato de uma pastilha que não está cortada em cubos. Da mesma forma, os termos pastilha e matriz podem ser usados indistintamente, a menos que tal troca coloque a credibilidade à prova.

[0061] Aspectos da presente invenção incluem um fluxo de integração inovador para formar contatos envolventes em aletas altamente dimensionadas com contatos do metal-isolador-semicondutor (MIS) ou contatos diretos para reduzir drasticamente a resistência de contato. Aspectos adicionais da presente invenção podem também proporcionar um contato MIS ou um contato direto com a fonte / dreno de dispositivos à base de nanofios de porta circundante (GAA) e outros dispositivos semicondutores semelhantes para reduzir a resistência de contato. As estruturas envolventes de contato, incluindo contatos envolventes, podem permitir a operação dentro das

geometrias reduzidas do dispositivo da tecnologia lógica avançada. Uma estrutura envolvente de contato pode ser fabricada utilizando materiais e capacidades de processo existentes, proporcionando ao mesmo tempo uma substancial redução da resistência de contato.

[0062] A FIGURA 5A ilustra uma vista em corte transversal de uma estrutura baseada em aletas 500 que inclui uma primeira estrutura de contato 510 convencional. A estrutura baseada em aletas 500 pode ser utilizada dentro de um circuito integrado. As aletas 520 podem ser suportadas por um substrato (não ilustrado) e dopadas com um tipo específico de portador de carga, de tal modo que as aletas 520 são condutoras. O substrato pode ser um substrato semicondutor, um substrato de silício sobre isolador (SOI), uma camada de óxido enterrado (BOX), ou semelhante. Um substrato SOI pode estar completamente esgotado. As aletas 520 podem ser dopadas com um dopante do tipo n ou um dopante do tipo p dependendo do tipo de portador de carga desejado no dispositivo final.

[0063] A primeira estrutura de contato convencional 510 para as aletas 520 é fabricada utilizando crescimento epitaxial completamente fundido ou outro processo similar. Uma área de contato (CA) da primeira estrutura de contato convencional 510 proporcionada pelo crescimento epitaxial totalmente fundido pode ser determinada como se segue:

$$CA = CD * [(NF-1) * FP + FP / \cos(55^\circ)], \quad (1)$$

em que CD é a dimensão crítica, NF é o número de aletas e FP é o espaçamento entre as aletas para permitir o cálculo da área de superfície de contato para a primeira estrutura de contato 510 convencional.

[0064] A FIGURA 5B ilustra uma vista em corte transversal de uma estrutura baseada em aletas 550 que

inclui uma segunda estrutura de contato 560 convencional para as aletas 570. A estrutura baseada em aletas 550 também pode ser utilizada dentro de um circuito integrado. As aletas 570 podem ser suportadas por um substrato (não ilustrado) e dopadas com um tipo específico de portador de carga, de tal modo que as aletas 570 são condutoras. As aletas 570 também podem ser dopadas com um dopante do tipo n ou um dopante do tipo p, dependendo do tipo de portador de carga especificado para o dispositivo final.

[0065] A segunda estrutura de contato 560 convencional é fabricada utilizando um crescimento epitaxial parcialmente em contato ou outro processo similar. Nesta disposição, a segunda estrutura de contato 560 convencional é fabricada em um ângulo de setenta graus ( $70^\circ$ ). Uma área de contato (CA) da segunda estrutura de contato 560 convencional proporcionada pelo crescimento epitaxial parcialmente em contato pode ser determinada como segue:

$$CA = CD * FP / \cos(55^\circ) * NF, \quad (2)$$

em que CD é a dimensão crítica, NF é o número de aletas, e FP é o espaçamento entre as aletas para permitir o cálculo da área de superfície de contato para a segunda estrutura de contato 560 convencional.

[0066] A FIGURA 6 ilustra uma vista em corte transversal de uma estrutura baseada em aletas 600 que inclui um contato envolvente 610 de acordo com um aspecto da presente invenção. A estrutura baseada em aletas 600 também pode ser utilizada dentro de um circuito integrado. As aletas 620 podem ser suportadas por um substrato (não ilustrado) e dopadas com um tipo específico de portador de carga, de modo que as aletas 620 são condutoras. As aletas 620 podem ser dopadas com um dopante tipo n ou um dopante

tipo p dependendo do tipo de portador de carga desejado no dispositivo final.

[0067] O contato envolvente 610 é fabricado utilizando, por exemplo, um contato metal-isolador-semicondutor (MIS) ou um contato direto, em vez de depender de crescimento ou outro processo semelhante. Uma área de contato do contato envolvente 610 proporcionado pelo contato MIS ou pelo contato direto pode ser determinada da seguinte forma:

$$CA = CD * (2 * FH + FW / \cos(55^\circ)) * NF, \quad (3)$$

em que CD é a dimensão crítica, NF é o número de aletas, FH é a altura da aleta, FW é a largura da aleta e FP é espaçamento entre as aletas para permitir o cálculo da área da superfície de contato para o contato envolvente 610.

[0068] Por exemplo, em tecnologia lógica de sete (7) nanômetros, CD = 14 nanômetros, FP = 24 nanômetros, FH = 35 nanômetros, FW = 6 nanômetros e NF = 3. Com base nestes valores, a área de superfície de contato para a primeira estrutura de contato convencional 510 pode ser calculada de acordo com a equação (1), de modo que  $CD = 14 * [(3-1) * 24 + 24 / 0,57] = 14 * 90 \Rightarrow x1,00$ . Com base nestes valores, a área de superfície de contato para a segunda estrutura de contato 560 convencional pode ser calculada de acordo com a equação (2), de modo que  $CD = 14 * 24 / 0,57 * 3 = 14 * 126 \Rightarrow x1,40$ . Utilizando estes mesmos valores, a área de superfície de contato para o contato envolvente 610 pode ser calculada de acordo com a equação (3), de modo que  $CD = 14 * (2 * 35 + 6 / 0,57) * 3 = 14 * 241 \Rightarrow x2,68$ . Assumindo FH = 60 nanômetros, a área de superfície de contato para o contato envolvente 610 é x4,35 superior à área de superfície de contato para a primeira estrutura de contato convencional 510, e x3,11 superior à área de superfície de contato para a segunda estrutura de contato

convencional 560, o que pode reduzir a resistência de contato em cerca de cinquenta por cento (50%).

[0069] As FIGURAS 7A e 7B ilustram vistas em corte transversal de dispositivos semicondutores de óxido metálico complementares (CMOS) incluindo um contato MIS 730 ou um contato direto 780 de acordo com um aspecto da presente invenção. Na FIGURA 7A, um dispositivo CMOS tipo n (dispositivo NMOS 700) inclui uma região do semicondutor de óxido metálico tipo n (NMOS) 740 que circunda uma aleta 720. As regiões tipo n 740 podem ser compostas de silício dopado com fósforo (Si-P) para proporcionar as regiões tipo n 740. Uma porta 710 é formada sobre a aleta 720. A porta 710 inclui uma camada de elevador valor de K 716, uma camada de função de trabalho tipo n 714 e uma camada condutora 712 (por exemplo, tungstênio (W) ou cobalto (Co)). Um contato auto alinhado 702 está disposto sobre a porta 710 e um espaçador de porta 704 está disposto sobre paredes laterais da porta 710.

[0070] Um aspecto da presente invenção prevê um contato não siliceto com as regiões fonte / dreno do dispositivo NMOS 700. Nesta disposição, um contato do metal-isolador-semiconductor (MIS) 730 pode ser depositado nas regiões fonte / dreno (por exemplo, as regiões tipo n 740) do dispositivo NMOS 700. O contato MIS 730 pode incluir uma primeira camada 736 (por exemplo, uma camada de óxido de titânio ( $TiO_2$ )) sobre as regiões tipo n 740. O contato MIS 730 pode incluir uma segunda camada 734 (por exemplo, titânio (Ti)) sobre a primeira camada 736 e nas paredes laterais de um material condutor 732.

[0071] Para as regiões tipo n 740 (por exemplo, fonte / dreno) do dispositivo NMOS 700, a deposição química de vapor (CVD) ou deposição física de vapor (PVD) da segunda camada 734 (por exemplo, uma camada de titânio (Ti)

reagirá com a primeira camada 736 (por exemplo, óxido de titânio ( $TiO_2$ )) para formar  $Ti / TiO_{2-x}$  de baixa resistividade do contato MIS 730 em material de silício dopado com fósforo das regiões tipo n 740. Alternativamente, um contato direto (por exemplo, titânio ( $Ti$ )) sobre material de silício dopado com fósforo das regiões tipo n 740 é também uma opção. Uma resistividade de contato proporcionada pelo contato MIS 730 (ou pelo contato direto) está no intervalo de  $7E-9$  ohms por centímetro cúbico ( $Ohm \cdot cm^2$ ) quando depositada sobre o material de silício dopado com fósforo das regiões tipo n 740.

[0072] Na FIG. 7B, um dispositivo CMOS tipo p (dispositivo PMOS 750) inclui uma região do semicondutor de óxido metálico tipo p (PMOS) 790 que circunda uma aleta 720. As regiões tipo p 790 podem ser compostas de silício e germânio dopado com boro (SiGe-B) para proporcionar as regiões tipo p 790. Uma porta 760 é formada sobre a aleta 770. A porta 760 inclui uma camada de elevado valor de K 766, uma camada de função de trabalho tipo p 764 e uma camada condutora 762 (por exemplo, tungstênio (W)). Um contato auto alinhado 752 está disposto sobre a porta 760 e um espaçador de porta 754 está disposto nas paredes laterais da porta 760.

[0073] Um aspecto da presente invenção prevê um contato não gemimídeo com as regiões fonte / dreno do dispositivo PMOS 750. Nesta disposição, um contato direto 780 pode ser depositado sobre as regiões fonte / dreno (por exemplo, as regiões tipo p 790) do dispositivo PMOS 750. O contato direto 780 pode incluir uma primeira camada 784 (por exemplo, titânio ( $Ti$ )) sobre as regiões tipo p 790 e nas paredes laterais de um material condutor 782. Uma resistividade de contato proporcionada pelo contato direto 780 está no intervalo de  $2E-8$  ohms por centímetro cúbico

( $\text{Ohm}\cdot\text{cm}^2$ ) quando depositada sobre material de germânio dopado com boro das regiões tipo p 790.

[0074] A FIGURA 8 ilustra uma vista em corte transversal de um dispositivo baseado em aletas 800 que inclui uma estrutura envolvente de contato de acordo com um aspecto da presente invenção. Representativamente, o dispositivo baseado em aletas 800 inclui uma região de isolamento de trincheira rasa (STI) 809 que envolve uma parte de aleta de base 820. A parte de aleta de base 820 pode ser silício, germânio, silício e germânio, fosfato de índio ou outro material semicondutor semelhante. É formada uma parte de aleta regenerada 870 sobre a parte de aleta de base 820 usando, por exemplo, crescimento epitaxial com uma formação de faceta de índice Miller controlada (111) sem fundir as aletas. A parte de aleta regenerada 870 funciona como uma fonte / dreno do dispositivo baseado em aletas 800. Para um dispositivo baseado em aletas 800 que é de um tipo n (por exemplo, um NFET), a parte de aleta regenerada 870 é composta de silício dopado com fósforo (SiP), silício dopado com fósforo de carbono (SiCP), silício e germânio dopado com fósforo (SiGeP), germânio dopado com fósforo (GeP) ou outro material três / cinco (III / V) semelhante. Para um dispositivo baseado em aletas 800 que é de um tipo p (por exemplo, um PFET), a parte de aleta regenerada 870 é composta de silício e germânio dopado com boro (SiGeB), germânio dopado com boro (GeB) ou outro material dopado semelhante.

[0075] Nesta configuração, um contato MIS 830 ou um contato direto 880 circunda a parte de aleta regenerada 870 (fonte / dreno) do dispositivo baseado em aletas 800. Um material de enchimento de contato 832 (por exemplo, tungstênio (W) ou cobalto (Co)) é disposto sobre o material do contato de MIS 830 ou o contato direto 880 que circunda

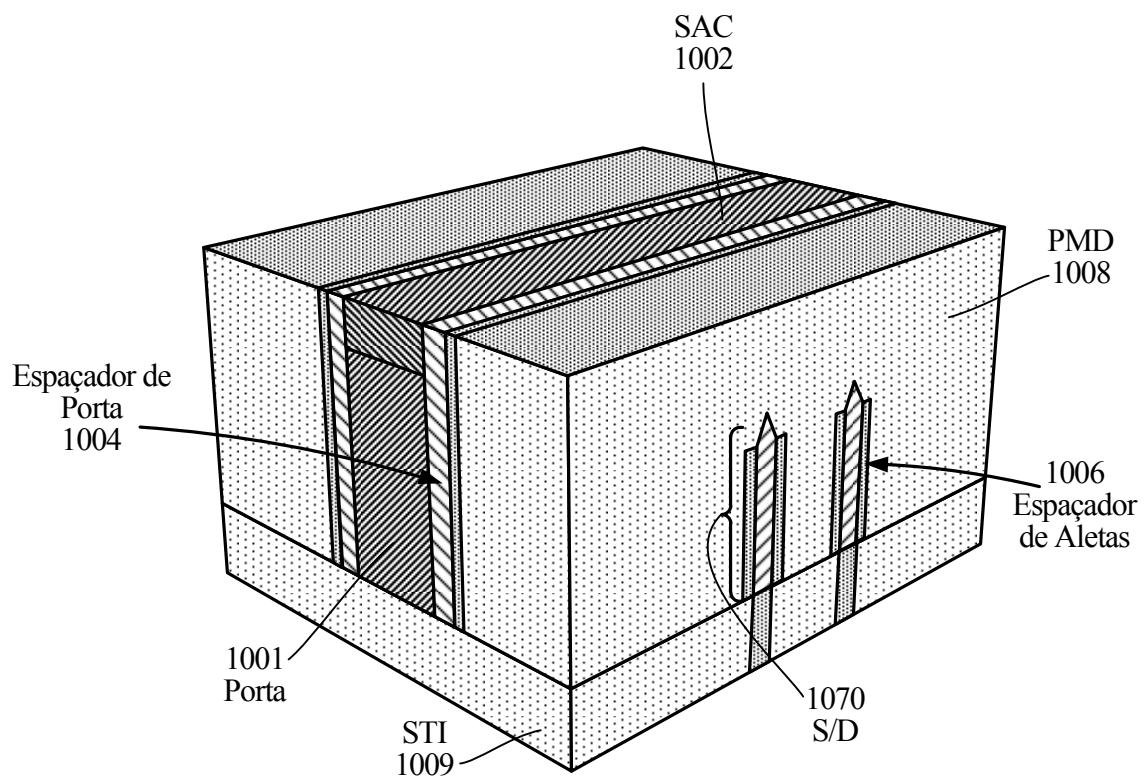

a parte de aleta regenerada 870. Além disso, um óxido (por exemplo, um dielétrico pré-metálico (PMD) 808) está nas paredes laterais do material do contato MIS 830 ou do contato direto 880 e um espaçador de aletas 806. O dispositivo baseado em aletas 800 inclui também uma porta 810 incluindo um contato auto alinhado (SAC) 802 (por exemplo, SAC baseado em nitreto) sobre a porta 810 e um espaçador de porta 804 (por exemplo, um espaçador de porta de baixo valor de K à base de nitreto) nas paredes laterais da porta 810. O SAC 802 também pode fornecer um batente de gravação para fabricação da porta 810. O dispositivo baseado em aletas 800 pode ser formado como mostrado nas FIGURAS 9A-9L. O dispositivo baseado em nanofios de porta circundante (GAA) 1000 pode ser formado como mostrado nas FIGURAS 10A-10L, que correspondem às FIGURAS 9A-9L. Descreve-se com referência às FIGURAS 11A e 11B, um processo para a formação do dispositivo baseado em aletas 800, tal como mostrado nas FIGURAS 9A-9L ou o dispositivo baseado em nanofios GAA 1000, como mostrado nas FIGURAS 10A-10L, que correspondem às FIGURAS 9A-9L.

[0076] A FIGURA 11A ilustra um método 1100 para fabricar um dispositivo semicondutor incluindo uma estrutura envolvente de contato de acordo com aspectos da presente invenção. O processo descrito nas FIGURAS 11A e 11B permite a formação do dispositivo baseado em aletas 900, como mostrado nas FIGURAS 9A-9L ou o dispositivo baseado em nanofios GAA 1000, como mostrado nas FIGURAS 10A-10L, que correspondem às FIGURAS 9A-9L. No bloco 1102, uma pastilha de entrada é mostrada depois que um processo de padronização de porta poli falsa é concluído para formar uma porta poli falsa (por exemplo, silício (Si)). Por exemplo, tal como ilustrado nas FIGURAS 9A / 10A, uma máscara dura 901/1001 (por exemplo, óxido) está disposta

sobre uma porta 910/1010 durante a padronização da porta 910/1010. A porta 910/1010 é suportada por uma região de isolamento de trincheira rasa (STI) 909/1009, a qual pode ser suportada por um substrato. As regiões fonte / dreno da porta 910/1010 serão proporcionadas por fontes / drenos regenerados 970/1070, como mostrado nas FIGURAS 9E / 10E. Além disso, a porta poli falsa também é substituída para proporcionar a porta 910/1010, como mostrado nas FIGURAS 9L / 10L.

[0077] Fazendo novamente referência à FIGURA 11A, no bloco 1104, um espaçador de portas (por exemplo, um espaçador de portas com baixo valor de K baseado em nitreto) é formado nas paredes laterais da porta falsa e da máscara rígida. Por exemplo, como mostrado nas FIGURAS 9B / 10B, um espaçador de portas 904/1004 é formado nas paredes laterais da porta 910/1010 e a máscara rígida 901/1001. No bloco 1106, é formado um espaçador de fonte / dreno (S / D). Por exemplo, como mostrado nas FIGURAS 9C / 10C, um espaçador de fonte / dreno 906/1006 é formado nas paredes laterais da porta 910/1010 e a máscara rígida 901/1001. Conforme ilustrado na FIG. 9A, o espaçador de aletas 906 é formado nas paredes laterais das aletas 920. Conforme ilustrado na FIGURA 10A, um espaçador de nanofios de porta circundante (GAA) 1006 é formado nas paredes laterais do nanofio GAA 1020.

[0078] Fazendo novamente referência à FIGURA 11A, no bloco 1108, é realizada uma gravação por recesso das regiões fonte / dreno. As regiões fonte / dreno são rebaixadas através do espaçador S / D e no espaçador de portas para formar partes de fonte / dreno regeneradas. Conforme ilustrado na FIG. 9D, as aletas 920 são gravadas por recesso através do espaçador de aletas 906 e o espaçador de portas 904. Conforme ilustrado na FIG. 10D, o

nanofio GAA 1020 é gravado por recesso através do espaçador GAA 1006 e do espaçador de portas 1004. Um implante de drenagem ligeiramente dopado (LDD) não é mais fornecido a partir das regiões fonte / dreno regeneradas (S / D), como mostrado nas FIGURAS 9E / 10E.

[0079] Fazendo novamente referência à FIGURA 11A, no bloco 1110, o crescimento epitaxial é utilizado para formar partes S / D regeneradas. As partes S / D regeneradas podem ser formadas com uma formação de faceta controlada (por exemplo, Índice de Miller <111>) sem fundir as partes S / D regeneradas. Por exemplo, o crescimento epitaxial de silício dopado com fósforo (SiP), silício dopado com fósforo de carbono (SiCP) ou germânio dopado com fósforo (GeP) pode formar regiões S / D regeneradas de um tipo n (por exemplo, NFET). De forma semelhante, o crescimento epitaxial de silício e germânio dopado com boro (SiGeB), ou germânio dopado com boro (GeB) pode formar regiões S / D regeneradas de um tipo p (por exemplo, um PFET). Conforme ilustrado nas FIGURAS 9E / 10E, as regiões S / D regeneradas 970/1070 são formadas utilizando o crescimento epitaxial observado. Nesta disposição, as regiões S / D regeneradas 970/1070 têm paredes laterais substancialmente paralelas. Conforme ilustrado na FIGURA 10E, o dispositivo baseado em nanofios GAA 1000 inclui regiões S / D de tipo n e tipo p 1070. No bloco 1112, um material dielétrico de pré-metal (PMD) é depositado. Conforme ilustrado nas FIGURAS 9F / 10F, o PMD 908/1008 é depositado sobre o dispositivo baseado em aletas 900 ou o dispositivo baseado em nanofios GAA 1000.

[0080] A FIGURA 11B ilustra ainda o método 1100 da FIGURA 11A para fabricar um dispositivo semicondutor incluindo uma estrutura envolvente de contato de acordo com aspectos da presente invenção. No bloco 1120, é realizado

um processo de polimento químico-mecânico (CMP) no material PMD para parar e expor a porta falsa. Conforme ilustrado nas FIGURAS 9G / 10G, o processo CMP é realizado no PMD 908/1008 para expor a porta 910/1010. No bloco 1122, é realizado um processo de porta de substituição para substituir a porta falsa por uma porta ativa. Conforme ilustrado nas FIGURAS 9H / 10H, a porta falsa é removida para formar a porta 910/1010 e expondo a porta 910/1010 utilizando um processo CMP que para no PMD 908/1008.

[0081] Conforme ilustrado na FIGURA 10H, uma camada de elevado valor de K 1016 é depositada sobre a parte exposta do nanofio GAA 1020. Um primeiro material de função de trabalho (WFM) (por exemplo, um WFM tipo n) é depositado sobre uma primeira parte exposta do nanofio GAA 1020 para formar um NFET. Além disso, um segundo material de função de trabalho (WFM) (por exemplo, um WFM tipo p) é depositado sobre uma segunda parte exposta do nanofio GAA 1020 para formar um PFET. Uma camada condutora 1012 (por exemplo, tungstênio (W) ou cobalto (Co)) é depositada sobre o primeiro WFM e o segundo WFM para completar a formação da porta 1010. Finalmente, um processo CMP é executado para parar no PMD 1008.

[0082] Com referência novamente à FIGURA 11B, no bloco 1124, a porta é gravada por recesso seguida por deposição de um contato auto alinhado (SAC) que funciona como uma camada de batente de gravação durante um processo CMP subsequente para completar a formação da porta. Conforme ilustrado nas FIGURAS 91/101, uma camada condutora é gravada e o SAC 902/1002 é depositado. Um processo CMP pode ser realizado no SAC 902/1002. Após conclusão da porta 910/1010, formou-se um contato envolvente para rodear as regiões S / D regeneradas 970/1070.

[0083] No bloco 1126, é realizada uma gravação de SAC para remover tanto o óxido de PMD como o espaçador na cavidade de contato. A gravação de SAC pode ser uma gravura baixa / sem danos para evitar danos nas regiões S / D regeneradas. Uma gravação de camada atômica (ALE) pode expor as regiões S / D regeneradas. Conforme ilustrado nas FIGURAS 9J / 10J, é realizada uma gravação do PMD 908/1008 e do espaçador do espaçador de aletas 906 / GAA 1006 para expor as regiões SD regeneradas 970/1070 e parar no STI 909/1009 e o espaçador de portas 904 / 1004. No bloco 1128, uma deposição forma um contato metal-óxido-semicondutor (MIS) ou um contato direto que circunda as regiões S / D regeneradas. Conforme ilustrado nas FIGURAS 9K / 10K, um contato MIS 930/1030 ou um contato direto 980/1080 é formado para rodear as regiões S / D regeneradas 970/1070. No bloco 1130, um material de enchimento de contato (por exemplo, 932/1032) é depositado sobre o contato MIS ou um contato direto em torno das regiões S / D regeneradas. Conforme ilustrado nas FIGURAS 9L / 10L, é formado um contato MIS 930/1030 ou um contato direto 980/1080 para rodear as regiões S / D regeneradas 970/1070 para completar a formação do dispositivo baseado em aletas 900 ou o dispositivo baseado em nanofios GAA 1000.

[0084] Aspectos da presente invenção incluem um fluxo de integração inovador para formar contatos envolventes em aletas altamente dimensionadas com contatos metal-isolador-semicondutor (MIS) ou contatos diretos para reduzir drasticamente a resistência de contato. Aspectos adicionais da presente invenção podem também proporcionar um contato MIS ou um contato direto com a fonte / dreno de dispositivos à base de nanofios de porta circundante (GAA) e outros dispositivos semicondutores semelhantes para reduzir a resistência de contato. Uma estrutura envolvente

de contato, incluindo contatos envolventes, pode permitir o funcionamento dentro das geometrias reduzidas do dispositivo de tecnologias de lógica avançada, tal como tecnologia de lógica de sete (7) nanômetros e além. Uma estrutura envolvente de contato pode ser fabricada usando materiais e capacidades de processo existentes, ao mesmo tempo proporcionando uma substancial redução da resistência de contato.

[0085] De acordo com um aspecto da presente invenção, é descrita uma estrutura baseada em aletas que inclui uma pilha de portas. Em uma configuração, a estrutura baseada em aletas inclui meios para contatar substancialmente com toda a área de superfície de uma região fonte / dreno regenerada da estrutura baseada em aletas próxima à pilha de portas. Os meios de contato podem ser o contato envolvente 610, o contato MIS 830 ou o contato direto 880. Em outro aspecto, os meios acima mencionados podem ser qualquer módulo ou qualquer aparelho ou material configurado para executar as funções enumeradas pelos meios acima mencionados.

[0086] A FIG. 12 é um diagrama em blocos que ilustra um sistema de comunicação sem fios 1200 exemplificativo, no qual um aspecto da invenção pode ser utilizado vantajosamente. Para fins de ilustração, a FIG. 12 mostra três unidades remotas 1220, 1230 e 1250 e duas estações base 1240. Será reconhecido que os sistemas de comunicação sem fios podem ter muitas mais unidades remotas e estações base. As unidades remotas 1220, 1230 e 1250 incluem dispositivos IC 1225A, 1225C e 1225B que incluem os contatos descritos. Será reconhecido que outros dispositivos podem também incluir os contatos descritos, tais como as estações base, dispositivos de comutação e equipamento de rede. A FIGURA 12 mostra os sinais de

ligação direta 1280 da estação base 1240 às unidades remotas 1220, 1230 e 1250 e sinais de ligação inversa 1290 das unidades remotas 1220, 1230 e 1250 às estações base 1240.

[0087] Na FIGURA 12, a unidade remota 1220 é mostrada como um telefone móvel, a unidade remota 1230 é mostrada como um computador portátil e a unidade remota 1250 é mostrada como uma unidade remota de localização fixa em um sistema de circuito local sem fios. Por exemplo, as unidades remotas podem ser um telefone móvel, uma unidade portátil de sistemas de comunicação pessoal (PCS), uma unidade de dados portátil tal como um assistente de dados pessoais, um dispositivo GPS ativado, um dispositivo de navegação, um decodificador, um leitor de música, um leitor de vídeo, uma unidade de entretenimento, uma unidade de dados de localização fixa tal como um equipamento de leitura de medidores ou outros dispositivos que armazenam ou recuperam dados ou instruções de computador ou suas combinações. Embora a FIG. 12 ilustre unidades remotas de acordo com os aspectos da invenção, a descrição não se limita a estas unidades ilustradas exemplificativas. Aspectos da invenção podem ser adequadamente utilizados em muitos dispositivos, que incluem os dispositivos semicondutores descritos.

[0088] A FIGURA 13 é um diagrama em blocos que ilustra uma concepção de estação de trabalho utilizada para concepção de circuito, disposição e lógica de uma estrutura baseada em aletas, tais como os contatos descritos acima. Uma concepção de estação de trabalho 1300 inclui um disco rígido 1301 contendo software de sistema operacional, arquivos de suporte e software de design como Cadence ou OrCAD. A concepção de estação de trabalho 1300 também inclui um mostrador 1302 para facilitar a concepção de um

circuito 1310 ou uma estrutura baseada em aletas 1312, tal como um contato. Um meio de armazenamento 1304 é proporcionado para armazenar de forma tangível a concepção do circuito 1310 ou a estrutura baseada em aletas 1312. A concepção do circuito 1310 ou a estrutura baseada em aletas 1312 pode ser armazenada no meio de armazenamento 1304 em um formato de arquivo tal como GDSII ou GERBER. O meio de armazenamento 1304 pode ser um CD-ROM, DVD, disco rígido, memória flash ou outro dispositivo apropriado. Além disso, a concepção de estação de trabalho 1300 inclui um aparelho de acionamento 1303 para aceitar a entrada de ou registrar a saída para o meio de armazenamento 1304.

[0089] Os dados registrados no meio de armazenamento 1304 podem especificar configurações de circuitos lógicos, dados de padrão para máscaras de fotolitografia ou dados de padrão de máscara para ferramentas de gravação em série, tais como litografia por feixe de elétrons. Os dados podem ainda incluir dados de verificação lógica tais como diagramas de tempo ou circuitos de rede associados a simulações lógicas. O fornecimento de dados no meio de armazenamento 1304 facilita a concepção do circuito 1310 ou a estrutura baseada em aletas 1312 por diminuição do número de processos para a concepção de pastilhas de semicondutores.

[0090] Para uma implementação de firmware e / ou software, as metodologias podem ser implementadas com módulos (por exemplo, procedimentos, funções e assim por diante) que executam as funções aqui descritas. Um meio legível por máquina que incorpora de forma tangível instruções pode ser utilizado na implementação das metodologias aqui descritas. Por exemplo, os códigos de software podem ser armazenados em uma memória e executados por uma unidade de processador. A memória pode ser

implementada dentro da unidade de processador ou externa à unidade de processador. Tal como aqui utilizado, o termo “memória” se refere a tipos de memória de longo prazo, de curto prazo, volátil, não volátil ou outra memória e não se limita a um tipo particular de memória ou número de memórias ou tipo de suporte no qual a memória seja armazenada.

[0091] Se implementadas em firmware e / ou software, as funções podem ser armazenadas como uma ou mais instruções ou código em um meio legível por computador. Exemplos incluem meios legíveis por computador codificados com uma estrutura de dados e meios legível por computador codificados com um programa de computador. Os meios legíveis por computador incluem meios de armazenamento de computador. Um meio de armazenamento pode ser um meio disponível que possa ser acessado por um computador. A título de exemplo, e não de limitação, tais meios legível por computador podem incluir RAM, ROM, EEPROM, CD-ROM ou outro armazenamento em disco óptico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnéticos, ou outro meio que possa ser usado para armazenar código de programa desejado na forma de instruções ou estruturas de dados e que possa ser acessado por um computador; disco (disk) e disco (disc) (CD), disco laser, disco óptico, disco versátil digital (DVD), disquete e disco Blu-ray, em que os discos (disks) normalmente reproduzem dados magneticamente, ao passo que os discos (discs) reproduzem dados opticamente com lasers. Combinações dos anteriores também devem ser incluídas no âmbito de meios legíveis por computador.

[0092] Além do armazenamento em meio legível por computador, instruções e / ou dados podem ser proporcionados como sinais em meios de transmissão

incluídos em um aparelho de comunicação. Por exemplo, um aparelho de comunicação pode incluir um transceptor tendo sinais indicativos de instruções e dados. As instruções e os dados são configurados para levar um ou mais processadores a implementar as funções descritas nas reivindicações.

[0093] Embora a presente descrição e as suas vantagens tenham sido descritas em detalhes, deve ser entendido que várias trocas, substituições e alterações podem ser feitas aqui sem afastamento da tecnologia da descrição como definida pelas reivindicações anexas. Por exemplo, termos relacionais, tais como "acima" e "abaixo" são usados com respeito a um substrato ou dispositivo eletrônico. Evidentemente, se o substrato ou o dispositivo eletrônico for invertido, acima se torna abaixo, e vice-versa. Adicionalmente, se orientados lateralmente, acima e abaixo podem referir-se a lados de um substrato ou dispositivo eletrônico. Além disso, o âmbito do presente pedido de patente não se destina a limitar-se às configurações particulares do processo, máquina, fabricação, composição da matéria, meios, métodos e etapas descritas no relatório descritivo. Como um especialista na técnica irá facilmente apreciar a partir da invenção, processos, máquinas, fabricação, composições de matéria, meios, métodos ou etapas, atualmente existentes ou que venham a ser desenvolvidos posteriormente, que executem substancialmente a mesma função ou alcancem substancialmente o mesmo resultado como as configurações correspondentes aqui descritas, podem ser utilizadas de acordo com a presente invenção. Consequentemente, as reivindicações anexas pretendem incluir dentro do seu âmbito tais processos, máquinas, fabricação, composições de matéria, meios, métodos ou etapas.

[0094] Os especialistas compreenderão ainda que os vários blocos lógicos, módulos, circuitos e etapas de algoritmo ilustrativos descritos em ligação com a descrição aqui apresentada podem ser implementados como hardware eletrônico, software de computador ou combinações de ambos. Para ilustrar claramente esta permutabilidade de hardware e software, vários componentes, blocos, módulos, circuitos e etapas ilustrativos foram descritos acima geralmente em termos de sua funcionalidade. Se tal funcionalidade é implementada como hardware ou software depende da aplicação particular e restrições de design impostas ao sistema geral. Os artesões experientes podem implementar a funcionalidade descrita de modos variados para cada aplicação particular, mas tais decisões de implementação não devem ser interpretadas como provocando um afastamento do âmbito da presente invenção.

[0095] Os vários blocos lógicos, módulos e circuitos ilustrativos descritos em ligação com a descrição aqui apresentada podem ser implementados ou executados com um processador de propósito geral, um processador de sinal digital (DSP), um circuito integrado de aplicação específico (ASIC), um arranjo de portas programável em campo (FPGA) ou outro dispositivo lógico programável, porta discreta ou lógica de transistor, componentes de hardware discretos, ou qualquer combinação destes concebida para executar as funções aqui descritas. Um processador de finalidade geral pode ser um microprocessador, mas, em alternativa, o processador pode ser qualquer processador, controlador, microcontrolador ou máquina de estados convencional. Um processador pode também ser implementado como uma combinação de dispositivos de computação (por exemplo, uma combinação de um DSP e um microprocessador, microprocessadores múltiplos, um ou mais microprocessadores

em conjunto com um núcleo DSP, ou qualquer outra configuração semelhante).

[0096] As etapas de um método ou algoritmo descritas em ligação com a invenção podem ser incorporadas diretamente em hardware, em um módulo de software executado por um processador, ou em uma combinação dos dois. Um módulo de software pode residir em RAM, memória flash, ROM, EPROM, EEPROM, registradores, disco rígido, um disco removível, um CD-ROM ou em qualquer outra forma de meio de armazenamento conhecida na arte. Um meio de armazenamento exemplificativo é acoplado ao processador de tal modo que o processador pode ler informações de, e escrever informações para o meio de armazenamento. Em alternativa, o meio de armazenamento pode ser integrante ao processador. O processador e o meio de armazenamento podem residir em um ASIC. O ASIC pode residir em um terminal de usuário. Em alternativa, o processador e o meio de armazenamento podem residir como componentes discretos em um terminal de usuário.

[0097] Em um ou mais modelos exemplificativos, as funções descritas podem ser implementadas em hardware, software, firmware ou qualquer combinação destes. Se implementadas em software, as funções podem ser armazenadas ou transmitidas como uma ou mais instruções ou código em um meio legível por computador. Os meios legíveis por computador incluem meios de armazenamento de computador e meios de comunicação, incluindo qualquer meio que facilite a transferência de um programa de computador de um local para outro. Um meio de armazenamento pode ser qualquer meio disponível que possa ser acessado por um computador de propósito geral ou propósito especial. A título de exemplo, e não de limitação, tais meios legível por computador podem incluir RAM, ROM, EEPROM, CD-ROM ou outro armazenamento em

disco óptico, armazenamento em disco magnético ou outros dispositivos de armazenamento magnéticos ou qualquer outro meio que possa ser utilizado para transportar ou armazenar meios de código de programa específicos sob a forma de instruções ou estruturas de dados e que possam ser acessados por um computador de propósito geral ou propósito especial ou por um processador de propósito geral ou propósito especial. Além disso, qualquer conexão é adequadamente chamada de um meio legível por computador. Por exemplo, se o software for transmitido de um site, servidor ou outra fonte remota usando um cabo coaxial, cabo de fibra óptica, par trançado, linha de assinante digital (DSL) ou tecnologias sem fio como infravermelho, rádio e micro-ondas, então o cabo coaxial, cabo de fibra óptica, par trançado, DSL, ou tecnologias sem fio como infravermelho, rádio e micro-ondas estão incluídos na definição de meio. Disco (disk) e disco (disc), tal como aqui utilizados, incluem disco compacto (CD), disco laser, disco óptico, disco versátil digital (DVD), disquete e disco Blu-ray, em que os discos (disks) reproduzem dados magneticamente, ao passo que os discos (discs) reproduzem dados opticamente com lasers. Combinações dos anteriores também devem ser incluídas no âmbito de meios legível por computador.

[0098] A descrição anterior é proporcionada para permitir que qualquer perito na arte pratique os vários aspectos aqui descritos. Várias modificações a estes aspectos serão facilmente evidentes para os especialistas na técnica, e os princípios genéricos aqui definidos podem ser aplicados a outros aspectos. Assim, as reivindicações não se destinam a ser limitadas aos aspectos aqui mostrados, mas deve ser concedido o âmbito abrangente consistente com a linguagem das reivindicações, em que a

referência a um elemento no singular não pretende significar "um e apenas um", a menos que especificamente assim afirmado, mas sim "um ou mais". Salvo indicação específica em contrário, o termo "algum" se refere a um ou mais. Uma frase que se refere a "pelo menos um de" uma lista de itens se refere a qualquer combinação desses itens, incluindo elementos individuais. Como exemplo, "pelo menos um de: a, b ou c" se destina a abranger: a; b; c; a e b; a e c; b e c; e a, b e c. Todos os equivalentes estruturais e funcionais aos elementos dos vários aspectos descritos ao longo desta descrição que são conhecidos ou que mais tarde venham a ser conhecidos para os peritos na arte são aqui expressamente incorporados por referência e pretendem ser abrangidos pelas reivindicações. Além disso, nada aqui divulgado pretende ser dedicado ao público, independentemente de tal divulgação ser explicitamente mencionada nas reivindicações. Nenhum elemento de reivindicação deve ser interpretado de acordo com as disposições do instrumento 35 U.S.C. § 112, sexto parágrafo, a menos que o elemento seja expressamente enumerado usando a expressão "meios para" ou, no caso de uma reivindicação de método, o elemento seja enumerado usando a expressão "uma etapa para".

## REIVINDICAÇÕES

1. Dispositivo transistor de efeito de campo de aletas, FinFET, **caracterizado por** compreender:

uma pilha de portas (710, 760, 810, 910) disposta sobre uma região de isolamento por trincheira rasa, STI (809, 909) do dispositivo FinFET;

um espaçador de porta (704, 804, 904, 1004) sobre paredes laterais da pilha de portas;

um segundo espaçador (806, 906, 1006) sobre partes de paredes laterais do espaçador de porta;

uma pluralidade de porções dielétricas de pré-metal, PMD (808, 908, 1008) sobre paredes laterais do segundo espaçador e acima da região de STI;

uma pluralidade de aletas (720, 770, 820, 870, 920, 970, 1070) do dispositivo FinFET, em que cada aleta compreende uma parte de aleta de base (820, 920) e uma região fonte/dreno (870, 970, 1070),

em que cada parte de aleta de base é envolvida na região de isolamento por trincheira rasa, STI, (809, 909),

em que cada região fonte/dreno é formada sobre cada parte de aleta de base e acima da região STI, espaçadas entre si e da pluralidade de porções PMD, e é próxima à pilha de portas e em que cada região fonte/dreno possui paredes laterais paralelas e compreende um material dopado; e

um contato de não siliceto envolvente (730, 780, 830, 880, 930, 980, 1030, 1080),

em que o contato envolvente é disposto para envolver a região fonte/dreno de cada aleta, para assim contatar as paredes laterais paralelas da região fonte/dreno de cada aleta, e disposta para contatar porções das paredes laterais do espaçador de porta, o segundo

espaçador, a pluralidade de porções PMD e a região de STI, e

em que o contato envolvente compreende um contato de metal-isolador-semicondutor, MIS, ou um contato direto.

2. Dispositivo FinFET, de acordo com a reivindicação 1, **caracterizado pelo** fato de que compreende adicionalmente um material de preenchimento de contato (832, 932, 1032) depositado sobre o contato envolvente, o contato envolvente separando as porções das paredes laterais do espaçador de porta, do segundo espaçador, da pluralidade de porções PMD e da região STI a partir do material de preenchimento de contato.

3. Dispositivo FinFET, de acordo com a reivindicação 1, **caracterizado pelo** fato de que a pilha de portas está sobre uma superfície da parte de aleta de base de cada aleta.

4. Dispositivo FinFET, de acordo com a reivindicação 1, **caracterizado pelo** fato de que a parte de aleta de base de cada aleta compreende silício, germânio, silício e germânio ou fosfato de índio.

5. Dispositivo FinFET, de acordo com a reivindicação 1, **caracterizado pelo** fato de que o contato MIS é acoplado a uma região de semicondutor de óxido metálico tipo n, NMOS, do dispositivo FinFET ou o contato direto é acoplado a uma região de semicondutor de óxido metálico tipo p, PMOS, do dispositivo FinFET.

6. Dispositivo FinFET, de acordo com a reivindicação 4, **caracterizado pelo** fato de que o contato MIS compreende:

uma camada de óxido de titânio ( $TiO_2$ ) sobre a região NMOS do dispositivo FinFET; e

uma camada de titânio (Ti) sobre a camada de óxido de titânio.

7. Dispositivo FinFET, de acordo com a reivindicação 4, **caracterizado pelo** fato de que o contato direto compreende uma camada de titânio (Ti) sobre a região PMOS do dispositivo FinFET.

8. Dispositivo FinFET, de acordo com a reivindicação 1, **caracterizado pelo** fato de que é integrado em um telefone móvel, um set top box, um leitor de música, um leitor de vídeo, uma unidade de entretenimento, um dispositivo de navegação, um computador, uma unidade portátil de sistemas de comunicação pessoal (PCS), uma unidade de dados portátil e/ou uma unidade de dados de localização fixa.

9. Método para fabricar um dispositivo transistor de efeito de campo de aletas, FinFET conforme definido em qualquer uma das reivindicações 1 a 8, o método **caracterizado pelo** fato de que compreende:

formar (1104) um espaçador de porta sobre paredes laterais de uma porta falsa;

formar (1106) um segundo espaçador sobre paredes laterais do espaçador de porta e uma região fonte/dreno de cada um dentre uma pluralidade de aletas do dispositivo FinFET acima de uma região de isolamento por trincheira rasa, STI, do dispositivo FinFET, cada aleta compreendendo adicionalmente uma porção de aleta de base envolvida na região STI;

gravar por recesso (1108) a região fonte/dreno de cada aleta através do segundo espaçador e do espaçador de porta;

regenerar (1110) a região fonte/dreno de cada aleta, a região fonte/dreno regenerada de cada aleta tendo paredes laterais paralelas e compreendendo um material dopado;

depositar (1112) um dielétrico de pré-metal, PMD (808, 908, 1008) no dispositivo FinFET;

substituir (1122) a porta falsa do dispositivo FinFET por uma pilha de portas, em que a região fonte/dreno de cada aleta está próxima da pilha de portas;

gravar (1126) o PMD e o segundo espaçador para expor a região fonte/dreno regenerada de cada aleta e uma parte da parede lateral do espaçador de porta, a região fonte/dreno regenerada de cada aleta sendo espaçada entre si e de porções de PMD restantes; e

fabricar (1128) um contato de não siliceto envolvente envolvendo a região fonte/dreno regenerada de cada aleta, em que o contato envolvente é disposto para contatar as paredes laterais paralelas da região fonte/dreno regenerada de cada aleta e contatar as porções expostas do espaçador de porta, do segundo espaçador, das porções de PMD restantes e da região STI, e em que o contato envolvente compreende um contato de metal-isolador-semicondutor, MIS, ou um contato direto.

10. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que o PMD que é depositado no dispositivo FinFET contacta o segundo espaçador, a região fonte/dreno de cada aleta e a região STI.

11. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que a gravação do PMD e do segundo espaçador para expor a região fonte/dreno regenerada de cada aleta compreende:

depositar um contato auto alinhado, SAC, que opera como uma camada de interrupção de gravação; e

remover porções do PMD e do segundo espaçador.

12. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que compreende adicionalmente:

depositar (1130) um material de preenchimento de contato sobre o contato envolvente.

13. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que a regeneração da região fonte/dreno de cada aleta compreende crescimento epitaxial de acordo com uma formação de faceta <111> controlada.

14. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que fabricar o contato não siliceto envolvente compreende:

depositar uma camada de óxido de titânio ( $TiO_2$ ) sobre uma região do semicondutor de óxido metálico tipo n, NMOS, do dispositivo FinFET; e

depositar uma camada de titânio (Ti) sobre a camada de óxido de titânio.

15. Método, de acordo com a reivindicação 9, **caracterizado pelo** fato de que fabricar o contato de não siliceto envolvente compreende depositar uma camada de titânio (Ti) diretamente sobre uma região do semicondutor de óxido metálico tipo p, PMOS, do dispositivo FinFET.

***FIG. 1***

***FIG. 2***

***FIG. 3***

**FIG. 4**

**FIG. 6**

**FIG. 7A**

**FIG. 7B**

**FIG. 8**

**FIG. 9A**

**FIG. 9B**

**FIG. 9C**

**FIG. 9D****FIG. 9E****FIG. 9F**

**FIG. 9G****FIG. 9H****FIG. 9I**

**FIG. 10A****FIG. 10B****FIG. 10C**

**FIG. 10G**

**FIG. 10H**

**FIG. 10I**

**FIG. 10J****FIG. 10K****FIG. 10L**

**FIG. 11A**

**FIG. 11B**

**FIG. 12**

**FIG. 13**