## (12) 发明专利

(10) 授权公告号 CN 109906505 B

(45) 授权公告日 2023.06.27

(21) 申请号 201780068363.0

(74) 专利代理机构 北京律盟知识产权代理有限公司

11287

(22) 申请日 2017.11.22

专利代理人 林斯凯

(65) 同一申请的已公布的文献号

申请公布号 CN 109906505 A

(51) Int.CI.

H01L 21/768 (2006.01)

(43) 申请公布日 2019.06.18

H01L 23/34 (2006.01)

(30) 优先权数据

15/361,390 2016.11.26 US

(56) 对比文件

US 2007035011 A1, 2007.02.15

(85) PCT国际申请进入国家阶段日

CN 103013033 A, 2013.04.03

2019.05.06

US 2003209802 A1, 2003.11.13

(86) PCT国际申请的申请数据

US 2006289988 A1, 2006.12.28

PCT/US2017/063131 2017.11.22

US 2007064398 A1, 2007.03.22

(87) PCT国际申请的公布数据

US 2014321026 A1, 2014.10.30

W02018/098360 EN 2018.05.31

US 2016291256 A1, 2016.10.06

(73) 专利权人 德州仪器公司

TW 200632086 A, 2006.09.16

地址 美国德克萨斯州

CN 104861909 A, 2015.08.26

(72) 发明人 阿尔莎娜·韦努戈帕尔

CN 102823005 A, 2012.12.12

本杰明·史塔生·库克

CN 102856465 A, 2013.01.02

路易吉·科隆博

CN 105679725 A, 2016.06.15

罗伯特·里德·多林

CN 1875480 A, 2006.12.06

审查员 孙程程

权利要求书3页 说明书9页 附图17页

(54) 发明名称

是通过加成工艺形成。

互连区上方的集成电路纳米颗粒热路由结

构

(57) 摘要

在所描述实例中,集成电路(100)在顶部互连层(124)上具有热路由结构(132)。所述顶部互连层(124)包含连接到下互连层的互连件(118),且不包含接合垫、探测垫、输入/输出垫或到凸块接合垫的再分布层。所述热路由结构(132)在含有所述顶部互连层(124)的所述集成电路(100)的平面的部分而非全部上方延伸。所述热路由结构(132)包含纳米颗粒层,其中相邻纳米颗粒彼此附接。所述纳米颗粒层不含有机粘合剂材料。所述热路由结构(132)的导热率高于所述顶部互连层(124)中的金属的导热率。所述纳米颗粒层

CN 109906505 B

1. 一种集成电路,其包括:

衬底,其包含半导体材料;

互连区,其在所述衬底上方,所述互连区包含:

电介质层堆叠;

触点,其在所述电介质层堆叠中;

互连件,其在所述电介质层堆叠中,所述互连件中的至少两者在所述互连区中的顶部互连层中,所述顶部互连层接近所述互连区中的与所述衬底与所述互连区之间的边界相对的顶部表面;及

通孔,其在所述电介质层堆叠中;

生热组件,其接近所述衬底与所述互连区之间的所述边界、在所述衬底及所述互连区中;

热路由结构,其在所述顶部互连层上方、并且在所述生热组件上方以及在所述顶部互连层的一部分延伸,所述热路由结构包含在所述互连区的所述顶部表面上方的第一粘结纳米颗粒膜,所述第一粘结纳米颗粒膜包含第一非导电纳米颗粒,所述热路由结构包含在所述第一粘结纳米颗粒膜上方的第二粘结纳米颗粒膜,所述第二粘结纳米颗粒膜包含第二非导电纳米颗粒,且所述第一粘结纳米颗粒膜及所述第二粘结纳米颗粒膜实质上不含有机粘合剂材料,且

电介质材料,其在所述顶部互连层上方并且接触所述热路由结构,所述热路由结构的导热率高于所述电介质材料的导热率。

2. 根据权利要求1所述的集成电路,其中所述第一非导电纳米颗粒包含选自由氧化铝、金刚石、六方氮化硼、立方氮化硼及氮化铝组成的群组的材料。

3. 根据权利要求2所述的集成电路,接合垫结构接触所述热路由结构。

4. 根据权利要求1所述的集成电路,其进一步包括除热区,所述热路由结构延伸到所述除热区。

5. 根据权利要求1所述的集成电路,其进一步包括热敏组件,所述热路由结构延伸远离所述热敏组件。

6. 根据权利要求1所述的集成电路,其进一步包括匹配组件,所述热路由结构在所述匹配组件上方延伸。

7. 根据权利要求1所述的集成电路,其进一步包括热路由组件,所述热路由组件选自由深沟槽热路由结构、高导热率通孔、高导热率横向结构、高导热率贯穿封装导管及石墨通孔组成的群组;

所述深沟槽热路由结构包含粘结纳米颗粒膜,并且所述深沟槽热路由结构经安置在所述衬底中且延伸到所述衬底与所述互连区之间的所述边界;

所述高导热率通孔包含粘结纳米颗粒膜,并且所述高导热率通孔经安置在所述互连区中;

所述高导热率横向结构包含粘结纳米颗粒膜,并且所述高导热率横向结构经安置在所述互连区中;

所述高导热率贯穿封装导管包含粘结纳米颗粒膜,并且所述高导热率贯穿封装导管贯穿囊封材料安置在所述集成电路上方且延伸到所述集成电路;且

所述石墨通孔包含粘结纳米颗粒膜，并且所述石墨通孔电耦合到所述生热组件中的一者。

8. 根据权利要求1所述的集成电路，其中所述第一非导电纳米颗粒及所述第二非导电纳米颗粒由相同类型的纳米颗粒材料形成。

9. 根据权利要求1所述的集成电路，其中所述第一非导电纳米颗粒由与形成所述第二非导电纳米颗粒的纳米颗粒材料的类型不同的纳米颗粒材料形成。

10. 根据权利要求9所述的集成电路，其中所述第一粘结纳米颗粒膜的导热率与所述第二粘结纳米颗粒膜的导热率不同。

11. 一种形成集成电路的方法，所述方法包括：

提供包含半导体材料的衬底；

在所述衬底中形成生热组件；

在所述衬底上形成互连区，所述互连区包含：

在所述衬底上形成电介质层堆叠；

在所述电介质层堆叠中形成触点，所述触点与所述生热组件形成电连接；

在所述电介质层堆叠中形成互连件，所述互连件经形成在互连层中，所述互连件中的至少两者位于第一互连层中且与所述触点形成电连接，且所述互连件的部分位于顶部互连层中，所述顶部互连层在所述互连区中与所述衬底相对的顶部表面处；及

在所述电介质层堆叠中形成通孔，所述通孔与所述互连件形成电连接；及

形成热路由结构，所述热路由结构包含：

通过加成工艺在所述集成电路上的所述顶部互连层上方施配第一纳米颗粒墨水以形成包含第一非导电纳米颗粒及第一载液的第一纳米颗粒墨水膜；

诱导所述第一非导电纳米颗粒的粘结以形成第一粘结纳米颗粒膜；及

通过加成工艺在所述第一粘结纳米颗粒膜上施配第二纳米颗粒墨水以形成第二纳米颗粒墨水膜，所述第二纳米颗粒墨水膜包含第二非导电纳米颗粒及第二载液，并且所述第一纳米颗粒墨水膜及所述第二纳米颗粒墨水膜不含有有机粘合剂材料；以及

诱导所述第二非导电纳米颗粒的粘结以形成在所述第一粘结纳米颗粒膜上方的第二粘结纳米颗粒膜；以及

在形成所述第一纳米颗粒墨水膜之前，在所述顶部互连层上方形成电介质隔离层，所述热路由结构的导热率高于所述电介质隔离层的导热率。

12. 根据权利要求11所述的方法，其中形成所述热路由结构包含在诱导所述第一非导电纳米颗粒的粘结之前，加热所述第一纳米颗粒墨水膜以移除挥发性材料以形成所述第一粘结纳米颗粒膜。

13. 根据权利要求12所述的方法，其中加热所述第一纳米颗粒墨水膜包含使用红外发光二极管IRLED。

14. 根据权利要求11所述的方法，其中所述第一非导电纳米颗粒包含选自由氧化铝、金刚石、六方氮化硼、立方氮化硼及氮化铝组成的群组的材料。

15. 根据权利要求11所述的方法，其中所述加成工艺包含选自由离散液滴施配工艺、连续挤压工艺、直接激光转移工艺、静电沉积工艺及电化学沉积工艺组成的群组的工艺。

16. 根据权利要求11所述的方法，其中诱导所述第一非导电纳米颗粒的粘结包含选自

由扫描激光加热工艺、闪光加热工艺及尖峰加热工艺组成的群组的工艺。

## 互连区上方的集成电路纳米颗粒热路由结构

### 技术领域

[0001] 本发明涉及集成电路，且更特定来说，涉及集成电路中的热管理。

### 背景技术

[0002] 集成电路经常在一些有源组件中生成非期望热。有时期望通过散热器或其它无源结构移除热。有时期望从集成电路中的热敏组件转移热。管理集成电路中的过多热已变得越来越成问题。

### 发明内容

[0003] 在所描述实例中，集成电路具有衬底及安置在所述衬底上的互连区。所述互连区具有多个互连层，包含内含互连件的顶部互连层。所述集成电路在所述顶部互连层上具有热路由结构。所述热路由结构在所述顶部互连层上的所述集成电路的部分而非全部上方延伸。所述热路由结构包含粘结纳米颗粒膜，其中相邻纳米颗粒彼此粘结。所述热路由结构的导热率高于接触所述热路由结构的电介质材料的导热率。所述粘结纳米颗粒膜是通过包含加成工艺的方法形成。

### 附图说明

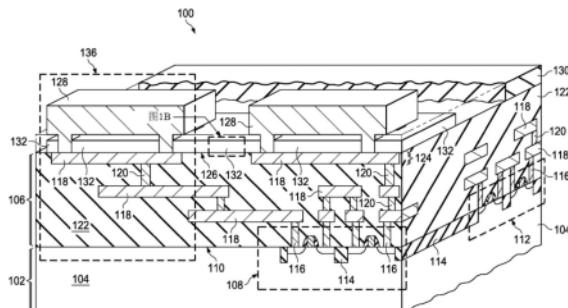

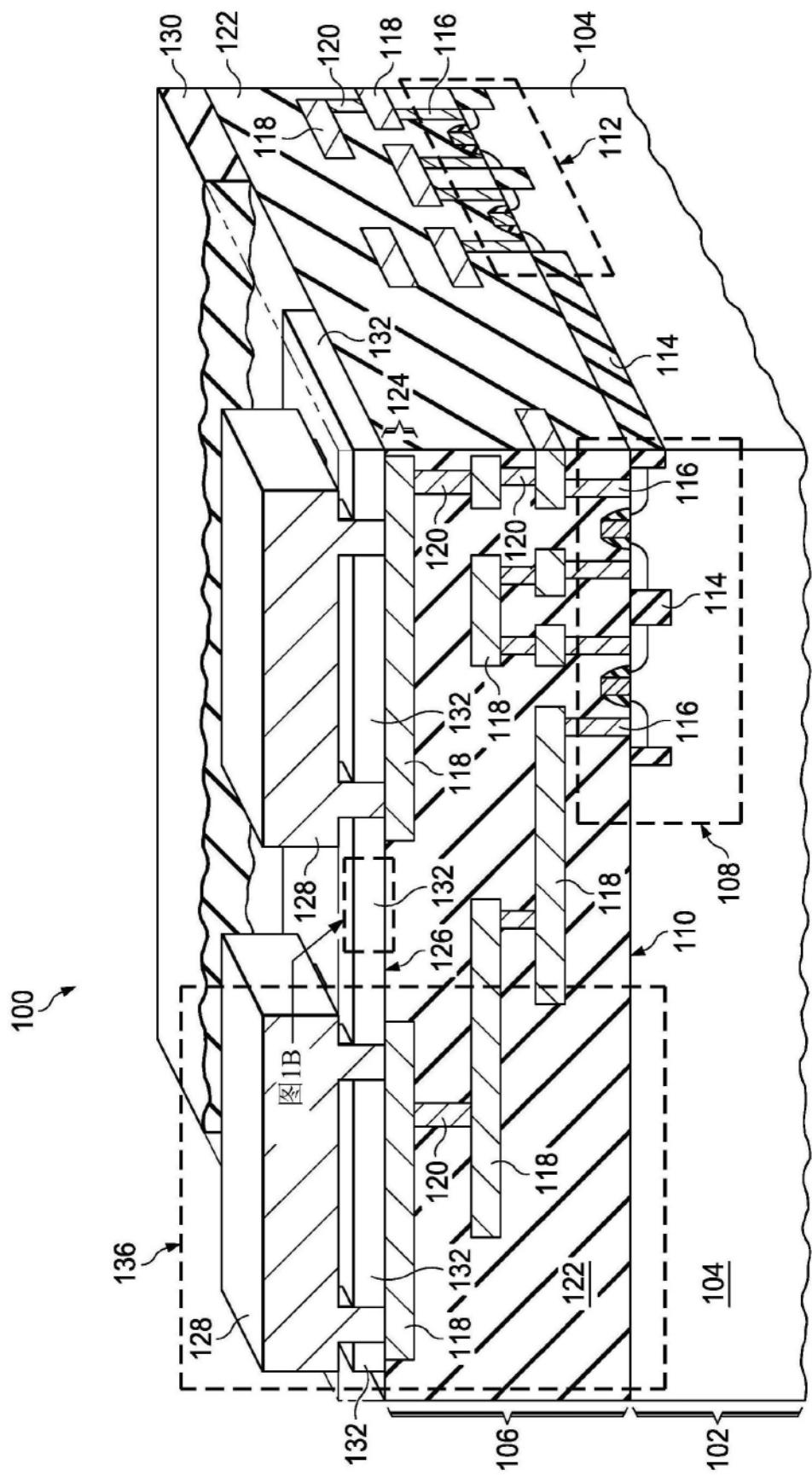

[0004] 图1A及图1B是根据实施例的实例集成电路的横截面。

[0005] 图2A到图2F描绘根据实施例的形成具有参考图1A及图1B所描述的类型的热路由结构的集成电路的实例方法。

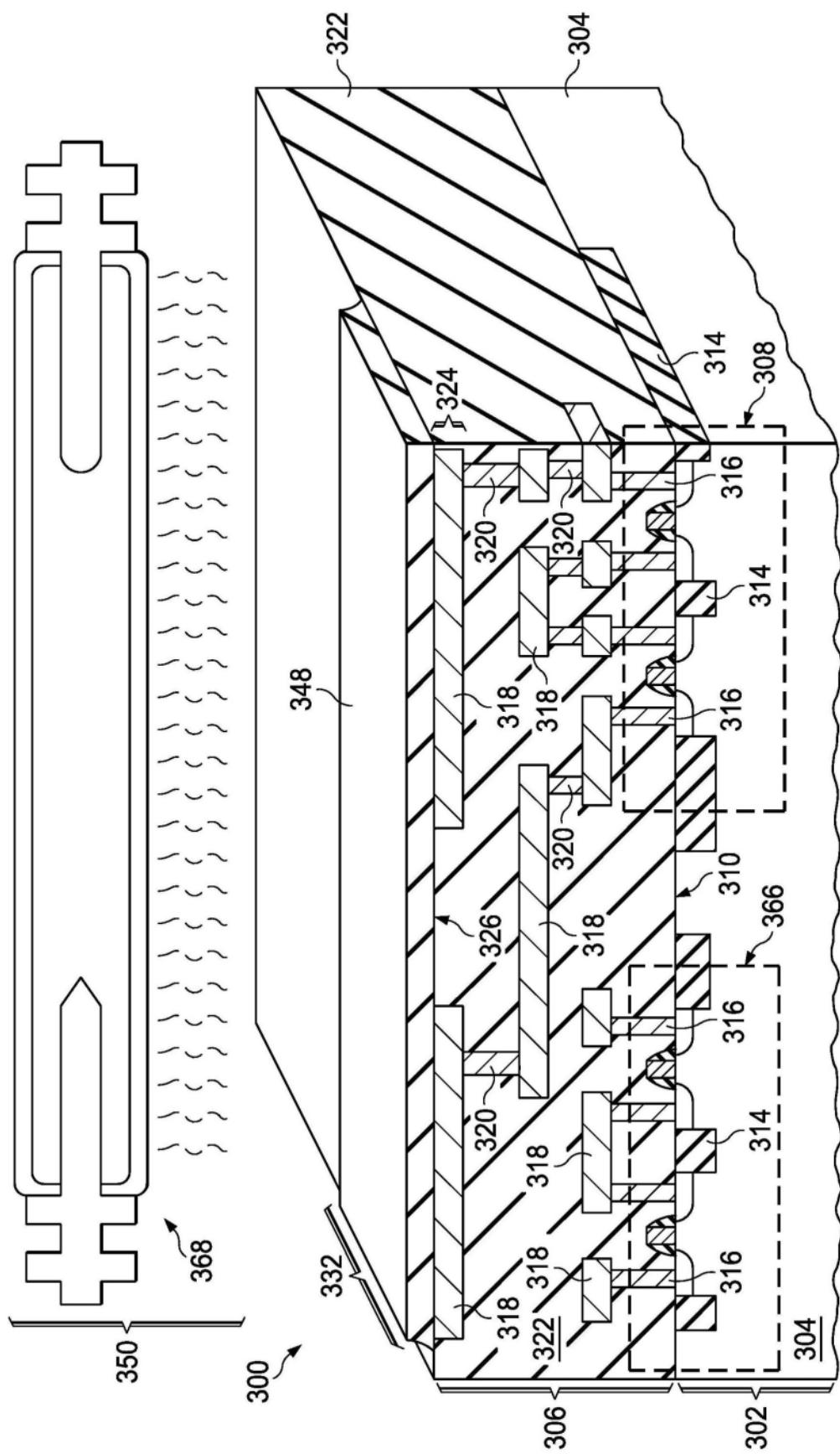

[0006] 图3A到图3C描绘根据实施例的形成具有参考图1A及图1B所描述的类型的热路由结构的集成电路的另一实例方法。

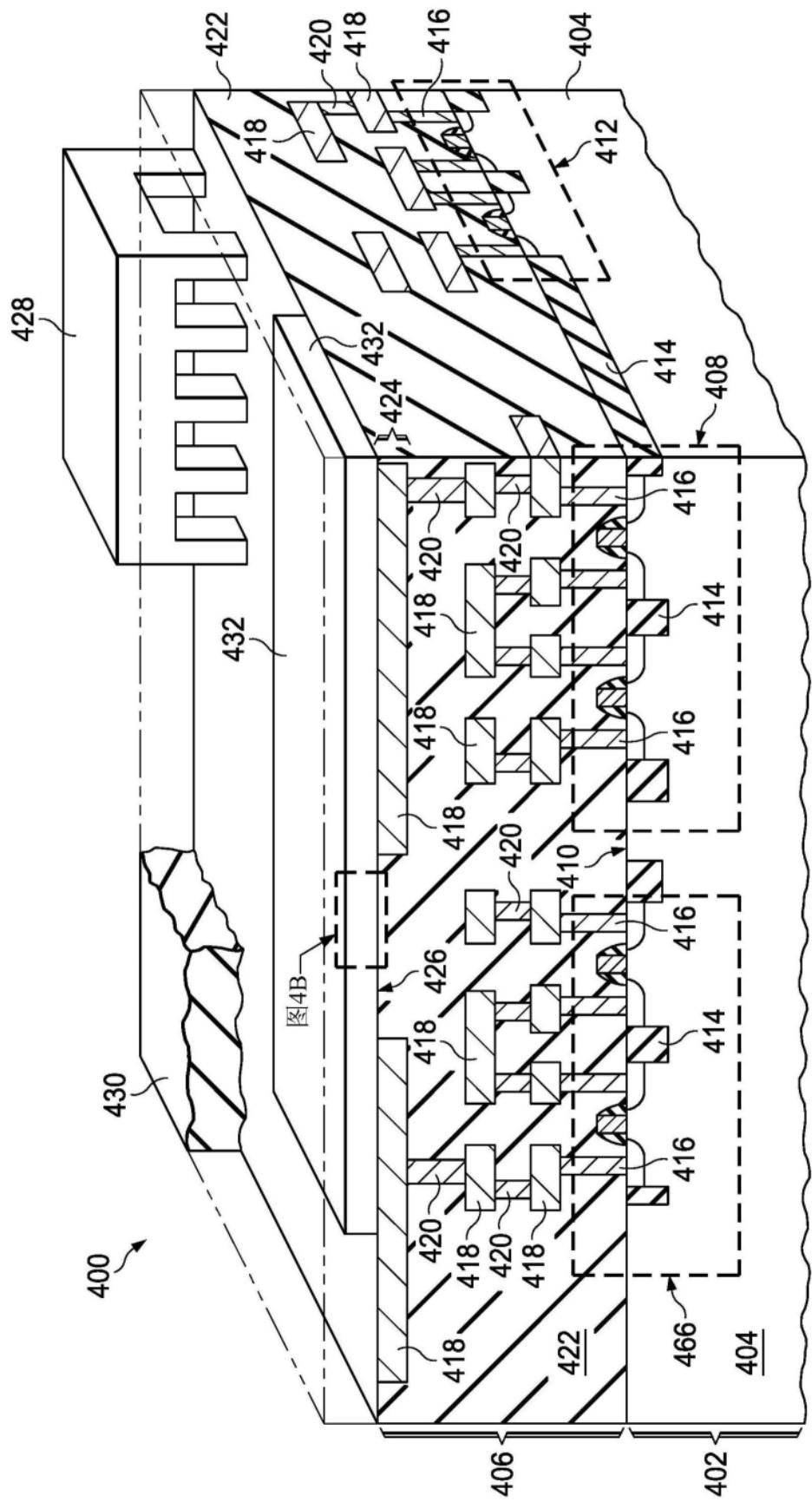

[0007] 图4A及图4B是根据实施例的另一实例集成电路的横截面。

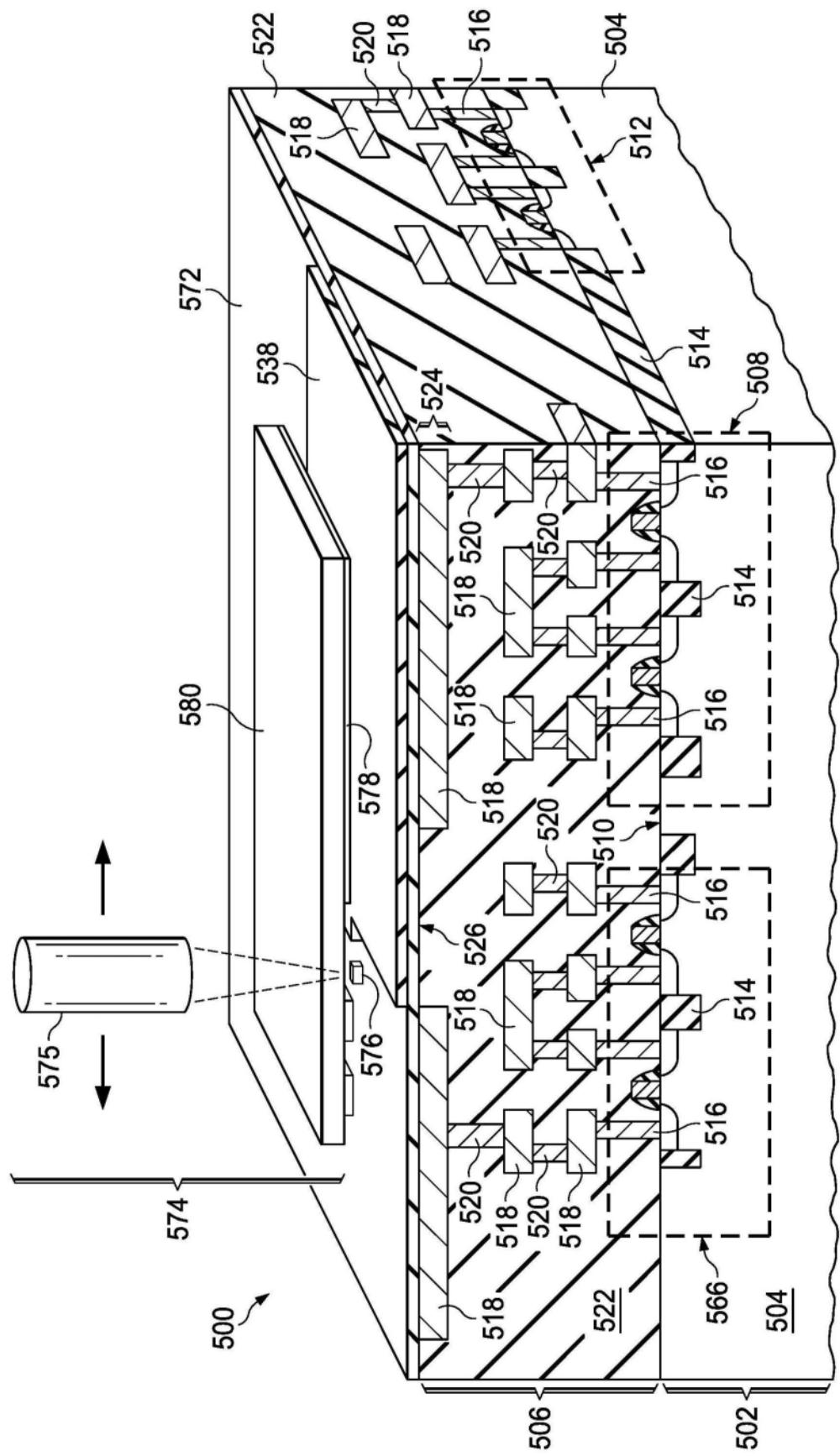

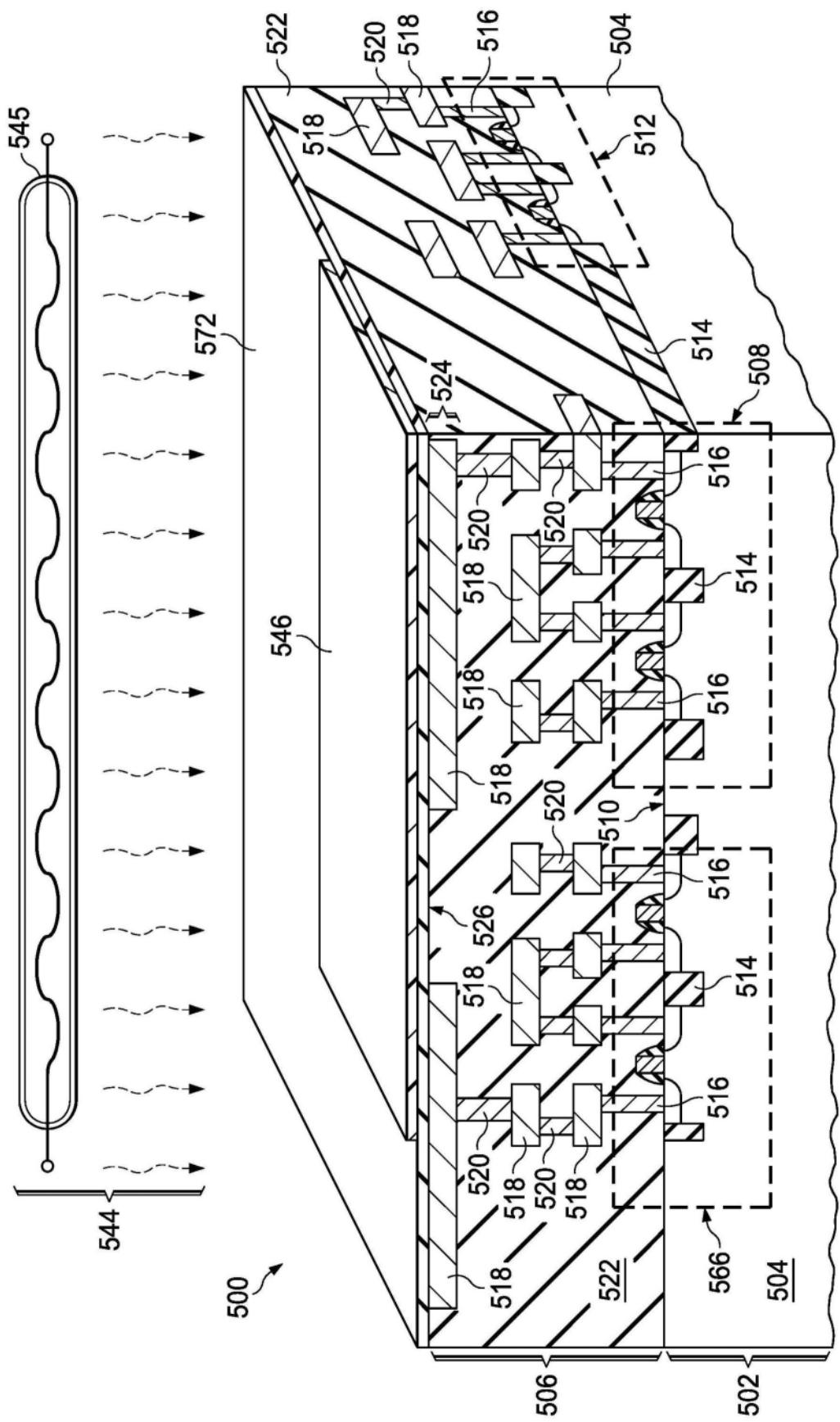

[0008] 图5A到图5D描绘根据实施例的形成具有参考图4A及图4B所描述的类型的热路由结构的集成电路的实例方法。

[0009] 图6是根据实施例的包含组合热路由结构的实例集成电路的横截面。

### 具体实施方式

[0010] 附图未按比例绘制。实例实施例不受所说明动作或事件的排序限制，因为一些动作可以不同顺序发生及/或与其它动作或事件同时发生。此外，一些所说明动作或事件是任选的。

[0011] 以下共同待决的专利申请案据此以引用方式并入：第US 15/361,394号专利申请案、第US 15/361,397号专利申请案、第US 15/361,399号专利申请案、第US 15/361,401号专利申请案及第US 15/361,403号专利申请案。

[0012] 本描述可使用例如“顶部”、“底部”、“前”、“后”、“上方”、“上”、“下方”、“下”等术语。这些术语不应被解释为限制结构或元件的位置或定向，但是提供结构或元件之间的空

间关系。

[0013] 在本描述中,术语集成电路的“瞬时顶部表面”是指集成电路的顶部表面,其存在于所描述的特定步骤处。在形成集成电路时,瞬时顶部表面在步骤间可改变。

[0014] 在本描述中,术语“横向”是指平行于集成电路的瞬时顶部表面的平面的方向,且术语“垂直”是指垂直于集成电路的瞬时顶部表面的平面的方向。

[0015] 图1A及图1B是根据实施例的实例集成电路的横截面。参考图1A,集成电路100包含内含半导体材料104的衬底102。半导体材料104可为IV型半导体,例如硅、硅锗或碳化硅。替代地,半导体材料104可为III-V型半导体,例如氮化镓或砷化镓。其它半导体材料在这个实例的范围内。集成电路100进一步包含安置在衬底102上的互连区106。集成电路100的生热组件108(图1A中被描绘为金属氧化物半导体(MOS)晶体管)接近衬底102与互连区106之间的边界110安置在衬底102中,可能延伸到互连区106中。生热组件108的其它表现形式(例如双极结型晶体管、结型场效应晶体管(JFET)、电阻器及硅控整流器(SCR))是在这个实例的范围内。在这个实例中,集成电路100还可包含图1A中被描绘为MOS晶体管的热敏组件112。热敏组件112的其它表现形式是在这个实例的范围内。所述组件可在衬底102与互连区106之间的边界110处通过场氧化物114横向分离。例如,场氧化物114可具有如图1A中所描绘的浅沟槽隔离(STI)结构,或可具有硅的局部氧化(LOCOS)结构。

[0016] 互连区106可包含安置在电介质层堆叠122中的触点116、互连件118及通孔120。触点116与生热组件108及热敏组件112形成电连接。互连件118经安置在多个互连层中。第一互连层中的互连件118与触点116形成电连接。通孔120经安置在连续互连层之间且与互连件118形成电连接。一些互连件118经安置在顶部互连层124中,顶部互连层124经定位成接近互连区106的顶部表面126。互连区106的顶部表面126位于互连区106中与衬底102与互连区106之间的边界110相对的表面处。顶部互连层124中的互连件118可包含铝互连件、镶嵌铜互连件及/或镀铜互连件。铝互连件可能在包含钛的粘附层上可包含具有百分之几的硅、钛及/或铜的铝层,且可能在铝层上具有氮化钛的抗反射层。镶嵌铜互连件可在安置在电介质层堆叠122中的沟槽中的钽及/或氮化钽的势垒层上包含铜。镀铜互连件可在互连件底部处包含粘附层,且可具有安置在互连件侧面上的势垒层。接合垫结构128可经安置在互连区106的顶部表面126上方,且可电耦合到顶部互连层124中的互连件118。保护性外涂层130可经安置在互连区106的顶部表面126上方。保护性外涂层130可邻接接合垫结构128。保护性外涂层130可包含一或多个电介质材料层,例如二氧化硅、氮化硅、氮氧化硅、聚酰亚胺及/或苯并环丁烯(BCB)。

[0017] 热路由结构132经安置在互连区106的顶部表面126上方,在顶部表面126的部分而非全部上方延伸。热路由结构132的导热率高于接触热路由结构132的电介质材料的导热率。接触热路由结构132的电介质材料可包含电介质层堆叠122的电介质材料及/或保护性外涂层130的电介质材料。导热率是材料的性质,且可以单位瓦/米°C表示。热路由结构132包含图1B中更详细地展示的主要含纳米颗粒135的粘结纳米颗粒膜134。粘结纳米颗粒膜134中的相邻纳米颗粒135彼此粘结。在纳米颗粒135的表面上可能存在无机官能分子,例如包含硅及氧的硅烷基分子。粘结纳米颗粒膜134基本上不含有机粘合剂材料,例如粘附剂及或聚合物。热路由结构132可从生热组件108上方的区域延伸到集成电路100的除热区136,如图1A中所展示。热路由结构132可位于热敏组件112上方的区域外,如图1A中所展示,因此经

配置以在集成电路100的操作期间有利地从生热组件108转移热远离热敏组件112。

[0018] 在如图1A及图1B中所描绘的这个实例的版本中,热路由结构132可为非导电的,且纳米颗粒135的实例可包含氧化铝、金刚石、六方氮化硼、立方氮化硼及/或氮化铝的纳米颗粒。热路由结构132可接触接合垫结构128而没有相邻接合垫结构128之间的非期望电分流的风险,从而有利地使能够更完全地覆盖生热组件108上方及除热区136中的区域,以有利地从生热组件108收集更多热,且更有效地将热传递到除热区136。

[0019] 在这个实例的另一版本中,热路由结构132可为导电的。在此版本中,纳米颗粒135的实例可包含金属、石墨烯、金属内嵌石墨烯、石墨、石墨碳及/或碳纳米管的纳米颗粒。热路由结构132的导电版本可与接合垫结构128横向分离且可与顶部互连层124中的互连件118垂直隔离。

[0020] 在这个实例的进一步版本中,纳米颗粒135可包含适于催化石墨材料的金属,且热路由结构132可在粘结纳米颗粒134上包含石墨材料层。在此版本中,纳米颗粒135的实例可包含铜、镍、钯、铂、镓、铑、铈、锇、钼及/或金的纳米颗粒。石墨材料可包含石墨、石墨碳、石墨烯及/或碳纳米管等。在此版本中,热路由结构132是导电的,且因此可与接合垫结构128横向分离且可与顶部互连层124中的互连件118垂直隔离。

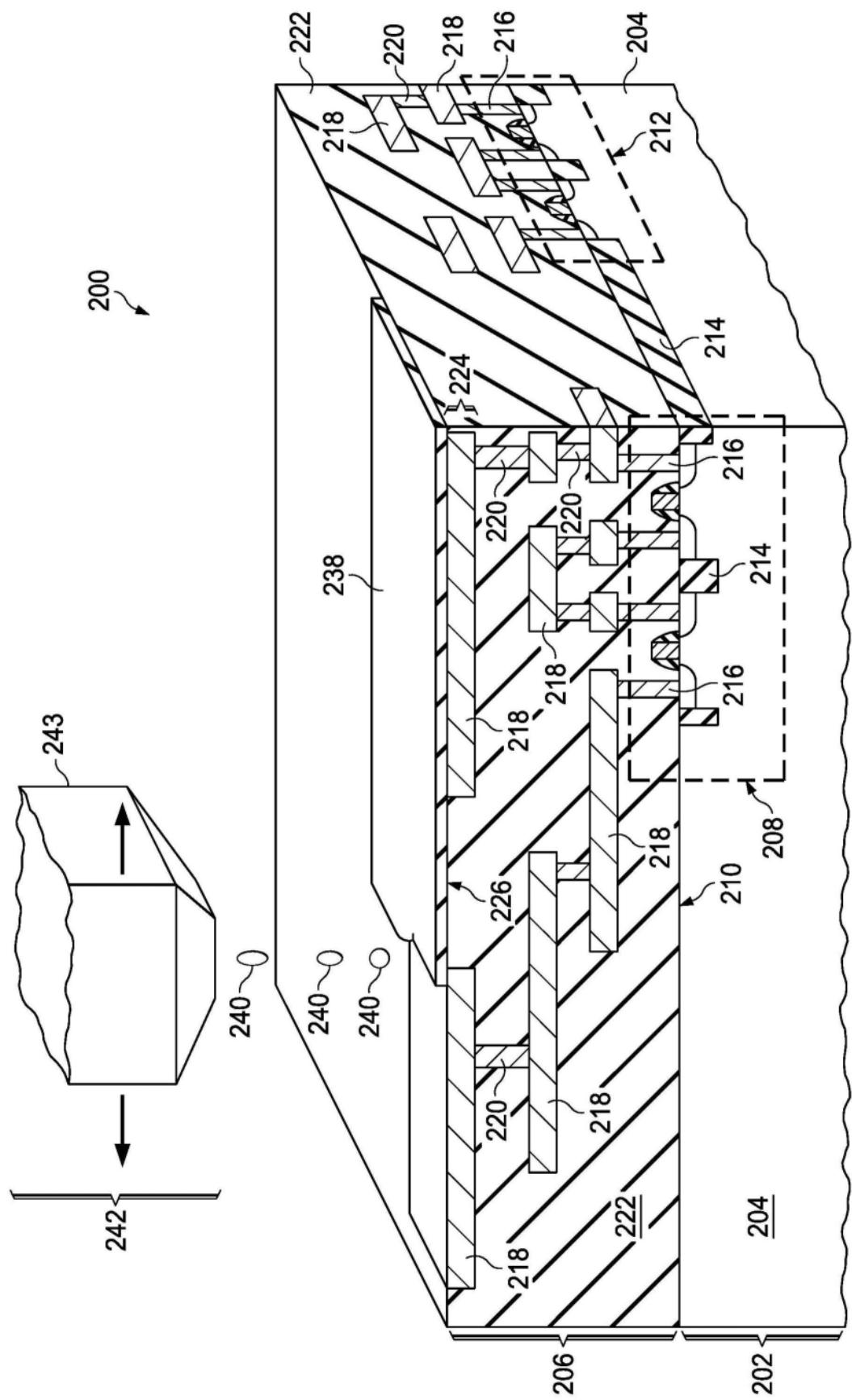

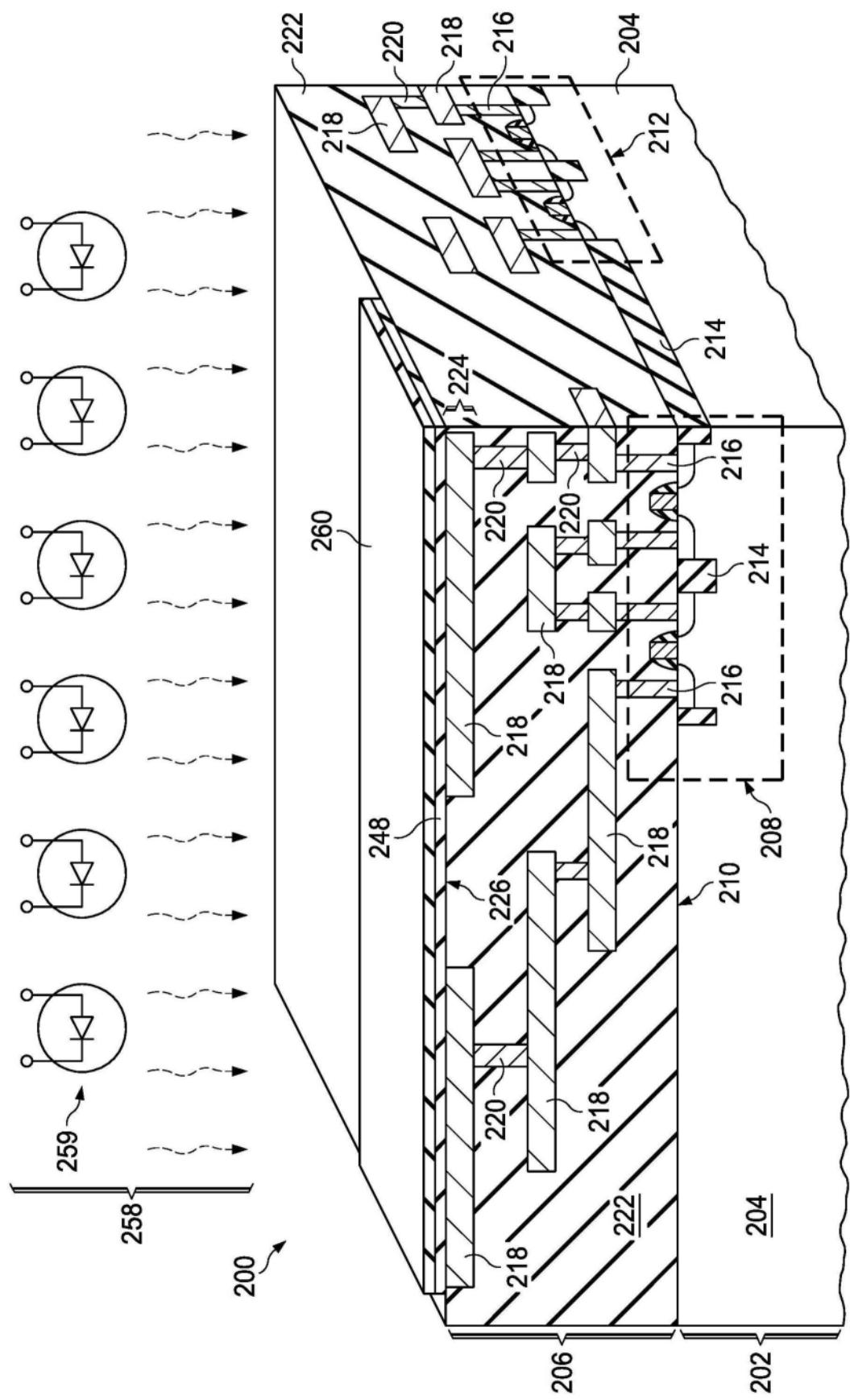

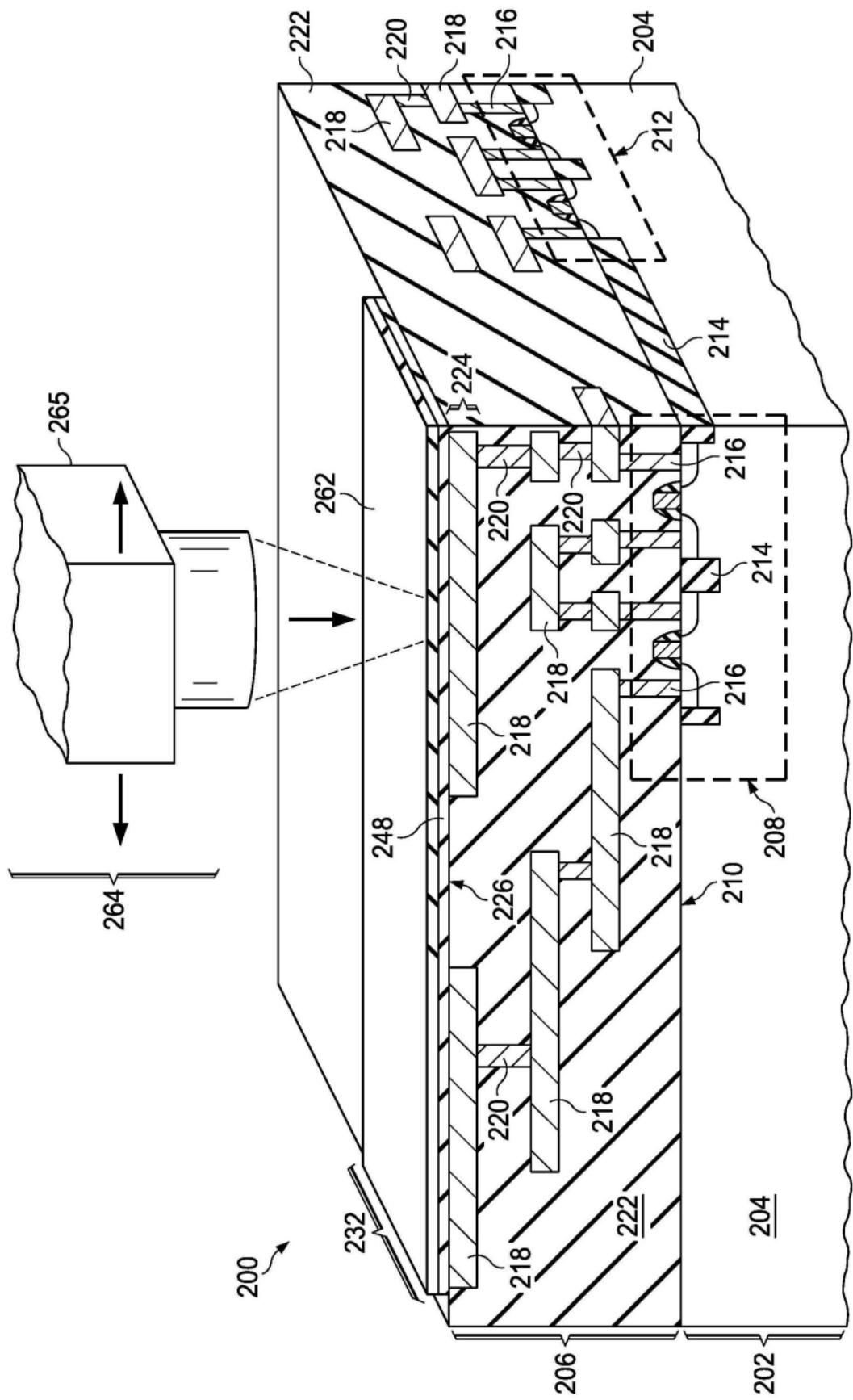

[0021] 图2A到图2F描绘根据实施例的形成具有热路由结构的集成电路的实例方法。参考图2A,在包含半导体材料204的衬底202上形成集成电路200。例如,衬底202可为半导体晶片。在半导体材料204中形成组件,例如生热组件208及热敏组件212。组件可包含MOS晶体管、双极结型晶体管、JFET、电阻器、SCR、二极管等。可在衬底202中形成场氧化物214以横向分离组件。场氧化物214可通过STI工艺或替代地通过LOCOS工艺形成。

[0022] 在衬底202上方形成互连区206。互连区206可经形成成为一系列电介质层以形成电介质层堆叠222,其中互连元件经形成在电介质层中的每一者中。可直接在衬底202上方形成电介质层堆叠222的预金属电介质(PMD)层,且随后可通过PMD层形成触点216以与组件形成电连接,包含生热组件208及热敏组件212。第一金属内电介质(IMD)层经形成成为电介质层堆叠222的部分。在PMD层及触点216上方形成第一IMD层中的第一互连层中的互连件218。第一互连层中的互连件218与触点216形成电连接。在第一IMD层及第一互连层上方形成第一层间电介质(ILD)层,作为电介质层堆叠222的部分。在第一ILD中形成通孔220,从而与第一互连层中的互连件218形成电连接。在互连区206中形成具有循序互连层中的互连件的额外IMD层及具有通孔220的额外ILD层,最终在顶部互连层224中形成互连件218。顶部互连层224延伸到互连区206的顶部表面226。

[0023] 形成这个实例的热路由结构开始于通过第一加成工艺242在互连区206的顶部表面226上方形成第一纳米颗粒墨水240的第一纳米颗粒墨水膜238。在本描述中,加成工艺将第一纳米颗粒墨水240安置在所期望区域中且不将第一纳米颗粒墨水240安置在所期望区域外,因此产生第一纳米颗粒墨水膜238的最终期望形状而不需要移除第一纳米颗粒墨水238的部分。加成工艺可使能够在所期望区域中形成膜而不需要光刻工艺及后续蚀刻工艺,因此有利地降低制造成本及复杂性。在这个实例的一个版本中,可直接在互连区206的顶部表面226上形成第一纳米颗粒墨水膜238,如图2A中所描绘。在替代版本中,在形成第一纳米颗粒墨水膜238之前,可在顶部表面226上形成一或多层保护性外涂层。第一纳米颗粒墨水240可包含纳米颗粒及载液。例如,第一纳米颗粒墨水240可为墨水、浆料、悬浮液或溶胶凝

胶。纳米颗粒可包含参考图1A及图1B所描述的纳米颗粒135的材料。在纳米颗粒的表面上可存在无机功能性分子以促后粘结。可选择第一纳米颗粒墨水240的成分以提供与集成电路200的所期望粘附。第一纳米颗粒墨水240在后续形成的热路由结构的区域中施配到集成电路200上,且未经施配在互连区206的整个瞬时顶部表面上方。第一加成工艺242可包含使用如图2A所描绘的离散液滴施配设备243的离散液滴工艺,有时称为喷墨工艺。离散液滴施配设备243可经配置使得集成电路200及离散液滴施配设备243可相对于彼此横向移动以便为第一纳米颗粒墨水膜238提供所期望施配图案。离散液滴施配设备243可具有可独立地并行激活以便为第一加成工艺242提供所期望吞吐量的多个施配端口。在这个实例的替代版本中,第一加成工艺242可包含连续挤压工艺、直接激光转印工艺、静电沉积工艺或电化学沉积工艺。

[0024] 参考图2B,通过第一烘烤工艺244加热图2A的第一纳米颗粒墨水膜238以从第一纳米颗粒墨水膜238移除至少部分挥发性材料,以形成主要包含纳米颗粒的第一纳米颗粒膜246。第一烘烤工艺244可为例如使用如图2B中示意性地指示的白炽光源245或红外发光二极管(IR LED)的辐射热工艺。替代地,第一烘烤工艺244可为通过衬底202加热第一纳米颗粒墨水膜238的热板工艺。第一烘烤工艺244可在部分真空中或在具有连续低压气流的环境中执行,以增强挥发性材料的移除。

[0025] 参考图2C,通过第一粘结诱导工艺250加热图2B的第一纳米颗粒膜246使得相邻纳米颗粒彼此粘结,以形成第一粘结纳米颗粒膜248。诱导相邻纳米颗粒之间的粘结所要的温度依据纳米颗粒的大小而变化。较小纳米颗粒可在低于较大纳米颗粒的温度下加热以获得所期望粘结。可选择纳米颗粒以使实现在与集成电路组件及结构兼容的温度下的粘结。粘结可通过包含涉及相邻纳米颗粒之间的原子扩散的物理机理的过程发生。粘结也可通过包含涉及相邻纳米颗粒之间的原子反应的化学机理的过程发生。第一粘结诱导工艺250可包含通过如图2C中示意性地描绘的扫描激光设备251进行加热。扫描激光设备251可经配置以基本上将热仅提供给第一纳米颗粒膜246,且不将热提供给与第一纳米颗粒膜246横向相邻的集成电路200的部分,从而有利地减少组件208及212上的总热负荷。

[0026] 在这个实例的一个变型中,第一粘结诱导工艺250可包含施加辐射能量达1微妙到10微妙的闪光加热工艺。在另一变型中,第一粘结诱导工艺250可包含施加辐射能量达100毫秒到5秒的尖峰加热工艺。在这个实例的替代版本中,参考图2B所描述的第一烘烤工艺244可与第一粘结诱导工艺250组合,其中施加到图2B的第一纳米颗粒膜246的热功率经斜变以首先移除挥发性材料,接着诱导纳米颗粒粘结。诱导纳米颗粒之间的粘结的其它方法是在这个实例的范围内。

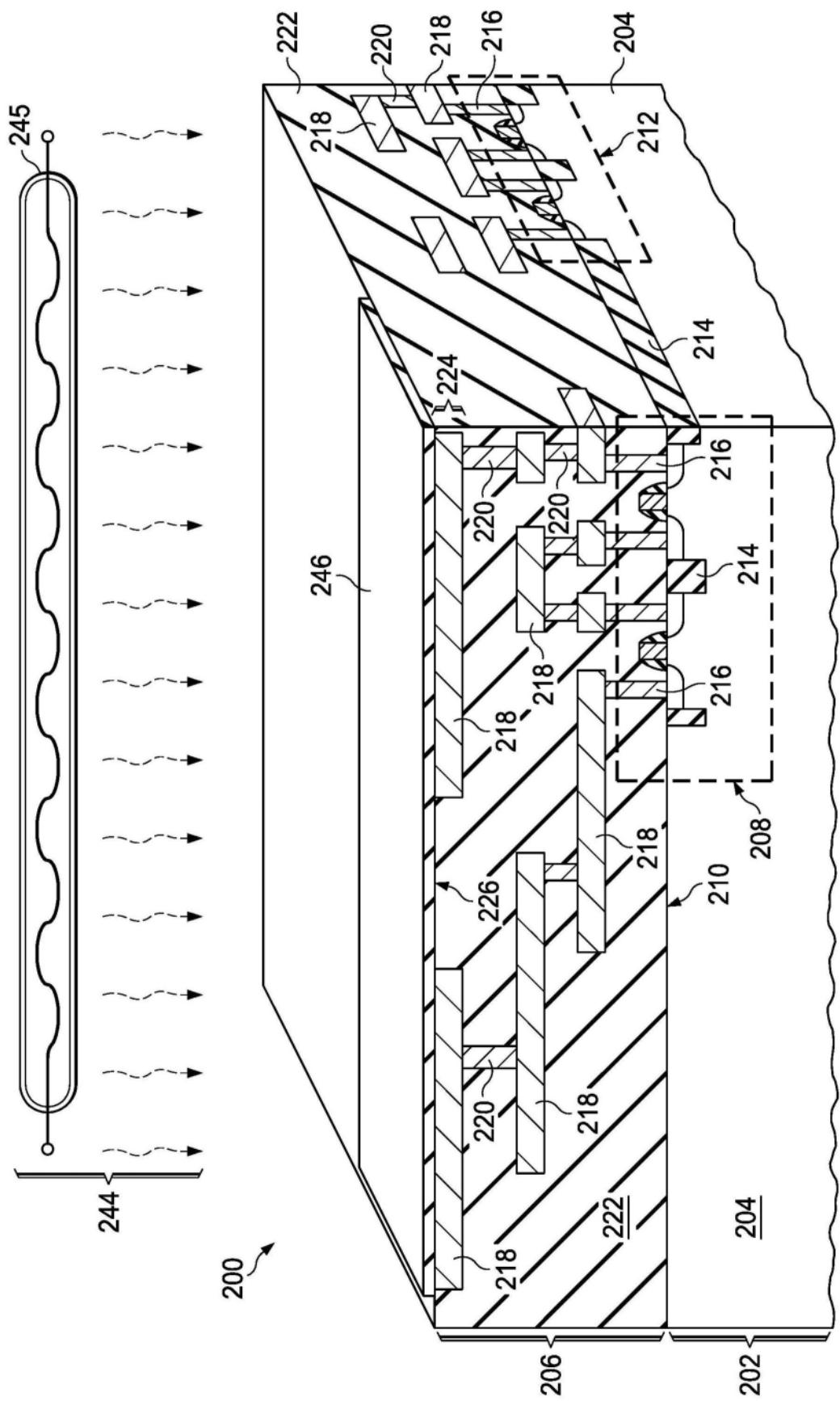

[0027] 参考图2D,形成这个实例的热路由结构以通过在第一粘结纳米颗粒膜248上施配第二纳米颗粒墨水254来形成第二纳米颗粒墨水膜252而继续。例如,第二纳米颗粒墨水254可为墨水、浆料、或溶胶凝胶。第二纳米颗粒墨水252可具有与图2A的第一纳米颗粒墨水膜238基本上相同的成分。替代地,第二纳米颗粒墨水膜252可具有与第一纳米颗粒墨水膜238不同的成分,例如经选择以提供所期望导热率的成分。通过第二加成工艺256将第二纳米颗粒墨水254施配到第一粘结纳米颗粒膜248上。第二加成工艺256可使用由参考图2A所描述的第一加成工艺242使用的相同类型的设备,例如如图2D中所描绘的离散液滴施配设备257。替代地,第二加成工艺256可使用不同设备或可使用不同工艺,尤其是如果第二纳米颗

粒墨水膜252的成分不同于第一纳米颗粒墨水膜238的成分。

[0028] 参考图2E,通过第二烘烤工艺258加热图2D的第二纳米颗粒墨水膜252以从第二纳米颗粒墨水膜252移除至少部分挥发性材料以形成第二纳米颗粒膜260。第二纳米颗粒膜260主要包含纳米颗粒。第二烘烤工艺258可使用如图2E中示意性地描绘的IR LED259。使用IR LED 259可实现将辐射热基本上仅施加到含有第二纳米颗粒墨水膜252的区域,而不将辐射热施加到第二纳米颗粒墨水膜252外的集成电路200的区域,从而有利地减少组件208及212上的热负荷。替代地,第二烘烤工艺258可包含使用白炽光源的辐射热工艺,或可包含热板工艺。第二烘烤工艺258可任选地在比第一烘烤工艺244更高的温度下或更长的时间内执行。

[0029] 参考图2F,通过第二粘结诱导工艺264加热图2E的第二纳米颗粒膜260使得第二纳米颗粒膜260中的相邻纳米颗粒彼此粘结,以在第一粘结纳米颗粒膜248上方形成第二粘结纳米颗粒膜262。第二粘结诱导工艺264可与第一粘结诱导工艺250类似,例如使用扫描激光设备265的第二扫描激光加热工艺。可通过第二粘结诱导工艺264诱导第一粘结纳米颗粒膜248中的纳米颗粒的进一步粘结。

[0030] 第一粘结纳米颗粒膜248及第二粘结纳米颗粒膜262可提供热路由结构232。替代地,可形成、烘烤及加热额外纳米颗粒墨水膜以诱导纳米颗粒粘结,以与第一粘结纳米颗粒膜248及第二粘结纳米颗粒膜262组合以提供热路由结构232。

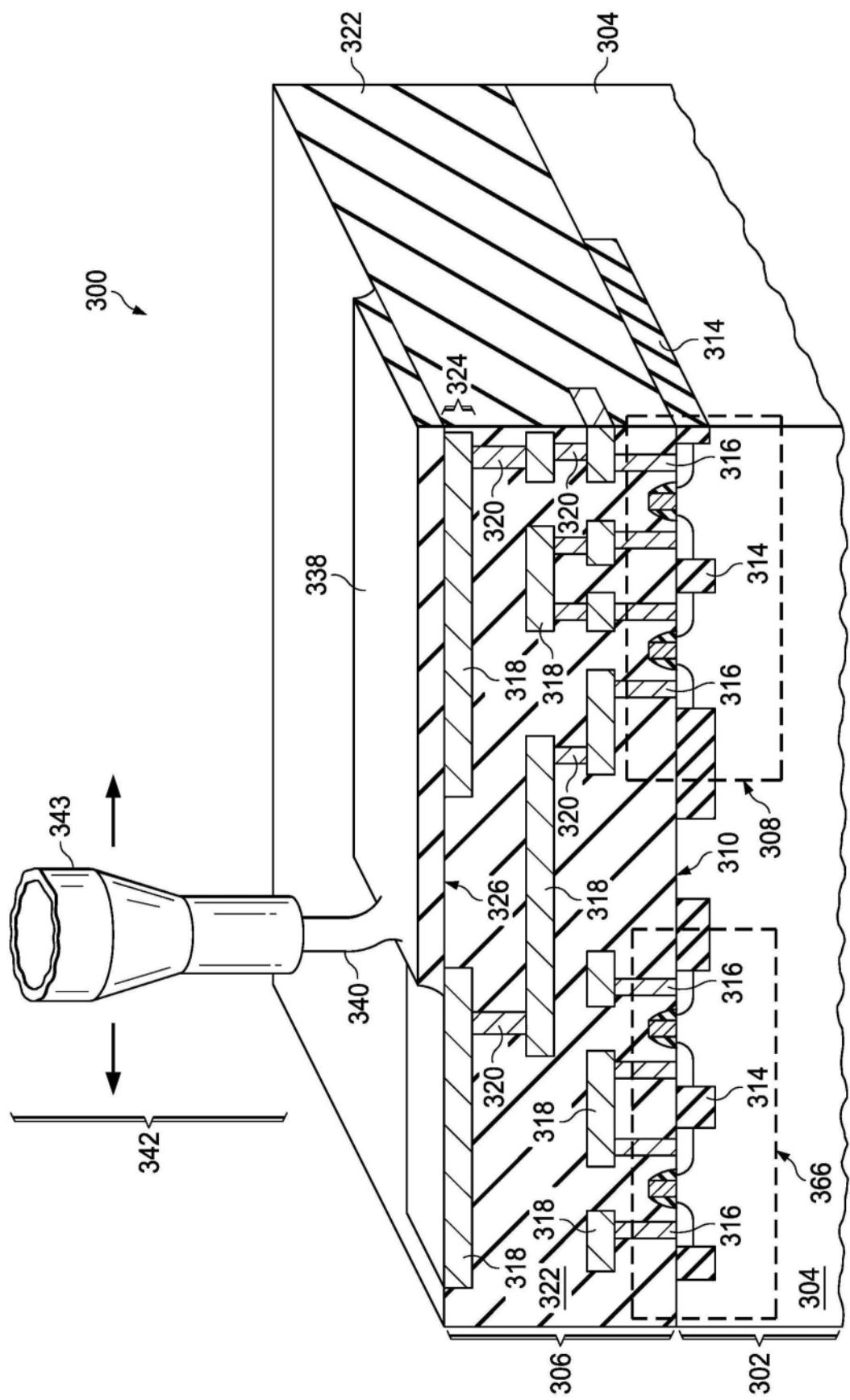

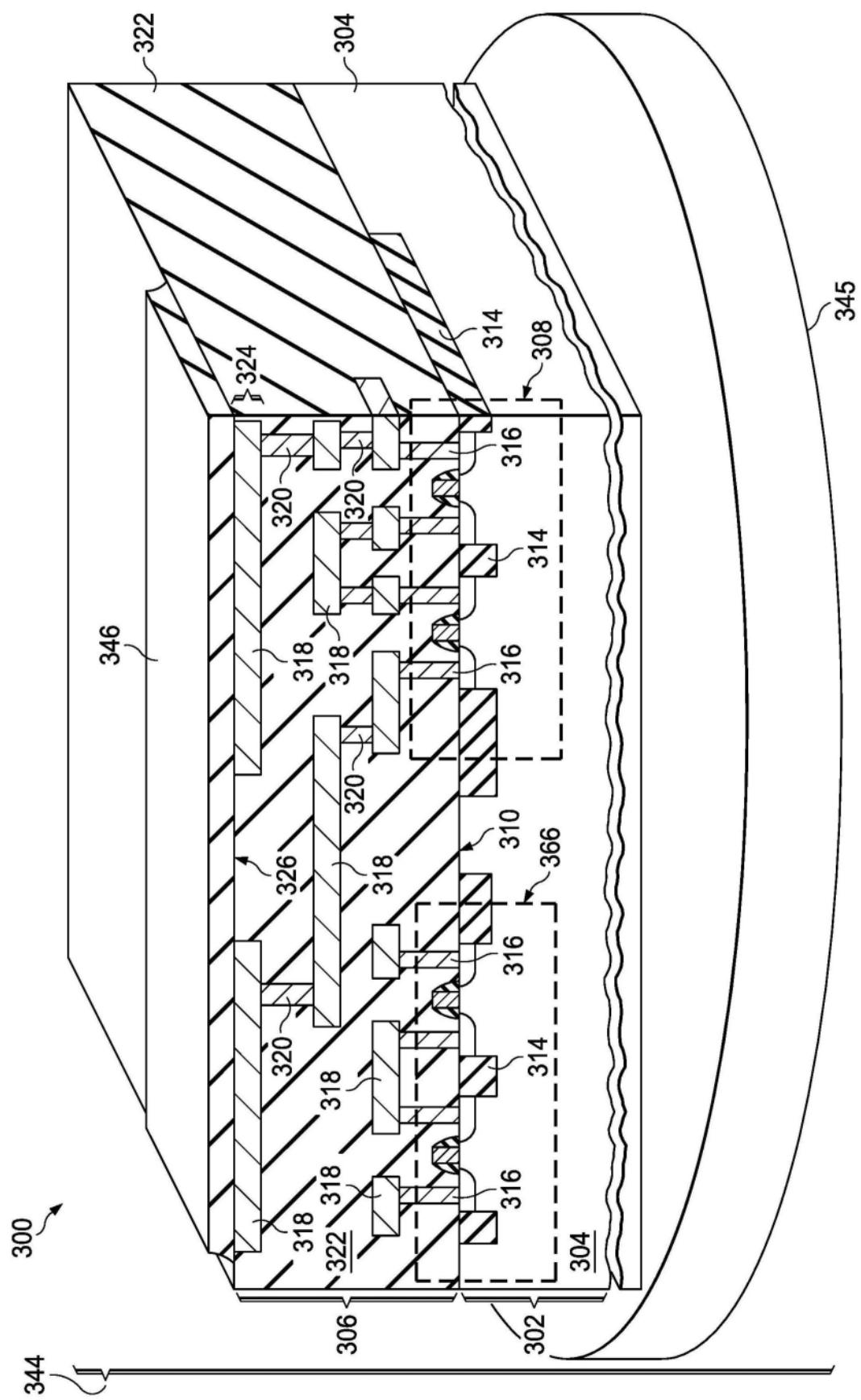

[0031] 图3A到图3C描绘根据实施例的形成具有热路由结构的集成电路的另一实例方法。参考图3A,在包含半导体材料304的衬底302上形成集成电路300。在半导体材料304中接近衬底302的顶部表面310形成组件。这个实例的组件可包含第一组组件308及第二组组件366,其中第一组组件308在空间上与第二组组件366分离,且其中第一组组件308及第二组组件366受益于共享相同热环境。第一组组件308及第二组组件366可为模拟电路的匹配组件。匹配组件经设计为具有基本上相同的性能参数,例如驱动电流及阈值。因为这些性能参数受温度影响,所以减小匹配组件之间的温差可有利地减小性能参数的差异。组件308及366可包含MOS晶体管、双极结型晶体管、JFET、电阻器、SCR、二极管等。可在衬底302中形成场氧化物314以横向分离组件。场氧化物314可通过STI工艺或替代地通过LOCOS工艺形成。

[0032] 在衬底302上方形成互连区306。衬底302的顶部表面310也是衬底302与互连区306之间的边界。互连区306可经形成为一系列电介质层(例如PMD层以及交替的IMD层及ILD层)以形成电介质层堆叠322,其中互连元件(例如触点316、互连件318及通孔320)经形成在电介质层中。在顶部互连层324中安置互连件318的部分。顶部互连层324接近互连区306的顶部表面326延伸。互连区306的顶部表面326位于互连区306中与衬底302与互连区306之间的边界310相对的表面处。

[0033] 形成这个实例的热路由结构开始于通过加成工艺342在互连区306的顶部表面326上方形成纳米颗粒墨水340的纳米颗粒墨水膜338。在这个实例的一个版本中,可直接在顶部表面326上形成纳米颗粒墨水膜338,如图3A中所描绘。这个实例的纳米颗粒墨水340包含纳米颗粒及载液。纳米颗粒墨水340在后续形成的热路由结构的区域中施配到集成电路300上,且未经施配在互连区306的整个顶部表面326上。加成工艺342可包含使用如图3A中所描绘的微挤压施配设备343的连续挤压工艺。微挤压施配设备343可经配置使得集成电路300及微挤压施配设备343可相对于彼此横向移动,以便为纳米颗粒墨水膜338提供所期望施配

图案。在这个实例中,微挤压施配设备343可形成足够厚的纳米颗粒墨水膜338以形成热路由结构而不需要额外纳米颗粒墨水膜。

[0034] 参考图3B,通过烘烤工艺344加热图3A的纳米颗粒墨水膜338以从纳米颗粒墨水膜338移除至少部分挥发性材料以形成主要包含纳米颗粒的纳米颗粒膜346。烘烤工艺344可为使用安置在衬底302下方的热板345的热板工艺。替代地,烘烤工艺344可为如参考图2B或图2E所描述的辐射热工艺。烘烤工艺344可在部分真空中或在具有连续低压气流的环境中执行,以增强挥发性材料的移除。

[0035] 参考图3C,通过粘结诱导工艺350加热图3B的纳米颗粒膜346使得相邻纳米颗粒彼此粘结,以形成粘结纳米颗粒膜348。粘结诱导工艺350可包含使用闪光灯368的闪光加热工艺350,如图3C中示意性地描绘。诱导纳米颗粒之间的粘结的其它方法是在这个实例的范围内。粘结纳米颗粒膜348可提供基本上整个热路由结构332。替代地,可形成额外粘结纳米颗粒膜以与粘结纳米颗粒膜348组合以提供热路由结构332。

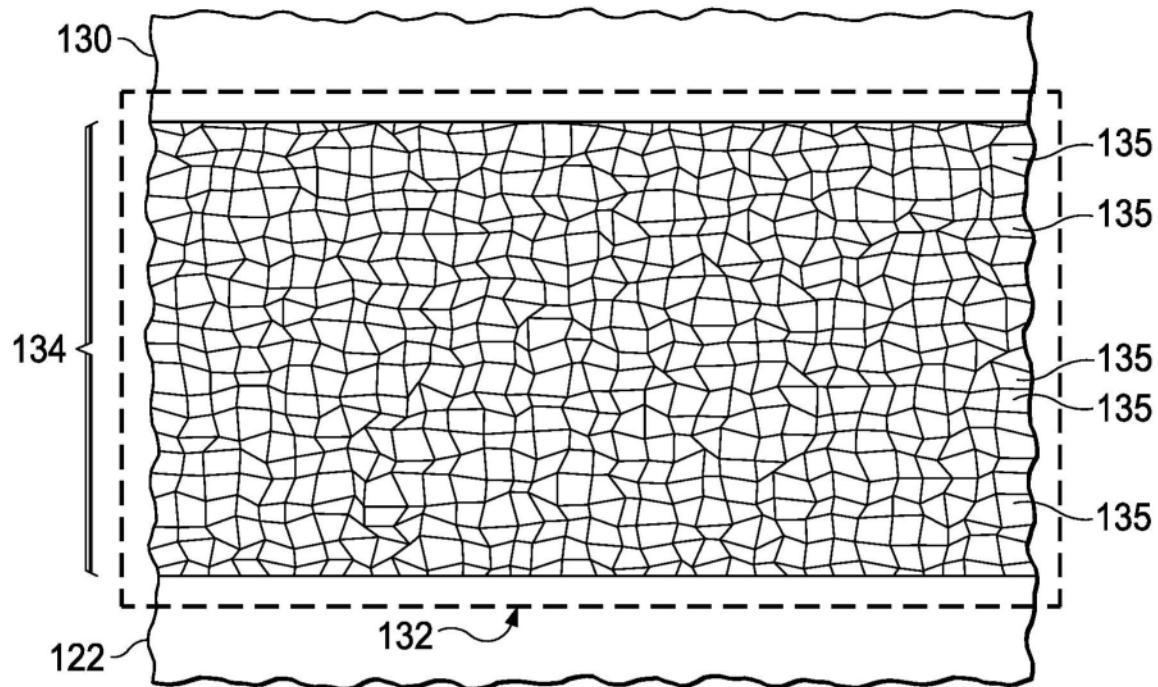

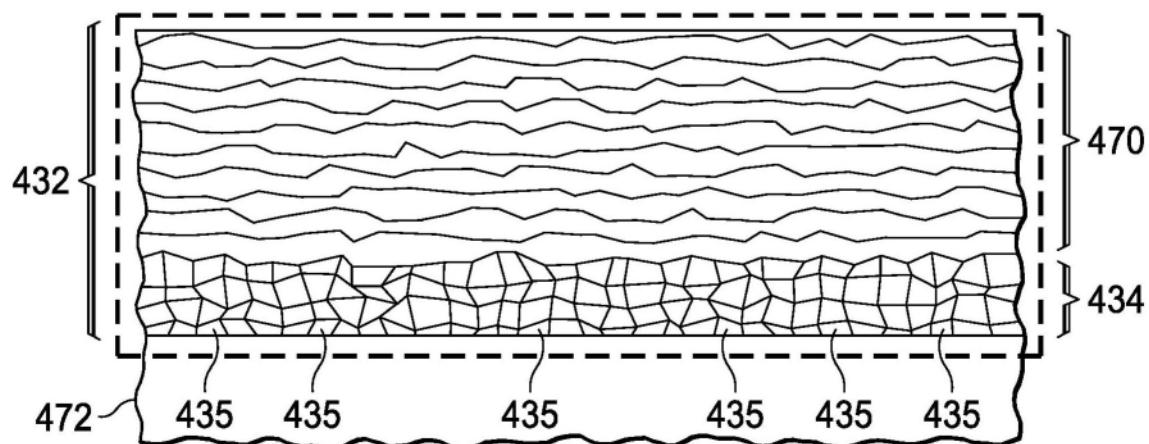

[0036] 图4A及图4B是根据实施例的另一实例集成电路的横截面。参考图4A,集成电路400包含内含半导体材料404的衬底402。集成电路400进一步包含安置在衬底402上的互连区406。在这个实例中,第一组组件408及第二组组件466接近衬底402与互连区406之间的边界410安置在衬底402中。在这个实例中,第一组组件408及第二组组件466可为其性能受益于具有类似热环境的匹配组件。集成电路400可进一步包含其性能随着操作温度降低而升高的热敏组件412。组件408、466及412在图4A中被描绘为MOS晶体管,但是其它表现形式(例如双极结型晶体管、JFET、电阻器及SCR)也在这个实例的范围内。组件408、466及412可在衬底402与互连区406之间的边界410处通过场氧化物414横向分离。

[0037] 互连区406可包含安置在电介质层堆叠422中的触点416、互连件418及通孔420。一些互连件418经安置在顶部互连层424中,顶部互连层424位于互连区406的顶部表面426处。互连区406的顶部表面426位于互连区406中与衬底402与互连区406之间的边界410相对的表面处。接合垫结构428可经安置在互连区406的顶部表面426上方。接合垫结构428电耦合到顶部互连层424中的互连件418。保护性外涂层430可经安置在互连区406的顶部表面426上方。接合垫结构428可延伸穿过保护性外涂层430。

[0038] 热路由结构432经安置在互连区406的顶部表面426上方,在顶部表面426的部分而非全部上方延伸。在这个实例中,热路由结构432包含:粘结纳米颗粒膜434,其包含内含金属的纳米颗粒435;及石墨材料层470,其经安置在粘结纳米颗粒膜434上,如图4B中详细地展示。例如,纳米颗粒435中的金属可包含铜、镍、钯、铂、铱、铑、铈、锇、钼及/或金。石墨材料层470可包含石墨、石墨碳、石墨烯、碳纳米管等。

[0039] 电介质隔离层472可任选地安置在粘结纳米颗粒膜434下方。电介质隔离层472可电隔离粘结纳米颗粒膜434与顶部互连层424中的下伏互连件418。

[0040] 在这个实例中,热路由结构432可在第一组组件408及第二组组件466上方延伸,且可延伸远离热敏组件412,如图4A中所展示。因此,热路由结构432可为第一组组件408及第二组组件466提供更紧密匹配的热环境且从而提高其性能,同时有利地从第一组组件408及第二组组件466转移热远离热敏组件412。

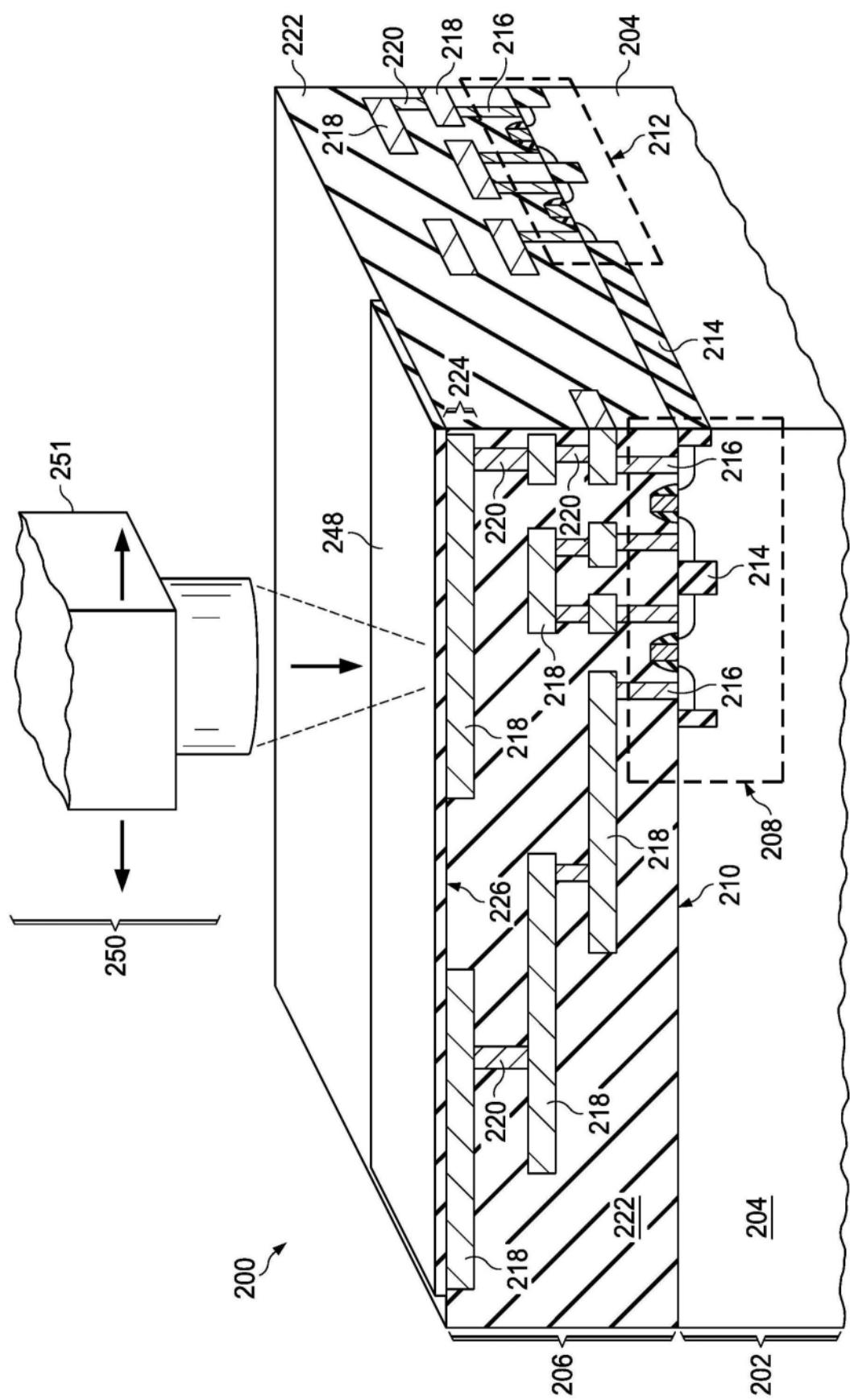

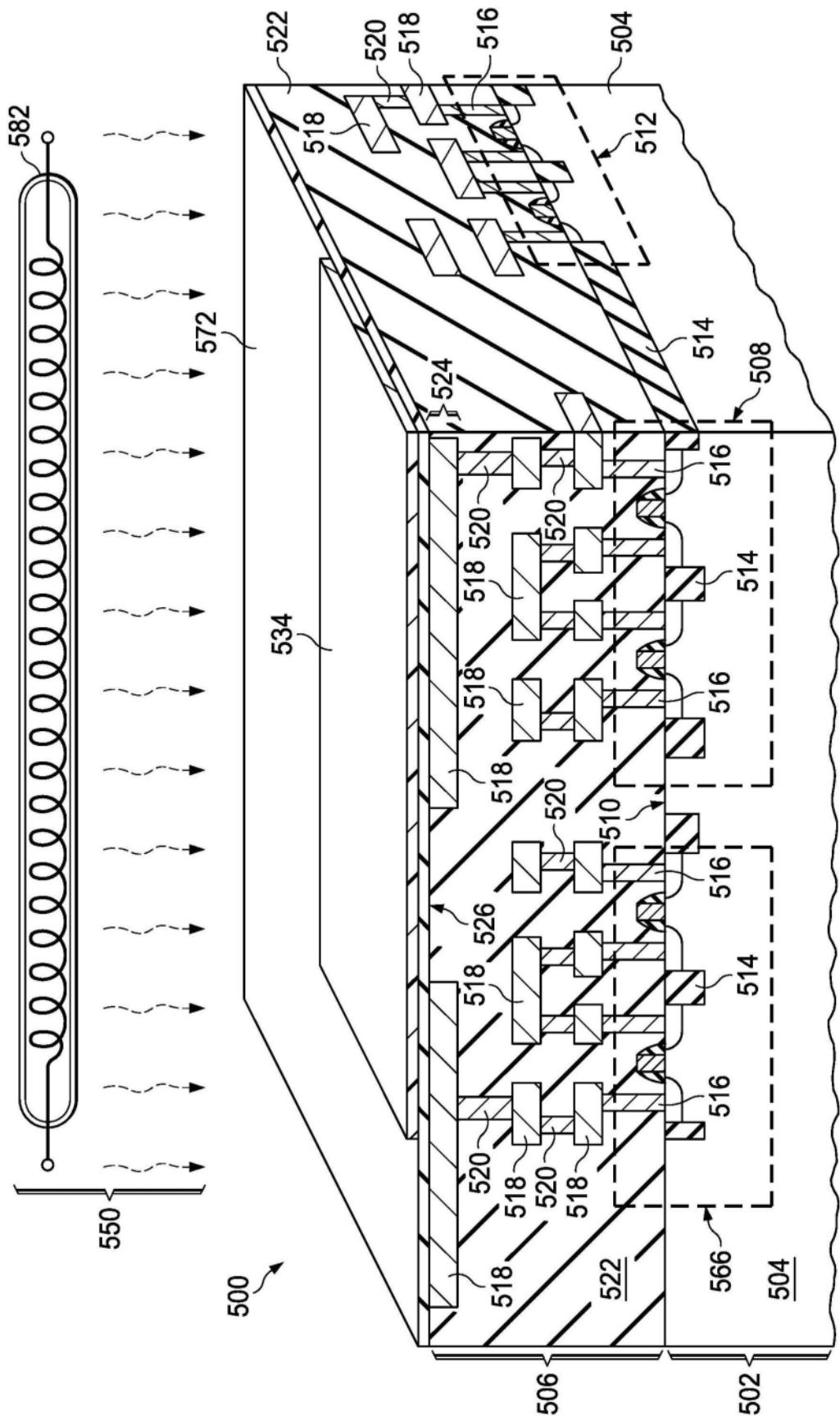

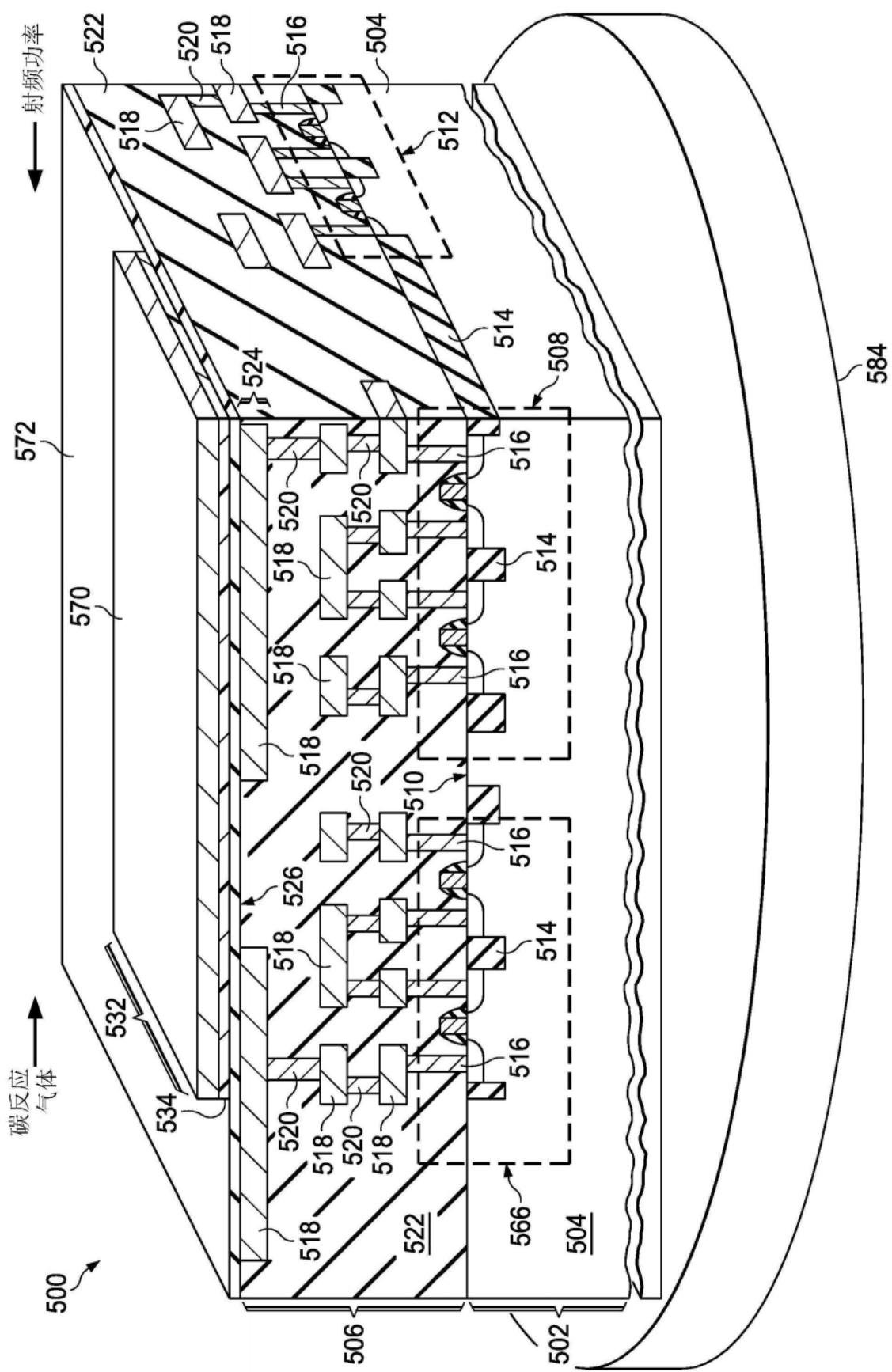

[0041] 图5A到图5D描绘根据实施例的形成具有热路由结构的集成电路的另一实例方法。参考图5A,在包含半导体材料504的衬底502上形成集成电路500。在半导体材料504中接近

衬底502的顶部表面510形成组件(例如生热组件508、热敏组件512及匹配组件566)。可接近衬底502的顶部表面510形成场氧化物514以横向分离组件508、512及566。在衬底502上方形成互连区506。衬底502的顶部表面510也是衬底502与互连区506之间的边界。互连区506可经形成为具有电介质层堆叠522,其中互连元件(例如触点516、互连件518及通孔520)经形成在电介质层堆叠522中,例如参考图2A所描述。在顶部互连层524中安置互连件518的部分,顶部互连层524接近互连区506的顶部表面526延伸。互连区506的顶部表面526位于互连区506中与衬底502与互连区506之间的边界510相对的表面处。

[0042] 形成这个实例的热路由结构可任选地开始于在互连区506的顶部表面526上方形成电介质隔离层572。电介质隔离层572的目的是电隔离导电的热路由结构与顶部互连层524中的互连件518。电介质隔离层572可经形成为在互连区506的整个顶部表面526上方延伸的毯覆层,如图5A中所描绘。替代地,电介质隔离层572可经形成为图案化层,从而覆盖热路由结构的区域。例如,电介质隔离层572可包含二氧化硅、氮化硅或其它无机电介质材料。电介质隔离层572可通过多种方法形成,包含使用原硅酸四乙酯(TEOS)的等离子体增强化学气相沉积(PECVD)工艺。在这个实例的一个版本中,电介质隔离层572的图案化表现形式可使用根据参考图2A到图2F或图3A到图3C所描述的方法的加成工艺由导热率高于下伏电介质材料的非导电纳米颗粒形成。包含导热纳米颗粒的图案化电介质隔离层572将有利地增加热路由结构的总导热率。

[0043] 形成热路由结构以通过加成工艺574在电介质隔离层572上方形成含有包含金属的纳米颗粒的纳米颗粒墨水膜538继续。纳米颗粒可包含参考图4A及图4B所描述的金属,或适合作为后续石墨材料生长的催化剂的其它金属。纳米颗粒墨水膜538经形成在后续形成的热路由结构的区域中,且未经形成在互连区506的整个顶部表面526上方。加成工艺574可包含使用脉冲激光575来将小片纳米颗粒墨水576从纳米颗粒墨水层578转移到集成电路500的直接激光转移工艺。纳米颗粒墨水层578经附接到背衬层580。组合的纳米颗粒墨水层578及背衬层580有时被称为带状物。脉冲激光575、纳米颗粒墨水层578及背衬层580及集成电路500可相对于彼此移动以在所期望区域中形成纳米颗粒墨水膜538。在这个实例的替代版本中,纳米颗粒墨水膜538可通过施配纳米颗粒墨水形成,例如参考图2A到图2F或图3A到图3C所描述。

[0044] 参考图5B,通过烘烤工艺544加热图5A的纳米颗粒墨水膜538以从纳米颗粒墨水膜538移除至少部分挥发性材料,以形成主要包含纳米颗粒的纳米颗粒膜546。烘烤工艺544可为使用白炽灯545的辐射热工艺,如图5B中示意性地指示。烘烤工艺544的其它表现形式是在这个实例的范围内。

[0045] 参考图5C,通过粘结诱导工艺550加热图5B的纳米颗粒膜546使得相邻纳米颗粒彼此粘结,以形成粘结纳米颗粒膜534。粘结诱导工艺550可包含使用白炽灯582的尖峰加热工艺,如图5C中示意性地描绘。尖峰加热工艺加热纳米颗粒膜546达一段时间(例如1毫秒到10毫秒),以有利地限制组件508、512及566的加热。诱导纳米颗粒之间的粘结的其它方法是在这个实例的范围内。

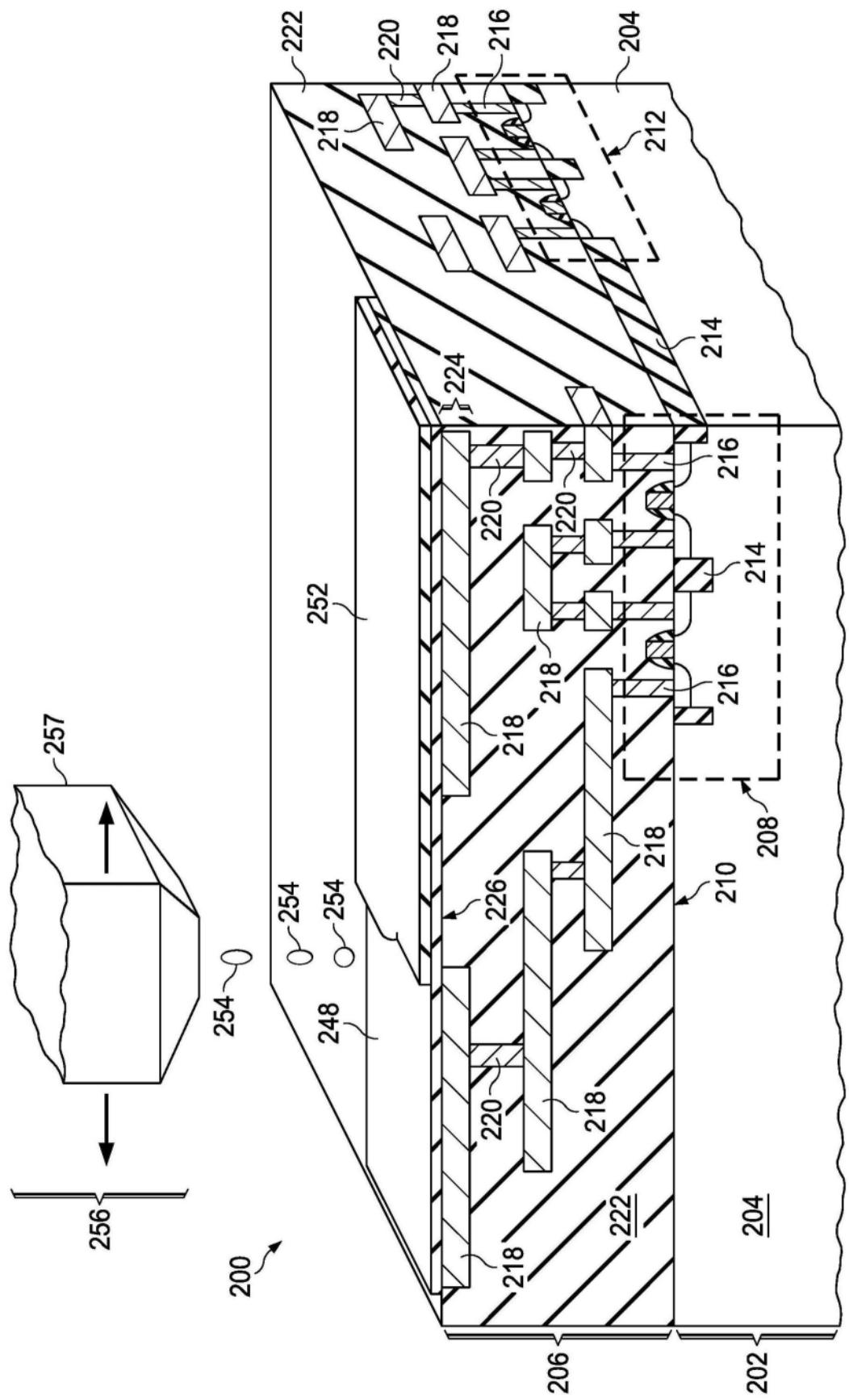

[0046] 参考图5D,通过石墨材料PECVD工艺选择性地在粘结纳米颗粒膜534上形成石墨材料层570。在石墨材料PECVD工艺中,在晶片卡盘584上安置衬底502且通过晶片卡盘584加热衬底502到例如200°C到400°C的温度。图5D中被表示为“碳反应气体”的含碳反应气体在集

成电路500上方流动且图5D中被表示为“射频(RF)电力”的射频电力施加到含碳反应气体以在集成电路500上生成碳资源基。含碳反应气体可包含甲烷、直链烷烃(例如乙烷、丙烷及/或丁烷)、醇(例如乙醇)及/或环烃(例如环丁烷或苯)。额外气体(例如氢气、氩气及/或氧气)也可在集成电路500上方流动。粘结纳米颗粒膜534中的纳米颗粒中的金属催化碳自由基起反应以形成石墨材料,使得选择性地在粘结纳米颗粒膜534上形成石墨材料层570的第一层。选择性地在先前形成的石墨材料层上形成后续石墨材料层,使得选择性地在粘结纳米颗粒534上形成石墨材料层570,且在粘结纳米颗粒膜534外的集成电路500上未形成石墨材料570。组合的粘结纳米颗粒膜534及石墨材料层570提供热路由结构532。

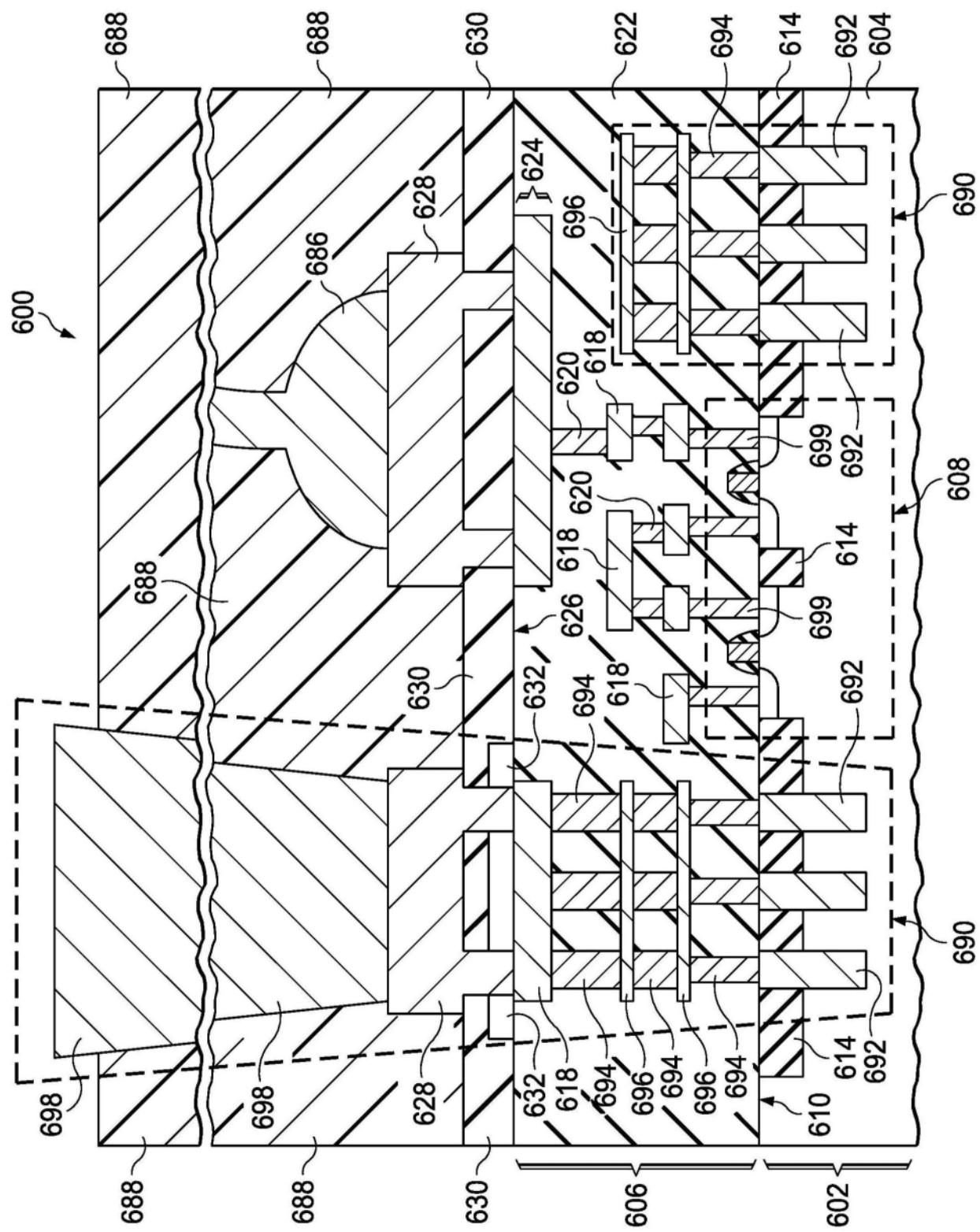

[0047] 图6是根据实施例的包含组合热路由结构的实例集成电路的横截面。集成电路600包含内含半导体材料604的衬底602。集成电路600进一步包含安置在衬底602上的互连区606。组件608在衬底602与互连区606之间的边界610处安置在衬底602及互连区606中。例如,组件608可为MOS晶体管、双极结型晶体管、JFET、电阻器及/或SCR。组件608可在衬底602与互连区606之间的边界610处通过场氧化物614横向分离。互连区606可包含安置在电介质层堆叠622中的触点616、互连件618及通孔620。一些互连件618经安置在顶部互连层624中,顶部互连层624位于互连区606的顶部表面626处。互连区606的顶部表面626经定位成与衬底602与互连区606之间的边界610相对。接合垫结构628经安置在互连区606的顶部表面626上方,且电耦合到顶部互连层624中的互连件618。保护性外涂层630经安置在互连区606的顶部表面626上方。

[0048] 在这个实例中,使用一些接合垫结构628上的引线接合686组装集成电路600。通过囊封在囊封材料688中来封装集成电路600。囊封材料688(例如环氧树脂)经安置在保护性外涂层630及接合垫结构628上方。

[0049] 这个实例的集成电路600包含组合的热路由结构690,热路由结构690从衬底602内部延伸穿过互连区606,且穿过有机聚合物囊封材料688。组合的热路由结构690包含安置在根据本文中的任何实例的顶部互连层624上的热路由结构632。组合的热路由结构690可将由组件608生成的热传导到位于含有集成电路600的封装外的除热设备(例如散热器),这可有利地降低组件608的操作温度。

[0050] 组合的热路由结构690可包含安置在衬底602中且延伸到衬底602与互连区606之间的边界610的深沟槽热路由结构692。深沟槽热路由结构692可环绕组件608的部分且可在图6的平面外的位置处彼此连接。深沟槽热路由结构692可具有第US 15/361,397号专利申请案中所描述的结构且可例如在第US 15/361,397号专利申请案中所描述那样形成。

[0051] 组合的热路由结构690可包含安置在互连区606中的高导热率通孔694。高导热率通孔694可环绕组件608的部分且可在图6的平面外的位置处彼此连接。高导热率通孔694可具有第US 15/361,399号专利申请案中所描述的结构且可例如在第US 15/361,399号专利申请案中所描述那样形成。

[0052] 组合的热路由结构690可包含安置在互连区606中的高导热率横向结构696。高导热率横向结构696可环绕组件608的部分且可在图6的平面外的位置处彼此连接。高导热率横向结构696可具有第US 15/361,394号专利申请案中所描述的结构且可例如在第US 15/361,394号专利申请案中所描述那样形成。

[0053] 组合的热路由结构690可包含贯穿囊封材料688安置到集成电路600的高导热率貫

穿封装导管698。高导热率贯穿封装导管698可具有第US 15/361,403号专利申请案中所描述的结构且可例如在第US 15/361,403号专利申请案中所描述那样形成。

[0054] 集成电路600可进一步包含电耦合到组件608的石墨通孔699。石墨通孔699可传导由组件608生成的热远离衬底,可能到组合的热路由结构690,这有利地降低组件608的操作温度。石墨通孔699可具有第US 15/361,401号专利申请案中所描述的结构且可例如在第US 15/361,401号专利申请案中所描述那样形成。

[0055] 在所描述实施例中修改是可能的,且在权利要求书的范围内其它实施例也是可能的。

图1A

图1B

图4B

图2A

图2B

图2C

图2D

图2E

图2F

图3A

图3B

图3C

图4A

图5A

图5B

图5C

图5D

图6