(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-1709

(P2016-1709A)

(43) 公開日 平成28年1月7日(2016.1.7)

(51) Int.Cl.

H01L 27/146 (2006.01)

F 1

H01L 27/14

A

テーマコード(参考)

4M118

審査請求 未請求 請求項の数 15 O L (全 19 頁)

(21) 出願番号

特願2014-121849 (P2014-121849)

(22) 出願日

平成26年6月12日 (2014.6.12)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置の製造方法

## (57) 【要約】

【課題】画素部のゲート電極膜をパターニングする際にエッチング残渣が発生する可能性を低減する。

【解決手段】画素部および周辺回路部を有する固体撮像装置の製造方法は、前記画素部の第1素子分離および第1活性領域を半導体基板に形成するとともに前記周辺回路部の第2素子分離および第2活性領域を前記半導体基板に形成する工程と、前記第1素子分離、前記第1活性領域、前記第2素子分離および前記第2活性領域を覆うようにゲート電極膜を形成する工程と、前記ゲート電極膜のうち前記画素部に対応する部分の少なくとも一部分に対して選択的にn型不純物を注入する工程と、前記n型不純物を注入する前記工程の後に、前記ゲート電極膜のパターニングを行うことにより前記画素部の第1ゲート電極および前記周辺回路部の第2ゲート電極を形成する工程と、を含み、前記少なくとも一部分は、前記第1素子分離と前記第1活性領域との境界部分の上に位置する部分を含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

画素部および周辺回路部を有する固体撮像装置の製造方法であって、

前記画素部の第1素子分離および第1活性領域を半導体基板に形成するとともに前記周辺回路部の第2素子分離および第2活性領域を前記半導体基板に形成する工程と、

前記第1素子分離、前記第1活性領域、前記第2素子分離および前記第2活性領域を覆うようにゲート電極膜を形成する工程と、

前記ゲート電極膜のうち前記画素部に対応する部分の少なくとも一部分に対して選択的にn型不純物を注入する工程と、

前記n型不純物を注入する前記工程の後に、前記ゲート電極膜のパターニングを行うことにより前記画素部の第1ゲート電極および前記周辺回路部の第2ゲート電極を形成する工程と、を含み、

前記少なくとも一部分は、前記第1素子分離と前記第1活性領域との境界部分の上に位置する部分を含む、

ことを特徴とする固体撮像装置の製造方法。

**【請求項 2】**

前記第1ゲート電極および前記第2ゲート電極を形成する前記工程の後に、前記第2ゲート電極に不純物を注入する工程を更に含む、

ことを特徴とする請求項1に記載の固体撮像装置の製造方法。

**【請求項 3】**

前記第2ゲート電極に不純物を注入する前記工程において、前記第2ゲート電極を含むMOSトランジスタのソースおよびドレインとなるべき領域にも不純物が注入される、

ことを特徴とする請求項2に記載の固体撮像装置の製造方法。

**【請求項 4】**

前記n型不純物を注入する前記工程において、前記ゲート電極膜のうち前記画素部に対応する部分の全域に前記n型不純物が注入される、

ことを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 5】**

前記第1ゲート電極および前記第2ゲート電極を形成する前記工程の後に、前記第1ゲート電極および前記第2ゲート電極が形成された前記半導体基板を覆う絶縁膜を形成する工程と、

前記絶縁膜のうち前記画素部に対応する部分、および、前記第2ゲート電極の側面にサイドスペーサを構成する部分が残るように前記絶縁膜をエッチングする工程と、

前記絶縁膜をエッチングする前記工程の後に、前記第2ゲート電極を含むMOSトランジスタのソースおよびドレインとなるべき領域に不純物を注入する工程と、

を更に含むことを特徴とする請求項1乃至4のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 6】**

前記第2ゲート電極を含むMOSトランジスタのソースおよびドレインとなるべき領域に不純物を注入する前記工程では、前記第1ゲート電極、および、前記半導体基板のうち前記画素部に対応する部分には不純物が注入されない、

ことを特徴とする請求項5に記載の固体撮像装置の製造方法。

**【請求項 7】**

前記画素部は、複数の第1ゲート電極を有し、

前記少なくとも一部分は、前記画素部の前記複数の第1ゲート電極の少なくとも1つの第1ゲート電極となるべき部分の少なくとも一部を更に含む、

ことを特徴とする請求項1乃至6のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 8】**

前記少なくとも1つの第1ゲート電極は、増幅MOSトランジスタのゲート電極を含む、

10

20

30

40

50

ことを特徴とする請求項 7 に記載の固体撮像装置の製造方法。

**【請求項 9】**

前記ゲート電極膜を形成する工程では、前記ゲート電極膜としてノンドープの半導体膜を形成する、

ことを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 10】**

前記第 1 素子分離および前記第 2 素子分離は、S T I ( S h a l l o w T r e n c h I s o l a t i o n ) である、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 11】**

前記ゲート電極膜を形成する工程の前に、前記画素部の第 1 ゲート絶縁膜および前記周辺回路部の第 2 ゲート絶縁膜を形成する工程を含み、

前記第 1 ゲート絶縁膜は、前記第 2 ゲート絶縁膜より厚い、

ことを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 12】**

前記画素部のM O S トランジスタは、シングルドレイン構造を有し、前記周辺回路部のM O S トランジスタは、L D D 構造 ( L i g h t l y D o p e d D r a i n ) 構造を有する、

ことを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 13】**

前記周辺回路部のM O S トランジスタは、金属半導体化合物層を有し、前記画素部のM O S トランジスタは、前記金属半導体化合物層と同じ金属成分を含む金属半導体化合物層を有しない、

ことを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 14】**

前記周辺回路部は、抵抗素子を含み、

前記n型不純物を注入する前記工程において、前記抵抗素子となるべき部分にも前記n型不純物が注入される、

ことを特徴とする請求項 1 乃至 13 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【請求項 15】**

前記ゲート電極膜のうち前記第 1 素子分離と前記第 1 活性領域との境界部分の上に位置する部分とは異なる部分にp型不純物を注入する工程を更に含む、

ことを特徴とする請求項 1 乃至 14 のいずれか 1 項に記載の固体撮像装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、固体撮像装置の製造方法に関する。

**【背景技術】**

**【0 0 0 2】**

固体撮像装置の画素数の増大に伴って、光電変換素子のみならず、画素部および周辺回路部に配置されたM O S トランジスタの微細化も必要とされる。光電変換素子やM O S トランジスタ等の素子が微細化されると、それに伴って素子を形成する活性領域、および活性領域を分離する素子分離にも微細化が要求される。微細な素子分離としては、S T I ( S h a l l o w T r e n c h I s o l a t i o n ) が有利である。

**【0 0 0 3】**

また、画素の微細化が進行した場合においても光電変換素子の感度を確保するために、光電変換素子の占める面積比率を高くするレイアウトが求められる。そのような要求の下で、多数の光電変換素子が周期的パターンとして配置される画素部においては、周辺回路部と比較して、活性領域の占める比率が高くなる傾向にある。画素部と周辺回路部における活性領域の占有率の差異は、活性領域と素子分離との段差を解消する平坦化工程に影

10

20

30

40

50

響を及ぼしうる。具体的には、素子分離が活性領域の基準面に対して上側に突き出る量は、周辺回路部よりも画素部の方が大きくなりうる。ここで、活性領域の基準面に対して素子分離が上側に突き出た量（高さ）を突き出し量と定義する。

#### 【0004】

画素部と周辺回路部との間の突き出し量の差を低減するために、素子分離のためのトレンチを埋めた絶縁膜を平坦化する前に活性領域の絶縁膜の一部をエッティングによって除去するプリエッチと呼ばれる手法が知られている。このプリエッチ工程を追加することで、活性領域と素子分離との面積占有率が異なるパターンが混在する場合においても、平坦化後の段差を低減することができる。

#### 【0005】

更に、活性領域上にプリエッチによって形成される開口の端と素子分離の端との距離を周辺回路部よりも画素部で小さくすることで、画素部と周辺回路部における平坦化後の突き出し量の差を低減する技術が提案されている（特許文献1参照）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

#### 【特許文献1】特開2009-117681号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

ところが、画素の微細化が進行するにつれて、画素部の活性領域の寸法も小さくなる。画素部の活性領域の寸法が小さくなると、活性領域上の絶縁膜のプリエッチによるパターニングが難しくなる。また、プリエッチによるパターニングが仮に可能であるとしても、プリエッチによって形成される開口の端と素子分離の端との距離を制御する手法には限界がある。例えば、プリエッチによって、素子分離として残すべき部分までもエッティングされると、素子分離において意図しないリークが発生する可能性がある。したがって、加工寸法のばらつきやパターン形成時の位置ずれなどの制約を考慮した上でプリエッチパターン（開口パターン）と活性領域との位置関係を定めるルールを決定する必要がある。このように、画素の微細化が進行すると、プリエッチパターンの配置に制約を受けることが多くなるため、平坦化後の画素部と周辺回路部の素子分離の突き出し量の差異を十分に低減することは難しくなる。

#### 【0008】

画素部での突き出し量が周辺回路部での突き出し量よりも大きくなつた場合の問題点として、ゲート電極膜のエッティング工程におけるエッティング残渣が発生しうることが挙げられる。特にゲート電極膜の形成前に段差が大きい部分（すなわち画素部内の活性領域と素子分離との境界部分）においてエッティング残渣が発生する可能性がある。

#### 【0009】

本発明は、上記の課題認識を契機としてなされたものであり、画素部のゲート電極膜をパターニングする際にエッティング残渣が発生する可能性を低減するために有利な技術を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明の1つの側面は、画素部および周辺回路部を有する固体撮像装置の製造方法に係り、前記製造方法は、前記画素部の第1素子分離および第1活性領域を半導体基板に形成するとともに前記周辺回路部の第2素子分離および第2活性領域を前記半導体基板に形成する工程と、前記第1素子分離、前記第1活性領域、前記第2素子分離および前記第2活性領域を覆うようにゲート電極膜を形成する工程と、前記ゲート電極膜のうち前記画素部に対応する部分の少なくとも一部分に対して選択的にn型不純物を注入する工程と、前記n型不純物を注入する前記工程の後に、前記ゲート電極膜のパターニングを行うことにより前記画素部の第1ゲート電極および前記周辺回路部の第2ゲート電極を形成する工程と

10

20

30

40

50

、を含み、前記少なくとも一部分は、前記第1素子分離と前記第1活性領域との境界部分の上に位置する部分を含む。

**【発明の効果】**

**【0011】**

本発明によれば、画素部のゲート電極膜をパターニングする際にエッチング残渣が発生する可能性を低減するために有利な技術が提供される。

**【図面の簡単な説明】**

**【0012】**

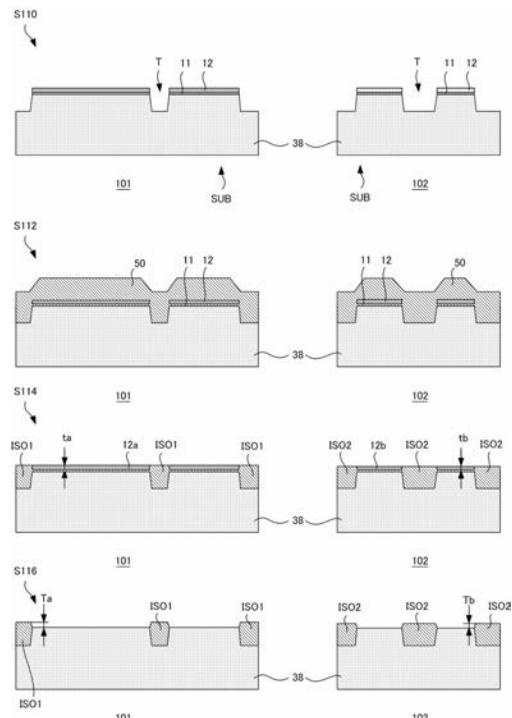

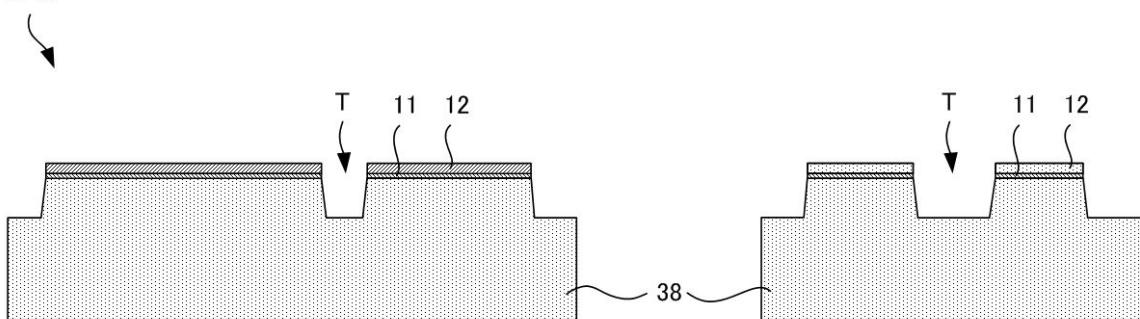

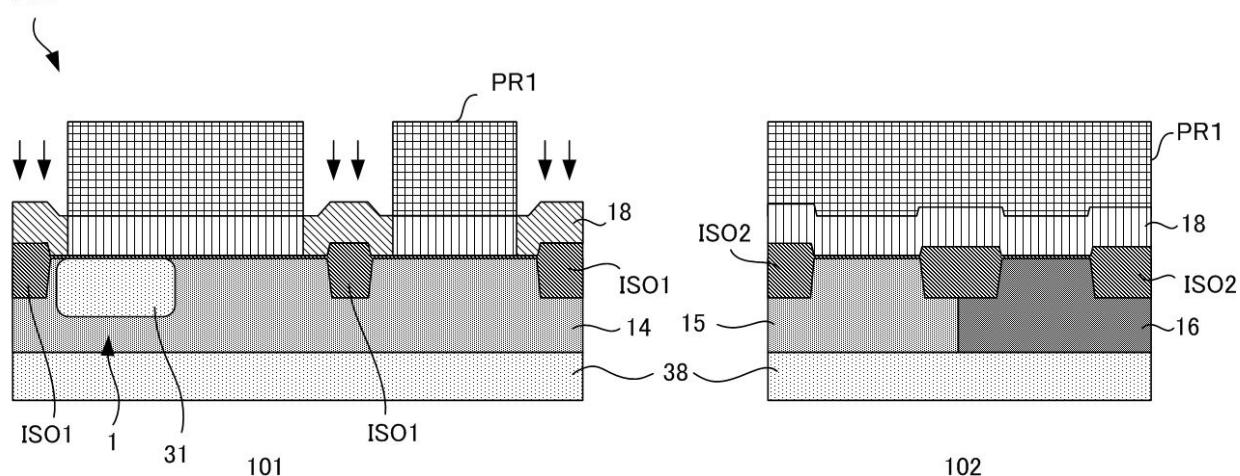

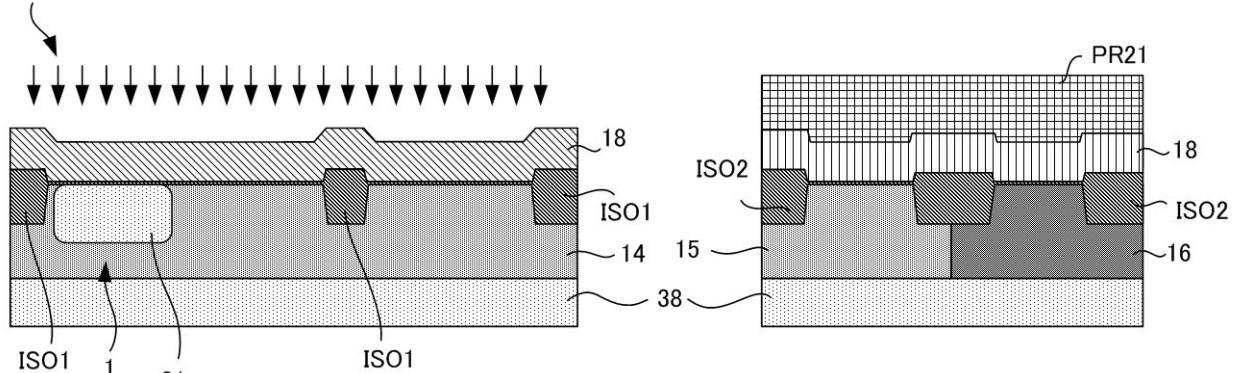

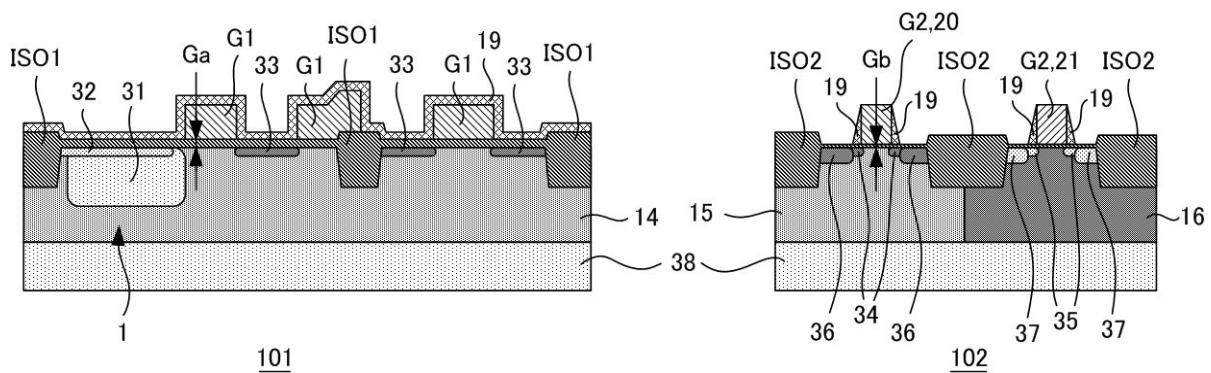

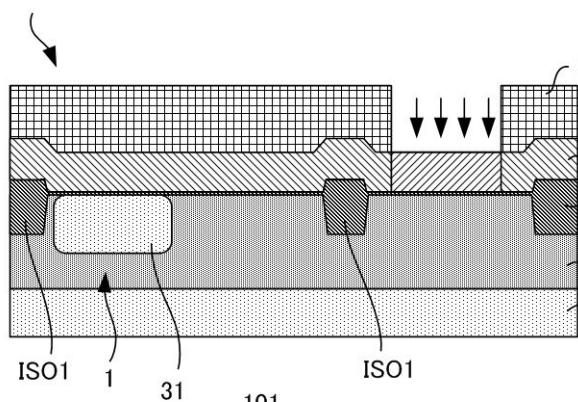

【図1】本発明の第1実施形態の固体撮像装置の製造方法を示す図。

10

【図2】本発明の第1実施形態の固体撮像装置の製造方法を示す図。

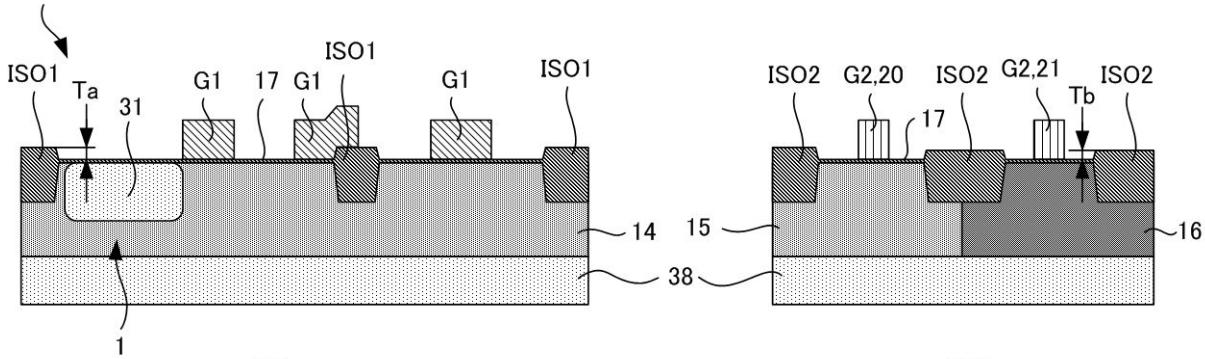

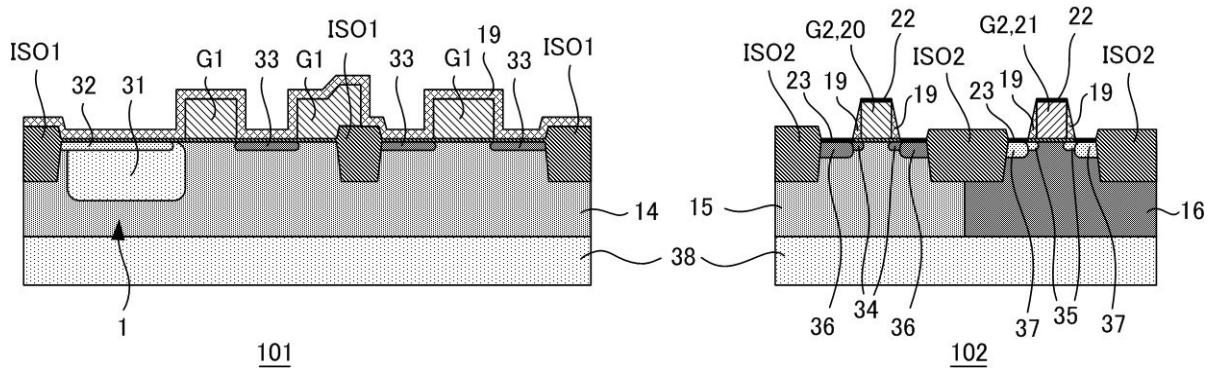

【図3】本発明の第2実施形態の固体撮像装置の製造方法を示す図。

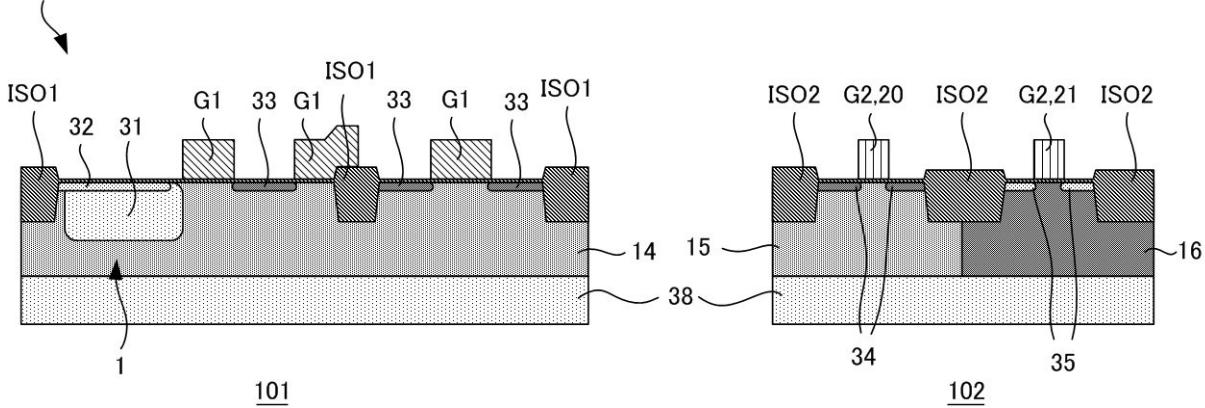

【図4】本発明の第2実施形態の固体撮像装置の製造方法を示す図。

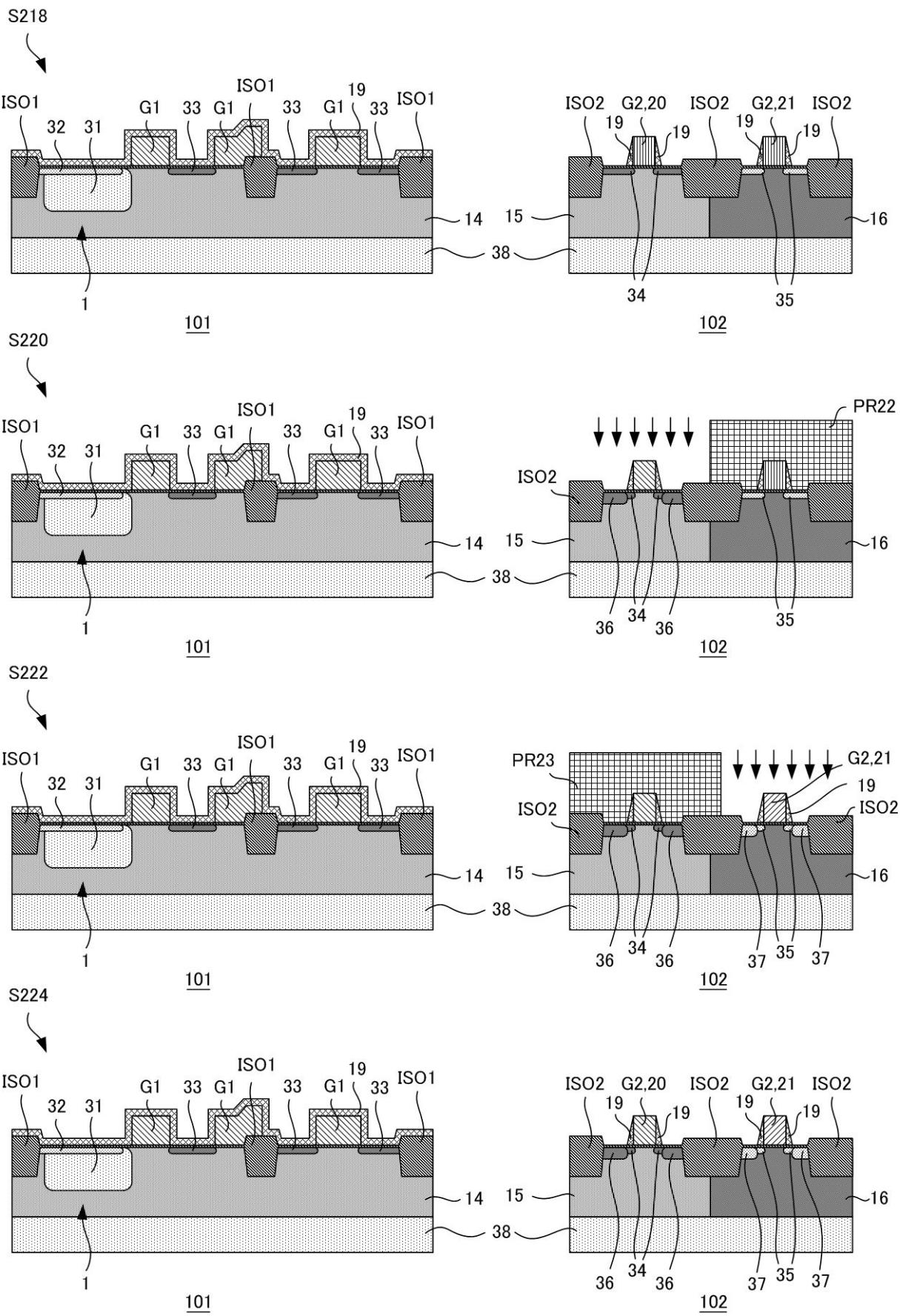

【図5】本発明の第3実施形態の固体撮像装置の製造方法を示す図。

【図6】本発明の第4実施形態の固体撮像装置の製造方法を示す図。

【図7】本発明の第5実施形態の固体撮像装置の製造方法を示す図。

**【発明を実施するための形態】**

**【0013】**

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。

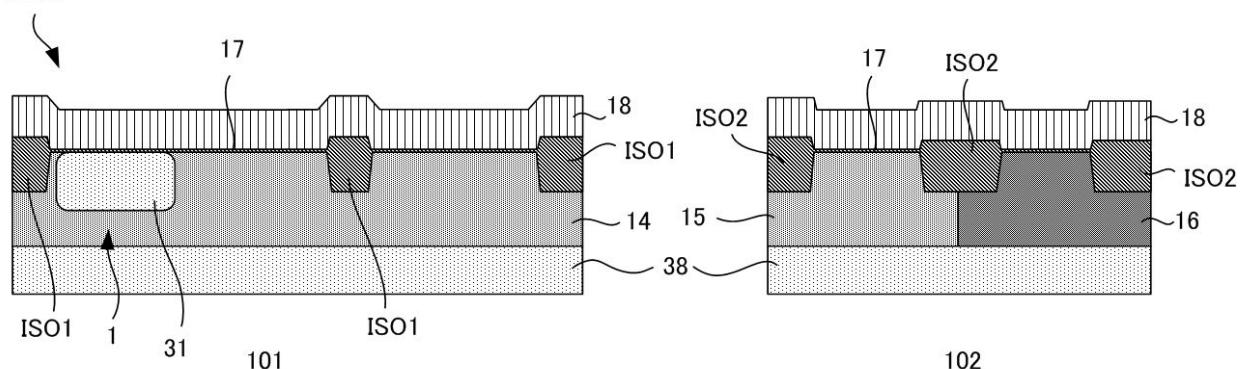

**【0014】**

図1、2を参照しながら本発明の第1実施形態の固体撮像装置の製造方法を説明する。固体撮像装置は、複数の画素が配列された画素部101と、画素部101の周辺に配置された周辺回路部102とを含む。各画素は、1又は複数の光電変換素子1、フローティングディフュージョンおよび1又は複数のMOSトランジスタを含みうる。

20

**【0015】**

各画素の1又は複数のMOSトランジスタは、例えば、光電変換素子1で発生し蓄積された電荷をフローティングディフュージョンに転送する転送MOSトランジスタを含みうる。画素部において、複数の画素は、複数行および複数列を構成するように配列されうる。画素部101は、フローティングディフュージョンで電位に応じた信号、即ち、フローティングディフュージョンに転送された電荷の量に応じた信号を出力する増幅MOSトランジスタを含みうる。増幅MOSトランジスタは、各画素に備えられてもよいし、複数の画素によって共有されてもよい。

30

**【0016】**

周辺回路部102は、例えば、画素部の各から信号を読み出すための読出回路を含みうる。読出回路は、例えば、画素部における行を選択する行選択部、画素部における列を選択する列選択部、画素部の画素からの信号を処理する処理部などを含みうる。

**【0017】**

図1、2において、画素部101は、製造途中の固体撮像装置における画素部の一部を模式的に示す部分であり、周辺回路部102は、製造途中の固体撮像装置における周辺回路部の一部を模式的に示す部分である。なお、以降の説明において、「基板」は、半導体基板SUBを含む構造体、例えば、半導体基板SUBとその上に形成された膜とを含む構造体を意味する。

40

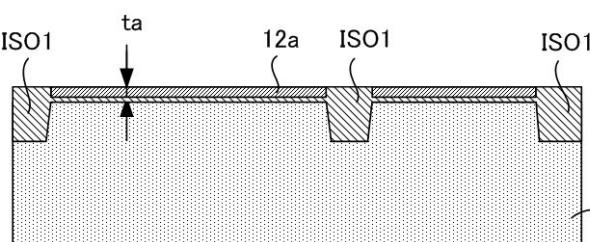

**【0018】**

工程S110-S116では、画素部101の第1素子分離ISO1および第1活性領域ACT1が半導体基板SUBに形成されるとともに周辺回路部102の第2素子分離ISO2および第2活性領域ACT2が半導体基板SUBに形成される。

**【0019】**

まず、工程S110では、n型エピタキシャル層38を表面に有する半導体基板SUBを準備し、n型エピタキシャル層38の表面に酸化シリコン膜11と窒化シリコン膜12とを形成する。ここで、酸化シリコン膜11と窒化シリコン膜12との間にバッファ層としてポリシリコン膜が形成されてもよい。その後、窒化シリコン膜12の上にフォトレジ

50

ストパターンを形成し、該フォトレジストパターンの開口を通して窒化シリコン膜12、酸化シリコン膜11およびn型エピタキシャル層38をエッチングし、n型エピタキシャル層38にトレンチTを形成する。

#### 【0020】

工程S112では、トレンチTに露出しているn型エピタキシャル層38の表面を酸化させた後、高密度プラズマCVD法などの方法によってトレンチTを酸化シリコン50で埋める。このとき、窒化シリコン膜12の上にも酸化シリコン50の膜が形成され、基板の表面には凹凸が形成される。トレンチTを酸化シリコン50で埋める前に、画素部101における暗電流を抑制するために、トレンチTにボロンなどのp型不純物層を注入してもよい。

10

#### 【0021】

工程S114では、酸化シリコン50のうち余分な部分を除去するとともに基板の表面を平坦化するために平坦化処理を実施する。これにより、画素部101には第1素子分離ISO1が形成され、周辺回路部102には第2素子分離ISO2が形成される。第1、第2素子分離ISO1、ISO2は、STI(Shallow Trench Isolation)で構成されうる。ここで、平坦化処理は、CMP工程を含みうるが、該CMP工程の前に前述のプリエッチング工程(活性領域上の酸化シリコン50をエッチングして開口を形成する工程)を含んでもよい。ただし、一般的な固体撮像装置は、画素部における活性領域密度は、周辺回路部における活性領域密度よりも大きく、仮にプリエッチング工程を適用したとしても画素部の平坦化処理にかかる負荷は、周辺回路部よりも大きくなる。これは、前述のように、プリエッチによって形成される開口の端と素子分離の端との間に十分な距離を確保する必要があるために、該開口を十分に大きくすることができないからである。

20

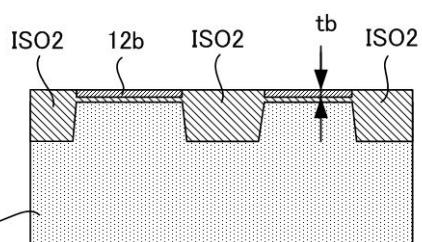

#### 【0022】

CMP工程による平坦化処理は、活性領域に存在する窒化シリコン膜12をストップとして用いて停止されうる。平坦化処理により、画素部101よりも平坦化処理の負荷が小さい周辺回路部102の一部の領域における窒化シリコン膜12bは、画素部101の窒化シリコン膜12aよりも薄くなりうる。図1において、taは平坦化処理後に残存した画素部101における窒化シリコン膜12aの厚さ、tbは平坦化処理後に残存した周辺回路部102の一部の領域における窒化シリコン膜12bの厚さを示している。ここで、上述したようにta > tbの関係が成り立ちうるが、周辺回路部102においても局所的に活性領域密度のばらつきがあるので、周辺回路部102の全域においてta > tbが常に成立するわけではない。

30

#### 【0023】

工程S116では、活性領域に存在する窒化シリコン膜12a、12bをリン酸などの薬液によるウェットプロセスを用いて除去する。また、酸化シリコン膜11もフッ化水素酸などの薬液を用いて除去してもよい。ここで、窒化シリコン膜12a、12bを除去するためのリン酸などの薬液は、酸化シリコンのエッチングレートが窒化シリコンのエッチングレートよりも小さい。よって、第1素子分離ISO1および第2素子分離ISO2は、第1活性領域ACT1および第2活性領域ACT2に対して上側に突き出すように形成される。画素部101における第1活性領域ACT1に対する第1素子分離ISO1の突き出し量をTa、周辺回路部102における第2活性領域ACT2に対する第2素子分離ISO2の突き出し量をTbとすると、Ta > Tbの関係が成り立つ。これは、平坦化処理後に残存した窒化シリコン膜12a、12bの厚さが、素子分離ISO1、ISO2における酸化シリコン50の突き出し量に影響を及ぼすためである。ここで、図1では、Ta、Tbとも正となるように図示されているが、どちらか一方が負となっても構わないし、両方が負の値となっても構わない。

40

#### 【0024】

また、上述したように、周辺回路部102においても局所的に活性領域の密度にばらつきがあるため、周辺回路部の全域においてTa > Tbの関係式が常に成立するわけではな

50

い。ただし、通常の固体撮像装置においては、活性領域に対する素子分離の平均的な突き出し量は、周辺回路部 102 よりも画素部 101 の方が大きくなる構成が一般的である。また、固体撮像装置の特性の観点においても、画素部 101 における突き出し量が小さい方向へシフトすると、白キズや暗電流が増加する傾向が見られる場合があり、周辺回路部 102 よりも画素部 101 の突き出し量を大きく制御することが好ましい。

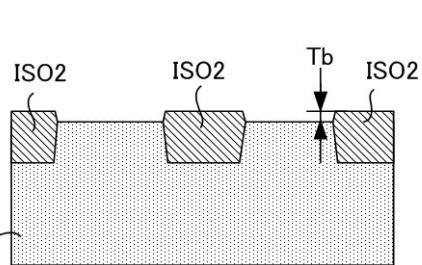

#### 【0025】

工程 S118 では、画素部 101 の p 型ウェル領域 14、周辺回路部 102 の p 型ウェル領域 15、周辺回路部 102 の n 型ウェル領域 16、および、画素部 101 の光電変換素子 1 を構成する n 型の半導体領域（電荷蓄積領域）31 を形成する。工程 S118 ではまた、ゲート絶縁膜 17 を形成して、その後にゲート電極膜 18 を成膜する。ゲート電極膜 18 は、MOS トランジスタのゲート電極の主成分を含む膜である。ゲート電極の主成分は、例えば、シリコンまたはゲルマニウムなどの半導体材料であり、ゲート電極膜 18 は、当該半導体材料からなる膜、すなわち半導体膜である。あるいは、ゲート電極膜 18 は、シリコンとゲルマニウムの双方を含む SiGe であってもよい。なお、ゲート電極には半導体としての機能よりもむしろ導電体としての機能が求められるため、その母材となるゲート電極膜 18 は、ゲート電極膜 18 は絶縁体でなければ、半導体であってもよい導電体であってもよい。つまり、ゲート電極膜 18 は非絶縁体である。成膜直後のゲート電極膜 18 は、例えば、不可避の不純物を除いては機能的な不純物を含まない、ノンドープの半導体膜でありうる。ただし、以下に説明するように、ゲート電極膜 18 の加工時にゲート電極膜 18 の部分に応じてエッチングレートを異ならせることが可能であれば、成膜直後のゲート電極膜 18 は不純物を含んでいてもよい。また、ゲート電極膜 18 は、多結晶膜または非晶質膜でありうる。より具体的には、ゲート電極膜 18 は、ノンドープのポリシリコン膜、または、ノンドープのアモルファスシリコン膜でありうる。

10

20

30

#### 【0026】

工程 S120 では、フォトレジストパターン PR1 を形成する。フォトレジストパターン PR1 は、画素部 101 に対応する部分の少なくとも一部分に開口を有する。該少なくとも一部分は、第 1 素子分離 ISO1 と第 1 活性領域 ACT1 との境界部分の上に位置する部分、あるいは、第 1 素子分離 ISO1 の全域およびその周辺をカバーする領域を含みうる。該少なくとも一部分は、画素部 101 の複数の第 1 ゲート電極のうち少なくとも 1 つの第 1 ゲート電極（例えば、増幅 MOS トランジスタのゲート電極）となるべき部分の少なくとも一部を含んでもよい。

30

#### 【0027】

ここで、フォトレジストパターン PR1 は、周辺回路部 102 の全域をカバーする。即ち、フォトレジストパターン PR1 は、周辺回路部 102 には開口を有しない。なお、良く知られているように、フォトレジストパターン PR1 の形成工程は、フォトレジスト膜の形成工程、露光工程、現像工程を含みうる。

#### 【0028】

工程 S120 では、更に、フォトレジストパターン PR1 の開口を通してゲート電極膜 18 に n 型不純物を注入する。つまり、工程 S120 では、ゲート電極膜 18 のうち画素部 101 に対応する部分の少なくとも一部分に n 型不純物を注入する。工程 S120 でフォトレジストパターン PR1 の開口を通して注入する n 型不純物は、例えば、リンまたはヒ素を含みうる。ここで、周辺回路部 102 は、抵抗素子を含んでもよく、工程 S120 における n 型不純物の注入工程では、周辺回路部 102 の抵抗素子となるべき部分など、周辺回路部 102 の一部にも n 型不純物が注入されてもよい。n 型不純物の注入工程の後に、フォトレジストパターン PR1 は除去される。

40

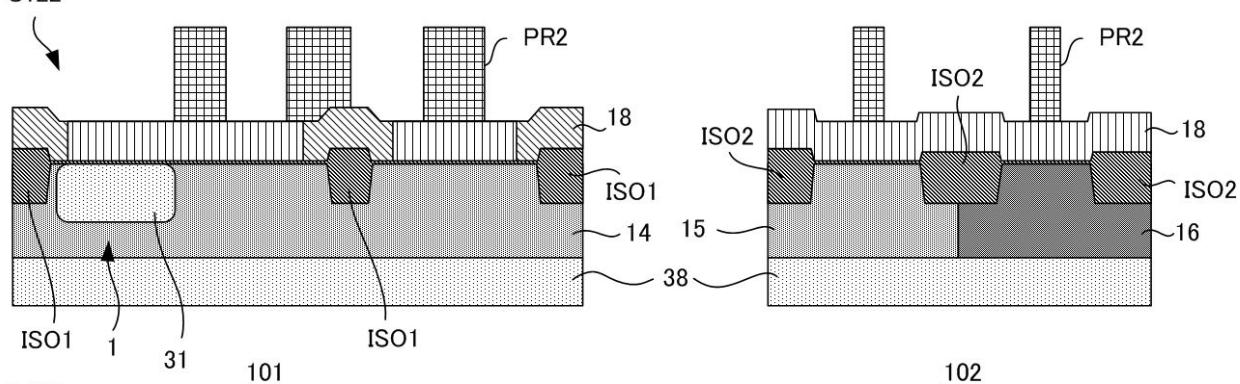

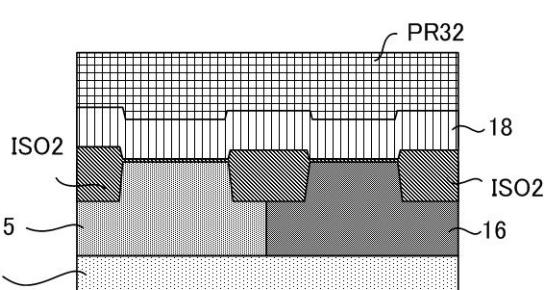

#### 【0029】

工程 S122 では、ゲート電極膜 18 をパターニングするためのフォトレジストパターン PR2 を形成する。そして、フォトレジストパターン PR2 の開口を通してゲート電極膜 18 をエッチングすることによってゲート電極膜 18 をパターニングし、画素部の第 1 ゲート電極 G1 および周辺回路部の第 2 ゲート電極 G2 を形成する。図 2 に示された例で

50

は、画素部 101 の複数の第 1 ゲート電極 G1 のうち増幅 MOS ランジスタのゲート電極の少なくとも一部にも、工程 S120 において n 型不純物が注入されている。

#### 【0030】

ゲート電極膜 18 のパターニングによるゲート電極 G1、G2 の形成については、以下の(1)、(2)、(3)を満たすことが求められる。

(1) ゲート電極膜 18 の下にあるゲート絶縁膜 17 とのエッチング選択比を確保してゲート絶縁膜 17 でエッチングをストップさせること。

(2) ゲート電極 G1、G2 を目標寸法範囲内に制御すること。

(3) ゲート電極膜 18 のエッチング残渣が発生しやすい活性領域と素子分離の境界部分においてエッチング残渣が発生しないこと。

10

#### 【0031】

ここで、画素部 101 は素子分離の突き出し量が周辺回路と比較して大きくなる傾向にある。したがって、(1)、(2)、(3)の中でも、画素部 101 の活性領域と素子分離との境界部分 200 においてゲート電極膜 18 のパターニング(エッチング)時のエッチング残渣を抑制することは非常に重要である。また、固体撮像装置の中の面積比率として、通常は画素部 101 が周辺回路部 102 よりも大きいため、画素部 101 にゲート電極膜 18 の残渣が発生すれば、歩留まりを低下させる可能性が高くなる。特に、量産時に安定的に高い歩留まりを確保する観点においては、素子分離の突き出し量が多少ばらついたとしても、ゲート電極膜のパターニング時のエッチング残渣マージンを確保する事は非常に重要である。

20

#### 【0032】

ポリシリコンのエッチングにおいては、ポリシリコンの伝導帯中の電子がエッチングを促進するために、ノンドープ(i型)ポリシリコンよりも n 型ポリシリコンのエッチング速度が速い。また、n 型不純物の注入量を増加させることによってエッチングレートを高くすることができる。本実施形態では、工程 S120 において、ゲート電極膜 18 のうち画素部の活性領域と素子分離との境界部分 200 に n 型不純物が注入される。これにより、エッチング残渣が発生しやすい境界部分 200 のエッチングレートを画素部の全体の平均的なエッチングレートよりも高くすることができます。これによって境界部分 200 におけるエッチング残渣の発生の可能性を低減することができる。

30

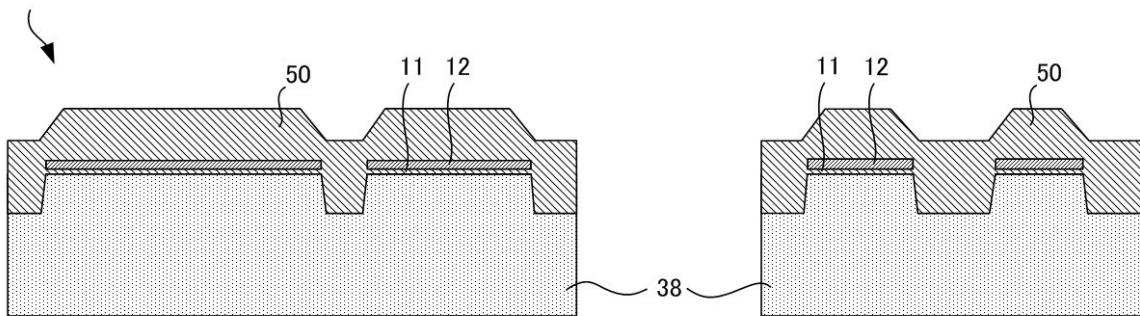

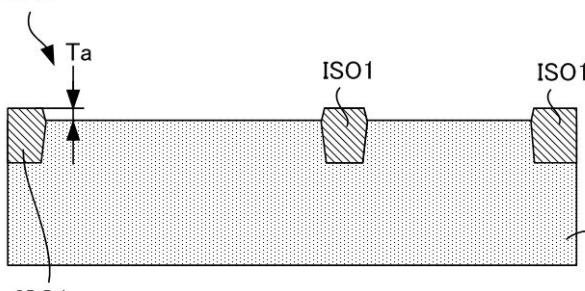

#### 【0033】

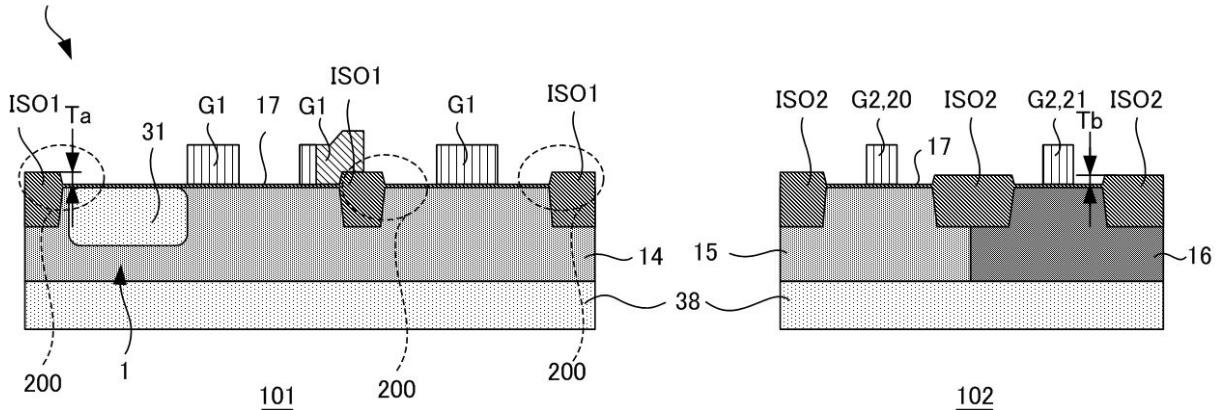

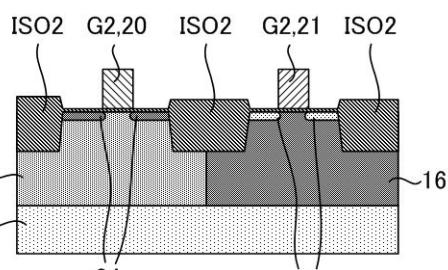

図 3、図 4 を参照しながら本発明の第 2 実施形態の固体撮像装置の製造方法を説明する。なお、第 2 実施形態として言及しない事項は、第 1 実施形態に従う。まず、第 1 実施形態における工程 S110～116 と同様の工程が実施され、その後に、工程 S210 が実施される。工程 S210 は、第 1 実施形態における工程 S118 と同様の構成である。

#### 【0034】

工程 S212 では、フォトレジストパターン PR21 を形成する。フォトレジストパターン PR2 は、画素部 101 に対応する部分に開口を有し、周辺回路部 102 を覆う。工程 S212 では、更に、フォトレジストパターン PR21 の開口を通してゲート電極膜 18 に n 型不純物を注入する。つまり、工程 S212 では、ゲート電極膜 18 のうち画素部 101 に対応する部分の全域に n 型不純物を注入する。

40

#### 【0035】

工程 S214 では、ゲート電極膜 18 をパターニングするためのフォトレジストパターン(不図示)を形成する。そして、該フォトレジストパターンの開口を通してゲート電極膜 18 をエッチングすることによってゲート電極膜 18 をパターニングし、画素部 101 の第 1 ゲート電極 G1 および周辺回路部 102 の第 2 ゲート電極 G2 を形成する。ここで、ゲート電極膜 18 のエッチング前にゲート電極膜 18 のうち画素部 101 の全域に n 型不純物を注入することにより、ゲート電極膜 18 のパターニング時にエッチング残渣が発生する可能性を低減することができる。

#### 【0036】

50

本実施形態では、画素部 101 の n 型の半導体領域 31 は、電子を蓄積する電荷蓄積領域を構成する。つまり、画素部 101 の光電変換素子 1 は、電子蓄積型である。電子蓄積型の固体撮像装置では、画素部 101 の MOS トランジスタとして NMOS トランジスタが採用されうる。本実施形態では、ゲート電極膜 18 のうち画素部 101 の全域に n 型不純物を注入することにより、画素部 101 の NMOS トランジスタの第 1 ゲート電極 G1 を n 型にすることができる。

#### 【0037】

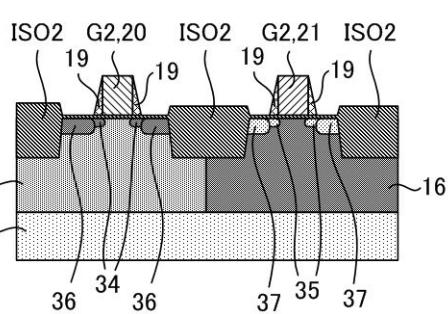

工程 S216 では、光電変換素子 1 を埋め込み型とするために、n 型の半導体領域 31 (半導体基板 SUB) の表面部分に p 型の不純物を注入し、p 型の不純物層 32 を形成する。また、工程 S216 では、画素部 101 の MOS トランジスタのソースおよびドレインを形成すべき領域に n 型の不純物を注入し、n 型の不純物領域 33 を形成する。n 型の不純物領域 33 は、シングルドレイン構造を有する。また、工程 S216 では、周辺回路部 102 の LDD (Lightly Doped Drain) 構造を有する NMOS トランジスタのソースおよびドレインの LDD 領域として n 型の不純物拡散領域 34 を形成する。また、工程 S216 では、周辺回路部の LDD 構造を有する PMOS トランジスタのソースおよびドレインの LDD 領域として p 型の不純物拡散領域 35 を形成する。

#### 【0038】

工程 S218 では、第 1 ゲート電極 G1 および第 2 ゲート電極 G2 が形成された半導体基板 SUB を覆う絶縁膜 19 を形成する。工程 S218 では、次いで、絶縁膜 19 のうち画素部 101 に対応する部分、および、第 2 ゲート電極 G2 の側面にサイドスペーサを構成する部分が残るように絶縁膜 19 をエッチングする。絶縁膜 19 は、例えば、単層の酸化シリコン膜で構成される。あるいは、絶縁膜 19 は、窒化シリコン層または酸窒化シリコン層と、酸化シリコン層と、の 2 層構造を有する。あるいは、絶縁膜 19 は、酸化シリコン層と、窒化シリコン層または酸窒化シリコン層と、酸化シリコン層と、の 3 層構造を有する。絶縁膜 19 を窒化シリコン層または酸窒化シリコン層を有する積層構造にして、絶縁膜 19 を光電変換素子 1 上の反射防止膜として機能させることができる。

#### 【0039】

工程 S220 では、周辺回路部 102 の PMOS トランジスタ領域を覆い、周辺回路部 102 の NMOS トランジスタ領域および画素部 101 に開口を有するフォトレジストパターン PR22 を形成する。そして、該開口を通して NMOS トランジスタ領域にリンまたはヒ素などの n 型不純物を高濃度で注入することで、n 型のゲート電極 20 (第 2 ゲート電極 G2) と、n 型のソースおよびドレイン 36 を形成する。ここで、画素部 101 の半導体基板 SUB および第 1 ゲート電極 G1 は絶縁膜 19 によって覆われているので、画素部 101 の半導体基板 SUB および第 1 ゲート電極 G1 には、n 型不純物が注入されない。

#### 【0040】

工程 S222 では、周辺回路部 102 の NMOS トランジスタ領域を覆い、周辺回路部 102 の PMOS トランジスタ領域および画素部 101 に開口を有するフォトレジストパターン PR23 を形成する。そして、該開口を通して PMOS トランジスタ領域にボロンなどの p 型不純物を高濃度で注入することで、p 型のゲート電極 21 (第 2 ゲート電極 G2) と、p 型のソースおよびドレイン 37 を形成する。ここで、画素部 101 の半導体基板 SUB および第 1 ゲート電極 G1 は絶縁膜 19 によって覆われているので、画素部 101 の半導体基板 SUB および第 1 ゲート電極 G1 には、p 型不純物が注入されない。

#### 【0041】

以上の方法により、NMOS トランジスタは n 型のゲート電極 20 を有し、PMOS トランジスタは p 型のゲート電極 21 を有する、いわゆるデュアルゲート電極が形成される。

#### 【0042】

本実施形態では、n 型不純物の注入の後に p 型不純物の注入を行うが、この順番には制約はなく、入れ替え可能である。また、本実施形態では、周辺回路部のゲート電極に不純

10

20

30

40

50

物を注入する工程と、ソースおよびドレインを形成すべき領域に不純物を注入する工程とを兼用しているが、これらの工程を別個に実施してもよい。この場合、別個の工程において、注入エネルギーおよびドーズ量を自由に決定することができる。

#### 【0043】

工程S222およびS224の後に、高濃度の不純物注入によって生じた結晶欠陥の回復と、注入した高濃度不純物の活性化のための熱処理工程が実施されうる。

#### 【0044】

本実施形態では、画素部のMOSトランジスタはシングルドレン構造を有し、周辺回路部のMOSトランジスタはLDD構造を有するが、画素部のMOSトランジスタおよび周辺回路部のMOSトランジスタの双方がLDD構造を有してもよい。

10

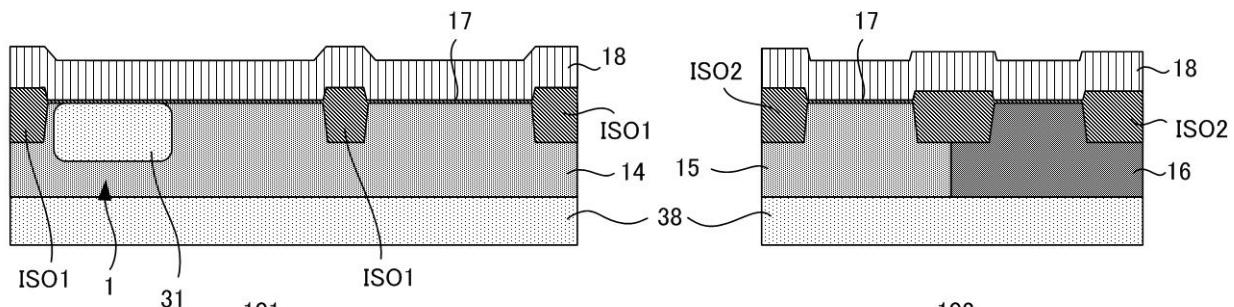

#### 【0045】

図5を参照しながら本発明の第3実施形態の固体撮像装置の製造方法を説明する。第3実施形態では、第1、第2実施形態におけるゲート絶縁膜17が第1ゲート絶縁膜17aおよび第2ゲート絶縁膜17bによって置き換えられている。第1ゲート絶縁膜17aは画素部101のゲート絶縁膜であり、第2ゲート絶縁膜17bは周辺回路部102のゲート絶縁膜である。第1ゲート絶縁膜17aの厚さG<sub>a</sub>は、第2ゲート絶縁膜17bの厚さG<sub>b</sub>より厚い。

#### 【0046】

このような構成は、例えば、半導体基板SUBの全域に厚さG<sub>a</sub>を有するゲート絶縁膜を形成した後に、周辺回路部102のゲート絶縁膜をウェットエッチングによって選択的に除去し、その後に第2ゲート絶縁膜17bを形成することによって得られる。

20

#### 【0047】

第3実施形態では、第1、第2実施形態と同様に、ゲート電極膜18のパターニング前にゲート電極膜18のうち画素部101に対応する部分の少なくとも一部分に対して選択的にn型不純物が注入される。これによって、周辺回路部102の少なくとも一部よりも突き出し量が大きい画素部101においてゲート電極膜18のエッチング時にエッチング残渣が発生する可能性が低減される。一方で、ゲート電極膜18のエッチング時には、ゲート電極膜18の下地であるゲート絶縁膜17aでエッチングをストップさせる必要がある。画素部101では、周辺回路部102よりも早くゲート電極膜18がエッチングされるため、下地となる第1ゲート絶縁膜17aが過剰にエッチングされてしまうという課題がある。ここで、第1ゲート絶縁膜17aの過剰エッチングと、ゲート電極膜18のエッチング時に発生するエッチング残渣とは、トレードオフの関係となっている。このような問題に対して、G<sub>a</sub> > G<sub>b</sub>の関係が成り立つことで、ゲート電極膜18のエッチング時に第1ゲート絶縁膜17aが過剰にエッチングされることによって画素部101において半導体基板SUBの表面が露出する可能性を低減することができる。

30

#### 【0048】

また、画素部101と周辺回路部102とでゲート絶縁膜の厚さを互いに異ならせることで、画素部101の電源電圧と周辺回路部102の一部の回路に用いる電源電圧とを異ならせることが可能になる。

40

#### 【0049】

第3実施形態においても、画素部の少なくとも一部分（例えば、エッチング残渣が発生しやすい活性領域と素子分離との境界部分）におけるゲート電極膜のエッチングレートを周辺回路部におけるゲート電極膜のエッチングレートも高くすることができる。

#### 【0050】

図6を参照しながら本発明の第4実施形態の固体撮像装置の製造方法を説明する。なお、第4実施形態として言及しない事項は、第1乃至第3実施形態に従う。第4実施形態では、周辺回路部102の少なくとも一部のMOSトランジスタが金属半導体化合物層（金属シリサイド層）を有している。一方、かつ画素部101のMOSトランジスタは、周辺回路部102のMOSトランジスタの金属半導体化合物層の金属成分と同じ金属成分を含む金属半導体化合物層を有していない。

50

## 【0051】

画素部101における第1ゲート電極G1および半導体基板SUBを覆っている絶縁膜19は、金属半導体化合物層の形成を防止する保護膜として機能しうる。周辺回路部102においては、サリサイド(セルファアラインシリサイド)と呼ばれる手法を用いて、ゲート電極20、21の上層に金属半導体化合物層22が形成され、ソースおよびドレインの表層に金属半導体化合物層23が形成される。金属半導体化合物層22、23は、例えば、コバルトシリサイドで構成されうる。ただし、金属半導体化合物層を構成する金属は、ニッケルなどの他の金属であってもよいし、半導体は、シリコン以外の半導体であってもよい。金属半導体化合物層22、23を構成する金属は、MOSトランジスタに接続される導電部材(コンタクトプラグあるいは配線)に含まれる金属ではない金属でありうる。金属半導体化合物層22、23は、例えば、導電部材に含まれる金属がタンゲステン、チタン、タンタル、銅またはアルミニウムであれば、これら以外の金属(コバルト、ニッケル等)と半導体との化合物層である。画素部101のMOSトランジスタは、画素部101のMOSトランジスタに接続する導電部材に含まれる金属成分以外の金属と半導体との化合物層を有していない。画素部101のMOSトランジスタは、その一部が、画素部101のMOSトランジスタに接続する導電部材に含まれるチタンまたはタンゲステンなどの金属と反応しうる。その結果、導電部材に含まれる金属とMOSトランジスタの半導体との金属半導体化合物からなる部分を含うる。また、本実施形態では、絶縁膜19が金属半導体化合物層の形成を防止するための保護膜として利用されるが、絶縁膜19とは異なる膜を別工程で形成した後にパターニングして保護層を形成してもよい。

10

20

## 【0052】

本実施形態によれば、画素部のゲート電極膜のエッチング残渣の低減に加えて、金属半導体化合物層の導入によってトランジスタの特性を向上させることができる。

## 【0053】

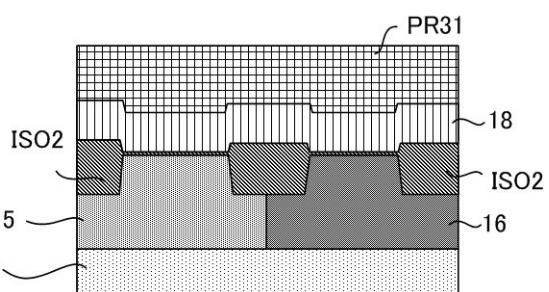

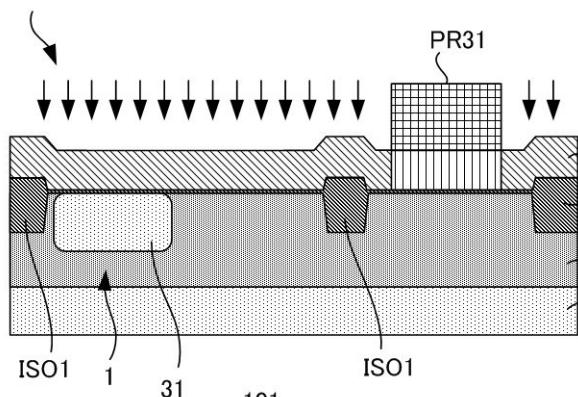

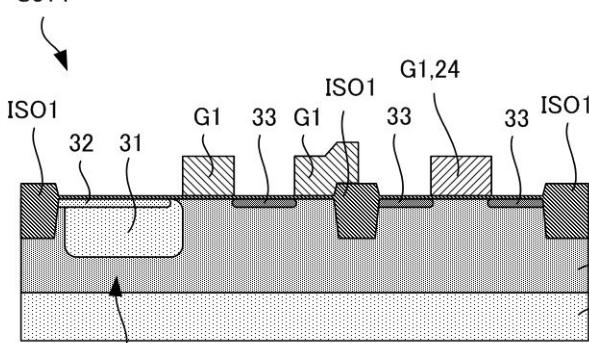

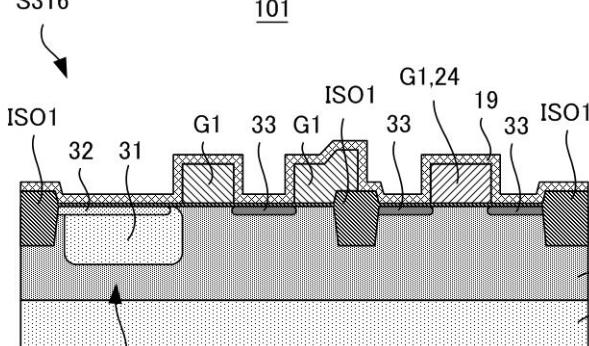

図7を参照しながら本発明の第5実施形態の固体撮像装置の製造方法を説明する。なお、第5実施形態として言及しない事項は、第1乃至第4実施形態に従いうる。まず、第1実施形態における工程S110～118と同様の工程が実施され、その後に、工程S310が実施される。

30

## 【0054】

工程S310では、フォトレジストパターンPR31を形成する。フォトレジストパターンPR31は、画素部101に対応する部分の一部分に第1開口を有し、画素部101の他の一部分および周辺回路部102を覆っている。該少なくとも一部分は、第1素子分離ISO1と第1活性領域ACT1との境界部分の上に位置する部分、あるいは、第1素子分離ISO1の全域およびその周辺をカバーする領域を含みうる。工程S310では、更に、フォトレジストパターンPR31の第1開口を通してゲート電極膜18にn型不純物を注入する。つまり、工程S310では、ゲート電極膜18のうち画素部101に対応する部分の少なくとも一部分にn型不純物を注入する。その後、フォトレジストパターンPR31を除去する。

## 【0055】

工程S312では、フォトレジストパターンPR32を形成する。フォトレジストパターンPR32は、画素部101に対応する部分の一部分に第2開口を有し、画素部101の他の一部分および周辺回路部102を覆っている。ここで、第1開口の面積は、第2開口の面積よりも大きい。第1開口と第2開口は、相互に一部が重複してもよいし、重複する領域を有しなくてもよい。工程S312では、更に、フォトレジストパターンPR1の第2開口を通してゲート電極膜18にp型不純物を注入する。つまり、工程S312では、ゲート電極膜18のうち画素部に対応する部分の少なくとも一部分にp型不純物を注入する。その後、フォトレジストパターンPR32を除去する。ここで、ゲート電極膜18のうちp型不純物を注入する部分は、例えば、増幅MOSトランジスタのゲート電極24となる部分でありうる。

40

## 【0056】

50

工程 S 3 1 4 では、ゲート電極膜 1 8 をパターニングするためのフォトレジストパターン（不図示）を形成する。そして、該フォトレジストパターンの開口を通してゲート電極膜 1 8 をエッチングすることによってゲート電極膜 1 8 をパターニングし、画素部 1 0 1 の第 1 ゲート電極 G 1 および周辺回路部 1 0 2 の第 2 ゲート電極 G 2 を形成する。

#### 【 0 0 5 7 】

ここで、前述したように、n 型ポリシリコンのエッチングレートはノンドープ（i型）ポリシリコンと比較して高く、また、n 型不純物の注入量の増加によってエッチングレートが高くなる。一方、p 型ポリシリコンのエッチングレートは、ノンドープ（i型）ポリシリコンのエッチングレートと比較してわずかに低くなるものの、ほぼ同等と考えてよい。このため、p 型ポリシリコンのエッチングレートを基準としてエッチングの条件を設定すれば、n 型またはノンドープのポリシリコンについては、p 型ポリシリコンよりも残渣が発生しにくいエッチャリング条件とすることができます。しかも、n 型ポリシリコンについては、エッチング残渣の発生に対するプロセスマージンが大幅に改善されたエッチング条件とすることができます。

10

#### 【 0 0 5 8 】

n 型ポリシリコンと i 型あるいは p 型ポリシリコンとのエッチングレートに差が生じる一因を説明する。エッチングに用いられるプラズマ中で、エッチャントとして働くプラスイオンは、多数キャリアが電子である n 型の部分に、p 型や i 型の部分よりも多く引き寄せられる。つまり、n 型の部分には i 型、p 型の部分よりもエッチングガスが多く供給される。そのため、n 型の部分は他の部分に比べてエッチングレートが高くなると考えられる。また、ゲート電極 1 8 膜自体も、含有する不純物が多いほどエッチングレートが高くなりやすいことも一因として考えられる。このような理由から、ゲート電極膜 1 8 において、n 型の部分が i 型または p 型の部分に比べてエッチングレートを高くなる現象は、ゲート電極膜 1 8 の膜質や主成分、不純物の種類によるものではないことが分かる。そのため、ゲート電極膜 1 8 がポリシリコンあるいはアモルファスシリコンでなくとも、本実施形態を適用することができる。

20

#### 【 0 0 5 9 】

以上の実施形態では、配線層、カラーフィルター、マイクロレンズなどの構造が省略されているが、固体撮像装置は、配線層、カラーフィルターおよび / またはマイクロレンズを備えうる。

30

#### 【 符号の説明 】

#### 【 0 0 6 0 】

1 : 光電変換素子、2 : 増幅用 M O S ツランジスタ、1 1 : 酸化シリコン膜、1 2 : 室化シリコン膜、I S O 1 : 第 1 素子分離、A C T 1 : 第 1 活性領域、I S O 2 : 第 1 素子分離、A C T : 第 2 素子分離、2 0 0 : 境界部分、1 0 1 : 画素部、1 0 2 : 周辺回路部

【図1】

S110

101

SUB

102

SUB

S112

101102

S114

101102

S116

101102

ISO1

【図2】

S118

S120

S122

S124

【図3】

S210

S212

S214

S216

【図4】

【図5】

【図6】

【図7】

S310

S312

102

S314

S316

101102

---

フロントページの続き

(72)発明者 板橋 政次

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 柿沼 伸明

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 下津佐 峰生

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 藤田 雅人

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 大貫 裕介

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 荻野 拓海

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 鳥居 廉大

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 4M118 AB01 BA14 CA04 CA34 DD04 EA01 EA14 FA27 FA28 FA33