(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4754792号

(P4754792)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月3日(2011.6.3)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>HO1L 21/336</b> | <b>(2006.01)</b> | HO1L 29/78 | 627C |

| <b>HO1L 29/786</b> | <b>(2006.01)</b> | HO1L 29/78 | 627G |

| <b>HO1L 21/20</b>  | <b>(2006.01)</b> | HO1L 29/78 | 617J |

| <b>HO1L 21/28</b>  | <b>(2006.01)</b> | HO1L 21/20 |      |

| <b>HO1L 29/423</b> | <b>(2006.01)</b> | HO1L 21/28 | E    |

請求項の数 8 (全 18 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-243673 (P2004-243673)  |

| (22) 出願日     | 平成16年8月24日 (2004.8.24)        |

| (65) 公開番号    | 特開2005-101571 (P2005-101571A) |

| (43) 公開日     | 平成17年4月14日 (2005.4.14)        |

| 審査請求日        | 平成19年6月13日 (2007.6.13)        |

| (31) 優先権主張番号 | 特願2003-307489 (P2003-307489)  |

| (32) 優先日     | 平成15年8月29日 (2003.8.29)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 磯部 敦生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 齋藤 晓<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 藤川 最史<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

審査官 宮澤 尚之

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ガラス基板上に下地膜を形成し、

前記下地膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜にレーザー光を照射することにより結晶性半導体膜を形成し、

前記結晶性半導体膜上に第1のマスクを形成し、

前記第1のマスクを用いて前記結晶性半導体膜をエッチングし、

前記下地膜の表面、及び前記結晶性半導体膜の側面を窒化し、

前記第1のマスクを除去し、

前記結晶性半導体膜の表面を洗浄し、

前記結晶性半導体膜上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に導電膜を形成し、

前記導電膜上にテープを有する第2のマスクを形成し、

前記第2のマスクを後退させつつ前記導電膜をエッチングしてゲート電極を形成する半導体装置の作製方法であって、

前記ゲート電極のゲート長が1.0 μm以下となるように前記導電膜をエッチングすることを特徴とする半導体装置の作製方法。

## 【請求項 2】

ガラス基板上に下地膜を形成し、

前記下地膜上に非晶質半導体膜を形成し、

10

20

前記非晶質半導体膜にレーザー光を照射することにより結晶性半導体膜を形成し、

前記結晶性半導体膜上に第1のマスクを形成し、

前記第1のマスクを用いて前記結晶性半導体膜をエッチングし、

前記下地膜の表面、及び前記第1のマスクが形成された前記結晶性半導体膜に対して、窒素又はアンモニアを用いたプラズマ処理を施し、

前記第1のマスクを除去し、

前記結晶性半導体膜の表面を洗浄し、

前記結晶性半導体膜上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に導電膜を形成し、

前記導電膜上にテープを有する第2のマスクを形成し、

前記第2のマスクを後退させつつ前記導電膜をエッチングしてゲート電極を形成する半導体装置の作製方法であって、

前記ゲート電極のゲート長が1.0 μm以下となるように前記導電膜をエッチングすることを特徴とする半導体装置の作製方法。

10

**【請求項3】**

ガラス基板上に下地膜を形成し、

前記下地膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜にレーザー光を照射することにより結晶性半導体膜を形成し、

前記結晶性半導体膜上に第1のマスクを形成し、

前記第1のマスクを用いて前記結晶性半導体膜をエッチングし、

前記下地膜の表面、及び前記第1のマスクが形成された前記結晶性半導体膜を、窒素又はアンモニアを用いたプラズマ雰囲気にさらし、

前記第1のマスクを除去し、

前記結晶性半導体膜の表面を洗浄し、

前記結晶性半導体膜上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に導電膜を形成し、

前記導電膜上にテープを有する第2のマスクを形成し、

前記第2のマスクを後退させつつ前記導電膜をエッチングしてゲート電極を形成する半導体装置の作製方法であって、

前記ゲート電極のゲート長が1.0 μm以下となるように前記導電膜をエッチングすることを特徴とする半導体装置の作製方法。

20

30

**【請求項4】**

請求項1乃至3のいずれか一において、

ドライエッティング法又はウェットエッティング法により前記導電膜をエッチングすることを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項4において、

前記ドライエッティング法は、CF<sub>4</sub>、Cl及びO<sub>2</sub>を用いて行われることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項4において、

前記ドライエッティング法は、Cl<sub>2</sub>を用いて行われることを特徴とする半導体装置の作製方法。

**【請求項7】**

請求項1乃至6のいずれか一において、

前記レーザー光を照射する前に、前記非晶質半導体膜上に結晶化を促進させる金属元素を添加し、加熱処理を行うことを特徴とする半導体装置の作製方法。

**【請求項8】**

請求項1乃至7のいずれか一に記載の半導体装置の作製方法を用いたCPUの作製方法。

**【発明の詳細な説明】**

40

50

**【技術分野】****【0001】**

本発明は、ガラス基板上に薄膜トランジスタ（以下、TFTとも表記する）を形成した半導体装置、特に中央処理装置（CPU）、及びその作製方法に関する。

**【背景技術】****【0002】**

従来のCPUは単結晶の半導体基板を用いた半導体素子、いわゆるシリコンウェハ上に形成されたIC（integrated circuit：集積回路）チップを積層して形成されている。このようなCPUは、動作速度が1GHzを越えるものが製造されており、高周波数化が進んでいる。そして将来的には、より高い動作周波数を確保することができる集積回路の実現が期待されている。10

**【0003】**

また安価なガラス基板上に形成されたTFTを有するアクティブマトリクス型の半導体装置への開発が進められている。特に集積回路を画素部とガラス基板上に一体形成する技術、いわゆるシステムオンパネル化が重要視されており、その流れから、薄膜の半導体膜を用いた大規模集積回路の形成に関する研究も進められている。特に、多結晶半導体膜を用いたTFTは、移動度（モビリティ）が高いため、システムオンパネル化する場合の半導体素子として期待されている。

**【0004】**

このようなガラス基板上にTFTを形成する技術として以下のものがある。20

**【0005】**

耐熱性の劣る基板上に良好な特性を示す絶縁ゲイト型シリコン半導体装置の作製方法に関する、ガラス基板上に下地膜を介して形成されたシリコン半導体膜表面を酸素等の酸化雰囲気中にさらし、更に強光を照射することによって、表面に極薄い酸化膜を形成し、かかる後にプラズマCVD法等によりゲイト絶縁膜を形成する方法がある（特許文献1参照）。

**【0006】**

また良好なオーム接触が実現されたコンタクト構造を備えた高性能な半導体装置を実現するため、三層以上の積層構造を有する配線を形成し、この配線に達するコンタクトホールを形成する場合、第2の導電層をエッティングストッパーとして機能させることにより、良好なオーム接触が実現されたコンタクト構造を形成する方法がある（特許文献2参照）。30

**【0007】**

また第1層、及び第2層を有するゲート電極をエッティングし、いわゆるGOLD構造TFTを作製する方補に関し、フォトリソグラフィ工程によりゲート電極のエッティングマスクとなるレジストパターンを形成し、第2層のゲート電極膜のみをテーパーエッティングする方法がある。レジストパターンは高精度に制御されたテーパー角を有している（特許文献3参照）。

**【特許文献1】特開平7-94756号公報****【特許文献2】特開2000-252473号公報****【特許文献3】特開2002-33273号公報****【発明の開示】****【発明が解決しようとする課題】****【0008】**

しかし、従来のCPUはシリコンウェハ上に形成しているため、高価な機材が必要である。さらにフレキシブル性が乏しかった。またガラス基板上に形成されたTFTを用いてCPU等を形成する場合、ガラスに含まれるナトリウムや、ガラス自体の耐熱性の問題があり、実現できなかった。

**【0009】**

また高速度でCPUを動作させる場合、TFTのゲートの長さ（ゲート長）をより小さ50

くすることが必要となる。しかし、ガラス基板はたわみが大きいため、C P Uとして動作させる程度のゲート長に、ゲート電極をエッチングすることが難しかった。

#### 【0010】

そこで本発明は、ガラス基板上に形成されたT F TによりC P Uを形成することを課題とする。特にT F Tのゲート長が $1 \mu m$ 以下となる微細なT F Tを有するC P Uを形成することを課題とする。

#### 【課題を解決するための手段】

#### 【0011】

上記問題を鑑み本発明は、ガラス基板上に形成された結晶性半導体膜上に導電膜を形成し、導電膜上にテーパーを有するマスクを形成し、該マスクを用いて導電膜をエッチングすることによりゲート長が $1.0 \mu m$ 以下の薄膜トランジスタを形成することを特徴とする。特に結晶性半導体膜は、ガラス基板上に形成された非晶質半導体膜の結晶化に際し、レーザー照射を用いることを特徴とする。

#### 【0012】

レーザー光として、Arレーザー、Krレーザー、エキシマレーザー、YAGレーザー、 $Y_2O_3$ レーザー、 $YVO_4$ レーザー、YLFレーザー、 $YAlO_3$ レーザー、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、Ti:サファイヤレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種を用いることができる。

#### 【0013】

また連続発振型のレーザー(C Wレーザーとも表記する)やパルス発振型のレーザー(パルスレーザーとも表記する)を用いることができる。またレーザーのビーム形状は、線状とすると好ましく、長軸の長さは $200 \sim 350 \mu m$ とすればよい。またさらにレーザーは、半導体膜に対して入射角 $1(0^\circ < 1 < 90^\circ)$ を持たせてもよい。

#### 【0014】

また本発明は、テーパーを有するマスクを用いて導電膜をエッチングすることを特徴とする。またテーパーを有するマスクとは、マスクの底辺と、マスクの斜辺(端面)とがある角度 $\alpha$ を有する状態をいう。なお該角度 $\alpha$ は、 $20^\circ < \alpha < 85^\circ$ 、好ましくは $45^\circ < \alpha < 60^\circ$ とするとよい。このようなテーパーを有するマスクは、有機材料または無機材料から形成することができる。具体的には有機材料としてレジスト、無機材料として酸化珪素膜を用いることができる。またテーパーを有するマスクは、マスクの端面がテーパーを有していればよく、マスクの上面の形状は平坦であっても、凸状であってもよく、つまり上面はどのような形状でもよい。

#### 【0015】

さらに本発明は、導電膜を少なくとも第1の導電膜及び第2の導電膜の順に積層される積層構造とする。第2の導電膜を、上記マスクを用いてエッチングする場合、第1の導電膜をいわゆるエッチングストッパーとして用いることができる。第1の導電膜をエッチングストッパーとして用いることにより、第2の導電膜のチャネル長方向の長さ、つまりゲート長に相当する長さを $1.0 \mu m$ 以下と小さくすることができる。

#### 【0016】

なおゲート長が $1.0 \mu m$ 以下のT F Tを、特にサブミクロンT F Tと呼ぶことがある。このようなサブミクロンT F Tでは、半導体膜に形成される不純物領域と、配線(ソース電極、又はドレイン電極に相当する)とを接続するための、絶縁膜に形成される開口部(コンタクトホールとも表記する)の直径も小さくなる。またコンタクトホールの形状が垂直となると、ゲート電極と、コンタクトホール(つまり配線)間のキャリアの移動を小さくすることができる。そのため、意図的に、コンタクトホールを形成するためのレジストの端部はテーパー形状とならないように形成するとよい。またレジストと、コンタクトホールを開口する絶縁膜との選択比が高ければ、絶縁膜のエッチング速度が速く、コンタクトホールを垂直に形成することができるため、レジスト端部がテーパー形状となっても構わない。

#### 【0017】

10

20

30

40

50

コンタクトホールを形成する絶縁膜の材料により、コンタクトホール形成用のマスクの材料を有機材料、又は無機材料から選択することができる。具体的には、無機材料からなる絶縁膜の場合、有機材料、例えばレジストからなるマスクを用い、有機材料からなる絶縁膜の場合、無機材料、例えば酸化珪素からなるマスクを用いるとよい。

#### 【0018】

またサブミクロンTFTとなると、半導体膜と、ゲート電極との間に設けられたゲート絶縁膜の膜厚が薄膜化する。そのため、ゲート絶縁膜を形成する前に半導体膜表面をフッ酸等により洗浄すると、下地膜、特に半導体膜と接して設けられた下地膜に、溝や凹部等が形成されてしまうことがあるため、薄膜化されたゲート絶縁膜の段差被覆性が低下してしまう。そのため、半導体膜表面をフッ素等により洗浄する前に、下地膜を窒化することで、該洗浄による溝や凹部の形成を防止すると、好ましい。10

#### 【0019】

以上のように形成された薄膜トランジスタを用いて、半導体装置、特にCPU(中央演算処理装置)を形成することができる。このように形成された半導体装置やCPUは、ゲート長が $1.0\text{ }\mu\text{m}$ 以下の薄膜トランジスタを有するため、高速動作を行うことができる。。

#### 【発明の効果】

#### 【0020】

従来のようにシリコンウェハを用いたCPUの製造には高価な機材が必要であるが、ガラス基板に形成されたTFTを用いたCPUの場合は廉価な機材だけで実現でき、低コストなCPUを作製することができる。さらにシリコンウェハを用いたCPUと比べ、ガラス基板上の薄膜トランジスタを用いたCPUは軽量であり、携帯や実装する場合に好ましい。20

#### 【0021】

本発明より、表示部と駆動回路部をはじめとする周辺回路だけでなく、CPU、メモリなどの情報処理回路を同一基板上に一体形成することができる。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。30

#### 【0023】

##### (実施の形態1)

本実施の形態では、具体的な作製工程について説明する。

#### 【0024】

図1(A)に示すように、絶縁表面を有する基板100上に下地膜101を形成する。40 基板100には、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、SUS基板等を用いることができる。また、PET(ポリエチレンテレフタレート)、PES(ポリエチレンサルファイル)、PEN(ポリエチレンナフタレート)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板は、一般的に他の基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

#### 【0025】

下地膜101は基板100中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。そのためアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒化酸化珪素などの絶縁膜を用いて形成する。本実施の形態では、プラズ50

マ C V D 法を用いて SiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O 及び H<sub>2</sub> を反応ガスとして形成される酸化窒化珪素膜 (SiNO) を 10 ~ 200 nm (本実施の形態では 50 nm) 、 SiH<sub>4</sub> 及び N<sub>2</sub>O を反応ガスとして形成される酸化窒化珪素膜 (SiON) を 50 ~ 200 nm (本実施の形態では 100 nm) の順に積層する。なお下地膜 101 は単層構造を有してもよく、例えば窒化酸化珪素膜を 10 ~ 400 nm (好ましくは 50 ~ 300 nm) の膜厚になるように形成することができる。

#### 【0026】

ガラス基板、ステンレス基板 (SUS 基板) またはプラスチック基板のように、アルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いる場合、不純物の拡散を防ぐという観点から下地膜を設けることは有効であるが、石英基板など不純物の拡散がさして問題とならない場合は、必ずしも設ける必要はない。10

#### 【0027】

下地膜 101 上に非晶質半導体膜 102 を形成する。非晶質半導体膜 102 の膜厚は 25 ~ 100 nm (好ましくは 30 ~ 60 nm) とする。また非晶質半導体は珪素だけではなくシリコンゲルマニウムも用いることができ、シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は 0.01 ~ 4.5 atomic % 程度であることが好ましい。本実施の形態では 66 nm の珪素を主成分とする半導体膜 (非晶質珪素膜、アモルファスシリコンとも表記する) を用いる。

#### 【0028】

次に、非晶質半導体膜 102 に金属元素を添加する。ここで添加とは、少なくとも非晶質半導体膜の結晶化が促進されるように非晶質半導体膜 102 の表面上に金属元素を形成することをいう。金属元素を形成することにより、低温で結晶化できるため好ましい。20

#### 【0029】

例えば、非晶質半導体膜 102 上にスピノコーティング法やディップ法といった塗布方法により Ni 溶液 (水溶液や酢酸溶液を含む) を塗布し、Ni を含む膜 103 (但し、極めて薄いため膜として観測できない場合もある) を形成する。このとき非晶質半導体膜 102 の表面の濡れ性を改善し、非晶質半導体膜の表面全体に溶液を行き渡らせるため、酸素雰囲気中の UV 光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜 (図示しない) を 10 ~ 50 (1 ~ 5 nm) に成膜することが望ましい。また、イオン注入法により Ni イオンを非晶質半導体膜中に注入したり、Ni を含有する水蒸気雰囲気中で加熱したり、ターゲットを Ni 材料として Ar プラズマでスパッタリングしてもよい。本実施の形態では、Ni 酢酸塩 10 ppm を含有した水溶液をスピノコーティング法により塗布する。30

#### 【0030】

その後、非晶質半導体膜 102 を 500 ~ 550 で 2 ~ 20 時間かけて熱処理を行い、非晶質半導体膜を結晶化し結晶性半導体膜を形成する。このとき加熱温度を徐々に高温となるように変化させると好ましい。最初の低温加熱工程により、非晶質半導体膜の水素等が出てくるため、結晶化の際の膜荒れを低減する、いわゆる水素だしを行うことができる。また磁場をかけて、その磁気エネルギーと合わせて結晶化させてもよいし、高出力マイクロ波を使用しても構わない。本実施の形態では、縦型炉を用いて 500 で 1 時間熱処理後、550 4 時間で熱処理を行う。40

#### 【0031】

このように金属元素を用いて熱処理を行うため、低温にて結晶化を行うことができる。そのため、ガラス基板上に結晶性半導体膜を形成することができる。さらには、上記熱処理温度に耐えうるプラスチック基板状に半導体膜を形成することもできる。その結果、フレキシブル性を有する半導体装置を形成することができ、いわゆるシート型コンピュータの実現に貢献することができる。

#### 【0032】

図 1 (B) に示すように、結晶性半導体膜の表面に形成された酸化膜をフッ酸等でエッチング除去した後、結晶化が行われた非晶質半導体膜 102 にレーザー光 (レーザービー50

ム) 105を照射する。レーザーとして、Arレーザー、Krレーザー、エキシマレーザー、YAGレーザー、 $Y_2O_3$ レーザー、 $YVO_4$ レーザー、YLFレーザー、 $YAlO_3$ レーザー、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、Ti:サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種を用いることができる。また連続発振型のレーザー(CWレーザー)やパルス発振型のレーザー(パルスレーザー)を用いることができる。またレーザーのビーム形状は、線状とすると好ましく、長軸の長さは200~350μmとすればよい。またさらにレーザーは、半導体膜に対して入射角1(0°<1<90°)を持たせてもよい。

#### 【0033】

本実施の形態では、大気中において、6.4WのCWレーザー105を、半導体膜に対して1=25度で入射し、レーザービームの長軸を300μmとし、走査速度40cm/secで照射する。すると、幅(レーザーの照射方向に垂直な方向の長さ)が210μmの領域が、結晶成長が良好な領域のとなり、レーザービームの長軸を90μmずつ重ね合わせて照射するとよい。

10

#### 【0034】

このようなレーザー照射において、精度よく重ね合わせたり、照射開始位置や照射終了位置を制御するため、マーカーを形成することもできる。マーカーは非晶質半導体膜とともに、同一材料によって、基板へ形成すればよい。

#### 【0035】

その後、金属元素を低減、又は除去するためにゲッタリング工程を施す。本実施の形態では、非晶質半導体膜をゲッタリングシンクとして金属元素をゲッタリングする(捕獲する)方法を説明する。まず、結晶性半導体膜上に酸素雰囲気中でのUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を形成する。次いでプラズマCVD法を用いて、原料ガスにSH<sub>4</sub>、Ar、圧力が0.3パスカル、RFパワーが3kW、基板温度が150として非晶質半導体膜を150nmの膜厚で形成する。

20

#### 【0036】

その後、窒素雰囲気で550、4時間の加熱処理を行い、金属元素を低減、又は除去する。そして、ゲッタリングシンクとなる非晶質半導体膜、及び酸化膜をフッ酸等により除去し、金属元素が低減、又は除去された結晶性半導体膜を得ることができる。

30

#### 【0037】

以上のように、結晶性半導体膜を形成することができるが、レーザー照射のみによって、結晶性半導体膜を形成しても構わない。レーザー光は、その波長によって、ガラス基板等の透明基板を透過することができるため、基板の選択幅を広げることができる。またレーザー照射のみによって結晶化すると、金属元素を添加する工程や、ゲッタリング工程を削除することができ、好ましい。

#### 【0038】

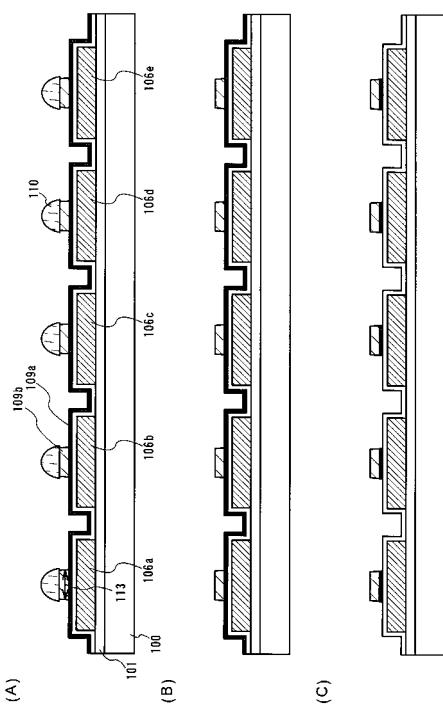

図1(C)に示すように、結晶性半導体膜を所定の形状にパターニングし、島状の半導体膜106a~106eを得る。パターニングに際し、結晶性半導体膜にフォトレジストを塗布し、所定のマスク形状を露光し、焼成して、結晶性半導体膜上にマスクを形成する。このマスクを用いて、ドライエッチング法により結晶性半導体膜をパターニングする。ドライエッチング法のガスは、CF<sub>4</sub>と、O<sub>2</sub>とを用いることができる。

40

#### 【0039】

その後、必要に応じて結晶性半導体膜に不純物を添加する。例えば、ドーピング法によりボロン(B)を添加する。すると、薄膜トランジスタの電気特性であるしきい値をよりゼロに近づかせることができる。すなわち結晶性半導体膜をより真性状態とすることができます。

#### 【0040】

その後、結晶性半導体膜106a~106eを覆うように絶縁膜、いわゆるゲート絶縁膜108を形成する。なお、ゲート絶縁膜108の形成前に、島状の半導体膜の表面をフ

50

ツ酸等により洗浄するとよい。その結果、半導体膜表面と、ゲート絶縁膜との界面状態を良好に保つことができる。ゲート絶縁膜108はプラズマCVD法またはスパッタ法を用い、厚さを10～150nm、好ましくは20～40nmとしてシリコンを含む絶縁膜で形成する。本実施の形態では、プラズマCVD法により、原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用い、成膜室の温度を400として、20nmの厚さで酸化窒化シリコン膜を形成する。このとき、ゲート絶縁膜の膜厚を薄くするため、成膜レートを落とすとよい。その結果、成膜初期であって膜質が良くない膜の形成を減らすことができる。勿論、ゲート絶縁膜は酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いてもよい。

## 【0041】

10

その後、結晶性半導体膜上にゲート絶縁膜108を介してゲート電極109となる導電膜109a、109bを形成する。勿論ゲート電極109は、単層であっても積層であってもよい。導電膜109a、109bは、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。本実施の形態では、ゲート絶縁膜108を覆うように、第1の導電膜108aとして膜厚10～50nm、例えば30nmの窒化タンタル膜を形成し、第2の導電膜108bとして膜厚200～400nm、例えば370nmのタンゲステン膜を順次積層する。

## 【0042】

その後図2(A)に示すように、第1の導電膜109a、第2の導電膜109bを、マスクを用いてエッチングする。まず、第2の導電膜上にフォトレジストをスピニング法等により塗布する。フォトレジストは、ポジ型及びネガ型のいずれかを使用することができる。このとき、吸光剤が添加されたフォトレジストを用いてもよい。本実施の形態では、吸光剤が添加されたポジ型のノボラック型のものを使用する。

20

## 【0043】

そして、塗布されたフォトレジストに対し加熱処理、いわゆるプリベークを施す。プリベークの加熱温度は50～120とし、後に行われるポストベークより低い温度で行う。本実施の形態では、加熱温度90、加熱時間90secとしてプリベークを行う。

## 【0044】

次いで露光機を用いて、フォトレジストへマスクを転写するため露光を施す。本実施の形態では、露光機にステッパーを用いる。露光時間は150～250ms以此ればよく、本実施の形態ではゲート長0.8μmが要求されるため205ms以此とする。その他、ゲート長が0.6μmの場合露光時間は320μm、ゲート長が1.0μmの場合露光時間は175μmとする。すなわち所望のゲート長により露光時間を決定することができる。

30

## 【0045】

その後、フォトレジストへ現像液を滴下したり、スプレーノズルからスプレーすることにより、露光されたフォトレジストを現像し、加熱処理を行う。本実施の形態では、現像液にNMD-3を用い、現像時間60secとする。

## 【0046】

その後本実施の形態では、現像されたフォトレジストを125、180secで加熱処理を行う、いわゆるポストベークを行う。その結果、フォトレジスト中に残っている水分等を除去し、同時に熱に対する安定性を高めることができる。すると、端面に角度2となるテーパー形状を有するレジストマスク110が第2の導電膜上に形成される。なお、レジストマスクの形状は扇形、又は台形となってもよい、つまりレジストマスクの上面の形状は限定されない。

40

## 【0047】

またマスク自体に露光解像度の限界以下のパターンを付けて、レジスト形状を制御することにより、端面にテーパー形状を有するレジストマスクを形成することもできる。これは、露光解像度の限界以下のパターンを付けると、レジストマスク端面の露光精度が低下するため、レジストマスク端面は垂直に露光されることなく、テーパー形状に露光されて

50

しまうからである。

【0048】

このようにレジストマスクの端面にテーパー形状を有することにより、エッチング工程により、レジストマスクの側面に付着してしまう反応生成物の形成を防止することができる。

【0049】

図2(B)に示すように、レジストマスク110を用いて、第2の導電膜109bをエッチングする。本実施の形態では、ガスとしてCF<sub>4</sub>、Cl、O<sub>2</sub>を用いたドライエッティング法により、第2の導電膜109bをエッチングする。このときレジストマスク110のテーパーと同様に、第2の導電膜109bの端部にはテーパー形状が形成される。また第1の導電膜109aは、ゲート絶縁膜や半導体膜がエッチングされないよう、いわゆるエッチングストッパーとして機能する。

【0050】

エッチングされた第2の導電膜109bは、0.2μm以上1.0μm以下のゲート長113を有する。またこのとき、レジストマスク110も数μm後退する場合がある。本実施の形態では、レジストマスク110を0.4μm後退させ、ゲート長0.8μmの第2の導電膜を形成する。

【0051】

図2(C)に示すように、レジストマスク110を設けた状態で、第1の導電膜109aをエッチングする。このとき、ゲート絶縁膜108と、第1の導電膜109aとの選択比の高い条件で第1の導電膜109aをエッチングする。本実施の形態では、ガスとしてCl<sub>2</sub>を用い、第1の導電膜109aをエッチングする。すると、薄膜状態にゲート絶縁膜108を維持しながら、第1の導電膜109aをエッチングすることができる。この工程により、レジストマスク110、第2の導電膜109bも多少エッチングされ、さらに細くなることがある。以上のようにゲート長が1.0μm以下と非常に小さくゲート電極109が形成される。

【0052】

その後、レジストマスク110をO<sub>2</sub>アッシングやレジスト剥離液により除去し、不純物添加用のレジストマスク115を形成する。具体的には図3(A)に示すように、pチャネル型TFTとなる領域に、レジストマスク115を形成する。このレジストマスク115の作製方法は、上記記載を参考にすればよいため、詳細な説明を省略する。

【0053】

次いで、nチャネル型TFTとなる領域に、ゲート電極109をマスクとして自己整合的に不純物元素であるリン(P)を添加する。本実施の形態では、ホスフィン(PH<sub>3</sub>)を60~80kVでドーピングする。すると、nチャネル型のTFTとなる領域に、不純物領域116a~116cが形成される。このとき、半導体膜に対して深さ方向に均一になるようにホスフィンを添加する。しかし、添加時の不純物元素の回り込みにより、ゲート電極109と重なるように不純物領域が形成されることもある。但し、このようなゲート電極109と重なる不純物領域のチャネル長方向の長さは、0.1~0.3μmとなるようとする。

【0054】

図3(B)に示すように、nチャネル型TFTとなる領域にレジストマスク117を形成する。その後、pチャネル型TFTとなる領域にゲート電極109をマスクとして、自己整合的に不純物元素であるボロン(B)を添加する。本実施の形態では、B<sub>2</sub>H<sub>6</sub>を30~45kVでドーピングする。すると、pチャネル型のTFTとなる領域に、不純物領域118a~118bが形成される。その後、レジストマスク117をO<sub>2</sub>アッシングやレジスト剥離液により除去する。

【0055】

その後図3(C)に示すように、ゲート電極の側面を覆うように、絶縁膜、いわゆるサイドウォール119a~119cを形成する。サイドウォールは、プラズマCVD法や減

10

20

30

40

50

圧CVD( LPCVD )法を用いて、珪素を有する絶縁膜により形成することができる。本実施の形態では、減圧CVD( LPCVD )法により原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用い、圧力2 Torr( 266 パスカル )、温度400で、窒化した酸化珪素膜、いわゆる酸化窒化珪素( SiON )を形成する。またプラズマCVD法を用いてサイドウォールを形成する場合、原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用い圧力1 Torr( 133 パスカル )で窒化した酸化珪素膜( SiON )を形成することができる。その後、酸化窒化珪素膜( SiON )をエッティングすることにより、テーパー形状を有するサイドウォールを形成する。

#### 【 0 0 5 6 】

減圧CVD法を用いてサイドウォールを形成する場合のエッティング条件は以下の通りである。第1のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、数sec、例えば3 secかけてプラズマをたてる。このとき、成膜装置に配置された基板と対向する側の電極を475Wとし、基板が配置される電極を300Wとする。基板が配置される電極に印加する電圧により、エッティングガスのイオンを加速することができる。第2のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、数十sec、例えば60sec間電圧を印加する。エッティング対象となる膜の高さが所定値(本実施の形態では100nm)となるとき終了するように、エッティング時間を決定することができる。このとき、成膜装置に配置された基板と対向する側の電極を475Wとし、基板が配置される電極を300Wとする。第3のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、エッティング対象となる表面の膜が無くなつたと思われる時間から数十sec、例えば31sec間電圧を印加する。このとき、成膜装置に配置された基板と対向する側の電極を50Wとし、基板が配置される電極を450Wとする。10

#### 【 0 0 5 7 】

またプラズマCVD法を用いてサイドウォールを形成する場合のエッティング条件は以下の通りである。第1のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、数sec、例えば3 secかけてプラズマをたてる。このとき、成膜装置に配置された基板と対向する側の電極を475Wとし、基板が配置される電極を300Wとする。第2のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、数十sec、例えば50sec間電圧を印加する。エッティング対象となる膜の高さが残り100nmとなるとき終了するように、エッティング時間を決定することができる。このとき、成膜装置に配置された基板と対向する側の電極を900Wとし、基板が配置される電極を150Wとする。第3のエッティング条件として、原料ガスにCHF<sub>3</sub>、Heを用いて、エッティング対象となる表面の膜が無くなつたと思われる時間から数十sec、例えば30sec間電圧を印加する。このとき、成膜装置に配置された基板と対向する側の電極を50Wとし、基板が配置される電極を300Wとする。20

#### 【 0 0 5 8 】

以上のように形成されるサイドウォールの端部は、テーパー形状を有さなくともよく、垂直、つまり矩形状を有すると好ましい。サイドウォールを矩形状に形成すると、次に添加される不純物濃度がサイドウォール下方で濃度勾配を有することを防ぐことができるからである。

#### 【 0 0 5 9 】

このサイドウォール119a～119cを用いて、nチャネル型TFTの不純物領域に、高濃度不純物領域を形成120a～120cする。すなわち、ゲート電極109、及びサイドウォール119a～119cをマスクとして自己整合的に高濃度不純物領域120a～120cを形成する。このときpチャネル型のTFT上にはレジストマスク121を形成する。本実施の形態では、ホスフィン(PH<sub>3</sub>)を15～25kVでドーピングし、高濃度不純物領域、いわゆるソース領域及びドレイン領域を形成する。その後、レジストマスク121をO<sub>2</sub>アッシングやレジスト剥離液により除去する。40

#### 【 0 0 6 0 】

その後不純物領域を活性化するため加熱処理を行う。本実施の形態では、窒素雰囲気中で550に加熱する。50

## 【0061】

図4(A)に示すように、ゲート絶縁膜108、ゲート電極109を覆うように第1の絶縁膜122を形成する。第1の絶縁膜は窒素を有する絶縁膜であればよく、本実施の形態では、プラズマCVD法により100nmの窒化珪素を形成する。その後、加熱処理を行い、活性化を施す。本実施の形態では、窒素雰囲気中410で1時間の加熱処理を行う。その結果、不純物添加により生じた膜荒れ等を低減することができる。

## 【0062】

そして、第1の絶縁膜122を覆うように第2の絶縁膜123を形成する。第2の絶縁膜123は、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン)、珪素(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含み、また置換基にはフッ素、アルキル基、あるいは芳香族炭化水素のうち少なくとも1種を有する材料、いわゆるシロキサン、及びそれらの積層構造を用いることができる。有機材料として、ポジ型感光性有機樹脂又はネガ型感光性有機樹脂を用いることができる。例えば、有機材料としてポジ型の感光性アクリルを用いた場合、フォトリソフラフィ工程による露光処理により感光性有機樹脂をエッチングすると上端部に曲率を有する開口部を形成することができる。本実施の形態では、原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用いるプラズマCVD法により形成される窒化された酸化珪素膜を600nmの膜厚に形成する。このとき、基板の温度を300~450に加熱し、本実施の形態では400に加熱する。

10

20

## 【0063】

図4(B)に示すように、ゲート絶縁膜108、第1の絶縁膜122、第2の絶縁膜123に開口部、いわゆるコンタクトホールを形成し、不純物領域と接続する配線125a~125eを形成する。同時にゲート電極と接続する配線を形成する。このとき、開口部の直径を1.0μm程度とするため、開口部は垂直に開口するとよい。そのため、意図的にレジストマスク端部がテーパー形状とならない、つまり垂直となるように形成する。またレジストと、コンタクトホールを開口する絶縁膜との選択比が高ければ、絶縁膜のエッチングが早いため、レジスト端部がテーパー形状となっても構わない。本実施の形態では、第2の絶縁膜123に窒化された酸化珪素膜を用いるため、端部が垂直となるように、つまり意図的にテーパー形状とならないように形成されたレジストマスクを用いて、ドライエッチング法により開口部を形成する。エッチングガスにはCHF<sub>3</sub>、Heを用い、第1のエッチング時間として数sec、例えば3sec、第2のエッチング時間として100~130sec、例えば117sec、第3のエッチング時間として200~270sec、例えば256secとしてエッチングを行う。このとき、開口部のエッチング状況に応じて、エッチングガスの流量を決定することができる。

30

## 【0064】

なお第2の絶縁膜123に、有機材料やシロキサンを用いる場合、開口部の側面を垂直とするため、有機材料からなるレジストマスクよりも高硬度を有するレジストマスク、例えば酸化珪素膜等の無機材料から形成するレジストマスクを用いるとよい。

40

## 【0065】

その後、レジストマスクをO<sub>2</sub>アッシングやレジスト剥離液により除去する。

## 【0066】

そして開口部に配線125a~125eを形成する。配線は、アルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タンクステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。本実施の形態では、チタン膜/窒化チタン膜/チタン-アルミニウム合金膜/チタン膜(Ti/TiN/A1-Si/Ti)をそれぞれ60/40/300/100nmに積層したのち、所望の形状にパターニング及びエッチングして配線、つまりソース電極、ドレイン電極を形成する。

## 【0067】

以上のようにして、低濃度不純物領域を有するように形成するLDD構造からなり、ゲ

50

ート長が $1.0\text{ }\mu\text{m}$ 以下となるnチャネル型の薄膜トランジスタを形成することができる。また、低濃度不純物領域を有さないように形成するいわゆるシングル・ドレイン構造からなり、ゲート長が $1.0\text{ }\mu\text{m}$ 以下となるpチャネル型の薄膜トランジスタが完成する。pチャネル型の薄膜トランジスタは、ホットキャリアによる劣化や短チャネル効果が生じにくいことから、シングル・ドレイン構造とすることができる。勿論本発明において、pチャネル型の薄膜トランジスタをLDD構造としてもよい。さらにnチャネル型の薄膜トランジスタ、及びpチャネル型の薄膜トランジスタにおいて、LDD構造に代えて、低濃度不純物領域がゲート電極と重なる、いわゆるGOLD構造を有してもよい。なおゲート長が $1.0\text{ }\mu\text{m}$ 以下となるTFTをサブミクロントフトとも表記できる。

## 【0068】

10

そして、以上のように形成された薄膜トランジスタを有する半導体装置、本実施の形態においてはCPUを作製することができ、駆動電圧5Vで、動作周波数30MHzと高速動作が可能となった。

## 【0069】

その他の半導体装置としては、集積回路や半導体表示装置であって、特に液晶表示装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)等の半導体表示装置の画素部及び駆動回路部に本実施の形態のように形成された薄膜トランジスタを用いることもできる。

## 【0070】

20

## (実施の形態2)

半導体膜と、ゲート絶縁膜との界面特性は、TFTの電気特性に大きく影響を与える。そのため、ゲート絶縁膜形成前にフッ酸等により半導体膜の表面を洗浄している。このとき、半導体膜は所定の形状となるようにパターニングされているため、フッ酸処理により下地膜、特に半導体膜の側面に設けられた下地膜までが一部除去され、溝や凹部が形成されてしまう。このような形状でゲート絶縁膜、さらにはゲート電極が形成されると、段差被覆性が十分でないためゲート絶縁膜の耐圧不良の原因となってしまう。特に、ゲート絶縁膜の膜厚が薄くなるにつれ、耐圧不良は顕著な問題となってくる。そこで、本実施の形態では薄膜化する場合のゲート絶縁膜の作製方法について説明する。

## 【0071】

30

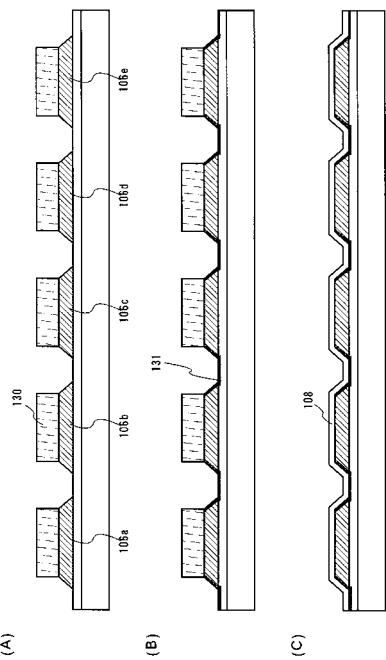

図5(A)に示すように、実施の形態1と同様に基板100、下地膜101、非晶質半導体膜102を形成する。非晶質半導体膜102を結晶化し、レジストマスク130を用いて島状の半導体膜106a～106eを形成する。

## 【0072】

その後図5(B)に示すように、島状の半導体膜をパターニングするときに用いるレジストマスク130を除去する前に、窒素雰囲気に曝して下地膜101の一部の表面、及び島状の半導体膜106a～106eの側面を窒化する。本実施の形態では、窒素( $N_2$ )、又はアンモニア( $NH_3$ )を用いたプラズマ処理により、下地膜101の表面の一部、及び島状の半導体膜106a～106eの側面に窒化領域131を形成する。窒化領域とは、下地膜や半導体膜の材料により、窒化珪素(SiN)又は酸化窒化珪素(SiON)となる。本実施の形態では、下地膜101の表面の一部は酸化窒化珪素(SiON)が形成され、半導体膜の側面には窒化珪素(SiN)が形成されている。なお、図5(B)において示す窒化領域131は模式図であり、実際の窒化される領域とは異なる場合がある。その結果、次に行うゲート絶縁膜形成前のフッ酸等による島状の半導体膜表面の洗浄を行っても、溝や凹部が形成されることを防止できる。

40

## 【0073】

そして図5(C)に示すように、実施の形態1と同様に、ゲート絶縁膜108を形成する。以降の工程は、実施の形態1を参照すればよいため、詳細な説明を省略する。

## 【0074】

そして、以上のように形成された薄膜トランジスタを有する半導体装置、本実施の形態

50

においては C P U を作製することができる。その他の半導体装置としては、集積回路や半導体表示装置であって、特に液晶表示装置、D M D 、P D P 、F E D 等の半導体表示装置の画素部及び駆動回路部に本実施の形態のように形成された薄膜トランジスタを用いることもできる。

#### 【0075】

(実施の形態3)

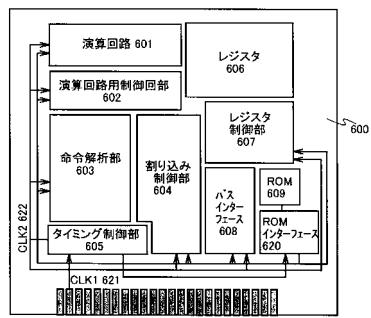

本実施の形態では、C P U の構成についてブロック図を用いて説明する。

#### 【0076】

図6に示すC P U は、基板600上に、演算回路(ALU: Arithmetic logic unit)601、演算回路用の制御部(ALU Controller)602、命令解析部(Instruction Decoder)603、割り込み制御部(Interrupt Controller)604、タイミング制御部(Timing Controller)605、レジスタ(Register)606、レジスタ制御部(Register Controller)607、バスインターフェース(Bus I/F)608、書き換え可能なROM609、ROMインターフェース(ROM I/F)620とを主に有している。またROM609及びROM I/F620は、別チップに設けても良い。

#### 【0077】

以上のような各種回路を実施の形態1、2に示した方法により形成されるガラス基板上の薄膜トランジスタを用いて構成することができる。

#### 【0078】

勿論、図6に示すC P U は、その構成を簡略化して示した一例にすぎず、実際のC P U はその用途によって多種多様な構成を有している。

#### 【0079】

バスインターフェース608を介してC P U に入力された命令は、命令解析部603に入力され、デコードされた後、演算回路用の制御部602、割り込み制御部604、レジスタ制御部607、タイミング制御部605に入力される。

#### 【0080】

演算回路用の制御部602、割り込み制御部604、レジスタ制御部607、タイミング制御部605は、デコードされた命令に基づき、各種制御を行う。具体的に演算回路用の制御部602は、演算回路601の動作を制御するための信号を生成する。また、割り込み制御部604は、C P U のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部607は、レジスタ606のアドレスを生成し、C P U の状態に応じてレジスタ606の読み出しや書き込みを行う。

#### 【0081】

またタイミング制御部605は、演算回路601、演算回路用の制御部602、命令解析部603、割り込み制御部604、レジスタ制御部607の動作のタイミングを制御する信号を生成する。例えばタイミング制御部605は、基準クロック信号C L K 1(621)を元に、内部クロック信号C L K 2(622)を生成する内部クロック生成部を備えており、クロック信号C L K 2を上記各種回路に供給する。

#### 【0082】

また本実施の形態では、半導体装置としてC P U を例に挙げて説明したが、本発明のガラス基板上に形成された薄膜トランジスタは、有機発光素子に代表される発光素子を各画素に備えた表示装置を作製することができる。その他の半導体装置としては、集積回路や半導体表示装置であって、特に液晶表示装置、D M D 、P D P 、F E D 等の半導体表示装置の画素部及び駆動回路部に用いることができる。本発明を適用して作製される半導体装置の具体例として、デジタルカメラ、カーオーディオなどの音響再生装置、ノート型パソコン、携帯電話機、携帯型ゲーム機等)、家庭用ゲーム機などの記録媒体を備えた画像再生装置などが挙げられる。

10

20

30

40

50

**【 0 0 8 3 】**

特に本発明により形成される薄膜トランジスタはゲート長が小さいため、駆動回路部に用いることによる駆動電圧の低下が期待できる。また本発明のゲート長が小さい薄膜トランジスタにより、高精細化が進む、すなわち各画素の間隔が小さくなる画素部に対応することができる。

**【 0 0 8 4 】**

その結果、ガラス基板の場合は廉価な機材で実現でき、低コストなCPU、その他の半導体装置を作製することができる。

**【 0 0 8 5 】**

(実施の形態4)

10

本実施の形態では、CPUの形態について説明する。

**【 0 0 8 6 】**

図7には、画素部と、CPU、その他の回路が同一基板に形成された表示装置、いわゆるシステムオンパネルを示す。基板700上に画素部701、画素部701が有する画素を選択する走査線駆動回路702と、選択された画素にビデオ信号を供給する信号線駆動回路703とが設けられている。走査線駆動回路702、及び信号線駆動回路703から引き回される配線によりCPU704、その他の回路、例えばコントロール回路705とが接続されている。なおコントロール回路にはインターフェースが含まれている。そして、基板の端部にFPC端子との接続部を設け、外部信号とのやりとりを行う。

**【 0 0 8 7 】**

20

その他の回路として、映像信号処理回路、電源回路、階調電源回路、ビデオRAM、メモリ(DRAM、SRAM、PROM)等を基板上に設けることができる。またこれら回路は、ICチップにより形成し、基板上に実装してもよい。さらに必ずしも走査線駆動回路702、及び信号線駆動回路703を同一基板に形成する必要はなく、例えば走査線駆動回路702のみを同一基板に形成し、信号線駆動回路703をICチップにより形成し、実装してもよい。

**【 0 0 8 8 】**

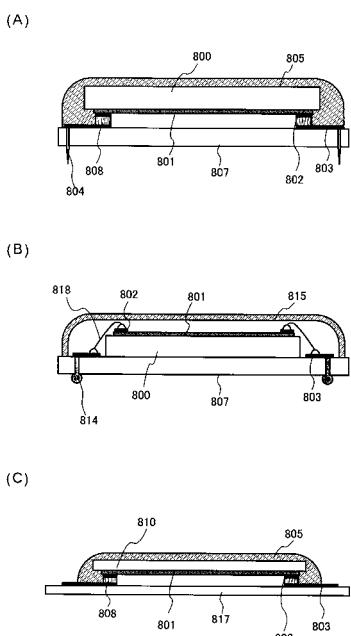

図8(A)には、パッケージングされたCPUの形態を示す。基板800上に形成されたCPUの機能を有する薄膜トランジスタアレイ801を、CPU表面に設けられた電極(ソース電極やドレイン電極、又はそれらの上に絶縁膜を介して形成された電極等)802が下側となるフェイスダウン状態とする。基板800は、ガラス、プラスチックを用いることができる。また銅やその合金で形成される配線803が設けられた配線基板、例えばプリント基板807を用意する。プリント基板807には、接続端子(ピン)804が設けられている。そして電極802と、配線803とを異方性導電膜808等を介して接続する。その後、エポキシ樹脂等の樹脂805で基板800上方から覆い、パッケージングされたCPUとして完成する。または中空に保った状態で外周をプラスチックなどで囲んでもよい。

30

**【 0 0 8 9 】**

図8(B)には、図8(A)と異なり、CPU表面に設けられた電極802が上側となるフェイスアップ状態とする。そしてプリント基板807上に基板800を固定し、電極802と、配線803とをワイヤ818により接続する。このようにワイヤにより接続することをワイヤボンディングという。そして電極802と、配線803に接続されるバンプ814とが接続する。その後、中空に保った状態で外周をプラスチック815等で囲み、パッケージングされたCPUとして完成する。

40

**【 0 0 9 0 】**

図8(C)には、フレキシブル性を有する基板、例えばFPC(Flexible printed circuit)上に、CPUの機能を有する薄膜トランジスタアレイ801を固定する例を示す。基板810に形成されたCPUの機能を有する薄膜トランジスタアレイ801を、CPU表面に設けられた電極802が下側となるフェイスダウン状態とする。基板810には、ガラス、石英、金属、バルク半導体、プラスチックを用いることができるが、図8(C)

50

ではフレキシブル性の高いプラスチックを用いると好ましい。また、銅やその合金で形成される配線 803 が設けられたフレキシブル性を有する FPC817 を用意する。そして、電極 802 と、配線 803 とを異方性導電膜 808 を介して接続する。その後、エポキシ樹脂等の樹脂 805 で基板 800 上方から覆い、パッケージングされた CPU として完成する。

#### 【0091】

このようにパッケージングされた CPU は、外部から保護され、さらに携帯しやすくなる。そして所望箇所に、CPU を実装することができ、特に図 8 (C) のようにフレキシブル性を有すると、実装する位置の自由度が高まる。またパッケージングすることにより CPU の機能を補助することもできる。

10

#### 【0092】

以上のように、ガラス基板上の薄膜トランジスタにより形成される CPU は、多様な形態をとることができ。そして、ガラス基板上の薄膜トランジスタにより形成される CPU は軽量であるため、携帯や実装するときの負担を軽減することができる。

#### 【0093】

##### (実施の形態 5)

本実施の形態では、上記実施の形態と異なる作製工程について説明する。

#### 【0094】

図 9 (A) に示すように、上記実施の形態と同様にレジストマスク 110 まで形成し、これを用いて、導電膜 109b をエッチングする。

20

#### 【0095】

その後、図 9 (B) に示すように、レジストマスク 110 を除去する。そして図 9 (C) に示すように、エッチングされた導電膜 109b を用いて、導電膜 109a をエッチングする。このようにレジストマスクを用いずに、導電膜 109a をエッチングしてもよい。

#### 【0096】

その後の工程は、上記実施の形態を参照することができる。

#### 【0097】

本実施の形態のように、レジストマスクを除去した後、エッチングされた導電膜 109b を用いて、導電膜 109a をエッチングすると、レジストマスクの形状の影響を受けることなく、導電膜をエッチングすることができる。

30

#### 【0098】

以上のように形成された薄膜トランジスタを有する半導体装置、例えば CPU を作製することができ、高速動作が可能となる。

#### 【図面の簡単な説明】

#### 【0099】

【図 1】本発明の薄膜トランジスタの作製工程を示す図。

【図 2】本発明の薄膜トランジスタの作製工程を示す図。

【図 3】本発明の薄膜トランジスタの作製工程を示す図。

【図 4】本発明の薄膜トランジスタの作製工程を示す図。

40

【図 5】本発明の薄膜トランジスタの作製工程を示す図。

【図 6】本発明の半導体装置の一つである、CPU のブロック図。

【図 7】本発明の半導体装置の一つである CPU が実装された表示装置を示す図。

【図 8】本発明の半導体装置の一つである CPU がパッケージングされた図。

【図 9】本発明の薄膜トランジスタの作製工程を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/49 (2006.01) H 01 L 29/58 G

H 01 L 21/027 (2006.01) H 01 L 21/30 5 7 6

(56)参考文献 特開2003-045857(JP,A)

特開2002-033273(JP,A)

特開2002-203862(JP,A)

特開2003-186421(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

H 01 L 29 / 786