(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5007250号

(P5007250)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月1日(2012.6.1)

(51) Int.Cl.

**H01L 23/12 (2006.01)**

**H01L 21/3205 (2006.01)**

**H01L 21/768 (2006.01)**

**H01L 23/522 (2006.01)**

**H01L 27/04 (2006.01)**

F 1

**H01L 23/12 501 P**

**H01L 21/88 T**

**H01L 27/04 E**

請求項の数 1 (全 22 頁) 最終頁に続く

(21) 出願番号 特願2008-33012 (P2008-33012)

(22) 出願日 平成20年2月14日 (2008.2.14)

(65) 公開番号 特開2009-194144 (P2009-194144A)

(43) 公開日 平成21年8月27日 (2009.8.27)

審査請求日 平成23年2月3日 (2011.2.3)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 小出 優樹

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 南 正隆

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 坂本 薫昭

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

(a) 半導体基板上に多層配線を形成した後、前記多層配線を覆うように前記半導体基板上に第1絶縁膜を形成する工程、

(b) 前記第1絶縁膜上に第2絶縁膜を形成する工程、

(c) 前記多層配線の最上配線の一部上の前記第1絶縁膜および前記第2絶縁膜に、前記最上配線の一部を露出する第1開口部を形成する工程、

(d) 電解メッキ法を用いて、前記第1開口部の内部を埋め込むように前記第2絶縁膜上に第1パターンを構成する再配線を形成すると共に、前記第1パターンとは電気的に分離されるように前記第2絶縁膜上に第2パターンを構成する前記再配線を形成する工程、

(e) 前記再配線を覆うように前記半導体基板上に第3絶縁膜を形成した後、前記第1パターンの一部上であって、前記第1パターンの一部を露出する第2開口部を前記第3絶縁膜に形成する工程、

を含み、

前記工程(d)では、前記第1パターンと前記第2パターンとが前記半導体基板の面内で混在するように前記再配線を形成し、

(f) 前記工程(d)前に、計算機を用いた自動設計によって、前記第1パターンおよび前記第2パターンを前記半導体基板の面内で位置決めする工程、

を更に含み、

前記工程(f)は、

10

20

(f1) 前記半導体基板の面内に前記第1パターンを配置した第1処理パターンを形成する工程、

(f2) 前記半導体基板の全面に前記第2パターンを配置した第2処理パターンを形成する工程、

(f3) 前記第1処理パターンと前記第2処理パターンを合成する工程、

(f4) 前記工程(f3)の後、前記第1パターンから一定の間隔内にある前記第2パターンを算出し、削除する工程、

を含むことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、半導体装置および半導体装置の製造技術に関し、特に、WPP(Wafer Process Package)技術における再配線を有する半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

WPP技術(またはWLP(Wafer Level Package)技術ともいう)は、ウエハプロセス(前工程)とパッケージプロセス(後工程)とを一体化し、ウエハ状態でパッケージングを完了する技術であり、半導体ウエハから切断した半導体チップ毎にパッケージプロセスを処理する技術に比べて工程数を大幅に削減できるという利点がある。WPP技術のパッケージプロセスにおいては、その前工程で形成された半導体素子と電気的に接続される再配線がメッキ法によって形成され、再配線が表面保護膜で覆われる。

20

【0003】

なお、特開平9-306914号公報(特許文献1)には、半導体素子の配線形成方法としてダミーメッキパターンを実際の配線となる本パターンと共に半導体ウエハ上に設ける技術が開示されている。この特許文献1は、半導体素子の配線として均一なメッキ配線を安定に形成することを主題とするものであり、WPP技術における再配線を安定に形成する観点についての記載はされていない。

【特許文献1】特開平9-306914号公報

30

【発明の開示】

【発明が解決しようとする課題】

【0004】

例えば、高速SRAM(Static Random Access Memory)やCMOS(Complementary Metal Oxide Semiconductor)ロジック製品では、パッケージコストの低減および高速化などを目的としてWPP技術が採用されており、それらはハンダよりなるバンプ電極で実装基板にフリップチップ接続するようなパッケージ構造となっている。

【0005】

例えば、WPP技術では以下に示すような工程を経ることにより半導体装置を製造することができる。まず、半導体ウエハの主面上にMISFET(Metal Insulator Semiconductor Field Effect Transistor)などの半導体素子を形成し、その半導体素子の上部に多層配線(複数の配線層)を形成する。次いで、多層配線上に、窒化シリコン膜および酸化シリコン膜を形成し、さらに酸化シリコン膜上にポリイミド樹脂膜を形成する。なお、これまでの工程がWPP技術のウエハプロセスとなり、以下の工程がWPP技術のパッケージプロセスとなる。

40

【0006】

続いて、酸化シリコン膜、窒化シリコン膜およびポリイミド樹脂膜をパターニングすることにより、底面に多層配線の最上配線が露出する開口部を形成する。そして、開口部内を含むポリイミド樹脂膜上に薄い電極層(バリア層/シード層)を形成し、この電極層上にメッキ法を使用して再配線を形成する。再配線は、例えば銅膜とニッケル膜の積層膜から構成される。次いで、再配線上にポリイミド樹脂膜を形成した後、パターニングするこ

50

とにより、再配線の一端部を露出させる。その後、露出した再配線の一端部上にバンプ電極を形成する。これにより、半導体ウエハの状態でパッケージングされ、再配線および再配線に接続されたバンプ電極を有する半導体装置を製造することができる。

#### 【0007】

このようなW P P技術を用いた半導体装置において、メッキ法を使用して形成した再配線では外観異常（例えば粒径の粗大化、面荒れ）や半導体ウエハの中心部と周辺部での膜厚に差が生じる問題があることを本発明者らは見出した。特に、半導体ウエハの中心部では、再配線の膜厚が薄く、かつ外観異常が著しい。さらに、外観異常のある再配線の一端部上に形成されたバンプ電極では、剥がれなどによる半導体装置の信頼性を低下させてしまう。このため、再配線の外観異常を不良と判断することによる半導体装置の製造歩留まりが低下する。10

#### 【0008】

本発明者らの検討によると、再配線の外観異常は、再配線パターンに依存性があり、半導体素子と電気的に接続された再配線が形成されている領域Aと、再配線が形成されていない領域Bとの境界付近の再配線の端部に集中していた。すなわち、メッキ法の観点からその境界の再配線の端部では電界集中がし易く、電流密度が局所的に増大し、再配線の結晶粒径が粗大化したと考えられる。このため、再配線の外観異常の対策として、再配線が形成されていない領域Bにも、再配線を配置することが考えられる。しかしながら、単に領域Bに再配線を配置しただけでは、再配線の疎密差によって、再配線の端部に外観異常が生じる場合もある。そこで、前述の領域Aのような局所的（Local）な領域においても、再配線の疎密差が大きくなることを防止する必要がある。20

#### 【0009】

また、半導体ウエハの中心部と周辺部での再配線の膜厚差の原因としては、再配線形成時のメッキ電流値が半導体ウエハ面内における再配線の占有率に依存し、適正な膜厚を得るためにメキシ電流を確保できなかったと考えられる。このため、半導体ウエハ面内領域の再配線の占有率で、メキシ膜厚（再配線の膜厚）差を低減する必要がある。

#### 【0010】

本発明の目的は、半導体装置の信頼性を向上させる技術を提供することにある。

#### 【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。30

#### 【課題を解決するための手段】

#### 【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0013】

本発明の一実施の形態では、W P P技術における再配線が半導体基板の面内において互いに電気的に分離された本体パターン（第1パターン）およびダミーパターン（第2パターン）を有している。多層配線と電気的に接続された本体パターンと、フローティングされたダミーパターンとが、半導体基板の面内で混在して設けられている。40

#### 【発明の効果】

#### 【0014】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0015】

この一実施の形態によれば、半導体基板の面内に配置された再配線の疎密差を低減するので、半導体装置の信頼性を向上することができる。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明50

するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する場合がある。また、以下の実施の形態を説明する図面においては、構成を分かり易くするために平面図であってもハッチングを付す場合がある。

#### 【0017】

##### (実施の形態1)

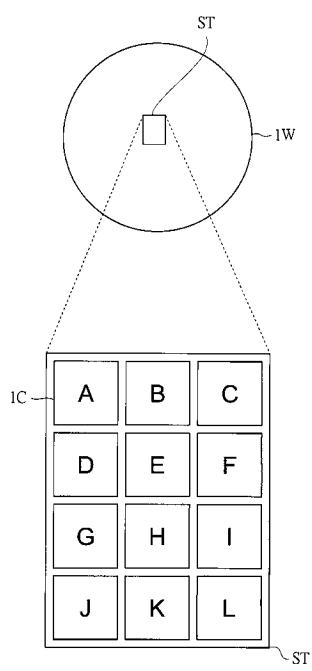

本実施の形態における半導体装置は、CSP (Chip Size Package) 構造の半導体装置であり、その製造のためにWPP技術を用いたものである。CSPは、半導体チップのサイズと同等またはわずかに大きいパッケージの総称であり、小型化・軽量化を実現できる上、内部の配線長を短くすることができる、信号遅延や雑音等を低減できる。まず、本実施の形態における半導体装置の特徴的な構造について、図1～図3を参照して説明する。

10

#### 【0018】

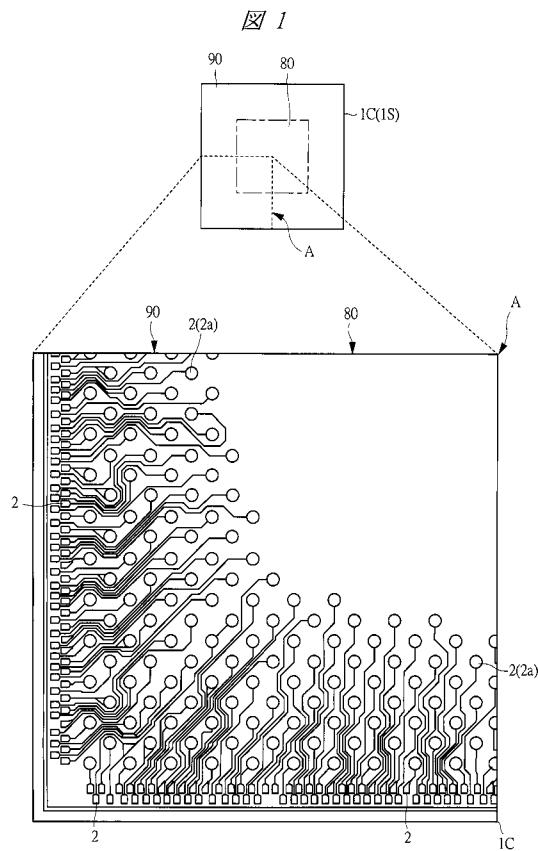

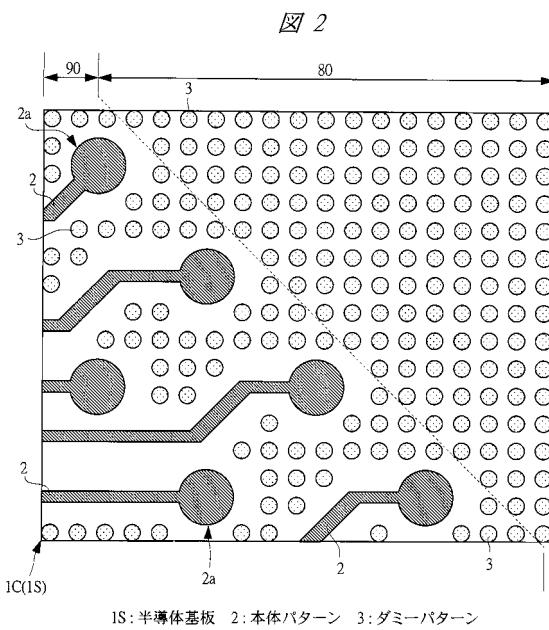

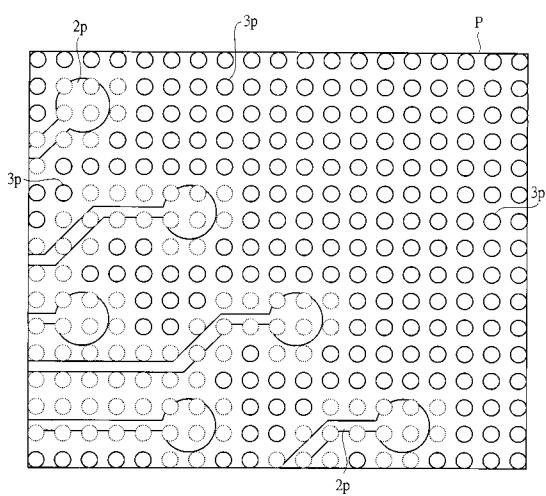

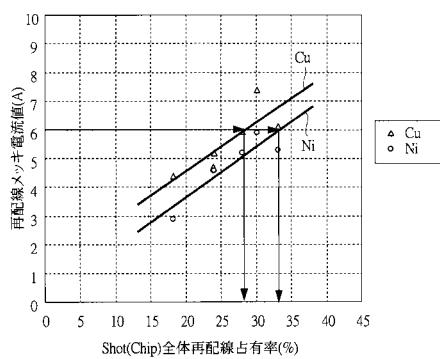

図1に本実施の形態における半導体チップ1Cの平面を模式的に示すと共に、その一部（破線で囲まれた領域A）を拡大して示し、また、図2に図1で示した半導体チップ1Cの平面をより拡大して示す。図2中に示す本体パターン2およびダミーパターン3がWPP技術における再配線であるが、図1では説明を容易にするために、ダミーパターン3を省略して示している。本体パターン2は半導体チップ1Cの半導体素子などから構成される内部回路と電気的に接続され、ダミーパターン3は電気的に分離、すなわちフローティングされているものである。また、図3に半導体チップ1Cの要部断面を模式的に示す。

20

#### 【0019】

図1に示すように、矩形状の半導体チップ1Cは、その面内の中心領域80（一点破線で囲まれた領域）および中心領域80の周囲の周辺領域90を有している。半導体チップ1Cの表面は例えばポリイミド樹脂膜からなる表面保護膜で覆われており、その表面保護膜に設けられた開口部には、外部と半導体チップ1C内部との信号の受け渡しを行うバンプ電極（図示しない）が設けられている。このバンプ電極は、図1中の拡大した領域Aにおける半導体チップ1Cで示す本体パターン2のランド電極2a上に設けられる。CSP構造の半導体装置のような小型化に対応した半導体チップ1Cでも、本体パターン2（再配線）を半導体チップ1Cの外周から中心領域80側に引き回すことによってバンプ電極が形成される領域（ランド電極2aの面積）を確保することができる。なお、この本体パターン2は周辺領域90に設けられている。

30

#### 【0020】

図2に示すように、半導体チップ1Cの面内では、本体パターン2とダミーパターン3とが混在して設けられている。これらはWPP技術における再配線として、同時に形成されたものであり、互いに電気的に分離されているものである（図3参照）。本体パターン2は前述したように周辺領域90に設けられており、ダミーパターン3は中心領域80および本体パターン2間に位置する周辺領域90に設けられている。このようにダミーパターン3を中心領域80および周辺領域90に設けることにより、半導体チップ1Cの面内で再配線がほぼ均等に分布し、ダミーパターン3がない場合より再配線の疎密差を低減できる。

30

#### 【0021】

本体パターン2の一端に位置する円形状のランド電極2aは、径が例えば $108\mu m$ であり、ピッチが例えば $180\mu m$ である。また、円形状のダミーパターン3は、径が例えば $34\mu m$ であり、ピッチが例えば $50\mu m$ である。なお、ダミーパターン3の平面形状は、角部での応力緩和するため全ての角が鈍角の多角形状であっても良い。

40

#### 【0022】

また、ダミーパターン3の加工寸法は、本体パターン2の加工寸法以下としている。これにより、周辺領域90における本体パターン2間に、ダミーパターン3を設けることができ、半導体チップ1Cの面内で再配線がほぼ均一に分布する。なお、ダミーパターン3の大きさは、再配線の最小線幅以上及び再配線形成後のバリア層およびシード層の除去工程において消失しない大きさとしている。

50

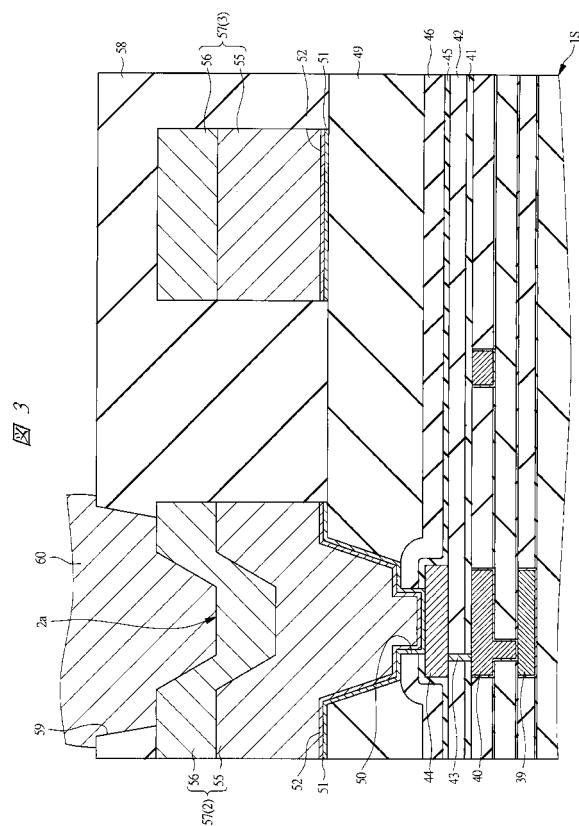

## 【0023】

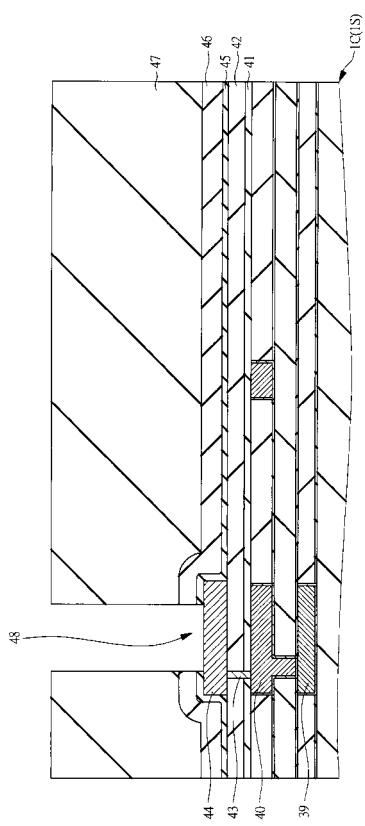

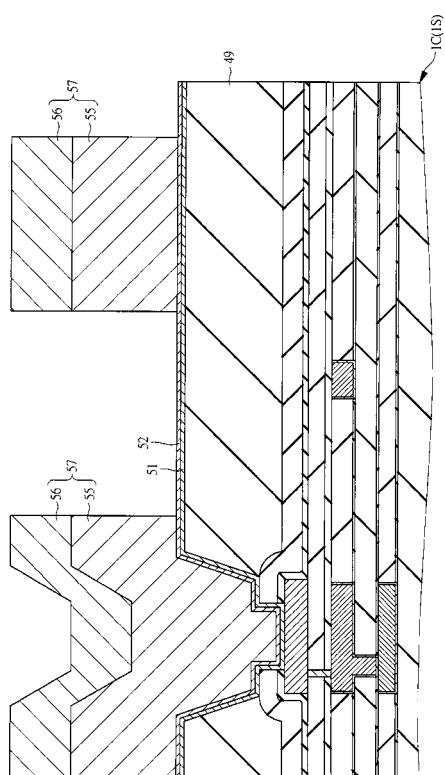

図3に示すように、半導体チップ1Cを構成する半導体基板1S上には、第3層配線39、第4層配線40、第5層配線44を含む多層配線が設けられている。この多層配線は、多層配線の下部に設けられている複数の半導体素子を電気的に接続して回路を形成する役割を有している。この多層配線を覆うように半導体基板1S上には、パッシベーション膜として、例えば薄い酸化シリコン膜45および窒化シリコン膜46が設けられている。これら酸化シリコン膜45および窒化シリコン膜46は、無機系絶縁膜であり、例えばプラズマCVDで形成することができる。

## 【0024】

また、窒化シリコン膜46上には、絶縁膜として、例えば有機系絶縁膜であるポリイミド樹脂膜49が設けられている。このポリイミド樹脂膜49上には、メッキ法によって形成された銅膜55およびニッケル膜56が積層してなる再配線57が設けられている。この再配線57は、図1および図2に示すように、本体パターン2とダミーパターン3を構成している。また、再配線57を覆うようにポリイミド樹脂膜49上には、表面保護膜(絶縁膜)として、例えば有機系絶縁膜であるポリイミド樹脂膜58が設けられている。

10

## 【0025】

表面保護膜として、ポリイミド樹脂等のような有機系絶縁膜としたのは、最上の絶縁膜を無機系絶縁膜とすると半導体チップの取り扱い(搬送等)時に絶縁膜にクラックが入り易くその取り扱いが困難となるので、比較的軟らかい有機系絶縁膜を最上層として半導体チップの取り扱いを容易にするためである。

20

## 【0026】

本体パターン2の再配線57の一部上であってポリイミド樹脂膜58には、開口部59が設けられており、本体パターン2の再配線57の一部が露出してランド電極2aを構成している。このランド電極2aが半導体チップ1Cの外部電極としての役割をする。さらに、外部との信号の受け渡しや、外部と実装による接続を行うために、ランド電極2a上に、それと電気的に接続するようにバンプ電極60を設けている。なお、バンプ電極60を設けずに、ランド電極2a上にワイヤボンディングを接続して、外部との信号の受け渡しを行うこともできる。

## 【0027】

再配線57は、半導体ウエハのレベルでパッケージングを完成するために設けられたものであり、多層配線の最上配線である第5層配線44とバンプ電極60とを接続する機能を有している。すなわち、再配線57は、第5層配線44とバンプ電極60とを接続する引き出し配線の役割を有する。別の言い方をすれば、再配線57は、第5層配線44の間隔をバンプ電極60の間隔へ変換するインタポーバととしての機能を有しているとも言える。

30

## 【0028】

本体パターン2の再配線57は、多層配線の最上配線である第5層配線44の一部上であって酸化シリコン膜45、窒化シリコン膜46およびポリイミド樹脂膜49に設けられた開口部50で、第5層配線44を含む多層配線と電気的に接続され、外部との信号との受け渡しの役割をする。

## 【0029】

40

その一方で、ダミーパターン3の再配線57は、有機系絶縁膜であるポリイミド樹脂膜49およびポリイミド樹脂膜58に覆われており、多層配線および本体パターン2と電気的に分離されており、フローティング状態となっている。このため、ダミーパターン3は外部との信号の受け渡しを行わない。しかしながら、ダミーパターン3を設けることによつて、メッキ法で形成される再配線の疎密差を低減し、本体パターン2の外観異常が発生するのを防止することができる。さらに、外観異常のない本体パターン2上に設けられたバンプ電極60が剥がれる等の市場不良を防止できるので、半導体装置の信頼性を向上することができる。

## 【0030】

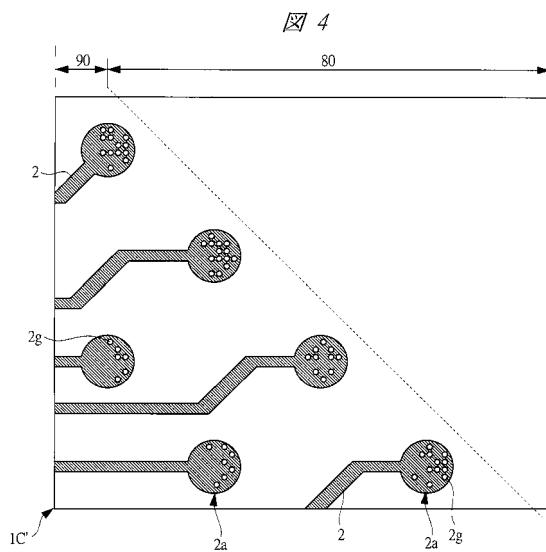

ここで、ダミーパターン3を設けない場合について、図4を参照して説明する。図4は

50

図2に対応する本発明者らが検討した半導体チップ1C'の平面を拡大して示す説明図である。なお、その他の構成は、図1～図3に示した半導体チップ1Cの構成と同様である。

### 【0031】

図4に示すように、本体パターン2が設けられている周辺領域90や、本体パターン2が設けられていない中心領域80にダミーパターンを設けない場合には、中心領域80と周辺領域90の境界付近の本体パターン2の端部(ランド電極2a)には、メッキ法で形成された銅(銅膜55)またはニッケル(ニッケル膜56)の粒2gが粗大化して、面荒れを起こして外観異常が生じている。さらに、外周領域90の内側であって本体パターン2間ににおいても、本体パターン2には、外観異常が生じていることがわかる。10なお、外観異常は顕微鏡によって確認することができる。

### 【0032】

しかしながら、本実施の形態では、ダミーパターン3を本体パターン2と混在させることによって、図2で示したように、本体パターン2の外観異常が発生するのを防止することができる。具体的には、再配線57の本体パターン2が形成される周辺領域90以外の中心領域80にダミーパターン3として再配線57を設けることによって、本体パターン2の外観異常が発生するのを防止することができる。さらに、再配線57の本体パターン2が形成される周辺領域90の本体パターン2間にダミーパターン3の再配線57を設けることによって本体パターン2の外観異常が発生するのをより防止することができる。これは、例えば本体パターン2間のような局所的な領域においてメッキ法で形成される本体パターン2およびダミーパターン3から構成される再配線57の疎密差が低減されたためであると考えられる。20

### 【0033】

また、本実施の形態では、WPP技術のパッケージプロセスにおける再配線57が有機系絶縁膜であるポリイミド樹脂膜49上に設けられ、その再配線57を覆うように表面保護膜として有機系絶縁膜であるポリイミド樹脂膜58が設けられている。これによりダミーパターン3をフローティング状態(電気的に分離した状態)としているが、ポリイミド樹脂膜49とポリイミド樹脂膜58の密着性は、同質の有機系絶縁膜を用いているので確保することができる。

### 【0034】

また、低温と高温との温度サイクルを繰り返す信頼性試験によって再配線57および再配線57の周囲にあるポリイミド樹脂膜49、58に膨張・収縮が発生するが、本体パターン2の加工寸法以下で、ダミーパターン3を加工することによって、発生した応力を緩和することができる。30

### 【0035】

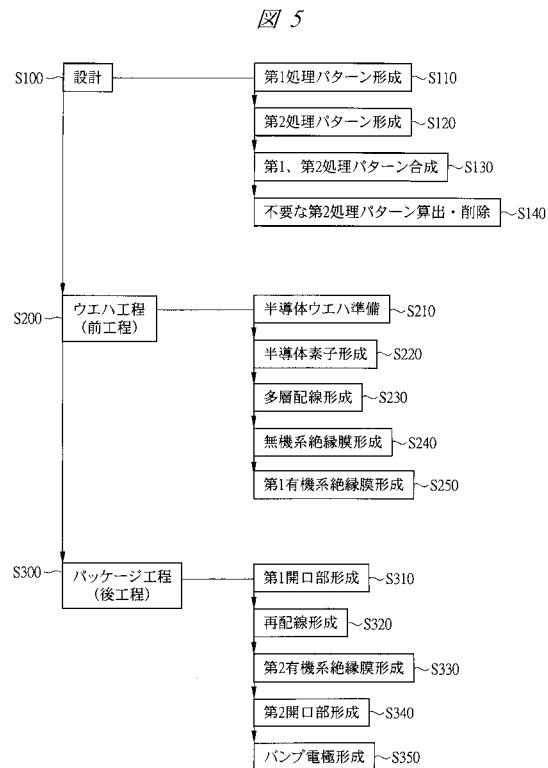

次に、本実施の形態における半導体装置の製造方法について、図5～図20を参照して説明する。図5に本実施の形態における半導体装置の製造工程の流れ図を示し、図6～図10に設計工程における処理パターンを示し、図11～図18にウエハ工程およびパッケージ工程における半導体装置の平面または断面を示す。

### 【0036】

図5に示すように、本実施の形態における半導体装置の製造工程は概略すると、まず設計工程(S100)により、半導体素子のレイアウト、回路配線などの設計が行われる。次いで、ウエハ工程(S200)では、半導体装置の製造におけるいわゆる前工程が行われ、半導体素子などが形成される。次いで、パッケージ工程(S300)では、半導体装置の製造におけるいわゆる後工程が行われ、引き出し配線としての再配線が形成されるとともに、パッケージングされる。なお、WPP技術は、このウエハ工程とパッケージ工程を半導体ウエハ状態で行うものである。40

### 【0037】

まず、設計工程(S100)において、特に、再配線57のパターン設計について説明する。なお、その他の構成についての設計は、DFM (design for manufacturing) を考50

慮して、例えば計算機を用いた周知の方法などにより行うことができる。

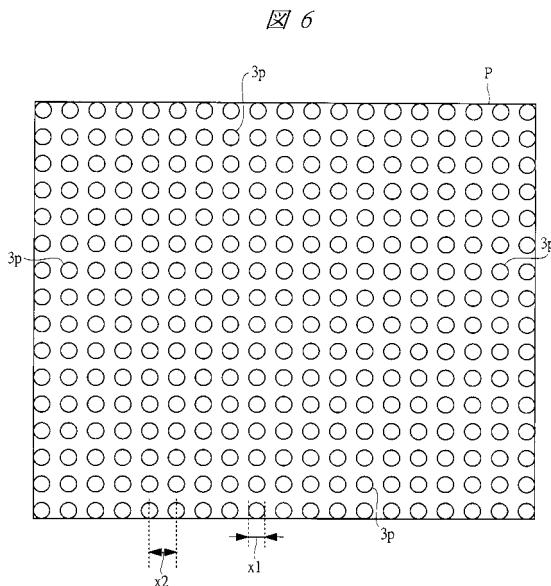

#### 【0038】

図6に示すように、計算機を用いて、半導体ウエハ(半導体チップ)などの所定の領域を想定した領域Pに、所定の径 $\times$ 1および所定のピッチ $\times$ 2でダミー処理パターン3pを形成する(S110)。ダミー処理パターン3pは、例えば、平面形状が64角形とし、径 $\times$ 1が34μm、ピッチ $\times$ 2が50μmとし、領域P内に均等に配置される。なお、設計の最終段階までに不要なダミー処理パターン3pは除去される。除去されずに残存したダミー処理パターン3pによって、前述した再配線57のダミーパターン3が、再配線57の最小線幅及び最小間隔より大きくかつ再配線57の本体パターン2のランド電極2aより小さくなるように設計される。

10

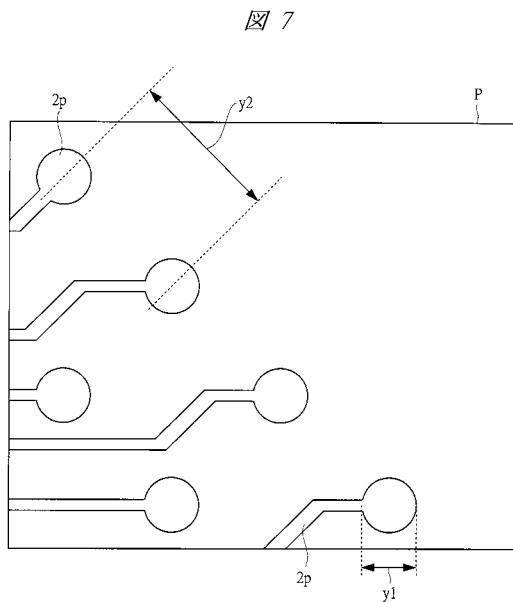

#### 【0039】

続いて、図7に示すように、計算機を用いて、領域Pに本体処理パターン2pを形成する(S120)。この本体処理パターン2pは、前述したような引き出し配線として用いられる再配線57(本体パターン2)の処理パターンである。なお、ランド電極2aとなる本体処理パターン3pの先端部は、例えば、平面形状が円形状とし、径y1が108μm、ピッチy2が180μmとして配置されている。

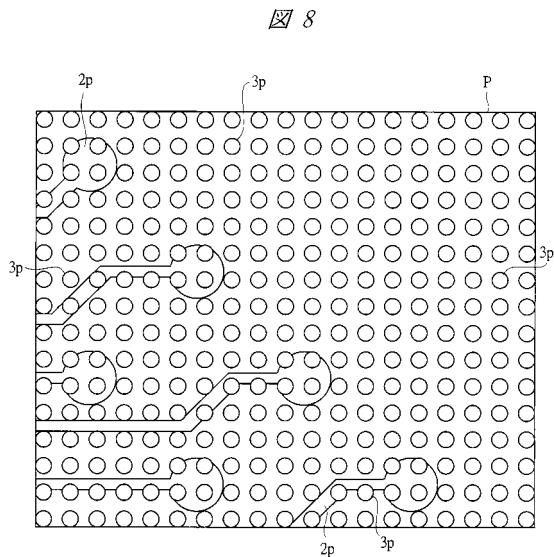

#### 【0040】

続いて、図8に示すように、計算機を用いて、本体処理パターン2pとダミー処理パターン3pとを合成する(S130)。次いで、図9に示すように、計算機を用いて、本体処理パターン2pから規定スペース内にあるダミー処理パターン3p(図中、破線で示している)を算出し、図10に示すように、その規定スペース領域内にあるダミー処理パターン3pを削除する(S140)。これにより、図2に示したような本体パターン2とダミーパターン3を構成する再配線57の疎密差を低減して配置することができる。

20

#### 【0041】

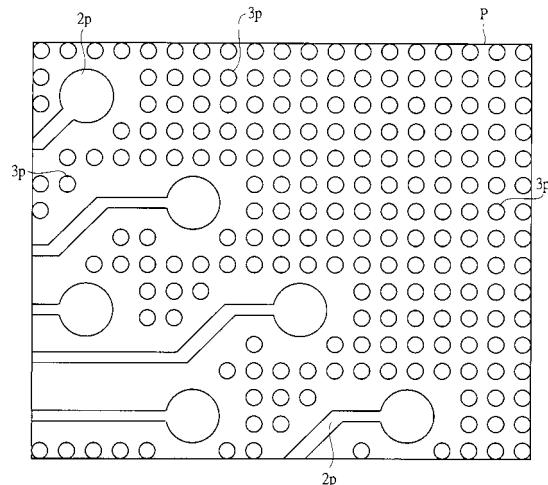

次に、ウエハ工程(S200)について説明する。図11に示すように、例えばショット領域STに複数のチップ領域(A~L)を有する略円形状の半導体ウエハ1Wを準備する(S210)。なお、図11の半導体ウエハ1Wでは、オリエンテーションフラットは図示していない。

#### 【0042】

本実施の形態では、半導体ウエハ1Wの複数のチップ領域(A~L)から、前述の半導体チップ1Cが取り出される。すなわち、複数のチップ領域(A~L)の全ての半導体チップ1Cは、WPP技術における、本体パターン2およびダミーパターン3で構成される再配線57が形成されることとなる。

30

#### 【0043】

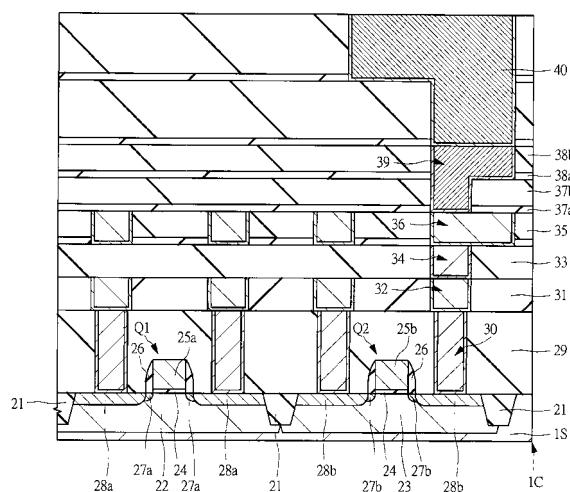

続いて、図12に示すように、半導体ウエハ1W(以下、半導体基板1Sとして説明する)の主面にnチャネル型MISFETQ1、pチャネル型MISFETQ2などの半導体素子を形成する(S220)。これらMISFETは、例えば高速SRAMやロジック回路を構成するものである。

#### 【0044】

例えばシリコン単結晶からなる半導体基板1Sの主面には、例えばSTI(Shallow Tranch Isolation)構造をした素子分離領域21が形成されており、素子分離領域21で活性領域が分離されている。活性領域のうちnチャネル型MISFETQ1を形成する領域には、p型ウェル22が形成されており、pチャネル型MISFETQ2を形成する領域には、n型ウェル23が形成されている。p型ウェル22は、例えばホウ素(B)などのp型不純物が導入された半導体領域となっており、n型ウェル23は、例えばリン(P)や砒素(As)などのn型不純物が導入された半導体領域となっている。

40

#### 【0045】

p型ウェル22上にはnチャネル型MISFETQ1が形成されている。このnチャネル型MISFETQ1の構成は以下のようになっている。すなわち、p型ウェル22上にゲート絶縁膜24が形成されており、このゲート絶縁膜24上にゲート電極25aが形成

50

されている。ゲート絶縁膜24は、例えば酸化シリコン膜から形成されるが、酸化シリコン膜より誘電率の高い高誘電体膜から形成してもよい。ゲート電極25aは、例えばポリシリコン膜から形成されるが、このポリシリコン膜には、例えばn型不純物が導入されている。これは、nチャネル型MISFETQ1のしきい値電圧を下げるために行なわれる。

#### 【0046】

ゲート電極25aの両側の側壁には、サイドウォール26が形成されており、このサイドウォール26下のp型ウェル22内には、低濃度n型不純物拡散領域27aが形成されている。そして、この低濃度n型不純物拡散領域27aの外側には、高濃度n型不純物拡散領域28aが形成されている。10 低濃度n型不純物拡散領域27aおよび高濃度n型不純物拡散領域28aは、n型不純物を導入した半導体領域となっており、低濃度n型不純物拡散領域27aよりも高濃度n型不純物拡散領域28aの方が高濃度にn型不純物が導入されている。この低濃度n型不純物拡散領域27aと高濃度n型不純物拡散領域28aにより、nチャネルMISFETQ1のソース領域あるいはドレイン領域が形成される。ソース領域あるいはドレイン領域を低濃度n型不純物拡散領域27aおよび高濃度n型不純物拡散領域28aより構成することにより、いわゆるLDD(Lightly Doped Drain)構造が形成される。したがって、ゲート電極25a下の電界集中を緩和することができる。

#### 【0047】

一方、n型ウェル23上にはpチャネル型MISFETQ2が形成されている。このpチャネル型MISFETQ2の構成はほぼnチャネル型MISFETQ1と同様の構成となっている。すなわち、n型ウェル23上にゲート絶縁膜24が形成されており、このゲート絶縁膜24上にゲート電極25bが形成されている。ゲート電極25bは、例えばポリシリコン膜から形成され、p型不純物が導入されている。このようにpチャネル型MISFETQ2においては、ゲート電極25bにp型不純物を導入することによりしきい値電圧を下げることができる。本実施の形態1では、nチャネル型MISFETQ1のゲート電極25aにn型不純物を導入する一方、pチャネル型MISFETQ2のゲート電極25bにp型不純物を導入している。このため、nチャネル型MISFETQ1とpチャネル型MISFETQ2の両方でしきい値電圧を低下させることができるのである。

#### 【0048】

ゲート電極25bの両側の側壁には、サイドウォール26が形成されており、このサイドウォール26下のn型ウェル23内には、低濃度p型不純物拡散領域27bが形成されている。そして、低濃度p型不純物拡散領域27bの外側には、高濃度p型不純物拡散領域28bが形成されている。低濃度p型不純物拡散領域27bおよび高濃度p型不純物拡散領域28bは、p型不純物を導入した半導体領域となっており、低濃度p型不純物拡散領域27bよりも高濃度p型不純物拡散領域28bの方が高濃度にp型不純物が導入されている。この低濃度p型不純物拡散領域27bと高濃度p型不純物拡散領域28bにより、pチャネルMISFETQ2のソース領域あるいはドレイン領域が形成される。

#### 【0049】

このようにして、本実施の形態における半導体装置では、半導体基板1S上にnチャネル型MISFETQ1およびpチャネル型MISFETQ2などの半導体素子が形成されている。

#### 【0050】

続いて、半導体基板1S上に多層配線を形成する(S230)。図12に示すように、半導体基板1S上に形成したnチャネル型MISFETQ1およびpチャネル型MISFETQ2上には、層間絶縁膜となる酸化シリコン膜29が形成されている。そして、酸化シリコン膜29には、nチャネル型MISFETQ1あるいはpチャネル型MISFETQ2のソース領域、ドレイン領域に達するプラグ30が形成されている。このプラグ30は、例えばバリアメタル膜となる窒化チタン膜とタンゲステン膜の積層膜から形成される。

#### 【0051】

10

20

30

40

50

プラグ30を形成した酸化シリコン膜29上には、層間絶縁膜となる酸化シリコン膜31が形成され、この酸化シリコン膜31に埋め込むように第1層配線32が形成されている。この第1層配線32は、例えばタンゲステン膜から形成され、下層に形成されたプラグ30と電気的に接続されている。

#### 【0052】

第1層配線32上には、酸化シリコン膜33が形成され、この酸化シリコン膜33に埋め込むようにプラグ34が形成されている。このプラグ34もプラグ30と同様にバリアメタル膜およびタンゲステン膜の積層膜から構成されている。プラグ34は、下層に形成されている第1層配線32と電気的に接続されるようになっている。

#### 【0053】

プラグ34を形成した酸化シリコン膜33上には、層間絶縁膜となる酸化シリコン膜35が形成されており、この酸化シリコン膜35へ埋め込むように第2層配線36が形成されている。この第2層配線36は、銅の拡散を防止するためのバリアメタル膜および銅(銅またはその合金)膜の積層膜から構成されている。

#### 【0054】

第2層配線36上には、銅の拡散を防止するための窒化シリコン膜37aが形成されており、この窒化シリコン膜37a上に酸化シリコン膜37bが形成されている。酸化シリコン膜37b上には、窒化シリコン膜38aおよび酸化シリコン膜38bが積層して形成され、窒化シリコン膜38aおよび酸化シリコン膜38bへ埋め込むように第3層配線39が形成されている。この第3層配線39は、銅の拡散を防止するためのバリアメタル膜および銅膜の積層膜から構成されており、下層に形成されている第2層配線36と電気的に接続されている。

#### 【0055】

この第3層配線39と同様にして、第3層配線39の上層に、銅の拡散を防止するためのバリアメタル膜および銅膜の積層膜から構成される第4層配線40が形成されている。この第4層配線40は、下層に形成されている第3層配線39と電気的に接続されている。なお、図示しないが、第4層配線40と同層に、一定の間隔毎に複数のメモリ救済用ヒューズが形成されていても良い。このヒューズは冗長救済回路に電気的に接続され、特定のヒューズを切断することによって、欠陥メモリセルを選択するアドレス信号を、冗長救済用のメモリセルに対応するアドレス信号に変えることができる。

#### 【0056】

第4層配線40の銅が上層へ拡散を防止するため第4層配線40を覆うようにキャップ絶縁膜41が半導体基板15上に形成されており、このキャップ絶縁膜41上には、例えばプラズマCVD法によって酸化シリコン膜42が形成されている(図13参照)。キャップ絶縁膜41は、窒化シリコン膜から構成されており、窒化シリコン膜としてSiCN膜を用いることにより、例えばSiN膜を用いた場合に比べて、キャップ絶縁膜41の経時絶縁破壊(TDDB; Time Dependent Dielectric Breakdown)耐性と、第4層配線40のエレクトロマイグレーション耐性とを向上することができる。

#### 【0057】

酸化シリコン膜42およびキャップ絶縁膜41には、第4層配線40と電気的に接続されたプラグ43が形成されている。このプラグ43は、マスク(フォトレジスト膜)を用いて酸化シリコン膜42およびキャップ絶縁膜41をドライエッティングし、第4層配線40に達する接続孔を形成し、チタン(Ti)膜、窒化チタン(TiN)膜またはそれらの積層膜をバリア導電膜として接続孔内を含む酸化シリコン膜42上に堆積し、次いでタンゲステン膜で接続孔内を埋め込んだ後に、接続孔外のタンゲステン膜およびバリア導電膜をCMP法等で除去することによって形成することができる。

#### 【0058】

プラグ43上であって第4層配線40の上層には、プラグ43と電気的に接続された第5層配線44が形成されている。この第5層配線44は、例えばアルミニウム(A1)を主導電層とするもので、主導電層となるA1膜の上下をTi膜およびTiN膜の積層膜か

10

20

30

40

50

らなるバリア導電膜で挟んだ構造とするものである。このような配線は、下のバリア導電膜、A1膜および上のバリア導電膜を順次堆積した後に、これらの積層膜をフォトリソグラフィ技術によってパターニングされたフォトレジスト膜をマスクとしてドライエッチングすることで形成することができる。

#### 【0059】

このように本実施の形態では、第1層配線32、第2層配線36、第3層配線39、第4層配線40および第5層配線44から多層配線が形成されている。多層配線は、複数の半導体素子を電気的に接続して回路を形成する役割を有している。

#### 【0060】

続いて、この多層配線を覆うように半導体基板1S、すなわち酸化シリコン膜42上にパッシベーション膜として、例えば薄い酸化シリコン膜45および窒化シリコン膜46を順次形成する(S240)。これら酸化シリコン膜45および窒化シリコン膜46は、無機系絶縁膜であり、例えばプラズマCVDで形成することができる。

#### 【0061】

続いて、フォトリソグラフィ技術によってパターニングされたフォトレジスト膜47をマスクとして、窒化シリコン膜46および酸化シリコン膜45をドライエッチングし、第5層配線の一部を露出する開口部48を形成する。その後、フォトレジスト膜47をアッシング(炭化処理)により除去する。

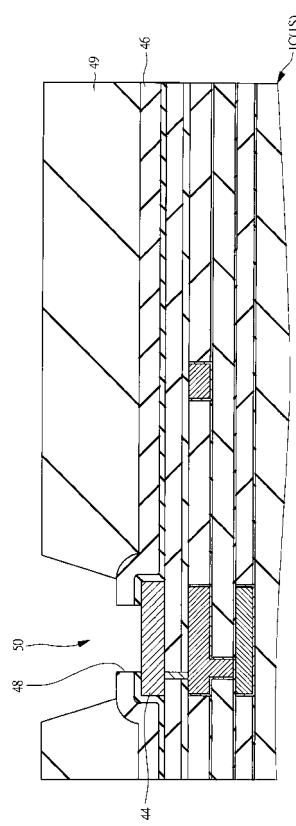

#### 【0062】

続いて、図14に示すように、窒化シリコン膜46上に絶縁膜として、例えば有機系絶縁膜であるポリイミド樹脂膜49を形成する(S250)。このポリイミド樹脂膜49は、半導体基板1Sの半導体素子および多層配線を保護する表面保護膜(絶縁膜)を構成する。

#### 【0063】

次に、パッケージ工程(S300)について説明する。図14に示すように、ポリイミド樹脂膜49を感光処理およびアッシング処理によってパターニングし、開口部48上のポリイミド樹脂膜49を除去する。これにより、第5層配線44の一部上の酸化シリコン膜45、窒化シリコン膜46、およびポリイミド樹脂膜49に、第5層配線44の一部を露出する開口部50が形成されることとなる(S310)。

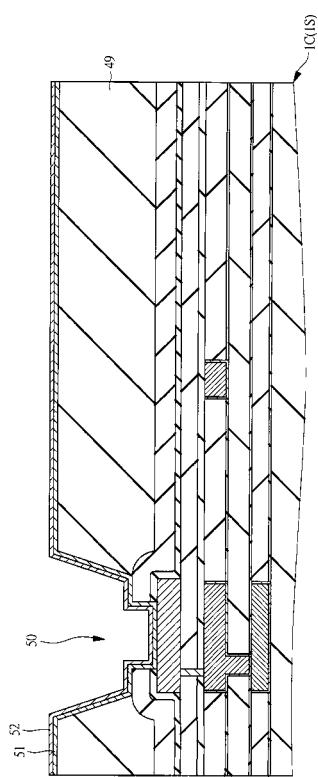

#### 【0064】

続いて、図15に示すように、半導体基板1Sの表面に対してスパッタエッチング処理を施した後に、スパッタリング法により開口部50およびポリイミド樹脂膜49上にTiN膜およびTi膜を順次堆積し、バリア層51を形成する。次いで、バリア層51上に、スパッタリング法によって銅(Cu)膜を堆積し、シード層52を形成する。このシード層52は、後の工程でメッキ法を用いて形成する再配線のシード層である。

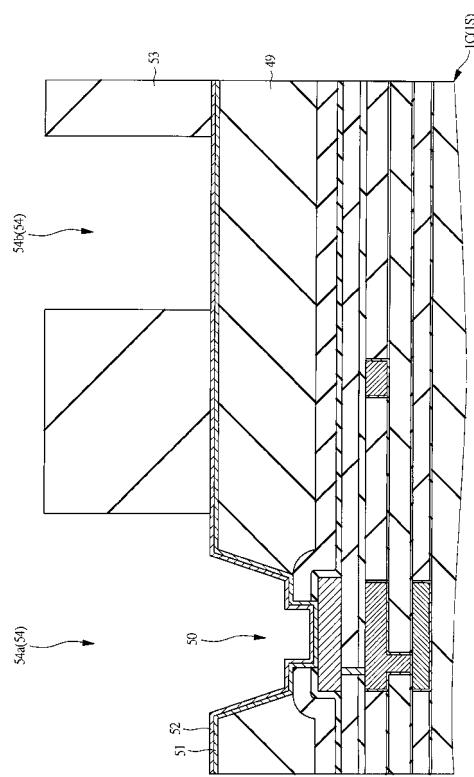

#### 【0065】

続いて、図16に示すように、半導体基板1S上にフォトレジスト膜53を塗布し、そのフォトレジスト膜53をフォトリソグラフィ技術によりパターニングする。これにより、シード層52の一部上のフォトレジスト膜53に、シード層52の一部を露出する再配線形成用の開口部54を形成する。開口部54のうち開口部54aはポリイミド樹脂膜49の一部が除去されてなる開口部50を露出するように形成され、開口部54bはポリイミド樹脂膜49上に形成される。開口部54は図1、図2に示したような再配線のパターンを形成するために用いられ、開口部54aが本体パターン2、開口部54bがダミーパターン3のパターンとなる。

#### 【0066】

続いて、パターニングされたフォトレジスト膜53をマスクとした電解メッキ法により、銅膜56およびニッケル膜57を順次堆積し、銅膜56およびニッケル膜57からなる再配線58を形成した後、アッシング処理によってフォトレジスト膜53を除去すると、図17に示すようになる(S320)。この再配線57は、図1、図2に示したように、本体パターン2とダミーパターンとが半導体基板1Sの面内で混在するように形成される

10

20

30

40

50

。

### 【 0 0 6 7 】

続いて、図18に示すように、再配線57をマスクとしてシード層52およびバリア層51に対してウエットエッチング(洗浄)処理を施すことにより、再配線57下のシード層52およびバリア層51を残し、それ以外のシード層52およびバリア層51を除去する。

### 【 0 0 6 8 】

続いて、図3に示すように、再配線57を覆うように半導体基板1S上に、表面保護膜(絶縁膜)として、例えば有機系絶縁膜であるポリイミド樹脂膜58を形成(S330)した後、再配線57からなる本体パターン2の一部(ランド電極2aとなる)上に、その一部を露出する開口部59をポリイミド樹脂膜58に形成する(S340)。開口部59は、ポリイミド樹脂膜58を感光処理およびアッシング処理によってパターニングし、本体パターン2のランド電極2a上のポリイミド樹脂膜58を除去してなる。

### 【 0 0 6 9 】

次いで、無電解メッキ法により、開口部59下のランド電極2a上に図示しない金(Au)膜を形成する。次いで、はんだ印刷技術により半導体基板1S上にはんだペーストを印刷した後、リフロー処理によりはんだペーストを溶融および再結晶化させ、前記金膜上にバンプ電極60を形成する(S350)。そのはんだペーストとしては、例えばSn(錫)、Ag(銀)およびCuから形成されたPb(鉛)フリーはんだを用いることができる。また、はんだペーストを用いる代わりに、予め球状に成形されたはんだボールを開口部59上に供給した後に、半導体基板1Sに対してリフロー処理を施すことによってもバンプ電極60を形成することができる。なお、はんだペーストのリフロー処理によって、前記金膜は、バンプ電極60に拡散してなくなってしまう。

### 【 0 0 7 0 】

その後、ウエハ状態の半導体基板1Sを区画されたチップ領域間のスクライブ(ダイシング)領域に沿って切断し、図1に示したように個々の半導体チップ1Cに分割して、本実施の形態における半導体装置が完成する。本実施の形態における半導体チップ1Cは、実装基板上にバンプ電極60を介して実装することができ、半導体チップ1Cを実装基板上に配置した後、バンプ電極60をリフローし、次いで半導体チップ1Cと実装基板との間にアンダーフィル樹脂を充填されて、種々の半導体装置を構成する。

### 【 0 0 7 1 】

ここで、本体パターン2およびダミーパターン3を構成する再配線57の半導体ウエハ1Wにおける局所的な領域内の占有率、例えば半導体チップ1C内の占有率、ショット領域ST内の占有率について説明する。

### 【 0 0 7 2 】

再配線57の半導体チップ1C(ショット領域ST)内の占有率が低くなると、メッキ着工安定性確保、すなわち安定電流値が確保できず、再配線57を構成するメッキ膜(銅膜55/ニッケル膜56)の膜厚が半導体ウエハ1Wの面内で発生する場合や、半導体ウエハ1Wの中心部にて面荒れが発生する場合がある。また、図4を参照して説明したように、再配線57の占有率にて局所的な偏りがあると、本体パターン2が形成されている周辺領域90(再配線57が密の領域となる)と、本体パターン2が形成されていない中心領域80(再配線57が疎の領域となる)の境界付近の再配線57(本体パターン2)の端部に面荒れが発生する。

### 【 0 0 7 3 】

その一方で、再配線57の半導体ウエハ1Wの面内の占有率が高くなると、半導体ウエハ1Wのバックグラインド後の半導体ウエハ1Wの厚さとの関係で、半導体ウエハ1Wに反りが発生する。このため、バックグラインド後のバンプ電極60の形成ができなくなる、または半導体ウエハ1Wのハンドリングができなくなり、チッピングが生じ、後の工程の歩留り低下となる。

### 【 0 0 7 4 】

10

20

30

40

50

そこで、本実施の形態では、W P P 技術における再配線 5 7において、本体パターン 2 の他にダミーパターン 3 を配置し、本体パターン 2 およびダミーパターン 3 から構成される再配線 5 7 のショット領域 S T ( 半導体チップ 1 C ) 全体の占有率 ( 局所的な領域の占有率 ) の下限および上限を規定することによって、再配線 5 7 の形成工程、バックグラインド後の着工、ハンドリングを安定させ、半導体装置の製造歩留まりを低減している。

#### 【 0 0 7 5 】

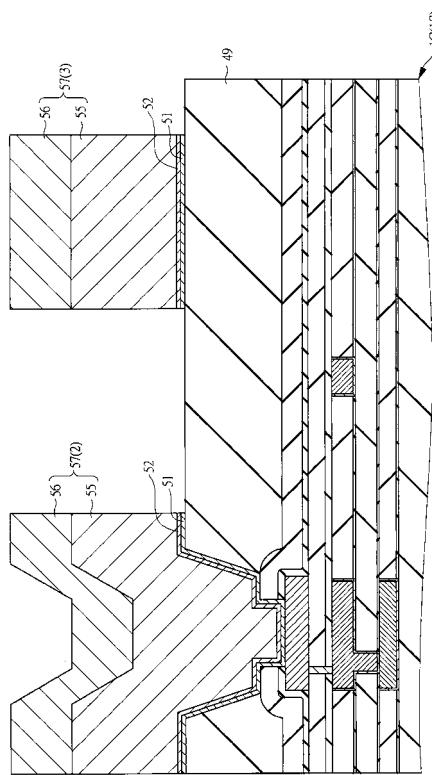

例えば、本実施の形態で用いたメッキ装置は、メッキ膜 ( 再配線 5 7 を構成する銅膜 5 5 およびニッケル膜 5 6 ) を安定して形成するためには、メッキ電流値を 6 A 以上確保する必要がある。図 19 に示すようなメッキ電流と、半導体ウエハ 1 W の面内の再配線 5 7 の占有率とには相関関係がある。メッキ電流が 6 A の場合、銅 ( Cu ) メッキが安定したメッキ膜となるには、銅膜 5 5 の占有率が 28.5 % であることがわかる。また、メッキ電流が 6 A の場合、ニッケル ( Ni ) メッキが安定したメッキ膜となるには、ニッケル膜 5 6 の占有率が 33.4 % であることがわかる。

#### 【 0 0 7 6 】

したがって、本実施の形態では、マージンを含めたショット領域 S T ( 半導体チップ 1 C ) 内の再配線 5 7 の占有率の下限は、35 % 以上としている。これにより、再配線 5 7 を安定して形成することができ、製造歩留まりを低減することができる。また、安定して形成された再配線 5 7 では、面荒れを防止することにより製品不具合を抑制し、半導体装置の信頼性を向上することができる。

#### 【 0 0 7 7 】

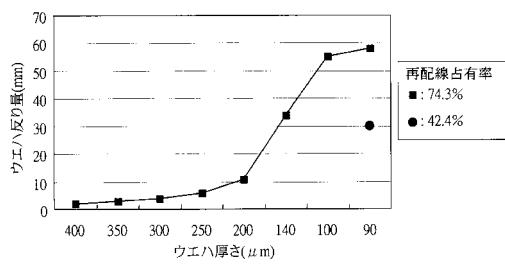

また、半導体装置の量産を考慮した場合、バンプ電極 6 0 が形成された半導体ウエハ 1 W では、その反り量は 50 mm 以下であることが望ましい。例えば、図 20 に 300 mm 径の半導体ウエハ 1 W の厚さと半導体ウエハ 1 W の反り量との関係を示すように、再配線 5 7 の占有率が 74.3 % の場合、半導体ウエハ 1 W の厚さが薄くなるに従い、半導体ウエハ 1 W の反り量が増加することがわかる。この場合、半導体ウエハ 1 W の反り量が 50 mm 以下の半導体ウエハ 1 W の厚さは、120 μm である。

#### 【 0 0 7 8 】

半導体装置の小型化を考慮した場合、半導体ウエハ 1 W ( 半導体チップ 1 C ) の厚さはより、薄いことが望ましく、現状の製品においては半導体ウエハ 1 W の下限が 100 μm である。したがって、本実施の形態では、ショット領域 S T ( 半導体チップ 1 C ) 内の再配線 5 7 の占有率の上限は、半導体ウエハ 1 W の反り量が 50 mm 以下で、半導体ウエハ 1 W の厚さが 100 μm 以下で検討した結果から、60 % 以下としている。これにより、バックグラインド後のバンプ電極 6 0 を安定して形成することができる。また、半導体ウエハ 1 W の反り量を抑えることによって、ハンドリングを容易に行うことができる。また、半導体ウエハ 1 W のチッピング・割れを防止できるので、半導体装置の製造歩留りを低減することができる。

#### 【 0 0 7 9 】

##### ( 実施の形態 2 )

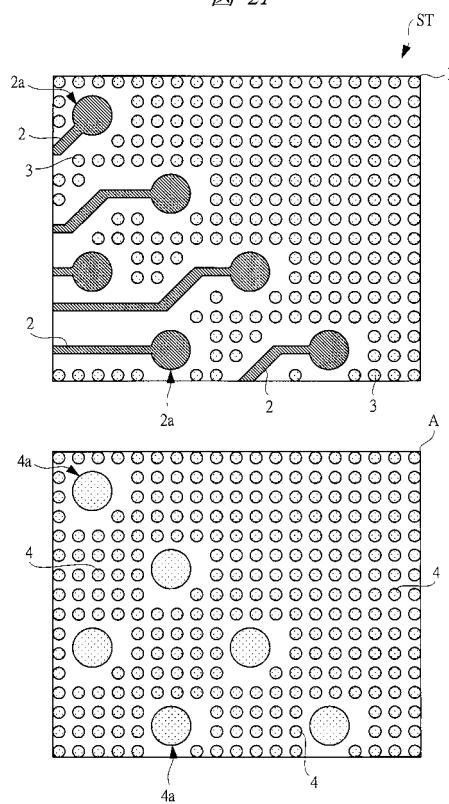

前記実施の形態 1 では、ショット領域の複数のチップ領域の全てに、内部回路の引き回し配線となる本体パターンおよびフロー・ティイングされているダミーパターンから構成される再配線が形成される場合について説明した。本実施の形態では、ショット領域の複数のチップ領域の一部に、本体パターンおよびダミーパターンから構成される再配線が形成される場合について説明する。なお、前記実施の形態と重複する説明は省略する。

#### 【 0 0 8 0 】

例えば、図 11 に示すショット領域 S T の複数のチップ領域 ( A ~ L ) に、種々のテストチップが配置される場合について説明する。ショット領域 S T には、あるチップ領域 ( E, F, H ) には W P P 技術を必要とするテストチップが形成されるが、別のチップ領域 ( A, B, C, G, I, J, K, L ) には W P P 技術を必要としないテストチップが形成される。すなわち、ショット領域 S T には W P P 技術を必要とする半導体チップと W P P 技術を必要としない半導体チップが混在する。

10

20

30

40

50

## 【0081】

W P P 技術はウエハレベルにて着工されるので、本実施の形態では、前記実施の形態1で説明したようにショット領域内の再配線の占有率の要件を満たすためには、W P P 技術を必要とするテストチップはもちろん、W P P 技術を必要としないテストチップにもダミーパターンを配置する。

## 【0082】

図21に本実施の形態におけるショット領域S Tのチップ領域Eおよびチップ領域Aのそれぞれの要部を示す。図21のチップ領域Eは、図2で示した領域と対応している。すなわち、前記実施の形態1で示した半導体チップ1Cが、例えば図21のチップ領域Eにテストチップとして形成される。したがって、チップ領域Eの半導体チップ1Cの断面として図3を参照することができる。10

## 【0083】

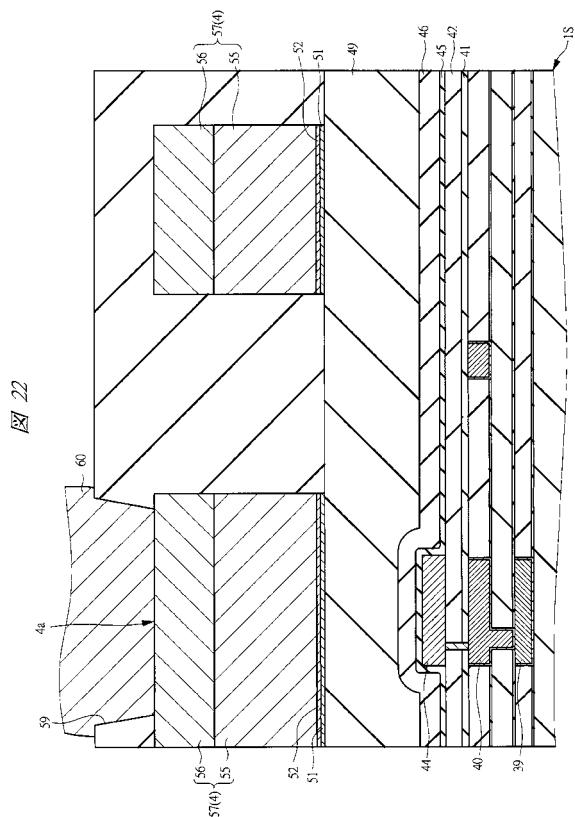

一方、チップ領域Aの半導体チップの断面を図22に示す。本来ならば、W P P 技術を必要としないので、チップ領域Aの半導体チップには図5に示したウエハ工程(S200)と同様にして形成した場合、半導体素子(S220)、第3層配線39、第4層配線40および第5層配線を含む多層配線(S230)、無機系絶縁膜である酸化シリコン膜45および窒化シリコン膜46(S240)、有機系絶縁膜であるポリイミド樹脂膜49(S250)が形成されれば良い。しかしながら、本実施の形態では、前記実施の形態1で説明したようにショット領域S T内の再配線の占有率の要件を満たすため、チップ領域Aに再配線57から構成されるダミーパターン4を配置している。このダミーパターン4は、前記実施の形態におけるダミーパターン3と同様にして形成することができる。20

## 【0084】

また、ダミーパターン4として、本体パターン2のランド電極2aに対応してダミーランド電極4aを配置している。本実施の形態では、図22に示すように、このダミーランド電極4a上にもバンプ電極60を形成している。バンプ電極形成工程(S350)において、着工安定性(ハンダ塗れ性)を向上させるためには、ダミーパターン4にも、W P P 技術を必要とするテストチップと同程度にバンプ電極60を形成することが望ましい。

## 【0085】

このようにW P P 技術を必要としないチップ領域にも、ダミーパターン4を設けることによって、メッキ法で形成される再配線57の疎密差を低減し、W P P 技術を必要とするチップ領域の本体パターン2の外観異常が発生するのを防止することができる。30

## 【0086】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

## 【0087】

例えば、前記実施の形態では、W P P 技術における再配線を有する半導体装置に適用した場合について説明したが、半導体素子の配線としてメッキ配線を用いる半導体装置にも適用することができる。40

## 【産業上の利用可能性】

## 【0088】

本発明は、半導体装置、特に、W P P 技術における再配線を有する半導体装置に有効で、とりわけC S P (Chip Size Package)構造の半導体装置の製造業に幅広く利用されるものである。

## 【図面の簡単な説明】

## 【0089】

【図1】本発明の一実施の形態における半導体装置の平面を模式的に示す説明図である。

【図2】図1の半導体装置の平面を拡大して示す説明図である。

【図3】図1の半導体装置の要部断面を模式的に示す説明図である。50

【図4】図2に対応する本発明者らが検討した半導体装置の平面を拡大して示す説明図である。

【図5】本発明の一実施の形態における半導体装置の製造工程の流れ図である。

【図6】図5の設計工程における処理パターンを示す説明図である。

【図7】図6に続く設計工程における処理パターンを示す説明図である。

【図8】図7に続く設計工程における処理パターンを示す説明図である。

【図9】図8に続く設計工程における処理パターンを示す説明図である。

【図10】図9に続く設計工程における処理パターンを示す説明図である。

【図11】図5のウエハ工程およびパッケージ工程における半導体装置の平面を示す説明図である。

10

【図12】図11に続く半導体装置の断面を示す説明図である。

【図13】図12に続く半導体装置の断面を示す説明図である。

【図14】図13に続く半導体装置の断面を示す説明図である。

【図15】図14に続く半導体装置の断面を示す説明図である。

【図16】図15に続く半導体装置の断面を示す説明図である。

【図17】図16に続く半導体装置の断面を示す説明図である。

【図18】図17に続く半導体装置の断面を示す説明図である。

【図19】メッキ電流と再配線占有率との関係を示す説明図である。

【図20】半導体ウエハの厚さと半導体ウエハの反り量との関係を示す説明図である。

【図21】本発明の他の実施の形態における半導体装置の平面を示す説明図である。

20

【図22】図21の半導体装置の要部断面を模式的に示す説明図である。

#### 【符号の説明】

##### 【0090】

1C、1C' 半導体チップ

1S 半導体基板

1W 半導体ウエハ

2 本体パターン(第1パターン)

2a ランド電極

2g 粒

2p 本体処理パターン(第1処理パターン)

30

3 ダミーパターン(第2パターン)

3a ダミーランド電極

3p ダミー処理パターン(第2処理パターン)

4 ダミーパターン(第3パターン)

4a ダミーランド電極

21 素子分離領域

22 p型ウェル

23 n型ウェル

24 ゲート絶縁膜

25a ゲート電極

40

25b ゲート電極

26 サイドウォール

27a 低濃度n型不純物拡散領域

27b 低濃度p型不純物拡散領域

28a 高濃度n型不純物拡散領域

28b 高濃度p型不純物拡散領域

29 酸化シリコン膜

30 プラグ

31 酸化シリコン膜

32 第1層配線

50

|                 |                          |    |

|-----------------|--------------------------|----|

| 3 3             | 酸化シリコン膜                  |    |

| 3 4             | プラグ                      |    |

| 3 5             | 酸化シリコン膜                  |    |

| 3 6             | 第2層配線                    |    |

| 3 7 a           | 窒化シリコン膜                  |    |

| 3 7 b           | 酸化シリコン膜                  |    |

| 3 8 a           | 窒化シリコン膜                  |    |

| 3 8 b           | 酸化シリコン膜                  |    |

| 3 9             | 第3層配線                    | 10 |

| 4 0             | 第4層配線                    |    |

| 4 1             | キヤップ絶縁膜                  |    |

| 4 2             | 酸化シリコン膜                  |    |

| 4 3             | プラグ                      |    |

| 4 4             | 第5層配線                    |    |

| 4 5             | 酸化シリコン膜                  |    |

| 4 6             | 窒化シリコン膜（無機系絶縁膜、第1絶縁膜）    |    |

| 4 7             | フォトレジスト膜                 |    |

| 4 8             | 開口部                      |    |

| 4 9             | ポリイミド樹脂膜（第1有機系絶縁膜、第2絶縁膜） |    |

| 5 0             | 開口部（第1開口部）               | 20 |

| 5 1             | バリア層                     |    |

| 5 2             | シード層                     |    |

| 5 3             | フォトレジスト膜                 |    |

| 5 4、5 4 a、5 4 b | 開口部                      |    |

| 5 5             | 銅膜                       |    |

| 5 6             | ニッケル膜                    |    |

| 5 7             | 再配線                      |    |

| 5 8             | ポリイミド樹脂膜（第2有機系絶縁膜、第3絶縁膜） |    |

| 5 9             | 開口部（第2開口部）               |    |

| 6 0             | バンプ電極                    | 30 |

| 8 0             | 中心領域（第1領域）               |    |

| 9 0             | 周辺領域（第2領域）               |    |

| Q 1             | nチャネル型MISFET             |    |

| Q 2             | pチャネル型MISFET             |    |

| S T             | ショット領域                   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

【図17】

図17

【図18】

図18

【図19】

図19

【図21】

図21

【図20】

図20

【図22】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/822 (2006.01)

(56)参考文献 特開2007-220870(JP,A)

特開2003-017530(JP,A)

特開2001-351984(JP,A)

特開2000-349196(JP,A)

特開平09-306914(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23/12

H 01 L 21/3205

H 01 L 21/822

H 01 L 23/52

H 01 L 27/04