(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-179327

(P2004-179327A)

(43) 公開日 平成16年6月24日(2004.6.24)

(51) Int.Cl.<sup>7</sup>

H01L 21/28

H01L 21/285

F 1

H01L 21/28 301R

H01L 21/285 P

H01L 21/285 S

テーマコード(参考)

4M1O4

審査請求 未請求 請求項の数 10 O L (全 13 頁)

(21) 出願番号

特願2002-342797 (P2002-342797)

(22) 出願日

平成14年11月26日 (2002.11.26)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(71) 出願人 000217228

田中貴金属工業株式会社

東京都中央区日本橋茅場町2丁目6番6号

(74) 代理人 100065248

弁理士 野河 信太郎

(72) 発明者 井上 和範

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 石倉 千春

神奈川県伊勢原市鈴川26番地 田中貴金

属工業株式会社伊勢原工場内

最終頁に続く

(54) 【発明の名称】半導体用合金材料、該合金材料を用いた半導体チップ及びその製造方法

## (57) 【要約】

【課題】AuとAgによる単一膜を用いることにより、それぞれの単一金属膜のもつ固有の物性を最大限に引き出し、均質かつ安定な組成を有し、加工性に優れた合金材料を提供するとともに、このような合金材料を用いた半導体チップ及びその製造方法を提供することを目的とする。

【解決手段】Auを主成分とし、Agを3wt%以上40wt%以下の範囲で含有してなる半導体用合金材料、半導体基板上に上記合金材料による金属膜が形成される半導体チップ、半導体基板上に上記合金材料を用いて金属膜を形成する半導体チップの製造方法。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

Auを主成分とし、Agを3wt%以上40wt%以下の範囲で含有することを特徴とする半導体用合金材料。

**【請求項 2】**

Au及びAgが3N以上の純度である請求項1に記載の合金材料。

**【請求項 3】**

合金材料が、スパッタリングターゲット材料、蒸着用材料及びボンディング用ワイヤー材料の形態である請求項1又は2に記載の合金材料。

**【請求項 4】**

半導体基板上に請求項1又は2に記載の合金材料による金属膜が形成されてなることを特徴とする半導体チップ。 10

**【請求項 5】**

金属膜が、50nm以上1000nm以下の範囲の膜厚である請求項4に記載の半導体チップ

**【請求項 6】**

金属膜が、配線、電極、バンプ、遮光膜として形成されてなる請求項4又は5に記載の半導体チップ。

**【請求項 7】**

金属膜がAgペーストを介して形成されてなる請求項4～6のいずれか1つに記載の半導体チップ。 20

**【請求項 8】**

半導体基板上に、請求項1又は2の合金材料を用いて金属膜を形成することを特徴とする半導体チップの製造方法。

**【請求項 9】**

合金材料を、スパッタリング法又は蒸着により金属膜とする請求項8に記載の方法。

**【請求項 10】**

金属膜を形成した後、300以上520以下の温度範囲により加熱処理する請求項8又は9に記載の方法。 30

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体用合金材料、該合金材料を用いた半導体チップ及びその製造方法に関し、より詳細には、AuAg合金材料及びこの合金材料を用いて性能を安定させた半導体チップ及びその製造方法に関する。

**【0002】****【従来の技術及び発明が解決しようとする課題】**

従来、半導体装置作製用の金属材料として、AuやAgが、それぞれ、使用目的に応じて単層で使用されていた。

一般に、Auは、大気中では安定で、延展性に富む金属材料であり、加熱をしても他の材料や雰囲気中の成分と反応を起こさず、清浄な金属表面を維持できるため、また、Agは安価で、低抵抗であるため、半導体用金属材料として多用されている。 40

しかし、Au膜をSi層上に直接被覆させた場合、その後の加熱処理により、SiがAu中に拡散し、Au膜の組成が安定せず、被膜の物性を劣化させる恐れがある。

また、Agは単一金属膜として用いた場合、硫化しやすく自己焼純により再結晶し、軟化する。

**【0003】**

このようなことから、例えば、Au及びAg含有合金材料として、Agを主成分とし、Auを0.1wt%～10wt%含有し、かつCu、Al、Ti等の元素の少なくとも1種類をそれぞれ0.1wt%以上5wt%以下で含有する合金材料が、電子部品、電子機器 50

、電子光学部品等へ使用されることが提案されている（例えば、特許文献1）。このような合金材料、つまり、Au及びAgにCu、Al、Ti等が含有された合金材料は、素材の安定性及び加工性等を向上させ、配線の低抵抗率化を図るために用いられている。また、例えば、スパッタリング法で使用されるターゲット材として、単一金属のAuとAgとをモザイク状に加工したものを用いて、スパッタリング法により、AuとAgとの合金層を形成する方法、単一金属のAuとAgとを、別々のターゲット材料として用いて、Au膜とAg膜との多層膜を形成し、その後、両者を拡散させてAuとAgとの合金層を形成する方法がある。

#### 【0004】

しかし、これらのターゲットを用いて合金層を形成すると、得られる合金層が均質にならず、合金層の組成の安定性が悪くなるという問題がある。さらに、多層膜の形成後の拡散による方法では、工程数が増加して煩雑になるばかりでなく、拡散による均質化に限界があり、やはり合金層を均質に形成することが困難であった。

つまり、AuとAgとの短所を補いつつ、両者の長所を最大限に引き出すものとして、半導体用途にAuとAgとの合金による単一膜が使用されていないのが現状である。

#### 【0005】

本発明は、上記課題に鑑みなされたものであり、AuとAgとの合金による単一膜を用いることにより、それぞれの単一金属膜のもつ固有の物性を最大限に引き出し、均質かつ安定な組成を有し、加工性に優れた合金材料を提供するとともに、このような合金材料を用いた半導体チップ及びその製造方法を提供することを目的とする。

#### 【0006】

##### 【課題を解決するための手段】

本発明によれば、Auを主成分とし、Agを3wt%以上40wt%以下の範囲で含有してなる半導体用合金材料が提供される。

また、本発明によれば、半導体基板上に上記合金材料による金属膜が形成されてなる半導体チップが提供される。

さらに、本発明によれば、半導体基板上に、上記合金材料を用いて金属膜を形成する半導体チップの製造方法が提供される。

#### 【0007】

##### 【発明の実施の形態】

本発明の半導体用合金材料は、Auを主成分とし、Agを3wt%以上40wt%以下の範囲で含有してなる。ここで、半導体用とは、半導体デバイスや半導体チップ等の半導体装置を構成するために用いられる合金材料、半導体装置の製造プロセスにおいて使用される合金材料を意味する。また、合金材料とは、AuとAgとが均一に溶けあっているもの、あるいはAuとAgとの一様な結晶相で、AuとAgとが無秩序に格子点を占めているもの等、いわゆる固溶体、共晶合金のいずれであってもよいが、固溶体、特に完全固溶体であることが適当である。

#### 【0008】

半導体用合金材料を構成するAgは、5wt%以上、10wt%以上、15wt%以上、20wt%以上のものが好ましい。また、35wt%以下、30wt%以下、25wt%以下のものが好ましい。なかでも、10wt%以上、かつ30wt%以下のものがより好ましい。ただし、Agの割合が小さく、AuAg合金をシリコン基板上に直接薄膜として形成する場合には、シリコンの拡散を抑制する効果が小さくなるために、Agは、10wt%以上がより好ましく、硫化による影響及び接触抵抗の増大による電気的特性のシフトを抑制するため、30wt%以下であることがより好ましい。

また、Au及びAgは、使用目的にもよるが、例えば、半導体チップに適用する場合に、リーク電流等の電気的な特性を損なわず、半導体チップの信頼性等を確保するために、それぞれ3N(99.9%)以上の純度を有し、4N以上、さらに5N以上のものが好ましい。

#### 【0009】

10

20

30

40

50

本発明の半導体用合金材料は、当該分野で公知の方法、例えば、AuとAgとのインゴットを高周波溶解により溶解して合金とする方法、Au粉とAg粉とを混ぜ合わせ、焼結して合金とする方法などにより製造することができる。

これにより、Auの単体において生じた種々の問題、例えば、Si層上に直接成膜した場合の下地Siの拡散を大幅に低減することができ、Si拡散のない安定した被膜組成を維持することができ、耐候性及び金属強度を向上させることができる。

#### 【0010】

本発明の半導体用合金材料は、種々の用途に使用することができる。例えば、電子機器、電子部品、電子光学部品、具体的には配線、電極、バンプ、遮光膜、金属ペーストを介した接点又はワイヤー等を含む半導体デバイス又は半導体チップ（光送信用ユニット、リモコン用受光ユニット、PC・GP用ユニット、DRAM、フラッシュメモリ、CPU、MPU、ASIC、LSI、TFT、半導体レーザ、太陽電池、発光素子、CCD、サイリスタ、フォトダイオード、フォトトランジスタ、パワートランジスタ等）、液晶表示パネル（フラットパネルディスプレイ、反射型及び透過型液晶表示パネル等）等が挙げられる。代表的には、スパッタリングターゲット材料、蒸着用材料又はボンディング用ワイヤー材料の形態で使用することができる。

#### 【0011】

特に、上記機器及び部品に用いる場合には、金属材料の膜厚は特に限定されるものではないが、例えば、合金膜の応力を考慮して、50nm以上1000nm以下の範囲の膜厚で使用することが好ましい。つまり、応力が大きくなると、ウエハテスト時等のプローブ（測定針）が適切に接触できない等の製造上の不具合を生ずることがあるからである。しかし、ウエハテスト等が必要でない場合又はこの後に施されるバンプやメッキ処理等に用いられる場合には、合金膜の厚みは自由に設定することができる。

#### 【0012】

本発明の半導体用合金材料は、半導体基板上に種々の方法により金属膜として形成して用いることができる。例えば、スパッタリング法、蒸着法、メッキ法、ボンディング法等の既存の半導体プロセス等に柔軟かつ幅広く対応することができる。

具体的には、蒸着法では、例えば、1mmの線径を有するAuAg合金線としてルツボに設置し、 $3 \times 10^{-6}$  Torr程度の真空中度を維持して加熱することにより均質な組成のAuAg合金膜を形成することができる。メッキ法では、例えば、アルカリシアン溶のAuAg合金メッキ溶を用い、25程度の溶温にて $0.5\text{A}/\text{dm}^2$ 程度の電流密度でメッキを施すことによりAuAg合金膜を析出させることができる。ボンディングワイヤー法では、溶解鋸造法によりAuAg合金のインゴットを作製し、押し出し、伸線を繰り返すことにより最終的に線径 $20\sim30\mu\text{m}$ 程度の細線を形成し、具体的には、半導体チップ上の電極とリードフレーム上の外部電極との接続用ボンディングワイヤー用合金線を形成し、使用することができる。また、AuAg合金材料を、配線、電極、バンプ材料等としてパターンニングして用いる場合には、リフトオフ法による加工のほか、AuAg合金材料の組成比に応じて、ヨウ化カリウム水溶液又はヨウ化カリウム水溶液とリン酸系エッチングとの混合液等により、容易にエッチング加工を行うことができる。AuAg合金を適当な位置に、適当な大きさ等で加工することにより、配線、電極、バンプ、遮光膜、接点等の2種以上、例えば、配線と電極、遮光膜と電極、バンプと電極、配線と接点等を、同一工程で形成することが可能である。

なお、本発明の半導体用合金材料は、スパッタリング法、蒸着法等のどのような方法で使用した場合でも、得られた合金材料はほぼ同一の抵抗値、応力、伸び率、強度等を示し、簡易かつ確実に成膜することが可能である。

#### 【0013】

本発明においては、AuAg合金材料による金属膜を、例えば、半導体チップ、半導体基板、半導体層（例えば、シリコン、ゲルマニウム等の元素半導体、GaAs等の化合物半導体）等の上に形成した後、300以上520以下の温度範囲により加熱処理することができる。これにより、半導体層（例えば、シリコン等）との安定したコンタクトを

10

20

30

40

50

確保することができる。例えば、半導体基板表側電極としての代表金属である Al 又は Al-Si 合金が使用され、裏面電極として Au-Ag 合金を使用した場合に、Al スパイク (Al が半導体基板中へ入り込む現象) や、コンタクトにおける抵抗の増大等を防止することができる。

#### 【0014】

なかでも、シリコン層上に Au-Ag 合金を形成する場合には、Au-Ag-Si の共晶を抑制し、半導体チップ等の特性を劣化させないように、300 ~ 470 の温度範囲により加熱処理することが好ましい。このような温度範囲では、下地 Si の Au-Ag 合金への這い上がり、下地 Si と Au-Ag の合金化反応、Au-Ag 合金の最表面における酸化物の生成等を抑制することができ、つまり、加熱処理後においても Au-Ag 合金膜の均一な組成が変化せず、熱に対して安定な組成となり、Au-Ag 合金膜をより薄膜で使用することができる。さらに、これにより、チップダイボンドやワイヤーボンド時の接続面の接着強度を向上させることができるとともに、金属ペーストとの相性が良好となり、信頼性の高い各種部品、デバイス等を提供することが可能となる。

以下に本発明の合金材料、半導体チップ及びその製造方法について詳細に説明する。

#### 【0015】

##### 実施例 1：合金材料の作製

Au と Ag とが種々の割合になるように Au のインゴットと Ag のインゴットを秤量し、高周波溶解にて溶解した後鋳型に流し込むことにより Au-Ag 合金材料を作製した。なお、Au 及び Ag のいずれも 4 N の材料を用いた。

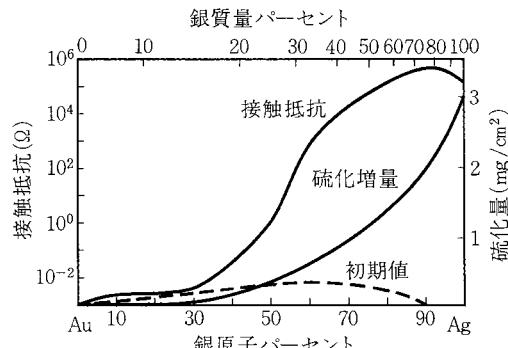

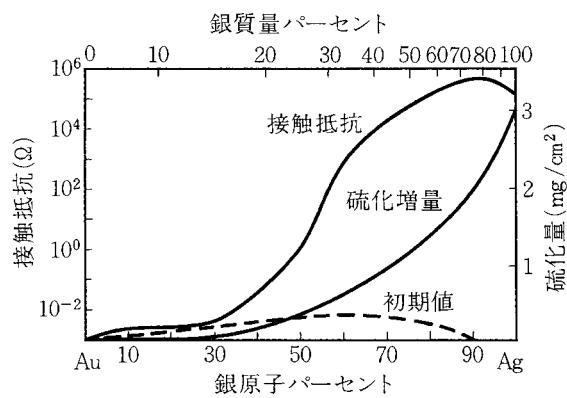

得られた各種組成割合の合金材料を、 $50 \times 20 \times 1 \text{ mm}$  程度の大きさの試験片とし、60、90 mmHg、H<sub>2</sub>S 霧囲気中に 10 日間放置し、その後、試験片の組成に対する硫化量と接触抵抗との関係を測定した。硫化試験前後における接触抵抗を四端子法にて測定した。また、硫化增量は、硫化試験前後における重量を、精密天秤を用いて測定した。その結果を図 1 に示す。

#### 【0016】

図 1 によれば、Ag の重量比が増加するにつれ、硫化量が増加し、Au 材料に比較して表面の経時変化が大きいことがわかる。また、Ag の重量比が増加するにつれ、初期値 (硫化試験を行う前の Au-Ag 合金の接触抵抗値) に比較して、接触抵抗値の増加が大きく、半導体チップにおける電極としての信頼性を損なう可能性が認められた。

一方、Ag 材料の重量比が小さい場合、下地 Si への這い上がり抑制の効果が小さくなることがわかった。

#### 【0017】

##### 実施例 2：合金材料の作製

純度 4 N の Au のインゴット 7.5 kg と、純度 4 N の Ag のインゴット 2.5 kg とをルツボに入れ、高周波溶解で溶解した後、鋳型に入れ、Au : Ag が 75 wt % : 25 wt % のインゴットを作製した。

このようにして得られた Au-Ag 合金材料は、Au の加工性と、Ag の展延性をもちあわせている。

得られたインゴットを圧延して、厚さ 8 mm の板材とした。この板材を旋盤にて直径 250 mm の円盤とし、Cu 製バッキングプレートに接合して、Au-Ag 合金のターゲットを作製した。

なお、比較のために、Au-Ag 合金のターゲットと同様に、Au ターゲット、Ag ターゲットを同様に作製した。

#### 【0018】

##### 実施例 3：合金材料の作製

Ag の組成比を 3 wt %、10 wt % 及び 40 wt % とする以外は実施例 2 と同様の方法により Au-Ag 合金のターゲットを作製した。

#### 【0019】

##### 実施例 4：合金膜の成膜

10

20

30

40

50

実施例 2 で得られたターゲットを用い、シリコン基板上に単一金属膜層としての AuAg 合金膜、Au 膜及び Ag 膜を、それぞれスパッタリング装置を利用して、膜厚 100 nm ~ 1000 nm 程度に成膜した。

スパッタリング装置は、ホリゾンタル型（フェイスアップ方式）の装置であり、スパッタ面の表面クリーニングを行う逆スパッタ室と、AuAg 合金ターゲット、Au ターゲット又は Ag ターゲットを装着したスパッタ室とが、各々独立した反応室として構成されている。ターゲット電極は 2 重磁極型電磁石カソードを備えている。

#### 【0020】

スパッタ条件は、反応室圧力を 2 mTorr ~ 9 mTorr の範囲内で、DC パワーを 0.3 kW ~ 1 kW の範囲に設定した。

このようにして形成された AuAg 合金膜は、蛍光 X 線による組成分析において、Ag が 27.5 wt%、Au が 72.5 wt% であり、均質な膜であった。合金材料の組成よりも Ag の組成比が若干増加するのは、Au に比べ質量数の小さい Ag はスパッタ散乱をより受け易く、Ag のスパッタ速度が速いためであると考えられる。

#### 【0021】

また、AuAg 合金膜は、Au 及び Ag の単一膜に比較して、スパッタリング時の圧力や DC パワーの依存性を受けにくく、成膜後の組成に大きな変化が認められず、均質な膜が形成された。

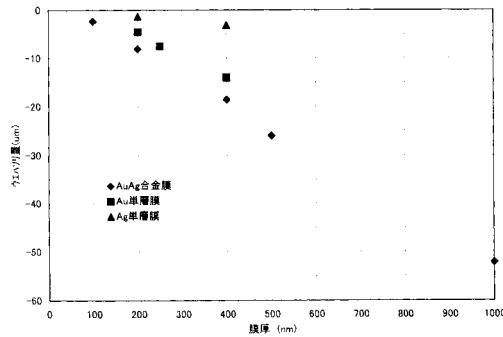

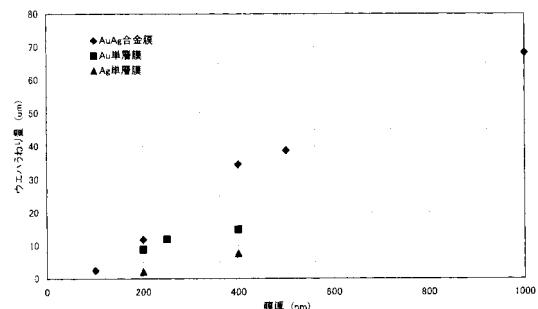

スパッタ後の合金膜及び金属膜の膜応力、窒素雰囲気下で加熱処理（380 ~ 40 分間）した後の合金膜及び金属膜の膜応力、抵抗値をそれぞれ測定した。

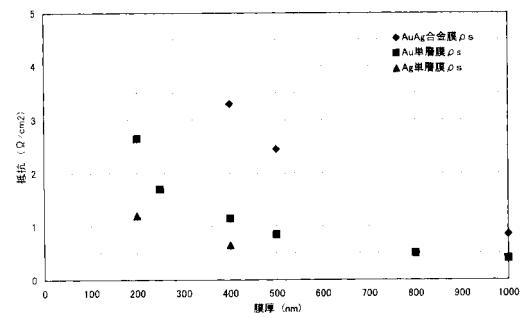

得られた結果を図 2 ~ 図 4 に示す。なお、ここでの膜応力は、金属膜形成前後又は加熱処理後における半導体基板の反り（Bow）とうねり（Warpage）で規定したものである。また、抵抗値の測定は、四探針法により室温で測定した。

#### 【0022】

図 2 及び図 3 によれば、AuAg 合金膜は、Au 膜に比較して、同一膜厚では、若干ウエハ反り量及びうねり量とも増加する傾向にあるが、大きな差は認められず、十分実用に耐えうるレベルにあることが示されている。

また、図 4 によれば、AuAg 合金膜は、Au 膜に比較して、同一膜厚では、若干抵抗値が増加する傾向にあるが、大きな差は認められず、十分実用に耐えうるレベルにあることが示されている。

これにより、AuAg 合金膜としての膜応力、抵抗値とも半導体チップに適用できるレベルにあることがわかった。

#### 【0023】

##### 実施例 5：合金膜の成膜

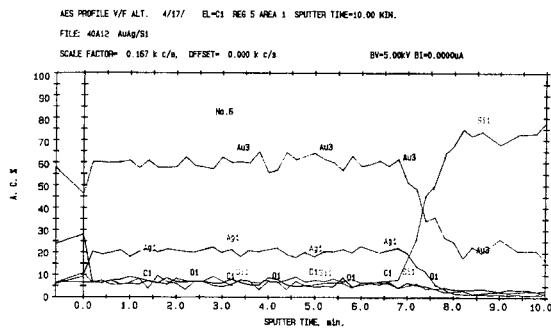

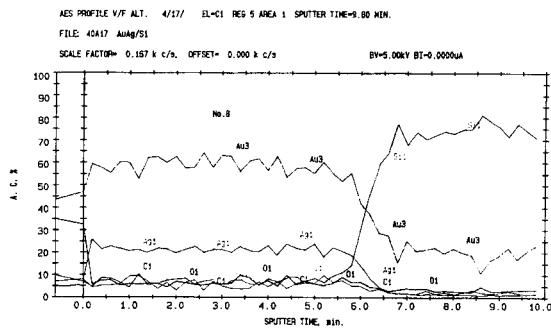

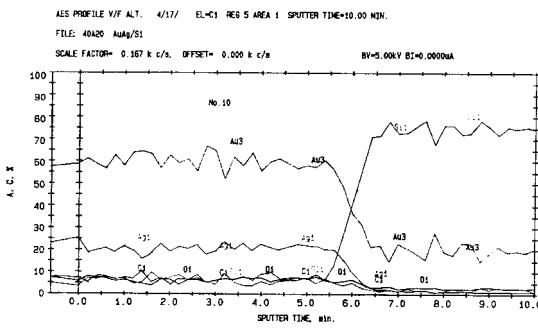

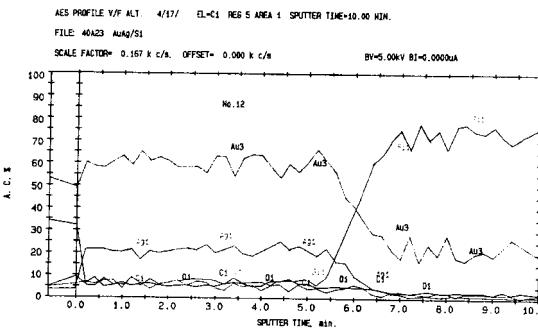

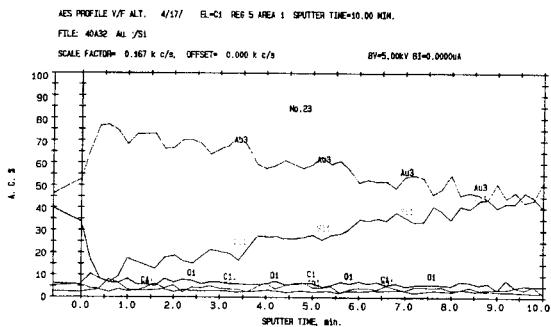

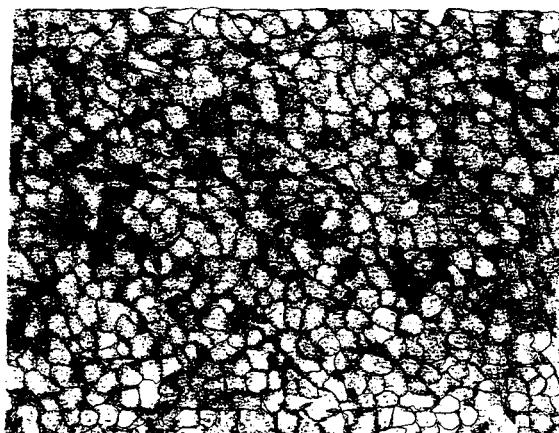

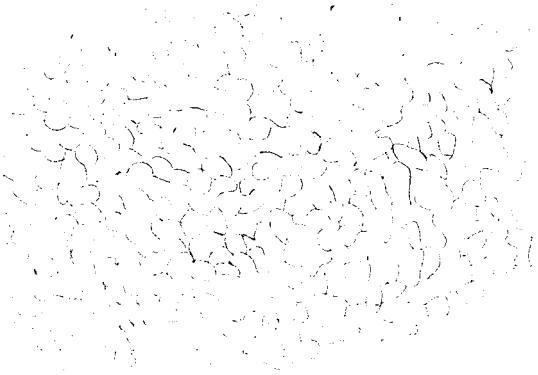

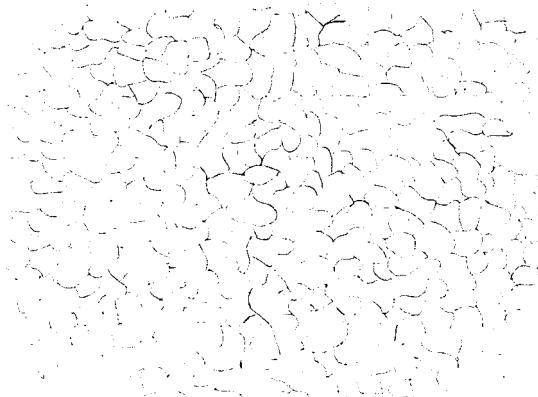

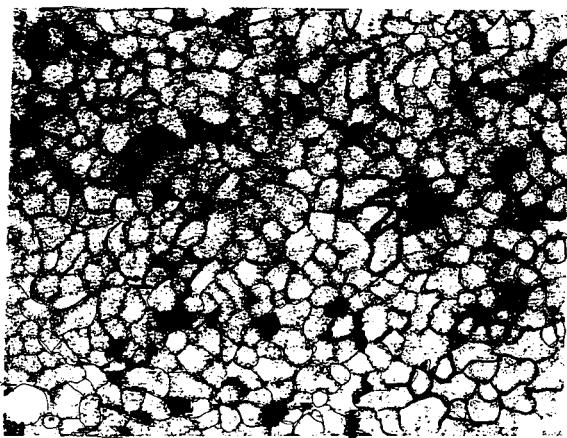

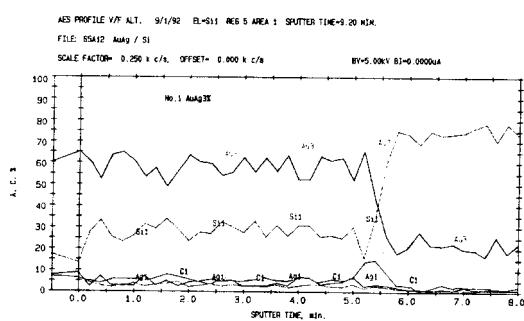

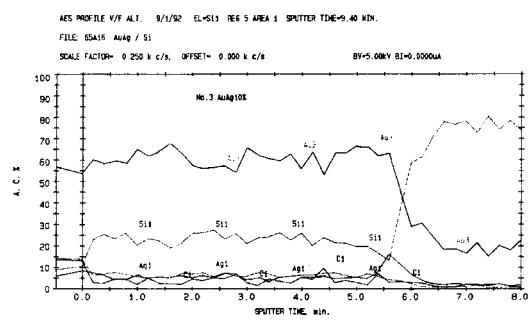

実施例 4 と同様に、実施例 2 で得られた合金材料を用いて、スパッタリング法にてシリコン基板上に 200 nm に成膜した AuAg 合金膜と、200 nm に成膜した Au 膜とに対して、それぞれ窒素雰囲気下、300、380、420 及び 470 で 40 分間加熱処理し、それらの膜の際表面側からオージェ分析を行うとともに、最表面の状態を電子顕微鏡にて観察した。

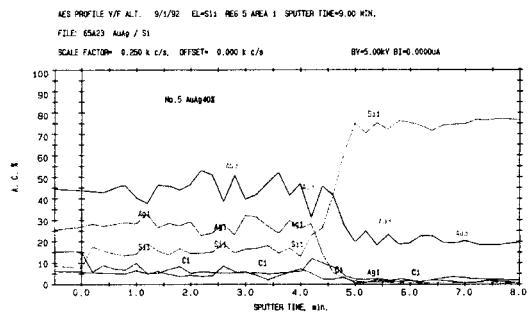

その結果を図 5 ~ 図 9 及び図 10 ~ 図 14 にそれぞれ示す。

#### 【0024】

図 5 ~ 図 8 及び図 10 ~ 図 13 によれば、最表面から一定の深さまでは Si、O の濃度が低いレベルで一定していることから、AuAg 合金膜は、下地シリコンの這い上がりの殆どなく、つまり、AuAg 合金とシリコンとの合金化反応が、AuAg とシリコンとの界面のわずか 50 nm に満たない領域で起こるのみであり、また、膜表面における酸素の量が少なく、均質で表面状態があまり変化しないことが示されている。したがって、Au 単体での膜に比較して、より薄い膜として使用することができる。

一方、図 9 及び図 14 によれば、Au 膜では、加熱処理をすることにより、シリコンが Au 膜の表面まで這い上がっており、シリコンと Au との合金化反応（共晶）が促進されており、さらに、Au 膜の表面における酸素の量が AuAg 合金膜に比較して多く検出され

10

20

30

40

50

ていることが示されている。

【0025】

実施例6：合金膜の成膜

実施例3で得られたターゲットをそれぞれ用い、実施例4と同様にスパッタリング装置を利用して、シリコン基板上に、Au組成の異なる3種のAuAg合金膜を、膜厚200nmで成膜した。

得られた各AuAg合金膜の組成を蛍光X線で分析した。その結果を表1に示す。

【0026】

【表1】

| No. | ターゲット    |          | AuAg合金膜  |          |

|-----|----------|----------|----------|----------|

|     | Au (wt%) | Ag (wt%) | Au (wt%) | Ag (wt%) |

| 1   | 97       | 3        | 96.6     | 3.4      |

| 2   | 90       | 10       | 88.8     | 11.2     |

| 3   | 60       | 40       | 65.3     | 34.7     |

10

【0027】

得られた各合金膜を、窒素雰囲気下、450 の温度で40分間熱処理し、その最表面側からオージェ分析を実施した。

その結果を図15～図17に示す。

図15～図17によれば、いずれの組成比においても、シリコンの這い上がりを抑制することを示しており、AuAgの合金膜の最表面に酸素も検出されていないことが示されている。

【0028】

実施例7：半導体チップ

実施例4と同様の方法により、実施例2で得られターゲットを用いて、シリコンからなる半導体チップ上に、AuAg合金膜(200nm)の電極を形成し、窒素雰囲気下にて380 で40分間、加熱処理を施した。その後の半導体チップに対するAuAg合金膜による電極の接着面強度を測定した。

その結果を表2に示す。なお、強度測定は、半導体チップの側面から加重をかけ、テンションゲージを使用して測定を行った。チップは0.6mm×0.6mmの大きさに切断し、Agペーストを用いてダイボンド加工したもので評価した。

【0029】

【表2】

|              | ダイボンド強度平均値 | 測定個数 |

|--------------|------------|------|

| AuAg合金膜による電極 | 500g       | 100  |

| Au膜による電極     | 495g       | 50   |

20

30

40

【0030】

表2によれば、AuAg合金膜による電極は、Au膜による電極と同等以上の接着強度を示しており、ダイボンド面での強度がチップ自体の強度よりも強いことが、破壊試験により確認できた。

【0031】

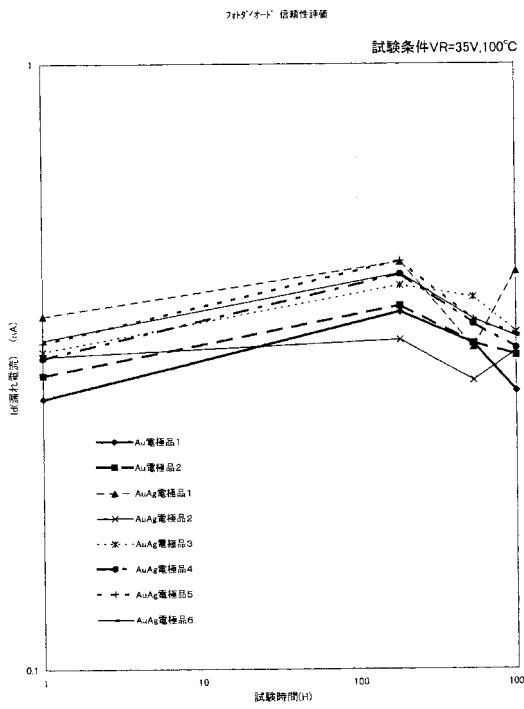

実施例8：半導体チップ

光半導体チップとしてフォトダイオードを作製した。フォトダイオードは、半導体基板上(表面)にパターニングを施し、アノード層を形成した後、実施例2で得られたAuAg合金ターゲットを用い、実施例4に示す製造方法により、半導体基板の裏側にAuAg合

50

金膜を 200 nm 形成し、窒素雰囲気中、380 にて、40 分間熱処理を施し、カソード電極を形成することにより、作製した。

このようなフォトダイオードに対して、逆電圧を 35 V 印加し、100 に加熱しながら AuAg 合金材料により形成された電極のリーク電流に関する電気的特性・信頼性を評価した。その結果を図 18 に示す。また、フォトダイオードの短絡電流 (Isc) を測定した。

その結果、リーク電流、短絡電流のいずれにおいても、Au 膜に比較して、大きな特性のシフトや変動が認められず、実用的には問題がないことを確認した。

また、AuAg 合金膜を用いた場合においても、Au 膜を用いた場合と同様の良品歩留まりが得られた。

10

### 【0032】

#### 実施例 9：半導体チップ

光半導体チップとしてフォトトランジスタを作製した。フォトトランジスタは、半導体基板上（表面）にパターニングを施し、ベース・エミッタ層を形成した後、実施例 2 で得られた AuAg 合金ターゲットを用い、実施例 4 に示す製造方法により、半導体基板の裏側に AuAg 合金膜を 200 nm 形成し、窒素雰囲気中、380 にて 40 分間熱処理を施し、コレクタ電極を形成することにより、作製した。

このフォトトランジスタを用いて、コレクタ・エミッタ間飽和電圧 VCE(sat)、コレクタ・エミッタ間降伏電圧 (BVCEO) を測定した。

その結果、コレクタ・エミッタ間飽和電圧 VCE(sat)、コレクタ・エミッタ間降伏電圧のいずれにおいても、Au 膜に比較して、特性のシフトや変動が認められず、実用的には問題がないことを確認した。

20

### 【0033】

さらに、電極としての信頼性を確認するための通電試験及び温度サイクル試験を実施したが、いずれの場合においても良好な結果が得られた。

ここで、通電試験は、常温（25）と高温（85）とで行った。測定条件として、順方向に流す電流 (IF) をそれぞれ 50 mA (25 時)、30 mA (85 時) とし、コレクタ・エミッタ間電力値 (Pc) をそれぞれ 150 mW (25 時)、70 mW (85 時) に設定した。温度サイクル試験は、-55 と 120 とで各 30 分間待機を繰り返すことにより、行った。

30

### 【0034】

#### 実施例 10：半導体チップ

半導体チップとして、フォトトライアックを作製した。このフォトトライアックは、半導体基板上（表面）にパターニングを施し、ベース・エミッタ層を形成した後、実施例 2 で得られた AuAg 合金ターゲットを用い、実施例 4 に示す製造方法により、半導体基板の裏側に AuAg 合金膜を 200 nm 形成し、窒素雰囲気中、380 にて、40 分間熱処理を施し、コレクタ電極を形成することにより、作製した。

このようなフォトトライアックを用いて、保持電流 (IH)、オン電圧 (VT)、最小トリガ電流 (IFT)、繰り返しピークオフ電圧 (VDRM) を測定した。

その結果、保持電流、オン電圧、最小トリガ電流、繰り返しピークオフ電圧のいずれにおいても、Au 膜に比較して、特性のシフトや変動が認められず、実用的には問題がないことを確認した。

40

### 【0035】

#### 【発明の効果】

本発明によれば、Au を主成分とし、Ag を 3 wt % 以上 40 wt % 以下の範囲で含有してなる合金材料を用いることにより、組成が安定し、Ag 単体の金属材料に比較して抵抗等の性能を安定させることができることが可能になる。また、加熱処理を施した前後での組成変化を最小限に抑えることができる。

特に、Au 及び Ag が 3 N 以上の純度である場合には、不純物による電気的な特性の劣化を防止することができ、より高品質の金属材料を提供することが可能となる。

50

また、本発明の半導体用合金材料を、スパッタリングターゲット材料、蒸着用材料及びボンディング用ワイヤー材料の形態で用いることにより、従来から汎用されている方法そのまま、特別な設備を要することなく、用いることができる。

### 【0036】

しかも、AuAg合金は貴金属であるため、他の金属材料に比べて回収、リサイクルが容易であり、環境に対しても配慮することが可能である。

さらに、本発明の半導体用合金材料を金属膜として形成して半導体チップ等を構成する場合には、電子機器、電子部品等の光学的及び電気的な特性を向上させることができ、より信頼性の高い電子機器、電子部品等を実現することができる。しかも、加工性に優れ、機器又は部品等の歩留まりを向上させることができるとともに、AgはAuよりも安価するために、Au単体を用いる場合に比較して、より安価な電子機器、電子部品等を提供することができる。10

### 【図面の簡単な説明】

【図1】AuAg合金材料についてのAgの組成比に対する硫化量及び接触抵抗の関係を示すグラフである。

【図2】本発明の半導体用合金材料をシリコン基板上に形成した場合のAuAg合金膜の応力(ウエハソリ量で規定)を示す図である。

【図3】本発明の半導体用合金材料をシリコン基板上に形成した場合のAuAg合金膜の応力(ウエハうねり量で規定)を示す図である。

【図4】本発明の半導体用合金材料をシリコン基板上に形成した場合のAuAg合金膜の膜厚に対する抵抗値を示す図である。20

【図5】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、300~40分の加熱処理を施した後のオージェ分析によるデプスプロファイルを示す図である。

【図6】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、380~40分の加熱処理を施した後のオージェ分析によるデプスプロファイルを示す図である。

【図7】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、420~40分の加熱処理を施した後のオージェ分析によるデプスプロファイルを示す図である。30

【図8】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、470~40分の加熱処理を施した後のオージェ分析によるデプスプロファイルを示す図である。

【図9】Au膜をシリコン基板上に200nm堆積し、380~40分の加熱処理を施した後のオージェ分析によるデプスプロファイルを示す図である。

【図10】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、300~40分の加熱処理を施した後の最表面を観察したSEM写真である。

【図11】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、380~40分の加熱処理を施した後の最表面を観察したSEM写真である。40

【図12】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、420~40分の加熱処理を施した後の最表面を観察したSEM写真である。

【図13】本発明の半導体用合金材料によるAuAg合金膜(Ag 25wt%)をシリコン基板上に200nm堆積し、470~40分の加熱処理を施した後の最表面を観察したSEM写真である。

【図14】Au膜をシリコン基板上に200nm堆積し、380~40分の加熱処理を実施した後の最表面を観察したSEM写真である。

【図15】本発明の半導体用合金材料によるAuAg合金膜(Ag 3wt%)をシリコン50

基板上に 200 nm 堆積し、470~40 分の加熱処理を施した後のオージェ分析によるデブスプロファイルを示す図である。

【図 16】本発明の半導体用合金材料による AuAg 合金膜 (Ag 10 wt %) をシリコン基板上に 200 nm 堆積し、470~40 分の加熱処理を施した後のオージェ分析によるデブスプロファイルを示す図である。

【図 17】本発明の半導体用合金材料による AuAg 合金膜 (Ag 40 wt %) をシリコン基板上に 200 nm 堆積し、470~40 分の加熱処理を施した後のオージェ分析によるデブスプロファイルを示す図である。

【図 18】本発明の半導体用合金材料による AuAg 合金膜をフォトダイオードの電極として形成した場合の電気特性 (漏れ電流) を示した図である。

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

フロントページの続き

F ターム(参考) 4M104 AA01 BB09 BB38 CC01 DD34 DD37 DD40 DD52 DD64 DD68

DD79 FF02 GG05 GG06