(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6957367号

(P6957367)

(45) 発行日 令和3年11月2日(2021.11.2)

(24) 登録日 令和3年10月8日(2021.10.8)

(51) Int.Cl.

G O 1 L 1/18 (2006.01)

F 1

G O 1 L 1/18

B

請求項の数 20 (全 22 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2018-6678 (P2018-6678)      |

| (22) 出願日  | 平成30年1月18日(2018.1.18)         |

| (65) 公開番号 | 特開2019-124638 (P2019-124638A) |

| (43) 公開日  | 令和1年7月25日(2019.7.25)          |

| 審査請求日     | 令和2年9月3日(2020.9.3)            |

(出願人による申告) 平成26年度、国立研究開発法人新エネルギー・産業技術総合開発機構、「S i P（戦略的イノベーション創造プログラム）／次世代パワーエレクトロニクス／S i C次世代パワーエレクトロニクスの統合的研究開発（研究開発項目1 S i Cに関する拠点型共通基盤技術開発）」に係る委託業務、産業技術力強化法第19条の適用を受ける特許出願

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 110002147<br>特許業務法人酒井国際特許事務所          |

| (72) 発明者  | 加藤 光章<br>東京都港区芝浦一丁目1番1号 株式会社東芝内       |

| (72) 発明者  | 牛流 章弘<br>東京都港区芝浦一丁目1番1号 株式会社東芝内       |

| (72) 発明者  | 廣畑 賢治<br>東京都港区芝浦一丁目1番1号 株式会社東芝内       |

最終頁に続く

(54) 【発明の名称】半導体チップの検査装置、半導体チップの検査システム、インテリジェントパワーモジュール、半導体チップの検査方法及びプログラム

## (57) 【特許請求の範囲】

## 【請求項1】

応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体チップに接続され、各半導体チップに流れた電流から各半導体チップの電気抵抗値を検出する検出部と、

電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを保持する第1記憶部と、

前記検出部で検出された各半導体チップの電気抵抗値を前記第1記憶部に保持された前記モデルデータを用いて前記特性値に変換する変換部と、

前記変換部で変換された前記特性値を前記複数の半導体チップごとの時系列データとして蓄積する第2記憶部と、

を備える、半導体チップの検査装置。

## 【請求項2】

前記検出部で取得された各半導体チップの前記電気抵抗値を前記複数の半導体チップごとの時系列データとして保存する第3記憶部をさらに備える請求項1に記載の半導体チップの検査装置。

## 【請求項3】

前記モデルデータは、前記電気抵抗値の変化率を前記特性値に変換する変換式である請求項1に記載の半導体チップの検査装置。

## 【請求項4】

前記変換式は、電気抵抗の変化率に対して、温度と、各方向の応力成分と、各方向のひ

ずみ成分とのうちの少なくとも 1 つを含む請求項 3 に記載の半導体チップの検査装置。

**【請求項 5】**

各方向の前記応力成分は、熱応力の成分と、実装応力の成分と、外力の成分とのうちの少なくとも 1 つを含む請求項 4 に記載の半導体チップの検査装置。

**【請求項 6】**

各方向の前記ひずみ成分は、熱ひずみの成分と、実装によるひずみの成分と、外力によるひずみの成分とのうちの少なくとも 1 つを含む請求項 4 に記載の半導体チップの検査装置。

**【請求項 7】**

前記変換式は、温度と応力 - 抵抗変化率との関係を示す係数を含む請求項 5 に記載の半導体チップの検査装置。10

**【請求項 8】**

前記変換部は、前記外力及び前記実装応力が既知である場合、前記変換式を用いて前記電気抵抗の変化率から前記温度を特定する請求項 5 に記載の半導体チップの検査装置。

**【請求項 9】**

前記変換部は、前記温度が既知であって且つ前記外力が既知である場合、前記変換式を用いて前記実装応力を特定する請求項 5 に記載の半導体チップの検査装置。

**【請求項 10】**

前記変換部は、前記温度が既知であって且つ前記実装応力が既知である場合、前記変換式を用いて前記外力を特定する請求項 5 に記載の半導体チップの検査装置。20

**【請求項 11】**

各半導体チップの電気抵抗の変化量を  $R_{on}$  とし、各半導体チップに応力が印加されていない状態での電気抵抗値を  $R_{o_n}$  とし、各半導体チップに応力を印加した際の電気抵抗の変化率を  $r_p$  とした場合、前記変換式は、以下の式(1)で与えられる

**【数 1】**

$$\Delta R_{on} = R_{on} \times r_p \quad (1)$$

請求項 3 に記載の半導体チップの検査装置。

**【請求項 12】**

温度と応力 - 抵抗変化率との関係を示す係数を  $\alpha$  とし、応力と抵抗変化率との関係を示す係数を  $\beta$  とし、温度と熱応力との関係を示す係数を  $\gamma$  とし、外力を  $\sigma$  とし、実装応力を  $\sigma_f$  とし、ジャンクション温度を  $T_j$  とし、基準温度を  $T_0$  とした場合、前記式(1)における前記電気抵抗の変化率  $r_p$  は、以下の式(2)で表される30

**【数 2】**

$$\begin{aligned} r_p &= r_p(\sigma_x, \sigma_y, T_j) \\ &= \{\alpha_x(T_j - T_0) + 1\}\beta_x\{\gamma_x(T_j - T_0) + \sigma_{x,f} + \sigma_{x,o}\} + \{\alpha_y(T_j - T_0) + 1\}\beta_y\{\gamma_y(T_j - T_0) + \sigma_{y,f} + \sigma_{y,o}\} \end{aligned} \quad (2)$$

請求項 11 に記載の半導体チップの検査装置。

**【請求項 13】**

各半導体チップは、炭化シリコン基板を含み、前記炭化シリコン基板の<11-20>方向が主要な応力負荷方向と平行になるように配置されている請求項 1 に記載の半導体チップの検査装置。40

**【請求項 14】**

前記第2記憶部に蓄積された前記複数の半導体チップごとの前記特性値の前記時系列データを用いて各半導体チップの故障確率を計算する解析部をさらに備える請求項 1 に記載の半導体チップの検査装置。

**【請求項 15】**

1 つ以上のセンサと、

前記 1 つ以上のセンサで得られた情報と前記特性値とを比較し、当該比較の結果に基づ50

いて、前記第1記憶部に保持されている前記モデルデータを修正する演算部と、

を更に備える請求項1に記載の半導体チップの検査装置。

**【請求項16】**

前記演算部は、前記1つ以上のセンサで得られた前記情報と前記特性値とのうちの少なくとも1つを用いて解析処理を実行する機能を備え、

前記第1記憶部は、前記解析処理を実行する際に前記演算部が使用するパラメータを格納する

請求項15に記載の半導体チップの検査装置。

**【請求項17】**

応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体チップに接続され、各半導体チップに流れた電流から各半導体チップの電気抵抗値を検出する検出部と、10

電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを保持する第1記憶部と、

前記検出部で検出された各半導体チップの電気抵抗値を前記第1記憶部に保持された前記モデルデータを用いて前記特性値に変換する変換部と、

前記変換部で変換された前記特性値を前記複数の半導体チップごとの時系列データとして蓄積する第2記憶部と、

を備える、半導体チップの検査システム。

**【請求項18】**

応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体素子形成領域と、20

各半導体素子形成領域に流れた電流から各半導体素子形成領域の電気抵抗値を検出する検出部と、

電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを保持する第1記憶部と、

前記検出部で検出された各半導体素子形成領域の電気抵抗値を前記第1記憶部に保持された前記モデルデータを用いて前記特性値に変換する変換部と、

前記変換部で変換された前記特性値を前記複数の半導体素子形成領域ごとの時系列データとして蓄積する第2記憶部と、

を備えるインテリジェントパワーモジュール。

**【請求項19】**

応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体チップそれぞれに流れた電流から各半導体チップの電気抵抗値を検出し、30

前記検出された各半導体チップの電気抵抗値を、電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを用いて特性値に変換し、

前記変換により得られた前記特性値を前記複数の半導体チップごとの時系列データとして蓄積し、

前記蓄積された前記複数の半導体チップごとの前記時系列データを解析する、半導体チップの検査方法。

**【請求項20】**

応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体チップに接続された半導体チップの検査装置が備えるプロセッサを機能させるためのプログラムであって、40

前記複数の半導体チップそれぞれに流れた電流から各半導体チップの電気抵抗値を検出し、

前記検出された各半導体チップの電気抵抗値を、電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを用いて特性値に変換し、

前記変換により得られた前記特性値を前記複数の半導体チップごとの時系列データとして蓄積する

ことを前記プロセッサに実行させるためのプログラム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の実施形態は、検査装置、検査システム、インテリジェントパワーモジュール、検査方法及びプログラムに関する。

**【背景技術】****【0002】**

近年、1又は複数の半導体デバイスを搭載した半導体モジュールは、幅広い分野の基幹部品として欠かすことができない存在となっている。例えばパワー半導体モジュールは、産業や医療機器のみならず、鉄道や自動車などにも用いられており、数年単位という長期間に渡る過酷な条件の下での使用に耐え得る程度の高い信頼性が求められている。10

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特許第4011345号公報

【特許文献2】特許第4329477号公報

【特許文献3】特開平11-64124号公報

【特許文献4】特開平4-307331号公報

【特許文献5】特開平1-290948号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

以下の実施形態では、半導体モジュールの信頼性の向上を可能にする検査装置、検査システム、インテリジェントパワーモジュール、検査方法及びプログラムを提供することを目的とする。

**【課題を解決するための手段】****【0005】**

実施形態に係る半導体チップの検査装置は、応力負荷方向に対して電気抵抗の変化率が異なる複数の半導体チップに接続され、各半導体チップに流れた電流から各半導体チップの電気抵抗値を検出する検出部と、電気抵抗値を温度、応力及びひずみのうちの少なくとも1つを示す特性値に変換するためのモデルデータを保持する第1記憶部と、前記検出部で検出された各半導体チップの電気抵抗値を前記第1記憶部に保持された前記モデルデータを用いて前記特性値に変換する変換部と、前記変換部で変換された前記特性値を前記複数の半導体チップごとの時系列データとして蓄積する第2記憶部とを備える。30

**【図面の簡単な説明】****【0006】**

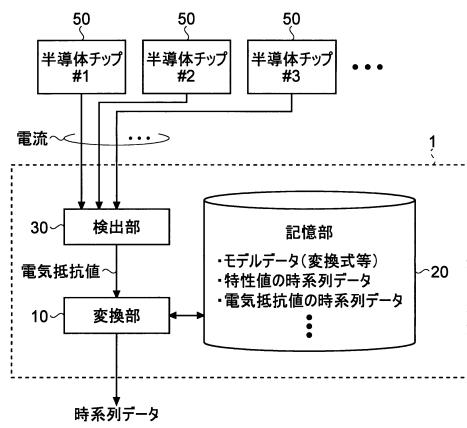

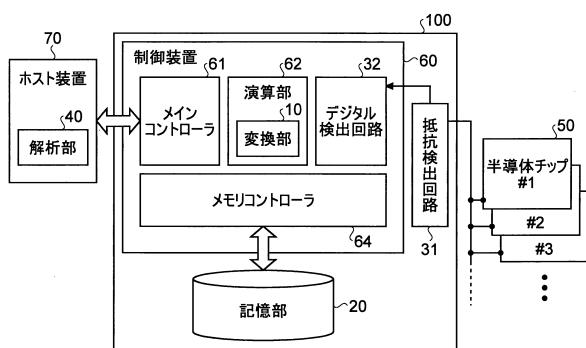

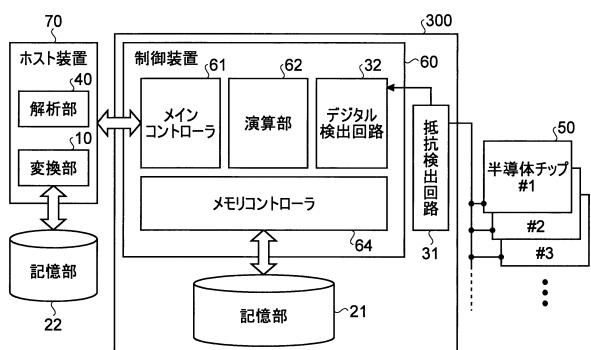

【図1】図1は、第1の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

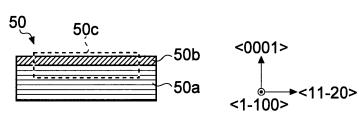

【図2】図2は、第1の実施形態に係る半導体チップの一例を示す断面図である。

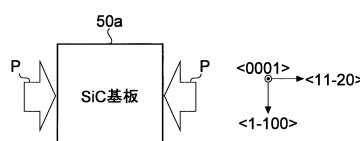

【図3】図3は、第1の実施形態に係る半導体チップに与える応力の方向を説明するための図である。40

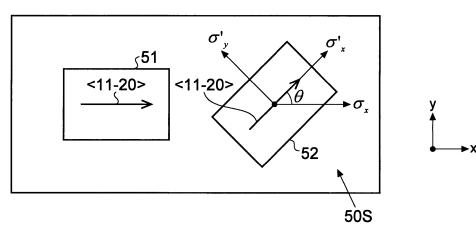

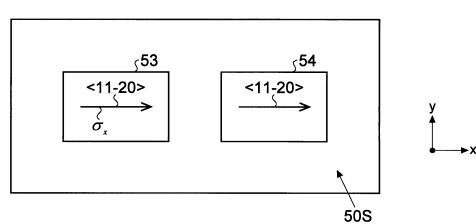

【図4】図4は、第1の実施形態に係る半導体チップの実装レイアウトの一例を示す図である。

【図5】図5は、第1の実施形態に係る半導体チップの実装レイアウトの他の一例を示す図である。

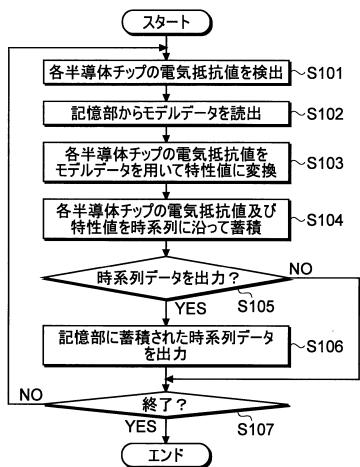

【図6】図6は、第1の実施形態に係る検査方法の一例を示すフローチャートである。

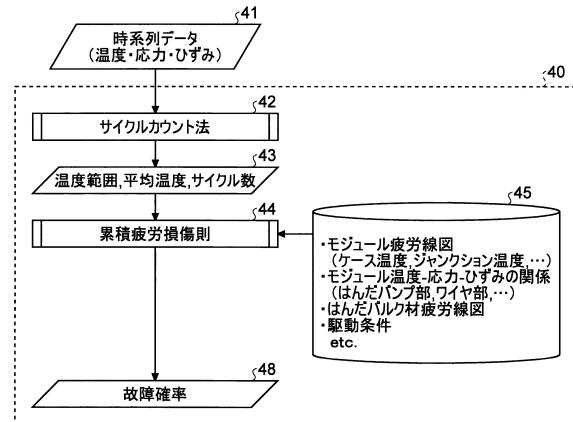

【図7】図7は、第1の実施形態で例示する故障予測処理を実行する解析部の概略例を示すブロック図である。

【図8】図8は、第2の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。50

【図9】図9は、第3の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

【図10】図10は、第4の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

【図11】図11は、第5の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

【図12】図12は、第6の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

【図13】図13は、第7の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。

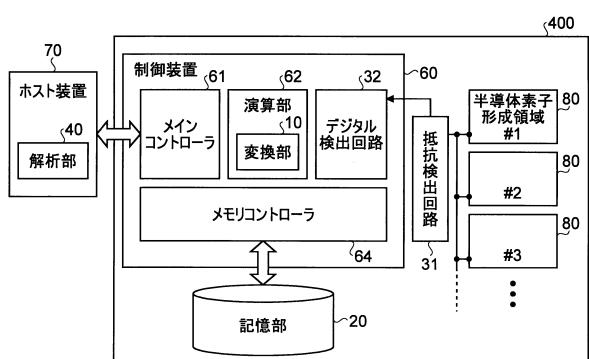

【図14】図14は、第8の実施形態に係るインテリジェントパワーモジュールの概略構成例を示すブロック図である。

#### 【発明を実施するための形態】

##### 【0007】

以下、添付図面を参照しながら、例示する実施形態にかかる検査装置、検査システム、インテリジェントパワーモジュール、検査方法及びプログラムを詳細に説明する。

##### 【0008】

上述したように、近年の半導体モジュールには高い信頼性が求められている。例えば鉄道や自動車などの分野においては、機器の故障が重大事故につながることも考えられるため、半導体モジュールの信頼性向上が特に要求されている。

##### 【0009】

半導体モジュールの信頼性向上には、電気・熱・応力の複合する領域において、実使用環境下までを含む統合的な解析システムを開発することが大事であるところ、このような解析システムへの入力データとしては、半導体モジュール内部の温度・応力・ひずみ等のデータが有用であると考えられる。

##### 【0010】

従来は、温度センサやひずみセンサ等の付加部品を半導体モジュール内部に配置することで、温度・応力・ひずみ等がモニタリングされていた。しかしながら、更なる小型化・高耐熱化・低コスト化を実現するためには、半導体モジュール内部にセンサ等の付加部品を極力設けることをせずに、温度や応力やひずみ等を特定できることが望ましい。そこで、例えば半導体モジュール自身に流れる電気信号を活用することで、半導体モジュール内部の温度や応力等を特定する方法が有効であると考えられる。また、更なる高精度化を実現するためには、センサ等の付加部品の情報と、半導体モジュール自身の情報とを共に活用することで、半導体モジュール内部の温度や応力等を特定する方法が有効であると考えられる。

##### 【0011】

ただし、半導体の電気特性の変化は、応力や温度だけでなく、応力の方向にも依存する。例えば、炭化シリコン（SiC）単結晶の（0001）面においては、<11-20>方向に圧縮又は引張応力を加えた場合、<1-100>方向と比較して、<11-20>方向の電気抵抗がより大きく減少又は増加する場合がある。また、一般的に用いられるシリコン（Si）、窒化ガリウム（GaN）、酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）等の半導体においても、チップに与えた応力の方向に応じて、電気抵抗の変化率が異なっている場合がある。

##### 【0012】

加えて、近年のパワー半導体モジュールにおいては、モジュール内部にメモリや演算回路等を搭載する、いわゆるインテリジェントパワーモジュールが開発されており、そのデータ記録機能や情報処理機能を利用した新たな付加価値のある製品の創出が求められている。

##### 【0013】

そこで、以下の実施形態では、半導体モジュール内部の温度や応力やひずみ等のデータ

10

20

30

40

50

を取得することで、半導体モジュールの信頼性を向上することを可能にする検査装置、検査システム、インテリジェントパワーモジュール、検査方法及びプログラムについて、幾つか例を挙げて説明する。

【0014】

(第1の実施形態)

まず、第1の実施形態に係る検査装置、検査システム、検査方法及びプログラムについて、図面を参照して詳細に説明する。本実施形態では、半導体に外部から応力や温度を与えた際の電気抵抗の変化率(抵抗変化率)から半導体の温度や各方向の応力を求める。その際に、本実施形態では、半導体に生じた応力の方向(応力負荷方向ともいう)に対する抵抗変化率の依存性が考慮される。それにより、半導体内部の温度・応力・ひずみ等をより詳細且つ正確に特定することができ、その結果、半導体モジュールの信頼性を向上することを可能にする検査装置、検査システム、検査方法及びプログラムを実現することが可能となる。10

【0015】

図1は、本実施形態に係る検査装置(又は検査システム)の概略構成例を示すブロック図である。図1に示すように、検査装置1は、変換部10と、記憶部20と、検出部30とを備える。

【0016】

検出部30は、例えば複数の半導体チップ50それぞれに接続されており、各半導体チップ50に作り込まれた半導体素子の動作時に流れる電流を入力し、入力された電流と半導体素子を動作させるために印加した電圧との関係(以下、電流電圧特性という)から、半導体素子のオン抵抗(以下、半導体チップ50のオン抵抗という)の値をそれぞれ電気抵抗値として検出する。そして検出部30は、半導体チップ50ごとに検出した電気抵抗値を変換部10へそれぞれ入力する。20

【0017】

記憶部20は、例えばDRAM(Dynamic Random Access Memory)(SDRAM(Synchronous DRAM)を含む)やSRAM(Static Random Access Memory)等によって構成された記憶領域である。ただし、これらに限定されず、フラッシュメモリやハードディスクドライブや磁気テープレコーダ等の種々の記憶装置を記憶部20に用いることが可能である。30

【0018】

この記憶部20は、電気抵抗値を半導体チップ50の温度や応力やひずみ等の値(以下、特性値という)に変換するモデルデータを保持する。このモデルデータは、例えば、電気抵抗値を入力として特性値を出力する変換式であってもよいし、電気抵抗値と特性値との対応関係が予め登録された変換テーブルであってもよい。なお、変換式の例については、後述において触れる。

【0019】

変換部10は、記憶部20に接続されており、検出部30から入力された電気抵抗値を記憶部20から読み出したモデルデータを用いて特性値に変換する。そして、変換部10は、検出部30から入力された電気抵抗値と、この電気抵抗値を変換することで得られた特性値とを記憶部20に入力する。これに対し、記憶部20は、入力された電気抵抗値及び特性値を、半導体チップ50ごとに区別しつつ時系列に沿って蓄積する。これにより、記憶部20には、各半導体チップ50に関する電気抵抗値の時系列データと特性値の時系列データとが保持される。なお、電気抵抗値については、検出部30から直接、記憶部20に入力されてもよい。また、本実施形態では、モデルデータと特性値の時系列データと電気抵抗値の時系列データとが共通の記憶部20に記憶されるが、このような構成に限定されず、それぞれ異なる記憶部に記憶されてもよい。40

【0020】

また、変換部10は、記憶部20に蓄積された電気抵抗値や特性値の時系列データを読み出して、外部へ出力する。外部に出力された時系列データは、電気・熱・応力等の複合50

する領域において、各半導体チップ 50 の特性や状況を実使用環境下までを含めて統合的に解析する解析処理に利用され得る。このような解析処理には、例えば、各半導体チップ 50 の故障時期等を予測する故障予測処理（寿命予測処理ともいう）など、半導体チップ 50 の信頼性に関する種々の解析処理を適用することができる。ただし、電気抵抗値や特性値の時系列データは、このような解析処理に限定されることなく、種々の用途に用いられてよい。

#### 【0021】

ここで、図 1 に示す半導体チップ 50 について説明する。本実施形態に係る各半導体チップ 50 は、例えば SiC 基板に対してユニポーラ型半導体素子やバイポーラ型半導体素子などの半導体素子が作り込まれた半導体デバイスである。図 2 に、本実施形態に係る半導体チップ 50 の一例を示す。図 2 に示すように、半導体チップ 50 は、半導体基板としての SiC 基板 50a と、SiC 基板 50a の(0001)面に対して平行又は所定のオフ角で傾いている素子形成面に形成された SiC エピタキシャル膜 50b を備える。SiC 基板 50a の素子形成面及び SiC エピタキシャル膜 50b には、ユニポーラ型半導体素子やバイポーラ型半導体素子などの種々の半導体素子が形成された素子形成領域 50c が設けられている。なお、ユニポーラ型半導体素子とは、電流通電時に電子あるいは正孔のみが電気伝導に作用する半導体素子であり、例えば、ショットキーバリヤダイオード（SBD）、接合電界効果トランジスタ（J-FET）、金属／酸化膜／半導体電界効果トランジスタ（MOS-FET）などが該当し得る。また、バイポーラ型半導体素子とは、電子と正孔の両者が電気伝導に作用する半導体素子であり、例えば、pn ダイオード、バイポーラ型接合トランジスタ（BJT）、サイリスタ、ゲートターンオフサイリスタ（GTO サイリスタ）、絶縁ゲート型バイポーラトランジスタ（IGBT）などが該当し得る。

#### 【0022】

このような半導体チップ 50 では、上述したように、半導体チップ 50 の電気特性が、応力や温度だけでなく、応力負荷方向にも依存して変化する。例えば、図 3 に例示したような、半導体基板に SiC 基板 50a を用いた半導体チップ 50 では、SiC 基板 50a の(0001)面においては、<11-20> 方向に圧縮応力 P を加えた場合、<1-100> 方向と比較して、<11-20> 方向の電気抵抗がより大きく減少する場合がある。反対に、<11-20> 方向に引張応力を加えた場合、<1-100> 方向と比較して、<11-20> 方向の電気抵抗がより大きく増加する場合がある。同様に、シリコン（Si）基板や窒化ガリウム（GaN）基板や酸化ガリウム（Ga<sub>2</sub>O<sub>3</sub>）基板等の一般的に使用される半導体基板を用いた場合でも、半導体チップ 50 の電気特性が、応力や温度だけでなく、応力負荷方向にも依存して変化する。なお、以下では、一例として、半導体チップ 50 が SiC 基板 50a を用いて構成されている場合を説明する。

#### 【0023】

そこで本実施形態では、図 4 に示すように、例えば、実装された半導体チップ 50 に与える応力（以下、実装応力という）の方向が一様の実装面 50S に複数の半導体チップ 50（図 4 では、2つの半導体チップ 51 及び 52）を搭載する場合、それぞれの半導体チップ 50 の方向が異なるように配置する。それにより、各半導体チップ 50 から得られる電気抵抗値の差から、それぞれの半導体チップ 50 に対する特性値をより正確に求めることが可能となる。なお、図 4 に示す例では、複数の半導体チップ 51 及び 52 それぞれで、SiC 基板 50a の結晶方向に対する半導体素子の向き（例えばチャネルにおける電流の流れ方向）が同一であるものとする。

#### 【0024】

ただし、複数の半導体チップ 50 間で SiC 基板 50a 及び / 又は SiC エピタキシャル膜 50b の特性（例えば応力及びその方向に対する抵抗値の変化率）や、SiC 基板 50a の結晶方向に対する半導体素子の向きや、他のデバイス構造・特性等が異なる場合には、図 5 に示すように、複数の半導体チップ 50（図 5 では、2つの半導体チップ 53 及び 54）を揃えるようにして、実装面 50S に配置されてもよい。そのような構成で

10

20

30

40

50

あっても、各半導体チップ 50 から得られる電気抵抗値の差から、それぞれの半導体チップ 50 に対する特性値をより正確に求めることが可能となる。

#### 【0025】

さらに、複数の半導体チップ 50 間で SiC 基板 50a 及び / 又は SiC エピタキシャル膜 50b の特性（例えば応力及びその方向に対する抵抗値の変化率）や、SiC 基板 50a の結晶方向に対する半導体素子の向きや、他のデバイス構造・特性等が異なる場合に、図 4 に示すように、それぞれの半導体チップ 50 の方向が異なるように配置されてもよい。そのような構成であっても、各半導体チップ 50 から得られる電気抵抗値の差から、それぞれの半導体チップ 50 に対する特性値をより正確に求めることが可能となる。

#### 【0026】

なお、以下の説明において、図 4 に例示したような、複数の半導体チップ 50 間で SiC 基板 50a の特性や SiC 基板 50a の結晶方向に対する半導体素子の向きや、他のデバイス構造・特性等が同じである半導体チップ 50 を、「特性の同じ半導体チップ 50」という。一方、図 5 に例示したような、複数の半導体チップ 50 間で SiC 基板 50a の特性や SiC 基板 50a の結晶方向に対する半導体素子の向きや、他のデバイス構造・特性等のいずれかが異なる半導体チップ 50 を、「特性の異なる半導体チップ 50」という。

#### 【0027】

つづいて、本実施形態に係るモデルデータの例について、以下に説明する。なお、以下の説明では、変換式をモデルデータとした場合を例示する。

#### 【0028】

以下の式(1)は、電気抵抗値を温度及び応力の値（特性値）に変換するための変換式の一例である。変換式(1)では、半導体チップ 50 のオン抵抗変化  $R_{on}$  が、半導体チップ 50 に応力が印加されていない状態（無応力という）でのオン抵抗  $R_{on}$  と、半導体チップ 50 に応力を印加した状態（以下、応力印加という）でのオン抵抗変化率  $r_p$  とに分離されている。

#### 【数1】

$$\Delta R_{on} = R_{on} \times r_p \quad (1)$$

#### 【0029】

なお、変換式(1)において、オン抵抗変化  $R_{on}$  は、例えばデータシートや実測値から設定される値である。また、オン抵抗変化率  $r_p$  は、以下の変換式(2)を用いて求められる値である。

#### 【数2】

$$\begin{aligned} r_p &= r_p(\sigma_x, \sigma_y, T_j) \\ &= \{\alpha_x(T_j - T_0) + 1\}\beta_x\{\gamma_x(T_j - T_0) + \sigma_{x,f} + \sigma_{x,o}\} + \{\alpha_y(T_j - T_0) + 1\}\beta_y\{\gamma_y(T_j - T_0) + \sigma_{y,f} + \sigma_{y,o}\} \end{aligned} \quad (2)$$

#### 【0030】

変換式(2)において、 $\alpha$  は、温度と抵抗変化率との関係を示す係数である。 $\beta$  は、応力と抵抗変化率との関係を示す係数である。 $\gamma$  は、温度と熱応力との関係を示す係数である。 $\sigma$  は、外部応力（外力）の値である。 $\sigma_f$  は、実装時に半導体チップ 50 に残留する残留応力（以下、実装応力という）の値である。 $T_j$  は、ジャンクション温度である。 $T_0$  は、係数  $\alpha$ 、 $\beta$  及び  $\gamma$  の各係数を設定した際の基準温度である。また、添え字  $x$ 、 $y$  は空間座標である。

#### 【0031】

このように、応力印加によるオン抵抗変化率  $r_p$  は、各方向の応力  $\sigma_x$  及び  $\sigma_y$  と、ジャンクション温度  $T_j$  とに依存している。また、応力  $\sigma_x$  及び  $\sigma_y$  は、駆動時の熱応力  $(T_j - T_0)$  と、実装応力  $\sigma_f$  と、その他の外力  $\sigma_o$  とに分けることができる。

10

20

30

40

50

## 【0032】

ここで、係数 $\alpha_{ij}$ 及び $\Lambda$ については、実験で得られた実測値や、半導体チップ50のデバイスシミュレーションや、構造解析や、それらの組み合わせにより事前に取得することができる。また、実装応力 $\sigma$ は、ラマン分光測定などの実験、または、デバイスシミュレーション、または、構造解析、または、それらの組み合わせにより、事前に取得することができる。

## 【0033】

以上のような変換式(2)を、半導体チップ50をn(nは1以上の整数)個配置し、m(mは1以上の整数)方向の応力成分を考慮する場合に当てはめると、n個の半導体チップ50それぞれのオン抵抗変化率 $r_{p1} \sim r_{pn}$ は、以下の式(3)のように表される。

10

## 【数3】

$$\begin{cases} r_{p1} = \alpha_{11}\sigma_1 + \alpha_{12}\sigma_2 + \Lambda + \alpha_{1m}\sigma_m \\ r_{p2} = \alpha_{21}\sigma_1 + \alpha_{22}\sigma_2 + \Lambda + \alpha_{2m}\sigma_m \\ \vdots \\ r_{pn} = \alpha_{n1}\sigma_1 + \alpha_{n2}\sigma_2 + \Lambda + \alpha_{nm}\sigma_m \end{cases} \quad (3)$$

## 【0034】

ここで、オン抵抗変化率ベクトル $\vec{r}_p$ 、応力ベクトル $\vec{\sigma}$ 及び行列Aを以下の式(4)のように定義する。なお、本説明において、<>付き文字はベクトルを表している。

20

## 【数4】

$$\vec{r}_p = \begin{bmatrix} r_{p1} \\ r_{p2} \\ \vdots \\ r_{pn} \end{bmatrix}, \quad \vec{\sigma} = \begin{bmatrix} \sigma_1 \\ \sigma_2 \\ \vdots \\ \sigma_m \end{bmatrix}, \quad A = \begin{bmatrix} \alpha_{11} & \alpha_{12} & \cdots & \alpha_{1m} \\ \alpha_{21} & \alpha_{22} & \cdots & \alpha_{2m} \\ \vdots & \vdots & \ddots & \vdots \\ \alpha_{n1} & \alpha_{n2} & \cdots & \alpha_{nm} \end{bmatrix} \quad (4)$$

## 【0035】

30

すると、上述した式(3)は、以下の式(5)で表すことができる。

## 【数5】

$$\vec{r}_p = A\vec{\sigma} \quad (5)$$

## 【0036】

ここで、 $n = m$ の場合、応力ベクトル $\vec{\sigma}$ は、行列Aの逆行列 $A^{-1}$ をガウスの消去法など、任意の公知の計算手法で計算することで、以下の式(6)のように得ることができる。

## 【数6】

$$\vec{\sigma} = A^{-1}\vec{r}_p \quad (6)$$

40

## 【0037】

一方、 $n > m$ の場合、応力ベクトル $\vec{\sigma}$ は、最小二乗法や他の統計的手法など、任意の公知の計算手法を用いて得ることができる。

## 【0038】

なお、ここでは、各方向に平行な応力成分についてのみを対象として説明したが、せん断応力や、最大主応力や、最小主応力や、ミーゼス応力など、任意の応力を対象とすることができます。また、式(2)や式(3)や式(5)などのオン抵抗変化率 $r_p$ の変換式においては、応力 $\sigma$ (又はそのベクトルやテンソル)の代わりにひずみ(又はそのベクトルやテンソル)が用いられてもよいし、これらの式に加えて、別途、応力とひずみの変換式

50

が適用されてもよい。すなわち、本実施形態に係るオン抵抗変化率  $r_p$  の変換式は、温度と、各方向の応力と、各方向のひずみ成分とのうちの少なくとも1つの項を含んで構成されたものであってよい。その際、各方向の応力成分には、熱応力の成分と、実装応力の成分と、外力の成分とのうちの少なくとも1つが含まれ得る。また、各方向のひずみ成分には、熱ひずみの成分と、実装によるひずみの成分と、外力によるひずみの成分とのうちの少なくとも1つが含まれ得る。

#### 【0039】

(外力・実装応力が既知である場合：温度算出)

つづいて、半導体チップ50が2個の場合の具体的な算出例について説明する。例えば、外力 $\sigma_o$ 及び実装応力 $\sigma_f$ が既知である場合(それぞれの応力が負荷されていない場合を含む)、オン抵抗変化率 $r_p$ は、以下の変換式(7)に示すように、温度以外のパラメータを係数a, b及びcとしてまとめることができる。10

#### 【数7】

$$\begin{aligned} r_p &= \{\alpha_x(T_j - T_0) + 1\}\beta_x\{\gamma_x(T_j - T_0) + \sigma_{x,f} + \sigma_{x,o}\} + \{\alpha_y(T_j - T_0) + 1\}\beta_y\{\gamma_y(T_j - T_0) + \sigma_{y,f} + \sigma_{y,o}\} \\ &= aT_j^2 + bT_j + c \end{aligned} \quad (7)$$

#### 【0040】

その結果、ジャンクション温度 $T_j$ については、以下の式(8)に示すように、解の公式を用いて求めることが可能となる。20

#### 【数8】

$$T_j = \frac{-b + \sqrt{b^2 - 4ac}}{2a} \quad (8)$$

#### 【0041】

(温度が既知である場合：x, y方向の応力算出)

一方、ジャンクション温度 $T_j$ が既知である場合(ジャンクション温度 $T_j$ が基準温度 $T_0$ と等しい場合を含む)、オン抵抗変化率 $r_p$ は、以下の変換式(9)に示すように、応力( $\sigma_o$ 及び $\sigma_f$ )以外のパラメータを係数a及びbとしてまとめることができる。30

#### 【数9】

$$\begin{aligned} r_p &= \{\alpha_x(T_j - T_0) + 1\}\beta_x\{\gamma_x(T_j - T_0) + \sigma_{x,f} + \sigma_{x,o}\} + \{\alpha_y(T_j - T_0) + 1\}\beta_y\{\gamma_y(T_j - T_0) + \sigma_{y,f} + \sigma_{y,o}\} \\ &= a\sigma_x + b\sigma_y \end{aligned} \quad (9)$$

#### 【0042】

・特性の異なる半導体チップの場合

ここで、例えば図5に例示したように、特性の異なる2個の半導体チップ50を同じ向きで実装面50Sに配置した場合、半導体チップ53のオン抵抗変化率 $r_{p1}$ と半導体チップ54のオン抵抗変化率 $r_{p2}$ とは、以下の式(10)のように表される。40

#### 【数10】

$$\begin{cases} r_{p1} = a_{1x}\sigma_x + a_{1y}\sigma_y \\ r_{p2} = a_{2x}\sigma_x + a_{2y}\sigma_y \end{cases} \quad (10)$$

#### 【0043】

したがって、それぞれの半導体チップ53及び54における応力 $\sigma_x$ 及び $\sigma_y$ は、以下の式(11)より求めることができる。

## 【数11】

$$\begin{Bmatrix} \sigma_x \\ \sigma_y \end{Bmatrix} = \frac{1}{a_{1x}a_{2y} - a_{2x}a_{1y}} \begin{bmatrix} a_{2y} & -a_{1y} \\ -a_{2x} & a_{1x} \end{bmatrix} \begin{Bmatrix} r_{p1} \\ r_{p2} \end{Bmatrix} \quad (11)$$

## 【0044】

・特性の同じ半導体チップの場合

一方、図4に例示したように、特性の同じ2個の半導体チップ51及び52を互いに異なる向きで実装面50Sに配置した場合、半導体チップ51のオン抵抗変化率 $r_{p1}$ と半導体チップ52のオン抵抗変化率 $r_{p2}$ とは、以下の式(12)のように表される。

10

## 【数12】

$$\begin{cases} r_{p1} = a_{1x}\sigma_x + a_{1y}\sigma_y \\ r_{p2} = a_{1x}\sigma'_x + a_{1y}\sigma'_y \end{cases} \quad (12)$$

## 【0045】

また、半導体チップ52の応力 $\sigma'_x$ 及び $\sigma'_y$ は、以下の式(13)のように表すことができる。

## 【数13】

$$\begin{cases} \sigma'_x = \sigma_x \cos\theta + \sigma_y \sin\theta \\ \sigma'_y = -\sigma_x \sin\theta + \sigma_y \cos\theta \end{cases} \quad (13)$$

20

## 【0046】

そこで、式(13)を式(12)に代入することで、以下の式(14)のように、係数 $a_{2x}$ 及び $a_{2y}$ を求めることができる。なお、式(12)及び式(14)において、係数 $a_{1x}$ 及び $a_{1y}$ は、SiC基板50aの<11-20>方向が応力負荷方向と一致している半導体チップ51に対する係数であり、係数 $a_{2x}$ 及び $a_{2y}$ は、SiC基板50aの<11-20>方向が応力負荷方向に対して角度 $\theta$ で傾いている半導体チップ52に対する係数である。

## 【数14】

30

$$\begin{cases} a_{2x} = a_{1x} \cos\theta - a_{1y} \sin\theta \\ a_{2y} = a_{1x} \sin\theta + a_{1y} \cos\theta \end{cases} \quad (14)$$

## 【0047】

よって、上述した式(12)は、以下の式(15)のように変換することができる。

## 【数15】

$$\begin{cases} r_{p1} = a_{1x}\sigma_x + a_{1y}\sigma_y \\ r_{p2} = a_{2x}\sigma_x + a_{2y}\sigma_y \end{cases} \quad (15)$$

40

## 【0048】

ここで、式(15)は式(10)と一致している。したがって、応力 $\sigma_x$ 及び $\sigma_y$ は、上述の式(11)から求めることができる。

## 【0049】

なお、図5及び図4に示す構成では、少なくとも1つの半導体チップ50におけるSiC基板50aの<11-20>方向が、実装応力の方向（応力が複数存在する場合は主要な応力負荷方向）と実質的に一致していてもよい。その場合、<11-20>方向が実装応力の方向と実質的に一致している半導体チップ50の電気抵抗値が、応力に対して感度良く変化する場合があるため、より正確に個々の半導体チップ50の特性値を求めることができとなる。

50

## 【0050】

( 温度が既知である場合 :  $x$ ,  $y$  方向の実装応力・外力算出 )

上述したように、ジャンクション温度  $T_j$  が既知 ( ジャンクション温度  $T_j$  が基準温度  $T_0$  と等しい場合を含む ) である場合、オン抵抗変化率  $r_p$  は変換式 ( 9 ) で表すことができる。ここで、外力  $f$  が既知である場合 ( 外力が負荷されていない場合を含む )、変換式 ( 9 ) が単純化された結果、以下の式 ( 16 ) を用いて、 $x$ ,  $y$  方向それぞれの実装応力  $f$  を算出することが可能となる。

## 【数16】

$$\begin{aligned}\sigma_{x,f} &= \sigma_x - \gamma_x (T_j - T_0) - \sigma_{x,o} \\ \sigma_{y,f} &= \sigma_y - \gamma_y (T_j - T_0) - \sigma_{y,o}\end{aligned}\quad (16)$$

10

## 【0051】

また、ジャンクション温度  $T_j$  が既知 ( ジャンクション温度  $T_j$  が基準温度  $T_0$  と等しい場合を含む ) であって実装応力  $f$  が既知である場合 ( 実装応力が負荷されていない場合を含む ) も同様に、変換式 ( 9 ) が単純化された結果、以下の式 ( 17 ) を用いて、 $x$ ,  $y$  方向それぞれの外力  $f$  を算出することが可能となる。

## 【数17】

$$\begin{aligned}\sigma_{x,o} &= \sigma_x - \gamma_x (T_j - T_0) - \sigma_{x,f} \\ \sigma_{y,o} &= \sigma_y - \gamma_y (T_j - T_0) - \sigma_{y,f}\end{aligned}\quad (17)$$

20

## 【0052】

以上のように、本実施形態によれば、電気抵抗値を半導体チップ 50 の温度や応力等の特性値に変換する変換式をモデルデータとして用いることで、検出部 30 から入力された電気抵抗値から、各半導体チップ 50 の特性値をより正確に求めることが可能となる。

## 【0053】

次に、本実施形態に係る検査装置 ( 又は検査システム ) 100 が実行する検査方法について、図面を用いて詳細に説明する。図 6 は、本実施形態に係る検査方法の一例を示すフローチャートである。

30

## 【0054】

図 6 に示すように、本動作では、まず、検出部 30 が、動作中の各半導体チップ 50 より入力された電流の電流値から各半導体チップ 50 のオン抵抗の値をそれぞれ電気抵抗値として検出し ( ステップ S101 ) 、変換部 10 に入力する。なお、ステップ S101 は、各半導体チップ 50 が通常動作を実行している最中に実行されてもよいし、図 6 に示す動作を実行するために各半導体チップ 50 に通常動作とは異なる動作を実行させた際に実行されてもよい。

## 【0055】

次に、変換部 10 が、電気抵抗値を温度や応力等の特性値に変換するためのモデルデータを記憶部 20 から読み出し ( ステップ S102 ) 、つづいて、入力された各半導体チップ 50 の電気抵抗値を、モデルデータを用いて各半導体チップ 50 の特性値に変換する ( ステップ S103 ) 。

40

## 【0056】

次に、変換部 10 は、入力された各半導体チップ 50 の電気抵抗値と、これを変換することで得られた特性値とを、時系列を特定するための情報 ( 例えば日時情報等 ) と共に記憶部 20 に蓄積する ( ステップ S104 ) 。これにより、記憶部 20 内には、各半導体チップ 50 に関する電気抵抗値の時系列データと特性値の時系列データとが保持される。なお、電気抵抗値については、検出部 30 から直接、時系列を特定するための情報 ( 例えば日時情報等 ) と共に記憶部 20 に入力されてもよい。

## 【0057】

50

次に、変換部 10 が、記憶部 20 に蓄積された電気抵抗値や特性値の時系列データを外部へ出力するか否かを判断し(ステップ S105)、時系列データを出力すると判断した場合(ステップ S105 の YES)、記憶部 20 から時系列データを読み出して外部へ出力する(ステップ S106)。例えば、変換部 10 は、外部に接続されたパーソナルコンピュータ等のホスト装置から時系列データを要求された場合に、時系列データを外部へ出力すると判断し(ステップ S105 の YES)、つづいて、記憶部 20 から時系列データを読み出し、この読み出した時系列データを有線又は無線でホスト装置へ出力する(ステップ S106)。一方、時系列データを出力しないと判断した場合(ステップ S105 の NO)、変換部 10 は、ステップ S106 をスキップして、ステップ S107 へ進む。

#### 【0058】

10

ステップ S107 では、本動作を終了するか否かが判断される。この判断は、例えば変換部 10 が実行してもよいし、不図示のコントローラが実行してもよい。終了しないと判断された場合(ステップ S107 の NO)、本動作は、ステップ S101 へリターンする。一方、終了すると判断された場合(ステップ S107 の YES)、本動作は終了する。

#### 【0059】

以上のようにして記憶部 20 に蓄積された時系列データは、上述したように、例えば、電気・熱・応力等の複合する領域において、各半導体チップ 50 の特性や状況を実使用環境下までを含めて統合的に解析する解析処理に利用され得る。そこで、本実施形態では、このような解析処理の一例として、各半導体チップ 50 の故障時期等を予測する故障予測処理を例示する。

20

#### 【0060】

図 7 は、本実施形態で例示する故障予測処理を実行する解析部の概略例を示すブロック図である。なお、図 7 に例示する解析部 40 は、検査装置 1 から出力された時系列データのうち、温度・応力・ひずみのいずれか、または、すべてに関する時系列データ(温度履歴ともいう)を用いて故障予測処理を実行するものとする。また、図 7 において、長方形で表されたブロックは解析機能を示し、平行四辺形で表されたブロックはデータを示し、円柱形はデータベースを表している。

#### 【0061】

30

図 7 に示すように、検査装置 1 から温度、応力及びひずみのうちの少なくとも 1 つの時系列データ 41 が入力されると、解析部 40 では、まず、入力された温度、応力及びひずみのうちの少なくとも 1 つの時系列データ 41 に対してサイクルカウント法 42 が適用されることで、各サイクルの温度範囲、平均温度、応力範囲、ひずみ範囲及びサイクル数 43 が求められる。つづいて、求められた各サイクルの温度範囲、平均温度、ひずみ範囲、応力範囲、及びサイクル数 43 と、前もってデータベース 45 に格納しておいた温度・ひずみ・応力の関係、各種の疲労線図、駆動条件などのうちの少なくとも 1 つから、累積疲労損傷則 44 に基づくことで、故障確率 48 が求められる。

#### 【0062】

40

なお、図 7 で例示した「故障予測」の代わりに、設定した温度又は応力又はひずみの閾値を超えた際に装置停止等の処理を行うための「故障検知」や「保護回路」、温度・応力・ひずみに応じて駆動方式等を修正するための「補正制御回路」、温度・応力・ひずみに応じて、記憶部 20 に含まれる抵抗変化率の変換式における係数等を修正するための「モデル補正回路」、及び、包括的な保守サービスを提供する「保守ソリューション」などを、解析部 40 が実行するように構成することも可能である。若しくは、「故障予測」を含むこれらのうちの 2 つ以上の組合せを解析部 40 が実行するように構成することもできる。

#### 【0063】

以上のように、本実施形態によれば、半導体に外部から応力や温度を与えた際の電気抵抗の変化率(抵抗変化率)から半導体の温度や各方向の応力を求める際に、半導体に生じた応力の方向(応力負荷方向)に対する抵抗変化率の依存性が考慮される。それにより、半導体内部の温度・応力・ひずみ等をより詳細且つ正確に特定することができ、その結果

50

、半導体モジュールの信頼性を向上することを可能にする検査装置、検査システム、検査方法及びプログラムを実現することが可能となる。

#### 【0064】

##### (第2の実施形態)

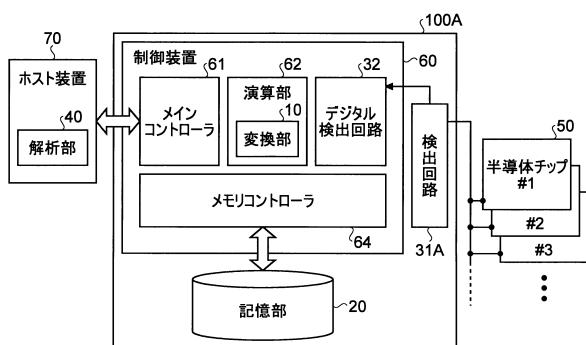

次に、第2の実施形態に係る検査装置、検査システム、検査方法及びプログラムについて、図面を参照して詳細に説明する。本実施形態では、第1の実施形態に係る検査装置、検査システム、検査方法及びプログラムのより具体的な構成例を説明する。なお、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。

#### 【0065】

10

図8は、第2の実施形態に係る検査装置(又は検査システム)の概略構成例を示すプロック図である。図8に示すように、検査装置100は、制御装置60と、記憶部20と、抵抗検出回路31とを備える。

#### 【0066】

記憶部20は、第1の実施形態で説明したように、例えばDRAMやSRAM等によって構成された記憶領域であり、電気抵抗値を半導体チップ50の温度や応力等の特性値に変換するモデルデータを保持する。

#### 【0067】

20

抵抗検出回路31は、例えば複数の半導体チップ50それぞれに接続されており、各半導体チップ50に作り込まれた半導体素子の動作時に流れる電流を入力し、入力された電流と半導体素子を動作させるために印加した電圧との関係を示す電流電圧特性から、各半導体チップ50のオン抵抗値をそれぞれアナログの電気抵抗値として検出する。

#### 【0068】

制御装置60は、例えばSoC(System-On-Chip)などの集積回路であってよい。この制御装置60は、メインコントローラ61と、演算部62と、メモリコントローラ64と、デジタル検出回路32とを備える。なお、メインコントローラ61、演算部62、メモリコントローラ64及びデジタル検出回路32は、不図示の内部バス等を介して相互に通信可能に接続されている。

#### 【0069】

30

メインコントローラ61は、例えばCPU(Central Processing Unit)等の情報処理装置と、無線又は有線のインターフェース回路又はネットワークカード(NIC)とを用いて構成される。このメインコントローラ61は、制御装置60を構成する各部を統括的に制御する他、外部のホスト装置70との間で無線又は有線にてデータやコマンド等の送受信を実行する。

#### 【0070】

演算部62は、例えばDSP(Digital Signal Processor)やCPU等の情報処理装置と、RAM(Random Access Memory)などの記憶領域とを用いて構成され、種々の演算処理を実行する。

#### 【0071】

40

メモリコントローラ64は、例えばDRAMやSRAM等で構成された記憶部20に対するデータの書き込み/読み出しを制御する。

#### 【0072】

デジタル検出回路32は、抵抗検出回路31に接続されており、抵抗検出回路31で検出されたアナログの電気抵抗値をデジタルの電気抵抗値に変換する。

#### 【0073】

このような構成において、抵抗検出回路31とデジタル検出回路32とは、第1の実施形態における検出部30を構成する。また、第1の実施形態における変換部10は、例えば演算部62の少なくとも一部の機能として実現される。

#### 【0074】

50

したがって、本実施形態では、抵抗検出回路31で検出されたアナログの電気抵抗値が

デジタル検出回路 3 2 でデジタルの電気抵抗値に変換される。そして、演算部 6 2 の変換部 1 0 が、デジタルの電気抵抗値を、記憶部 2 0 から読み出されたモデルデータを用いて特性値に変換し、これにより得られた特性値と、デジタル検出回路 3 2 で得られたデジタルの電気抵抗値とが、時系列に沿って記憶部 2 0 に蓄積される。

#### 【 0 0 7 5 】

また、メインコントローラ 6 1 は、ホスト装置 7 0 からの要求に応じて、記憶部 2 0 から電気抵抗値及び / 又は特性値の時系列データを読み出し、読み出した時系列データをホスト装置 7 0 へ送信する。

#### 【 0 0 7 6 】

ホスト装置 7 0 は、例えばパーソナルコンピュータやスマートデバイスなどで構成され 10 おり、種々の情報処理機能を備える。本実施形態では、ホスト装置 7 0 が第 1 の実施形態に係る解析部 4 0 を備えている。したがって、ホスト装置 7 0 は、検査装置 1 0 0 から入力された時系列データを解析部 4 0 に入力し、解析部 4 0 において、故障予測処理などの種々の処理を実行する。そして、ホスト装置 7 0 は、解析部 4 0 による処理の結果を、不図示のディスプレイやスピーカ等を用いてユーザへ出力する。

#### 【 0 0 7 7 】

その他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

#### 【 0 0 7 8 】

##### ( 第 3 の実施形態 )

第 2 の実施形態では、抵抗検出回路 3 1 は、例えば複数の半導体チップ 5 0 それぞれに接続されており、各半導体チップ 5 0 に作り込まれた半導体素子の動作時に流れる電流を入力し、入力された電流と半導体素子を動作させるために印加した電圧との関係を示す電流電圧特性から、各半導体チップ 5 0 のオン抵抗値をそれぞれアナログの電気抵抗値として検出したが、このような構成に限定されない。そこで第 3 の実施形態では、第 2 の実施形態の変形例について説明する。なお、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。

#### 【 0 0 7 9 】

図 9 は、第 3 の実施形態に係る検査装置（又は検査システム）の概略構成例を示すプロ 30 ック図である。図 9 に示すように、本実施形態に係る検査装置 1 0 0 A は、図 8 に示した検査装置 1 0 0 と同様の構成において、抵抗検出回路 3 1 が検出回路 3 1 A に置き換えられている。

#### 【 0 0 8 0 】

本実施形態では、検出回路 3 1 A は、例えば複数の半導体チップ 5 0 それぞれに接続されており、各半導体チップ 5 0 に作り込まれた半導体素子の動作時に流れる電流と、半導体素子を動作させるために印加した電圧とを入力し、その電流及び電圧をデジタル検出回路 3 2 へと出力する。

#### 【 0 0 8 1 】

デジタル検出回路 3 2 は、検出回路 3 1 A に接続されており、検出回路 3 1 A で検出されたアナログの電流及び電圧をデジタルの電流値及び電圧値に変換する。そして、演算部 6 2 の変換部 1 0 が、デジタルの電流値及び電圧値を電気抵抗値に変換し、さらに、記憶部 2 0 から読み出されたモデルデータを用いて特性値に変換し、これにより得られた特性値と、デジタル検出回路 3 2 で得られたデジタルの電気抵抗値とが、時系列に沿って記憶部 2 0 に蓄積される。

#### 【 0 0 8 2 】

その他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

#### 【 0 0 8 3 】

##### ( 第 4 の実施形態 )

上述の実施形態では、半導体チップ 5 0 から得られた情報に基づいて、温度や応力やひ 50

すみ等を特定していたが、このような構成に限定されない。そこで第4の実施形態では、半導体チップ50から得られた情報に加え、半導体チップ50以外から得られた情報にも基づいて、温度や応力やひずみ等を特定する場合について、例を挙げて説明する。なお、以下では、第3の実施形態をベースとして説明するが、上述又は後述する他の実施形態に対しても同様に適用することが可能である。また、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。

#### 【0084】

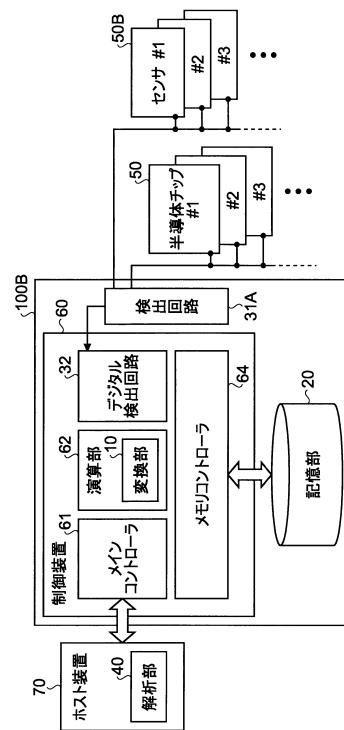

図10は、第4の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。図10に示すように、本実施形態に係る検査装置100Bは、図9に示した検査装置100Aと同様の構成において、複数のセンサ50Bが配置されている。10

#### 【0085】

本実施形態では、検出回路31Aは、例えば複数の半導体チップ50、および、複数のセンサ50Bそれぞれに接続される。複数のセンサ50Bには、温度センサ、ひずみセンサ、加速度センサ、湿度センサなどの任意のセンサを、任意の組み合わせで用いることができる。

#### 【0086】

センサ50Bから得られる、温度、ひずみ等の情報は、半導体チップ50から得られる特性値と共に、時系列データとして記憶部20に保存されてもよい。また、本実施形態では、例えば演算部62が、センサ50Bから得られる、温度、ひずみ等の情報と、半導体チップ50の特性値とを比較し、その結果に基づいて、記憶部20に含まれるモデルデータ（オン抵抗変化率に関する変換式の係数）が修正されてもよい。20

#### 【0087】

その他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

#### 【0088】

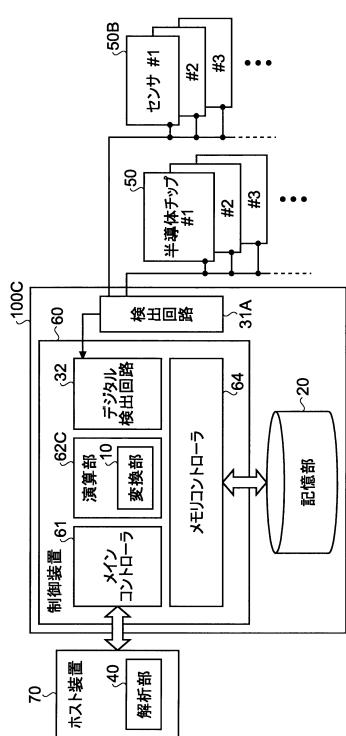

##### （第5の実施形態）

第4の実施形態では、半導体チップ50、および、各種センサ50Bから得られた情報を用いて温度や応力やひずみ等を特定していたが、このような構成に限定されない。そこで第5の実施形態では、第4の実施形態の变形例について説明する。なお、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。30

#### 【0089】

図11は、第5の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。図11に示すように、本実施形態に係る検査装置100Cは、図10に示した検査装置100Bと同様の構成において、演算部62が演算部62Cに置き換えられている。

#### 【0090】

演算部62Cは、オン抵抗変化率 $r_p$ に関する上記変換式を用いた演算を実行する変換部10に加え、電気回路や熱回路などの任意の回路解析機能や、電磁場解析、熱流体解析、構造解析、デバイスシミュレーションなどの、有限差分法、有限体積法、有限要素法等の計算手法を用いた任意の物理解析機能を備えている。40

#### 【0091】

また、本実施形態では、記憶部20は、変換部10が使用するモデルデータ、並びに、電気抵抗値及び／又は特性値の時系列データに加え、回路解析や物理解析等の各種解析処理を実行する際に使用する各種パラメータを格納する。このパラメータには、例えば、物性値、境界条件、駆動条件等が含まれ得る。演算部62Cは、記憶部20内に格納されている各半導体チップ50の特性値や各種センサ50Bから得られた情報に対し、記憶部20内に格納されている各種パラメータを用いて各種解析処理を実行する。

#### 【0092】

なお、回路解析や物理解析のために記憶部20に格納される物性値には、弾性係数、ボ50

アソン比、線膨張係数、熱伝導率、熱抵抗、比熱、密度、熱容量、電気伝導率、電子・正孔の移動度、電子・正孔の濃度などが含まれ得る。境界条件には、半導体チップ形状や、配線形状や、モジュール形状や、ヒートシンク形状や、デバイス構造などが含まれ得る。駆動条件には、入力電圧、デューティー比、周波数、ゲート抵抗、ゲート電圧などが含まれ得る。

#### 【0093】

演算部62Cが実行した各種解析処理によって得られた、温度、ひずみ等の情報は、半導体チップ50から得られる特性値や各種センサから得られる情報と共に、時系列データとして記憶部20に保存されてもよい。また、本実施形態では、演算部62Cが実行した各種解析処理によって得られた、温度、ひずみ等の情報と、半導体チップ50の特性値とを比較し、その結果に基づいて、記憶部20に含まれる、モデルデータ（例えばオン抵抗変化率に関する変換式の係数）や物性値や境界条件や駆動条件が修正されてもよい。10

#### 【0094】

他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

#### 【0095】

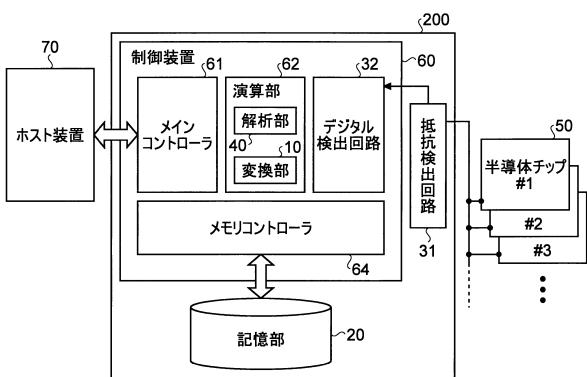

##### （第6の実施形態）

上述した第2～第5の実施形態では、解析部40が検査装置100の外部（例えばホスト装置70内）に配置された場合が例示したが、このような構成に限定されない。そこで第6の実施形態では、第2の実施形態の変形例について説明する。なお、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。20

#### 【0096】

図12は、第6の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。図12に示すように、本実施形態に係る検査装置200は、図8に示した検査装置100と同様の構成において、解析部40が制御装置60側の演算部62内に配置されている。

#### 【0097】

したがって、本実施形態では、演算部62が、ホスト装置70からの要求に応じて記憶部20から電気抵抗値及び／又は特性値の時系列データを読み出し、この読み出した時系列データを解析部40に入力する。そして、解析部40により得られた解析結果が、メインコントローラ61を介してホスト装置70へ出力され、ホスト装置70における不図示のディスプレイヤスピーカ等を用いてユーザへ出力される。30

#### 【0098】

他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

#### 【0099】

##### （第7の実施形態）

第2～第6の実施形態では、変換部10が検査装置100又は200内に配置された場合が例示したが、このような構成に限定されない。そこで第7の実施形態では、第2～第6の実施形態の変形例について説明する。なお、本実施形態では、図8に示した検査装置100をベースとした変形例を例示するが、これに限らず、例えば図12に示す検査装置200をベースとすることも可能である。また、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。40

#### 【0100】

図13は、第7の実施形態に係る検査装置（又は検査システム）の概略構成例を示すブロック図である。図13に示すように、本実施形態に係る検査装置300は、図8に示した検査装置100と同様の構成において、変換部10がホスト装置70内に配置されている。また、本実施形態では、検査装置100内の記憶部20（図8参照）が、検査装置300内の記憶部21と、ホスト装置70に接続された記憶部22とに分割されている。50

**【0101】**

検査装置300内の記憶部21は、例えばデジタル検出回路32で変換されたデジタルの電気抵抗値の時系列データを保持する。一方、ホスト装置70に接続された記憶部22は、例えば電気抵抗値を半導体チップ50の温度や応力等の特性値に変換するモデルデータと、記憶部21内の電気抵抗値の時系列データをモデルデータを用いて変換することで得られた特性値の時系列データとを保持する。

**【0102】**

したがって、本実施形態では、メインコントローラ61が、ホスト装置70からの要求に応じて記憶部21から電気抵抗値の時系列データを読み出し、この読み出した時系列データをホスト装置70へ出力する。そして、ホスト装置70内の変換部10において、電気抵抗値の時系列データがモデルデータを用いて特性値の時系列データに変換され、これにより得られた特性値の時系列データが記憶部22に格納される。その際、電気抵抗値の時系列データが記憶部22に格納されてもよい。その後、例えばユーザがホスト装置70に入力した指示に基づき、記憶部22から電気抵抗値及び／又は特性値の時系列データが読み出されて解析部40に入力され、解析部40により得られた解析結果が不図示のディスプレイやスピーカ等を用いてユーザへ出力される。

10

**【0103】**

その他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

**【0104】**

20

## (第8の実施形態)

また、上述したように、近年では、モジュール内部にメモリや演算回路等を搭載するインテリジェントパワーモジュールが存在する。そこで、第8の実施形態では、上述した実施形態に係る検査装置をインテリジェントパワーモジュールとした場合について、図面を用いて詳細に説明する。なお、本実施形態では、図8に示した検査装置100をインテリジェントパワーモジュールとした場合を例示するが、これに限らず、例えば図12に示す検査装置200や図13に示す検査装置300に対しても適用することが可能である。また、本実施形態において、上述した実施形態と同様の構成については、それらを引用することで、重複する説明を省略する。

**【0105】**

30

図14は、第8の実施形態に係るインテリジェントパワーモジュールの概略構成例を示すブロック図である。図14に示すように、本実施形態に係るインテリジェントパワーモジュール400は、図8に示した検査装置100と同様の構成において、検査装置100がインテリジェントパワーモジュール400としてモジュール化されているとともに、複数の半導体チップ50が複数の半導体素子形成領域80としてインテリジェントパワーモジュール400内に組み込まれた構成を備える。

**【0106】**

その他の構成、動作及び効果は、上述した実施形態と同様であるため、ここでは詳細な説明を省略する。

**【0107】**

40

なお、上述の実施形態では、半導体チップ50として、SiC基板50aを用いた半導体デバイスを例示したが、これに限定されるものではない。例えば、SiC基板50aに代えてSi基板、もしくは、GaN基板、もしくは、Ga<sub>2</sub>O<sub>3</sub>基板を用いた半導体デバイスが半導体チップ50として用いられてもよい。

**【0108】**

上記実施形態およびその変形例は本発明を実施するための例にすぎず、本発明はこれらに限定されるものではなく、仕様等に応じて種々変形することは本発明の範囲内であり、更に本発明の範囲内において、他の様々な実施形態が可能であることは上記記載から自明である。例えば実施形態に対して適宜例示した変形例は、他の実施形態と組み合わせることも可能であることは言うまでもない。

50

## 【符号の説明】

## 【0109】

1, 100, 100A, 100B, 100C, 200, 300...検査装置、10...変換部、20, 21, 22...記憶部、30...検出部、31...抵抗検出回路、31A...検出回路、32...デジタル検出回路、40...解析部、50, 51~54...半導体チップ、50a...SiC基板、50b...SiCエピタキシャル膜、50c...素子形成領域、50S...実装面、50B...センサ、60...制御装置、61...メインコントローラ、62, 62C...演算部、64...メモリコントローラ、70...ホスト装置、80...半導体素子形成領域、400...インテリジェントパワーモジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

審査官 公文代 康祐

(56)参考文献 特開2012-169524(JP,A)

特開2000-307011(JP,A)

米国特許出願公開第2011/0309357(US,A1)

特開2013-044550(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 01 L        1 / 18

G 01 K        7 / 01

G 01 R        31 / 26

H 01 L        29 / 84