# UK Patent Application GB 2636498

(43) Date of A Publication

(13) A

18.06.2025

(21) Application No: 2418671.0

(22) Date of Filing: 10.08.2021

Date Lodged: 19.12.2024

(30) Priority Data:

(31) 63065051 (32) 13.08.2020 (33) US

(31) 63146093 (32) 05.02.2021 (33) US

(31) 17314890 (32) 07.05.2021 (33) US

(31) 17314917 (32) 07.05.2021 (33) US

(31) 17343479 (32) 09.06.2021 (33) US

(31) 17349536 (32) 16.06.2021 (33) US

(31) 2109569 (32) 02.07.2021 (33) GB

(62) Divided from Application No

2300338.7 under section 15(9) of the Patents Act 1977

(71) Applicant(s):

Cirrus Logic International Semiconductor Limited

7B Nightingale Way, Quartermile, Edinburgh,

EH3 9EG, United Kingdom

(72) Inventor(s):

Axel Thomsen

Eric King

Anthony Doy

Thomas Hoff

John Melanson

(74) Agent and/or Address for Service:

Haseltine Lake Kempner LLP

One Portwall Square, Portwall Lane, BRISTOL,

BS1 6BH, United Kingdom

(54) Title of the Invention: **Driver circuitry and operation**

Abstract Title: **Multimode driver circuitry and operation**

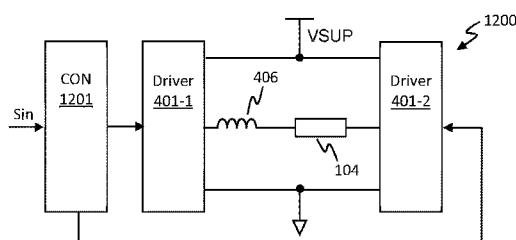

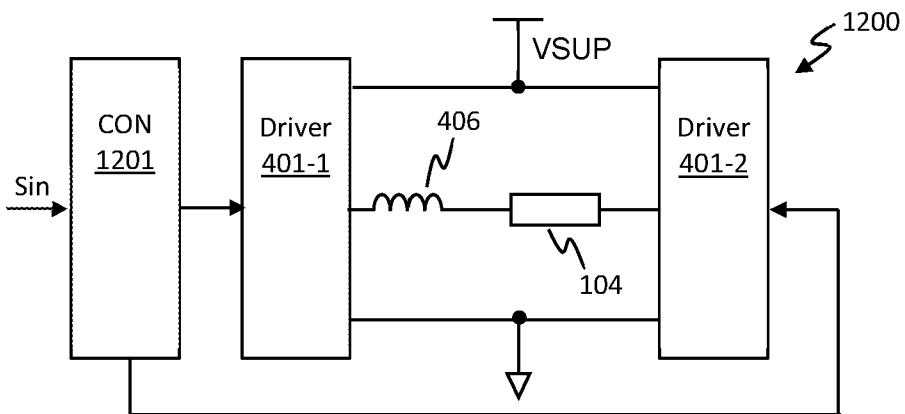

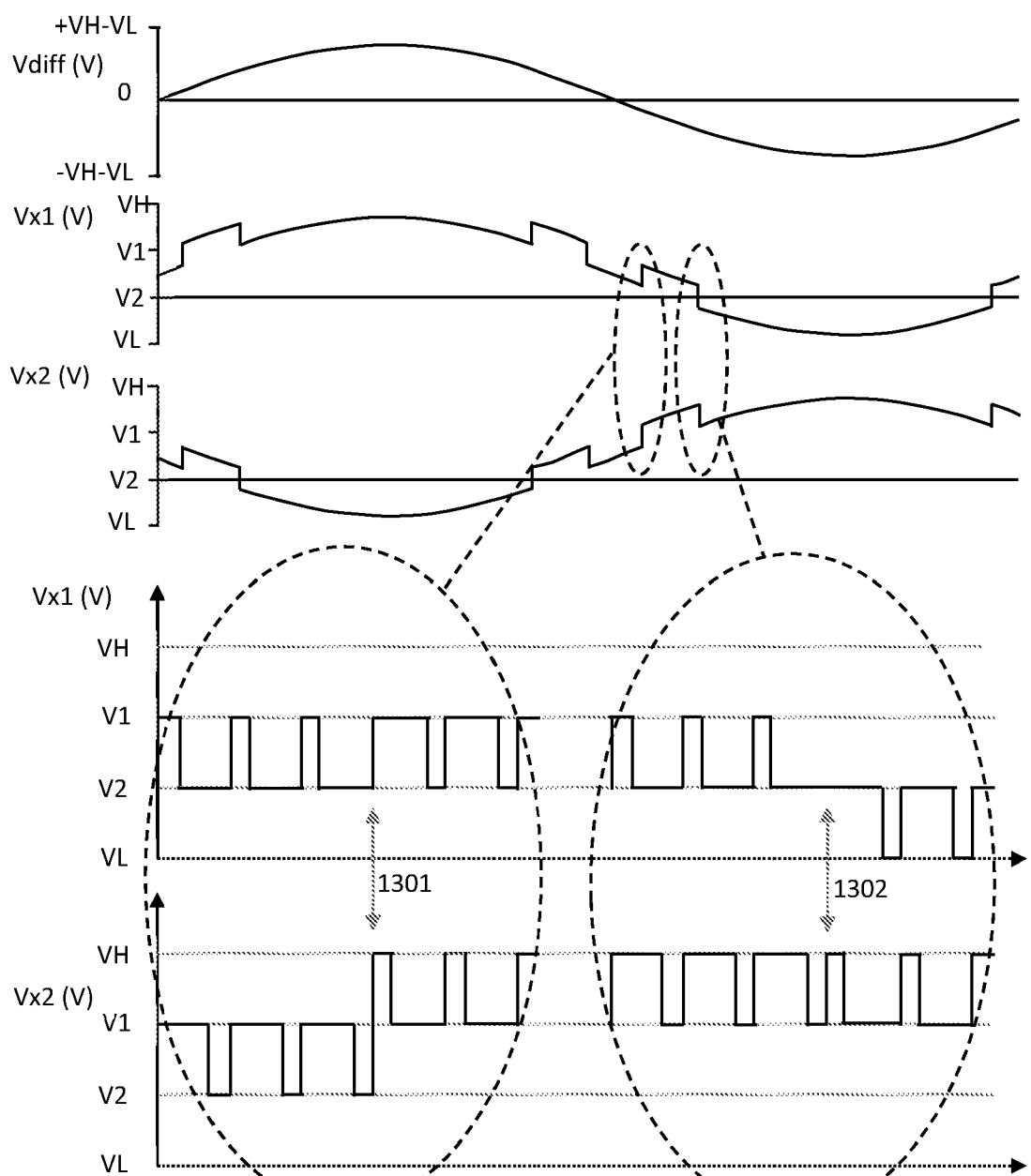

(57) A driver circuit 1200 has a first switching driver 401-1 and a second switching driver 401-2 for driving a transducer 104 in a bridge-tied-load (BTL) configuration, each switching driver having a respective output stage for controllably switching a respective driver output node between high and low switching voltages with a controlled duty cycle. Each switching driver is operable in a plurality of different driver modes, wherein the switching voltages are different in said different driver modes (e.g. Table 1). A controller 1201 controls the driver mode of operation and the duty cycle of the switching drivers based on the input signal. The controller is configured to control the duty cycles of the first and second switching drivers within defined minimum and maximum limits of duty cycles, and to transition between driver modes of operation when the duty cycle of one of the switching drivers reaches a duty cycle limit (Fig.13, 1301, 1302). The controller implements the transition by changing the driver mode of one switching driver and varying its duty cycle to the other duty cycle limit, and by maintaining the driver mode of the other switching driver and varying its duty cycle to maintain the differential output signal magnitude.

Figure 12

GB 2636498 A

Figure 1

Figure 2

Figure 3

Figure 4

Figure 5

Figure 6

Figure 7

|                                         | Switch and State | Source/bulk Voltage | Drain Voltage | NWell Voltage |

|-----------------------------------------|------------------|---------------------|---------------|---------------|

| <b>Mode 1</b><br><b>0V to +VSUP</b>     | SW1A ON          | +VSUP               | +VSUP         | +VSUP         |

|                                         | SW1B OFF         | 0V                  | +VSUP         | +VSUP         |

|                                         | SW1C ON          | +VSUP               | +VSUP         | +VSUP         |

|                                         | SWO1 DC          | 0V/+VSUP            | +VSUP         | +VSUP         |

|                                         | SWO2 DC          | 0V                  | 0V / +VSUP    | 0V            |

|                                         | SW2A OFF         | 0V                  | +VSUP         | 0V            |

|                                         | SW2B ON          | 0V                  | 0V            | 0V            |

|                                         | SW2C ON          | 0V                  | 0V            | 0V            |

| <b>Mode 2</b><br><b>+VSUP to +2VSUP</b> | SW1A ON          | + VSUP              | +VSUP         | +VSUP         |

|                                         | SW1B OFF         | 0V                  | +VSUP         | +VSUP         |

|                                         | SW1C OFF         | +VSUP               | +2VSUP        | +2VSUP        |

|                                         | SWO1 DC          | +VSUP /+2VSUP       | +2VSUP        | +2VSUP        |

|                                         | SWO2 DC          | +VSUP               | +VSUP/+2VSUP  | +VSUP         |

|                                         | SW2A ON          | +VSUP               | +VSUP         | +VSUP         |

|                                         | SW2B OFF         | 0V                  | +VSUP         | +VSUP         |

|                                         | SW2C ON          | +VSUP               | +VSUP         | +VSUP         |

| <b>Mode 3</b><br><b>-VSUP to 0V</b>     | SW1A OFF         | 0V                  | +VSUP         | +VSUP         |

|                                         | SW1B ON          | 0V                  | 0V            | 0V            |

|                                         | SW1C ON          | 0V                  | 0V            | 0V            |

|                                         | SWO1 DC          | -VSUP/0V            | 0V            | 0V            |

|                                         | SWO2 DC          | -VSUP               | -VSUP/0V      | 0V            |

|                                         | SW2A OFF         | 0V                  | +VSUP         | +VSUP         |

|                                         | SW2B ON          | 0V                  | 0V            | +VSUP         |

|                                         | SW2C OFF         | -VSUP               | 0V            | 0V            |

Figure 8

Figure 9

Figure 10

Figure 11

Figure 12

Figure 13

Figure 14

Figure 15

Figure 16

Figure 17

Figure 18

## DRIVER CIRCUITRY AND OPERATION

The field of representative embodiments of this disclosure relates to methods, apparatus and/or implementations concerning or relating to driver circuits, and in particular to

5 switching driver circuits as may be used to drive a transducer.

Many electronic devices include transducer driver circuitry for driving a transducer with a suitable driving signal, for instance for driving an audio output transducer of the host device or a connected accessory, with an audio driving signal.

10

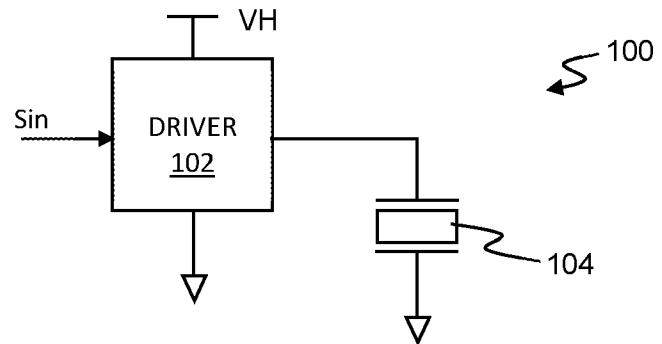

**Figure 1** is a schematic illustration of circuitry for driving a transducer. As shown generally at 100 in figure 1, a driver 102 may receive an input signal  $S_{in}$  and generate a corresponding drive signal for driving the transducer. The input signal  $S_{in}$  may, for example, be an input audio or ultrasonic signal or haptic waveform or the like and may

15 be received from upstream circuitry (not shown) such as upstream amplification and/or signal processing circuitry. The driver 102 drives the transducer 104 with the drive signal based on the input signal  $S_{in}$ . Where the transducer is an output transducer the driver 102 drives the transducer 104 to cause the transducer to produce a desired output, e.g. an audible, ultrasonic or haptic output based on the input signal  $S_{in}$ .

20

In some applications the driver 102 may include a switching amplifier stage, e.g. a class-D amplifier stage or the like, for generating the drive signal. Switching amplifier stages can be relatively power efficient and thus can be advantageously used in some applications. A switching amplifier stage generally operates to switch an output node

25 between defined high and low switching voltages, with a duty cycle that provides a desired average output voltage over the course of the duty cycle for the drive signal. To provide a desired output voltage range, the switching amplitude may be switched between the peak high and low voltages of the desired output range, for instance between a high-side voltage  $V_H$  and ground.

30

Figure 1 illustrates an example of a single-ended driver, but it will be understood that in some implementations a transducer may be driven in a bridge-tied-load configuration.

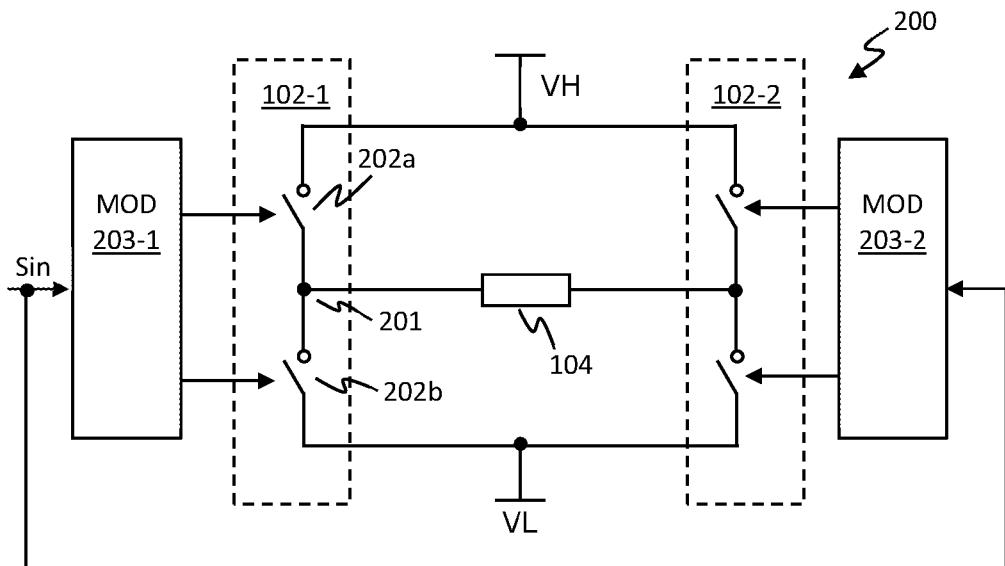

**Figure 2** illustrates an example of driver circuitry 200 for driving a bridge-tied-load (BTL).

Figure 2 illustrates that each side of the load 104 is connected to a respective driver 102-1 and 102-2. The output node 201 of each driver 102-1 and 102-2 is switched between a high-side voltage VH and a low-side voltage VL, for example between a

5 positive supply voltage and ground, with controlled duty cycles so as to control the voltage across the load 104. Figure 2 illustrates that each of the drivers 102-1 and 102-2 comprise switches 202a and 202b, which may be typically implemented as MOSFETs, for selectively connecting the output node 201 of the driver to the high-side voltage or the low-side voltage. Modulators 203-1 and 203-2 control the duty-cycle of the switching

10 of the switches 202a and 202b of the respective driver 102-1 and 102-2 based on the input signal. The modulators 105 may generate PWM or PDM switching signals based on the input signal as will be understood by one skilled in the art. The drivers 102-1 and 102-2 can thus be seen as generating respective first and second drive signals which are components of a differential driving signal for driving the load.

15

In at least some applications, for example for driving some piezoelectric transducers, it may be desirable to generate drive signals with relatively high amplitudes, for example with a peak-to-peak voltage range of the order of tens of volts or so. This may therefore typically require the input voltage for the driver 102, i.e. the voltage difference between

20 VH and VL, to be relatively high to provide the required output range.

For instance, piezoelectric or piezo transducers or ceramic transducers are increasingly being proposed for use in some applications, for instance for audio, ultrasonic or haptics output, and may be considered as an alternative to conventional cone and voice-coil type

25 speaker or resonant actuators or the like. Piezoelectric transducers may be advantageous in some applications, especially for portable electronics devices such as mobile telephones, laptop and tablet computers and the like, due to their thin form factor, which may be beneficial in meeting the demand for increasing functionality in such devices without significantly increasing their size. Piezoelectric transducers are also

30 increasingly finding application as transducers for ultrasonic and range-finding systems. Piezoelectric transducers may also be used as input transducers or sensors in some applications.

Using such high input voltages can, however, result in relatively large voltage stresses across the switches of the driver, which may require the use of devices with high voltage tolerances, which may not be practical for some applications, or which may add to the cost of the circuitry.

5

Using such high input voltages as the switching voltages for the switching drivers may also, in some implementations, require the use of components such as inductors with a relatively high inductances so as to avoid large ripple current due to the switching, which may be disadvantageous in some implementations.

10

Embodiments of the present disclosure relate to improved driving circuits.

According to an aspect of the disclosure there is provided a switching driver for driving a transducer comprising: first and second supply nodes for connection to first and second voltage supplies defining an input voltage; an output bridge stage comprising a first output switch connected between a first switching voltage node and an output node and a second output switch connected between a second switching voltage node and the output node; a capacitor; and a network of switches connecting said first and second supply nodes with said first and second switching voltage nodes and said capacitor. The network of switches may be operable in different switch states to provide different voltages at the first and second switching voltage nodes. The switch states may comprise a first switch state in which the capacitor is connected between the first and second supply nodes to be charged to the input voltage and the first and second switching voltage nodes are coupled to the first and second supply nodes respectively; and a second switch state in which the second switching voltage node is connected to a voltage different to that at the second supply node and the capacitor is connected between the second switching voltage node and the first switching voltage node to provide a boosted voltage at the first switching node. The driver may also comprise a controller configured to control the switch state of the network of switches and a duty cycle of the first and second output switches of the output bridge stage based on an input signal to generate an output signal at the output node for driving the transducer.

In some examples, in the second switch state, the second switching voltage node is connected to the first supply node. The network of switches may be further operable in

a third switch state in which the first switching voltage node is connected to the second supply node and said capacitor is connected between the second supply node and the second switching voltage node to provide a boosted voltage at the second switching node. The first voltage supply may be more positive than the second voltage supply and

- 5 the controller may be configured to operate: in the first switch state in a first mode of operation to provide a drive signal at the output node in a range between the first and second voltage supplies; in the second switch state in second mode of operation to provide a drive signal at the output node in a range between the first voltage supply and the first voltage supply boosted positively by the input voltage; and in the third switch

- 10 state in a third mode of operation to provide a drive signal at the output node in a range between the second voltage supply and the second voltage supply boosted negatively by the input voltage.

In some examples, the network of switches may be configured such that, in use, a

15 voltage difference across any of the switches of the network of switches and the first and second output switches is not substantially greater in magnitude than the input voltage.

The network of switches may be configured such a first electrode of the capacitor can be selective connected to either of the first or second supply nodes. The network of

20 switches may be configured such that a second electrode of the capacitor can be selectively connected to either of the first or second supply nodes. In some examples, the capacitor may be connected between the first and second switching voltage nodes in parallel with the output bridge stage. The network of switches may comprises: a first switch connecting the first supply node to a first supply select node; a second switch connecting the second supply node to the first supply select node; a third switch connecting the first supply select node to the first switching voltage node; a fourth switch connecting the first supply node to a second supply select node; a fifth switch connecting the second supply node to the second supply select node; and a sixth switch connecting the second supply select node to the second switching voltage node.

30

The controller may be configured such that, when operating in the second switch state: the fourth switch and sixth switch are closed, with the fifth switch open, to connect the first supply node to the second switching voltage node; and the second and third switches are open, with the first switch closed, so as to disconnect the first switching

voltage node from the first and second supply nodes and to limit the voltage difference across any of the first to third switches to be not substantially greater than the input voltage.

5 The capacitor may have a capacitance which is large enough to store sufficient charge to supply the transducer through a cycle of the input signal.

In some examples, the capacitor is a first capacitor, and the switching driver may further comprises a second capacitor. In at least one of the first and second switch states, the

10 second capacitor may be connected between the first and second voltage supplies to be charged to the input voltage. In the second switch state, the second switching voltage node may be connected to the first supply node. The switch network may be further operable in a third switch state in which the second capacitor is connected between the first supply node and the second switching voltage node to provide a boosted voltage at

15 the second switching node and the first capacitor is connected between the second switching voltage node and the first switching voltage node to provide a further boosted voltage at the first switching voltage node. The first capacitor may be connected between the first and second switching voltage nodes in parallel with the output bridge stage.

20 In some examples, at least one of the switches of the network of switches and the first and second output switches comprises an NMOS transistor where at least part of the NMOS transistor is formed within an N-well in a substrate and wherein the switching driver is configured such that the N-well of the NMOS transistor is, in use, driven with a voltage based on the voltages at the first and second switching voltage nodes.

25

In some examples, the switching driver may be a first switching driver and a switching driver circuit may further comprise a second switching driver, the first and second switching drivers being configured to drive the transducer in a bridge-tied load configuration. The second switching driver may comprise an output bridge stage, a

30 capacitor and a network of switches operable in the same way as the first switching driver. The controller may be configured to control the switch state of the network of switches and duty cycles of the output bridge stages of both the first and second switching drivers based on an input signal to generate a differential output signal.

In some examples a switching driver circuit may comprising the switching driver of any of the embodiments described herein and a DC-DC converter configured to receive at least one input voltage supply and to generate at least one of said first and second voltage supplies.

5

In some examples an inductor may be connected to the output node for connection in series with the transducer.

10 Embodiments also relate to a switching driver circuit comprising a switching driver of any of the embodiments and the transducer. The transducer may be at least one of an audio output transducer and a haptic output transducer. The transducer may be a piezoelectric or ceramic transducer. Embodiments also relate to an electronic device comprising such a switching driver.

15 In another aspect there is provided a switching driver for driving a transducer based on an input signal comprising: first and second supply nodes for connection to first and second voltage supplies defining an input voltage; an output bridge stage comprising a first output switch connected between a first switching voltage node and an output node and a second output switch connected between a second switching voltage node and the output node; a capacitor connected between said first and second switching voltage nodes in parallel with the output bridge stage; and a network of switches connecting said first and second supply nodes with said first and second switching voltage nodes, the network of switches being operable in different switch states. In a first switch, the first and second switching voltage nodes may be coupled to the first and second supply nodes respectively and the capacitor is charged to the input voltage. In a second switch state, the second switching voltage node may be connected to a voltage different to that at the second supply node and the capacitor is connected between the second switching voltage node and the first switching voltage node to provide a boosted voltage at the first switching node.

20

25

30 Aspects also relate to a switching driver for driving a transducer comprising: first and second supply nodes for connection to first and second voltage supplies defining an input voltage; an output bridge stage for selectively connecting an output node to first or second switching voltage nodes with a controlled duty cycle; a capacitor connected

between said first and second switching voltage nodes in parallel with the output bridge stage; and a network of switches connecting said first and second supply nodes with said first and second switching voltage nodes, wherein the network of switches is operable such that a first electrode of said capacitor can be selectively connected to 5 either of the first and second supply nodes.

In a yet further aspect, there is provided a driver circuit for driving a transducer based on an input signal comprising: first and second switching drivers with respective driver output nodes for driving said transducer in a bridge-tied-load configuration, each of the 10 first and second switching drivers comprising a respective output stage for controllably switching the respective driver output node between high and low switching voltages with a controlled duty cycle. Each of the first and second switching drivers is operable in a plurality of different driver modes, wherein the switching voltages are different in said different driver modes; and a controller controls the driver mode of operation and the 15 duty cycle of each of the first and second switching drivers based on the input signal. The controller is configured to control the duty cycles of the first and second switching drivers within defined minimum and maximum limits of duty cycles. The controller is configured to transition between different driver modes of operation when the duty cycle of at least one of the first and second switching drivers reaches the maximum or minimum 20 duty cycle limit and the controller is configured to implement the transition by changing the driver mode of one of the first and second switching drivers at said maximum or minimum limit of duty cycle and vary the duty cycle of that one of the first and second switching drivers to the other limit of duty cycle whilst maintaining the driver mode of the other of the first and second switching drivers and applying a variation in duty cycle to 25 maintain a magnitude of a differential component of the first and second driver signal.

In some examples, the maximum limit of duty cycle may be 95% or less. The minimum limit of duty cycle may be 5% or greater.

30 In some examples the difference between the switching voltages may be the same in each of the different driver modes.

In some examples, each of the first and second switching drivers may be operable in: a first mode in which the switching voltages are a first voltage V1 and a second voltage

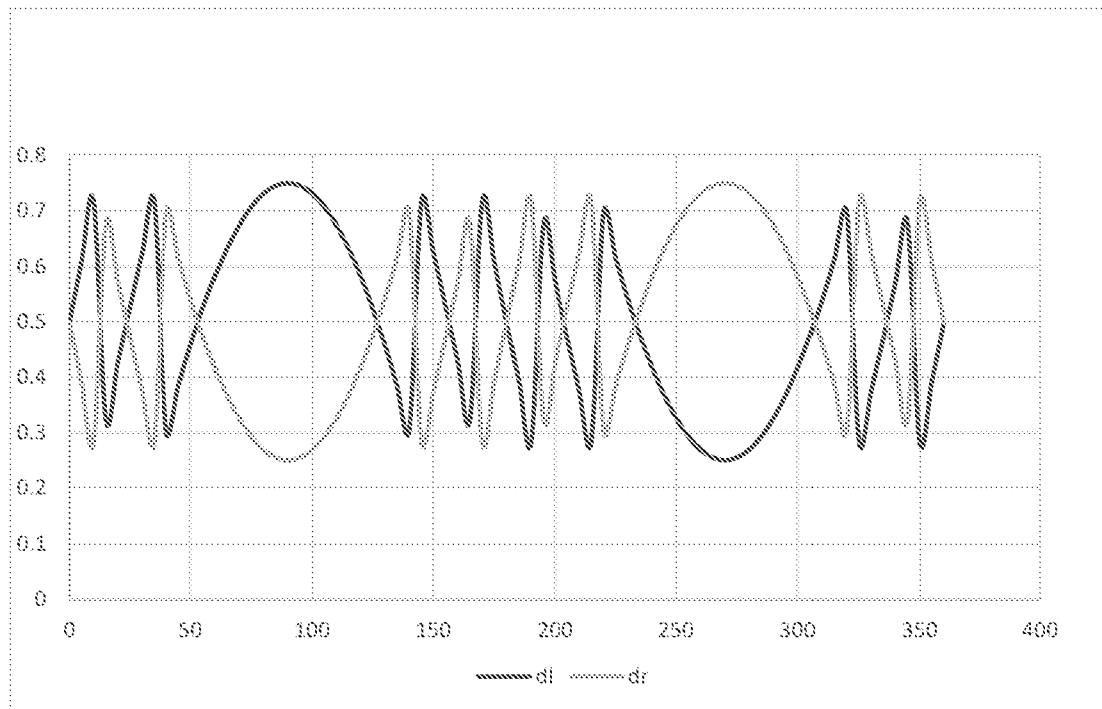

V2, where the first voltage is more positive than the second voltage; and at least one of: a second mode in which the switching voltages are the first voltage V1 and a voltage which is more positive than the first voltage V1; and a third mode in which the switching voltages are the second voltage V2 and a voltage which is more negative than the 5 second voltage V2. Each of the first and second switching drivers may have first and second supply nodes for receiving first and second supply voltages, and the first and second switching drivers may be configured such that the first voltage V1 and the second voltage V2 are equal to the supply voltages received at the respective first and second supply nodes. The controller may be configured to control the driver modes of the first 10 first and second switching drivers to provide a plurality of BTL modes. The BTL modes may comprise a low-signal mode in which both the first and second switching drivers operate in the first driver mode; an intermediate-signal mode in which one of the first and second switching drivers operate in the first driver mode and the other one of first and second switching drivers operates in either the second driver mode or the third driver mode; 15 and/or a high-signal level mode in which one of the first and second switching drivers operates in the second driver mode and the other one of first and second switching drivers operates in the third driver mode. The controller may be configured such that, in each of the BTL modes of operation, the controller controls the duty cycles of the first and second switching drivers so that a common-mode component of first and second 20 drive signals at the respective driver output nodes of the first and second switching drivers does not substantially vary with signal level. The controller may be configured such that the common-mode component of first and second drive signals when operating in the low-signal mode is substantially the same as the common-mode component of the first and second drive signals when operating in the high-signal mode, but different to 25 the common-mode component of first and second drive signals when operating in the intermediate-signal mode.

In some examples, the controller may be configured to control the duty cycles of the first and second switching drivers before and after a transition in mode such that a common- 30 mode component of the voltage across the transducer differs before and after the transition.

Each of the first and second switching drivers may comprise a variable boost stage selectively operable to provide voltage boosting to provide a voltage for use as a

switching voltage in at least one of the different driver modes. Each of the first and second switching drivers may comprise first and second supply nodes for receiving first and second supply voltages and the variable boost stage of each of the first and second switching drivers may comprise at least one capacitor and a network of switches for

5 connecting the first and second supply nodes with the capacitor and the respective output stage. The network of switches may be operable in one switch state in which the at least one capacitor is connected between the first and second supply nodes to be charged to the input voltage and in at least one switch state where the at least one capacitor is connected in series with one of the first and second supply nodes to provide

10 a boosted voltage as one of the switching voltages.

In some examples, the driver circuit may further comprise at least a first inductor connected to the driver output node of the first switching driver for connection in series with the transducer.

15 In a further aspect, there is provided a driver circuit for driving a transducer based on an input signal comprising: first and second switching drivers configured to drive the transducer in a bridge-tied-load configuration; wherein each of the first and second switching drivers comprise an output stage for controllably switching a driver output node

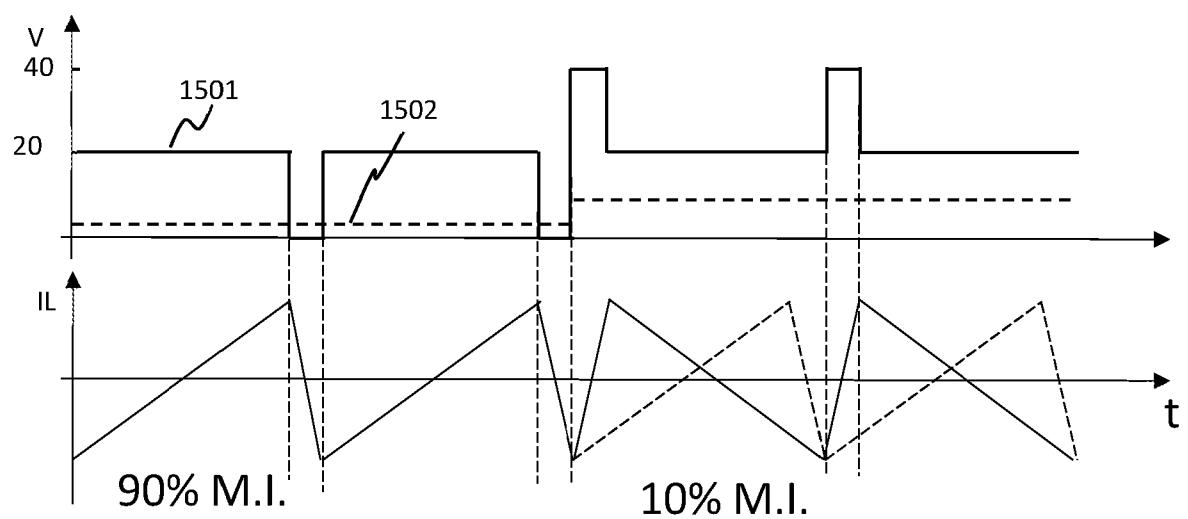

20 two switching voltages with a controlled duty cycle and wherein each of the first and second switching drivers is operable in a plurality of different driver modes where the switching voltages are different in the different driver modes. A controller may control the driver mode of operation and duty cycle of each of the first and second switching drivers based on the input signal, wherein the controller is configured to controllable vary

25 the duty cycle within a minimum duty cycle limit greater than 0% and a maximum duty cycle limit less than 100% and to transition between driver modes when one of the minimum or maximum duty cycle limits is reached. The controller may be configured such that during any mode transition, the driver mode of just one of the first and second switching drivers is changed.

30 In a further aspect, there is provided a driver circuit for driving a transducer based on an input comprising: first and second switching drivers for generating respective first and second drive signals at first and second output nodes for driving the transducer in a bridge tied load configuration, wherein each of the first and second switching drivers is

configured to controllably switch the respective first or second output node between two switching voltages with a controlled duty cycle; and wherein the first and second switching drivers are configured such that the two switching voltages are controllably variable to provide different BTL modes of operation. The driver circuit may be

5 configured so as to transition between modes by: controllably varying the switching voltages for one of the first and second switching drivers whilst switching the duty cycle of that driver from one of a maximum or minimum limit of duty cycle to the other or the maximum or minimum limit; whilst maintaining the switching voltages for the other of the first and second switching drivers and applying a corresponding change in duty cycle to

10 maintain a differential voltage.

In a further aspect there is provided a driver apparatus for driving a transducer comprising a first switching driver having a first driver output node for driving the transducer. The first switching driver comprises a first output bridge stage for selectively

15 switching the first driver output node between high and low switching voltages, a first modulator for controlling a duty cycle of switching of the first output bridge stage based on an input signal; and a first voltage controller for providing said switching voltages. The first switching driver is operable in a plurality of driver modes of operation in which the first voltage controller is operable to provide different switching voltages in each

20 driver mode. The apparatus also comprises a controller for controlling the driver mode of operation and the duty cycle of the first switching driver based on the input signal, wherein the controller is configured to transition between said driver modes of operation from a present mode to a new mode by: controlling the first voltage controller to provide the switching voltages for the new mode; and controlling the first modulator to vary the

25 duty cycle of the first output bridge stage, wherein the change in duty cycle is controlled such that there is no substantial discontinuity in switching ripple.

In some examples, the driver apparatus may also comprise a second switching driver having a second driver output node for driving the transducer in a bridge-tied load

30 configuration with the first switching driver. The second switching driver may comprise a second output bridge stage for selectively switching the second driver output node between respective high and low switching voltages and a second modulator for controlling a duty cycle of switching of the second output bridge stage based on the input signal. The controller may be configured, on a transition in mode of operation of the first

switching driver from the present mode to the new mode, to operate the second switching driver with no change to the switching voltages for the second output bridge stage and to control the second modulator to vary the duty cycle of the second output bridge stage such that a differential voltage across the transducer over the course of a switching cycle

5 is substantially the same before and after the transition. On such a transition of the first switching driver from the present mode to the new mode, the controller may be configured to control the first modulator to vary the duty cycle of the first output bridge stage by a first duty cycle amount and to vary the duty cycle of the second output bridge stage by a second duty cycle amount, wherein the magnitude of the first duty cycle

10 amount added to the magnitude of the second duty cycle amount corresponds to a duty cycle of 100%.

The controller may be configured to operate the first switching driver in a selected driver operating mode with a duty cycle for the first output bridge stage within predetermined

15 maximum and minimum limits of duty cycle. The controller may be configured to transition from the present mode to the new mode when the relevant duty cycle limit is reached. The controller may be configured to, when the relevant maximum or minimum duty cycle limit is reached for the present mode of operation, to transition to the new mode of operation and to control the first modulator to operate at the minimum or

20 maximum duty cycle limit respectively in the new mode of operation. In some examples the maximum duty cycle limit may be 75%. In some examples, the minimum duty cycle limit may be 25%.

In some implementations, the controller may be configured to control the first and second

25 switching drivers such that there is no substantially change in ramp direction in load current from the first driver output node at the point in time in which the first voltage controller varies the switching voltages to the switching voltages corresponding to the new mode.

30 Each of the first and second modulators may compare a modulator input, based on the input signal, with a carrier waveform to control the duty cycle of the respective output stage. The controller may be configured, on a change in operating mode of the first switching driver, to vary an amount of a mode correction applied to the modulator input by an amount related to the switching voltages of the new operating mode. In some

examples, on a transition of the first switching driver from the present mode to the new node, the controller may be configured to apply a phase shift to the carrier waveform. The phase shift applied to the carrier waveform may be based on the amount of change in duty cycle for the second switching driver. In some cases the carrier waveform may

- 5 be a triangle waveform that ramps from a minimum value to a maximum value and back to the minimum value over the course of a cycle period. In such a case, the controller may be configured such that the phase shift applied to the carrier waveform is a proportion of the cycle period that corresponds to half the change in duty cycle for the second switching driver.

10

In some implementations the second switching driver may comprise a second voltage controller for providing the switching voltages for the second output bridge stage and the second switching driver may also be operable in a plurality of driver modes of operation in which the second voltage provides different switching voltages in each driver mode.

- 15 The controller may also control the driver mode of operation of the second switching driver based on the input signal. The controller may be configured to transition between the driver modes of operation of the second switching driver from a present mode and a new mode by: controlling the second voltage controller to provide the switching voltages for the new mode; controlling the second modulator to vary the duty cycle of the second

- 20 output bridge stage; and operating the first switching driver with no change to the switching voltages for the first switching driver and controlling the first modulator to vary the duty cycle of the first output stage such that a differential voltage across the transducer over the course of a switching cycle is substantially the same before and after the transition.

25

In some implementations, the first switching driver may be configured to drive one side of the transducer in a single-ended configuration with an opposite side of the transducer connected to a DC voltage. In such a case, the controller may be configured, on a transition in driver mode of operation of the first switching driver from the present mode to the new mode, to controllably vary the value of the DC voltage such that a differential voltage across the load over the course of a switching cycle is substantially the same before and after the transition.

In some implementations the driver apparatus may further comprise at least a first inductor connected to the first driver output node for connection in series with the transducer.

5 In some examples the transducer may be at least one of: an audio output transducer; a haptic output transducer; a piezoelectric transducer; and a ceramic transducer.

Aspects also relate to an electronic device comprising the driver apparatus of any of the embodiments described herein.

10

In another aspect there is provided a driver apparatus comprising a first switching output stage for switching a first driver output node between a set of switching voltages with a controlled duty cycle wherein the driver apparatus is operable in at least first and second modes of operation. In the first mode of operation the set of switching voltages comprise

15 a first voltage and a second voltage, and in the second mode of operation the set of switching voltages comprise the second voltage and a third voltage. The driver apparatus further comprises a controller for controlling the mode of operation of the driver apparatus and the duty cycle of the first switching output stage based on an input signal.

The controller is configured to transition between the first and second mode of operations

20 from a present mode to a new mode by: controlling the driver apparatus in the present mode with a first duty cycle, controllably varying the set of switching voltages to the relevant voltages for the new mode of operation; and controllably varying the duty cycle of the first switching output stage, wherein the change in duty cycle is controlled such that there is substantially no discontinuity in switching ripple.

25

In a further aspects there is provided a driver apparatus for driving a transducer in a bridge-tied-load configuration between first and second driver output nodes with a differential drive signal based on an input signal. The driver apparatus comprises a first switching driver for switching the first driver output node between a first set of switching

30 voltages and a second switching driver for switching the second driver output node between a second set of switching voltages. At least the first switching driver is operable in different driver modes in which the first set of switching voltages is different in the different driver modes. A controller is configured to control a duty cycle of the first switching driver and a duty cycle of the second switching driver by comparing a carrier

signal with at least one modulator input signal that varies with the input signal. On a change of driver mode of the first switching driver, the controller is configured to adjust an offset applied to at least one modulator input signal and also apply a phase shift to the carrier waveform.

5

In a further aspect, there is provided a driver circuit for driving a transducer based on an input signal comprising: first and second supply nodes for receiving an input voltage; first and second switching drivers with respective driver output nodes for driving said transducer in a bridge-tied-load configuration, each of the first and second switching 10 drivers comprising a respective output stage for controllably switching the respective driver output node between high and low switching voltages with a controlled duty cycle to provide respective first and second drive signals. Each of the first and second switching drivers may be operable such that the high and low switching voltages can be controllably varied in at least three different driver modes. In a first driver mode the high 15 switching voltage is at a first voltage level V1 and the low switching voltage is at a second voltage level V2, and the first and second voltage levels differ by an amount equal to the input voltage. In a second driver mode the low switching voltage is at the first voltage level V1 and the high switching voltage is higher than the first voltage level V1 by an amount equal to the input voltage. In a third driver mode the high switching voltage is at 20 the second voltage level V2 and the low switching voltage is lower than the second voltage level V2 by an amount equal to the input voltage. A controller may control the driver mode and duty cycle of each of the first and second switching drivers based on the input signal, wherein the controller is operable in a plurality of BTL modes of operation comprising: a low-signal BTL mode to operate both the first and second switching drivers 25 in the first driver mode; an intermediate signal BTL mode to operate one of the first and second switching drivers in the first driver mode and the other of first and second switching drivers in one of the second or third driver mode; and a high-signal BTL mode to operate one of the first and second switching drivers in the second driver mode and the other of first and second switching drivers in the third driver mode.

30

Embodiments also relate to a driver circuit of any of the embodiments described herein comprising the transducer. The transducer may be at least one of an audio output transducer and a haptic output transducer. The transducer may be a piezoelectric or ceramic transducer.

Embodiments also relate to an electronic device comprising a driver circuit of any of the embodiments described herein.

- 5 It should be noted that, unless expressly indicated to the contrary herein or otherwise clearly incompatible, then any feature described herein may be implemented in combination with any one or more other described features.

For a better understanding of examples of the present disclosure, and to show more clearly how the examples may be carried into effect, reference will now be made, by way of example only, to the following drawings in which:

5 Figure 1 illustrates one example of a single-ended driving circuit for driving a load;

Figure 2 illustrates one example of a driver circuit for driving a load in a bridge-tied-load configuration;

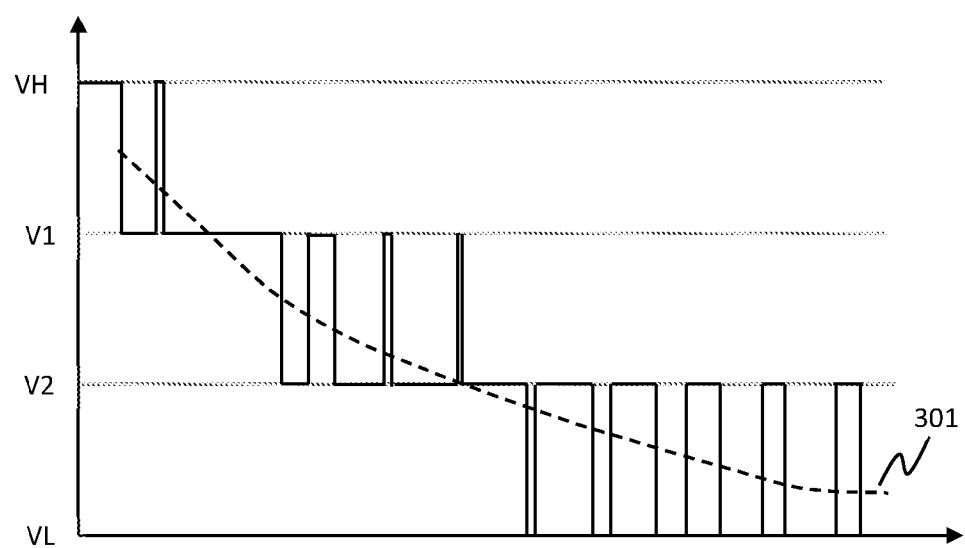

10 Figure 3 illustrates example output waveforms of a switching driver according to an embodiment;

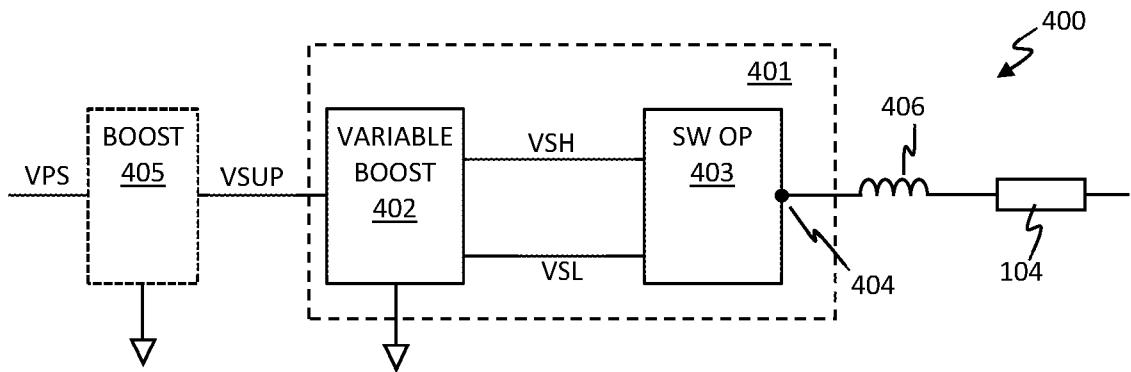

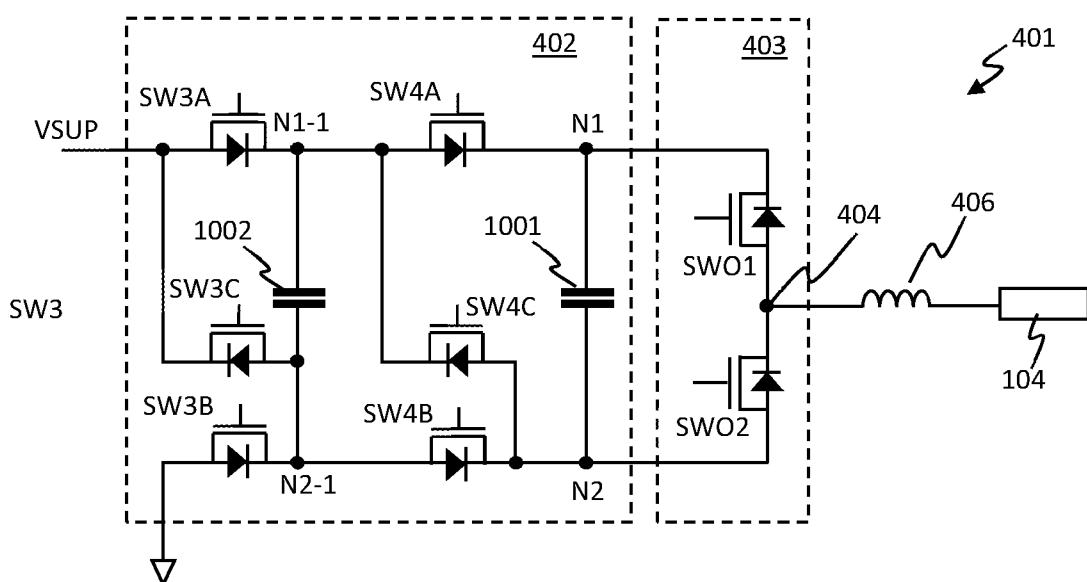

Figure 4 illustrates one example of a driver circuit according to an embodiment;

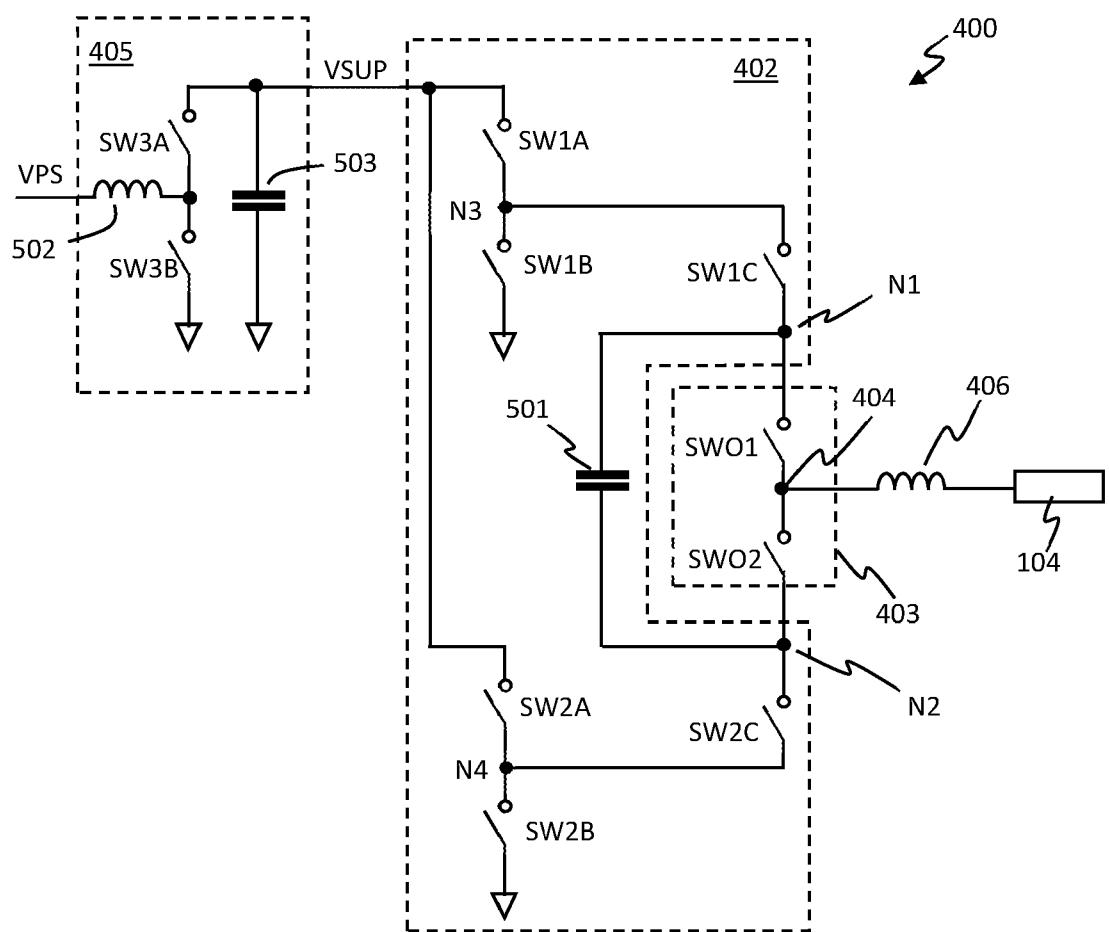

15 Figure 5 illustrates one example of the driver circuit of figure in more detail;

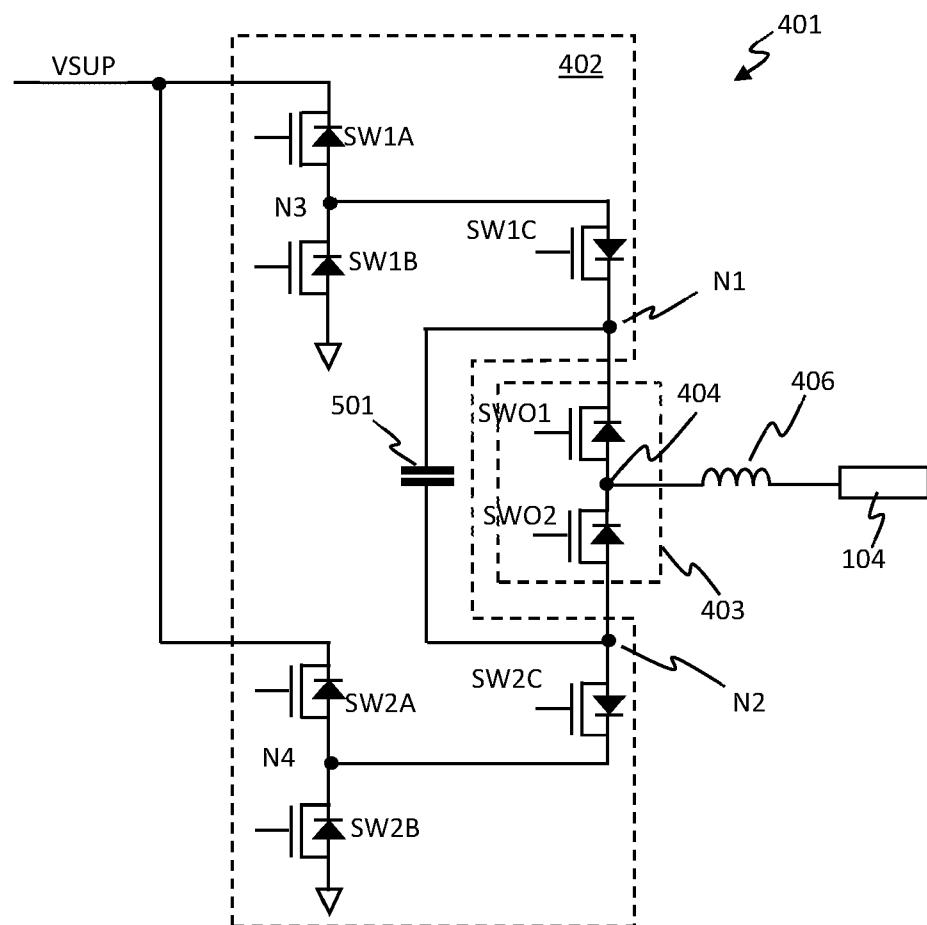

Figure 6 illustrates one example of a MOSFET implementation of a switching driver;

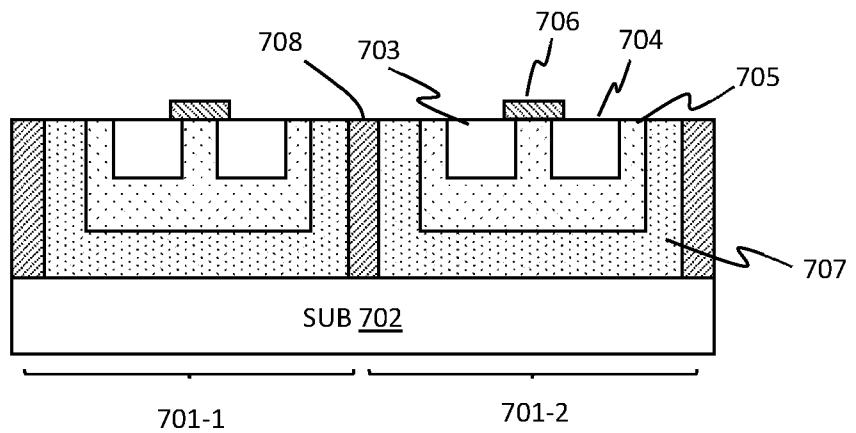

20 Figure 7 illustrates one example of NMOS devices suitable for use in the switching driver of figure 6;

Figure 8 illustrates one example of suitable operating voltages for different modes of operation;

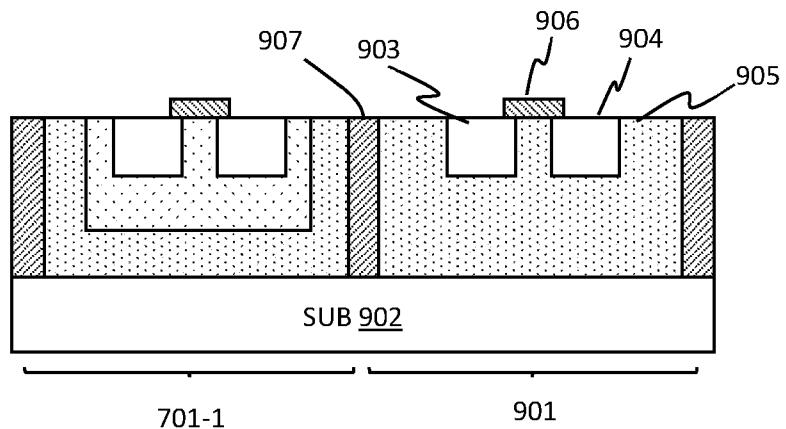

25 Figure 9 illustrates an example of one example of NMOS and PMOS devices suitable for use in the switching driver of figure 6;

Figure 10 illustrates another example of an implementation of a switching driver;

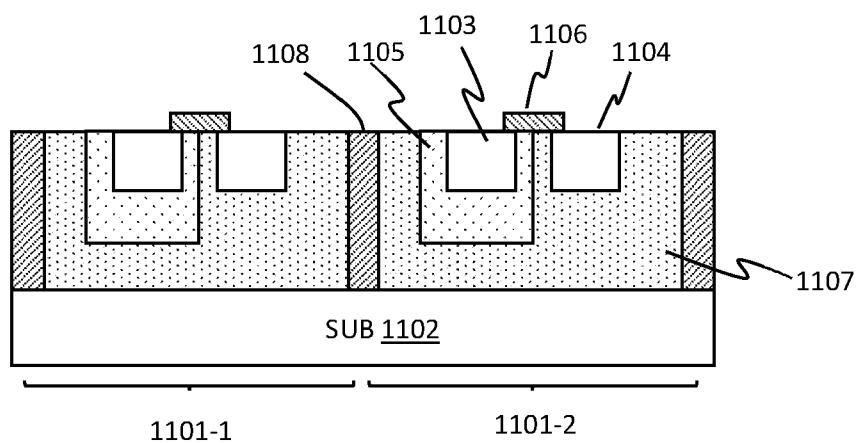

30 Figure 11 illustrates NMOS devices suitable for use in the switching driver of figure 10;

Figure 12 illustrates a driver circuit in a bridge-tied-load configuration;

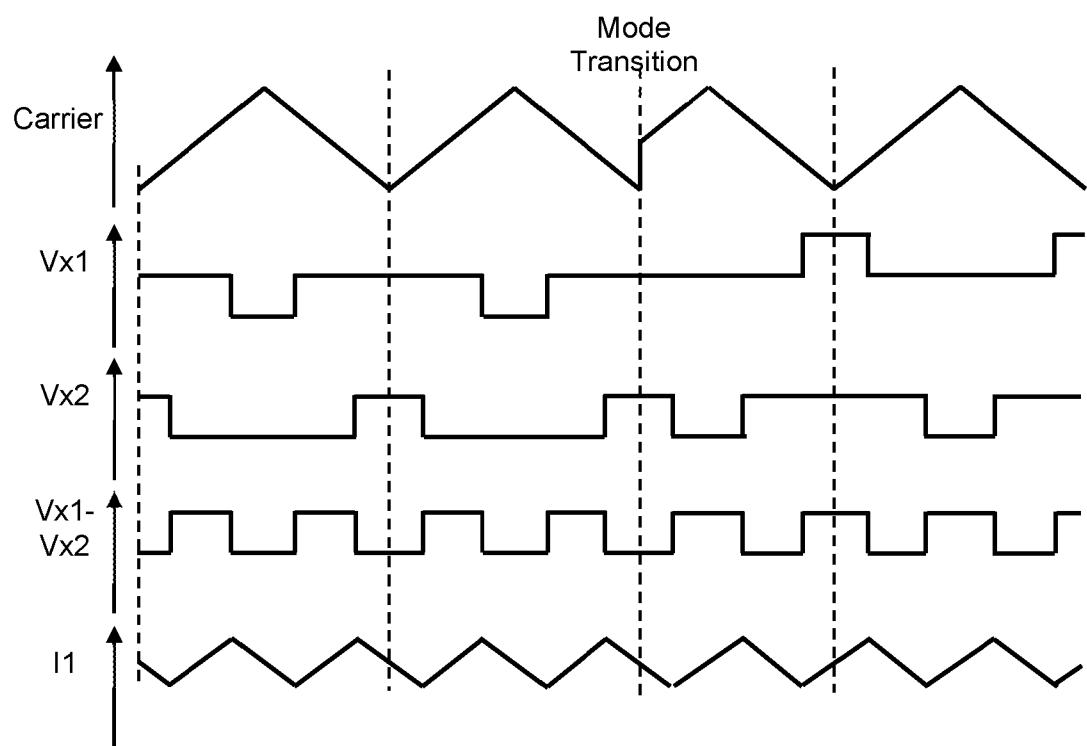

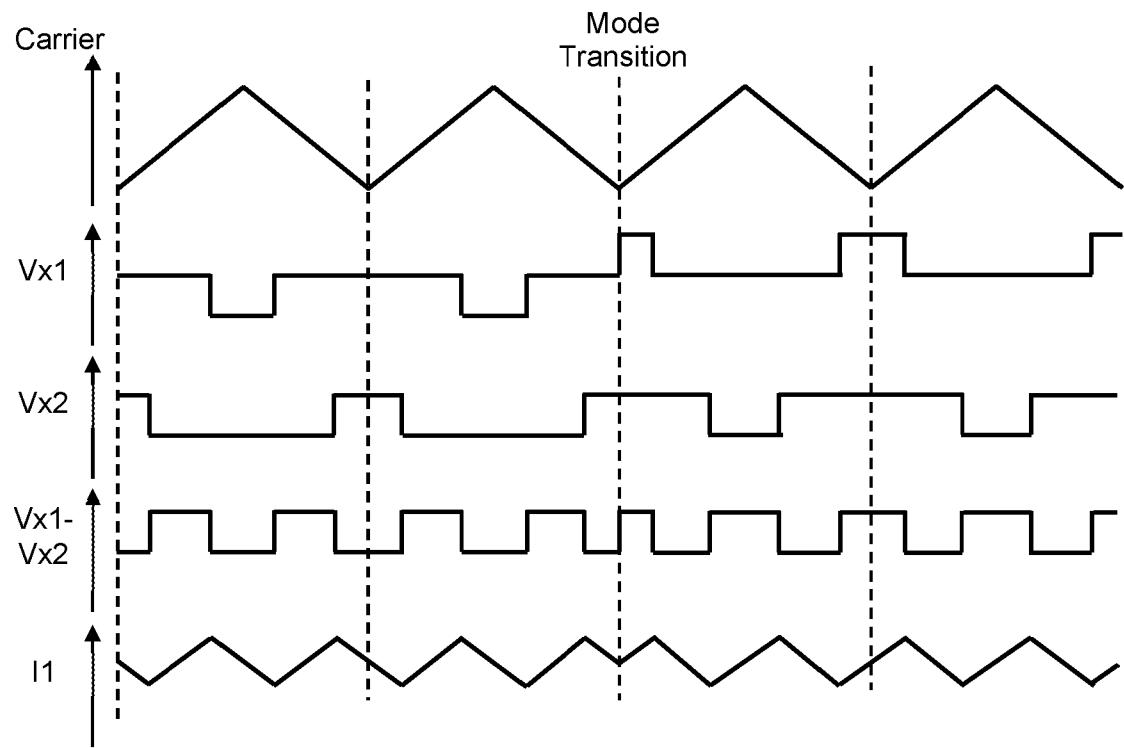

Figure 13 illustrates example waveforms for the drivers on each side of the load and the resultant differential voltage for a bridge-tied load configuration;

Figure 14 illustrates how the duty-cycles of the switching drivers on each side of the load

5 may vary for the differential waveform illustrated in figure 13;

Figure 15 illustrates example waveforms for a mode transition for a single-ended driver;

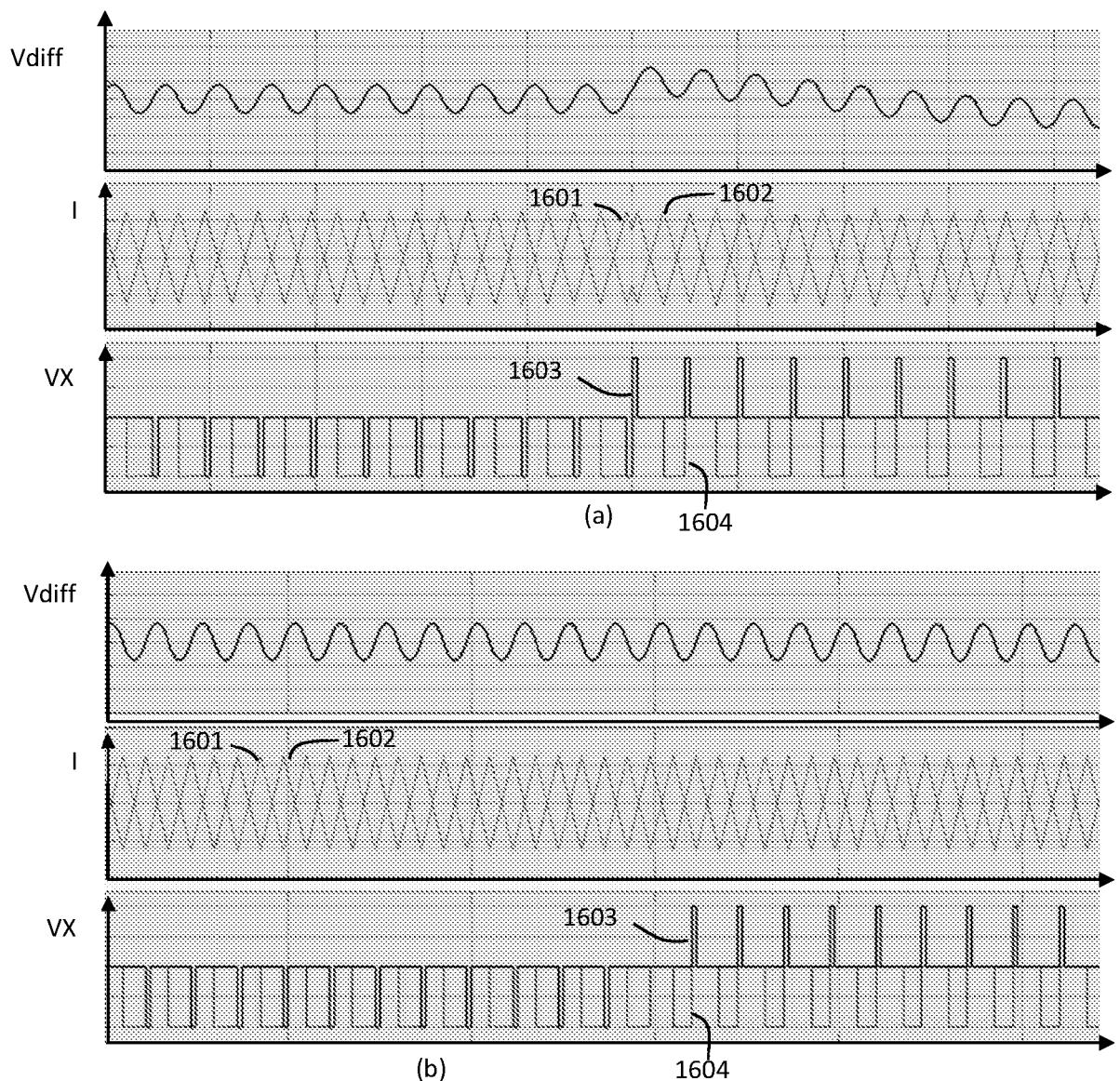

Figure 16 illustrates one example of waveforms for a driver circuit for driving a bridge-

10 tied-load;

Figure 17 illustrates examples waveforms across a mode transition; and

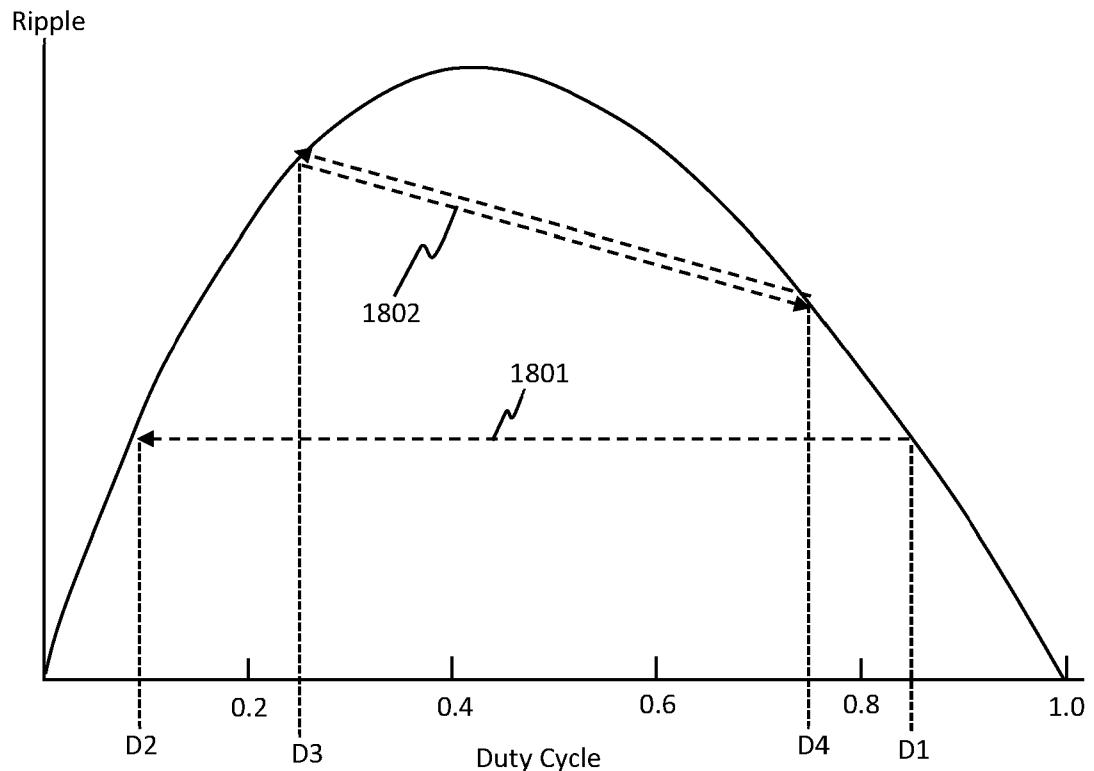

Figure 18 illustrates one example illustrates duty cycle of the switching drivers may be

15 controllably varied to manage discontinuities.

The description below sets forth example embodiments according to this disclosure.

20 Further example embodiments and implementations will be apparent to those having ordinary skill in the art. Further, those having ordinary skill in the art will recognize that various equivalent techniques may be applied in lieu of, or in conjunction with, the embodiments discussed below, and all such equivalents should be deemed as being encompassed by the present disclosure.

25

Embodiments of the disclosure relate to driver circuitry for driving a transducer and, in particular, to driver circuitry suitable for driving a reactive load such as a piezoelectric transducer, although embodiments may be implemented to drive other types of transducer. Embodiments of the disclosure also relate to methods of operation of driver

30 circuitry.

At least some embodiments of the present disclosure relate to switching drivers for generating a drive signal at a driver output node. The switching driver is operable in a plurality of different driver operating modes, wherein, in each of the different driver

operating modes, the output node is switched between two switching voltages, where the switching voltages are different in the different modes of operation. Thus, in a given driver mode of operation, the switching driver operates to switch the driver output node between the relevant switching voltages with a controlled duty cycle so as to provide the

- 5 drive signal with an average voltage (over the course of a cycle period) within a voltage range defined by the switching voltages. However, in a different driver mode of operation, the switching voltages are different so as to provide, in that driver mode, a different voltage range for the drive signal. The overall output voltage range for the switching driver may thus be defined by the different driver modes of operation, and each

- 10 individual driver mode of operation may provide only part of the overall output voltage range, that is, the voltage range between the two switching voltages in a given mode forms only a part or a subset of the overall output voltage range.

The switching driver thus switches between two defined switching voltages with a

- 15 controlled duty cycle to provide the drive signal at the driver output node with a desired average output voltage. In use, the average output voltage can vary within a defined voltage range between a peak high voltage VH and a peak low voltage VL. However, rather than switch a driver output node between these peak high and low voltage levels of the output range, as would be conventional for the drivers discussed with respect to

- 20 figures 1 and 2, the switching driver of embodiments of the disclosure switches between two switching voltages which form a subset, or only part, of the full output range between VH and VL. Thus, in each driver mode of operation, the output node is switched between two switching voltages that differ from one another by less than the full output range, but the full output range can be provided by varying the driver mode of operation, as

- 25 necessary.

In effect, the switching driver may be considered to operate with variable voltage rails, where the voltage rails are controllably varied to provide different operating ranges in the different operating modes, where each of the operating ranges is only part of the of full

- 30 output range of the driver.

Thus, a given peak-to-peak voltage variation for the driver signal can be achieved using switching voltages with a voltage difference which is lower than the peak-to-peak variation. Using switching voltages with a lower voltage difference can be beneficial in

terms of reduced switching losses and reduced radiated emissions, as well as reducing the requirement for a significant output inductance.

5 **Figure 3** illustrates this principle. Figure 3 illustrates the switching waveforms at an output node of a switching driver according to one example and the resulting average voltage 301 over a duty cycle, i.e. the desired voltage of the drive signal output from the switching driver. It should be noted that figure 3 illustrates the switching waveforms for the driver signal generated at one driver output node, i.e. as would be applied to just one side of the load.

10

In this example, the drive signal may vary within a full output range between a peak low voltage VL and a peak high voltage VH. In this example, however, the switching driver is operable in different driver modes. In one mode of operation an output node of the switching driver may be switched between the peak high voltage VH and a first intermediate voltage V1. In another mode of operation, the output node may be switched between the first intermediate voltage V1 and a second intermediate voltage V2. In a further mode of operation, the output node may be switched between the second intermediate voltage V2 and the peak low voltage VL.

20

To generate a drive signal with a voltage in the range between the peak high voltage VH and the intermediate voltage V1, the output stage may operate in the mode that switches between VH and V1. For a drive voltage which is between the first intermediate voltage V1 and the second intermediate voltage, the output node may be switched between V1 and V2, and if the desired voltage for the drive signal is between V2 and the peak low voltage VL, the switching driver may operate in the mode to switch the voltage at the output node between V2 and the peak low voltage VL. In each case, the duty cycle is controlled appropriately to provide the desired average voltage.

30

Figure 3 illustrates that the full driver output range between VL and VH is provided by three different driver operating modes. However, in other embodiments, there may be a different number of driver operating modes across a full output range of the switching output stage, for instance in some embodiments there may be just two driver operating modes or there may be more than three driver operating modes. The voltage ranges for the driver operating modes, defined by the switching voltages, may be defined so that

the respective voltage ranges of the driver operating modes are contiguous and non-overlapping and collectively cover the whole of the full output range of the switching driver. In other embodiments however it may be advantageous to have some overlap between the output voltage ranges in the different driver operating modes. In some 5 embodiments the magnitude of the voltage range of each of the driver operating modes, i.e. the voltage difference between the relevant two switching voltages: VL and V2, V2 and V1, or V1 and VH; may be the same as one another.

It will be understood that the reference to a voltage range, for the switching driver in a 10 given operating mode, refers to the voltage of the drive signal at the driver output node (in terms of the average voltage over the course of a switching cycle) in that driver operating mode. The actual voltage that is applied across the load will, of course, depend on the voltage on the other side of the load, e.g. a defined DC voltage for a single-ended configuration or the voltage of a second drive signal on the other side of the load 15 generated by another driver for a BTL configuration. The output signal range, for the output signal applied across the load, may therefore be different to the driver voltage range. For instance with reference to figure 3, if a defined DC voltage Vdc on the other side of the load was set to be a midpoint voltage between V1 and V2, then the switched driver may operate in the mode with switching voltages V1 and V2 for low output signal 20 levels, up to a magnitude of  $(V1-V2)/2$  and may swap to switching voltages V1 and VH for higher positive output signal values (up to VH-Vdc) and swap to switching voltages VL and V2 for greater negative output signal values (down to VL-Vdc).

As used herein the term driver operating mode will thus refer to the operation of a driver 25 on one side of the load only, and the reference to a driver output voltage or output voltage range, or just voltage range, will refer to the voltage of a drive signal at the driver output node. For at least some BTL configurations, each side of the load may be seen as being driven by a respective driver, i.e. there are first and second drivers for driving both sides of the load. In some implementations, as will be discussed in more detail below, both of 30 the drivers of a BTL implementation may be separately operable in different modes, in which case an overall BTL operating mode may be defined by the individual operating modes of the individual drivers.

The switching driver may be configured to receive a high-side supply voltage and a low-side supply voltage, for instance a positive supply voltage and ground, which define an input voltage with a magnitude which is significantly lower than the full peak-to-peak output voltage range of the switching driver. Operating in the different driver operating

5 modes also means that the voltage difference between the switching voltages is significantly less than the full output range of the switching driver, even when operating to provide a drive signal voltage near the peak high output voltage  $VH$ . In this way, the maximum voltage stress across components of the switching driver can be kept to a magnitude which is lower than, and in some implementations significantly lower than,

10 the peak-to-peak output voltage range of the switching driver. This can advantageously allow the use of components, e.g. transistors such as. FETs, with a voltage tolerance which may be significantly lower than the peak-to-peak output voltage of the driver circuit.

The switching driver may comprise a variable boost, or level-shifting circuit, such a

15 charge pump, for providing some of the appropriate switching voltages for operation in the selected driver mode. The variable boost circuit may selectively positively boost (i.e. increase) the high-side input voltage and/or negatively boost (i.e. lower) the low-side input voltage to controllably vary at least one of the switching voltages for a mode of operation.

20 **Figure 4** illustrates one example of driving circuitry 400 with a variable boosting switching driver 401. In the example of figure 4 the switching driver 401 comprises a variable boost stage 402 and a switching output bridge stage 403. The variable boost stage 402 is configured to receive a high-side supply voltage  $VSUP$  and a low-side input supply

25 voltage, which in this example is ground, which together define an input voltage  $Vin$ , i.e. as the voltage difference between the high- and low-side supplies. The switching output bridge stage 403 receives high-side and low-side-switching voltages  $VSH$  and  $VSL$  from the variable boost stage and switches a driver output node 404 between these two switching voltages with a controlled duty cycle to provide a desired average output

30 voltage. In the example of figure 4 the high-side supply voltage  $VSUP$  for the switching driver 401 is derived from a power supply voltage  $VPS$ , which may, for instance be a battery voltage. In some implementations the power supply voltage  $VPS$ , may be regulated and/or level shifted to provide an appropriate supply voltage  $VSUP$  for the

switching driver, for instance there may be an initial boost stage 405 operable to provide a defined boost to the received power supply voltage VPS.

The variable boost stage is operable to controllably vary the switching voltages VSH and

5 VSL supplied to the output bridge stage 403 so as to provide the different driver modes of operation. In one example, in one mode of operation, the supply voltages to the switching driver 401, i.e. the voltages VSUP and ground (0V), may be used as the switching voltages VSH and VSL. In this mode of operation the supply voltages received by the switching driver 401 are thus used as the switching voltages and such a mode of

10 operation may be seen as an unboosted driver mode of operation as no voltage boosting is applied by the switching driver. It will be understood however, as described above, that at least one of the supply voltages received by the switching driver may itself have been boosted by an upstream component.

15 In one example, in another driver mode of operation, the supply voltage VSUP may be used as the low-side switching voltage VSL, with the variable boost stage being operable to generate a positively boosted higher voltage as the high-side switching voltage VSH. In one example, in another driver mode of operation, the low-side supply voltage, i.e. ground in this example, may be used as the high-side switching voltage VSH, with the

20 variable boost stage being operable to generate a negatively boosted lower voltage as the low-side switching voltage VSL.

In some applications the load 104 could be a reactive load, such as a piezoelectric transducer. Figure 4 also illustrates that there may be a series inductance 406 in the

25 load path, e.g. the load 104 may be connected in series with an inductor 406. Especially for piezoelectric transducers, the capacitive nature of such transducers means that it may generally be beneficial to include an inductor in series with the transducer. The inductor 406 may help suppress the switching ripple at the switching frequency, whilst allowing the current to flow for the signal band of interest, e.g. at audio or ultrasonic

30 frequencies.

**Figure 5** illustrates one example of the driver circuitry of figure 4 in more detail and similar components are identified by the same references.

Figure 5 illustrates that the output bridge stage 403 comprises two switching paths for selectively connecting the driver output node 404 to a first node N1 or a second node N2. Each switching path comprises a respective output switch SWO1 and SWO2. The variable boost stage 402 is configured to selectively control the voltages at the first and 5 second nodes N1 and N2 to enable the various modes of operation, and thus the first and second nodes N1 and N2 may be referred to as first and second switching voltage nodes.

The variable boost stage 402 comprises, in use, a capacitor 501 and network of switches 10 which are operable in a plurality of different switch states so as to provide different voltages at the switching voltage nodes N1 and N2. The network of switching paths is arranged such that the capacitor 501 can be charged to a desired voltage, which in this case is the input voltage. The switch network is also arranged so that the charged capacitor 501 can selectively provide voltage boosting to one of the first and second 15 switching voltages nodes in one of the driver modes of operation.

In the example of figure 5, the capacitor 501 is connected between the first and second variable boost nodes N1 and N2 and thus in parallel with the output bridge stage 403. This arrangement means that the voltage difference between the switching voltages 20 corresponds to the voltage on the capacitor 501.

In the example of figure 5, the network of switches is arranged to provide a first set of switching paths SW1A, SW1B and SW1C and a second set of switching paths SW2A, SW2B and SW2C. Switching paths SW1A and SW1B are provided to selectively 25 connect a node N3 to the high-side input voltage or the low-side input voltage respectively, i.e. VBST and ground in this example. The node N3 can thus be seen as a variable supply node or a supply select node. Switching path SW1C selectively connects the node N3 to the first variable boost node N1. Likewise, switching paths SW2A and SW2B selectively connect a node N4 to the high-side input voltage or the 30 low-side input voltage respectively and switching path SW1C selectively connects the node N4, which can be seen as a second variable supply, or supply select, node, to the second variable boost node N2. This arrangement means that a first electrode of the capacitor 501 can be selectively connected to either of the first or second input supplies.

Likewise a second electrode of the capacitor 501 can be selectively connected to either of the first or second input supplies.

It will be understood that the switching driver 401 may be implemented as an integrated circuit (IC), but in some embodiments the capacitor 501 may not be an integrated component and may be a separate component which is connected to the IC in use, i.e. the capacitor 501 may be off-chip. The capacitor 501 may therefore be connected between first and second capacitor nodes (not separately identified), which may be connected to suitable contacts of an IC for connection to an external capacitor.

10

In use, the driver circuit may be selectively operable in three different driver modes of operation, where the voltages at the switching voltage nodes N1 and N2, and hence the switching voltages for the output stage 403 vary in each mode.

15 In a first mode of operation the switching voltages may be +VSUP and ground. In a second mode of operation the switching voltages may be +2VSUP and +VSUP. In a third mode of operation the switching voltages may be ground and -VSUP. By swapping between the three modes of operation the switching driver circuit 400 can provide a peak-to-peak voltage range of 3VSUP in magnitude, from -VSUP to +2VSUP.

20

To provide the first mode of operation the switch network of the variable boost stage may be operable in a first switch state, in which switching paths SW1A and SW1C may be closed (with switching path SW1B open) to connect the high-side supply voltage VSUP to the first switching voltage node N1, and the switching paths SW2B and SW2C may be 25 closed (with switching path SW2A open) to connect the second switching voltage node N2 to the low-side supply voltage, i.e. ground in this example. This results in the switching voltage nodes N1 and N2 being connected to the respective high-side and low-side supply voltages. Whilst in this first state, the output bridge stage 403 can be controlled so that switching paths SWO1 and SWO2 alternately connect the driver output 30 node 404 to first and second switching voltage nodes with a duty cycle controlled to provide the desired average output voltage in the range 0V to +VSUP.

In this first state of the first mode of operation, the capacitor 501 is also connected between the high-side and low-side supply voltages and thus is charged to the input voltage  $V_{in}$  for the variable boost stage, i.e. to  $+VSUP$  in this example.

5 As, in this first state of the first mode, the switching voltage nodes N1 and N2 are connected to the respective high-side and low-side supplies, the load current can be supplied from the input supply to the variable boost stage.

In some implementations the switch network of the variable boost stage 402 may

10 additionally be selectively operable in an alternative switch state to provide the same switching voltages as the first mode. Switching paths SW2B and SW1C may be closed (with switching path SW2A open) to connect the second switching voltage node N2 to ground, as in the first state, but in this alternative switch state the switching path SW1C may be open. In this case the switching voltage node N1 is isolated from the supply

15 voltages (other than the path via the capacitor 501), but the voltage on (previously charged) capacitor 501 will maintain the voltage at the first switching voltage node N1 substantially equal to  $VSUP$ . In this alternative switch state, any load current can be supplied from the capacitor 501 (when the output path SWO1 is closed).

20 It will be noted that, in this first mode of operation the maximum voltage difference across any of switching paths, and thus any of the switches of the switch network, is substantially equal to the magnitude of the input voltage  $V_{in}$ , i.e. the voltage difference between the high-side and low-side supply voltages. The voltages at the switching voltage nodes N1 and N2 are  $+VSUP$  and ground respectively, whilst the voltages at node N3 and N4 are

25  $VSUP$  and ground respectively (at least in the first state – in the alternative state the voltage at node N3 may be floating or this node could be selectively connected to  $VSUP$  or ground by switching paths SW1a or SW1B respectively).

To provide the second mode of operation, switching path SW2A is closed (with switching

30 path SW2B open) to connect node N4 to the high-side supply voltage  $VSUP$  and switching path SW2C is closed to connect node N4 to the second switching voltage node N2. In this state, the second switching voltage node N2 is thus substantially equal to the high-side supply voltage  $+VSUP$ . Switching path SW1C is open, and the voltage of the capacitor 501, which is charged to the input voltage  $V_{in}$ , in this case equal to  $+VSUP$ ,

positively boosts the voltage at the first switching voltage node N1 to +2VSUP. This driver mode can thus be seen as a positive boosted mode of operation.

In this second switch state the voltage at the first switching voltage node N1 is boosted

5 to +2VSUP (i.e. boosted above the high-side supply voltage VSUP by the voltage Vin on the capacitor 501), and thus this node is disconnected from the supply voltages. It will be noted that if switch SW1C were not present, this disconnection could be achieved by opening both switching paths SW1A and SW1B. However, in that case the voltage at node N3 would be the same as that at the first switching voltage node N1, i.e. equal to

10 +2VSUP and thus the voltage across switch SW1B would be equal to +2VSUP, i.e. this switch would be subjected to a voltage stress of twice the input voltage. The inclusion of switching path SW1C reduces the voltage stress. Switching path SW1C is open, to disconnect the first switching voltage node N1 from the supply select node but the switching path SW1A may be closed (with switching path SW1B open) to connect node

15 N3 to the high-side supply voltage VSUP. This limits the voltage difference across the switch of the open switching path SW1C to a voltage of magnitude equal to the input voltage Vin (which in this case equals VSUP). Thus, the maximum voltage difference across any of the switching paths is again substantially equal to the magnitude of the input voltage.

20

Whilst the variable boost stage is in this second switch state, the output bridge stage 403 can be controlled so that the output switches of the switching paths SWO1 and SWO2 alternately connect the driver output node 404 to first and second switching voltage nodes with a duty cycle controlled to provide the desired average output voltage within

25 the range +VSUP to +2VSUP.

When operating in this second driver mode, the load current will be drawn from the capacitor 501. However, if the capacitance of the capacitor 501 is relatively large and the load for the output stage is a reactive load, the capacitor 501 can provide the charge

30 needed with just one charge pumping cycle. In particular, when the output bridge stage 403 drives an inductor 406 in the output path, this can enable lossless movement of charge between the load and the capacitor 501 for charge recovery.

It will be understood that for driving a transducer with a drive signal based on an input signal, such as an audio signal, the required drive voltage of the switched driver will vary with the input signal. High output voltages, such as enabled in the second driver mode of operation may only be required for relatively large amplitude drive signals and for only

- 5 part of the input signal cycle, when the input signal is near its peak. Thus, in normal operation, the second driver mode may be expected to be used for only parts of the signal cycle of the input signal, and for the switching driver circuit to be operating in the second driver mode of operation, e.g. in the range  $+VSUP$  to  $+2VSUP$ , the drive signal output from the switching driver will have passed through the voltage range of the first

- 10 mode, e.g.  $0V$  to  $+VSUP$ . Thus prior to operating in the second driver mode there will have been a period of operation in the first driver mode and thus the capacitor 501 will have been charged during such operation in the first driver mode.

The size of the capacitor 501 may thus be selected, based on the reactive load to be driven, such that a single charge of the capacitor provides sufficient charge for the driving of the reactive load over the course of a signal cycle for the input signal.

It will be noted that in the second switch state the second switching voltage node is connected to a voltage other than the second supply voltage (e.g. ground) and, in the example of figure 5, this is the first supply voltage  $VSUP$ . However, in some embodiments a different defined voltage, say  $0.5VSUP$  for example, could be derived and supplied to the second switching voltage node in this second stage, in which case the capacitor would boost the voltage at the first switching voltage node to  $1.5VSUP$ .

- 25 To provide the third mode of operation, the switch network of the variable boost stage may be operable in a third switch state, in which switching paths SW1B and SW1C are closed (with switching path SW1A open) to connect the first switching voltage node to the low-side supply voltage, i.e. ground. The first switching voltage node N1 is thus substantially equal to the low-side supply voltage, i.e. ground in this example. Switching path SW2C is open and the voltage of the capacitor 502, which is charged to the input voltage, i.e.  $VSUP$  in this case, negatively boosts, or lowers, the voltage at the second switching voltage node N2 to  $-VSUP$ . To control the voltage stress across the switch path SW2C, the switching path SW2B may be closed to cause the voltage at node N4 to be equal to ground.

- 30

Whilst the switch network of the variable boost stage is in this third switch state, the output bridge stage 403 can be controlled so that the output switches SWO1 and SWO2 alternately connect the driver output node 404 to first and second switching voltage nodes with a duty cycle controlled to provide the desired average output voltage within the range -VSUP to 0V.

It will thus be understood that the variable boost stage 402 is operable to controllably vary the voltages at the switching voltage nodes N1 and N2 to provide different switching voltages for the output stage 403 in the different driver modes of operation. One of switching voltages in the second and third modes of operation is selectively boosted by the voltage of the capacitor 501, which is charged during operation in the first mode by the input voltage, i.e. the voltage between the high-side supply voltage and the low-side supply voltage, VSUP and ground in this example. Each of the operating modes therefore involves switching voltages that differ from one another by a magnitude equal to the input voltage Vin for the variable boost stage, i.e. the difference between the high-side and low-side supply voltages. In the embodiment of figure 5 the capacitor is charged to the input voltage and as the capacitor is connected in parallel with the output stage 501, the switching voltages in a given mode of operation differ by an amount equal to the input voltage. In the embodiment of figure 5 one capacitor may be used to selectively provide both positive boosting or negative boosting as required.

It will also be clear that the maximum voltage stress across any of the individual switching paths can be limited to be substantially equal to the input voltage. Typically, each switching path may be implemented with a transistor, e.g. a MOSFET, as a switch and this means that a drain-source voltage tolerance of the transistor need only be sufficient to withstand a voltage of magnitude equal to the input voltage supply to the variable boost stage. Note that for correct operation of the transistor it may be beneficial to implement at least some of the transistor in doped wells which are driven with voltages based on the switching voltages, as will be discussed in more detail below.

The input voltage for the switching driver 401 may thus define the voltage tolerance required for the switches of the switch network of the variable boost stage and also define

the voltage range of the different operating modes, and hence the overall voltage range of the switching driver.

As noted above, in some examples, to provide an appropriate input voltage for the

5 variable boost stage 402, the driver circuitry 400 may comprise a first boost stage 405 for receiving a power supply voltage VPS and boosting the power supply voltage to provide at least one of the voltage supplies for the switching driver 401. In this example the first boost stage receives the power supply voltage VPS and boosts the power supply voltage VPS to provide the supply voltage VSUP. The first boost stage, if present, could

10 be any suitable DC-DC converter with a voltage boost and figure 5 illustrates that the first boost stage may comprise a boost converter with an inductor 502, control switches SW3A and SW3B and a reservoir capacitor 503 coupled to maintain the output voltage VBST.

15 In some examples the power supply voltage VPS could be a battery voltage and thus could be of the order of a few volts, say a voltage at or around 4.2V. In some examples this supply voltage could be boosted to a supply voltage VSUP of say 20V or so to provide the high-side supply to the switching driver 401. The low-side voltage may, in some examples, be ground, so the input voltage for the switching driver may be 20V.

20 For the example illustrated in the figure 5, the switching driver may thus be operable to generate a drive signal with a voltage range of 60V, from a voltage of -20V to a voltage of +40V, by selectively operating in one of the three different operating modes, a -20V to 0V mode, a 0V to +20V mode and a +20V to 40V mode.

25 The use of a first voltage defined boost stage to generate a first boosted voltage at a predetermined level which may then be selectively boosted by a variable boost stage represents one particular aspect of the present disclosure. In general, therefore, at least some embodiments relate to driver circuitry comprising a switching output stage 403 for driving an output node 404 between two switching voltages with a controlled duty cycle,

30 where the two switching voltages are selectively variable. A variable boost stage 402 may have first and second input nodes configured to receive a first high-side voltage and a first low-side voltage respectively and provide the switching voltages at first and second variable boost nodes. The variable boosting stage may be operably to selectively boost at least one of the first high-side voltage and the first low-side voltage to controllably vary

the switching voltages in different modes of operation. The driver includes a first defined boost stage 405 for a first defined boost stage configured to receive a supply voltage and boost the supply voltage to a defined voltage level to provide one of said first high-side voltage and first low-side voltage. The variable boost stage may be a switched capacitor

5 variable boost stage, e.g. charge pump, which can allow for charge recovery from the load.

As described above, each of the switches of the network of switches of the variable boost stage 402 and also the output switches of the output bridge stage 403 may be

10 implemented by a suitable transistor, e.g. a suitable MOSFET. **Figure 6** illustrates an example of a switch driver such as described with respect to figure 5, wherein each of the switches of the switching paths is implemented by a FET.

In one implementation, each of the FETs illustrated in figure 6 may be an NMOS FET

15 device. At least part of the NMOS devices may be formed in deep N-wells as will be understood by one skilled in the art. **Figure 7** illustrates schematically an example of two NMOS devices 701-1 and 701-2 formed on a substrate 702. Each of the NMOS devices comprises source and drain regions 703 and 704 formed in a bulk region 705, with a gate electrode 706 for controlling channel conduction. The bulk region is 705 is

20 disposed within a deep N-well 707. Isolation regions 708 isolate the N-wells from neighbouring devices.

In use, the substrate 702 and isolation regions 708 will typically be held at ground and the bulk 705 is typically coupled so as to be driven to the same voltage as the source

25 703. The deep N-wells 707 may be driven with a voltage that varies according to the signal range on the output to avoid P-well to deep N-well breakdown or unwanted forward biasing of the deep N-well to the substrate or P-well. By driving the voltages in this way, the transistor devices may be protected from high voltages.

30 **Figure 8** illustrates a table showing one example how the N-wells of the NMOS switches of the switching driver 401 of figure 6 may be driven when operating in the different modes. The table illustrated in figure 8 lists the switches of the switching driver for each of the operating modes, and in each case, the state of each of the switches, i.e. on, off or being operated with a controlled duty cycle (represented by DC), is indicated, along

with the respective source/bulk and drain voltages and the voltage to which the respective N-well may be driven.

In another implementation, the FETs illustrated in figure 6 may be a mixture of NMOS and PMOS devices. For example, the switches of switching paths SW1A, SW1C, SW01 and SW2A may be implemented as PMOS devices, whilst the switches of switching paths SW1B, SW02, SW2B and SW2C may be implemented as NMOS devices. As discussed, above the NMOS devices may be formed in deep N-wells. **Figure 9** illustrates schematically an example of an NMOS device 701 and a PMOS device 901 formed on a substrate 902. The NMOS device 701 may have the same structure as the NMOS device discussed with reference to figure 7. The PMOS device also comprises a source region 903 and drain region 904 in a bulk region 905, with a gate 906, but for the PMOS device, as the bulk region is N-type there is no need for any N well.

15 In use, the switching driver 401 could be operated in the same three modes as described above, and in operation the N-wells of the NMOS devices could be driven in the same way as illustrated in figure 8, with the bulk of the PMOS devices connected to be at the same voltage as the source.