(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6203601号

(P6203601)

(45) 発行日 平成29年9月27日(2017.9.27)

(24) 登録日 平成29年9月8日(2017.9.8)

(51) Int.Cl.

F 1

|             |           |      |       |      |

|-------------|-----------|------|-------|------|

| HO1L 29/786 | (2006.01) | HO1L | 29/78 | 617K |

| HO1L 21/336 | (2006.01) | HO1L | 29/78 | 617A |

| HO1L 21/28  | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 29/49  | (2006.01) | HO1L | 29/78 | 617N |

| HO1L 29/423 | (2006.01) | HO1L | 29/78 | 618E |

請求項の数 10 (全 46 頁) 最終頁に続く

(21) 出願番号

特願2013-219843 (P2013-219843)

(22) 出願日

平成25年10月23日(2013.10.23)

(65) 公開番号

特開2014-103388 (P2014-103388A)

(43) 公開日

平成26年6月5日(2014.6.5)

審査請求日

平成28年10月18日(2016.10.18)

(31) 優先権主張番号

特願2012-234359 (P2012-234359)

(32) 優先日

平成24年10月24日(2012.10.24)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に形成された酸化物半導体層と、

前記酸化物半導体層に接するソース電極層およびドレイン電極層と、

前記酸化物半導体層、前記ソース電極層および前記ドレイン電極層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された、第1のゲート電極層、第2のゲート電極層および第3のゲート電極層と、を有し、

前記第1のゲート電極層乃至前記第3のゲート電極層は、それぞれ離間しており、

前記第1のゲート電極層は、前記酸化物半導体層と重畳し、

前記第2のゲート電極層は、前記酸化物半導体層のチャネル幅方向の一方の端部の一部を覆い、

前記第3のゲート電極層は、前記酸化物半導体層のチャネル幅方向の他方の端部の一部を覆うことを特徴とする半導体装置。

## 【請求項2】

請求項1において、

前記ソース電極層は、

前記酸化物半導体層に接する第1のソース電極層と、

前記第1のソース電極層を覆うように形成され、前記酸化物半導体層に接する第2のソース電極層からなり、

10

20

前記ドレイン電極層は、

前記酸化物半導体層に接する第1のドレイン電極層と、

前記第1のドレイン電極層を覆うように形成され、前記酸化物半導体層に接する第2のドレイン電極層からなることを特徴とする半導体装置。

【請求項3】

請求項1において、

前記ソース電極層は、

前記酸化物半導体層に接する第2のソース電極層と、

前記第2のソース電極層を覆うように形成され、前記酸化物半導体層に接する第1のソース電極層からなり、

10

前記ドレイン電極層は、

前記酸化物半導体層に接する第2のドレイン電極層と、

前記第2のドレイン電極層を覆うように形成され、前記酸化物半導体層に接する第1のドレイン電極層からなることを特徴とする半導体装置。

【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記酸化物半導体層は、前記基板側から第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の順で積層された構造を有し、

前記第1の酸化物半導体層および前記第3の酸化物半導体層は前記第2の酸化物半導体層よりも伝導帯下端のエネルギーが0.05eV以上2eV以下の範囲で真空準位に近いことを特徴とする半導体装置。

20

【請求項5】

基板上に形成された第1の酸化物半導体層と、

前記第1の酸化物半導体層上に形成された第2の酸化物半導体層と、

前記第2の酸化物半導体層に接する第1のソース電極層および第1のドレイン電極層と、

前記第2の酸化物半導体層、前記第1のソース電極層および前記第1のドレイン電極層上に形成された第3の酸化物半導体層と、

前記第1のソース電極層を覆うように重畠し、前記第1のソース電極層および前記第3の酸化物半導体層のそれぞれと接する第2のソース電極層と、

30

前記第1のドレイン電極層を覆うように重畠し、前記第1のドレイン電極層および前記第3の酸化物半導体層のそれぞれと接する第2のドレイン電極層と、

前記第3の酸化物半導体層、前記第2のソース電極層および前記第2のドレイン電極層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された、第1のゲート電極層、第2のゲート電極層および第3のゲート電極層と、を有し、

前記第1のゲート電極層乃至前記第3のゲート電極層は、それぞれ離間しており、

前記第1のゲート電極層は、前記第1の酸化物半導体層および前記第2の酸化物半導体層と重畠し、

前記第2のゲート電極層は、前記第1の酸化物半導体層および前記第2の酸化物半導体層のチャネル幅方向の一方の端部の一部を覆い、

40

前記第3のゲート電極層は、前記第1の酸化物半導体層および前記第2の酸化物半導体層のチャネル幅方向の他方の端部の一部を覆うことを特徴とする半導体装置。

【請求項6】

請求項5において、

前記第1の酸化物半導体層および前記第3の酸化物半導体層は、前記第2の酸化物半導体層よりも伝導帯下端のエネルギーが0.05eV以上2eV以下の範囲で真空準位に近いことを特徴とする半導体装置。

【請求項7】

請求項4乃至請求項6のいずれか一項において、

50

前記第1の酸化物半導体層乃至前記第3の酸化物半導体層は、In-M-Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)であり、前記第1の酸化物半導体層および前記第3の酸化物半導体層は、Inに対するMの原子数比が前記第2の酸化物半導体層よりも大きいことを特徴とする半導体装置。

【請求項8】

請求項2乃至請求項7のいずれか一項において、

前記第1のソース電極層および前記第1のドレイン電極層は、Al、Cr、Cu、Ta、Ti、Mo、W、またはこれらを主成分とする合金材料であることを特徴とする半導体装置。

【請求項9】

10

請求項2乃至請求項8のいずれか一項において、

前記第2のソース電極層および前記第2のドレイン電極層は、窒化タンタル、窒化チタン、ルテニウム、またはこれらを主成分とする合金材料であることを特徴とする半導体装置。

【請求項10】

請求項2乃至請求項9のいずれか一項において、

前記第1のゲート電極層は、前記第1のソース電極層および前記第1のドレイン電極層と重畠しないことを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は酸化物半導体を有する半導体装置に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電気機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ(薄膜トランジスタ(TFT)ともいう)を構成する技術が注目されている。該トランジスタは集積回路(IIC)や画像表示装置(表示装置)のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

30

【0004】

例えば、トランジスタの活性層として、インジウム(In)、ガリウム(Ga)、および亜鉛(Zn)を含む非晶質酸化物半導体を用いたトランジスタが特許文献1に開示されている。

【0005】

また、従来の薄膜トランジスタは、活性層、絶縁膜、および電極などを平面上に積み重ねていく、いわゆるプレーナ型構造が主流であったが、製造プロセスの微細化が進むにつれ、チャネル幅も縮小されるため、オン電流が低下してしまう。そのため、近年では、従来のプレーナ型構造に変わる、新しい構造のトランジスタの開発が進められている。例えば、特許文献2では、活性層(特許文献2では半導体薄膜と記載されている。)としてポリシリコン膜を用いた、フィン型構造のトランジスタが開示されている。

40

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006-165528号公報

【特許文献2】特開2009-206306号公報

【発明の概要】

【発明が解決しようとする課題】

50

**【 0 0 0 7 】**

特許文献2に開示されているようなトランジスタは、プレーナ型構造のトランジスタと比較して、オフ電流（トランジスタがオフ状態の時に、ソース-ドレイン間に流れる電流）を低減することができるため、消費電力の低減に有効であるといえる。しかしながら、半導体装置に対する低消費電力化の要望は今後さらに高まることは明らかであり、故に、トランジスタに対してもさらなるオフ電流の抑制対策が求められる。

**【 0 0 0 8 】**

トランジスタのオフ電流を低減する方法の一つとして、活性層に酸化物半導体材料を用いたトランジスタが提案されている。トランジスタの活性層として酸化物半導体材料を用いたトランジスタは、シリコン系半導体材料を用いたトランジスタと比較して、オフ電流が非常に低い特徴を有している。

10

**【 0 0 0 9 】**

また、トランジスタの動作の高速化、トランジスタの低消費電力化、高集積化、低価格化、などを達成するためには、トランジスタの微細化は必須である。しかし、トランジスタを微細化すると、しきい値電圧のマイナスシフトやS値（サブスレッシュホールド値）の上昇などの電気特性の低下が懸念される。

**【 0 0 1 0 】**

上記の対策として、酸化物半導体層（活性層）を絶縁膜を介して上下のゲート電極層で挟み、一方を動作制御用、他方をしきい値電圧制御用とする構造が検討されている。しかしながら、他方のゲート電極層と活性層との間には、より多く酸素を活性層に供給するための厚い酸化物絶縁膜が形成されていることが望ましく、他方のゲート電極層からの電界が酸化物半導体層に及びにくい問題があった。

20

**【 0 0 1 1 】**

したがって、本発明の一態様は、微細化に伴い顕著となる電気特性の低下を抑制できる構成の半導体装置を提供することを目的の一つとする。また、信頼性の高い半導体装置を提供することを目的の一つとする。

**【課題を解決するための手段】****【 0 0 1 2 】**

本発明の一態様における半導体装置は、複数のゲート電極層が、絶縁膜を介して酸化物半導体層と重畳する領域のみならず、酸化物半導体層のチャネル幅方向の端部（つまり、酸化物半導体層のチャネル幅方向の側壁）を覆う構成を有する。当該半導体装置の具体的な構成について、以下に説明する。

30

**【 0 0 1 3 】**

本発明の一態様は、第1のゲート電極層、第2のゲート電極層および第3のゲート電極層を有し、第1のゲート電極層乃至第3のゲート電極層は、それぞれ離間しており、第1のゲート電極層は、酸化物半導体層と重畳し、第2のゲート電極層は、酸化物半導体層のチャネル幅方向の一方の端部の一部を覆い、第3のゲート電極層は、酸化物半導体層のチャネル幅方向の他方の端部の一部を覆う半導体装置に関する。

**【 0 0 1 4 】**

本発明の一態様は、基板上に形成された酸化物半導体層と、酸化物半導体層に接するソース電極層およびドレイン電極層と、酸化物半導体層、ソース電極層およびドレイン電極層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第1のゲート電極層、第2のゲート電極層および第3のゲート電極層と、を有し、第1のゲート電極層乃至第3のゲート電極層は、それぞれ離間しており、第1のゲート電極層は、酸化物半導体層と重畳し、第2のゲート電極層は、酸化物半導体層のチャネル幅方向の一方の端部の一部を覆い、第3のゲート電極層は、酸化物半導体層のチャネル幅方向の他方の端部の一部を覆うことを特徴とする半導体装置である。

40

**【 0 0 1 5 】**

また、上記構成において、ソース電極層は、酸化物半導体層に接する第1のソース電極層と、第1のソース電極層を覆うように形成され、酸化物半導体層に接する第2のソース電

50

極層からなり、ドレイン電極層は、酸化物半導体層に接する第1のドレイン電極層と、第1のドレイン電極層を覆うように形成され、酸化物半導体層に接する第2のドレイン電極層からなることが好ましい。

【0016】

また、上記構成において、ソース電極層は、酸化物半導体層に接する第2のソース電極層と、第2のソース電極層を覆うように形成され、酸化物半導体層に接する第1のソース電極層からなり、ドレイン電極層は、酸化物半導体層に接する第2のドレイン電極層と、第2のドレイン電極層を覆うように形成され、酸化物半導体層に接する第1のドレイン電極層からなることが好ましい。

【0017】

また、上記構成において、酸化物半導体層は、基板側から第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の順で積層された構造を有し、第1の酸化物半導体層および第3の酸化物半導体層は第2の酸化物半導体層よりも伝導帯下端のエネルギーが0.05eV以上2eV以下の範囲で真空準位に近いことが好ましい。

【0018】

また、本発明の他の一態様は、基板上に形成された第1の酸化物半導体層と、第1の酸化物半導体層上に形成された第2の酸化物半導体層と、第2の酸化物半導体層に接する第1のソース電極層および第1のドレイン電極層と、第2の酸化物半導体層、第1のソース電極層および第1のドレイン電極層上に形成された第3の酸化物半導体層と、第1のソース電極層を覆うように重疊し、第1のソース電極層および第3の酸化物半導体層のそれぞれと接する第2のソース電極層と、第1のドレイン電極層および第3の酸化物半導体層のそれぞれと接する第2のドレイン電極層と、第3の酸化物半導体層、第2のソース電極層および第2のドレイン電極層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第1のゲート電極層、第2のゲート電極層および第3のゲート電極層と、を有し、第1のゲート電極層乃至第3のゲート電極層は、それぞれ離間しており、第1のゲート電極層は、第1の酸化物半導体層および第2の酸化物半導体層と重疊し、第2のゲート電極層は、第1の酸化物半導体層および第2の酸化物半導体層のチャネル幅方向の一方の端部の一部を覆い、第3のゲート電極層は、第1の酸化物半導体層および第2の酸化物半導体層のチャネル幅方向の他方の端部の一部を覆うことを特徴とする半導体装置である。

【0019】

また、上記構成において、第1の酸化物半導体層および第3の酸化物半導体層は、第2の酸化物半導体層よりも伝導帯下端のエネルギーが0.05eV以上2eV以下の範囲で真空準位に近いことが好ましい。

【0020】

また、上記構成において、第1の酸化物半導体層乃至第3の酸化物半導体層は、In-M-Zn酸化物 (MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) であり、第1の酸化物半導体層および第3の酸化物半導体層は、Inに対するMの原子数比が前記第2の酸化物半導体層よりも大きいことが好ましい。

【0021】

また、上記構成において、第1のソース電極層および第1のドレイン電極層は、Al、Cr、Cu、Ta、Ti、Mo、W、またはこれらを主成分とする合金材料であることが好ましい。

【0022】

また、上記構成において、第2のソース電極層および第2のドレイン電極層は、窒化タンタル、窒化チタン、ルテニウム、またはこれらを主成分とする合金材料であることが好ましい。

【0023】

また、上記構成において、第1のゲート電極層は、第1のソース電極層および第1のドレイン電極層と重疊しない位置に形成されていることが好ましい。

10

20

30

40

50

## 【発明の効果】

## 【0024】

本発明の一態様を用いることにより、微細化にともなうしきい値電圧のマイナスシフトやS値の上昇などの電気特性の低下を抑制することができる半導体装置を提供することができる。また、信頼性の高い半導体装置を提供することができる。

## 【図面の簡単な説明】

## 【0025】

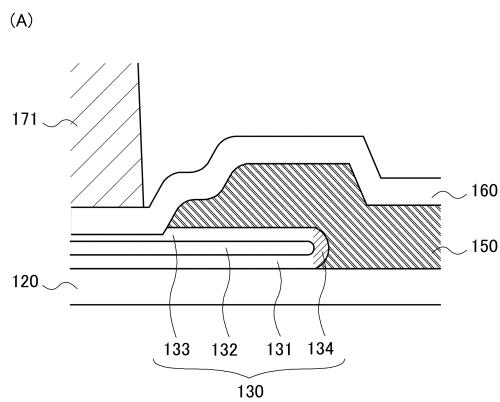

【図1】トランジスタを説明する上面図および断面図。

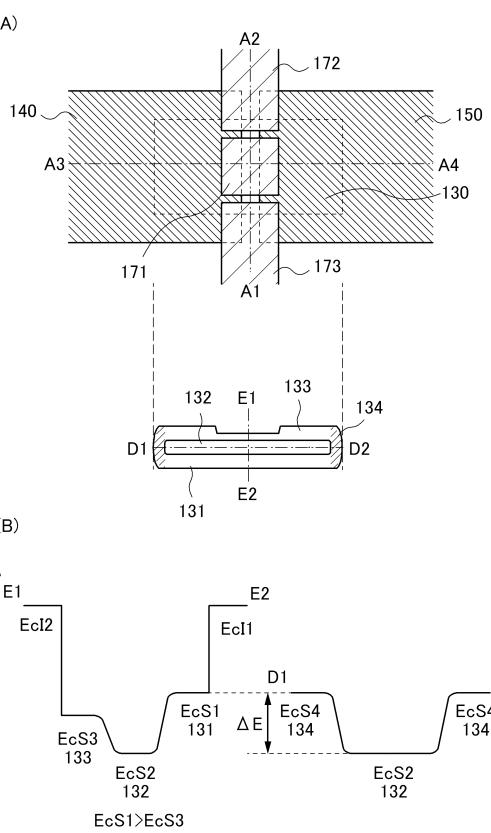

【図2】酸化物半導体層のバンド構造を説明する図。

【図3】酸化物半導体層のバンド構造を説明する図。

10

【図4】酸化物半導体層のバンド構造を説明する図。

【図5】トランジスタの拡大断面図。

【図6】トランジスタを説明する上面図、断面図、および酸化物半導体層のバンド構造を説明する図。

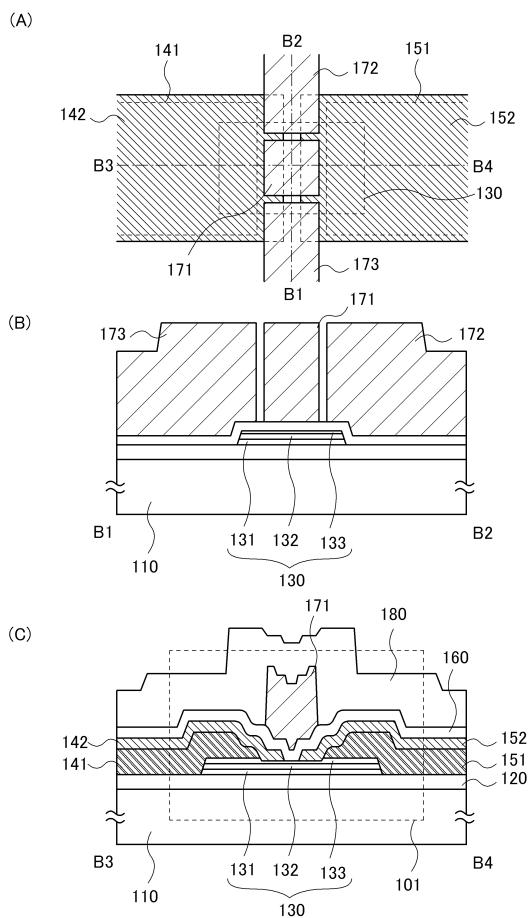

【図7】トランジスタを説明する上面図および断面図。

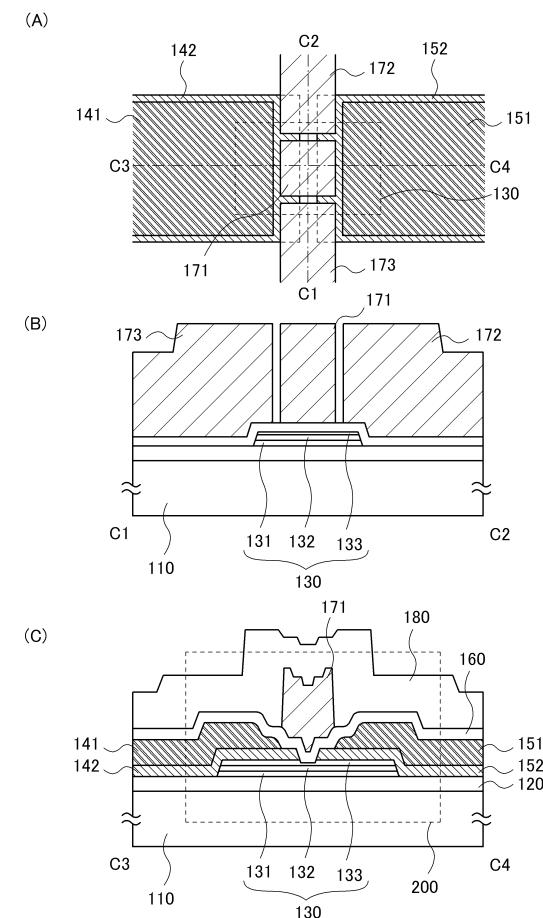

【図8】トランジスタを説明する上面図および断面図。

【図9】トランジスタを説明する上面図および断面図。

【図10】トランジスタの作製方法を説明する図。

【図11】トランジスタの作製方法を説明する図。

【図12】トランジスタの作製方法を説明する図。

20

【図13】半導体装置の断面図および回路図。

【図14】半導体装置の回路図および斜視図。

【図15】半導体装置のプロック図。

【図16】半導体装置の断面図。

【図17】半導体装置のプロック図。

【図18】半導体装置を適用することができる電子機器および電気機器を説明する図。

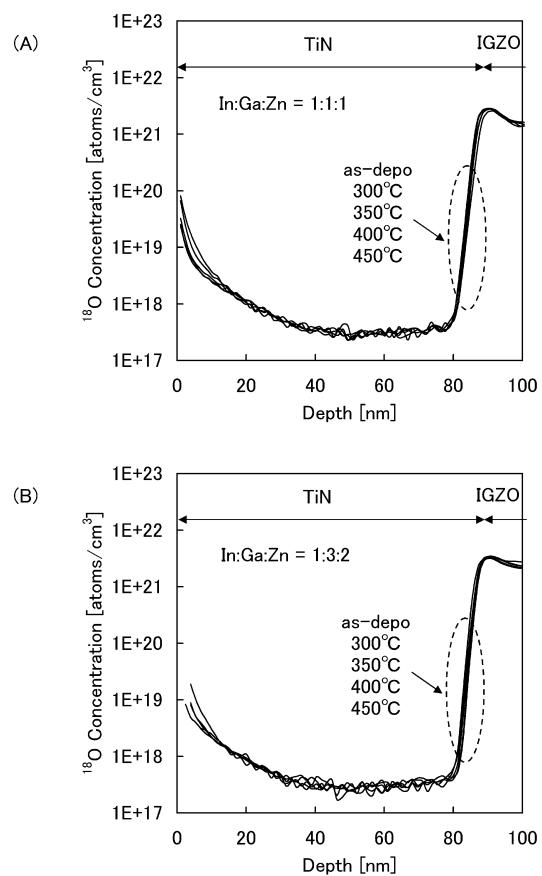

【図19】IGZO膜およびW膜の積層をSIMS分析した結果を示す図。

【図20】IGZO膜および窒化タンタル膜の積層をSIMS分析した結果を示す図。

【図21】IGZO膜および窒化チタン膜の積層をSIMS分析した結果を示す図。

## 【発明を実施するための形態】

30

## 【0026】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。

## 【0027】

## (実施の形態1)

本実施の形態では、本発明の一態様の半導体装置について図面を用いて説明する。

40

## 【0028】

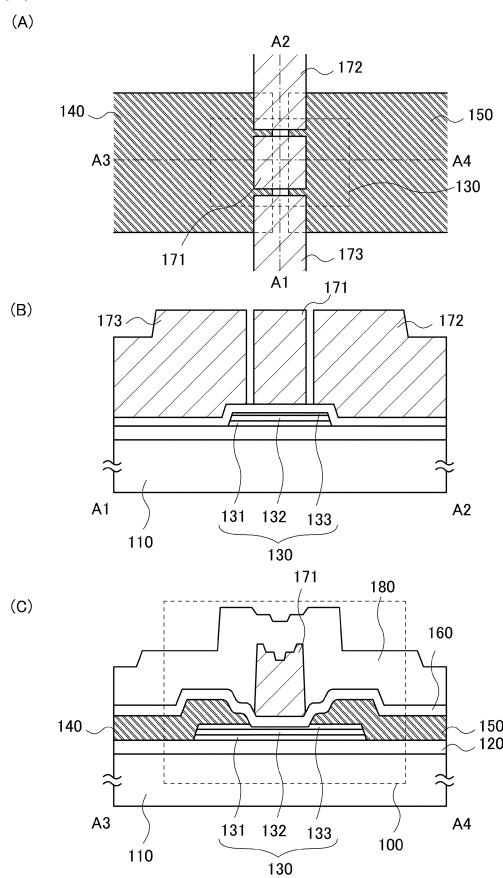

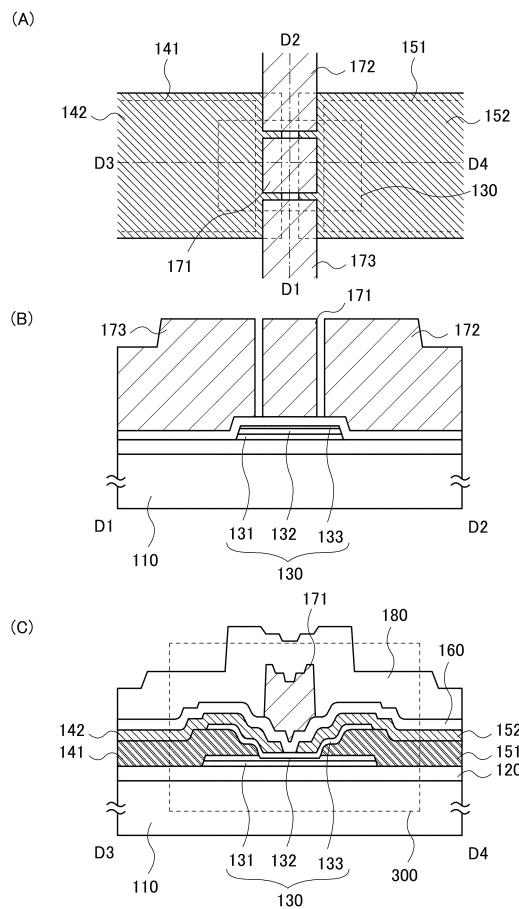

図1(A)、(B)、(C)は、本発明の一態様のトランジスタの上面図および断面図である。図1(A)は上面図であり、図1(A)に示す一点鎖線A1-A2の断面が図1(B)に相当する。また、図1(A)に示す一点鎖線A3-A4の断面が図1(C)に相当する。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線A1-A2方向をチャネル幅方向、一点鎖線A3-A4方向をチャネル長方向と呼称する場合がある。

## 【0029】

図1(A)、(B)、(C)に示すトランジスタ100は、基板110上に形成された下地絶縁膜120、該下地絶縁膜120上に形成された酸化物半導体層130、該酸化物半

50

導体層 130 上に形成されたソース電極層 140、ドレイン電極層 150、該ソース電極層 140、該ドレイン電極層 150、および酸化物半導体層 130 上に形成されたゲート絶縁膜 160、該ゲート絶縁膜 160 上に形成された第 1 のゲート電極層 171、第 2 のゲート電極層 172、第 3 のゲート電極層 173 を有する。また、該ゲート絶縁膜 160 および該第 1 のゲート電極層 171、第 2 のゲート電極層 172、第 3 のゲート電極層 173 上に酸化物絶縁層 180 が形成されていてもよい。当該酸化物絶縁層 180 は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

#### 【 0 0 3 0 】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

10

#### 【 0 0 3 1 】

基板 110 は、単なる支持基板に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ 100 の第 1 のゲート電極層 171、第 2 のゲート電極層 172、第 3 のゲート電極層 173、ソース電極層 140、およびドレイン電極層 150 の少なくとも一つは、上記の他のデバイスと電気的に接続されていてもよい。

#### 【 0 0 3 2 】

下地絶縁膜 120 は、基板 110 からの不純物の拡散を防止する役割を有するほか、酸化物半導体層 130 に酸素を供給する役割を担うことができるため、酸素を含む絶縁膜であることが好ましく、過剰な酸素を含む絶縁膜がより好ましい。また、上述のように基板 110 が他のデバイスが形成された基板である場合、下地絶縁膜 120 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように CMP ( Chemical Mechanical Polishing ) 法等で平坦化処理を行うことが好ましい。

20

#### 【 0 0 3 3 】

酸化物半導体層 130 は、基板 110 側から第 1 の酸化物半導体層 131、第 2 の酸化物半導体層 132、第 3 の酸化物半導体層 133 が積層された構造を有している。ここで、第 2 の酸化物半導体層 132 には、第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 よりも電子親和力（真空準位から伝導帯下端までのエネルギー）が大きい酸化物半導体を用いる。電子親和力は、真空準位と価電子帯上端とのエネルギー差（イオン化ポテンシャル）から、伝導帯下端と価電子帯上端とのエネルギー差（バンドギャップ）を差し引いた値として求めることができる。

30

#### 【 0 0 3 4 】

なお、本実施の形態では、酸化物半導体層 130 が三層の積層である場合について説明するが、酸化物半導体層 130 が一層、二層または四層以上であってもよい。一層の場合は、第 2 の酸化物半導体層 132 に相当する層を用いればよい。二層の場合は、基板 110 側に第 2 の酸化物半導体層 132 に相当する層を用い、ゲート絶縁膜 160 側に第 1 の酸化物半導体層 131 または第 3 の酸化物半導体層 133 に相当する層を用いればよい。四層以上である場合は、本実施の形態の説明と同じように第 2 の酸化物半導体層 132 が第 1 の酸化物半導体層 131 または第 3 の酸化物半導体層 133 に相当する層で挟まれる構造とすればよい。

40

#### 【 0 0 3 5 】

第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 は、第 2 の酸化物半導体層 132 を構成する金属元素を一種以上含み、伝導帯下端のエネルギーが第 2 の酸化物半導体層 132 よりも、0.05 eV、0.07 eV、0.1 eV、0.15 eV のいずれか以上であって、2 eV、1 eV、0.5 eV、0.4 eV のいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

#### 【 0 0 3 6 】

このような構造において、第 1 のゲート電極層 171 に電界を印加すると、酸化物半導体

50

層 130 のうち、伝導帯下端のエネルギーが最も小さい第 2 の酸化物半導体層 132 にチャネルが形成される。すなわち、第 2 の酸化物半導体層 132 とゲート絶縁膜 160 との間に第 3 の酸化物半導体層 133 が形成されていることによって、トランジスタのチャネルをゲート絶縁膜 160 と接しない構造とすることができます。

【 0037 】

また、第 2 の酸化物半導体層 132 を構成する金属元素を一種以上含んで第 1 の酸化物半導体層 131 が構成されるため、第 2 の酸化物半導体層 132 と第 1 の酸化物半導体層 131 の界面に界面準位を形成しにくくなる。該界面準位はチャネルを形成することがあるため、しきい値電圧の異なる第 2 のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。したがって、第 1 の酸化物半導体層 131 を設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。10

【 0038 】

また、第 2 の酸化物半導体層 132 を構成する金属元素を一種以上含んで第 3 の酸化物半導体層 133 が構成されるため、第 2 の酸化物半導体層 132 と第 3 の酸化物半導体層 133 との界面ではキャリアの散乱が起こりにくくなる。したがって、第 3 の酸化物半導体層 133 を設けることにより、トランジスタの電界効果移動度を高くすることができます。

【 0039 】

第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 には、例えば、Al、Ti、Ga、Ge、Y、Zr、Sn、La、Ce または Hf を第 2 の酸化物半導体層 132 よりも高い原子数比で含む材料を用いることができる。具体的には、当該原子数比を 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上とする。前述の元素は酸素と強く結合するため、酸素欠損が酸化物半導体層に生じることを抑制する機能を有する。すなわち、第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 は、第 2 の酸化物半導体層 132 よりも酸素欠損が生じにくいことができる。20

【 0040 】

なお、第 1 の酸化物半導体層 131 、第 2 の酸化物半導体層 132 、第 3 の酸化物半導体層 133 が、少なくともインジウム、亜鉛および M (Al、Ti、Ga、Ge、Y、Zr、Sn、La、Ce または Hf 等の金属) を含む In-M-Zn 酸化物であるとき、第 1 の酸化物半導体層 131 を  $In : M : Zn = x_1 : y_1 : z_1$  [原子数比] 、第 2 の酸化物半導体層 132 を  $In : M : Zn = x_2 : y_2 : z_2$  [原子数比] 、第 3 の酸化物半導体層 133 を  $In : M : Zn = x_3 : y_3 : z_3$  [原子数比] とすると、 $y_1 / x_1$  および  $y_3 / x_3$  が  $y_2 / x_2$  よりも大きくなることが好ましい。 $y_1 / x_1$  および  $y_3 / x_3$  は  $y_2 / x_2$  よりも 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上とする。このとき、第 2 の酸化物半導体層 132 において、 $y_2$  が  $x_2$  以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_2$  が  $x_2$  の 3 倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$  は  $x_2$  の 3 倍未満であることが好ましい。30

【 0041 】

また、第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 の In と M の原子数比率は、好ましくは In が 50 atomic % 未満、M が 50 atomic % 以上、さらに好ましくは In が 25 atomic % 未満、M が 75 atomic % 以上とする。また、第 2 の酸化物半導体層 132 の In と M の原子数比率は、好ましくは In が 25 atomic % 以上、M が 75 atomic % 未満、さらに好ましくは In が 34 atomic % 以上、M が 66 atomic % 未満とする。40

【 0042 】

第 1 の酸化物半導体層 131 および第 3 の酸化物半導体層 133 の厚さは、3 nm 以上 100 nm 以下、好ましくは 3 nm 以上 50 nm 以下とする。また、第 2 の酸化物半導体層 132 の厚さは、3 nm 以上 200 nm 以下、好ましくは 3 nm 以上 100 nm 以下、さらに好ましくは 3 nm 以上 50 nm 以下とする。50

## 【0043】

第1の酸化物半導体層131、第2の酸化物半導体層132、および第3の酸化物半導体層133には、例えば、インジウム、亜鉛およびガリウムを含んだ酸化物半導体を用いることができる。特に、第2の酸化物半導体層132にインジウムを含ませると、キャリア移動度が高くなるため好ましい。

## 【0044】

なお、酸化物半導体層をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$  未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$  未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$  未満であることを指す。10

## 【0045】

また、酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素は、ドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは、酸化物半導体層中で不純物準位を形成する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させことがある。したがって、第1の酸化物半導体層131、第2の酸化物半導体層132および第3の酸化物半導体層133の層中や、それぞれの界面において不純物濃度を低減することが有効である。

## 【0046】

酸化物半導体層を真性または実質的に真性とすることには、SIMS (Secondary Ion Mass Spectrometry) 分析において、シリコン濃度を $1 \times 10^{19} \text{ atoms} / \text{cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満とする。また、水素濃度は、 $2 \times 10^{20} \text{ atoms} / \text{cm}^3$  以下、好ましくは $5 \times 10^{19} \text{ atoms} / \text{cm}^3$  以下、より好ましくは $1 \times 10^{19} \text{ atoms} / \text{cm}^3$  以下、さらに好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下とする。また、窒素濃度は、 $5 \times 10^{19} \text{ atoms} / \text{cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、より好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、さらに好ましくは $5 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。20

## 【0047】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、シリコン濃度を $1 \times 10^{19} \text{ atoms} / \text{cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満とすればよい。また、炭素濃度を $1 \times 10^{19} \text{ atoms} / \text{cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  未満とすればよい。30

## 【0048】

また、上述のように高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さく、トランジスタのチャネル幅で規格化したオフ電流は、数  $y \text{ A} / \mu\text{m} \sim \text{数 } z \text{ A} / \mu\text{m}$  にまで低減することが可能となる。40

## 【0049】

なお、トランジスタのゲート絶縁膜としては、シリコンを含む絶縁膜が多く用いられるため、上記理由により酸化物半導体層のチャネルとなる領域はゲート絶縁膜と接しないことが好ましいということができる。また、ゲート絶縁膜と酸化物半導体層との界面にチャネルが形成される場合、該界面でキャリアの散乱が起こり、トランジスタの電界効果移動度が低くなることがある。このような観点からも、酸化物半導体層のチャネルとなる領域はゲート絶縁膜から離すことが好ましい。

## 【0050】

したがって、酸化物半導体層130を第1の酸化物半導体層131、第2の酸化物半導体50

層 1 3 2、第 3 の酸化物半導体層 1 3 3 の積層構造とすることで、トランジスタのチャネルが形成される第 2 の酸化物半導体層 1 3 2 をゲート絶縁膜から離すことができ、高い電界効果移動度を有し、安定した電気特性のトランジスタを形成することができる。

【 0 0 5 1 】

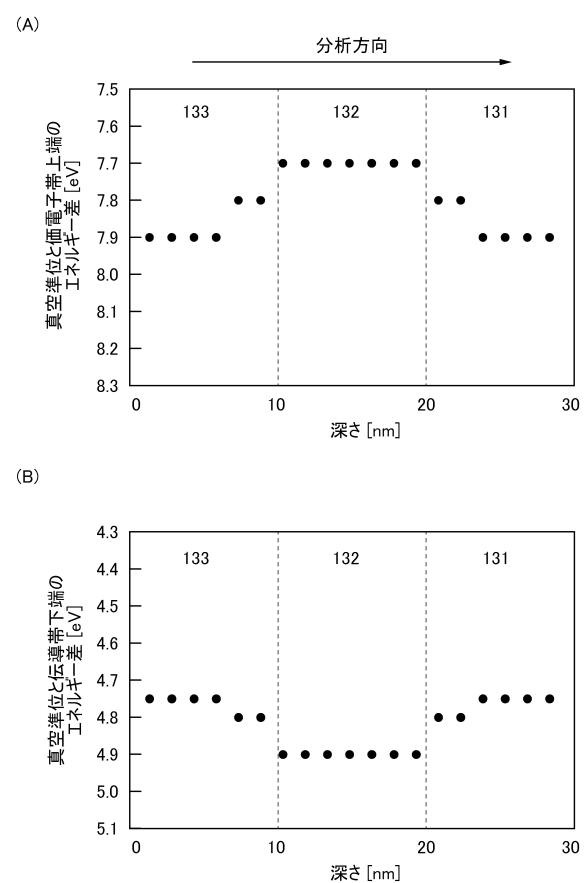

次に、酸化物半導体層 1 3 0 のバンド構造を説明する。バンド構造の解析は、第 1 の酸化物半導体層 1 3 1 および第 3 の酸化物半導体層 1 3 3 に相当する層としてエネルギーギャップが 3.15 eV である In - Ga - Zn 酸化物、第 2 の酸化物半導体層 1 3 2 に相当する層としてエネルギーギャップが 2.8 eV である In - Ga - Zn 酸化物を用い、酸化物半導体層 1 3 0 に相当する積層を作製して行っている。なお、便宜的に当該積層を酸化物半導体層 1 3 0 、当該積層を構成するそれぞれの層を第 1 の酸化物半導体層 1 3 1 、第 2 の酸化物半導体層 1 3 2 、第 3 の酸化物半導体層 1 3 3 と称して説明する。

10

【 0 0 5 2 】

第 1 の酸化物半導体層 1 3 1 、第 2 の酸化物半導体層 1 3 2 、第 3 の酸化物半導体層 1 3 3 の膜厚はそれぞれ 10 nm とし、エネルギーギャップは、分光エリプソメータ (HORIBA JOBIN YVON 社 U T - 300) を用いて測定した。また、第 1 の酸化物半導体層 1 3 1 と第 2 の酸化物半導体層 1 3 2 との界面近傍のエネルギーギャップは 3 eV 、第 3 の酸化物半導体層 1 3 3 と第 2 の酸化物半導体層 1 3 2 との界面近傍のエネルギーギャップは 3 eV とした。

【 0 0 5 3 】

図 2 (A) は、酸化物半導体層 1 3 0 を第 3 の酸化物半導体層 1 3 3 からエッティングしつつ、各層の真空準位と価電子帯上端のエネルギー差を測定し、その値をプロットした図である。真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析 (UPS: UV visible Photoelectron Spectroscopy) 装置 (PHI 社 Versa Probe) を用いて測定した。

20

【 0 0 5 4 】

図 2 (B) は、真空準位と価電子帯上端のエネルギー差と、各層のエネルギーギャップとの差分として算出される真空準位と伝導帯下端のエネルギー差 (電子親和力) をプロットした図である。

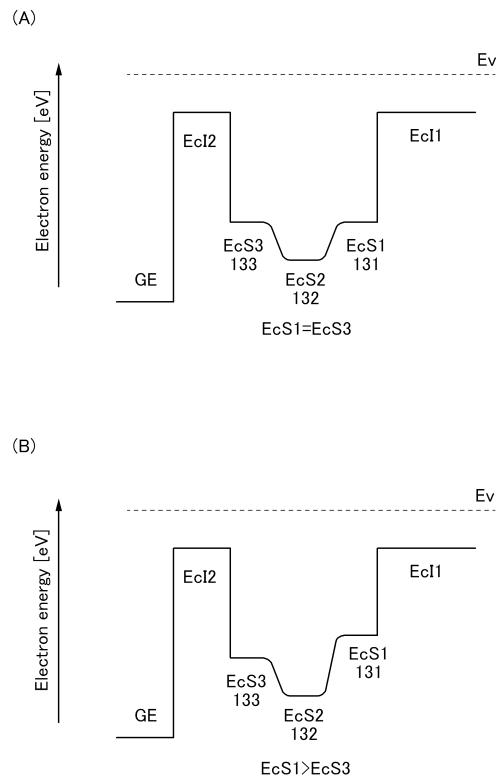

【 0 0 5 5 】

そして、図 2 (B) を模式的に示したバンド構造の一部が、図 3 (A) である。図 3 (A) では、第 1 の酸化物半導体層 1 3 1 および第 3 の酸化物半導体層 1 3 3 と接して、酸化シリコン膜を設けた場合について説明する。ここで、Ev は真空準位のエネルギー、EcI1 および EcI2 は酸化シリコン膜の伝導帯下端のエネルギー、EcS1 は第 1 の酸化物半導体層 1 3 1 の伝導帯下端のエネルギー、EcS2 は第 2 の酸化物半導体層 1 3 2 の伝導帯下端のエネルギー、EcS3 は第 3 の酸化物半導体層 1 3 3 の伝導帯下端のエネルギーを示す。また、トランジスタを構成する場合、ゲート電極層 (トランジスタ 100 では第 1 のゲート電極層 171 に相当) は EcI2 を有する酸化シリコン膜に接するものとする。

30

【 0 0 5 6 】

図 3 (A) に示すように、第 1 の酸化物半導体層 1 3 1 、第 2 の酸化物半導体層 1 3 2 、第 3 の酸化物半導体層 1 3 3 において、伝導帯下端のエネルギーが連続的に変化する。これは、第 1 の酸化物半導体層 1 3 1 、第 2 の酸化物半導体層 1 3 2 、第 3 の酸化物半導体層 1 3 3 の組成が近似することにより、酸素が相互に拡散しやすい点からも理解される。

40

【 0 0 5 7 】

主成分を共通として積層された酸化物半導体層 1 3 0 は、各層を単に積層するのではなく連続接合 (ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化する U 字型の井戸構造) が形成されるように作製する。すなわち、各層の界面に酸化物半導体にとってトラップ中心や再結合中心のような欠陥準位、あるいはキャリアの流れを阻害するバリアを形成するような不純物が存在しないように積層構造を形成する。仮に、積層された酸化物半導体層の層間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界面

50

でキャリアがトラップあるいは再結合により消滅してしまう。

【0058】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタ装置）を用いて各層を大気に触れさせることなく連続して積層することが必要となる。スパッタ装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべく、クライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $1 \times 10^{-4}$  Pa ~  $5 \times 10^{-7}$  Pa 程度まで）できること、かつ、成膜される基板を 100 以上に加熱できることが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に炭素成分や水分等を含む気体が逆流しないようにしておくことが好ましい。

10

【0059】

高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が -40 以下、好ましくは -80 以下、より好ましくは -100 以下にまで高純度化したガスを用いることで酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

【0060】

なお、図3(A)では、ECS1とECS3が同様である場合について示したが、それぞれが異なっていてもよい。例えば、ECS3よりもECS1が高いエネルギーを有する場合、バンド構造の一部は、図3(B)のように示される。

20

【0061】

例えば、ECS1 = ECS3 である場合は、第1の酸化物半導体層 131 および第3の酸化物半導体層 133 に In : Ga : Zn = 1 : 3 : 2 (原子数比)、第2の酸化物半導体層 132 に In : Ga : Zn = 1 : 1 : 1 (原子数比) の In - Ga - Zn 酸化物などを用いることができる。また、ECS1 > ECS3 である場合は、第1の酸化物半導体層 131 に In : Ga : Zn = 1 : 6 : 4 または 1 : 9 : 6 (原子数比)、第2の酸化物半導体層 132 に In : Ga : Zn = 1 : 1 : 1 または 3 : 1 : 2 (原子数比)、第3の酸化物半導体層 133 に In : Ga : Zn = 1 : 3 : 2 (原子数比) の In - Ga - Zn 酸化物などを用いることができる。

【0062】

30

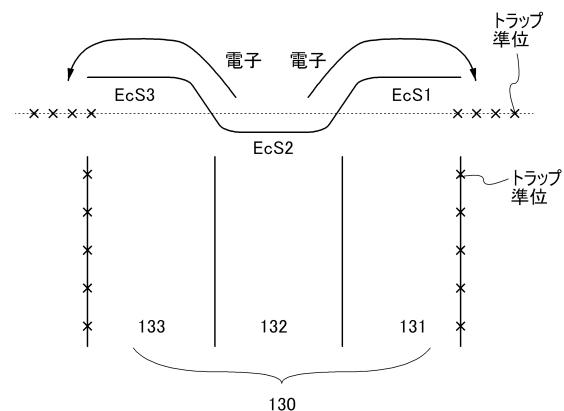

図2(A)、(B)および図3(A)、(B)より、酸化物半導体層 130 における第2の酸化物半導体層 132 がウェル（井戸）となり、酸化物半導体層 130 を用いたトランジスタにおいて、チャネルが第2の酸化物半導体層 132 に形成されることがわかる。なお、酸化物半導体層 130 は伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸（U Shape Well）とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルといふこともできる。

【0063】

なお、図4に示すように、第1の酸化物半導体層 131 および第3の酸化物半導体層 133 と、酸化シリコン膜などの絶縁膜との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。第1の酸化物半導体層 131 および第3の酸化物半導体層 133 があることにより、第2の酸化物半導体層 132 と当該トラップ準位とを遠ざけることができる。ただし、ECS1 または ECS3 と、ECS2 とのエネルギー差が小さい場合、第2の酸化物半導体層 132 の電子が該エネルギー差を超えてトラップ準位に達することができる。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

40

【0064】

したがって、ECS1 および ECS3 と、ECS2 とのエネルギー差を、それぞれ 0.1 eV 以上、好ましくは 0.15 eV 以上とすることで、トランジスタのしきい値電圧の変動が低減され、安定した電気特性を得ることができる。

【0065】

50

なお、第1の酸化物半導体層131、第2の酸化物半導体層132および第3の酸化物半導体層133のいずれか一つ以上の層には、結晶部が含まれることが好ましい。例えば、第1の酸化物半導体層131を非晶質とし、第2の酸化物半導体層132および第3の酸化物半導体層133を結晶部が含まれる層とする。チャネルが形成される第2の酸化物半導体層132が結晶部を含むことにより、トランジスタに安定した電気特性を付与することができる。

【0066】

特に、第2の酸化物半導体層132および第3の酸化物半導体層133に含まれる結晶部は、表面と略垂直な方向にc軸が配向した結晶を有することが好ましい。

【0067】

また、図1の構造のトランジスタにおいて、第3の酸化物半導体層133はソース電極層140およびドレイン電極層150に接しており、電流を効率良く取り出すにはエネルギー・ギャップが絶縁体のように大きくないこと、および膜厚が薄いことが好ましい。また、酸化物半導体層130にIn-Ga-Zn酸化物を用いる場合は、Inのゲート絶縁膜への拡散を防ぐために、第3の酸化物半導体層133は第2の酸化物半導体層132よりもInを少なくする組成とすることが好ましい。

【0068】

また、図5(A)のトランジスタの拡大図に示すように、酸化物半導体層130の端部に曲面を有する領域134を設けても良い。酸化物半導体層130をIn-M-Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)で形成する場合、第2の酸化物半導体層132を構成するM(MS2)と領域134を構成するM(MS4)の量的関係は、MS4 > MS2であることが好ましい。より好ましくは、MS4は第1の酸化物半導体層131を構成するM(MS1)と同等とする。

【0069】

酸化物半導体層130の端部における領域134は、ドライエッチング法にて第1の酸化物半導体層131の成分を第2の酸化物半導体層132及び第3の酸化物半導体層133に再付着させる、所謂ラビットイヤーを利用して形成することができる。さらに酸化処理によりラビットイヤー形成時に付着するエッチングガス成分を除去し、M成分を酸化することで領域134の絶縁性を高めることができる。

【0070】

また、図5(B)に示すように酸化物半導体層130をドライエッチングする際に、下地絶縁膜120の一部がエッチングされる。このため、酸化物半導体層130が接する領域の下地絶縁膜120の膜厚は、酸化物半導体層130が接しない領域の下地絶縁膜120の膜厚より大きい。このような構成になることで、酸化物半導体層130と、ソース電極層140またはドレイン電極層150との密着性を向上させることができる。

【0071】

図6(A)は図1に示すトランジスタの上面図および酸化物半導体層130の断面図である。ゲート電極層が重畳する酸化物半導体層130の領域134は、外的要因による不純物の混入や酸素欠損の発生などによりn型化しやすく、寄生チャネルとなることがある。特にエネルギー・ギャップの小さい第2の酸化物半導体層132ではn型化が顕著に起こりやすいため、第2の酸化物半導体層132を覆う領域134には寄生チャネルの発生を抑制する作用があるといえる。

【0072】

第1の酸化物半導体層131と領域134の主成分が同一であるとき、第2の酸化物半導体層132の伝導帯下端のエネルギー(EcS2)と領域134の伝導帯下端のエネルギー(EcS4)の差分(E)が大きいほど寄生チャネルの発生を抑える効果が高い。また、領域134の厚みは、第1の酸化物半導体層131または第3の酸化物半導体層133よりも厚いことが好ましく、厚いほど第2の酸化物半導体層132端部のn型化による寄生チャネルの発生を抑えることができる。

【0073】

10

20

30

40

50

また、領域134は、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133と組成が近似することにより、酸化物半導体層130のバンド構造の一部を示す図6(B)のように伝導帯下端のエネルギーが連続的に変化する。すなわち、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133、および領域134は連続接合であることができる。なお、図6(B)に示す一点鎖線D1-D2は、図6(A)の酸化物半導体層130の断面図に示す一点鎖線D1-D2方向に相当し、図6(B)に示すE1-E2は図6(A)に示す一点鎖線E1-E2方向に相当する。

#### 【0074】

ソース電極層140およびドレイン電極層150には、酸素と結合し易い導電材料を用いることができる。例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどを用いることができる。後のプロセス温度が比較的高くできることなどから、融点の高いWを用いることが特に好ましい。なお、酸素と結合し易い導電材料には、酸素が拡散し易い材料も含まれる。

#### 【0075】

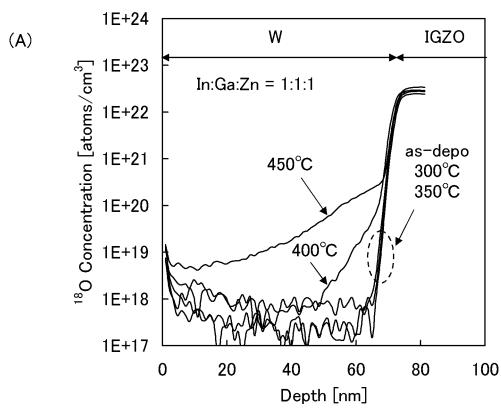

酸素と結合し易い導電材料と酸化物半導体層を接触させると、酸化物半導体層中の酸素が、酸素と結合し易い導電材料側に拡散する現象が起こる。例えば、図19(A)、(B)はスパッタ法でIn-Ga-Zn酸化物膜(以降、IGZO膜ともいう)およびタンゲステン膜の積層サンプルを形成し、酸素同位体( $^{18}\text{O}$ )の深さ方向のプロファイルを熱処理前後でSIMS分析した結果である。なお、IGZO膜はIn:Ga:Zn=1:1:1または1:3:2(原子数比)をスパッタターゲットとし、Ar:O<sub>2</sub>( $^{18}\text{O}$ )=2:1(流量比)をスパッタガスとして用いてDCスパッタ法で形成している。また、タンゲステン膜は、金属Wをスパッタターゲットとし、Ar 100%をスパッタガスとしてDCスパッタ法で形成している。なお、熱処理は、300、350、400、450の各1時間で行い、熱処理無しサンプルを含めて計5サンプルで比較を行った。図19に示すように、熱処理温度が高くなると酸化物半導体層中の酸素がタンゲステン膜に拡散していることがわかる。

#### 【0076】

トランジスタの作製工程には、いくつかの加熱工程があることから、上記現象により、酸化物半導体層のソース電極層およびドレイン電極層と接触した近傍の領域に酸素欠損が発生し、当該領域はn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

#### 【0077】

しかしながら、チャネル長が極短いトランジスタを形成する場合、上記酸素欠損の発生によってn型化した領域がトランジスタのチャネル長方向に延在してしまうことがある。この場合、トランジスタの電気特性には、しきい値電圧のシフトやゲート電圧でオンオフの制御ができない状態(導通状態)が現れる。そのため、チャネル長が極短いトランジスタを形成する場合は、ソース電極層およびドレイン電極層に酸素と結合し易い導電材料を用いることは好ましくない。

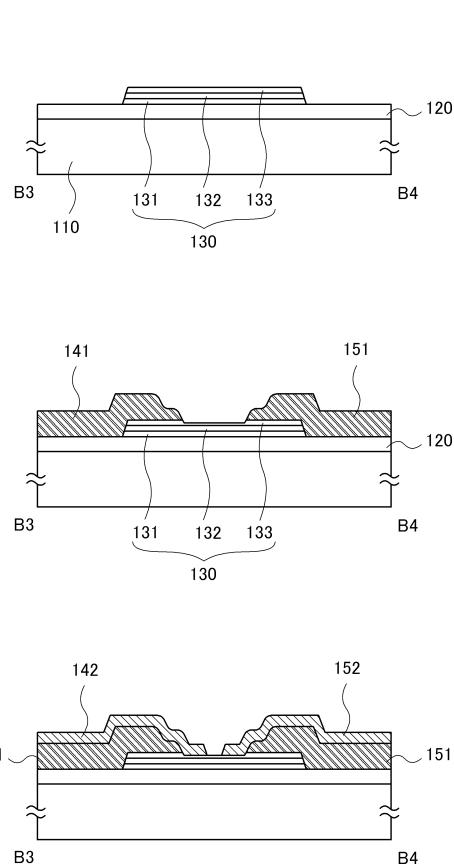

#### 【0078】

したがって、図7(A)、(B)、(C)に示すトランジスタ101のようにソース電極層およびドレイン電極層を積層としてもよい。図7(A)は上面図であり、図7(A)に示す一点鎖線B1-B2の断面が図7(B)に相当する。また、図7(A)に示す一点鎖線B3-B4の断面が図7(C)に相当する。また、一点鎖線B1-B2方向をチャネル幅方向、一点鎖線B3-B4方向をチャネル長方向と呼称する場合がある。第1のソース電極層141および第1のドレイン電極層151には、上述したタンゲステン膜を用い、チャネル長を定める第2のソース電極層142および第2のドレイン電極層152には、酸素と結合しにくい導電材料を用いる。当該導電材料としては、例えば、窒化タンタル、窒化チタン、ルテニウムなどを用いることが好ましい。なお、酸素と結合しにくい導電材料には、酸素が拡散しにくい材料も含まれる。

10

20

30

40

50

## 【0079】

図20(A)、(B)はスパッタ法でIGZO膜および窒化タンタル膜の積層サンプルを形成し、酸素同位体( $^{18}\text{O}$ )の深さ方向のプロファイルを熱処理前後でSIMS分析した結果である。また、図21(A)、(B)はスパッタ法でIGZO膜および窒化チタン膜の積層サンプルを形成し、酸素同位体( $^{18}\text{O}$ )の深さ方向のプロファイルを熱処理前後でSIMS分析した結果である。

## 【0080】

IGZO膜はIn:Ga:Zn = 1:1:1または1:3:2(原子数比)をスパッタターゲットとし、Ar:O<sub>2</sub>( $^{18}\text{O}$ ) = 2:1(流量比)をスパッタガスとして用いてDCスパッタ法で形成している。また、窒化タンタル膜は、金属Taをスパッタターゲットとし、Ar:N<sub>2</sub> = 5:1(流量比)をスパッタガスとして反応性スパッタ法(DCスパッタ法)で形成し、窒化チタン膜は、金属Tiをスパッタターゲットとし、N<sub>2</sub> 100%をスパッタガスとして反応性スパッタ法(DCスパッタ法)で形成している。なお、熱処理は、300、350、400、450の各1時間で行い、熱処理無しサンプルを含めて計5サンプルで比較を行っている。

## 【0081】

いずれのサンプルにおいても、窒化タンタル中または窒化チタン膜中への酸素拡散は確認されず、図19(A)、(B)に示したタンゲステン膜を用いたサンプルとは異なった挙動を示した。したがって、窒化タンタル膜および窒化チタン膜は酸素と結合しにくい膜、または酸素が拡散しにくい膜ということができる。

## 【0082】

なお、図7の構造のトランジスタにおいて、チャネル長とは、第2のソース電極層142と第2のドレイン電極層152の間隔のことをいう。

## 【0083】

また、図7の構造のトランジスタにおいて、チャネルとは、第2のソース電極層142と第2のドレイン電極層152の間ににおける第2の酸化物半導体層132のことをいう。

## 【0084】

また、図7の構造のトランジスタにおいて、チャネル形成領域とは、第2のソース電極層142と第2のドレイン電極層152の間ににおける第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133のことをいう。

## 【0085】

上記酸素と結合しにくい導電材料を第2のソース電極層142および第2のドレイン電極層152に用いることによって、酸化物半導体層に形成されるチャネル形成領域に酸素欠損が形成されることを抑制することができ、チャネルのn型化を抑えることができる。したがって、チャネル長が極短いトランジスタであっても良好な電気特性を得ることができる。

## 【0086】

なお、上記酸素と結合しにくい導電材料のみでソース電極層およびドレイン電極層を形成すると、酸化物半導体層130とのコンタクト抵抗が高くなりすぎることから、図7(C)に示すように、第1のソース電極層141および第1のドレイン電極層151を酸化物半導体層130上に形成し、第1のソース電極層141および第1のドレイン電極層151を覆うように第2のソース電極層142および第2のドレイン電極層152を形成することが好ましい。

## 【0087】

このとき、第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130との接触面積を大として、第2のソース電極層142および第2のドレイン電極層152と酸化物半導体層130との接触面積は小とすることが好ましい。第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130の接触した領域は、酸素欠損の生成によってn型化した領域となる。該n型化した領域により第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130のコンタクト

10

20

30

40

50

抵抗を下げることができる。したがって、第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130の接触面積を大とすることで、n型化した領域の面積も大とすることが可能となる。

【0088】

ただし、第2のソース電極層142および第2のドレイン電極層152に窒化タンタルや窒化チタンなどの窒化物を用いる場合は第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130との接触面積を大とする必要はない。窒化物中の窒素が酸化物半導体層130との界面近傍に僅かに拡散し、酸化物半導体層130中で窒素がドナーとして作用してn型領域を形成し、コンタクト抵抗を低下させることができる。

【0089】

ここで、第1のソース電極層141と第1のドレイン電極層151との間隔L1は、0.8μm以上、好ましくは1.0μm以上とする。L1が0.8μmより小さいとチャネル形成領域において発生する酸素欠損の影響を排除できなくなり、トランジスタの電気特性が低下してしまう。

【0090】

一方、第2のソース電極層142と第2のドレイン電極層152との間隔L2は、例えば、30nm以下としても良好なトランジスタの電気特性を得ることができる。

【0091】

また、ゲート-ドレイン間およびゲート-ソース間の寄生容量を小さくし、半導体装置の周波数特性を向上させるため、ゲート電極層とソース電極層またはドレイン電極層とが極力重ならない構造とすることが好ましい。

【0092】

また、図1に示すソース電極層140およびドレイン電極層150の端部、図7に示す第1のソース電極層141および第1のドレイン電極層151の端部は、階段状に複数の段を設けた形状とすることが好ましい。このような複数の段を設けた形状とすることで、それらの上方に形成される膜の被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。

【0093】

ゲート絶縁膜160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、ゲート絶縁膜160は上記材料の積層であってもよい。

【0094】

第1のゲート電極層171、第2のゲート電極層172、第3のゲート電極層173は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、TaおよびWなどの導電膜を用いることができる。また、それぞれのゲート電極層は、上記材料の積層であってもよい。

【0095】

第1のゲート電極層171、第2のゲート電極層172、第3のゲート電極層173は、それぞれ離間しており、第1のゲート電極層171は、ゲート絶縁膜160を介して酸化物半導体層130と重疊し、第2のゲート電極層172は、ゲート絶縁膜160を介して酸化物半導体層130のチャネル幅方向の一方の端部の一部を覆い、第3のゲート電極層173は、ゲート絶縁膜160を介して酸化物半導体層130のチャネル幅方向の他方の端部の一部を覆っている。

【0096】

低消費電力の半導体装置を形成するには、トランジスタのオフ電流、特にゲート電圧が0V時の電流(I<sub>cut</sub>ともいう)を低減させることが有効である。I<sub>cut</sub>を低減させる方法としては、トランジスタのゲート電極とは活性層を挟んで逆側に電極を設け、当該電極に適切な電位を供給することによりトランジスタのしきい値電圧を制御する、所謂バッ

10

20

30

40

50

クゲート構造が知られている。しかしながら、本発明の一態様のトランジスタのように、活性層が酸化物半導体である場合は、当該酸化物半導体に酸素を供給するための下地絶縁膜として、膜厚の厚い酸化物絶縁層を用いることが適している。そのため、バックゲートの電位を高くしなければならない問題やバックゲートを設けるための工程増加の問題がある。

【0097】

本発明の一態様のトランジスタにおいて、第1のゲート電極層171は、トランジスタのスイッチングを制御し、第2のゲート電極層172および第3のゲート電極層173は、トランジスタのしきい値電圧を制御する。トランジスタの動作において、第1のゲート電極層171にはトランジスタをオンまたはオフする電位が供給され、第2のゲート電極層172および第3のゲート電極層173にはトランジスタのしきい値電圧を制御するための定電位が供給される。第2のゲート電極層172および第3のゲート電極層173には同じ電位が供給されていてもよいし、異なった電位が供給されていてもよい。

10

【0098】

上記のように、バックゲートと同様の効果を有する第2のゲート電極層172および第3のゲート電極層173を第1のゲート電極層171と同じ膜厚の薄いゲート絶縁膜側に形成することでしきい値電圧を供給するための電位を低下させることができる。また、第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173は同時に形成することができ、工程は増加しない。また、下地絶縁膜である酸化物絶縁層を厚く形成することができる。また、第2のゲート電極層172および第3のゲート電極層173の電位が効率良くトランジスタの活性層にかかるようにするため、図5(B)に示すような下地絶縁膜の一部がエッチングされた構造とすることが好ましい。

20

【0099】

したがって、第2のゲート電極層172および第3のゲート電極層173に定電位を供給することでトランジスタのしきい値電圧を制御することができ、 $I_{cut}$ を低減させるとともに半導体装置の長期信頼性を向上させることができる。

【0100】

ゲート絶縁膜160、第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173上には酸化物絶縁層180が形成されていてもよい。当該酸化物絶縁層180には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、当該酸化物絶縁層180は上記材料の積層であってもよい。

30

【0101】

ここで、酸化物絶縁層180は過剰酸素を有することが好ましい。過剰酸素を含む酸化物絶縁層とは、加熱処理などによって酸素を放出することができる酸化物絶縁層をいう。好ましくは、昇温脱離ガス分光法分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{19} \text{ atoms/cm}^3$ 以上である膜とする。当該酸化物絶縁層180から放出される酸素はゲート絶縁膜160を経由して酸化物半導体層130のチャネル形成領域に拡散させることができることから、不本意に形成された酸素欠損に酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。

40

【0102】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

【0103】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0104】

(実施の形態2)

50

本実施の形態では、実施の形態1で説明したトランジスタとは異なる構造のトランジスタについて説明する。

【0105】

図8(A)、(B)、(C)は、本発明の一態様のトランジスタの上面図および断面図である。図8(A)は上面図であり、図8(A)に示す一点鎖線C1-C2の断面が図8(B)に相当する。また、図8(A)に示す一点鎖線C3-C4の断面が図8(C)に相当する。なお、図8(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線C1-C2方向をチャネル幅方向、一点鎖線C3-C4方向をチャネル長方向と呼称する場合がある。

【0106】

図8(A)、(B)、(C)に示すトランジスタ200は、基板110上に形成された下地絶縁膜120、該下地絶縁膜120上に形成された酸化物半導体層130、該酸化物半導体層130上に形成された第2のソース電極層142、第2のドレイン電極層152、該第2のソース電極層142および該第2のドレイン電極層152のそれぞれの上に形成された第1のソース電極層141、第1のドレイン電極層151、該第1のソース電極層141、該第2のソース電極層142、該第1のドレイン電極層151、該第2のドレイン電極層152、および酸化物半導体層130上に形成されたゲート絶縁膜160、該ゲート絶縁膜160上に形成された第1のゲート電極層171、第2のゲート電極層172、第3のゲート電極層173、該ゲート絶縁膜160、該第1のゲート電極層171、該第2のゲート電極層172および該第3のゲート電極層173上に形成された酸化物絶縁層180を有する。なお、酸化物絶縁層180は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

10

【0107】

図7(A)、(B)、(C)に示すトランジスタ101と図8(A)、(B)、(C)に示すトランジスタ200とは、第1のソース電極層141と第2のソース電極層142との積層順序、および第1のドレイン電極層151と第2のドレイン電極層152との積層順序が異なり、その他の点では同じである。また、実施の形態1で説明したトランジスタ100またはトランジスタ101と同じようにトランジスタ200は、第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173を有している。

20

【0108】

トランジスタ200では、酸化物半導体層130と、第1のソース電極層141および第1のドレイン電極層151とが接していないことから、第1のソース電極層141および第1のドレイン電極層151が起因した酸化物半導体層130における酸素欠損の発生は起こらない。そのため、当該酸素欠損によってソースまたはドレインとして作用するn型領域は形成されない。

30

【0109】

トランジスタ200においては、第2のソース電極層142および第2のドレイン電極層152に実施の形態1で説明した導電性の窒化物(窒化タンタルまたは窒化チタン)を用いる。したがって、当該窒化物から酸化物半導体層130の界面近傍にドナーとなる窒素を拡散させることができ、窒素を拡散させた領域をソースまたはドレインとして作用させることができる。なお、窒素はチャネル長方向にも拡散することができ、図示してあるようにチャネル形成領域の一部を取り除くことが好ましい。当該チャネル形成領域の一部は、第2のソース電極層142および第2のドレイン電極層152の形成時のエッチング工程によっても取り除くことができる。なお、窒素は酸化物半導体層130中に深く拡散させる必要はなく、界面近傍に拡散させるのみで十分にソースまたはドレインとして作用させることができる。

40

【0110】

また、トランジスタ200では、第1のソース電極層141および第1のドレイン電極層151が起因した酸化物半導体層130における酸素欠損の発生は起こらないことから、第1のソース電極層141と第1のドレイン電極層151の距離をトランジスタ100よ

50

りも短くすることができる。例えば、第2のソース電極層142の端面と第1のソース電極層141の端面、および第2のドレイン電極層152の端面と第1のドレイン電極層151の端面とを一致させてよい。このようにすることで、ソース電極層およびドレイン電極層全体としての抵抗を低下させることができる。

【0111】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

【0112】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

10

【0113】

(実施の形態3)

本実施の形態では、実施の形態1および実施の形態2で説明したトランジスタとは異なる構造のトランジスタについて説明する。

【0114】

図9(A)、(B)、(C)は、本発明の一態様のトランジスタの上面図および断面図である。図9(A)は上面図であり、図9(A)に示す一点鎖線D1-D2の断面が図9(B)に相当する。また、図9(A)に示す一点鎖線D3-D4の断面が図9(C)に相当する。なお、図9(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線D1-D2方向をチャネル幅方向、一点鎖線D3-D4方向をチャネル長方向と呼称する場合がある。

20

【0115】

図9(A)、(B)、(C)に示すトランジスタ300は、基板110上に形成された下地絶縁膜120、該下地絶縁膜120上に形成された第1の酸化物半導体層131および第2の酸化物半導体層132、該第2の酸化物半導体層132上に形成された第1のソース電極層141、第1のドレイン電極層151、該第2の酸化物半導体層132、該第1のソース電極層141、および該第1のドレイン電極層151上に形成された第3の酸化物半導体層133、第1のソース電極層141を覆うように重畠し、該第1のソース電極層141および第3の酸化物半導体層133のそれぞれと接する第2のソース電極層142、第1のドレイン電極層151を覆うように重畠し、該第1のドレイン電極層151および第3の酸化物半導体層133のそれぞれと接する第2のドレイン電極層152、第3の酸化物半導体層133、第2のソース電極層142、第2のドレイン電極層152上に形成されたゲート絶縁膜160、該ゲート絶縁膜160上に形成された第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173、該ゲート絶縁膜160および該第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173上に形成された酸化物絶縁層180を有する。なお、酸化物絶縁層180は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

30

【0116】

図7(A)、(B)、(C)に示すトランジスタ101と図9(A)、(B)、(C)に示すトランジスタ300とは、第3の酸化物半導体層133が第1のソース電極層141上および第1のドレイン電極層151上に形成されている点が異なり、その他の点は同じである。また、実施の形態1で説明したトランジスタ100またはトランジスタ101と同じようにトランジスタ300は、第1のゲート電極層171、第2のゲート電極層172および第3のゲート電極層173を有している。

40

【0117】

トランジスタ300では、チャネルが形成される第2の酸化物半導体層132と第1のソース電極層141および第1のドレイン電極層151が接しており、第2の酸化物半導体層132に高密度の酸素欠損が生成し、n型領域が形成される。したがって、キャリアのパスに抵抗成分が少なく、効率良くキャリアを移動させることができる。

【0118】

50

また、第3の酸化物半導体層133は、第1のソース電極層141および第1のドレイン電極層151形成後に形成するため、該第1のソース電極層141および該第1のドレイン電極層151形成時の第3の酸化物半導体層133のオーバーエッチングが無い。したがって、チャネルが形成される第2の酸化物半導体層132をゲート絶縁膜160から十分離すことができ、第3の酸化物半導体層133とゲート絶縁膜160との界面からの不純物拡散の影響を抑える効果を大きくすることができる。

【0119】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

【0120】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0121】

(実施の形態4)

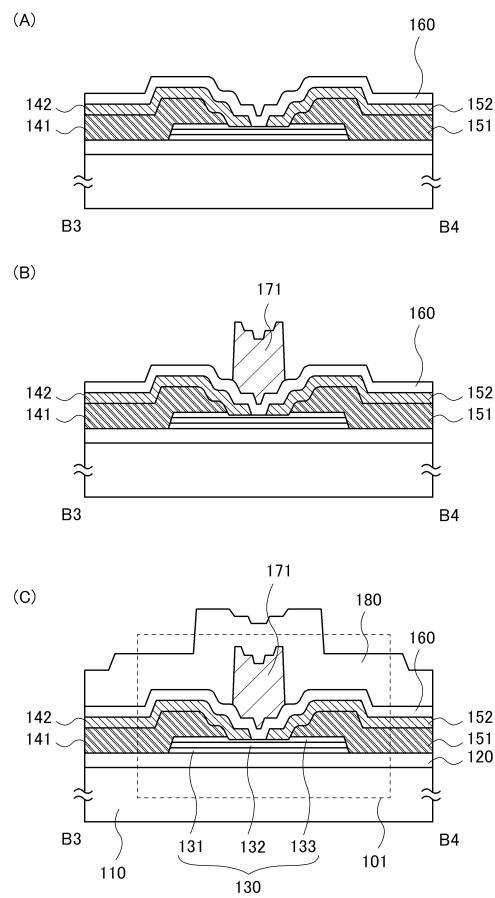

本実施の形態では、実施の形態1で説明した図7に示すトランジスタ101の作製方法について説明する。

【0122】

基板110には、ガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI (Silicon On Insulator) 基板などを用いることも可能であり、これらの基板上に半導体素子が設けられたものを用いてもよい。

【0123】

下地絶縁膜120は、プラズマCVD法またはスパッタ法等により、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いて形成することができる。また、上記材料の積層であってもよく、少なくとも酸化物半導体層130と接する上層は酸化物半導体層130への酸素の供給源となりえる酸素を含む材料で形成することが好ましい。

【0124】

なお、基板110の表面が絶縁体であり、後に設ける酸化物半導体層130への不純物拡散の影響が無い場合は、下地絶縁膜120を設けない構成とすることができる。

【0125】

次に、下地絶縁膜120上に第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133をスパッタ法、CVD法、MBE (Molecular Beam Epitaxy) 法、MOCVD (Metal Organic Chemical Vapor Deposition) 法、ALD (Atomic Layer Deposition) 法またはPLD (Pulse Laser Deposition) 法を用いて成膜し、選択的にエッチングを行うことで酸化物半導体層130を形成する(図10(A)参照)。なお、エッチングの前に加熱工程を行ってもよい。

【0126】

第1の酸化物半導体層131、第2の酸化物半導体層132、および第3の酸化物半導体層133には、実施の形態1で説明した材料を用いることができる。例えば、第1の酸化物半導体層131にIn:Ga:Zn = 1:3:2 [原子数比] のIn-Ga-Zn酸化物、第2の酸化物半導体層132にIn:Ga:Zn = 1:1:1 [原子数比] のIn-Ga-Zn酸化物、第3の酸化物半導体層133にIn:Ga:Zn = 1:3:2 [原子数比] のIn-Ga-Zn酸化物を用いることができる。

【0127】

10

20

30

40

50

また、第1の酸化物半導体層131、第2の酸化物半導体層132、および第3の酸化物半導体層133として用いることのできる酸化物半導体は、少なくともインジウム(Indium)もしくは亜鉛(Zinc)を含むことが好ましい。または、IndiumとZincの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

【0128】

スタビライザーとしては、ガリウム(Gallium)、スズ(Silver)、ハフニウム(Hafnium)、アルミニウム(Aluminum)、またはジルコニウム(Zirconium)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplum)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)等がある。

10

【0129】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、Indium-Zinc酸化物、Silver-Zinc酸化物、Aluminum-Zinc酸化物、Zinc-Magnesium酸化物、Silver-Magnesium酸化物、Indium-Magnesium酸化物、Indium-Gallium-Zinc酸化物、Indium-Aluminum-Zinc酸化物、Indium-Silver-Zinc酸化物、Silver-Gallium-Zinc酸化物、Aluminum-Gallium-Zinc酸化物、Silver-Aluminum-Zinc酸化物、Indium-Hafnium-Zinc酸化物、Indium-Lanthanum-Zinc酸化物、Indium-Cerium-Zinc酸化物、Indium-Praseodymium-Zinc酸化物、Indium-Neodimium-Zinc酸化物、Indium-Samarium-Zinc酸化物、Indium-Europium-Zinc酸化物、Indium-Gadolinium-Zinc酸化物、Indium-Terbium-Zinc酸化物、Indium-Dysprosium-Zinc酸化物、Indium-Holmium-Zinc酸化物、Indium-Erbium-Zinc酸化物、Indium-Triplum-Zinc酸化物、Indium-Lutetium-Zinc酸化物、Indium-Samarium-Gallium-Zinc酸化物、Indium-Hafnium-Gallium-Zinc酸化物、Indium-Aluminum-Gallium-Zinc酸化物、Indium-Silver-Aluminum-Zinc酸化物、Indium-Silver-Hafnium-Zinc酸化物、Indium-Hafnium-Aluminum-Zinc酸化物を用いることができる。

20

【0130】

なお、ここで、例えば、Indium-Gallium-Zinc酸化物とは、IndiumとGalliumとZincを主成分として有する酸化物という意味であり、IndiumとGalliumとZincの比率は問わない。また、IndiumとGalliumとZinc以外の金属元素が入っていてもよい。また、本明細書においては、Indium-Gallium-Zinc酸化物で構成した膜をIGZO膜とも呼ぶ。

30

【0131】

また、 $IndiumMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、Gallium、Iron、ManganeseおよびCobaltから選ばれた一つの金属元素または複数の金属元素を示す。また、 $Indium_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

【0132】

ただし、実施の形態1に詳細を記したように、第1の酸化物半導体層131および第3の酸化物半導体層133は、第2の酸化物半導体層132よりも電子親和力が大きくなるように材料を選択する。

40

【0133】

なお、酸化物半導体膜の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。特に、成膜時に発生するゴミを低減でき、かつ膜厚分布も均一とすることからDCスパッタ法を用いることが好ましい。

【0134】

第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133としてIndium-Gallium-Zinc酸化物を用いる場合、Indium、Gallium、Zincの原子数比としては、例えば、Indium:Gallium:Zinc = 1:1:1、Indium:Gallium:Zinc = 2:2:1、Indium:Gallium:Zinc = 3:1:2、Indium:Gallium:Zinc = 1:3:2、Indium:Gallium:Zinc = 1:4:3、Indium:Gallium:Zinc = 4:1:2、Indium:Gallium:Zinc = 1:2:3、Indium:Gallium:Zinc = 2:3:1、Indium:Gallium:Zinc = 3:2:1、Indium:Gallium:Zinc = 1:1:2、Indium:Gallium:Zinc = 2:1:1、Indium:Gallium:Zinc = 1:2:1、Indium:Gallium:Zinc = 1:1:1、Indium:Gallium:Zinc = 2:2:2、Indium:Gallium:Zinc = 3:3:3、Indium:Gallium:Zinc = 4:4:4、Indium:Gallium:Zinc = 5:5:5、Indium:Gallium:Zinc = 6:6:6、Indium:Gallium:Zinc = 7:7:7、Indium:Gallium:Zinc = 8:8:8、Indium:Gallium:Zinc = 9:9:9、Indium:Gallium:Zinc = 10:10:10、Indium:Gallium:Zinc = 11:11:11、Indium:Gallium:Zinc = 12:12:12、Indium:Gallium:Zinc = 13:13:13、Indium:Gallium:Zinc = 14:14:14、Indium:Gallium:Zinc = 15:15:15、Indium:Gallium:Zinc = 16:16:16、Indium:Gallium:Zinc = 17:17:17、Indium:Gallium:Zinc = 18:18:18、Indium:Gallium:Zinc = 19:19:19、Indium:Gallium:Zinc = 20:20:20、Indium:Gallium:Zinc = 21:21:21、Indium:Gallium:Zinc = 22:22:22、Indium:Gallium:Zinc = 23:23:23、Indium:Gallium:Zinc = 24:24:24、Indium:Gallium:Zinc = 25:25:25、Indium:Gallium:Zinc = 26:26:26、Indium:Gallium:Zinc = 27:27:27、Indium:Gallium:Zinc = 28:28:28、Indium:Gallium:Zinc = 29:29:29、Indium:Gallium:Zinc = 30:30:30、Indium:Gallium:Zinc = 31:31:31、Indium:Gallium:Zinc = 32:32:32、Indium:Gallium:Zinc = 33:33:33、Indium:Gallium:Zinc = 34:34:34、Indium:Gallium:Zinc = 35:35:35、Indium:Gallium:Zinc = 36:36:36、Indium:Gallium:Zinc = 37:37:37、Indium:Gallium:Zinc = 38:38:38、Indium:Gallium:Zinc = 39:39:39、Indium:Gallium:Zinc = 40:40:40、Indium:Gallium:Zinc = 41:41:41、Indium:Gallium:Zinc = 42:42:42、Indium:Gallium:Zinc = 43:43:43、Indium:Gallium:Zinc = 44:44:44、Indium:Gallium:Zinc = 45:45:45、Indium:Gallium:Zinc = 46:46:46、Indium:Gallium:Zinc = 47:47:47、Indium:Gallium:Zinc = 48:48:48、Indium:Gallium:Zinc = 49:49:49、Indium:Gallium:Zinc = 50:50:50、Indium:Gallium:Zinc = 51:51:51、Indium:Gallium:Zinc = 52:52:52、Indium:Gallium:Zinc = 53:53:53、Indium:Gallium:Zinc = 54:54:54、Indium:Gallium:Zinc = 55:55:55、Indium:Gallium:Zinc = 56:56:56、Indium:Gallium:Zinc = 57:57:57、Indium:Gallium:Zinc = 58:58:58、Indium:Gallium:Zinc = 59:59:59、Indium:Gallium:Zinc = 60:60:60、Indium:Gallium:Zinc = 61:61:61、Indium:Gallium:Zinc = 62:62:62、Indium:Gallium:Zinc = 63:63:63、Indium:Gallium:Zinc = 64:64:64、Indium:Gallium:Zinc = 65:65:65、Indium:Gallium:Zinc = 66:66:66、Indium:Gallium:Zinc = 67:67:67、Indium:Gallium:Zinc = 68:68:68、Indium:Gallium:Zinc = 69:69:69、Indium:Gallium:Zinc = 70:70:70、Indium:Gallium:Zinc = 71:71:71、Indium:Gallium:Zinc = 72:72:72、Indium:Gallium:Zinc = 73:73:73、Indium:Gallium:Zinc = 74:74:74、Indium:Gallium:Zinc = 75:75:75、Indium:Gallium:Zinc = 76:76:76、Indium:Gallium:Zinc = 77:77:77、Indium:Gallium:Zinc = 78:78:78、Indium:Gallium:Zinc = 79:79:79、Indium:Gallium:Zinc = 80:80:80、Indium:Gallium:Zinc = 81:81:81、Indium:Gallium:Zinc = 82:82:82、Indium:Gallium:Zinc = 83:83:83、Indium:Gallium:Zinc = 84:84:84、Indium:Gallium:Zinc = 85:85:85、Indium:Gallium:Zinc = 86:86:86、Indium:Gallium:Zinc = 87:87:87、Indium:Gallium:Zinc = 88:88:88、Indium:Gallium:Zinc = 89:89:89、Indium:Gallium:Zinc = 90:90:90、Indium:Gallium:Zinc = 91:91:91、Indium:Gallium:Zinc = 92:92:92、Indium:Gallium:Zinc = 93:93:93、Indium:Gallium:Zinc = 94:94:94、Indium:Gallium:Zinc = 95:95:95、Indium:Gallium:Zinc = 96:96:96、Indium:Gallium:Zinc = 97:97:97、Indium:Gallium:Zinc = 98:98:98、Indium:Gallium:Zinc = 99:99:99、Indium:Gallium:Zinc = 100:100:100、Indium:Gallium:Zinc = 101:101:101、Indium:Gallium:Zinc = 102:102:102、Indium:Gallium:Zinc = 103:103:103、Indium:Gallium:Zinc = 104:104:104、Indium:Gallium:Zinc = 105:105:105、Indium:Gallium:Zinc = 106:106:106、Indium:Gallium:Zinc = 107:107:107、Indium:Gallium:Zinc = 108:108:108、Indium:Gallium:Zinc = 109:109:109、Indium:Gallium:Zinc = 110:110:110、Indium:Gallium:Zinc = 111:111:111、Indium:Gallium:Zinc = 112:112:112、Indium:Gallium:Zinc = 113:113:113、Indium:Gallium:Zinc = 114:114:114、Indium:Gallium:Zinc = 115:115:115、Indium:Gallium:Zinc = 116:116:116、Indium:Gallium:Zinc = 117:117:117、Indium:Gallium:Zinc = 118:118:118、Indium:Gallium:Zinc = 119:119:119、Indium:Gallium:Zinc = 120:120:120、Indium:Gallium:Zinc = 121:121:121、Indium:Gallium:Zinc = 122:122:122、Indium:Gallium:Zinc = 123:123:123、Indium:Gallium:Zinc = 124:124:124、Indium:Gallium:Zinc = 125:125:125、Indium:Gallium:Zinc = 126:126:126、Indium:Gallium:Zinc = 127:127:127、Indium:Gallium:Zinc = 128:128:128、Indium:Gallium:Zinc = 129:129:129、Indium:Gallium:Zinc = 130:130:130、Indium:Gallium:Zinc = 131:131:131、Indium:Gallium:Zinc = 132:132:132、Indium:Gallium:Zinc = 133:133:133、Indium:Gallium:Zinc = 134:134:134、Indium:Gallium:Zinc = 135:135:135、Indium:Gallium:Zinc = 136:136:136、Indium:Gallium:Zinc = 137:137:137、Indium:Gallium:Zinc = 138:138:138、Indium:Gallium:Zinc = 139:139:139、Indium:Gallium:Zinc = 140:140:140、Indium:Gallium:Zinc = 141:141:141、Indium:Gallium:Zinc = 142:142:142、Indium:Gallium:Zinc = 143:143:143、Indium:Gallium:Zinc = 144:144:144、Indium:Gallium:Zinc = 145:145:145、Indium:Gallium:Zinc = 146:146:146、Indium:Gallium:Zinc = 147:147:147、Indium:Gallium:Zinc = 148:148:148、Indium:Gallium:Zinc = 149:149:149、Indium:Gallium:Zinc = 150:150:150、Indium:Gallium:Zinc = 151:151:151、Indium:Gallium:Zinc = 152:152:152、Indium:Gallium:Zinc = 153:153:153、Indium:Gallium:Zinc = 154:154:154、Indium:Gallium:Zinc = 155:155:155、Indium:Gallium:Zinc = 156:156:156、Indium:Gallium:Zinc = 157:157:157、Indium:Gallium:Zinc = 158:158:158、Indium:Gallium:Zinc = 159:159:159、Indium:Gallium:Zinc = 160:160:160、Indium:Gallium:Zinc = 161:161:161、Indium:Gallium:Zinc = 162:162:162、Indium:Gallium:Zinc = 163:163:163、Indium:Gallium:Zinc = 164:164:164、Indium:Gallium:Zinc = 165:165:165、Indium:Gallium:Zinc = 166:166:166、Indium:Gallium:Zinc = 167:167:167、Indium:Gallium:Zinc = 168:168:168、Indium:Gallium:Zinc = 169:169:169、Indium:Gallium:Zinc = 170:170:170、Indium:Gallium:Zinc = 171:171:171、Indium:Gallium:Zinc = 172:172:172、Indium:Gallium:Zinc = 173:173:173、Indium:Gallium:Zinc = 174:174:174、Indium:Gallium:Zinc = 175:175:175、Indium:Gallium:Zinc = 176:176:176、Indium:Gallium:Zinc = 177:177:177、Indium:Gallium:Zinc = 178:178:178、Indium:Gallium:Zinc = 179:179:179、Indium:Gallium:Zinc = 180:180:180、Indium:Gallium:Zinc = 181:181:181、Indium:Gallium:Zinc = 182:182:182、Indium:Gallium:Zinc = 183:183:183、Indium:Gallium:Zinc = 184:184:184、Indium:Gallium:Zinc = 185:185:185、Indium:Gallium:Zinc = 186:186:186、Indium:Gallium:Zinc = 187:187:187、Indium:Gallium:Zinc = 188:188:188、Indium:Gallium:Zinc = 189:189:189、Indium:Gallium:Zinc = 190:190:190、Indium:Gallium:Zinc = 191:191:191、Indium:Gallium:Zinc = 192:192:192、Indium:Gallium:Zinc = 193:193:193、Indium:Gallium:Zinc = 194:194:194、Indium:Gallium:Zinc = 195:195:195、Indium:Gallium:Zinc = 196:196:196、Indium:Gallium:Zinc = 197:197:197、Indium:Gallium:Zinc = 198:198:198、Indium:Gallium:Zinc = 199:199:199、Indium:Gallium:Zinc = 200:200:200、Indium:Gallium:Zinc = 201:201:201、Indium:Gallium:Zinc = 202:202:202、Indium:Gallium:Zinc = 203:203:203、Indium:Gallium:Zinc = 204:204:204、Indium:Gallium:Zinc = 205:205:205、Indium:Gallium:Zinc = 206:206:206、Indium:Gallium:Zinc = 207:207:207、Indium:Gallium:Zinc = 208:208:208、Indium:Gallium:Zinc = 209:209:209、Indium:Gallium:Zinc = 210:210:210、Indium:Gallium:Zinc = 211:211:211、Indium:Gallium:Zinc = 212:212:212、Indium:Gallium:Zinc = 213:213:213、Indium:Gallium:Zinc = 214:214:214、Indium:Gallium:Zinc = 215:215:215、Indium:Gallium:Zinc = 216:216:216、Indium:Gallium:Zinc = 217:217:217、Indium:Gallium:Zinc = 218:218:218、Indium:Gallium:Zinc = 219:219:219、Indium:Gallium:Zinc = 220:220:220、Indium:Gallium:Zinc = 221:221:221、Indium:Gallium:Zinc = 222:222:222、Indium:Gallium:Zinc = 223:223:223、Indium:Gallium:Zinc = 224:224:224、Indium:Gallium:Zinc = 225:225:225、Indium:Gallium:Zinc = 226:226:226、Indium:Gallium:Zinc = 227:227:227、Indium:Gallium:Zinc = 228:228:228、Indium:Gallium:Zinc = 229:229:229、Indium:Gallium:Zinc = 230:230:230、Indium:Gallium:Zinc = 231:231:231、Indium:Gallium:Zinc = 232:232:232、Indium:Gallium:Zinc = 233:233:233、Indium:Gallium:Zinc = 234:234:234、Indium:Gallium:Zinc = 235:235:235、Indium:Gallium:Zinc = 236:236:236、Indium:Gallium:Zinc = 237:237:237、Indium:Gallium:Zinc = 238:238:238、Indium:Gallium:Zinc = 239:239:239、Indium:Gallium:Zinc = 240:240:240、Indium:Gallium:Zinc = 241:241:241、Indium:Gallium:Zinc = 242:242:242、Indium:Gallium:Zinc = 243:243:243、Indium:Gallium:Zinc = 244:244:244、Indium:Gallium:Zinc = 245:245:245、Indium:Gallium:Zinc = 246:246:246、Indium:Gallium:Zinc = 247:247:247、Indium:Gallium:Zinc = 248:248:248、Indium:Gallium:Zinc = 249:249:249、Indium:Gallium:Zinc = 250:250:250、Indium:Gallium:Zinc = 251:251:251、Indium:Gallium:Zinc = 252:252:252、Indium:Gallium:Zinc = 253:253:253、Indium:Gallium:Zinc = 254:254:254、Indium:Gallium:Zinc = 255:255:255、Indium:Gallium:Zinc = 256:256:256、Indium:Gallium:Zinc = 257:257:257、Indium:Gallium:Zinc = 258:258:258、Indium:Gallium:Zinc = 259:259:259、Indium:Gallium:Zinc = 260:260:260、Indium:Gallium:Zinc = 261:261:261、Indium:Gallium:Zinc = 262:262:262、Indium:Gallium:Zinc = 263:263:263、Indium:Gallium:Zinc = 264:264:264、Indium:Gallium:Zinc = 265:265:265、Indium:Gallium:Zinc = 266:266:266、Indium:Gallium:Zinc = 267:267:267、Indium:Gallium:Zinc = 268:268:268、Indium:Gallium:Zinc = 269:269:269、Indium:Gallium:Zinc = 270:270:270、Indium:Gallium:Zinc = 271:271:271、Indium:Gallium:Zinc = 272:272:272、Indium:Gallium:Zinc = 273:273:273、Indium:Gallium:Zinc = 274:274:274、Indium:Gallium:Zinc = 275:275:275、Indium:Gallium:Zinc = 276:276:276、Indium:Gallium:Zinc = 277:277:277、Indium:Gallium:Zinc = 278:278:278、Indium:Gallium:Zinc = 279:279:279、Indium:Gallium:Zinc = 280:280:280、Indium:Gallium:Zinc = 281:281:281、Indium:Gallium:Zinc = 282:282:282、Indium:Gallium:Zinc = 283:283:283、Indium:Gallium:Zinc = 284:284:284、Indium:Gallium:Zinc = 285:285:285、Indium:Gallium:Zinc = 286:286:286、Indium:Gallium:Zinc = 287:287:287、Indium:Gallium:Zinc = 288:288:288、Indium:Gallium:Zinc = 289:289:289、Indium:Gallium:Zinc = 290:290:290、Indium:Gallium:Zinc = 291:291:291、Indium:Gallium:Zinc = 292:292:292、Indium:Gallium:Zinc = 293:293:293、Indium:Gallium:Zinc = 294:294:294、Indium:Gallium:Zinc = 295:295:295、Indium:Gallium:Zinc = 296:296:296、Indium:Gallium:Zinc = 297:297:297、Indium:Gallium:Zinc = 298:298:298、Indium:Gallium:Zinc = 299:299:299、Indium:Gallium:Zinc = 300:300:300、Indium:Gallium:Zinc = 301:301:301、Indium:Gallium:Zinc = 302:302:302、Indium:Gallium:Zinc = 303:303:303、Indium:Gallium:Zinc = 304:304:304、Indium:Gallium:Zinc = 305:305:305、Indium:Gallium:Zinc = 306:306:306、Indium:Gallium:Zinc = 307:307:307、Indium:Gallium:Zinc = 308:308:308、Indium:Gallium:Zinc = 309:309:309、Indium:Gallium:Zinc = 310:310:310、Indium:Gallium:Zinc = 311:311:311、Indium:Gallium:Zinc = 312:312:312、Indium:Gallium:Zinc = 313:313:313、Indium:Gallium:Zinc = 314:314:314、Indium:Gallium:Zinc = 315:315:315、Indium:Gallium:Zinc = 316:316:316、Indium:Gallium:Zinc = 317:317:317、Indium:Gallium:Zinc = 318:318:318、Indium:Gallium:Zinc = 319:319:319、Indium:Gallium:Zinc = 320:320:320、Indium:Gallium:Zinc = 321:321:321、Indium:Gallium:Zinc = 322:322:322、Indium:Gallium:Zinc = 323:323:323、Indium:Gallium:Zinc = 324:324:324、Indium:Gallium:Zinc = 325:325:325、Indium:Gallium:Zinc = 326:326:326、Indium:Gallium:Zinc = 327:327:327、Indium:Gallium:Zinc = 328:328:328、Indium:Gallium:Zinc = 329:329:329、Indium:Gallium:Zinc = 330:330:330、Indium:Gallium:Zinc = 331:331:331、Indium:Gallium:Zinc = 332:332:332、Indium:Gallium:Zinc = 333:333:333、Indium:Gallium:Zinc = 334:334:334、Indium:Gallium:Zinc = 335:335:335、Indium:Gallium:Zinc = 336:336:336、Indium:Gallium:Zinc = 337:337:337、Indium:Gallium:Zinc = 338:338:338、Indium:Gallium:Zinc = 339:339:339、Indium:Gallium:Zinc = 340:340:340、Indium:Gallium:Zinc = 341:341:341、Indium:Gallium:Zinc = 342:342:342、Indium:Gallium:Zinc = 343:343:343、Indium:Gallium:Zinc = 344:344:344、Indium:Gallium:Zinc = 345:345:345、Indium:Gallium:Zinc = 346:346:346、Indium:Gallium:Zinc = 347:347:347、Indium:Gallium:Zinc = 348:348:348、Indium:Gallium:Zinc = 349:349:349、Indium:Gallium:Zinc = 350:350:350、Indium:Gallium:Zinc = 351:351:351、Indium:Gallium:Zinc = 352:352:352、Indium:Gallium:Zinc = 353:353:353、Indium:Gallium:Zinc = 354:354:354、Indium:Gallium:Zinc = 355:355:355、Indium:Gallium:Zinc = 356:356:356、Indium:Gallium:Zinc = 357:357:357、Indium:Gallium:Zinc = 358:358:358、Indium:Gallium:Zinc = 359:359:359、Indium:Gallium:Zinc = 360:360:360、Indium:Gallium:Zinc = 361:361:361、Indium:Gallium:Zinc = 362:362:362、Indium:Gallium:Zinc = 363:363:363、Indium:Gallium:Zinc = 364:364:364、Indium:Gallium:Zinc = 365:365:365、Indium:Gallium:Zinc = 366:366:366、Indium:Gallium:Zinc = 367:367:367、Indium:Gallium:Zinc = 368:368:368、Indium:Gallium:Zinc = 369:369:369、Indium:Gallium:Zinc = 370:370:370、Indium:Gallium:Zinc = 371:371:371、Indium:Gallium:Zinc = 372:372:372、Indium:Gallium:Zinc = 373:373:373、Indium:Gallium:Zinc = 374:374:374、Indium:Gallium:Zinc = 375:375:375、Indium:Gallium:Zinc = 376:376:376、Indium:Gallium:Zinc = 377:377:377、Indium:Gallium:Zinc = 378:378:378、Indium:Gallium:Zinc = 379:379:379、Indium:Gallium:Zinc = 380:380:380、Indium:Gallium:Zinc = 381:381:381、Indium:Gallium:Zinc = 382:382:382、Indium:Gallium:Zinc = 383:383:383、Indium:Gallium:Zinc = 384:384:384、Indium:Gallium:Zinc = 385:385:385、Indium:Gallium:Zinc = 386:386:386、Indium:Gallium:Zinc = 387:387:387、Indium:Gallium:Zinc = 388:388:388、Indium:Gallium:Zinc = 389:389:389、Indium:Gallium:Zinc = 390:390:390、Indium:Gallium:Zinc = 391:391:391、Indium:Gallium:Zinc = 392:392:392、Indium:Gallium:Zinc = 393:393:393、Indium:Gallium:Zinc = 394:394:394、Indium:Gallium:Zinc = 395:395:395、Indium:Gallium:Zinc = 396:396:396、Indium:Gallium:Zinc = 397:397:397、Indium:Gallium:Zinc = 398:398:398、Indium:Gallium:Zinc = 399:399:399、Indium:Gallium:Zinc = 400:400:400、Indium:Gallium:Zinc = 401:401:401、Indium:Gallium:Zinc = 402:402:402、Indium:Gallium:Zinc = 403:403:403、Indium:Gallium:Zinc =

$n : Ga : Zn = 1 : 5 : 4$ 、 $In : Ga : Zn = 1 : 6 : 6$ 、 $In : Ga : Zn = 2 : 1 : 3$ 、 $In : Ga : Zn = 1 : 6 : 4$ 、 $In : Ga : Zn = 1 : 9 : 6$ 、 $In : Ga : Zn = 1 : 1 : 4$ 、 $In : Ga : Zn = 1 : 1 : 2$ のいずれかの材料を用い、第1の酸化物半導体層131および第3の酸化物半導体層133の電子親和力が第2の酸化物半導体層132よりも大きくなるようにすればよい。

#### 【0135】

なお、例えば、 $In$ 、 $Ga$ 、 $Zn$ の原子数比が $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ ) である酸化物の組成が、原子数比が $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ ) の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$ が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 \leq r^2$  を満たすことをいう。 $r$ としては、例えば、0.05とすればよい。他の酸化物でも同様である。

#### 【0136】

また、第2の酸化物半導体層132は、第1の酸化物半導体層131および第3の酸化物半導体層133よりもインジウムの含有量を多くするとよい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、 $In$ の含有率を多くすることにより、より多くのs軌道が重なるため、 $In$ が $Ga$ よりも多い組成となる酸化物は $In$ が $Ga$ と同等または少ない組成となる酸化物と比較して移動度が高くなる。そのため、第2の酸化物半導体層132にインジウムの含有量が多い酸化物を用いることで、高い移動度のトランジスタを実現することができる。

#### 【0137】

以下では、酸化物半導体膜の構造について説明する。

#### 【0138】

なお、本明細書において、「平行」とは、二つの直線が $-10^\circ$ 以上 $10^\circ$ 以下の角度で配置されている状態をいう。従って、 $-5^\circ$ 以上 $5^\circ$ 以下の場合も含まれる。また、「垂直」とは、二つの直線が $80^\circ$ 以上 $100^\circ$ 以下の角度で配置されている状態をいう。従って、 $85^\circ$ 以上 $95^\circ$ 以下の場合も含まれる。

#### 【0139】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0140】

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜などをいう。

#### 【0141】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

#### 【0142】

微結晶酸化物半導体膜は、例えば、 $1\text{ nm}$ 以上 $10\text{ nm}$ 未満の大きさの微結晶(ナノ結晶ともいう。)を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

#### 【0143】

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が $100\text{ nm}$ 未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一辺が $10\text{ nm}$ 未満、 $5\text{ nm}$ 未満または $3\text{ nm}$ 未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-OS膜について詳細な説明を行う。

10

20

30

40

50

## 【0144】

C AAC - OS 膜を透過型電子顕微鏡 (TEM: Transmission Electron Microscope) によって観察すると、結晶部同士の明確な境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することができない。そのため、AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0145】

C AAC - OS 膜を、試料面と概略平行な方向から TEM によって観察 (断面 TEM 観察) すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、AAC - OS 膜の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、AAC - OS 膜の被形成面または上面と平行に配列する。

10

## 【0146】

一方、AAC - OS 膜を、試料面と概略垂直な方向から TEM によって観察 (平面 TEM 観察) すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

## 【0147】

断面 TEM 観察および平面 TEM 観察より、AAC - OS 膜の結晶部は配向性を有していることがわかる。

## 【0148】

C AAC - OS 膜に対し、X線回折 (XRD: X - Ray Diffraction) 装置を用いて構造解析を行うと、例えば  $InGaZnO_4$  の結晶を有する AAC - OS 膜の out-of-plane 法による解析では、回折角 ( $2\theta$ ) が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$  の結晶の (009) 面に帰属されることから、AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

20

## 【0149】

一方、AAC - OS 膜に対し、c 軸に概略垂直な方向から X 線を入射させる in - plane 法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$  の結晶の (110) 面に帰属される。 $InGaZnO_4$  の単結晶酸化物半導体膜であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、(110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、AAC - OS 膜の場合は、 $2\theta$  を  $56^\circ$  近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

30

## 【0150】

以上のことから、AAC - OS 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

## 【0151】

なお、結晶部は、AAC - OS 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、AAC - OS 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、AAC - OS 膜の形状をエッティングなどによって変化させた場合、結晶の c 軸が AAC - OS 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

40

## 【0152】

また、AAC - OS 膜中の結晶化度が均一でなくてもよい。例えば、AAC - OS 膜の結晶部が、AAC - OS 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、AAC - OS 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

50

## 【0153】

なお、 $\text{InGaZnO}_4$  の結晶を有する CAAc - OS 膜の out - of - plane 法による解析では、2θ が 31° 近傍のピークの他に、2θ が 36° 近傍にもピークが現れる場合がある。2θ が 36° 近傍のピークは、CAAc - OS 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。CAAc - OS 膜は、2θ が 31° 近傍にピークを示し、2θ が 36° 近傍にピークを示さないことが好ましい。

## 【0154】

CAAc - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

## 【0155】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAAc - OS 膜のうち、二種以上を有する積層膜であってもよい。

10

## 【0156】

また、CAAc - OS 膜を成膜するために、以下の条件を適用することが好ましい。

## 【0157】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物を低減すればよい。具体的には、露点が -80 以下、好ましくは -100 以下である成膜ガスを用いる。

## 【0158】

20

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタ粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタ粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタ粒子の平らな面が基板に付着する。

## 【0159】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積 % 以上、好ましくは 100 体積 % とする。

## 【0160】

30

スパッタ用ターゲットの一例として、 $\text{In}_x\text{Ga}_y\text{Zn}_z\text{O}$  化合物ターゲットについて以下に示す。

## 【0161】

$\text{InO}_x$  粉末、 $\text{GaO}_y$  粉末および $\text{ZnO}_z$  粉末を所定のモル数で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理することで多結晶である  $\text{In}_x\text{Ga}_y\text{Zn}_z\text{O}$  化合物ターゲットとする。なお、X、Y および Z は任意の正数である。ここで、粉末の種類、およびその混合するモル数比は、作製するスパッタ用ターゲットによって適宜変更すればよい。

## 【0162】

40

次に、第 1 の加熱処理を行うことが好ましい。第 1 の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。また、第 1 の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。第 1 の加熱処理によって、第 2 の酸化物半導体層 132 の結晶性を高め、さらに下地絶縁膜 120、第 1 の酸化物半導体層 131、および第 3 の酸化物半導体層 133 から水素や水などの不純物を除去することができる。なお、酸化物半導体層 130 を形成するエッチングの前に第 1 の加熱工程を行ってもよい。

## 【0163】

次に、酸化物半導体層 130 上に第 1 のソース電極層 141 および第 1 のドレイン電極層 151 となる第 1 の導電膜を形成する。第 1 の導電膜としては、Al、Cr、Cu、Ta

50

、Ti、Mo、W、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法、CVD法、MBE法、MOCVD法、ALD法またはPLD法などにより100nmのタンゲステン膜を形成する。

【0164】

次に、第1の導電膜を酸化物半導体層130上で分断するようにエッチングし、第1のソース電極層141および第1のドレイン電極層151を形成する(図10(B)参照)。このとき、第1のソース電極層141および第1のドレイン電極層151の端部は図10(A)および図10(C)に示すように階段状に形成する。当該端部の加工は、アッシングによってレジストマスクを後退させる工程とエッチングの工程を交互に複数回行うことで形成することができる。

10

【0165】

このとき、第1の導電膜のオーバーエッチングによって、図示したように酸化物半導体層130の一部がエッチングされた形状となる。ただし、第1の導電膜と酸化物半導体層130のエッチングの選択比が大きい場合は、酸化物半導体層130がほとんどエッチングされない形状となる。

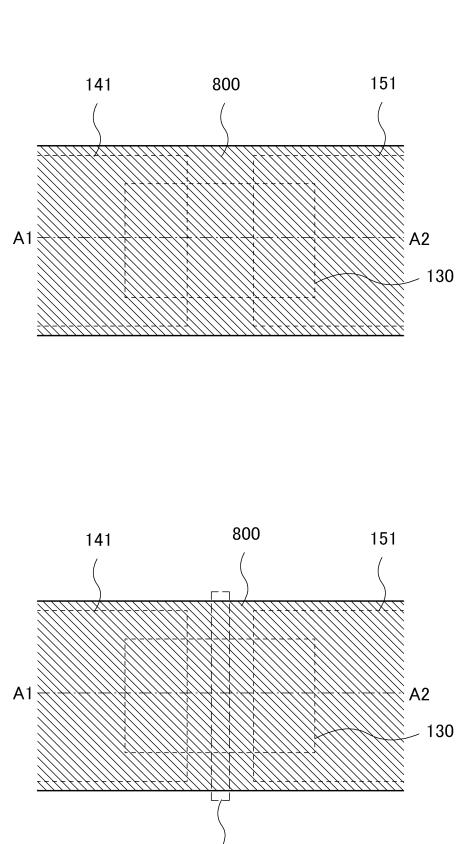

【0166】

次に、酸化物半導体層130、第1のソース電極層141および第1のドレイン電極層151上に、第2のソース電極層142および第2のドレイン電極層152となる第2の導電膜800を形成する。第2の導電膜としては、窒化タンタル、窒化チタン、ルテニウム、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法、CVD法、MBE法、MOCVD法、ALD法またはPLD法などにより20nmの窒化タンタル膜を形成する。

20

【0167】

次に、第2の導電膜800を酸化物半導体層130上で分断するようにエッチングし、第2のソース電極層142および第2のドレイン電極層152を形成する(図10(C)参照)。このとき、酸化物半導体層130の一部がエッチングされてもよい。

【0168】

なお、チャネル長(第2のソース電極層142と第2のドレイン電極層152との間)が極短いトランジスタを形成する場合は、図12(A)に示す上面図のように、まず、第1のソース電極層141および第1のドレイン電極層151を覆うような形状に第2の導電膜800をエッチングする。なお、第2の導電膜800は、酸化物半導体層130の近傍で第1のソース電極層141および第1のドレイン電極層151と重畳していればよい。

30

【0169】

そして、図12(B)に示す第2の導電膜800を分断する領域400に対して、電子ビーム露光などの細線加工に適した方法を用いてレジストマスク加工を行い、エッチング工程によって領域400をエッチングし、第2のソース電極層142および第2のドレイン電極層152を形成する。なお、当該レジストマスクとしては、ポジ型レジストを用いれば、露光領域を最小限にすることができる、スループットを向上させることができる。このような方法を用いれば、チャネル長を30nm以下とするトランジスタを形成することができる。

40

【0170】

次に、第2の加熱処理を行うことが好ましい。第2の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第2の加熱処理により、酸化物半導体層130から、さらに水素や水などの不純物を除去することができる。

【0171】

次に、酸化物半導体層130、第2のソース電極層142および第2のドレイン電極層152上にゲート絶縁膜160を形成する(図11(A)参照)。ゲート絶縁膜160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどを用い

50

ることができる。なお、ゲート絶縁膜160は、上記材料の積層であってもよい。ゲート絶縁膜160は、スパッタ法、CVD法、MBE法、MOCVD法、ALD法またはPLD法などを用いて形成することができる。

【0172】

次に、ゲート絶縁膜160上に第1のゲート電極層171、第2のゲート電極層172、第3のゲート電極層173となる第3の導電膜を形成する。第3の導電膜としては、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W、またはこれらを主成分とする合金材料を用いることができる。第3の導電膜は、スパッタ法、CVD法、MBE法、MOCVD法、ALD法またはPLD法などにより形成することができる。そして、チャネル形成領域と重畠し、かつ離間するようにエッチングし、第1のゲート電極層171、第2のゲート電極層172、第3のゲート電極層173を形成する(図11(B)参照)。なお、第2のゲート電極層172および第3のゲート電極層173は図示していない。

10

【0173】

次に、ゲート絶縁膜160、第1のゲート電極層171、第2のゲート電極層172、および第3のゲート電極層173上に酸化物絶縁層180を形成する(図11(C)参照)。酸化物絶縁層180は、下地絶縁膜120と同様の材料、方法を用いて形成することができる。酸化物絶縁層180としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタル、もしくは窒素を含む酸化物絶縁層を用いるとよい。酸化物絶縁層180は、スパッタ法、CVD法、MBE法、MOCVD法、ALD法またはPLD法を用いて形成することができ、酸化物半導体層130に対し酸素を供給できるよう過剰に酸素を含む膜とすることが好ましい。

20

【0174】

また、酸化物絶縁層180にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加してもよい。酸素を添加することによって、酸化物絶縁層180から酸化物半導体層130への酸素の供給をさらに容易にすることができる。

30

【0175】

次に、第3の加熱処理を行うことが好ましい。第3の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第3の加熱処理により、下地絶縁膜120、ゲート絶縁膜160、酸化物絶縁層180から過剰酸素が放出されやすくなり、酸化物半導体層130の酸素欠損を低減することができる。

【0176】

以上の工程で、図7に示すトランジスタ101を作製することができる。

【0177】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0178】

40

(実施の形態5)

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を、図面を用いて説明する。

【0179】

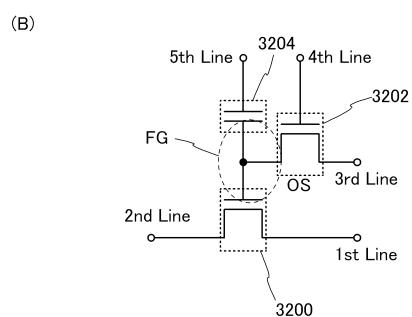

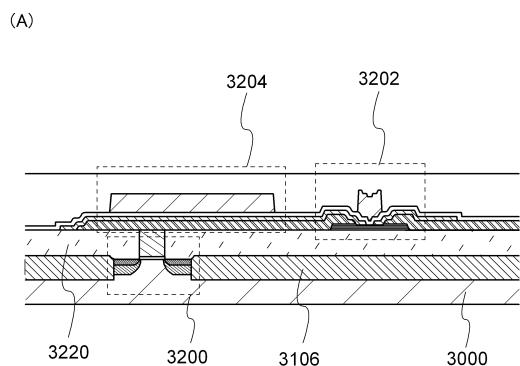

図13(A)に半導体装置の断面図、図13(B)に半導体装置の回路図をそれぞれ示す。

【0180】

図13(A)および図13(B)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ3200を有し、上部に第2の半導体材料を用いたトランジスタ3202お

50

および容量素子3204を有している。なお、トランジスタ3202としては、実施の形態1乃至3で説明したトランジスタを用いることができ、本実施の形態では、実施の形態1の図7に示すトランジスタ101を適用する例を示している。また、容量素子3204は、一方の電極をトランジスタ3202のゲート電極層、他方の電極をトランジスタ3202のソース電極層またはドレイン電極層、誘電体をトランジスタ3202のゲート絶縁膜160と同じ材料を用いる構造とすることで、トランジスタ3202と同時に形成することができる。

#### 【0181】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料（シリコンなど）とし、第2の半導体材料を実施の形態1で説明した酸化物半導体とすることができます。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い電気特性により長時間の電荷保持を可能とする。

#### 【0182】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのではない。また、情報を保持するために酸化物半導体を用いた実施の形態1乃至3に示すようなトランジスタを用いる他は、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

#### 【0183】

図13(A)におけるトランジスタ3200は、半導体材料（例えば、結晶性シリコンなど）を含む基板3000に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、不純物領域に接する金属間化合物領域と、チャネル形成領域上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極層と、を有する。なお、図において、明示的にはソース電極層やドレイン電極層を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極層やドレイン電極層と表現することがある。つまり、本明細書において、ソース電極層との記載には、ソース領域が含まれうる。

#### 【0184】

基板3000上にはトランジスタ3200を囲むように素子分離絶縁層3106が設けられており、トランジスタ3200を覆うように絶縁層3220が設けられている。なお、素子分離絶縁層3106は、LOCOS (Local Oxidation of Silicon) や、STI (Shallow Trench Isolation) などの素子分離技術を用いて形成することができる。

#### 【0185】

例えば、結晶性シリコン基板を用いたトランジスタ3200は、高速動作が可能である。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。トランジスタ3202および容量素子3204の形成前の処理として、トランジスタ3200を覆う絶縁層3220にCMP処理を施して、絶縁層3220を平坦化すると同時にトランジスタ3200のゲート電極層の上面を露出させる。

#### 【0186】

絶縁層3220上にはトランジスタ3202が設けられ、そのソース電極層またはドレイン電極層の一方は延在して、容量素子3204の一方の電極として作用する。

#### 【0187】

図13(A)に示すトランジスタ3202は、酸化物半導体層にチャネルが形成されるトップゲート型トランジスタである。トランジスタ3202は、オフ電流が低いため、これを用いることにより長期にわたり記憶内容を保持することができる。つまり、リフレ

10

20

30

40

50

ツシュー動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

【0188】

また、図示はされていないが、トランジスタ3202には、図面の奥行き方向に酸化物半導体層の端部をゲート絶縁膜を介して覆う第2のゲート電極層および第3のゲート電極層が形成されており、第2のゲート電極層および第3のゲート電極層に適切な電位を供給することで、トランジスタ3202のしきい値電圧を制御することができる。また、トランジスタ3202の長期信頼性を高めることができる。

【0189】

図13(A)に示すように、トランジスタ3200とトランジスタ3202は重畠するように形成することができるため、その占有面積を低減することができる。したがって、半導体装置の集積度を高めることができる。 10

【0190】

次に、図13(A)に対応する回路構成の一例を図13(B)に示す。

【0191】

図13(B)において、第1の配線(1st Line)とトランジスタ3200のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ3200のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ3202のソース電極層またはドレイン電極層の他方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ3202のゲート電極層とは、電気的に接続されている。そして、トランジスタ3200のゲート電極層と、トランジスタ3202のソース電極層またはドレイン電極層の一方は、容量素子3204の電極の他方と電気的に接続され、第5の配線(5th Line)と、容量素子3204の電極の他方は電気的に接続されている。 20

【0192】

図13(B)に示す半導体装置では、トランジスタ3200のゲート電極層の電位が保持可能という特徴を活かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0193】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ3202がオン状態となる電位にして、トランジスタ3202をオン状態とする。これにより、第3の配線の電位が、トランジスタ3200のゲート電極層、および容量素子3204に与えられる。すなわち、トランジスタ3200のゲート電極層には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ3202がオフ状態となる電位にして、トランジスタ3202をオフ状態とすることにより、トランジスタ3200のゲート電極層に与えられた電荷が保持される(保持)。 30

【0194】

トランジスタ3202のオフ電流は極めて低いため、トランジスタ3200のゲート電極層の電荷は長時間にわたって保持される。 40

【0195】

次に情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ3200のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th-H}$ は、トランジスタ3200のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th-L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、 50

第5の配線の電位を $V_{t_h\_H}$ と $V_{t_h\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $> V_{t_h\_H}$ )となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $< V_{t_h\_L}$ )となっても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線の電位を判別することで、保持されている情報を読み出すことができる。

#### 【0196】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{t_h\_H}$ より小さい電位を第5の配線に与えればよい。または、ゲート電極層の状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{t_h\_L}$ より大きい電位を第5の配線に与えればよい。

10

#### 【0197】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて低いトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であつても、長期にわたって記憶内容を保持することが可能である。

20

#### 【0198】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁膜の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。

30

#### 【0199】

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置、および該半導体装置の作製方法を提供することができる。

#### 【0200】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【0201】

##### （実施の形態6）

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態5に示した構成と異なる半導体装置の説明を行う。

40

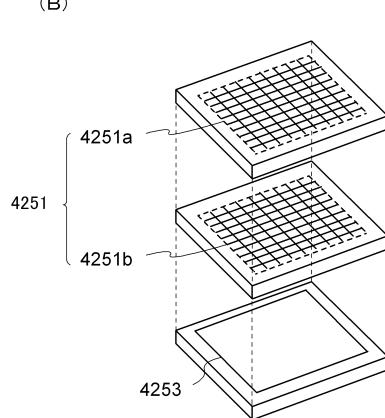

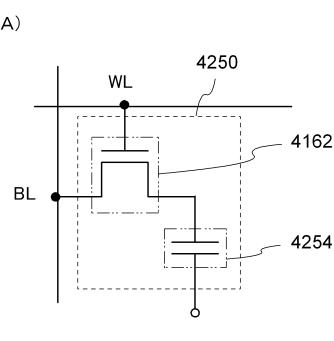

#### 【0202】

図14(A)は、半導体装置の回路構成の一例を示し、図14(B)は半導体装置の一例を示す概念図である。なお、当該半導体装置に含まれるトランジスタ4162としては、実施の形態1乃至3で説明したトランジスタを用いることができる。また、容量素子4254は、実施の形態5で説明した容量素子3204と同様に、トランジスタ4162の作製工程にて同時に作製することができる。

#### 【0203】

図14(A)に示す半導体装置において、ビット線BLとトランジスタ4162のソース電極層とは電気的に接続され、ワード線WLとトランジスタ4162のゲート電極層とは電気的に接続され、トランジスタ4162のドレイン電極層と容量素子4254の第1の

50

端子とは電気的に接続されている。

【0204】

次に、図14(A)に示す半導体装置(メモリセル4250)に、情報の書き込みおよび保持を行う場合について説明する。

【0205】

まず、ワード線WLの電位を、トランジスタ4162がオン状態となる電位として、トランジスタ4162をオフ状態とする。これにより、ビット線BLの電位が、容量素子4254の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ4162がオフ状態となる電位として、トランジスタ4162をオフ状態とすることにより、容量素子4254の第1の端子の電位が保持される(保持)。

10

【0206】

酸化物半導体を用いたトランジスタ4162は、オフ電流が極めて低いという特徴を有している。このため、トランジスタ4162をオフ状態とすることで、容量素子4254の第1の端子の電位(あるいは、容量素子4254に蓄積された電荷)を極めて長時間にわたって保持することが可能である。

【0207】

次に、情報の読み出しについて説明する。トランジスタ4162がオン状態となると、浮遊状態であるビット線BLと容量素子4254とが導通し、ビット線BLと容量素子4254の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子4254の第1の端子の電位(あるいは容量素子4254に蓄積された電荷)によって、異なる値をとる。

20

【0208】

例えば、容量素子4254の第1の端子の電位をV、容量素子4254の容量をC、ビット線BLが有する容量成分(以下、ビット線容量とも呼ぶ)をCB、電荷が再分配される前のビット線BLの電位をVB0とすると、電荷が再分配された後のビット線BLの電位は、 $(CB \times VB0 + C \times V) / (CB + C)$ となる。したがって、メモリセル4250の状態として、容量素子4254の第1の端子の電位がV1とV0( $V1 > V0$ )の2状態をとるとすると、電位V1を保持している場合のビット線BLの電位( $= (CB \times VB0 + C \times V1) / (CB + C)$ )は、電位V0を保持している場合のビット線BLの電位( $= (CB \times VB0 + C \times V0) / (CB + C)$ )よりも高くなることがわかる。

30

【0209】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

【0210】

このように、図14(A)に示す半導体装置は、トランジスタ4162のオフ電流が極めて低いという特徴から、容量素子4254に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。

40

【0211】

次に、図14(B)に示す半導体装置について、説明を行う。

【0212】

図14(B)に示す半導体装置は、上部に記憶回路として図14(A)に示したメモリセル4250を複数有するメモリセルアレイ4251(メモリセルアレイ4251aおよび4251b)を有し、下部に、メモリセルアレイ4251を動作させるために必要な周辺回路4253を有する。なお、周辺回路4253は、メモリセルアレイ4251と電気的に接続されている。

【0213】

図14(B)に示した構成とすることにより、周辺回路4253をメモリセルアレイ42

50

51の直下に設けることができるため半導体装置の小型化を図ることができる。

【0214】

周辺回路4253に設けられるトランジスタは、トランジスタ4162とは異なる半導体材料を用いることが好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることがより好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、該トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することができる。

【0215】

なお、図14(B)に示した半導体装置では、メモリセルアレイ4251がメモリセルアレイ4251aとメモリセルアレイ4251bの積層である構成を例示したが、積層するメモリセルの数はこれに限定されない。3つ以上のメモリセルを積層する構成としても良いし、単層であってもよい。

【0216】

トランジスタ4162は、酸化物半導体を用いて形成されており、実施の形態1乃至3で説明したトランジスタを用いることができる。酸化物半導体を用いたトランジスタは、オフ電流が低いため、長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

10

【0217】

また、酸化物半導体以外の材料を用いたトランジスタ（換言すると、十分な高速動作が可能なトランジスタ）を用いた周辺回路と、酸化物半導体を用いたトランジスタ（より広義には、十分にオフ電流が低いトランジスタ）を用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

20

【0218】

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置を提供することができる。

【0219】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

30

【0220】

（実施の形態7）

本実施の形態では、実施の形態1乃至4で説明したトランジスタを用いることのできる電子機器および電気機器の例について説明する。

【0221】

実施の形態1乃至3で説明したトランジスタは、さまざまな電子機器（遊技機も含む）や電気機器に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、デスクトップ型またはノート型のパーソナルコンピュータ、ワードプロセッサ、DVD(Digital Versatile Disc)などの記録媒体に記憶された静止画または動画を再生する画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ、ステレオ、コードレス電話子機、トランシーバ、携帯電話、自動車電話、携帯型ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、ICチップなどが挙げられる。電気機器としては、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、放射線測定器、透析装置等の医療機器、などが挙げられる。また、電気機器としては、煙感知器、ガス警報装置、防犯警報装置などの警報装置も挙げられる。さらに、電気機器

40

50

としては、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電力貯蔵システム等の産業機器も挙げられる。また、石油を用いたエンジンや、非水系二次電池からの電力を用いて電動機により推進する移動体なども、電気機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車（EV）、内燃機関と電動機を併せ持ったハイブリッド車（HEV）、プラグインハイブリッド車（PHEV）、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型または大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器や電気機器の具体例を図15、図16、図17、および図18に示す。

## 【0222】

10

まず、警報装置の例として火災報知器の構成について説明する。なお、本明細書中にあって、火災報知器とは、火災の発生を急報する装置全般を示すものであり、例えば、住宅用火災警報器や、自動火災報知設備や、当該自動火災報知設備に用いられる火災感知器なども火災報知器に含むものとする。

## 【0223】

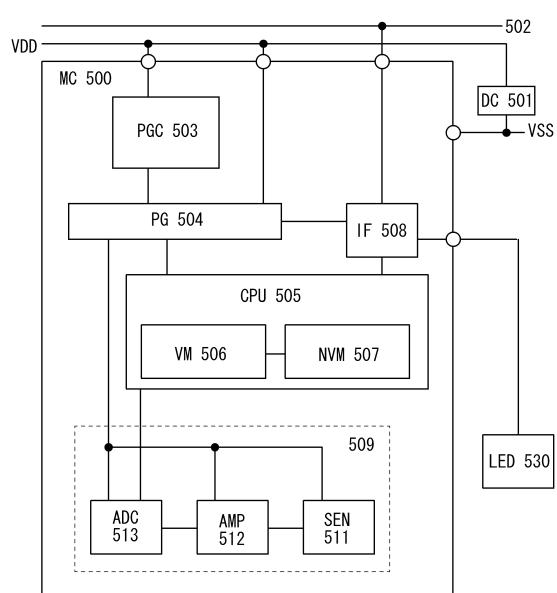

図15に示す警報装置は、マイクロコンピュータ500を少なくとも有する。ここで、マイクロコンピュータ500は、警報装置の内部に設けられている。マイクロコンピュータ500は、高電位電源線VDDと電気的に接続されたパワーゲートコントローラ503と、高電位電源線VDDおよびパワーゲートコントローラ503と電気的に接続されたパワーゲート504と、パワーゲート504と電気的に接続されたCPU(Central Processing Unit)505と、パワーゲート504およびCPU505と電気的に接続された検出部509と、が設けられる。また、CPU505には、揮発性記憶部506と不揮発性記憶部507と、が含まれる。

20

## 【0224】

また、CPU505は、インターフェース508を介してバスライン502と電気的に接続されている。インターフェース508もCPU505と同様にパワーゲート504と電気的に接続されている。インターフェース508のバス規格としては、例えば、I<sup>2</sup>Cバスなどを用いることができる。また、本実施の形態に示す警報装置には、インターフェース508を介してパワーゲート504と電気的に接続される発光素子530が設けられる。

30

## 【0225】

発光素子530は指向性の強い光を放出するものが好ましく、例えば、有機EL素子、無機EL素子、LED(Light Emitting Diode)などを用いることができる。

## 【0226】

パワーゲートコントローラ503はタイマーを有し、当該タイマーに従ってパワーゲート504を制御する。パワーゲート504は、パワーゲートコントローラ503の制御に従って、CPU505、検出部509およびインターフェース508に高電位電源線VDDから供給される電源を供給または遮断する。ここで、パワーゲート504としては、例えば、トランジスタなどのスイッチング素子を用いることができる。

40

## 【0227】

このようなパワーゲートコントローラ503およびパワーゲート504を用いることにより、光量を測定する期間に検出部509、CPU505およびインターフェース508への電源供給を行い、測定期間の合間に検出部509、CPU505およびインターフェース508への電源供給を遮断することができる。このように警報装置を動作させることにより、上記の各構成に常時電源供給を行う場合より消費電力の低減を図ることができる。

## 【0228】

また、パワーゲート504としてトランジスタを用いる場合、不揮発性記憶部507に用いられる、極めてオフ電流の低いトランジスタ、例えば、酸化物半導体を用いたトランジ

50

スタを用いることが好ましい。このようなトランジスタを用いることにより、パワーゲート 504 で電源を遮断する際にリーク電流を低減し、消費電力の低減を図ることができる。

【0229】

本実施の形態に示す警報装置に直流電源 501 を設け、直流電源 501 から高電位電源線 VDD に電源を供給しても良い。直流電源 501 の高電位側の電極は、高電位電源線 VDD と電気的に接続され、直流電源 501 の低電位側の電極は、低電位電源線 VSS と電気的に接続される。ここで、高電位電源線 VDD は、高電位 H が与えられている。また、低電位電源線 VSS は、例えば接地電位 (GND) などの低電位 L が与えられている。

10

【0230】

直流電源 501 として電池を用いる場合は、例えば、高電位電源線 VDD と電気的に接続された電極と、低電位電源線 VSS に電気的に接続された電極と、当該電池を保持することができる筐体と、を有する電池ケースを筐体に設ける構成とすればよい。なお、本実施の形態に示す警報装置は、必ずしも直流電源 501 を設ける必要はなく、例えば、当該警報装置の外部に設けられた交流電源から配線を介して電源を供給する構成としても良い。

【0231】

また、上記電池として、二次電池、例えば、リチウムイオン二次電池（リチウムイオン蓄電池、リチウムイオン電池、またはリチウムイオンバッテリーとも呼ぶ。）を用いることもできる。また、当該二次電池を充電できるように太陽電池を設けることが好ましい。

20

【0232】

検出部 509 は、異常に係る物理量を計測して計測値を CPU 505 に送信する。異常に係る物理量は、警報装置の用途によって異なり、火災報知器として機能する警報装置では、火災に係る物理量を計測する。故に、検出部 509 には、火災に係る物理量として光量を計測し、煙の存在を感知する。

【0233】

検出部 509 は、パワーゲート 504 と電気的に接続された光センサ 511 と、パワーゲート 504 と電気的に接続されたアンプ 512 と、パワーゲート 504 および CPU 505 と電気的に接続された AD コンバータ 513 と、を有する。発光素子 530、および検出部 509 に設けられた光センサ 511、アンプ 512 並びに AD コンバータ 513 は、パワーゲート 504 が検出部 509 に電源を供給したときに動作する。

30

【0234】

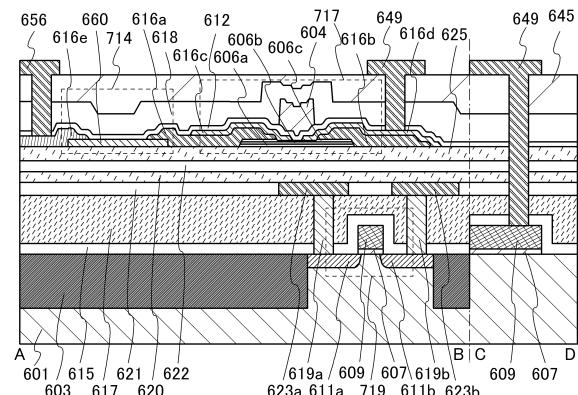

図 16 に警報装置の断面の一部を示す。当該警報装置は、p 型の半導体基板 601 に形成された素子分離領域 603 と、ゲート絶縁膜 607、ゲート電極層 609、n 型の不純物領域 611a、n 型の不純物領域 611b、絶縁膜 615 および絶縁膜 617 を有する n 型のトランジスタ 719 とが形成されている。n 型のトランジスタ 719 は、単結晶シリコンなど、酸化物半導体とは異なる半導体を用いて形成されるため、十分な高速動作が可能となる。これにより、高速アクセスが可能な CPU の揮発性記憶部を形成することができる。

【0235】

40

絶縁膜 615 および絶縁膜 617 の一部を選択的にエッチングした開口部には、コントラクトプラグ 619a およびコントラクトプラグ 619b が形成され、絶縁膜 617、コントラクトプラグ 619a およびコントラクトプラグ 619b 上に溝部を有する絶縁膜 621 が設けられている。

【0236】

絶縁膜 621 の溝部に配線 623a および配線 623b が形成されており、絶縁膜 621、配線 623a および配線 623b 上には、スパッタ法または CVD 法等によって形成された絶縁膜 620 が設けられている。また、当該絶縁膜 620 上に溝部を有する絶縁膜 622 が形成されている。

【0237】

50

絶縁膜 622 上には、スパッタ法またはCVD法等により形成された絶縁膜 625 が設けられており、絶縁膜 625 上には、第2のトランジスタ 717 と、光電変換素子 714 が設けられている。

【0238】

第2のトランジスタ 717 は、第1の酸化物半導体層 606a、第2の酸化物半導体層 606b および第3の酸化物半導体層 606c と、第1の酸化物半導体層 606a、第2の酸化物半導体層 606b および第3の酸化物半導体層 606c に接する第1のソース電極層 616a および第1のドレイン電極層 616b と、第1のソース電極層 616a および第1のドレイン電極層 616b の上部に接する第2のソース電極層 616c および第2のドレイン電極層 616d と、ゲート絶縁膜 612 と、ゲート電極層 604 と、酸化物絶縁層 618 を含む。また、光電変換素子 714 と第2のトランジスタ 717 を覆う絶縁膜 645 が設けられ、絶縁膜 645 上に第2のドレイン電極層 616d に接して配線 649 を有する。配線 649 は、第2のトランジスタ 717 のドレイン電極層とn型のトランジスタ 719 のゲート電極層 609 とを電気的に接続するノードとして機能する。

10

【0239】

ここで、第2のトランジスタ 717 には、実施の形態1乃至3で説明したトランジスタを用いることができ、第1の酸化物半導体層 606a、第2の酸化物半導体層 606b および第3の酸化物半導体層 606c のそれぞれは、実施の形態1で説明した第1の酸化物半導体層 131、第2の酸化物半導体層 132 および第3の酸化物半導体層 133 に相当する。また、第1のソース電極層 616a および第1のドレイン電極層 616b のそれぞれは、実施の形態1で説明した第1のソース電極層 141 および第1のドレイン電極層 151 に相当する。また、第2のソース電極層 616c および第2のドレイン電極層 616d のそれぞれは、実施の形態1で説明した第2のソース電極層 142 および第2のドレイン電極層 152 に相当する。

20

【0240】

また、図示はされていないが、トランジスタ 717 には、図面の奥行き方向に酸化物半導体層の端部をゲート絶縁膜を介して覆う第2のゲート電極層および第3のゲート電極層が形成されており、第2のゲート電極層および第3のゲート電極層に適切な電位を供給することで、トランジスタ 717 のしきい値電圧を制御することができる。また、トランジスタ 717 の長期信頼性を高めることができる。

30

【0241】

光センサ 511 は、光電変換素子 714 と、容量素子と、第1のトランジスタと、第2のトランジスタ 717 と、第3のトランジスタと、n型のトランジスタ 719 と、を含む。ここで光電変換素子 714 としては、例えば、フォトダイオードなどを用いることができる。

【0242】

光電変換素子 714 の端子の一方は、低電位電源線 VSS と電気的に接続され、端子の他方は、第2のトランジスタ 717 の第1のソース電極層 616a もしくは第1のドレイン電極層 616b の一方、および / または第2のソース電極層 616c もしくは第2のドレイン電極層 616d の一方に電気的に接続される。

40

【0243】

第2のトランジスタ 717 のゲート電極層 604 には、電荷蓄積制御信号  $T_x$  が与えられ、第1のソース電極層 616a もしくは第1のドレイン電極層 616b の他方、および / または第2のソース電極層 616c もしくは第2のドレイン電極層 616d の他方は、容量素子の一対の電極の一方、第1のトランジスタのソース電極層およびドレイン電極層の一方、および n型のトランジスタ 719 のゲート電極層と電気的に接続される（以下、当該ノードをノード FD と呼ぶ場合がある）。

【0244】

容量素子の一対の電極の他方は、低電位電源線 VSS と電気的に接続される。第1のトランジスタのゲート電極層は、リセット信号 Res が与えられ、ソース電極層およびドレイ

50

ン電極層の他方は、高電位電源線 V D D と電気的に接続される。

【 0 2 4 5 】

n 型のトランジスタ 7 1 9 のソース電極層およびドレイン電極層の一方は、第 3 のトランジスタのソース電極層およびドレイン電極層の一方と、アンプ 5 1 2 と電気的に接続される。また、n 型のトランジスタ 7 1 9 のソース電極層およびドレイン電極層の他方は、高電位電源線 V D D と電気的に接続される。第 3 のトランジスタのゲート電極層は、バイアス信号 B i a s が与えられ、ソース電極層およびドレイン電極層の他方は、低電位電源線 V S S と電気的に接続される。

【 0 2 4 6 】

なお、容量素子は必ずしも設ける必要はなく、例えば、n 型のトランジスタ 7 1 9 などの寄生容量が十分大きい場合、容量素子を設けない構成としても良い。 10

【 0 2 4 7 】

また、第 1 のトランジスタおよび第 2 のトランジスタ 7 1 7 には、極めてオフ電流の低いトランジスタを用いることが好ましい。また、極めてオフ電流の低いトランジスタとしては、酸化物半導体を含むトランジスタを用いることが好ましい。このような構成とすることによりノード F D の電位を長時間保持することが可能となる。

【 0 2 4 8 】

また、図 1 6 に示す構成は、第 2 のトランジスタ 7 1 7 と電気的に接続して、絶縁膜 6 2 5 上に光電変換素子 7 1 4 が設けられている。 20

【 0 2 4 9 】

光電変換素子 7 1 4 は、絶縁膜 6 2 5 上に設けられた半導体膜 6 6 0 と、半導体膜 6 6 0 上に接して設けられた第 1 のソース電極層 6 1 6 a 、電極 6 1 6 e と、を有する。第 1 のソース電極層 6 1 6 a は第 2 のトランジスタ 7 1 7 のソース電極層またはドレイン電極層として機能する電極であり、光電変換素子 7 1 4 と第 2 のトランジスタ 7 1 7 とを電気的に接続している。 30

【 0 2 5 0 】

半導体膜 6 6 0 、第 1 のソース電極層 6 1 6 a および電極 6 1 6 e 上には、ゲート絶縁膜 6 1 2 、酸化物絶縁層 6 1 8 および絶縁膜 6 4 5 が設けられている。また、絶縁膜 6 4 5 上に配線 6 5 6 が設けられており、ゲート絶縁膜 6 1 2 、酸化物絶縁層 6 1 8 および絶縁膜 6 4 5 に設けられた開口を介して電極 6 1 6 e と接する。 30

【 0 2 5 1 】

電極 6 1 6 e は、第 1 のソース電極層 6 1 6 a および第 1 のドレイン電極層 6 1 6 b と、配線 6 5 6 は、配線 6 4 9 と同様の工程で作成することができる。 40

【 0 2 5 2 】

半導体膜 6 6 0 としては、光電変換を行うことができる半導体膜を設ければよく、例えば、シリコンやゲルマニウムなどを用いることができる。半導体膜 6 6 0 にシリコンを用いた場合は、可視光を検知する光センサとして機能する。また、シリコンとゲルマニウムでは吸収できる電磁波の波長が異なるため、半導体膜 6 6 0 にゲルマニウムを用いる構成とすると、赤外線を中心に検知するセンサとして用いることができる。

【 0 2 5 3 】

以上のように、マイクロコンピュータ 5 0 0 に、光センサ 5 1 1 を含む検出部 5 0 9 を内蔵して設けることができる、部品数を削減し、警報装置の筐体を縮小することができる。なお、光センサまたは光電変換素子の位置に自由度が必要な場合は、光センサまたは光電変換素子を外付けとして、マイクロコンピュータ 5 0 0 に電気的に接続すればよい。 40

【 0 2 5 4 】

上述した I C チップを含む警報装置には、先の実施の形態に示したトランジスタを用いた複数の回路を組み合わせ、それらを 1 つの I C チップに搭載した C P U 5 0 5 が用いられる。

【 0 2 5 5 】

図 1 7 は、実施の形態 1 乃至 3 で説明したトランジスタを少なくとも一部に用いた C P U 50

の具体的な構成を示すブロック図である。

【0256】

図17(A)に示すCPUは、基板1190上に、ALU1191(ALU:Arithmetical Unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198、書き換え可能なROM1199、およびROMインターフェース1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図17(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。10

【0257】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0258】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。20

【0259】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。30

【0260】

図17(A)に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

【0261】

図17(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。40

【0262】

電源停止に関しては、図17(B)または図17(C)に示すように、メモリセル群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図17(B)および図17(C)の回路の説明を行う。

【0263】

図17( B )および図17( C )では、メモリセルへの電源電位の供給を制御するスイッチング素子に、先の実施の形態で示したトランジスタを含む記憶回路の構成の一例を示す。

【 0 2 6 4 】

図17( B )に示す記憶装置は、スイッチング素子1141と、メモリセル1142を複数有するメモリセル群1143とを有している。具体的に、各メモリセル1142には、先の実施の形態に記載されているトランジスタを用いることができる。メモリセル群1143が有する各メモリセル1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが供給されている。さらに、メモリセル群1143が有する各メモリセル1142には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

【 0 2 6 5 】

図17( B )では、スイッチング素子1141として、先の実施の形態で示したトランジスタを用いており、当該トランジスタは、そのゲート電極層に与えられる信号SigAによりスイッチングが制御される。

【 0 2 6 6 】

なお、図17( B )では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、特に限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

【 0 2 6 7 】

また、図17( B )では、スイッチング素子1141により、メモリセル群1143が有する各メモリセル1142への、ハイレベルの電源電位VDDの供給が制御されているが、スイッチング素子1141により、ローレベルの電源電位VSSの供給が制御されているてもよい。

【 0 2 6 8 】

また、図17( C )には、メモリセル群1143が有する各メモリセル1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、メモリセル群1143が有する各メモリセル1142への、ローレベルの電源電位VSSの供給を制御することができる。

【 0 2 6 9 】

メモリセル群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

【 0 2 7 0 】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

【 0 2 7 1 】

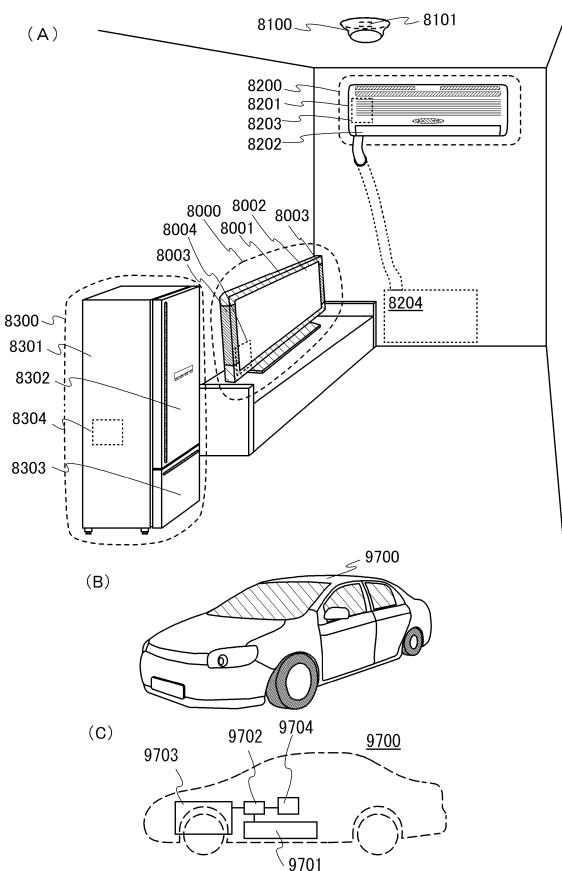

図18( A )において、警報装置8100は、住宅用火災警報器であり、検出部と、マイクロコンピュータ8101を用いた電気機器の一例である。マイクロコンピュータ8101は、先の実施の形態に示したトランジスタを用いたCPUを含む電子機器の一例である。

【 0 2 7 2 】

図18( A )において、室内機8200および室外機8204を有するエアコンディショナーは、先の実施の形態に示したトランジスタを用いたCPUを含む電気機器の一例であ

10

20

30

40

50

る。具体的に、室内機 8200 は、筐体 8201、送風口 8202、CPU 8203 等を有する。図 18 (A) において、CPU 8203 が、室内機 8200 に設けられている場合を例示しているが、CPU 8203 は室外機 8204 に設けられていてもよい。または、室内機 8200 と室外機 8204 の両方に、CPU 8203 が設けられていてもよい。先の実施の形態に示したトランジスタをエアコンディショナーの CPU に用いることによって省電力化が図れる。

【0273】

図 18 (A) において、電気冷凍冷蔵庫 8300 は、先の実施の形態に示したトランジスタを用いた CPU を含む電気機器の一例である。具体的に、電気冷凍冷蔵庫 8300 は、筐体 8301、冷蔵室用扉 8302、冷凍室用扉 8303、CPU 8304 等を有する。図 18 (A) では、CPU 8304 が、筐体 8301 の内部に設けられている。先の実施の形態に示したトランジスタを電気冷凍冷蔵庫 8300 の CPU 8304 に用いることによって省電力化が図れる。

【0274】

図 18 (B) および図 18 (C) において、電気機器の一例である電気自動車の例を示す。電気自動車 9700 には、二次電池 9701 が搭載されている。二次電池 9701 の電力は、制御回路 9702 により出力が調整されて、駆動装置 9703 に供給される。制御回路 9702 は、図示しない ROM、RAM、CPU 等を有する処理装置 9704 によって制御される。先の実施の形態に示したトランジスタを電気自動車 9700 の CPU に用いることによって省電力化が図れる。

【0275】