# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>5</sup> G11C 11/14 (45) 공고일자 1990년01월18일

(11) 공고번호 특1990-0000046

G11C 19/08

(21) 출원번호특 1985-0001315(65) 공개번호특 1985-0007151(22) 출원일자1985년03월02일(43) 공개일자1985년10월30일

(30) 우선권주장 59-039741 1984년03월03일 일본(JP) (71) 출원인 후지쓰가부시끼가이샤 야마모도 다꾸마

일본국 가나가와껜 가와사끼시 나까하라꾸 가미고다나까 1015반지

(72) 발명자 마지마 데이지

일본국 가나가와껜 가와사끼시 나까하라꾸 가미고다나까 1015반지 후지

쓰 가부시끼가이샤 내

(74) 대리인 장용식

## 심사관 : \_\_ 유환열 (책자공보 제1721호)

### (54) 마그네틱 버블 메모리칩을 제조하는 방법

#### 요약

내용 없음.

#### 出丑도

#### 도1

## 명세서

[발명의 명칭]

마그네틱 버블 메모리칩을 제조하는 방법

[도면의 간단한 설명]

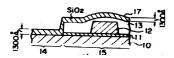

제1도는 공개된 종래의 방법에 따라 제조된 마그네틱 버블 메모리칩의 단면도.

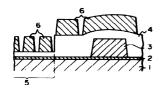

제2도는 버블메모리칩을 제조하는 공개된 종래의 방법에 대한 단계중 한 단계에 대한 단면도.

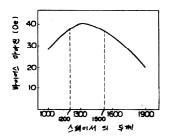

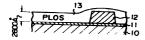

제3도는 마그네틱 버블 메모리칩의 스페이서 두께 및 바이어스 마아진과 같은 특성사이의 관계에 대한 예시도.

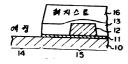

제4a 내지 4f도는 본 발명에 따르는 마그네틱 버블메모리칩을 제조하기 위한 방법의 단면도.

제5도는 본 발명에 따라 제조된 마그네틱버블메모리 칩의 일실시예의 대한 평면도.

제6도는 제5도의 실시예에서 게이트에 근접해 있는 마이너 루우프 조직 영역에 대한 평면도.

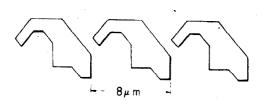

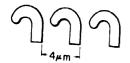

제7 및 8도는 제5도의 실시예에서 각각 제1 및 제2영역에 사용된 소프트 마그네틱 패턴의 형상에 대한 평면도.

\* 도면의 주요부분에 대한 부호의 설명

11 : 제1절연층

12 : 전도패턴

13 : 제2절연층

14 : 제1영역

15 : 제2영역

17 : 제3절연층

20-1 내지 20-n, 21-1 내지 21-n ; 30 : 마이너 루우프 조직

25 : 기록용메이저선 26 : 독출용

29 : 반복게이트

#### [발명의 상세한 설명]

본 발명은 마그네틱 버블메모리칩을 제조하는 방법 특히, 제1영역이 버블정보를 기억시키기 위한 마

이너루우프 전송선으로 제공되고 제2영역이 마이너 루우프 전송선에 따라 버블정보를 기록 또는 독출하기 위한 메이저 전송선으로 제공되는 얇은 버블막을 갖는 이중 간격형 마그네틱메모리칩을 제공하는 방법에 관한 것이다.

마이너루우프 전송선으로 구성되는 이러한 칩의 버블 정보 수용부분은 이러한 장치의 고밀도 시설을 가능케 하도록 더욱더 소형으로 형성하기 위해 마그네틱 버블 메모리칩의 설계에서 진전된 발전이 최근에 이루어져 왔다.

예를 들어, 4메가비트 칩에서 패턴주기는 4㎞이다. 한편, 스웹게이트(swap gate), 반복게이트, 발신기 및 마이너루우프 전송선 조직에 수용된 버블정보를 기록하도 독출하기 위한 메이저 전송선(메이저 선)과 같은 기능부분에 있어서, 16㎞ 주기와 같은 비교적 큰 패턴이 버블 메모리칩의 제조 과정동안 더 높은 위치 정확도를 가능하게 하도록 사용된다. 그러나, 다른 크기 전송패턴이 상기 언급한 바와같이 단일 메모리칩에서 사용될 경우, 구동력의 차이로 인해 특성에 관한 문제가 발생한다는 것이 알려져왔다.

제1도는 종래 기법에 따라 제조된 이중간격층을 갖는 마그네틱 버블 메모리칩의 단면도를 예시한다. 그리고, 제2도는 제작 처리동안 제1도의 버블메모리 칩의 확대된 단면을 예시한다.

종래 기술에서 SiO₂ 총(2)은 스퍼터링에 의해 가아넷막(1)상에 형성되며 기능 게이트를 제어하기 위한 금(은)전도패턴(3)이 그위에 형성된다. 전도패턴(3)의 단계를 평평하게 하기 위해, 폴리래더오르 가노실록산(polyladder-organosiloxane)(PLOS)과 같은 고내열성(4)가 그위에 코팅되고 가열 경화되며 그리고나서 정보수용부분을 위한 소형 전송패턴에 의한 칩의 영역(5)에서 PLOS층(4)만이 CF₄에칭 가스를 포함하는 플라즈마 에칭제로 에칭된다. 전송패턴용 퍼몰로이(permalloy)패턴(6)이 그후에 형성된다.

상기에서 언급한 종래기술은 몇가지 문제점을 안고 있다. 첫째는 마그네틱 버블 메모리칩을 제조하는 경우에 있어서 각 처리시의 에칭율의 불균일성이다. 통상적으로, 플래너 판형 에칭 기계는 이러한 고내열성(4)의 에칭용으로 일반적으로 사용되며, 이러한 형의 에칭기계가 균일한 에칭에 있어서 원통형 에칭기계보다 더 우수하다고 할지라도, 보통 각 처리당 ±5%미만의 에칭율의 변동이 여전히 존재하게 된다. 예를 들어, 고내열성 수지층(4)이 막두께가 3800Å이고 이 두께가 에칭에 의해 3000Å으로 감소될 경우, 500Å의 SiO2층(2)을 포함하여 1300Å의 두께를 갖는 스페이서를 얻기 위해 고온 허용수지의 두께가 3000Å으로 감소될 때 각 처리당 ±150Å미만의 에칭변동이 발생해야 할것이다. 게다가, 각 처리간의 변동이 고려될 경우, 적어도 ±300Å의 변동이 있을 수 있다. 앞으로 설명하겠지만, 1300Å은 스페이서를 위한 가장 적합한 두께이기 때문에 ±300Å과 같은 큰변동은 버블메모리칩의 성능감쇠와 같은 심각한 문제를 일으킬 것이다.

둘째는 200Å 내지 300Å의 두께를 갖는 불균일한 면(7)이 에칭면에 형성될 경우이며 이때 이 위에 형성된 퍼몰로이막은 국부적인 고점(高點)을 가질 수 있으며 이것은 버블 메모리의 특성에 영향을 가질 수 있으며 이것은 버블 메모리의 특성에 영향을 미치게 될 것이다.

본 발명의 목적은 공개된 종래의 제조방법과 관련해서 상기에서 언급한 단점을 제거하기 위한 마그네틱 버블메모리칩을 제조하는 방법을 제공하는 것이다.

본 발명의 목적은 스페이서의 두께에서 더 적은 변동이 있고 표면이 평평하며 따라서 안정된 특성을 얻을 수 있는 마그네틱 버블 메모리칩을 제조하는 방법을 제공하는 것이다.

본 발명에 의해, 제1영역이 적어도 버블 정보를 기억시키기 위해 마이너루우프 전송선에 의해 제공되고 제2영역이 마이너 루우프 전송선에 대해 버블 정보를 기록하고 독출하기 위한 메이저 전송선에 의해 제공되는 얇은 버블막을 가진 마그네틱버블 메모리칩을 제조하는 방법에 있어서, 1) 제1 및 제2영역에 걸친 얇은 버블막상에 제1절연층을 형성하기 위한 제1단계, 2) 상기 제1절연층상에 기능게이트 제어용 전도패턴을 형성하기 위한 제2단계, 3) 상기 제1절연층 및 기능게이트 제어용 상기 전도패턴에 걸쳐 제2절연층의 수지를 코팅하고 코팅된 제2절연층을 가열경화시키기 위한 제3단계, 4) 제1영역상에 존재하는 제1절연층과 제2수지절연층의 부분을 에칭에 의해 제거하기 위한 제4단계, 5) 제1 및 제2영역을 포함하는 전표면에 걸쳐 제3절연층을 형성하기 위한 제5단계 및 6) 제3절연층상에 마이너루우프 전송선과 메이저 전송선을 형성하기 위한 제6단계로 구성되는 것을 특징으로 하는 마그네틱버블 메모리칩을 제조하는 방법이 제공된다.

제3도는 4㎞패턴 주기를 갖는 소프트 마그네틱패턴을 사용할 경우 스페이서의 두께 및 버블 전파성 등 사이 관계를 나타낸다. 도면에서 알수 있듯이, 1300Å의 두께가 가장 바람직한 관계를 보여주고 있다.

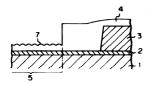

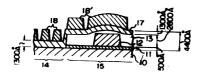

제4a도 내지 제4f도는 본 발명에 의한 마그네틱 버블메모리칩을 제조하는 방법에 있어서, 각각의 단계를 순차적으로 예시한다. 제4a도 내지 제4f도에 있어서, 참조번호(10)는 마그네틱 버블의 얇은 가아넷(garnet)막을, (11)은 제1절연층을, (12)는 기능게이트를 제어하기위한 전도패턴을, (13)은 제2절연층을, (14)는 제1영역을, (15)는 제2영역을, (16)은 포토레지스트(photoresist)층을, (17)은 제3절연층을 그리고 (18과 18')는 버블 전송용 소프트마그네틱 패턴을 각각 나타낸다.

본 발명에 따르는 마그네틱 버블 메모리칩을 제조하는 방법의 일실시예가 제4a도 내지 제4f도를 참조로 지금 설명될 것이다.

제4a도에서와 같이, 제1단계에서, 제1절연층(11)은 기판상에서 형성된 마그네틱 버블의 얇은 약(10)상에 SiO<sub>2</sub>를 500Å의 두께로 스퍼터링함으로써 형성된다.

제4b도에서와 같이, 제2단계에서, 약 3500Å의 두께로 Au로 구성된 기능게이트 제어콘덕터는 증착에의해 제1절연층(11)에 형성되며, 그후에 기능게이트 제어전도패턴(12)이 사진 석판식으로 스퍼터링함으로써 형성된다. 이 경우에, 또한 100Å 내지 150Å의 두께를 갖는 TaMo는 SiO<sub>2</sub> 절연층(11)에 대

한 Au전도체(12)의 접착성을 향상시키도록 사용될 수 있다.

제4c도에서와 같이, 제3단계에서, 2600Å의 두께를 갖는 폴리래더오르가노실록산 수지 (polyladderorgano - siloxane resin)(PLOS)가 전표면에 코팅되며 제2절연층(13)을 형성하기 위해가열 경화시킨다.

제4d도 에서와 같이, 제4단계에서, 이러한 칩의 제2영역(15)이 레지스토(16)로 덮여진다. 한편, 정보 수용부분으로서 작용하는 이러한 칩의 제1영역(14)에서,  $\mathrm{SiO}_2$  및 PLOS 수지로 각각 구성되는 제1및 제2절연층(11과 13)은 마그네틱 버블 메모리칩의 제1영역(14)에서 얇은 막(10)의 표면을 노출시키기 위해 플래너판형 건조 에칭기계에서  $\mathrm{CF}_4$  에칭가스를 표함하는 에칭제로 에칭된 플즈마이다. 이경우에,  $\mathrm{SiO}_2$  및 PLOS수지의 제1 및 제2절연층은 PLOS의 주성분이  $\mathrm{SiO}_2$  및 PLOS수지의 제1 및 제2절연층은 PLOS의 주성분이  $\mathrm{SiO}_2$  등 이 하지에 의해 에칭될 수 있다.

제4e도에서와 같이, 제5단계에서, 1300Å이 두께를 갖는 SiO<sub>2</sub>의 제3절연층(17)은 제1(14) 및 제2(15)영역에 스피터링함으로써 형성되어진다. 제3도에서 알수 있듯이, 절연층(17)의 두께는 1200Å 내지 1500Å이 적합하며 가장 적합한 것은 1300Å이다.

제4f도에서와 같이, 제6 및 최종단계에서, 퍼멀로이(permalloy)와 같은 소프트 마그네틱 재료가 제3 절연층(17)상에 증착에 의해 형성된 후에, 여러 패턴 주기로된 버블 전송용 소프트 마그네틱 패턴 (18과 18')이 사진석판 또는 이온에칭에 의해 형성된다. 이 경우에, 소프트 마그네틱패턴(18)은 제1 영역(14)내의 마이너루우프조직의 전송선은 구성되며 이것의 패턴 주기는 예를 들어 4㎞ 내지 6㎞이다. 한편, 소프트 마그네틱 패턴(18')은 메이저 전송선 및 메이저 전송선을 마이너 루우프 조직으로 연결시키기 위한 패턴으로 구성되며 이것의 패턴 주기는 예를 들어 8㎞ 내지 16㎞이다.

예시된 실시예에 의해, 마그네틱 버블의 얇은 막(10)은 CF₄를 사용한 플라즈마 에칭제로 에칭되지 않으므로 약간의 과에칭은 에칠의 약간의 불균일성 및 에칭층 두께의 변동을 방지하는데 효과적이다. 그러므로, 안정된 전파성능을 가진 마그네틱 버블 메모리칩이 얻어질 수 있다.

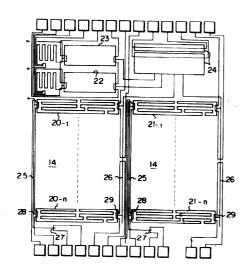

제5도는 본 발명에 따라 제작된 마그네틱 버블 메모리칩의 일실시예의 평면도이다.

제5도에서, 참조번호(20-1 내지 20-n 및 21-1 내지 21-n)는 마이너 루우프 조직을, (22와 23)은 마이너 루우프 조직내의 고장 루우프에 관한 정보를 기억시키기 위한 부트 루우프를, (24)는 검파기를, (25)는 기록용 메이저선을, (26)은 독출 메이저선을, (27)은 발신기를, (28)은 스웹 (swap)게이트를 그리고(29)는 반복게이트를 각각 나타낸다.

제5도에 표시된 실시예는 홀수, 짝수형 메이저-마이너 조직이며, 여기서 제1영영은 정보 수용부분으로 작용하는 마이너 루우프조직(20-1 내지 20-n 및 21-1 내지 21-n) 및 부트 루우프(22와 23)로 구성된다.

제1영역(14)은 4㎞주기를 가진 작은 소프트 마그네틱 패턴(18)(제4f도)를 사용하고 스페이서의 두께는 제4f도와 같이 1300Å이다.

제1영역(14)의 영역은 예를 들어 발신기(27), 기록용 메이저라인(25), 독출메이저라인(26), 스웹게 이트(28), 반복게이트(29), 검파기(24) 및 게이트에 근접해 있는 마이너 루우프 조직의 약간의 소부분으로 구성되는 제2영역이다.

제2영역은 소프트 마그네틱 패턴(8㎢ 내지 16㎢ 주기)으로 구성되며 스페이서의 두께는 제4f도에서 알수 있듯이 4400Å이다.

제6도는 마이너 루우프 조직 및 이 조직의 게이트의 주변영역에 대한 평면도이며, 여기서 참조번호 (30)는 마이너 루우프 조직을, (25)는 기록용 메이저라인을, (26)은 독출메이저라인을, (28)은 스웹 게이트를 그리고 (29)는 반복 게이트를 각각 나타낸다. 제6도에서, 마이너 루우프조직(30)에서 에칭에 의해 예시된 영역은 제1영역이다.

한편, 연결용의 큰 소프트 마그네틱패턴(35)을 사용하는 게이트 주변의 몇몇 비트영역은 제2영역에 포함된다. 또한, 제6도에서 알 수 있듯이, 제1 및 제2영역사이의 경계부분은 각각의 영역의 주변패 턴사이의 버블 전송 갭에 의해 한정된다.

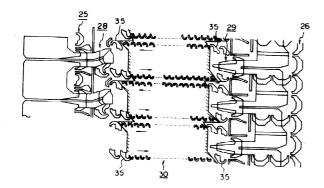

제7 및 8도는 제1영역의 마이너 루우프 조직(30)(제6도)에서 전송선용으로 그리고 제2영역에서 패턴 (35)(제6도)용으로 각각 사용된 소프트 마그네틱 패턴을 예시한다. 제7 또는 8도의 어느 하나에서 예시된 패턴은 "와이드 갭(wide gap)"패턴으로 불리어지며, 이것은 종래 기술에서 통상적으로 사용된 반 디스크 패턴 또는 비대칭 세브론(chevron) 패턴보다 크기 및 고밀도 부하 가능성면에서 더많은 이점을 갖고 있으며, 그 이유는 전자의 갭공간이 후자보다 더 크기 때문이다.

앞에서 상세히 설명했듯이, 본 발명에 의한 마그네틱 버블 메모리칩을 제조하는 방법은 얇고 두꺼운 층으로 구성된 이중간격층 구조 또는 이중간격형 버블칩을 제작할 경우 특히 유리하게 채택된다.

따라서, 본 발명에 의해 얇은 층이 형성될 경우, 그것의 두께에 있어서 에칭 및 변동의 불균일성이 방지되며, 더 작은 변동을 가진 안정된 버블전송성능 및 특성으로 된 마그네틱 버블 메모리칩이 얻 어질 수 있다.

## (57) 청구의 범위

#### 청구항 1

제1영역에는 적어도 버블정보를 기억시키기 위한 마이너 루우프 전송선이 제공되고 제2영역에는 마이너 루우프 전송선에 대해 버블정보를 기록하고 독출하기 위한 메이저 전송선이 제공되는 얇은 버

불막을 가진 마그네틱 버블 메모리 칩을 제조하는 방법에 있어서, 제1 및 제2영역에 걸친 얇은 버블 막상에 제1절연층을 형성하기 위한 제1단계, 상기 제1절연층상에 기능게이트 제어용 전도패턴을 형 성하기 위한 제2단계, 상기 제1절연층 및 기능게이트 제어용 상기 전도패턴을 걸쳐 제2절연층의 수 지를 코팅하고 코팅된 제2절연층을 가열 경화시키기 위한 제3단계, 제1영역상에 존재하는 제1절연층 과 제2수지절연층의 부분을 에칭에 의해 제거하기 위한 제4단계, 제1 및 제2영역을 포함하는 전표면 에 걸쳐 제3절연층을 형성하기 위한 제5단계 및 제3절연층상에 마이너 루우프 전송선과 메이저 전송 선을 형성하기 위한 제6단계로 구성되는 것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방 법.

#### 청구항 2

제1항에 있어서, 상기 마이너 루우프 전송선의 버블 전송패턴이 상기 메이저 전송선의 버블 전송 패턴보다 더 작은 패턴주기를 갖는것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

#### 청구항 3

제1항에 있어서, 상기 제2절연층을  $SiO_2$ 이고 이것의 두께는  $1200\,\text{Å}$  내지  $1500\,\text{Å}$  인것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

#### 청구항 4

제3항에 있어서, SiO₂층의 두께가 약 1300Å인것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

#### 청구항 5

제1항에 있어서, 제1 및 제2영역의 버블 전송 패턴이 소프트 마그네틱패턴으로 형성되고 제1영역의 소프트 마그네틱 패턴은 4㎞ 내지 6㎞의 패턴 주기를 갖으며 제2영역의 소프트 마그네틱 패턴은 적 어도 8㎞의 패턴주기를 갖는 것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

### 청구항 6

제1항에 있어서, 상기 제1영역이 마이너루우프 전송선의 고장 루우프에 대한 정보를 기억시키기 위한 루우프를 포함하는 것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

#### 청구항 7

제5항에 있어서, 적어도 제1영역내의 소프트 마그네틱 패턴이 와이드 갭 패턴인 것을 특징으로 하는 마그네틱 버블 메모리칩을 제조하는 방법.

### 도면

#### 도면1

도면2

도면3

## 도면4A

도면48

도면4C

도면40

도면4E

도면4F

도면5

## 도면6

# 도면7

# 도면8