# (19) **日本国特許庁(JP)**

# (12)公表特許公報(A)

(11)特許出願公表番号

特表2004-523133 (P2004-523133A)

(43) 公表日 平成16年7月29日(2004.7.29)

(51) Int.C1.7

FI

テーマコード (参考)

H01G 4/38 H01G 9/26 HO1G 4/38Α 521 HO1G 9/00

5E082

#### 審查請求 有 予備審查請求 未請求 (全 80 頁)

(21) 出願番号 特願2003-525865 (P2003-525865) (86) (22) 出願日 平成14年9月5日(2002.9.5) (85) 翻訳文提出日 平成15年5月6日 (2003.5.6) (86) 国際出願番号 PCT/US2002/028100 (87) 国際公開番号 W02003/021614 (87) 国際公開日 平成15年3月13日 (2003.3.13)

(31) 優先権主張番号 60/317, 356

(32) 優先日 平成13年9月5日(2001.9.5)

(33) 優先権主張国 米国(US) (31) 優先権主張番号 10/234,972

(32) 優先日 平成14年9月4日 (2002.9.4)

(33) 優先権主張国 米国 (US) (71) 出願人 500047848

エイブイエックス コーポレイション アメリカ合衆国 29578-0867 サウスカロライナ州 マートル ビーチ エイブイエックス ドライブ 2200 ピー、オー、ボックス 867

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

(72) 発明者 ジョン エル. ガルバニ

> アメリカ合衆国 29575 サウスカロ ライナ州 サーフサイド ビーチ ターキ ー リッジ ロード 1450ビー

> > 最終頁に続く

(54) 【発明の名称】 カスケードコンデンサ

# (57)【要約】

高周波数応用分野およびその他の環境で使用される多層 カスケードコンデンサを開示する。このコンデンサは、 複数のコンデンサ構成部品(10)またはその複数の態 様を集積パッケージ中に含むことができる。これらの構 成部品としては、例えば、薄膜BGA構成部品、インタ ーデジタル型コンデンサ(IDC)構成、二重層電気化 学コンデンサ、単層コンデンサなどがある。本発明の例 示的な実施形態は、少なくとも特定の態様の薄膜BGA 技術および/またはIDC型構成を含むことが好ましい 。所与のキャパシタンス値を維持しながらESLの低下 を促進する取付けおよび相互接続のためのフィーチャを 設ける。さらなる利点としては、広い動作周波数範囲に わたって、低いESLと、減結合性能とが得られること が挙げられる。さらに詳細には、本開示の技術は、キロ ヘルツから数ギガヘルツまでの周波数範囲にわたって機 能することができ、広い範囲のキャパシタンス値をとる ことを特徴とすることもできる例示的なコンデンサを提 供する。本発明のさらなる開示の特徴は、様々な厚さの 誘電体層(22)を組み込み、特定の構成に関連する共

#### 【特許請求の範囲】

## 【請求項1】

多層コンデンサであって、

基板と、

前記基板をほぼ覆う第1の電極層と、

それぞれが第1の直径を有する第1の複数の貫通孔を画定する、前記第1の電極層をほぼ 覆う第1の絶縁層と、

それぞれが前記第1の直径以上の第2の直径を有する第2の複数の貫通孔を画定する、前記第1の絶縁層をほぼ覆う抵抗層と、

それぞれが前記第2の直径以上の第3の直径を有する第3の複数の貫通孔を画定する、前記抵抗層をほぼ覆う第2の電極層であり、前記第1、第2および第3の複数の貫通孔がそれぞれ同心円状に配列され、それぞれが複数の貫通孔トリプレットを形成する、第2の電極層と、

前記貫通孔トリプレットのうち選択されたものの中を通る第1の複数の導電性バイアであり、それぞれが前記第1の電極層に接続され、前記第2の電極層には接触しないように設けられた第1の複数の導電性バイアとを含むことを特徴とする多層コンデンサ。

#### 【請求項2】

それぞれ対応する前記複数の貫通孔トリプレットから横方向にずれた第 4 の複数の貫通孔 を画定する、前記第 2 の電極層をほぼ覆う第 2 の絶縁層と、

前記第2の電極層にそれぞれ接続された、前記第4の複数の貫通孔のうち選択されたものの中を通る第2の複数の導電性バイアとをさらに含むことを特徴とする請求項1に記載の多層コンデンサ。

# 【請求項3】

前記基板が外側周縁部を有し、

前記第1および第2の電極層がそれぞれ、実質的に連続した部分と、前記連続した部分から前記基板の前記外側周縁部に延びる複数のタブ部分とを含むことを特徴とする請求項1 に記載の多層コンデンサ。

#### 【請求項4】

複数のはんだ球をさらに含み、各はんだ球が、前記第1および第2の複数の導電性バイアのうち選択したものの一部分に取り付けられることを特徴とする請求項3に記載の多層コンデンサ。

# 【請求項5】

前記第1の複数の導電性バイアがそれぞれ第1および第2の端部を有することを特徴とし、前記第1の複数の導電性バイアそれぞれの選択された端部が、前記第1の電極層と接することを特徴とする請求項1に記載の多層コンデンサ。

# 【請求項6】

多層構成部品の等価直列抵抗(ESR)を調節する方法であって、

絶縁層で分離された少なくとも第 1 および第 2 の電極層を含む多層構成部品を作製するステップと.

絶縁層と第1または第2の電極層の一方との間に抵抗層を設けるステップと、

抵抗層の有効抵抗を変化させることによって前記構成部品のESRを調節するステップとを含むことを特徴とする方法。

# 【請求項7】

前記調節ステップが、

第 1 ま た は 第 2 の 電 極 層 の 一 方 に 、 複 数 の 貫 通 孔 を 穿 孔 す る ス テ ッ プ と 、

複数の貫通孔のうち選択したものの直径を調節することによって、穿孔された電極層の被覆範囲が抵抗層の有効抵抗を変化させることにより、抵抗層の有効抵抗を変化させるステップとを含むことを特徴とする請求項 6 に記載の方法。

# 【請求項8】

前記調節ステップが、

40

10

20

30

抵抗層の厚さを調節することによって抵抗層の有効抵抗を変化させるステップをさらに含むことを特徴とする請求項6に記載の方法。

#### 【請求項9】

前記調節ステップが、

抵抗層の組成を調節することによって抵抗層の有効抵抗を変化させることを特徴とする請求項6に記載の方法。

#### 【請求項10】

多層構成部品の共振特性を調節する方法であって、

連続的に積み重ねた複数の電極層を有する多層構成部品を作製するステップと、

各電極層に挟まれた別個の絶縁層を設けるステップと、

別個の絶縁層のうち選択されたものの厚さを様々に変化させることにより、多層構成部品の共振特性を調節するステップとを含むことを特徴とする方法。

#### 【請求項11】

前記変化させるステップが、

別個の絶縁層に、層ごとに連続的に変化する厚さを持たせるステップを含むことを特徴と する請求項10に記載の多層構成部品の共振特性を調節する方法。

## 【請求項12】

前記変化させるステップが、

別個の絶縁層に、あるパターンに従って層ごとに変化する厚さを持たせるステップを含む ことを特徴とする請求項10に記載の多層構成部品の共振特性を調節する方法。

# 【請求項13】

前記変化させるステップが、

別個の絶縁層に、層ごとに整合されて変化する厚さを持たせるステップを含むことを特徴とする請求項10に記載の多層構成部品の共振特性を調節する方法。

# 【請求項14】

多層コンデンサであって、

# 基板と、

前記基板をほぼ覆う第1の電極層と、

前記第1の電極層をほぼ覆い、それぞれ第1の直径を有する第1の複数の貫通孔を画定する第1の絶縁層と、

前記第1の絶縁層をほぼ覆い、それぞれ前記第1の直径以上の第2の直径を有する第2の複数の貫通孔を画定する第2の電極層であり、前記第1および第2の複数の貫通孔がそれぞれ同心円状に配列され、それぞれ複数の貫通孔対を形成する、第2の電極層と、

前記貫通孔対のうち選択されたものの中を通る第1の複数の導電性バイアであり、それぞれが前記第1の電極層に接続され、前記第2の電極層には接触しないように設けられた第1の複数の導電性バイアとを含み、

前記基板が外側周縁部を有し、

前記第1および第2の電極層がそれぞれ、実質的に連続した部分と、前記連続した部分から前記基板の前記外側周縁部に延びる複数のタブ部分とを含むことを特徴とする多層コンデンサ。

# 【請求項15】

それぞれ対応する前記複数の貫通孔対から横方向にずれた第3の複数の貫通孔を画定する、前記第2の電極層をほぼ覆う第2の絶縁層と、前記第2の電極層にそれぞれ接続された、前記第3の複数の貫通孔のうち選択されたものの中を通る第2の複数の導電性バイアとをさらに含むことを特徴とする請求項14に記載の多層コンデンサ。

# 【請求項16】

複数のはんだ球をさらに含み、各はんだ球が、前記第 1 および第 2 の複数の導電性バイアのうち選択したものの一部分に取り付けられることを特徴とする請求項 1 5 に記載の多層コンデンサ。

# 【請求項17】

50

10

20

30

30

前記第1の直径以上で前記第2の直径以下の第3の直径をそれぞれ有する、前記複数の貫通孔対とそれぞれ同心円状に配列された第3の複数の貫通孔を画定する、前記第1の絶縁層をほぼ覆う抵抗層をさらに含むことを特徴とする請求項14に記載の多層コンデンサ。

#### 【請求項18】

前記第1の複数の導電性バイアがそれぞれ第1および第2の端部を有することを特徴とし、前記第1の複数の導電性バイアそれぞれの選択された端部が、前記第1の電極層と接することを特徴とする請求項14に記載の多層コンデンサ。

## 【請求項19】

カスケードコンデンサであって、

外側周縁部を有する基板と、

前記基板上に積み重ねられ、絶縁層で互いに分離された、複数の縁部をそれぞれ有する第 1 および第 2 の電極層であり、前記絶縁層および前記第 2 の電極層がそれぞれ複数の貫通 孔を画定する、第 1 および第 2 の電極層と、

前記それぞれの複数の貫通孔のうち選択されたものの中を通り、前記第1の電極層に接続された、複数の導電性バイアと、

交互配置された電極層の外部構成部品への結合が容易になるようにインターデジタル型に 交互に配列された、前記第1および第2の電極層の選択された縁部から前記基板の前記外 側周縁部にそれぞれ延びる第1および第2の複数のタブと を含む第1の多層コンデンサ

それぞれが絶縁層で互いに分離された、それぞれ複数の縁部を有する第1および第2の複数の電極層と、

前記第1および第2の複数の電極層の交互配置された電極の外部構成部品への結合が容易になるようにインターデジタル型に交互に配列された、前記第1および第2の複数の電極層のうち選択された電極層の選択された縁部から前記第1の多層コンデンサの前記基板の外側周縁部に向かって延びる第1および第2の複数のタブと

を含む第2の多層コンデンサ、ならびに

前記第1の多層コンデンサの前記第1および第2の複数のタブのうち選択されたものを、前記第2の多層コンデンサの前記第1および第2の複数のタブのうち選択されたものに結合する、複数の導電性ランドを含むことを特徴とするカスケードコンデンサ。

#### 【請求項20】

前記複数の導電性ランドのうち選択されたものに結合された少なくとも1つの表面実装コンデンサをさらに含むことを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求項21】

ー 対 の 表 面 実 装 コン デン サ が 、 前 記 複 数 の 導 電 性 ラン ド の う ち 選 択 さ れ た も の に 結 合 さ れ る こ と を 特 徴 と す る 請 求 項 2 0 に 記 載 の カ ス ケ ー ド コ ン デ ン サ 。

#### 【請求項22】

前記複数の導電性ランドのうち選択されたものに結合された単層コンデンサをさらに含む ことを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求頃23】

前記複数の導電性ランドのうち選択されたものに結合された少なくとも1つの表面実装コンデンサをさらに含むことを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求項24】

一対の表面実装コンデンサが、前記複数の導電性ランドのうち選択されたものに結合されることを特徴とする請求項 2 3 に記載のカスケードコンデンサ。

#### 【請求項25】

前記第1の多層コンデンサを複数含み、

前記第2の多層コンデンサを複数含み、前記複数の第1の多層コンデンサの各多層コンデンサがそれぞれ、前記複数の第2の多層コンデンサの前記多層コンデンサの1つと個別にカスケード結合されて、複数のカスケードコンデンサセクションを形成し、

前記カスケードコンデンサセクションのそれぞれと結合された共通コンデンサをさらに含

10

20

30

40

20

30

50

むことを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求項26】

前記複数のカスケードコンデンサセクションが、前記共通コンデンサ上に物理的に並列に取り付けられることを特徴とする請求項25に記載のカスケードコンデンサ。

#### 【請求項27】

前記共通コンデンサが二重層コンデンサであることを特徴とする請求項 2 5 に記載のカスケードコンデンサ。

# 【請求項28】

前記共通コンデンサが単一の電気化学コンデンサであることを特徴とする請求項 2 5 に記載のカスケードコンデンサ。

## 【請求項29】

前記複数の導電性バイアがそれぞれ、前記第1の多層コンデンサの第1の電極層に接続され、前記それぞれの複数の貫通孔のうち選択されたものの中を、前記第1の多層コンデンサの第2の電極層と接触しないようにして通ることを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求項30】

前記第1の多層コンデンサの前記絶縁層によって画定される前記複数の貫通孔が、第1の 直径を有して形成され、

前記第1の多層コンデンサの前記第2の電極層によって画定される前記複数の貫通孔が、前記第1の直径以上の第2の直径を有して形成され、前記第1および第2の複数の貫通孔が、それぞれ同心円状に配列され、複数の貫通孔対を形成していることを特徴とする請求項21に記載のカスケードコンデンサ。

# 【請求項31】

前記複数の導電性ランドのうち選択されたものに結合された少なくとも1つの追加のコンデンサをさらに含み、前記少なくとも1つの追加のコンデンサが、表面実装コンデンサ、単層コンデンサ、二重層コンデンサ、電気化学コンデンサ、セラミックコンデンサ、およびタンタルコンデンサからなる一群から選択されることを特徴とする請求項19に記載のカスケードコンデンサ。

# 【請求項32】

前記第2の多層コンデンサの前記絶縁層の別個の絶縁層の厚さを層ごとに変化させて、前記カスケードコンデンサの共振特性を調節することを特徴とする請求項19に記載のカスケードコンデンサ。

#### 【請求項33】

前記第2の多層コンデンサの選択された別個の絶縁層の厚さが層ごとに連続的に変化していることを特徴とする請求項32に記載のカスケードコンデンサ。

#### 【請求項34】

前記第2の多層コンデンサの選択された別個の絶縁層の厚さが、あるパターンに従って層 ごとに変化していることを特徴とする請求項32に記載のカスケードコンデンサ。

# 【請求項35】

前記第2の多層コンデンサの選択された別個の絶縁層の厚さが、層ごとに変化しているこ 40とを特徴とする請求項32に記載のカスケードコンデンサ。

#### 【請求項36】

多層コンデンサであって、

連続的に積み重ねられた、複数の縁部をそれぞれ有する複数の電極層および複数の絶縁層と、

前記複数の電極層のそれぞれの選択された縁部から延び、前記多層コンデンサの選択された側面で露出する、インターデジタル型に交互に配列された複数のタブと、

前記最上部電極層および前記隣接するその下の絶縁層を穿孔し、前記その次の連続する電極層を露出させることによってそれぞれ形成された第1および第2の複数の貫通孔と、

それぞれが前記第1および第2の複数の貫通孔のうち選択されたものの中を通り、前記露

出した電極層に接続される第1の複数の導電性バイアと、

前記複数のタブのうち選択されたものを結合する複数の導電性ランドとを含むことを特徴とする多層コンデンサ。

# 【請求項37】

前記複数の導電性ランドのうち選択されたものに結合された少なくとも1つの追加のコンデンサをさらに含み、前記少なくとも1つの追加のコンデンサが、表面実装コンデンサ、単層コンデンサ、二重層コンデンサ、電気化学コンデンサ、セラミックコンデンサ、およびタンタルコンデンサからなる一群から選択されることを特徴とする請求項36に記載の多層コンデンサ。

#### 【請求項38】

一対の追加のコンデンサが、前記複数の導電性ランドのうち選択されたものに結合される ことを特徴とする請求項37に記載の多層コンデンサ。

#### 【請求項39】

前記複数の導電性ランドのうち選択されたものに結合された単層コンデンサをさらに含むことを特徴とする請求項36に記載の多層コンデンサ。

#### 【請求項40】

前記複数の導電性ランドのうち選択されたものに結合された少なくとも 1 つの表面実装コンデンサをさらに含むことを特徴とする請求項 3 9 に記載の多層コンデンサ。

#### 【 請 求 項 4 1 】

一対の表面実装コンデンサが、前記複数の導電性ランドのうち選択されたものに結合されることを特徴とする請求項 4 0 に記載の多層コンデンサ。

#### 【請求項42】

カスケードコンデンサセクションをそれぞれ形成する少なくとも 1 つの追加の多層コンデ ンサと、

カスケードコンデンサセクションのそれぞれと結合された共通コンデンサとをさらに含む ことを特徴とする請求項 3 6 に記載の多層コンデンサ。

# 【請求項43】

カスケードコンデンサセクションが、前記共通コンデンサ上に物理的に並列に取り付けられることを特徴とする請求項42に記載の多層コンデンサ。

#### 【請求項44】

前記共通コンデンサが二重層コンデンサであることを特徴とする請求項 4 2 に記載の多層 コンデンサ。

#### 【請求項45】

前記共通コンデンサが単一の電気化学コンデンサであることを特徴とする請求項 4 2 に記載の多層コンデンサ。

# 【請求項46】

前記最上部電極層を穿孔することによって形成された前記第1の複数の貫通孔がそれぞれ 第1の直径を有し、

前記隣接するその下の絶縁層を穿孔することによって形成された前記第2の複数の貫通孔がそれぞれ第1の直径以上の第2の直径を有することを特徴とする請求項36に記載の多層コンデンサ。

#### 【請求項47】

前記最上部電極層と前記隣接するその下の絶縁層との間に抵抗層をさらに含むことを特徴とする請求項36に記載の多層コンデンサ。

#### 【請求項48】

前記絶縁層のうち選択されたものの厚さを層ごとに変化させて、前記多層コンデンサの共振特性を調節することを特徴とする請求項36に記載の多層コンデンサ。

# 【請求項49】

前記絶縁層のうち選択されたものの厚さが層ごとに連続的に変化していることを特徴とする請求項48に記載の多層コンデンサ。

10

20

30

30

40

50

#### 【請求項50】

前記絶縁層のうち選択されたものの厚さが、あるパターンに従って層ごとに変化していることを特徴とする請求項48に記載の多層コンデンサ。

# 【請求項51】

前記絶縁層のうち選択されたものの厚さが、層ごとに変化していることを特徴とする請求 項48に記載の多層コンデンサ。

【発明の詳細な説明】

# [0001]

#### (優先権主張)

本願は、参照によりあらゆる目的のために本明細書に組み込む、USSN60/317356を付与された「Cascade Capacitor」と題する、本願と同じ発明者等による、2001年9月5日に既に出願された米国仮特許出願の特典を主張するものである。

# [0002]

# (発明の背景)

本発明は一般に、高周波の応用分野など、ある周波数範囲の応用分野で使用される、多層カスケードコンデンサに関する。さらに詳細には、本発明は、モノリシックパッケージに設けられた複数のコンデンサ構成部品に関する。本発明では、高いキャパシタンス、低い等価直列インダクタンス(ESL)、低いまたは同調可能な等価直列抵抗(ESR)など、改善および/または理想化された性能特性を有するデバイスを作製するための相互接続フィーチャおよび取付けフィーチャを利用する。

#### [0003]

最新技術の応用分野は多様化しているので、効率のよい電子構成部品と、その中で使用される集積回路とが必要とされるようになっている。このような最新技術の応用分野としてのは、無線通信、警報システム、レーダシステム、回線交換、整合ネットワーク、およびその他の多くの分野があり、コンデンサは、フィルタリング、減結合、バイパス、およびその他の様々な最新技術分野の側面で使用される基本的な構成要素である。集積回路の速なを度および実装密度が劇的に向上すると、とりわけ減結合コンデンサ技術の進歩が必要とさまる。高キャパシタンス減結合コンデンサが現在の多くの応用分野の高周波数を受けるときには、性能特性はますます重要となる。このような幅広い応用分野においてコンデンサはは必須であるので、それらが精密かつ効率的であることはきわめて重要である。したがって、コンデンサの性能特性を改善するために、コンデンサ設計の数多くの側面が注目されてきた。

# [0004]

このようにコンデンサ環境が驚くほど多様であるということは、コンデンサがいくつかの異なる動作周波数を受けることが多いということである。衛星やGPS、携帯電話の分野を含めた多くの無線通信システム、ならびに高速プロセッサの分野では、高い動作周波数囲に適応するようになされたコンデンサ技術が必要とされている。一般に高い動作周波数囲に適応するようになされたコンデンサ技術の例が、米国特許第6208501B1号(Lhivuku1a他)、第5576926号(Monsorno)、および第5220482号(Takemura他)に開示されている。多くの場合、コンデンサは、このようはことがって、広い範囲の周波数にわたのほれ、両方に対応するようには設計されない。したがって、広い範囲の周波数にわたの限された周波数範囲内で良好に動作することができるコンデンサの例は、米国特許第6184574B1号(Bissey)、第6038122号(Bergstedt他)、および第5786978号(Mizuno)に見ることができる。

#### [0005]

コンデンサは、様々な動作周波数を受ける可能性があるのと同時に、様々な動作温度にも

30

40

50

さらされる可能性がある。所与の温度における許容性能は、コンデンサの形成に使用した誘電材料のキャパシタンスの温度係数に関係することが多い。様々な温度で所望のコンデンサ動作を可能にする既存の技法の1つは、様々な誘電材料で形成したコンデンサを積層するものである。この積層技法の例は、米国特許第5799379号および第5517385号(Galvagni他)に見ることができる。

#### [0006]

実際のコンデンサは、理論的には存在しないこともある固有抵抗値を有する。コンデンサのこの付加的な性質は、しばしば等価直列抵抗(ESR)と呼ばれる。できる限り理論上の動作に近い動作をするコンデンサを作成することが望ましいので、一般にはESRの低いコンデンサが好ましい。ESRを最低限に抑える必要があることは、減結合コンデンサの分野で特に明らかである。ESRが高くなると、所与のキャパシタンス値に対してリプル電圧およびワット損が増大する。これは、コンデンサのRC時定数に関係し、低いコンデンサのESRが必要とされる1つの要因となっている。低ESRをもたらすよう設計されたコンデンサの例が、米国特許第6226170B1号(Ne11ison他)に開示されている。

#### [0007]

コンデンサ性能の改善を実現するもう1つの方法は、デバイスのインダクタンスを低下させることである。したがって、減結合コンデンサの場合には、回路効率を維持するために低い等価直列インダクタンス(ESL)を実現することが好ましい。また、減結合コンデンサの自己インダクタンスおよび相互インダクタンスを低下させるコンデンサ設計を実施することが好ましいこともある。米国特許第6038121号(Naito他)および米国特許第6034864号(Naito他)には、磁束を打ち消し、ESLを低下させるように設計された例示的なコンデンサ構成が示されている。

#### [00008]

電流路を短縮すると、自己インダクタンスを低下させることになる。電流はしばしばコンデンサの全長を移動しなければならないので、コンデンサ構造の長い方の端部に成端すると、電流路が短縮されることになる。隣り合うコンデンサ電極の電流が反対方向に流れると、コンデンサの相互インダクタンスが低下することになる。インターデジタル形コンデンサの技術で利用されるような複数の端子も、インダクタンス値を低下させる。米国特許第5880925号(DuPre他)および第6243253B1号(DuPre他)には、前述の低インダクタンス特性のうちいくつかを提供する多層コンデンサが開示されている。これらDuPreの特許で論じられている基本構成は、以下でインターデジタル形コンデンサ(IDC)と呼ぶ多層コンデンサの1タイプに相当する。

# [0009]

減結合コンデンサのESLを低下させるもう1つの手法は、端子構成および実装システムによって生じる相互接続誘導を最小限に抑えることである。いくつかの既知の成端方式は高いインダクタンスを特徴とし、構成要素間の間隔をあまり接近させることができないことが多い。したがって、低ESLを有し、かつ集積回路の構成要素密度を高める一助となる効率的な成端方式が必要とされている。米国特許第6104597号(Konushi)および米国特許第4439813号(Dougherty他)では、薄膜コンデンサ技術使用して、基板に取り付けられる例示的なコンデンサを提供している。

#### [0010]

既知の成端方式では、内部の柱状電極と接続する孔配列をその中に有する電極板を利用する。このようにすることで、ESLがさらに低い省スペースの相互接続方式が提供されるが、コンデンサ電極中の孔配列は有効面積を減少させるので、構造全体のキャパシタンスは低下する。これらのクリアランス孔を備えた層の数が増えて、クリアランス孔が多くなりすぎると、短絡の問題が生じる一因となる。このような成端方式の例は、ヨーロッパ特許出願第1115129A2号(AhikoおよびIshigara)に見ることができる。したがって、低いインダクタンスならびに高いキャパシタンスを実現する成端方式が必要とされている。

#### [ 0 0 1 1 ]

所望の動作を容易にするために改善の必要がある可能性のある、多くの様々なコンデンサの性能特性がある。上記で言及し論じた特性のうち、選択されるものとしては、低いESL、低いESRその他の形態のインダクタンス、高いキャパシタンス、広い動作周波数範囲、効率的な成端方式などがある。このように、これら所望の特性の多くまたは全てを単一のモノリシック構造で達成すると、有用な容量性構造が得やすくなる。様々な態様および代替の特徴がコンデンサ技術の分野では既知であるが、本明細書で論じる改善した性能特性の全てを包括的に集約した設計は出現していない。

## [0012]

本明細書においてここまでに引用したもの以外の例示的な背景技術の参考文献としては、 米国特許第5831810号(Bird他)、第5811868号(Bertin他)、 および第5599757号(Wilson他)がある。

# [ 0 0 1 3 ]

前述の全ての米国特許の開示は、参照により本願に完全に組み込まれる。

#### [0014]

#### (発明の概要)

本発明は、コンデンサ技術の特定の態様に関する前述およびその他の欠点のいくつかを認識し、これらに対処するものである。したがって、概して言えば、本明細書に開示する技術の主要な目的は、広い周波数範囲にわたってコンデンサ性能を改善することである。さらに詳細に言えば、本明細書に開示する多層カスケードコンデンサの実施形態は、広い周波数範囲にわたって好ましい動作特性および様々なフレキシビリティを提供するものである。

# [0015]

本発明の別の目的は、複数の構成部品、および集積コンデンサパッケージにおけるそれらの相当の利点を提供することである。複数の構成部品を様々に組み合わせることで、コンデンサ設計と、それによりもたらされる性能とがフレキシブルになる。この集積構造は、並列に配列され相互接続された、スタック状の複数のコンデンサを提供することができる

# [0016]

本技術の別の目的は、所望のキャパシタンス値および動作周波数を含めた、広範囲の動作条件に適応するコンデンサ構成を提供することである。可能な構成は、 0 . 5 μ F から 1 F 超のキャパシタンス範囲および数 k H z から数 G H z の動作周波数範囲を実現できることが好ましい。

# [0017]

本開示の技術の別の目的は、本発明の多層カスケードコンデンサのESRおよびESLに関する。本明細書に開示の実施形態は、低ESLおよび低ESRの両方を特徴とすることが好ましい。ESRは、選択したコンデンサ構成およびその調節可能な態様に応じて所望のレベルに同調可能にすることもできる。

# [0018]

本開示の技術の別の目的は、有利な相互接続フィーチャによって取り付けられたスタック状構成部品を有するカスケードコンデンサを提供することである。この取付けおよび相互接続フィーチャは、一般に構造の高いキャパシタンス値を維持しながら、低インダクタンスおよびその他の利点を提供することが好ましい。本発明では、内部電極の接続または外部電極の接続あるいはその両方を任意に選択できるので、汎用性のある端子構成がもたらされる。

# [0019]

本発明の多層カスケードコンデンサの別の目的は、エポキシ製成型品にカプセル化して、 そこに設けられたコンデンサと任意のワイヤボンドまたはその他の接続手段とを任意選択 でさらに保護することができるモノリシック構造を提供することである。

# [0020]

50

40

20

本発明の別の目的は、本発明のカスケードコンデンサの多層部分に、調節可能な厚さを有する誘電体層を任意選択で設けることである。様々な構成で、隣り合う誘電体層に様々な厚さを持たせることができ、したがって特定の構成に関係する共振曲線を拡大することができる。

# [0021]

開示の技術のさらに別の目的および利点については、本明細書の詳細な説明において述べる。あるいは、本明細書の詳細な説明を読めば当業者には明らかであろう。また、参照により、開示の技術の趣旨および範囲を逸脱することなく、開示の技術の様々な実施形態および用法において具体的に図示、参照および考察した特徴およびステップに対して様々な修正および変更を加えることができることも当業者なら理解されたい。このような変更としては、図示、参照または考察した手段や特徴、材料、またはステップの代わりに、それらと等価な手段や特徴、材料、またはステップを用いること、ならびに様々な部品、特徴またはステップなどの機能、動作または位置を入れ換えることなどが含まれるが、これらに限定されるわけではない。

#### [0022]

さらに、本技術の様々な実施形態ならびに様々な現在好ましい実施形態は、本開示の特徴、ステップまたはエレメントあるいはそれらの均等物の様々な組合せまたは構成を含むことができる(図面に明示していない、もしくは詳細な説明に記載していない特徴またはステップの組合せあるいはそれらの構成も含む)。本発明の第1の例示的な実施形態は、連続的に積み重ねた構成で設けた基板、第1の電極層、第1の絶縁層および第2の電極層を含む多層コンデンサに関する。次いで、電極層の選択した部分に電気的に接続されるように、導電性バイアも設ける。第1および第2の電極層ならびに絶縁層は全て、それぞれの直径を有する複数の貫通孔を画定し、導電性バイアはこれらの貫通孔に通すことができる

# [0023]

この第1の例示的な実施形態は、様々な追加の特徴を組み込むことができる。このような特徴の1つは、第1の絶縁層と第2の電極層の間に設けた抵抗層に相当し、この抵抗層も、導電性バイアを通すことができる複数の貫通孔を画定することができる。この例示的な実施形態のさらに別の考えられる特徴は、基板が外側周縁部を有することを特徴とし、第1および第2の電極層が、それぞれの実質的に連続した部分と、それぞれの連続した部分から基板の外側周縁部に延びる複数のタブ部分とを有することを特徴とすることに関係する。さらに別の任意選択の特徴としては、追加の絶縁層、および/または選択した導電性バイアに取り付けられたはんだ球がある。

# [0024]

本発明の第2の例示的な実施形態は、第1の多層コンデンサと、第2の多層コンデンサと、各多層コンデンサの選択した部分を結合する複数の導電性ランドとを含むカスケードコンデンサに相当する。各多層コンデンサは、それぞれ電極と絶縁層の組合せで形成される。電極層の選択した縁部からそれぞれ複数のタブが延びることができる。第1の多層コンデンサの選択された層は、複数の貫通孔を画定することができ、導電性バイアをこれらの貫通孔に通して、特定の電極層への電気接続を形成することができる。

# [ 0 0 2 5 ]

本開示の技術のこの第2の例示的な実施形態にさらに関連して、例えば表面実装コンデンサ、単層コンデンサ、二重層コンデンサ、電気化学コンデンサ、セラミックコンデンサ、タンタルコンデンサ、および/またはそれらから選択したものの組合せなどの追加のコンデンサを、カスケードコンデンサ実施形態の導電性ランドに結合することもできる。さらに特化した実施形態では、複数のカスケードコンデンサを共通コンデンサに結合することもできる。さらに特化した実施形態は、カスケードコンデンサ中の第2の多層コンデンサの個別の絶縁層の厚さを層ごとに変化させて、デバイスの共振特性を調節するように構成することができる。

# [0026]

50

20

30

20

30

40

50

本発明の第3の例示的な実施形態は、連続的に積み重ねられた複数の電極層および絶縁層と、各電極層の選択された縁部から延びて多層コンデンサの選択された側面で露出する複数のタブと、最上部電極層および隣接するその下の絶縁層を穿孔することによって形成した複数の貫通孔と、選択した貫通孔を通る複数の導電性バイアと、複数のタブのうち選択したものを結合する複数の導電性ランドとを含む多層コンデンサに関する。これらのタブは、インターデジタル型に配列されることが好ましく、貫通孔は、多層コンデンサの連続するその次の電極層を露出させるように形成されることが好ましい。

#### [0027]

本発明の追加の実施形態は、同様に、開示の多層カスケードコンデンサ実施形態の特定の態様を形成する方法論にも関する。この方法論の第1の例示的な実施形態は、多層構成部品の等価直列抵抗(ESR)を調節する方法に相当する。この方法は、絶縁層で分離された第1および第2の電極層を少なくとも含む多層構成部品を作製するステップと、絶縁層と第1または第2の電極層の一方との間に抵抗層を設けるステップと、抵抗層の有効抵抗を変化させることによって構成部品のESRを調節するステップとを含むことができる。さらに詳細には、有効抵抗は、抵抗層の組成または厚さを調節することによって変化させることもできる。別法として、有効抵抗は、電極層の1つを貫通する複数の貫通孔を形成し、次いでこれらの貫通孔のうち選択したものそれぞれの直径を調節して抵抗層の被覆範囲を変化させることによって変化させることもできる。

#### [0028]

本発明による方法論のさらに別の例示的な実施形態は、多層構成部品の共振特性を調節する方法に関する。この方法は、連続的に積み重ねられた複数の電極層を有する多層構成部品を作製するステップと、各電極層の間に挟まれた別個の絶縁層を設けるステップと、別個の絶縁層のうち選択したものの厚さを層ごとに変化させることによって多層構成部品の共振特性を調節するステップとを含むことが好ましい。この変化させるステップは、例えば、層ごとに厚さを連続的に変化させる、厚さをあるパターンで変化させる、および/または厚さを整合して変化させることによって行うことができる。

# [0029]

この概要部では必ずしも明記していないが、本発明のさらに別の実施形態は、上記の要約した本発明の目的記載部分で言及した特徴または部分、および / あるいはその他のかたちで本願で論じる特徴または部分の態様の様々な組合せを含み、かつ組み込むことができる

# [0030]

当業者なら、本明細書の残りの部分を読めば、以上その他の実施形態の特徴および態様がよりよく分かるであろう。

# [0031]

当業者を対象とする、その最良の実施の形態を含む本開示の技術の完全かつ実施可能な説明を、添付の図面を参照する本明細書に記載する。

## [0032]

本明細書および添付の図面を通じて繰り返し使用される参照符は、本開示の技術の同様または類似の特徴または要素を表すものである。

# [ 0 0 3 3 ]

(図面の詳細な説明)

発明の概要の節で既に述べたように、本発明は、広い周波数範囲にわたってコンデンサ性能を改善することに関するものである。さらに詳細には、開示のカスケードコンデンサは、広い動作周波数範囲にわたって、高キャパシタンス、低ESLおよび/または同調可能なESRを提供することが好ましい。

#### [0034]

本発明のカスケードコンデンサは、集積コンデンサパッケージ中に設けられた複数の構成部品を含むことができる。例示的なカスケードコンデンサは、薄膜 B G A コンデンサや、I D C 構造、単層コンデンサ、二重層電気化学コンデンサ、表面実装タンタルコンデンサ

20

30

40

50

、多層コンデンサ(MLC)など、多くの様々な構成部品を含むことができる。あるいは、選択したコンデンサ構成部品の特定の態様を組み合わせて、単一のモノリシックコンデンサ構造を形成することもできる。本技術の好ましい実施形態では、少なくとも 2 つのこれらの構成部品の態様を、それらを集積した構造に組み込む。

[ 0 0 3 5 ]

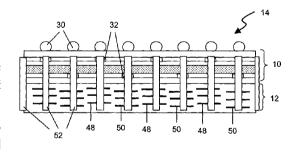

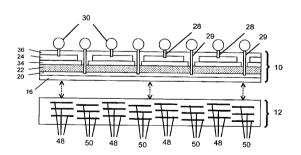

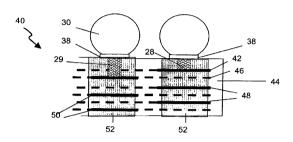

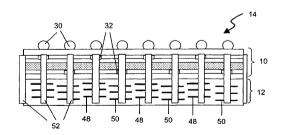

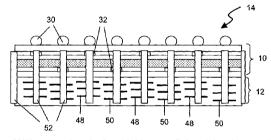

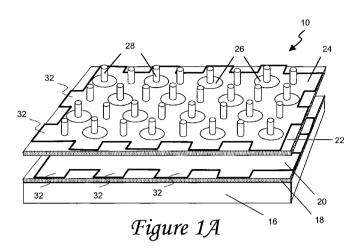

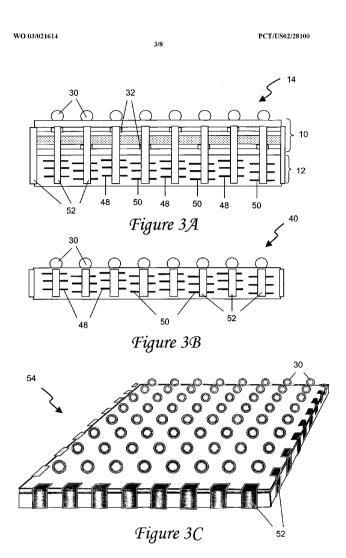

2 つの好ましい構成部品は、図1Aに示すような薄膜BGAコンデンサおよびインターデジタル形コンデンサ(IDC)である。薄膜BGA技法は、低ESLおよび同調可能なESRを提供し、電子プリント配線板(PWB)またはセラミックパッケージに取り付ける手段を提供する。第1の例示的な実施形態は、図1Bおよび図3Aに示すような、薄膜BGAデバイスと並列に電気接続するIDC型構成部品を含む。この例示的な組合せは、2つの減結合レベルを備えたカスケードコンデンサを実現する。

[0036]

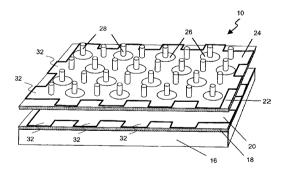

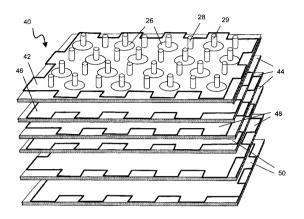

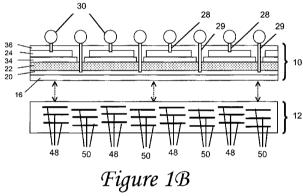

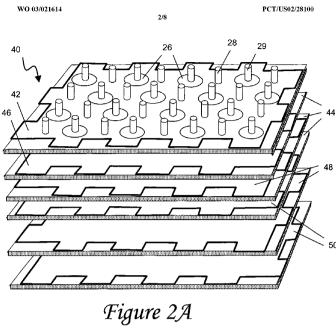

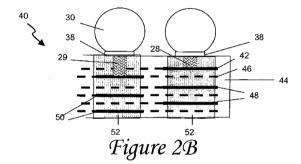

同様の減結合機能を提供する本開示によるカスケードコンデンサの第2の例示的な実施形態は、図2A、図2Bおよび図3Bに示すような、BGA技法をIDCの最上層に取り入れた厚膜構造である。この例示的なカスケードコンデンサ構成およびその他の例示的なカスケードコンデンサ構成は、数キロヘルツから1ギガヘルツまでの周波数範囲にわたる広帯域減結合を実現することができる。選択した構成について可能なキャパシタンス値は、単一の薄膜BGA/IDCの組合せで約0.5µFから約50µFの範囲となる。

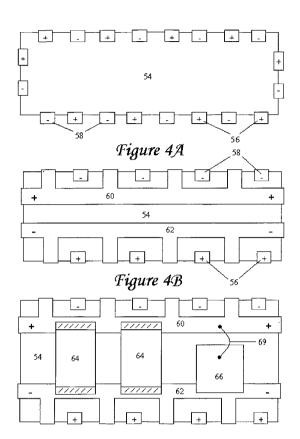

[0037]

図4 A および図4 B は、本発明の選択した実施形態の例示的な成端方式を示す図である。このような端子配列では、選択した実施形態に追加の構成部品を電気的に接続することが可能である。前述の第1または第2の例示的な実施形態のいずれかと組み合わせるこのような追加の構成部品としては、表面実装タンタルコンデンサ、多層コンデンサ、または単層コンデンサなどがある。

[0038]

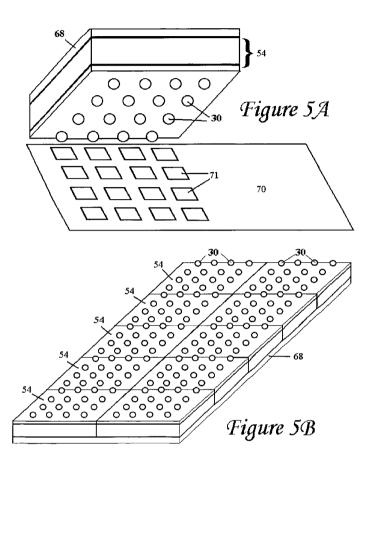

図 5 A は、この実施形態およびその他の実施形態をプリント配線板またはその他の適当な表面に取り付けるための例示的なフィーチャに注目した、本発明のカスケードコンデンサ技術の別の例示的な実施形態を示す図である。図 5 B は、前述の第 1 または第 2 の例示的な実施形態あるいはその他の実施形態と単一の電気化学コンデンサとを組み合わせて、全体のキャパシタンスを向上させたカスケードコンデンサを作製する、本発明のさらに別の例示的な実施形態を示す図である。

[0039]

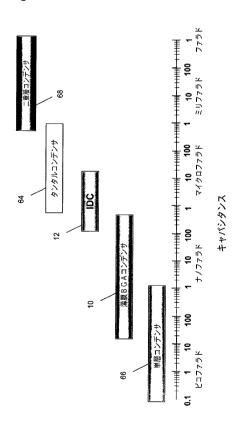

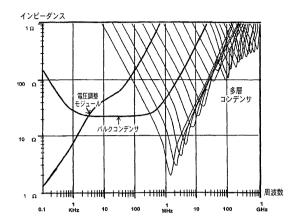

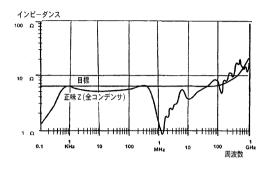

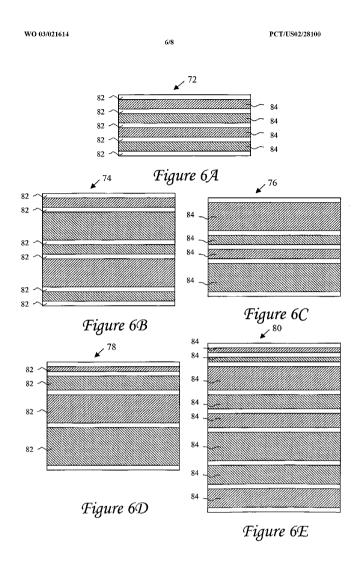

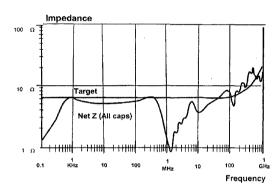

以下では一括して図6と称する図6Aから図6Eは、本発明の様々なカスケードコンデンサの多層部分に応じて適用される誘電体層および電極層の様々な構成を示す図である。図7は、選択したコンデンサ構成部品およびそれらの組合せについて有効な一般的なキャパシタンスの範囲を示す図である。図8Aおよび図8Bは、本発明の選択した実施形態に関連する選択した性能特性を説明するのに役立つインピーダンス曲線を示す図である。

[0040]

これらの例示的な実施形態はそれぞれ、本発明を制限するためのものではないことに留意されたい。ある実施形態の一部として図示または説明した特徴を、別の実施形態の諸態様と組み合わせて使用して、さらに別の実施形態を生み出すこともできる。さらに、特定のフィーチャを、同じまたは同様の機能を実行する明示的には述べていない同様のデバイスまたはフィーチャと置き換えることもできる。

[0041]

これらの図面は、一定の比率で描かれたものではないことを理解されたい。また、各図面中の選択された要素が、同じ図面中のその他の要素と同じ比率では描かれていないことがあることも理解されたい。さらに、本明細書で論じる実施形態の特定の要素を形成する例示的な物質として列挙した材料は、単に例として挙げたものに過ぎず、いかなる意味においても実施したコンデンサの特定の組成を限定するものではない。新たに改良された材料が設計および/または作成された場合には、それらの物質と本明細書に開示の技術とを組

30

40

50

み合わせることが予想されることを理解されたい。

#### [0042]

次に、本発明のカスケードコンデンサ技術の現在好ましい実施形態について詳細に述べのであると、図1Aおよび図1Bは、第1の例示的なカスケードコンデンサ技術の選択したた変にである。図1Aは、本発明のカスケードコンデンサ技術の選択したた変にである。第1の絶縁層18の方である。第1の絶縁層18のだけられる。基板16を形成するために使用することできるが設けられる。基板16を形成するために使用することである。ではカイイがあることである。ではカイイがある。ではかけ、またはでのでのであるしては、ガラスとはそのでのでのであるしては、ガラスとはそのでのではあるにはかり、またはシリコンの方とでは、ガラスにはかり、またはシリコンが一と選択しては、二酸化ケイ素に使用することもできる。基板16と絶縁層18の好ましいに使用することもできる。基板16と絶縁層18の好ましては、二酸化ケイ素絶縁層を備えたシリコンベース基板がある。

#### [0043]

底部電極層 2 0 は、絶縁層 1 8 より上方に配列される。底部電極層 2 0 を形成するために使用できる適当な物質の例としては、白金、ニッケル、パラジウム、ルテニウム、酸化イリジウム、その他の適当な導電性材料、あるいはこれらの物質から選択したものの組合せまたは合金がある。特定の応用分野で使用するるのもまたはこッケルに高部電極層を形成がある。特定の応週またはそのの追当ながある。はこッケルに高部電極層を形成がある。 B G A 構成部品 1 0 および / またはそのの本発明によるために使用が必要となる。このな接着層が必要となる。このな接着層が必要となる。このな接着層に接着層が必要となる。このな接着層に接着層が必要となる。とにより、ニクロム、チタングステン、またはマグネシウムなどの物質を含またはできる。好ましくは、適当な接着層は、スパッタリングを酸化チタンを形成することもできる。

# [0044]

一連のタブ32は、各タブ32がBGA構成部品10の外側表面に向かって延びるように、電極層20の周縁部から延びる。誘電体層22は、底部電極層20を覆って配置され、いくつかの実施形態では、誘電体層22と底部電極層20の間に任意選択の導電性酸化物バッファ層(参照番号なし)を用いることもある。誘電体層22を形成するために使用できる適当な物質の例としては、PbZrTiO₃(PZTと呼ばれることもある)、PNZT、PLZT、PbMg1/₃Nb2/₃O₃・PbTiO₃(PMN-PTと呼ばれることもある)、SrBaTiO₃、BaTiO₃、SrTiO₃、Bi₂SrTa2Og、多結晶セラミックペロブスカイト、多結晶リラクサ型強磁性セラミック酸化物、二酸化ケイ素、Si₃N4、酸窒化ケイ素、A12O₃、Ta2O5、多結晶タングステンブロンズ、多結晶チタン酸ビスマス、およびその他の適当な誘電体材料がある。PZTおよびPNZTは、選択された応用分野で好ましい誘電体材料として一般に利用される。

# [ 0 0 4 5 ]

最上部電極層 2 4 にも、概ね構成部品 1 0 の縁部に向かって延びるタブ 3 2 がついている。最上部電極 2 4 を形成するために使用できる適当な物質の例としては、銅、ニッケル、アルミニウム、パラジウム、金、銀、白金、鉛、スズ、これらの元素から選択したものの組合せ、またはその他の適当な導電性物質がある。誘電体層 2 2 と最上部電極層 2 4 の間に、バリヤ層 3 4 を設けることが好ましい。層 3 4 の性質によって、 B G A 構成部品 1 0 が一般により低いリーク電流とより高い信頼性とを特徴とすることを保証する。この後者

[0046]

次いで、一般にパッシベーション層とも呼ばれる第2の絶縁層36を、最上部電極層24に当てる。このパッシベーション層36は、その下にあるコンデンサの各層を保護し、構成部品を電気的に安定にする助けとなる。パッシベーション層36に適した例示的な材料は、窒化ケイ素(Si6N4)、二酸化ケイ素(SiO2)、酸窒化ケイ素(SiON)、およびSi、HwC、OyNzで表される様々な不定比化合物などの無機材料の薄膜から選択することができる。あるいは、パッシベーション層36は、ポリイミド、エポキシ、またはベンゾシクロブテン(BCB)などの有機ポリマーの様々な膜で構成する、あるいは無機材料層と有機材料層の組合せとして構成することもできる。

[0047]

最上部電極層 2 4 は、底部電極 2 0 への接続経路に非接触孔を提供するための円形開口 2 6 のアレイを有する。同様の孔アレイを、抵抗性バリヤ層 3 4 にも設ける。抵抗性バリヤ層 3 4 の対応する孔よりも大きな孔 2 6 を導電性層 2 4 に設けることにより(図 1 B に示す)、抵抗性バリヤ層 3 4 の露出部分が大きくなる。抵抗性バリヤ層の露出部分が大きくなる。抵抗性バリヤ層の露出部分が大きくなの。近には選択されたカスケードコンデンサ構成の同調可能抵抗を実証している。コンデンサ構成部品 1 0 には導電性バイア 2 8 および 2 9 が挿入され、これらは隣接するものどうしが交互に最上部電極 2 4 と底部電極 2 0 に接触する。その後、はんだ球 3 0 を導電性バイア 2 8 および 2 9 の各端部に取り付け、端子フィーチャを設けることができる。基板 1 6 上に全ての層を堆積させると、薄膜 B G A 構成部品 1 0 がもたらされる。

[0048]

本発明の第1の実施形態14は、薄膜BGA構成部品10と、多層IDC構成部品12とを含む。BGA構成部品10の超低ESLおよび高周波数性能特性と、IDC構成部品12のより大きなキャパシタンスとを組み合わせることにより、減結合機能を有効に発揮する周波数範囲を拡大する。薄膜BGA技法を多層IDC以外の構成部品とともに使用して、さらに別のカスケード構造を形成することもできる。

[0049]

通常のIDCは、電極層および誘電体層の多層配列に相当することができる。このような多層配列の部分展開図を図2Aに示す。好ましくは、各電極層は、平行に配列され、各層からタブ48および50が延び、交互に重なった電極層から延びる電極タブがそれぞれ柱状に整列するようになっている。インターデジタル型端子がこのように配列されることにより、電極構成は一般に低いESLを有することになる。電流は、チップ構成部品のより短い距離を進行し、それによりデバイスの自己誘導が低下することが好ましい。IDCの電極配列は、第1のセットの正極板から流れ出た電流が隣接する負極板のセットに沿って反対方向に戻るようになっている。このように電流が反対方向に流れるようにすることにより、隣り合う電流が同じ方向に流れることによって生じる誘導がかなり低減される。

[0050]

50

40

20

30

40

50

図 3 A は、 B G A 構成部品 1 0 を I D C 構成部品 1 2 に接続するフィーチャを有するカス ケードコンデンサ実施形態14を示す図である。これらの構成部品の選択した側面に沿っ てランド 5 2 を形成し、タブ 3 2 ならびにIDCタブ 4 8 および 5 0 によって形成される 端子を接続することができる。別法として、2組のランド52を設けて、一方のセットを BGA構成部品10用、もう一方のセットをIDC構成部品12用にすることもできる。 その後、これら2組のランドを対合させて、図3Cに示すように、一体化された側面端子 セットを形成することができる。外側ランドを形成するプロセスは、コンデンサの技術分 野の当業者には既知の比較的簡単な技法で実施される。その他の端子フィーチャとしては 、導電性バイア28および29に取り付けることができるはんだ球30またはその他のは んだ要素がある。はんだ球 3 0 を形成する材料の例としては、スズ鉛合金、スズ銅銀合金 、スズ銅合金、スズ銀合金、スズビスマス合金、スズ銀ビスマス合金、スズ銀ビスマス銅 合金、スズアンチモン合金、スズ銀銅アンチモン合金、およびその他の適当な物質がある 。はんだ材料30の流れを制御する助けとなるように、はんだ球30の下に任意選択のア ンダーバンプ金属を追加することが好ましいことが多い。図2Bは、このようなボールリ ミッティング 金 属 ( B L M ) 3 8 の 、 本 発 明 の 技 術 の 例 示 的 な 実 施 形 態 に 対 す る 相 対 位 置 を示す図である。BLM38として使用される例示的な物質は、銅、ニッケル、金、銀、 スズ、鉛、これらの金属元素から選択したものを組み合わせて作成した合金、およびその 他のはんだ付け可能な表面を備えた導電性金属の組合せに相当することができる。特定の 応 用 分 野 で 好 ま し い 例 示 的 な 特 定 の B L M 材 料 と し て は 、 ニ ッ ケ ル / 金 層 ま た は 銅 / ニ ッ ケル/金層がある。この場合、はんだ要素30を、本開示の技術の実施形態により有用に 適 用 し 、 そ の 後 、 カ ス ケ ー ド コ ン デ ン サ 実 施 形 態 を P W B に 接 続 す る た め に 利 用 す る こ と ができる。

[0051]

図2 A、図2 B、および図3 Bは、図1 A および図1 Bを参照して説明した第1の例示的な実施形態と同様の電気的性質をもたらす、本発明の第2の例示的な実施形態に関する。この第2の実施形態40は、12などのIDC型コンデンサの最上層に厚膜型のBGA構成部品を組み込むものである。第1のセットの電極層と対応するタブ48とで、所与の極性を特徴とする端子のセットを形成し、第2のセットの電極層と対応するタブ50とで電極48とは反対の極性を有する端子のセットを形成する。隣接する電極層の間に誘電体層44を設け、例示的なカスケードコンデンサ40を形成する。最上部電極層42は、第1の電極42に対向する第2の電極46につながる非接触経路を実現する孔26のアレイを有する。導電性バイア取付け28および29を利用して、最上部の2つの電極層への交互の接続をもたらす。図2Bの詳細図では、バイア28は電極層42に接続され、バイア29は電極層46に接続される。最上部の2つの層より下方の電極層は、通常の側面端子ランド52で接続されることが好ましい。

[0052]

電極の成端には多くの様々なタイプがあり、これらを本開示のカスケードコンデンサの実施形態に応じて利用することができる。図3Cに示すように、コンデンサの最上部表面および底部表面の周りを囲むランド52を設けた場合には、選択した側面をガラスまたは有機物のはんだ止めでコーティングすることができる。したがって、BLMを修正して適用し、はんだ要素30をリフローイングして、コンデンサの側面に端子構造が形成されないようにしながら、前記実施形態を取り付け、かつ応力を吸収する隔離碍子を提供するはいなする、柱状構造のはんだを提供することができる。別法として、内部バイアでタブ48および50を接続することにより外部ランドを不要にすることもできる。このように、内部バイアによる相互接続または外部バイアによる相互接続の利用を任意に選択できることにより、例示的なカスケードコンデンサ構成の多様性が向上する。

[ 0 0 5 3 ]

再度図2Aおよび図2Bを参照すると、好ましくは、最上部電極層42上に絶縁層を堆積させることができる。柱状バイア28および29にはんだ球30およびBLM38をさらに追加すると、図2Bに示すようなカスケードコンデンサ構成40がもたらされる。

30

40

50

#### [0054]

例示的な実施形態 4 0 (図 2 A 、図 2 B および図 3 B )ならびに例示的な実施形態 1 4 ( 図3A)で利用される成端方式は、多くの利点を提供する。開示の実施形態は、コンデン サの全ての電極層を貫通する孔26ならびにバイア28および29を必要としない。 構成 部品のキャパシタンスが、そのコンデンサの極板の面積に正比例することは既知である。 したがって、コンデンサ本体の全域に孔を設けると、有効キャパシタンスが低下し、デバ イスの信頼性も低下する。本発明の実施形態の選択した成端方式は、その他の成端方式よ り費用対効果が大きく、カスケードコンデンサ設計の全体のキャパシタンス値を低下させ ないので好ましい。例示的な実施形態における孔およびバイアを用いた多くの電極層のへ の 内 部 接 続 は 、 複 雑 な 端 子 配 列 を 生 じ る こ と に な る が 、 こ れ は 一 般 に 低 い イ ン ダ ク タ ン ス を特徴とすることが分かっている。一方、図1Bおよび図2Bに示すような、少数の電極 板のみへの内部接続が、信頼性のかなり高い内部端子配列をもたらすことも分かっている 。ただし、これはキャパシタンスが低下するという特徴がある。したがって、本発明の端 子配列の複雑さ、キャパシタンス、インダクタンスおよび信頼性の間に、両立し得ない部 分があることは明らかである。これらの特徴のうち選択されるものは、特定の応用分野で より望ましいものとすることができる。したがって、内部接続される電極層の数の変更が 可能であることは、本開示の技術の範囲内となるものとする。

#### [0055]

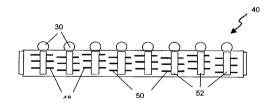

図3Aから図3Cは、本明細書において前述したものなどの例示的なカスケードコンデンサ実施形態を示す図である。図3Aは、組み合わさって薄膜BGA/IDCカスケードコンデンサの第1の実施形態14を形成する全ての要素を示す図である。図3Bは、厚膜BGA/IDCカスケードコンデンサの第2の例示的な実施形態40を示す図である。1つの例示的な実施形態に関連して上記で述べた様々な特徴は、本発明のその他の実施形態に関連して述べた任意選択の層および特徴は、本開示の技術の範囲を逸脱することなく実施形態40またはその他の実施形態に適用することができ、またその逆も可能である。図3Cは、実施形態14または40のいずれかを表す例示的な実施形態54を示す図である。本明細書以下では、BGA/IDC構成部品54は、薄膜カスケードコンザンサ構造14または厚膜モノリシックカスケードコンデンサ実施形態40のいずれに相当することもあることを理解されたい。

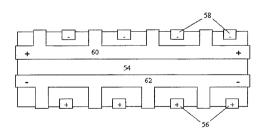

#### [0056]

図4 A および図4 B を参照すると、例示的なカスケードコンデンサ5 4 のための追加の端子フィーチャが示してある。正端子ランド5 6 のうち選択したものを相互に接続する一体化正端子バー6 0 が設けてある。負端子ランド5 8 のうち選択したものを相互に接続する一体化負端子バー6 2 も設けてある。端子バー6 0 および6 2 により、追加の構成部品を例示的なカスケードコンデンサ5 4 に接続することが容易になる。このような端子要素60 および6 2 は、スクリーン印刷する、あるいは直接書込みによる技法またはその他の当技術分野で既知の技法を用いて画定することができる。

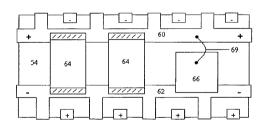

# [0057]

本発明のカスケードコンデンサ技術の別の実施形態を図4Cに示す。この実施形態は、単層コンデンサ66と並んで配列され、本開示の技術によるBGA/IDC構成部品54と電気的に接続された、2つのタンタルまたはセラミック製表面実装コンデンサ64を含む。このようなタンタルデバイス64を含めることで、本技術の選択された実施形態のとりうるキャパシタンス値の範囲が拡大されるので好ましい。小さな表面実装タンタルコンデンサで、高いエネルギー蓄積、高い動作周波数、および所望のESR性能を提供することが好ましい。本技術で使用される表面実装タンタルコンデンサ64の例として、AVVデンサ(SLC)66は、GHz周波数範囲においても信頼できる機能性を得るために、薄膜技法を利用して例示的なコンデンサを提供することが好ましい。本発明で使用する例示的な単層コンデンサは、様々な範囲の能力を有するセラミック誘電体に付着させた金被覆

30

40

50

薄膜層を含むことができる。本技術で使用する単層コンデンサ 6 6 の代替の使用例としては、AVX社製のものなどのAccu-Pブランドのコンデンサがある。

#### [0058]

単層コンデンサ66は、図4Cに示すように、カスケードコンデンサ実施形態54に接続することができる。単層コンデンサ66の底部電極は、選択した端子バー62に取り付けられ、上部電極は、1つまたは複数のワイヤボンド69によってもう一方の端子バー60にワイヤ接合される。端子要素60および62を設けることにより、表面実装タンタルまたは多層セラミックコンデンサ64を実施形態54に接続することが容易になる。単層コンデンサ66を含む図4Cの最終的なカスケード構成およびその他の例示的な実施形態は、個別のコンデンサ構成部品を取り付けるために使用する任意のワイヤボンドを保護するために、エポキシその他の適当な材料の成形コンパウンドでカプセル化されることが好ましい。

#### [0059]

本発明のさらに別の例示的な実施形態は、単一の表面実装タンタルコンデンサ 6 4 に取り付けられた B G A / I D C 構成部品 5 4 を含む。さらに別の実施形態では、カスケード実施形態 5 4 と並列な少なくとも 2 つの表面実装タンタルコンデンサを含むことができる。このようなタンタルコンデンサは、単層コンデンサ 6 6 がなくても、図 4 C に示す実施形態と同様に配列することができる。本技術のその他の例示的な実施形態は、タンタルコンデンサを用いずに、少なくとも 1 つの単層コンデンサと組み合わせて、 B G A / I D C 構成部品 5 4 を含むことができる。

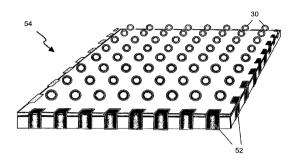

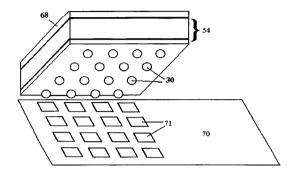

#### [0060]

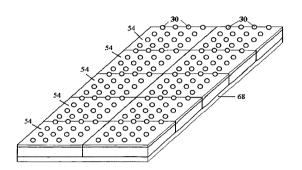

図5 A は、構成部品の1つとしてタンタルコンデンサ、単層コンデンサ、または電気化学コンデンサ68を特徴とする、本発明による例示的なカスケードコンデンサを示す図である。電気二重層コンデンサ68は、BGA/IDC構成部品54と並列に取り付けられ、電気的に接続される。セラミックパッケージまたはPWBにカスケードコンデンサを接続するために、はんだ球30をBGA/IDC構成部品に取り付ける。多数の二重層コンデンサ54はかさばるので、図5Bに示すように、複数のBGA/IDC構成部品54を並列に単一の電気化学的構成部品68に接続すると好都合であることが多い。図5Bの例示的な実施形態は、単一の電気化学コンデンサ68の上に並べて配列された10個のBGA/IDC構成部品54を示している。

#### [0061]

#### [0062]

図 5 A を参照すると、選択したカスケードコンデンサ構成を取り付ける例示的な位置が示してある。はんだ球 3 0 またはその他のはんだ要素は、通常は、構造 5 4 の B G A 型端子部分に取り付けることができる。はんだ球 3 0 は、プリント配線板(PWB) 7 0 上の対応する取付けパッド 7 1 に取り付けることができる。取付けパッド 7 1 は、様々な回路の接続に対応するように様々に配列することができる。カスケードコンデンサ構成内の別個

30

40

50

の構成部品を接続するために、それぞれのパッドおよびはんだバンプの配列を使用することもできる。

#### [0063]

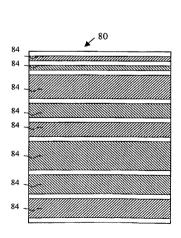

本発明のカスケードコンデンサ技術の特定の例示的な実施形態の利点は、これらの例示的な実施形態に存在する誘電体層の厚さを変化させることによって、また特にこれらの例示的な実施形態のIDC構成部品によってもたらされる共振特性の改善である。交互に配置された誘電体層84および電極層82の通常のパターンを、図6Aの配列72に示す。誘電体層84が一定の厚さを有するこのような配列72は、一般に狭い周波数範囲にわたって低いインピーダンスをもたらす。様々な厚さの誘電体層84を組み込む構成は、コンデンサが好ましいインピーダンス特性を示す周波数範囲を拡大する助けとなる。図6Bに示す配列74は、厚さが連続的に変化する誘電体層84を備える。図6Cおよび図6Dに示す例示的な配列76および78はそれぞれ、一定のパターンで厚さが変化する誘電体層84を備える。図6Eに示す例示的な配列80は、整合して変化する厚さを有する誘電体層84を備える。以上その他の例示的な実施形態は、一般により広い周波数範囲にわたって改善されたコンデンサ性能をもたらす。

#### [0064]

前述のように、約0.5μFから1F超の範囲のキャパシタンスを有するカスケードコン デンサ実施形態を提供することは、本発明の利点である。図7は、選択したカスケードコ ンデンサの諸実施形態について、このような広範囲のキャパシタンス値がどのように有効 となるかを示す図である。本発明のカスケードコンデンサの好ましい実施形態は、薄膜B GA構成部品10およびIDC構成部品12の少なくともいくつかの態様を含む。BGA コンデンサ10のキャパシタンス値は、通常、約10pFから約500nFの範囲であり 、インターデジタル型コンデンサの値は、追加の誘電体層および電極層が設けられること により、約100n F から10μ F 以上の範囲となる。したがって、複数の態様の薄膜 B GAコンデンサ10およびIDC12を組み込んだカスケードコンデンサは、IDC12 によりもたらされる一般に高いキャパシタンスと、BGAコンデンサ10によりもたらさ れる一般に低いインダクタンスとを特徴とする。単層コンデンサ66は、約0.1pFか ら約1nFのキャパシタンス範囲を維持しながら、さらに高い動作周波数範囲を示す。タ ンタルコンデンサは、約1μFから約1mFのキャパシタンス範囲を示しながら、将来的 に実現する可能性のあるカスケードコンデンサの実施形態にさらなる利点をもたらす。複 数 の 態 様 の 二 重 層 電 気 化 学 コ ン デ ン サ 6 8 を 含 む カ ス ケ ー ド コ ン デ ン サ は 、 一 般 に 高 い キ ャパシタンスを特徴とする。したがって、二重層コンデンサ68は、一般に、約1mFか ら約1Fのキャパシタンスを有する。したがって、特定のコンデンサの態様を選択して組 み合わせて、様々な潜在的なキャパシタンス値を有するカスケードコンデンサの実施形態 を生み出すことができる。多層表面実装コンデンサを使用することもでき、これらは10 、12および64の範囲をカバーする。

#### [0065]

例示的なデータでは、約5~10m の目標インピーダンスが一般に達成される。

#### [0066]

特定の実施形態に関連して本発明について詳細に説明したが、当業者なら、前述の内容を理解すれば、これらの実施形態の改変形態、変更形態、および均等物を容易に生み出すことができることを理解されたい。したがって、本開示の範囲は、限定ではなく例示を目的としたものであり、本開示は、当業者なら容易に思いつく本発明の修正、変更および/または追加を含むことを排除しない。

# 【図面の簡単な説明】

## 【図1A】

本発明の第1の例示的な実施形態に関する図であり、本発明の特定の実施形態に従って使用される例示的な薄膜ボールグリッドアレイ(BGA)コンデンサ構成の部分展開図である。

#### 【図1B】

本発明の第1の例示的な実施形態に関する図であり、図1Aに示すような薄膜BGA構成部品とインターデジタル型コンデンサ(IDC)構成部品とを含む、本発明のカスケードコンデンサ技術の例示的な実施形態を示す図である。

# 【図2A】

本発明の第2の例示的な実施形態に関する図であり、本発明のコンデンサ技術の第2の例示的な実施形態の部分展開図である。

## 【図2B】

本発明の第2の例示的な実施形態に関する図であり、図2Aに示すものなどの本発明の第2の例示的な実施形態の詳細図である。

# 【図3A】

本発明のカスケードコンデンサ技術の例示的な実施形態を示す図である。

#### 【図3B】

本発明のカスケードコンデンサ技術の例示的な実施形態を示す図である。

#### [図3C]

本発明のカスケードコンデンサ技術の例示的な実施形態を示す図である。

# 【図4A】

例 示 的 な 端 子 フ ィ ー チ ャ に 注 目 し た 、 本 発 明 の 例 示 的 な 実 施 形 態 を 示 す 図 で あ る 。

#### 【図4B】

例示的な端子フィーチャに注目した、本発明の例示的な実施形態を示す図である。

#### 【図4C】

選択した追加の構成部品が並列に接続されて、本開示の技術によるカスケードコンデンサのさらに別の実施形態を形成している、本発明の例示的な実施形態を示す図である。

# 【図5A】

プリント配線板またはその他の適当な表面上に取り付けるための手段を有する、本発明の 技術の例示的なカスケードコンデンサを示す図である。

# 【図5B】

本 発 明 に よ る カ ス ケ ー ド 構 造 を 複 数 レ ベ ル 備 え た 例 示 的 な カ ス ケ ー ド コ ン デ ン サ を 示 す 図 40 で あ る 。

#### 【図 6 A 】

本発明のカスケードコンデンサ設計の多層部分の例示的な構成を示す図であり、一定の厚さを有する誘電体層を備えた例示的な多層配列に対応する図である。

#### 【図 6 B】

本発明のカスケードコンデンサ設計の多層部分の例示的な構成を示す図であり、様々な厚さを有する誘電体層を備えた例示的な多層コンデンサ配列に対応する図である。

#### 【図60】

本発明のカスケードコンデンサ設計の多層部分の例示的な構成を示す図であり、様々な厚さを有する誘電体層を備えた例示的な多層コンデンサ配列に対応する図である。

10

20

30

# 【図 6 D】

本発明のカスケードコンデンサ設計の多層部分の例示的な構成を示す図であり、様々な厚さを有する誘電体層を備えた例示的な多層コンデンサ配列に対応する図である。

# 【図 6 E】

本発明のカスケードコンデンサ設計の多層部分の例示的な構成を示す図であり、様々な厚さを有する誘電体層を備えた例示的な多層コンデンサ配列に対応する図である。

# 【図7】

本発明のカスケードコンデンサ技術による構成部品の選択した組合せについて有効なキャパシタンスの例示的な範囲を示す図である。

# 【図8A】

本発明の選択した実施形態に対応する例示的なインピーダンス曲線を示す図である。

## 【図 8 B 】

本発明の選択した実施形態に対応する例示的なインピーダンス曲線を示す図である。

# 【図1A】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図3C】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

# 【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図7】

【図8A】

【図8B】

# 【国際公開パンフレット】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

#

# (43) International Publication Date 13 March 2003 (13.03.2003)

PCT

English

# WO 03/021614 A1

H01G 4/00. (51) International Patent Classification<sup>7</sup>: 4/228, 4/06, 4/20, 4/38

(22) International Filing Date: 5 September 2002 (05.09.2002)

(25) Filing Language:

(26) Publication Language:

(30) Priority Data: 5 September 2001 (05.09.2001) US 4 September 2002 (04.09.2002) US 60/317,356 Not furnished

(71) Applicant: AVX CORPORATION [US/US]; 801–17th Avenue South, Myrtle Beach, SC 29577 (US).

(72) Inventors: GALVAGNI, John, L.; 1450B Turkey Ridge Road, Surfside Beach, SC 29575 (US). HEISTAND, Robert, II; 3511 Brampton Drive, Myrtle Beach, SC

29588 (US). KORONY, Gheorghe; 4 Sioux Trail, Myrtle Beach. SC 29588 (US).

(21) International Application Number: PCT/US02/28100 (74) Agent: MOOSE, Richard, M.; Doroty & Manning, P.A., P.O. Box 1449, Greenville, SC 29602-1449 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FL, GB, GD, GF, GH, GM, IIR, IIU, DL, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NY, PL, FL, RO, RU, SI, SE, SG, SI, SK, SI, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, VU, ZA, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TI, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, II, IFX, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BB, CF), CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: CASCADE CAPACITOR

A1

52

(57) Abstract: Multi-layer and cascade capacitors for use in high frequency applications and other environments are disclosed. The subject capacitor may comprise multiple capacitor components (II) or aspects thereof in an integrated package. Such components may include, for example thin film BdA components, interdigitated capacitors (IIX) configurations, double-layer electrochemical capacitors, single layer capacitors and others. Exemplary embodiments of the present subject matter preferably encompass at least certain aspects of thin film BdA techniques and/or IIX-vile configurations. Features for attachment and interconnection are provided that facilitate low ESL with maintaining a given capacitance value. Additional advantages include low ESL and decoupling performance over a broad band of operational frequencies. More particularly, the presently disclosed technology provides for exemplary capacitors that may function over a frequency range from kilohertz up to several gigahertz, and that may also be characterized by a wide range of capacitance values. An additionally disclosed feature of the present subject matter is to incorporate dielectric layers (22) of varied thicknesses to broaden the resonancy curve associated with a particular configuration.

# WO 03/021614 A1

before the expiration of the time limit for amending the for two-letter codes and other abbreviations, refer to the "Guid-claims and to be republished in the event of receipt of ance Notes on Codes and Abbreviations" appearing at the begin-ning of each regular issue of the PCT Gazette.

WO 03/021614 PCT/US02/28100

1

#### UNITED STATES PATENT APPLICATION

#### TITLE: CASCADE CAPACITOR

#### PRIORITY CLAIM

This application claims the benefit of previously filed U.S. Provisional Patent Application with the same inventors as present, entitled "Cascade Capacitor," assigned USSN 60/317,356, filed September 5, 2001, and which is incorporated herein by reference for all purposes.

#### BACKGROUND OF THE INVENTION

The present subject matter generally concerns multilayer and cascade capacitors for use in a range of frequency applications including high frequency applications, and more particularly concerns multiple capacitor components provided in monolithic packages. The present subject matter utilizes interconnect and attachment features to create devices with improved and/or idealized performance characteristics, including high capacitance, low equivalent series inductance (ESL), and low or tunable equivalent series resistance (ESR).

The diversity of modern technical applications creates a need for efficient electronic components and integrated circuits for use therein. Capacitors are a fundamental component used for filtering, decoupling, bypassing and other aspects of such modern applications which may include wireless communications, alarm systems, radar systems, circuit switching, matching networks, and many other applications. A dramatic increase in the speed and packing density of integrated circuits requires advancements in decoupling capacitor technology in

WO 03/021614

PCT/US02/28100

2

particular. When high-capacitance decoupling capacitors are subjected to the high frequencies of many present applications, performance characteristics become increasingly more important. Since capacitors are fundamental to such a wide variety of applications, their precision and efficiency is imperative. Many specific aspects of capacitor design have thus been a focus for improving the performance characteristics of capacitors.

The incredible variety of capacitor environments implies that capacitors are often subjected to a number of different operating frequencies. Many wireless communications systems, including satellite, GPS, and cellular applications, as well as high speed processor applications require capacitor technology that can accommodate high frequencies of operation. Examples of capacitor technology that are designed to accommodate a generally higher frequency range of operation are disclosed in U.S. Patent Nos. 6,208,501 B1 (Ingalls et al.); 6,023,408 (Schaper); 5,886,867 (Chivukula et al.); 5,576,926 (Monsorno); and 5,220,482 (Takemura et al.). Capacitors are often designed either for such high frequency applications or for other lower frequency applications, but not both. Thus, a need exists for capacitors with diverse capabilities that are compatible with ideal operation over a wide range of frequencies. Examples of capacitors that may operate well in some limited range of frequencies can be found in U.S. Patent Nos. 6,184,574 B1 (Bissey); 6,038,122 (Bergstedt et al.); and 5,786,978 (Mizuno).

Just as capacitors may be subjected to different frequencies of operation, so might they be subjected to different temperatures of operation. Acceptable performance at a given temperature often relates to the temperature coefficient of capacitance of the dielectric WO 03/021614 PCT/US02/28100

3

material used to form the capacitor. An existing technique that allows for desired capacitor operation at different temperatures involves stacking capacitors formed with different dielectric materials. Examples of this stacking technique can be found in U.S. Patent Nos. 5,799,379 and 5,517,385 (Galvagni et al.).

An actual capacitor has an inherent resistance value that may not exist in a theoretical situation. This additional property of a capacitor is often referred to as equivalent series resistance (ESR). It is desired to create a capacitor that operates as close to theoretical operation as possible, and thus capacitors with low ESR are generally preferred. The need for minimal ESR is especially evident in decoupling capacitor applications. Increased ESR can increase the ripple voltage and power dissipation for a given capacitance value. This is related to the RC time constant of a capacitor and contributes to the need for low capacitor ESR. An example of a capacitor designed to offer low ESR is disclosed in U.S. Patent No. 6,226,170 B1 (Nellison et al.).

Another way to achieve improved capacitor performance is by lowering the inductance of the device. Thus, it is preferred for decoupling capacitors to provide low equivalent series inductance (ESL) in order to maintain circuit efficiency. It may also be preferred to implement a capacitor design that reduces the self and mutual inductance of decoupling capacitors. U.S. Fatent No. 6,038,121 (Naito et al.) and U.S. Patent No. 6,034,864 (Naito et al.) show exemplary capacitor configurations that are designed to cancel magnetic flux

Reducing the current path will lower self inductance. Since the current often has to travel the

and reduce ESL.

WO 03/021614 PCT/US02/28100

4

entire length of the capacitor, termination on the longer ends of the structure will reduce the current path. If the current in adjacent capacitor electrodes flows in opposite directions it will reduce the mutual inductance in a capacitor. Multiple terminations as utilized in interdigitated capacitor technology also lower the inductance value. U.S. Patent Nos. 5,880,925 (<u>DuPré et al.</u>) and 6,243,253 Bl (<u>DuPré et al.</u>) disclose multilayer capacitors that offer some of the aforementioned lower inductance characteristics. The basic configuration discussed in these DuPré patents corresponds to a type of multilayer capacitor hereafter referred to as an interdigitated capacitor (IDC).

Another approach to lowering the ESL of a decoupling capacitor is to minimize interconnect induction that results from termination configurations and mounting systems. Certain known termination schemes are characterized by high inductance and often prohibit very close spacing between components. Thus, an efficient termination scheme is desired that has low ESL and that facilitates high component density for integrated circuits. Thin film capacitor technology is used to provide exemplary capacitors for mounting on a substrate in U.S. Patent No. 6,104,597 (Konushi) and U.S. Patent No. 4,439,813 (Dougherty et al.).

Known termination schemes utilize electrode plates with hole arrangements therein to connect with internal columnar electrodes. Such arrangement provides a space-saving interconnect scheme with lowered ESL, but the hole arrangements in the capacitor electrodes reduce the overall capacitance of the structure by decreasing the effective area. An excess of these clearance holes can also contribute to shorting problems as the number of layers with them increases. An example of such a

WO 03/021614

5

PCT/US02/28100

5

termination scheme can be found in European Patent

Application 1,115,129 A2 (Ahiko and Ishigara.). Thus, a

need exists for a termination scheme that provides low

inductance as well as high capacitance.

There are many different performance characteristics of a capacitor for which improvement may be sought to facilitate desired operation. Selected of such characteristics as mentioned and discussed above may include low ESR, low ESL and other forms of inductance, high capacitance, broad frequency range of operation, efficient termination scheme and others. Achieving many or all of these desired characteristics in a single monolithic structure would thus facilitate a beneficial capacitive structure. While various aspects and alternative features are known in the field of capacitor technology, no one design has emerged that generally integrates all of the improved performance characteristics as discussed herein.

Exemplary background references in addition to those already cited in the specification include U.S. Patent Nos. 5,831,810 (<u>Bird et al.</u>); 5,811,868 (<u>Bertin et al.</u>); and 5,599,757 (<u>Wilson et al.</u>).

The disclosures of all the foregoing United States patents are hereby fully incorporated into this application by reference thereto.

## BRIEF SUMMARY OF THE INVENTION

The present subject matter recognizes and addresses various of the foregoing shortcomings, and others concerning certain aspects of capacitor technology. Thus, broadly speaking, a principal object of the presently disclosed technology is improved capacitor performance over a wide range of frequencies. More particularly, the disclosed multi-layer and cascade capacitor embodiments offer preferred operating

WO 03/021614 PCT/US02/28100

6

characteristics and a variety of flexibility over a wide frequency range.

Another object of the present subject matter is to provide multiple components and corresponding advantages thereof in an integrated capacitor package. Varied combinations of the multiple components offers flexibility in the capacitor design and resulting performance. The integrated structure may provide a plurality of stacked capacitors arranged and interconnected in parallel.

Yet another object of the subject technology is to provide capacitor configurations that accommodate a wide range of operating conditions, including desired capacitance value and frequency of operation. Preferably, possible configurations can provide a capacitance range from 0.5  $\mu F$  to over 1 F and an operating frequency range from several KHz to several GHz.

A still further object of the presently disclosed technology relates to the ESR and ESL of the subject multi-layer and cascade capacitors. The embodiments disclosed herein are preferably characterized by both low ESL and low ESR. The ESR may also be tunable to a desired level in accordance with selected capacitor configurations and adjustable aspects thereof.

It is another object of the presently disclosed technology to provide a cascade capacitor whose stacked components are attached by advantageous interconnect features. Such attachment and interconnect features preferably offer low inductance and other advantages while maintaining a generally high capacitance value of the structure. The option of internal and/or external electrode connections in accordance with the present

WO 03/021614 PCT/US02/28100

7

subject matter provides versatile termination configurations.

15

It is another object of the subject multi-layer and cascade capacitors to provide a monolithic structure that can be encapsulated in an epoxy molding to offer optional additional protection of the capacitor and any wire bonds or other connection means provided thereon.

It is yet another object of the present subject matter to optionally provide dielectric layers in multilayer portions of the subject cascade capacitor that have adjustable thickness. Different configurations can provide adjacent dielectric layers with varied thickness, thus broadening the resonance curve associated with a particular configuration.

Additional objects and advantages of the disclosed technology are set forth in, or will be apparent to those of ordinary skill in the art from, the detailed description herein. Also, it should be further appreciated by those of ordinary skill in the art that modifications and variations to the specifically illustrated, referenced, and discussed features and steps hereof may be practiced in various embodiments and uses of the disclosed technology without departing from the spirit and scope thereof, by virtue of present reference thereto. Such variations may include, but are not limited to, substitution of equivalent means and features, materials, or steps for those shown, referenced, or discussed, and the functional, operational, or positional reversal of various parts, features, steps, or the like.

Still further, it is to be understood that different embodiments, as well as different presently preferred embodiments, of this technology may include various combinations or configurations of presently disclosed WO 03/021614

15

PCT/US02/28100

features, steps, or elements, or their equivalents (including combinations of features or steps or configurations thereof not expressly shown in the figures or stated in the detailed description). A first exemplary embodiment of the present subject matter relates to a multi-layer capacitor comprising a substrate, a first electrode layer, a first insulating layer, and a second electrode layer provided in a successively stacked configuration. Electrically conductive vias are then also provided for electrical connection to selected portions of the electrode layers. The first and second electrode layers and the insulating layer all define respective pluralities of through-holes having respective diameters thereof through which the conductive vias may pass.

A variety of additional features may be incorporated with such first exemplary embodiment. One such feature corresponds to a resistive layer provided between the first insulating layer and the second electrode layer, wherein such resistive layer may also define a plurality of through-holes through which the conductive vias may pass. Yet another potential feature of such exemplary embodiment regards the substrate being characterized by an outer perimeter and the first and second electrode layers being characterized by respective substantially continuous portions and a plurality of tab portions extending from the respective continuous portions to the outer perimeter of the substrate. Still further optional features include additional insulating layers and/or solder balls attached to selected conductive vias.

A second exemplary embodiment of the present subject matter corresponds to a cascade capacitor comprising a first multi-layer capacitor, a second multi-layer capacitor and a plurality of electrically conductive WO 03/021614 PCT/US02/28100

9

lands coupling selected portions of the respective multilayer capacitors. Each multi-layer capacitor is formed by a respective combination of electrode and insulating layers. Respective pluralities of tabs may extend from selected edges of the electrode layers. Selected layers of the first multi-layer capacitor may define throughholes through which conductive vias may pass to form electrical connections to certain electrode layers.

With further reference to such second exemplary embodiment of the disclosed technology, additional capacitors, such as for example a surface mount capacitor, a single layer capacitor, a double layer capacitor, an electro-chemical capacitor, a ceramic capacitor, an electro-chemical capacitor, a ceramic capacitor, a tantalum capacitor, and/or selected combinations thereof, may also be coupled to conductive lands of the cascade capacitor embodiment. In more particular embodiments, a plurality of cascade capacitors may be coupled to a common capacitor. Still further particular embodiments may be formed such that the thickness among distinct insulating layers of the second multi-layer capacitor in the cascade capacitor are varied to adjust the resonance characteristics of the device.

A third exemplary embodiment of the present subject matter concerns a multi-layer capacitor comprising a plurality of electrode layers and insulating layers stacked successively, a plurality of tabs extending from selected edges of respective electrode layers and exposed on selected sides of the multi-layer capacitor, a plurality of through-holes formed by and perforating the top-most electrode layer and the adjacent underlying insulating layer, a plurality of conductive vias passing through selected through-holes, and a plurality of electrically conductive lands coupling selected of the plurality of tabs. The tabs may preferably be arranged

PCT/US02/28100

in an interdigitated fashion, and the through-holes are preferably formed to expose the next successive electrode layer of the multi-layer capacitor.

Additional embodiments of the present subject matter equally concern methodology in forming certain aspects of the disclosed multi-layer and cascade capacitor embodiments. A first exemplary embodiment of such methodology corresponds to a method for adjusting the equivalent series resistance (ESR) of a multi-layer component. The method may comprise such steps as producing a multi-layer component including at least first and second electrode layers separated by an insulating layer, providing a resistive layer between the insulating layer and one of the first or second electrode layers, and adjusting the ESR of the component by varying the effective resistance of the resistive layer. More particularly, the effective resistance may be varied by adjusting the composition or thickness of the resistive layer. Alternatively, the effective resistance may be varied by forming a plurality of through-holes perforating one of the electrode layers and by then adjusting the respective diameters of selected of the through-holes to vary the extent of coverage on the resistive layer.

A further exemplary embodiment of methodology in accordance with the present subject matter relates to a method of adjusting the resonance characteristics of a multi-layer component. Such method preferably comprises the steps of producing a multi-layer component having a plurality of successively stacked electrode layers, providing separate insulating layers sandwiched between each of the electrode layers, and varying the thickness among selected of the separate insulating layers whereby the resonance characteristics of the multi-layer

25

15

25

PCT/US02/28100

component are adjusted. Such varying step may be accomplished for example with continuous thickness variation, with patterned thickness variation, and/or with matched variable thickness variation among layers.

11

Additional embodiments of the present subject matter, not necessarily expressed in this summarized section, may include and incorporate various combinations of aspects of features or parts referenced in the summarized objectives above, and/or features or parts as otherwise discussed in this application.

Those of ordinary skill in the art will better appreciate the features and aspects of such embodiments, and others, upon review of the remainder of the specification.

### BRIEF DESCRIPTION OF THE DRAWINGS

A full and enabling description of the presently disclosed technology, including the best mode thereof, directed to one of ordinary skill in the art, is set forth in the specification, which makes reference to the appended figures, in which:

Figures 1A and 1B relate to a first exemplary embodiment of the present subject matter; in which

Figure 1A displays a partially exploded view of an exemplary thin film ball grid array (BGA) capacitor configuration for use in accordance with certain embodiments of the present subject matter;

Figure 1B displays an exemplary embodiment of the subject cascade capacitor technology, comprising a thin film BGA component such as that displayed in Figure 1A and an interdigitated capacitor (IDC) component;

Figures 2A and 2B relate to a second exemplary embodiment of the present subject matter; in which

15

25

PCT/US02/28100

12

Figure 2A illustrates a partially exploded view of a second exemplary embodiment of the subject capacitor technology;

Figure 2B displays a detailed view of a second exemplary embodiment of the present subject matter, such as that illustrated in Figure 2A:

Figures 3A through 3C, respectively, show varied illustrations of exemplary embodiments of the subject cascade capacitor technology;

Figures 4A and 4B display exemplary embodiments of the present subject matter, with a focus on exemplary termination features;

Figure 4C illustrates an exemplary embodiment of the present subject matter with selected additional components connected in parallel to form a yet further embodiment of a cascade capacitor in accordance with the presently disclosed technology;

Figure 5A illustrates an exemplary cascade capacitor of the present technology with means for mounting on a printed wire board or other appropriate surface;

Figure 5B depicts an exemplary cascade capacitor with multiple levels of cascaded structures in accordance with the present subject matter;

Figures 6A through 6E represent exemplary configurations for multilayered portions of the subject cascade capacitor designs; in which

Figure 6A corresponds to an exemplary multilayer arrangement with dielectric layers having fixed thickness;

Figures 6B, 6C, 6D and 6E, respectively, correspond to exemplary multilayer capacitor arrangements with dielectric layers having varied thickness;

Figure 7 illustrates an exemplary range of capacitance values available for selected combinations of

PCT/US02/28100

1

components in accordance with the subject cascade capacitor technology; and

Figures 8A and 8B display exemplary impedance curves corresponding to selected embodiments of the present subject matter.

Repeat use of reference characters throughout the present specification and appended drawings is intended to represent same or analogous features or elements of the disclosed technology.

#### DETAILED DESCRIPTION OF THE DRAWINGS

As referenced in the Brief Summary of the Invention section, supra, the present subject matter is directed towards improved capacitor performance over a wide range of frequencies. More particularly, the disclosed cascade capacitor preferably offers large capacitance, low ESL and/or tunable ESR over a wide frequency range of operation.

The subject cascade capacitor may comprise multiple components that are provided in an integrated capacitor package. Exemplary cascade capacitors may comprise many different components, including thin film BGA capacitors, IDC structures, single layer capacitors, double-layer electrochemical capacitors, surface mount tantalum capacitors, multilayer capacitors (MLCs) and others. Alternatively, certain aspects of selected capacitor components may be combined to form a single monolithic capacitor structure. Preferred embodiments of the subject technology incorporate aspects of at least two of these components into their integrated structure.

Two preferred components are thin film BGA capacitors, such as that illustrated in Figure 1A, and interdigitated capacitors (IDCs). Thin film BGA techniques offer low ESL and tunable ESR, and offer a means for attaching to an electronic printed wire board

PCT/US02/28100

14

(PWB) or ceramic package. A first exemplary embodiment comprises an IDC style component for electrically connecting in parallel with a thin film BGA device, such as displayed in Figures 1B and 3A. Such exemplary combination provides a cascade capacitor with two levels of decoupling.

A second exemplary embodiment of a cascade capacitor in accordance with the present disclosure that offers similar decoupling capabilities is a thick film construction that incorporates BGA techniques into the top layer of an IDC, such as disclosed in Figures 2A, 2B and 3B. This and other exemplary cascade capacitor configurations can provide broadband decoupling over a frequency range from kilohertz up to a gigahertz. Possible capacitance values for selected configurations might range from about 0.5 µF to about 50 µF for a single thin film BGA/IDC combination.

Figures 4A and 4B illustrate an exemplary termination scheme for selected embodiments of the present subject matter. Such a termination arrangement allows for electrical connection of additional components with the selected embodiments. Such additional components for combination with either of the aforementioned first or second exemplary embodiments may include surface mount tantalum capacitors, multilayer capacitors or single layer capacitors.

Figure 5A illustrates another exemplary embodiment of the subject cascade capacitor technology, with a focus towards exemplary features for attaching such an embodiment and other embodiments to a printed wire board or other appropriate surface. Figure 5B displays yet another exemplary embodiment of the present subject matter that incorporates either of the aforementioned first or second exemplary embodiments or others with a

15

PCT/US02/28100

1.5

single electrochemical capacitor to create a cascade capacitor with increased overall capacitance.

Figures 6A through 6E, hereafter collectively referred to as Figure 6, display varied configurations of dielectric layers and electrode layers for application in accordance with multilayer portions of the subject cascade capacitors. Figure 7 illustrates general capacitance ranges that may be available for selected capacitor components and combinations thereof. Figures 8A and 8B display impedance curves that help illustrate selected performance characteristics associated with selected embodiments of the present subject matter.

It should be noted that each of the exemplary embodiments should not insinuate limitations of the present subject matter. Features illustrated or described as part of one embodiment may be used in combination with aspects of another embodiment to yield yet further embodiments. Additionally, certain features may be interchanged with similar devices or features not expressly mentioned which perform the same or similar function.

It should be appreciated that the figures are not drawn to scale. Also, it should be appreciated that selected elements of each figure may not be represented in proportion to other elements in that figure. In addition, materials that are listed as exemplary substances for forming certain elements of the embodiments as discussed herein are merely presented as examples, and should in no way limit the specific composition of the capacitor embodiments. It should be appreciated that as newly improved materials are designed and/or created, incorporation of such substances with the technology disclosed herein will be anticipated.

PCT/US02/28100

16

Reference will now be made in detail to the presently preferred embodiments of the subject cascade capacitor technology. Referring now to the drawings, Figures 1A and 1B relate to a first exemplary cascade capacitor embodiment. Figure 1A illustrates a thin film BGA capacitor component 10 for use in accordance with selected embodiments of the subject cascade capacitor technology. A substrate 16 is provided onto which a first insulating layer 18 is deposited. Examples of suitable substances that might be used to form substrate 16 include silicon, glass ceramic, alumina, aluminum nitride, silicon carbide, zinc oxide, BaTIO3, varistor ceramics, perovskite ceramics, oxide ceramics, non-oxide ceramics, or other high temperature inert materials. Selected of the above-listed suitable substrate materials that may be preferred for use in selected applications include glass, glass ceramic, or silicon wafer. A suitable material may also be selected for insulating layer 18, also sometimes referred to as a planarization layer. A buffer type of insulation layer may be preferred for use with substrate materials having resistive, semi-conductive or conductive characteristics. Other particular materials may be chosen to use in conjunction with generally rough substrate materials. An example of a preferred combination of substrate 16 and insulation layer 18 is a silicon-based substrate with a silicon dioxide insulating layer.

A bottom electrode layer 20 is arranged above the insulating layer 18. Examples of suitable substances that might be used to form bottom electrode layer 20 include platinum, gold, nickel, palladium, ruthenium, iridium, ruthenium oxide, iridium oxide, other suitable conductive materials, or a combination or alloy of selected of the above-references substances. Selected of

15

PCT/US02/28100

1

the above-listed suitable materials for forming a bottom electrode layer in accordance with the present subject matter that may be preferred for use in certain applications may correspond to platinum, gold or nickel. Some combinations of selected materials for use in forming BGA component 10 and/or other embodiments of the present subject matter require an adhesion layer in between insulating layer 18 and bottom electrode 20. Such an adhesion layer (unlabeled) may comprise such exemplary substances as titanium dioxide, titanium, tantalum, chromium, tantalum nitride, titanium nitride, nichrome, titanium/tungsten, or magnesium. A suitable adhesion layer may also preferably be formed of titanium dioxide from oxidation of sputtered titanium or reactive sputtering of titanium in oxygen to form titanium dioxide.

A series of tabs 32 extends from around the edges of electrode layer 20 such that each tab 32 extends to an outer surface of BGA component 10. A dielectric layer 22 is placed over bottom electrode layer 20, with some embodiments utilizing an optional conductive oxide buffer layer (unlabeled) in between the dielectric layer 22 and bottom electrode layer 20. Examples of suitable substances that might be used to form dielectric layer 22 include PbZrTiO $_{\rm 3}$  (also referred to as PZT), PNZT, PLZT,  $PbMg_{1/3}Nb_{2/3}O_3-PbTiO_3$  (also referred to as PMN-PT), SrBaTiO3, BaTiO3, SrTiO3, Bi2SrTa2O9, polycrystalline ceramic perovskites, polycrystalline relaxor ferroelectric ceramic oxides, silicon dioxide, Si<sub>2</sub>N<sub>4</sub>. silicon oxynitride,  $Al_2O_3$ ,  $Ta_2O_5$ , polycrystalline tungsten bronzes, polycrystalline bismuth titanates, and other suitable dielectric materials. PZT and PNZT are commonly employed as a preferred dielectric material for selected applications.

PCT/US02/28100

18

A top electrode layer 24 is applied, also with tabs 32 generally extending to the edges of component 10. Examples of suitable substances that may be used for forming top electrode 24 include copper, nickel, aluminum, palladium, gold, silver, platinum, lead, tin, select combinations of the aforementioned elements, or other suitable conductive substances. A barrier layer 34 is preferably provided between the dielectric layer 22 and top electrode layer 24. Properties of layer 34 ensure that BGA component 10 is characterized by generally lower leakage currents and more reliability. This latter feature is typically enabled by the fact that the thickness of the resistive barrier layer 34 and/or the extent of coverage of the top electrode 24 can be easily adjusted, providing a tunable and controlled internal resistance. A generally small but tunable ESR may often be more desirable than negligible ESR in a capacitor component to avoid potential ringing in the resultant circuit. Layer 34 offers further advantages to a capacitor embodiment of the present technology. Such advantages may include preventing diffusion of the metal electrode layers into a dielectric or other layer. reducing the chance of shorting or conduction through a dielectric substance, promoting adhesion of an electrode, altering the polarity of a capacitor device, or promoting self-heating of a device. Examples of substances commonly employed in resistive barrier layers 34 include titanium, tantalum, chromium, titanium nitride, titanium/ tungsten, tungsten, magnesium and others as readily understood and appreciated in the art. Examples of other substances that may be preferred for use in certain embodiments of barrier layer 34 include tantalum nitride, nichrome, chromium silicide, and other resistive compounds.

15

PCT/US02/28100

19

A second insulating layer 36, also commonly referred to as a passivation layer is then applied to the top electrode layer 24. Such passivation layer 36 protects the underlying capacitor layers and helps provide electrical stability of the component. Exemplary suitable materials for passivation layer 36 may be selected from thin films of inorganic materials such as silicon nitride ( $Si_0N_4$ ), silicon dioxide ( $SiO_2$ ), silicon oxynitride ( $SiO_3$ ), and various nonstoichiometric combinations designated as  $Si_vH_vC_vO_vN_z$ . Alternatively, passivation layer 36 may be made from various films of organic polymers including polymides, epoxies, or benzocyclobutene (BCB), as well as combinations of layers of inorganic and organic materials.

Top electrode layer 24 has an array of circular openings 26 to provide non-contact holes for connection paths to the bottom electrode 20. A similar array of holes is provided in resistive barrier layer 34. By making the holes 26 in conductive layer 24 larger than the respective holes in resistive barrier layer 34 (as in Figure 1B), additional portions of resistive barrier layer 34 are exposed. More exposure of resistive barrier layer 34 increases the ESR of the device, exemplifying the tunable resistance of selected cascade capacitor configurations. Conductive vias 28 and 29 are inserted into capacitor component 10 with adjacent contacts alternating between top electrode 24 and bottom electrode 20. Solder balls 30 may then be attached to the respective ends of conductive vias 28 and 29 to provide termination features. Once all layers are deposited on the substrate 16, a thin film BGA component 10 is effected.

A first embodiment 14 of the present subject matter comprises a thin film BGA component 10 and a multilayer

25

PCT/US02/28100

20

IDC component 12. By combining the ultra-low ESL, high frequency performance characteristics of BGA component 10 with the greater capacitance of IDC component 12, the frequency range of useful decoupling functionality is expanded. Thin film BGA techniques may be utilized with components other than multilayer IDCs to form additional cascaded structures.

A typical IDC may correspond to a multilayer arrangement of electrode layers and dielectric layers. A partially exploded view of such a multilayer arrangement is shown in Figure 2A. Electrode layers are preferably arranged in parallel with tabs  $48\ \mathrm{and}\ 50\ \mathrm{extending}\ \mathrm{from}$ the layers such that electrode tabs extending from alternating electrode layers are aligned in respective columns. Such an arrangement of interdigitated terminals provides an electrode configuration with generally low ESL. Current preferably travels along the shorter distance of a chip component, thus lowering the self inductance of the device. The electrode arrangement of an IDC is such that current flowing out of a first set of positive plates returns in the opposite direction along a negative set of adjacent plates. Such provision of current flows in opposing directions considerably reduces inductance created by adjacent current flow in the same direction.

Figure 3A displays cascade capacitor embodiment 14 with features for connecting BGA component 10 with IDC component 12. Lands 52 may be provided along selected sides of the components to connect the terminations created by tabs 32 as well as IDC tabs 48 and 50. Alternatively, two sets of lands 52 may be provided, one set for BGA component 10 and one set for IDC component 12. These two sets of lands may then be mated to form a unified set of side terminations, such as displayed in

PCT/US02/28100

2

Figure 3C. The process of applying outside lands is effected through relatively simple techniques known to those of ordinary skill in the art of capacitor technology. Other termination features include solder balls 30 or other solder elements that may be applied to conductive vias 28 and 29. Examples of materials for forming solder balls 30 might include tin lead alloys, tin copper silver alloys, tin copper alloys, tin silver alloys, tin bismuth alloys, tin silver bismuth alloys, tin silver bismuth copper alloys, tin antimony alloys, tin silver copper antimony alloys, and other suitable substances. It is often preferred to add an optional under bump metallurgy beneath solder balls 30 to help control the flow of the solder material 30. Figure 2B displays the relative position of such ball limiting metallurgy (BLM) 38 to an exemplary embodiment of the present technology. Exemplary substances for use as BLM 38 may correspond to copper, nickel, gold, silver, tin lead, alloys formed from combinations of selected of the aforementioned metallic elements, and other combinations of conducting metals with a solderable surface. Exemplary particular BLM materials that may be preferable for certain applications include nickel-gold layers or copper-nickel-gold layers. Solder elements 30 can then be more conveniently applied to embodiments of the disclosed technology and subsequently utilized for connecting cascade capacitor embodiments to a PWB.

Figures 2A, 2B and 3B relate to a second exemplary embodiment of the present subject matter that offers similar electrical properties to the first exemplary embodiment as discussed with reference to Figures 1A and 1B. This second embodiment 40 builds a thick film version of a BGA component into the top layer of an IDC style capacitor such as 12. A first set of electrode

PCT/US02/28100

22

layers and corresponding tabs 48 form a set of terminals characterized by a given polarity and a second set of electrode layers and corresponding tabs 50 form a set of terminals with opposite polarity than the polarity of electrodes 48. Dielectric layers 44 are provided between adjacent electrode layers to form exemplary cascade capacitor 40. The top electrode layer 42 has an array of holes 26 enabling non-contact paths to the second electrode 46 which is counter to first electrode 42. Conductive via attachments 28 and 29 are then employed for providing alternating connections to the top two  $% \left( 1\right) =\left( 1\right) \left( 1\right)$ electrode layers. In the detailed perspective of Figure 2B, via 28 connects to electrode layer 42 and via 29 connects to electrode layer 46. Electrode layers below the top two layers are preferably connected with typical side termination lands 52.

There are many different types of electrode termination that may be utilized in accordance with presently disclosed cascade capacitor embodiments. If lands 52 are provided that wrap around the top and bottom surfaces of a capacitor, such as depicted in Figure 3C, then the selected sides can be coated with glass or organic solder-stop. A modified application of BLM is thus effected, and solder elements 30 can be reflowed to provide a columnar structure of solder that serves to mount the embodiment and provide a stress absorbing standoff, while keeping the sides of the capacitor free from termination structures. Alternatively, internal vias could connect the tabs 48 and 50 thus precluding the need for external lands. Thus, the option of utilizing internal or external via interconnection facilitates a variety of exemplary cascade capacitor configurations.

Referring again to Figures 2A and 2B, an insulating layer may then preferably be deposited onto top electrode

### PCT/US02/28100

23

layer 42. Further addition of solder balls 30 and BLM 38 to columnar vias 28 and 29 effects a cascade capacitor configuration 40 such as that displayed in Figure 2B.

configuration 40 such as that displayed in Figure 2B. The termination scheme utilized in exemplary embodiment 40 (Figures 2A, 2B and 3B) and exemplary embodiment 14 (Figure 3A) provide many advantages. The disclosed embodiments do not require the holes 26 and vias 28 and 29 to cut through all the electrode layers of the capacitor. It is known that capacitance of a component is directly proportional to the area of its capacitor plates. Holes throughout the capacitor body would thus decrease the effective capacitance and reduce the reliability of the device. Selected termination schemes of the present embodiments are more cost efficient than other termination schemes and preferably will not decrease the overall capacitance value of a cascade capacitor design. It is recognized that internal connection with holes and vias to many electrode layers in an exemplary embodiment would create a complex termination arrangement, but one that is characterized by generally low inductance. On the other hand, it is also recognized that internal connection to only a small number of electrode plates, such as displayed in Figure 1B and Figure 2B, provides quite a reliable internal termination arrangement. However, it is characterized by lowered capacitance. Thus, there is an evident tradeoff among the complexity, capacitance, inductance, and reliability of the termination arrangement of the present subject matter. Selected of these characteristics may be more desirable for certain applications, and thus it should fall within the scope of the presently discloses technology that variations to the number of electrode layers that are internally connected are available.

PCT/US02/28100

24

Figures 3A through 3C display exemplary cascade capacitor embodiments such as those described in the foregoing specification. Figure 3A illustrates a view of all elements in combination to form first embodiment 14 of a thin film BGA/IDC cascade capacitor. Figure 3B illustrates second exemplary embodiment 40 of a thick film BGA/IDC cascade capacitor. It should be appreciated that various features discussed above in reference to one exemplary embodiment may still be applied to other embodiments of the present subject matter. More particularly, optional layers and features described with respect to embodiment 14 or other embodiments can be applied to embodiment 40 or other embodiments, and vice versa, while still remaining within the scope of the presently disclosed technology. Figure 3C displays an exemplary embodiment 54 that represents either embodiment 14 or 40. For the remainder of the specification, it will be understood that BGA/IDC component 54 could correspond to either the thin film cascade capacitor structure 14 or the thick film monolithic cascade capacitor embodiment 40.

Referring to Figures 4A and 4B, additional termination features for an exemplary cascade capacitor 54 are displayed. A unified positive termination bar 60 is provided that connects selected of the positive termination lands 56 together. A unified negative termination bar 62 is also provided to connect selected of the negative termination lands 58 together. Termination bars 60 and 62 facilitate the connection of additional components to exemplary cascade capacitor 54. Such termination elements 60 and 62 can be screen-printed or defined using direct write based techniques or other techniques known in the art.

PCT/US02/28100

29