OFFICE FÉDÉRAL DE LA PROPRIÉTÉ INTELLECTUELLE

Int. Cl.<sup>2</sup>:

H 01 L 27/02 H 03 K 17/14

G 04 C

## FASCICULE DE LA DEMANDE A3 (1)

614837G

Numéro de la demande: (21)

8454/77

Additionnel à:

Demande scindée de:

Date de dépôt:

08.07.1977

Priorité:

(71)

Demande publiée le:

28. 12. 1979

Fascicule de la demande publié le:

Requérant:

Ebauches S.A., Neuchâtel

Mandataire:

Blasco Dousse, Carouge

Inventeur:

Andreas Rusznyak, Chêne-Bougeries, et Jakob Luscher, Venthône

- Rapport de recherche au verso

- (54) Dispositif pour régler, à une valeur déterminée, la tension de seuil de transistors IGFET d'un circuit intégré par polarisation du substrat d'intégration

- 57 Le dispositif comporte un transistor IGFET de réglage (R), réalisé par intégration dans le substrat même du circuit intégré (CI) et de même type de conduction que les transistors de ce circuit dont la tension de seuil doit être réglée. Un multiplicateur de tension (MT) fournit une tension qui peut atteindre plusieurs fois la valeur de celle de la pile (P). Un générateur (G) délivre un courant de référence à la source (M) du transistor de réglage (R), de manière que cette source se polarise par rapport au substrat à la valeur permettant le passage du courant du générateur au travers du transistor de réglage (R). Ainsi, le dispositif règle la tension de seuil à une valeur déterminée.

Ce dispositif ne consomme que très peu d'énergie. Il est destiné principalement à un circuit intégré pour montre-bracelet électronique.

Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.:

CH 8454/77

HO 12 740

|                        | Documents considérés comme pertinents<br>Einschlägige Dokumente                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A                      | FR - A - 2 152 031 (ITT INDUSTRIES INC)                                                                                                                                   | •                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | * page 1, ligne 1 à page 2, ligne 15 *                                                                                                                                    | I                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                      | ente entre date date                                                                                                                                                      |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A                      | <u>US - A - 3 657 575</u> (K.TANIGUCHI et al.)                                                                                                                            |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | * colonne 1, lignes 5 à 49 *                                                                                                                                              | I                                                          | Domaines techniques recherches<br>Recherchierte Sachgebiete<br>(INT. CL. <sup>2</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        |                                                                                                                                                                           |                                                            | H 03 K 17/14<br>G 05 F 3/14<br>H 01 L 27/02<br>G 04 C 3/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        |                                                                                                                                                                           |                                                            | Catégorie des documents cités Kategorie der genannten Dokumente: X: particulièrement pertinent von besonderer Bedeutung A: arrière-plan technologique technologischer Hintergrund O: divulgation non-ècrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze E: demande faisant interférence kollidierende Anmeldung L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; ubereinstimmendes Dokument |

| Etendue de la recherche | 'Umfang der | Recherche |

|-------------------------|-------------|-----------|

|-------------------------|-------------|-----------|

Revendications ayant fait l'objet de recherches Recherchierte Patentansprüche:

ensemble

Revendications n'ayant pas fait l'objet de recherches Nicht recherchierte Patentansprüche: Raison: Grund:

Date d'achèvement de la recherche/Abschlussdatum der Recherche

Examinateur I.I.B./I.I.B Prüfer

16 février 1978

## REVENDICATIONS

- 1. Dispositif pour régler, à une valeur déterminée, la tension de seuil de transistors IGFET d'un circuit intégré, par polarisation du substrat d'intégration, ce circuit présentant une ligne de référence constituant son point commun (masse), caractérisé par le fait qu'il comprend au moins

- un transistor IGFET de réglage, intégré dans ledit substrat et de même type de conduction que celui des transistors dont la tension de seuil doit être réglée, l'une des électrodes secondaires du transistor de réglage, source ou drain étant rattachée à une borne de polarisation destinée à être reliée au moins indirectement à ladite ligne de référence et son électrode de commande étant reliée à sa source.

- dudit transistor de réglage,

- un générateur délivrant une tension continue relié, d'une part, au drain de ce transistor et, d'autre part, audit substrat,

- le tout de manière que la source du transistor de réglage se polarise par rapport au substrat à la valeur permettant le passage du courant du générateur au travers du transistor de réglage.

- 2. Dispositif selon la revendication 1, caractérisé par le fait que ledit générateur de courant de référence comprend un circuit électronique englobant, intégrés dans ledit substrat, une ligne de référence de ce circuit, au moins une première ligne de commande 25 destinée à recevoir un signal périodique, une borne de sortie par laquelle est délivré ledit courant de référence, un condensateur et deux transistors IGFET de même type de conduction que celui dudit transistor de réglage, dans lequel ce condensateur est rattaché, par une électrode, à ladite première ligne de commande et est branché en série, par son autre électrode, avec l'électrode de commande et le drain du premier des deux transistors, la source de ce premier transistor étant reliée, au moins indirectement, à la ligne de référence du circuit générateur du courant de référence, et dans lequel le second desdits deux transistors est branché par ses électrodes secondaires, d'une part, à l'électrode de commande du premier transistor et, d'autre part, à ladite borne de sortie, l'électrode de commande de ce second transistor étant rattachée, au moins indirectement, à la ligne de référence du circuit générateur de courant.

- 3. Dispositif selon la revendication 2, caractérisé par le fait que ledit générateur de courant de référence comprend une seconde ligne de commande destinée à recevoir un signal périodique.en opposition de phase par rapport au signal devant être reçu par la première ligne de commande, par le fait que le drain dudit premier transistor et l'électrode de commande dudit second transistor sont rattachés à la ligne de référence du circuit du générateur de courant au travers d'un circuit intermédiaire de charge de ce drain et de cette électrode de commande, et par le fait que ce circuit intermédiaire de charge comprend un deuxième et un troisième condensateur ainsi qu'un troisième, un quatrième et un cinquième transistor IGFET de même type de conduction que celui du transistor de réglage, le deuxième condensateur étant rattaché, par une électrode, à la seconde ligne de commande et, par l'autre électrode, à l'électrode de commande et au drain du troisième transistor ainsi qu'à l'électrode de commande dudit second transistor, la source du troisième transistor étant reliée à la ligne de référence du circuit générateur de courant, le quatrième transistor étant rattaché, par ses électrodes secondaires, respectivement au drain dudit troisième transistor et à la source du premier transistor et, par sa propre électrode de commande, à ladite ligne de référence du circuit générateur de courant, le troisième condensateur étant branché en parallèle avec les électrodes secondaires du cinquième transistor et étant disposé entre la source du premier transistor et cette ligne de référence, l'électrode de commande de ce cinquième transistor étant rattaché à cette même ligne, l'ensemble de ces composants étant intégré dans ledit substrat.

- 4. Dispositif selon la revendication 1, dans lequel ledit générateur délivrant un courant de référence est constitué par un circuit électronique englobant une ligne de référence, caractérisé par le fait que ledit transistor de réglage est rattaché à ladite borne de 5 polarisation par sa source et par le fait que ladite ligne de référence du circuit électronique du générateur de courant de référence est rattachée au substrat d'intégration.

- 5. Dispositif selon la revendication 4, caractérisé par le fait qu'il comprend, de plus, une source de tension d'appoint reliée, 10 d'une part, à ladite borne de polarisation et, d'autre part, à ladite ligne de référence du circuit intégré.

- 6. Dispositif selon la revendication 1, dans lequel ledit générateur délivrant un courant de référence est constitué par un circuit électronique englobant une ligne de référence, caractérisé par le - un générateur délivrant un courant de référence à la source 15 fait que ledit transistor de réglage est rattaché à ladite borne de polarisation par sa source, par le fait que ledit générateur de tension est constitué par une disposition en série de deux sources de tension distinctes et par le fait que le point de liaison de ces deux sources de tension est rattaché à ladite ligne de référence du circuit électronique dudit générateur.

- 7. Dispositif selon la revendication 6, caractérisé par le fait qu'il comprend, de plus, une source de tension d'appoint reliée, d'une part, à ladite borne de polarisation et, d'autre part, à ladite ligne de référence du circuit intégré.

- 8. Dispositif selon la revendication 1, dans lequel ledit générateur délivrant un courant de référence est constitué par un circuit électronique englobant une ligne de référence, caractérisé par le fait que ledit générateur de tension est constitué par deux sources de tension distinctes reliées en série au travers des électrodes 30 secondaires d'un transistor IGFET supplémentaire de même type de conduction que celui du transistor de réglage et intégré dans ledit substrat, l'électrode de commande de ce transistor supplémentaire étant reliée à la source du transistor de réglage, et par le fait qu'il comprend une troisième source de tension branchée 35 entre le point de liaison dudit transistor supplémentaire et celle desdites deux sources de tension distinctes qui est rattachée au drain dudit transistor de réglage et ladite ligne de référence du circuit électronique dudit générateur.

- 9. Dispositif selon la revendication 8, caractérisé par le fait 40 que ledit transistor de réglage est rattaché à ladite borne de polarisation par sa source.

- 10. Dispositif selon la revendication 8, caractérisé par le fait que ledit transistor de réglage est rattaché à ladite borne de polarisation par son drain.

L'un des paramètres importants ayant une influence sur les 50 performances d'un circuit intégré MOS, comportant donc des transistors à effet de champ, à électrode de commande isolée (IGFET), est la valeur de la tension de seuil de ces transistors. Les performances en question peuvent être par exemple leur limite de fonctionnement en fonction de leur tension d'alimentation ou de 55 la température.

Dans la fabrication de circuits de ce type, il est relativement facile d'obtenir que la dispersion des valeurs de la tension de seuil des transistors se trouvant sur la même plaquette, dispersion due essentiellement à la tension flat-band, soit très faible. Il n'en est 60 toutefois pas de même en ce qui concerne la dispersion de ces valeurs entre transistors se trouvant sur des plaquettes différentes, notamment si, quoique obtenues par une même opération de fabrication, ces plaquettes font partie de charges différentes. C'est pourquoi on a cherché à concevoir des systèmes réglant, par des 65 moyens électroniques, la tension de seuil de transistors d'un circuit intégré à une valeur bien déterminée.

On connaît déjà des circuits intégrés MOS englobant des dispositifs réglant à une valeur déterminée la tension de seuil des transistors, cela par l'intermédiaire d'une polarisation de leur substrat. On signalera à titre d'exemple les publications ci-après: «Self-biasing Technique for MOS-Substrate Voltage», brevet des Etats-Unis d'Amérique N° 3806741 et, par Eugène M. Blaser, William M. Chu et George Sonoda, «Substrate Load Gate Voltage Compensation» (Digest of Technical Papers 1976 IEEE International Solid-State Circuits Conference, pp. 56-57).

Dans ces systèmes, le réglage est réalisé de manière qu'une tension de référence, dérivée de la tension d'alimentation, soit comparée avec la tension de seuil d'un transistor; la différence de ces tensions, constituant un signal d'erreur, contrôle un inverseur qui l'amplifie. Ce signal amplifié module un générateur d'impulsions dont la tension de sortie qui est redressée constitue la tension de polarisation du substrat, laquelle s'ajuste de manière que le signal d'erreur soit proche de zéro.

Si l'on désirait faire usage d'un tel système pour procéder au réglage de la tension de seuil des transistors d'un circuit intégré MOS d'une montre-bracelet à quartz par exemple, on aurait alors à faire face à des problèmes de consommation d'énergie. On sait en effet que dans un dispositif portatif, et notamment dans une montre-bracelet, le volume disponible pour les éléments constituants est très limité. De ce fait, la capacité énergétique de la source d'énergie qu'il englobe, en l'occurrence une pile de petites dimensions, est elle aussi très limitée. Pour assurer une autonomie de longue durée, par exemple de plusieurs années, il est donc indispensable que la consommation du système électronique complet du dispositif soit très faible.

On a déjà proposé des circuits électroniques de consommation faible et autorisant une fabrication rationnelle, réalisés sous forme de circuits intégrés MOS ne contenant que des transistors d'un seul type de conduction et des condensateurs. De tels circuits sont par exemple décrits dans les brevets des Etats-Unis d'Amérique N°s 3956714, 3932773 et 3983411. Ils sont avantageusement réalisés par intégration dans des substrats de dotation relativement faible. On réduit ainsi, d'une part, l'effet de la variation de tension de seuil de leurs transistors en fonction du potentiel de la source de ces derniers (body-effect) et, d'autre part, la capacité parasitaire des différentes zones diffusées par rapport au substrat.

Etant donné que la tension de seuil des transistors MOS ne varie qu'avec la racine carrée de la tension de polarisation appliquée entre leur source et le substrat, il est nécessaire, pour permettre de régler leur tension de seuil par l'intermédiaire d'une telle polarisation dans un domaine relativement large, par exemple plusieurs dixièmes de volt, que la tension de polarisation d'un tel substrat, faiblement doté, puisse atteindre des valeurs qui soient un multiple de la tension de pile (1,3 à 1,5 V) usuelle dans les montres-bracelets électroniques.

A cet effet, la présente invention propose un dispositif pour régler, à une valeur déterminée, la tension de seuil de transistors IGFET d'un circuit intégré, par polarisation du substrat d'intégration, lequel permet de consommer très peu d'énergie, par exemple quelques dixièmes de microampère seulement, et qui ne comporte également que des transistors d'un seul type de conduction et des condensateurs.

Ce circuit, qui présente une ligne de référence constituant son point commun (masse), est caractérisé par le fait qu'il comprend au moins:

- un transistor IGFET de réglage, intégré dans ledit substrat et de même type de conduction que celui des transistors dont la tension de seuil doit être réglée, l'une des électrodes secondaires du transistor de réglage, source ou drain, étant rattachée à une borne de polarisation destinée à être reliée au moins indirectement à ladite ligne de référence, et son électrode de commande étant reliée à sa source,

- un générateur délivrant un courant de référence à la source  $^{65}$  dudit transistor de réglage,

- un générateur délivrant une tension continue relié, d'une part, au drain de ce transistor et, d'autre part, audit substrat,

— le tout de manière que la source du transistor de réglage se polarise par rapport au substrat à la valeur permettant le passage du courant du générateur au travers du transistor de réglage.

Les dessins annexés représentent, à titre d'exemple et très schématiquement, trois formes d'exécution de la présente invention:

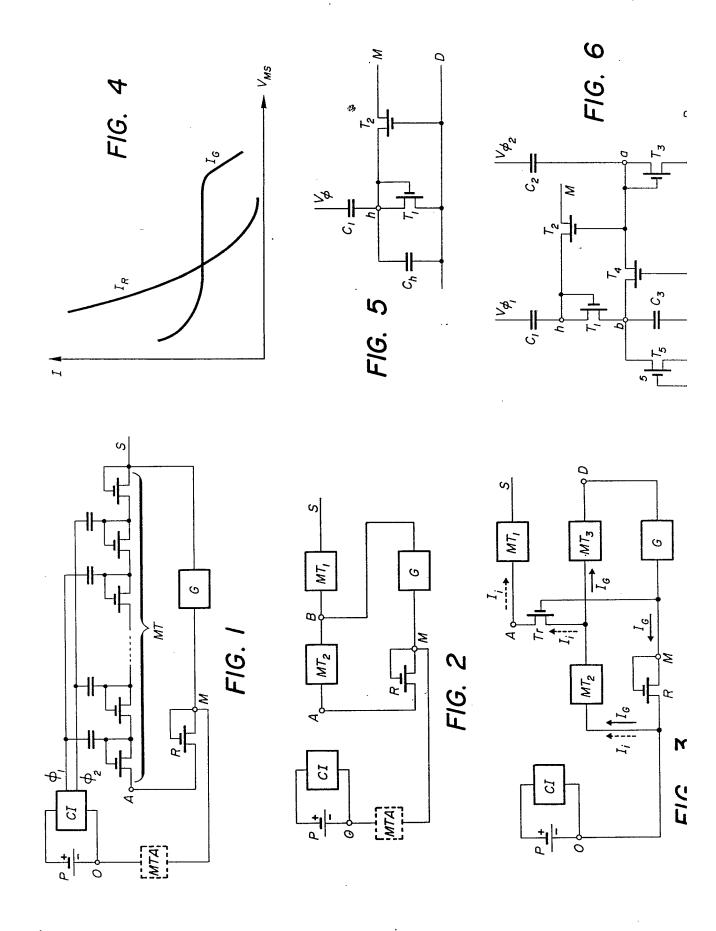

la fig. 1 montre le schéma de la première de ces formes d'exécution.

La fig. 2 est le schéma de la seconde forme d'exécution. La fig. 3 représente le schéma de la troisième forme d'exécution.

La fig. 4 est un diagramme explicatif.

'Les fig. 5 et 6 montrent des schémas d'un détail des formes d'exécution apparaissant sur les fig. 1 à 3.

Avant d'entreprendre la description des caractéristiques essentielles des formes d'exécution du dispositif selon l'invention, rappelons tout d'abord quelques caractéristiques fondamentales bien connues des transistors MOS à effet de champ, à électrode de commande isolée (IGFET).

Comme on le sait, le rapport entre le courant de saturation I<sub>s</sub> et la tension de commande V<sub>G</sub> d'un transistor MOS peut être caractérisé, dans un large domaine, par l'expression bien connue

$$I_s = K(V_G - V_T)^2 \tag{1}$$

où K est la pente du transistor en  $A/V^2$ . Cette pente est proportionnelle à W/L, où W est la largeur et L la longueur du canal. Il est usuel de définir la valeur de la tension de seuil  $V_T$  comme étant la valeur s'obtenant à l'intersection de la partie droite du diagramme

$\sqrt{I_s}$  = f (V<sub>G</sub>) avec l'axe de la tension; V<sub>T</sub> est donc une valeur extrapolée.

Pour des tensions  $V_G - V_T$  proches de 0, cette équation (1) n'est plus valable. Le courant de saturation  $I_s$  au travers du transistor pour  $V_G = V_T$  peut être calculé cependant par l'expression

$$I_s = K \cdot V_{GO}^2 \tag{2}$$

où  $V_{GO}$  dépend de la dotation du substrat et de l'épaisseur de la couche d'oxyde.

Pour des tensions  $V_G - V_T < 0$  (régime à faible inversion), le rapport entre le courant de saturation  $I_s$  et la tension de commande  $V_G$  est exponentiel dans un large domaine du courant  $I_s$  (plusieurs décades). En supposant que ce rapport exponentiel caractérise le transistor aussi pour des tensions jusqu'à  $V_T - V_G = 0$ , supposition qui peut se justifier lorsqu'on considère le dispositif de réglage en question, la fonction  $I_s = f(V_G)$  peut s'écrire, dans ce régime, par l'expression

$$I_s = KV_{GO}^2 \cdot \exp\left[\beta(V_G - V_T)\right]$$

(3)

où β dépend essentiellement de l'épaisseur de la couche d'oxyde et de <sup>50</sup> la dotation du substrat.

Lorsqu'il est question de tension de seuil d'un transistor, on fait usuellement référence à celle qu'on observe sans polarisation du substrat d'intégration par rapport à la source du transistor en question. Dans le brevet des Etats-Unis d'Amérique N° 3845331, il a déjà été montré quel était l'effet qui pouvait être obtenu par polarisation du substrat d'un tel transistor, effet qui, si on considère la caractéristique donnant la variation de la racine carrée du courant de saturation I<sub>s</sub> du transistor par rapport à la tension de commande V<sub>G</sub>, se traduit par un déplacement de la courbe de cette caractéristique le long de l'axe V<sub>G</sub>. L'importance de ce déplacement peut être calculée par la relation ci-après:

$$V_{T} = V_{FB} + 2\psi_{B} - \sqrt{\frac{2\varepsilon_{o}\varepsilon_{si}qN_{B}}{C_{ox}}} \sqrt{V_{s} + 2\psi_{B}}$$

(4)

où

V<sub>FB</sub> =tension flat-band,

$\psi_{\rm B}$  = potentiel Fermi du semi-conducteur,

ε<sub>si</sub> = constante diélectrique du silicium,

q =charge d'électron,

N<sub>B</sub> = dotation du silicium,

C<sub>ox</sub> = capacité par unité de surface de l'oxyde, sous l'électrode de commande.

V<sub>s</sub> = tension de polarisation de la source du transistor, par rapport au substrat.

La tension de seuil varie donc linéairement en fonction de

$\sqrt{V_s+2\psi_B}$  avec une pente qui dépend de la dotation du substrat et de la capacité de l'oxyde sous l'électrode de commande.

Dans la description qui va suivre et dans les dessins auxquels elle se réfère, il ne sera question que de circuits englobant des transistors de type n<sup>+</sup> intégrés dans un substrat de type p; il est évident que ces mêmes circuits pourront fort bien être réalisés par 15 intégration de zones p<sup>+</sup> dans un substrat de type n.

Le dispositif de réglage selon l'invention, dont la première forme d'exécution est visible sur la fig. 1, est destiné à assurer le réglage de la tension de seuil des transistors qu'englobe un circuit intégré CI, circuit qui est plus particulièrement destiné à une montre-bracelet électronique et contenant par exemple un oscillateur symétrique du genre décrit dans le brevet des Etats-Unis d'Amérique N° 3983714 déjà cité, ainsi qu'un diviseur de fréquence tel que défini par le brevet des Etats-Unis d'Amérique N° 3983411 également cité ci-dessus. Ce circuit CI est alimenté par une pile P, ayant une tension de 1,5 V par exemple, et délivre sur ses deux sorties  $\emptyset_1$  et  $\emptyset_2$  des signaux périodiques,  $V_{\emptyset 1}$  et  $V_{\emptyset 2}$  respectivement, en opposition de phase.

Comme on le voit au dessin (fig. 1), le circuit de réglage comprend un transistor IGFET, R, réalisé par intégration dans le substrat même du circuit CI et de même type de conduction que les transistors de ce circuit dont la tension de seuil doit être réglée. Ce circuit de réglage comporte de plus un générateur de courant de référence, G, dont les caractéristiques constructives seront décrites par la suite, et un multiplicateur de tension, MT, d'un type bien connu, notamment du brevet des Etats-Unis d'Amérique N° 3845331, qui est commandé par les signaux délivrés par le circuit intégré CI sur ses sorties  $\emptyset_1$  et  $\emptyset_2$ .

Le multiplicateur MT produit une tension entre le point A et le point S, relié au substrat, tension dont la valeur dépend évidem- 40 ment du nombre de chaînons que présente le multiplicateur et qui est relativement élevée. Celui-ci alimente donc le transistor R, dont l'électrode de commande est reliée à sa source, ainsi que le générateur de courant de référence G, ces deux éléments étant connectés en série entre les points A et S précédemment cités. Le générateur G est agencé de manière que le courant qu'il produit soit, dans une large mesure, indépendant de la tension existant entre le point M, de liaison du générateur et du transistor R, et le substrat. Vu que ce générateur est connecté en série avec le transistor R, le courant qu'il délivre est imposé à ce dernier, de sorte que la tension entre le point M et le substrat s'ajuste à la valeur qui permet le passage de ce courant.

Lorsque le dispositif est enclenché, le courant du transistor R est d'abord plus grand que celui débité par le générateur G et la différence de ces deux courants charge la capacité existant entre le point M et le substrat S. Ainsi, le potentiel du substrat S devient négatif par rapport au point M et cette tension, qui est celle de polarisation du transistor de réglage R, influe sur sa tension de seuil V<sub>T</sub> de sorte que la valeur de celle-ci croît (voir relation 4) et que, par conséquent, son courant de saturation décroît. L'équilibre s'établit de façon que le courant au travers du transistor de réglage soit égal à celui débité par le générateur de courant G. Les relations fondamentales des transistors MOS permettent de calculer la tension de seuil V<sub>T</sub> du transistor de réglage R qui sera obtenue lorsque l'état d'équilibre aura été atteint.

Comme l'électrode de commande du transistor de réglage R est reliée à sa source  $(V_G=0)$  et en supposant que la pente de ce tran-

sistor soit  $K_R$ , la tension de seuil  $V_T$  de ce transistor se calcule, d'après l'équation (3), selon

$$V_{\rm T} = \frac{1}{\beta} \ln \frac{K_{\rm R} V_{\rm GO}^2}{I_{\rm G}} \,. \tag{5}$$

Cette tension  $V_T$  peut être exprimée également en fonction de la tension  $\Delta V_G$ , qui est nécessaire pour changer d'un facteur 10 la valeur du courant de saturation d'un transistor en régime de faible inversion, par

$$V_{T} = \Delta V_{G} \cdot \log_{10} \frac{K_{R} V_{GO}^{2}}{I_{G}}$$

(6)

Si on rapproche les relations (5) et (6), on voit que le rapport entre  $\Delta V_{G}$  et  $\beta$  est égal à

$$\Delta V_{G} = \frac{1}{\beta \cdot \log_{10} e} \tag{7}$$

(e: 2,71..., base du logarithme naturel)

Avec des valeurs typiques pour un tel circuit intégré de  $V_{GO} = 0.0$  V et  $\Delta V_G = 0.08$  V, on obtient par exemple, avec  $K_R = 4 \cdot 10^{-4} \text{ A/V}^2$ ,  $I_G = 4 \cdot 10^{-8} \text{A}$ , une tension de seuil extrapolée de V<sub>T</sub>=0,1 V. Cette tension de seuil, qui est donc celle du transistor de réglage R, serait aussi caractéristique pour des transistors du circuit CI, dont les sources sont reliées au point commun de ce circuit, point qui est relié à la source de ce transistor de réglage. On voit ainsi que, par l'intermédiaire du dispositif de réglage décrit, la tension de seuil des transistors du circuit intégré CI a pu être réglée essentiellement par un choix adéquat des paramètres KR et IG à une valeur déterminée. A titre d'information, on indiquera ci-après la tension de polarisation qui serait nécessaire pour obtenir une tension de seuil  $V_T = 0,1$  V en partant d'une tension de seuil extrapolée V<sub>TO</sub> en état non polarisé du substrat. Pour des cas typiques elle est, pour l'exemple déjà cité, de -0.7 V <sup>35</sup> pour  $V_{TO} = 0$  V, et de -6 V pour  $V_{TO} = -0.4$  V.

Pour le cas où on désirerait avoir une tension de seuil V<sub>T</sub> de valeur plus élevée, on pourrait aussi introduire un multiplicateur de tension additionnel MTA entre les points M et O du dessin (représenté en traitillé sur la fig. 1), cela avec une diminution insignifiante de l'efficacité du réglage.

Ainsi, avec une tension additionnelle de 1 V, qui peut être produite avec un multiplicateur de tension ne présentant qu'un seul chaînon, la tension de seuil  $V_T$  serait 0,2 V ou 0,18 V pour  $V_{TO}$  ayant une valeur égale à 0 V et à -0.4 V respectivement.

La deuxième forme d'exécution du dispositif selon l'invention (fig. 2) se distingue de la forme d'exécution précédente, d'une part, par le fait que le multiplicateur de tension alimentant le drain du transistor de réglage R est remplacé par une disposition en série de deux multiplicateurs distincts MT<sub>1</sub> et MT<sub>2</sub>, et, d'autre part, par le fait que le générateur de courant G est connecté au point de liaison B de ces deux multiplicateurs. Cette disposition rend possible l'obtention d'une polarisation des éléments du générateur de courant de référence G, polarisation qui est très favorable du point de vue de la construction de ce générateur.

Dans ce cas également, il est possible de relier la ligne de référence du circuit intégré CI au point M du dispositif de réglage au travers d'un multiplicateur de tension additionnel MTA de manière à accroître la valeur de la tension de polarisation disponible.

La troisième forme d'exécution du dispositif de réglage selon l'invention (fig. 3) comprend trois multiplicateurs de tension, MT<sub>1</sub>, MT<sub>2</sub> et MT<sub>3</sub>, qui peuvent être du type décrit dans le brevet des Etats-Unis d'Amérique N° 3845331 et qui sont toutefois différents par le nombre de chaînons qu'ils englobent. Cette troisième forme d'exécution englobe de plus un transistor à effet de champ, à électrode de commande isolée, Tr, qui est branché en série entre les multiplicateurs MT<sub>1</sub> et MT<sub>2</sub>. L'électrode de com-

mande de ce transistor est reliée directement à la source du transistor de réglage R, de sorte que le potentiel de la source du transistor Tr est ainsi très proche de celui du point M. La tension obtenue grâce au multiplicateur de tension MT<sub>2</sub> peut être faible, par exemple de l'ordre de 1 V dans le cas de l'exemple d'exécution 5 déjà cité. Celle susceptible d'être obtenue grâce au multiplicateur MT<sub>3</sub> peut être encore plus faible, de l'ordre de 0,5 V; elle doit être telle que la tension du générateur G soit suffisante pour qu'il fonctionne correctement.

Le fait que, dans cette forme d'exécution, on dispose, entre les points M et D, d'une tension de valeur réduite signifie que les éléments du générateur de courant G peuvent bénéficier d'une polarisation par rapport au substrat S, polarisation qui est très favorable du point de vue de la construction de ce générateur.

On remarquera en outre que, dans cette forme d'exécution le point commun, O, du circuit intégré CI est relié au drain du transistor de réglage R alors que, dans les deux autres formes d'exécution décrites, ce point commun était relié à la source du transistor homologue. Par cet arrangement des composants, il est possible de faire jouer au multiplicateur de tension MT<sub>2</sub> également le rôle du multiplicateur additionnel MTA mentionné en se référant aux fig. 1 et 2. On se souviendra que ce multiplicateur additionnel permettait de créer une tension de seuil V<sub>T</sub> des transistors du circuit intégré CI de valeur plus élevée en utilisant des composants électroniques additionnels.

Il convient à ce point de remarquer que, dans cette troisième forme d'exécution, le courant  $I_G$  qui est un courant d'électrons, représenté par des flèches dans la fig. 3, passe par le transistor R et par les multiplicateurs de tension  $MT_2$  et  $MT_3$ . Toutefois, puisque les tensions produites par ces multiplicateurs sont réduites et que le courant  $I_G$  est faible, la consommation due à cette circulation de courant est extrêmement réduite. Le courant inverse,  $I_i$ , de toutes les jonctions du circuit intégré CI (courant d'électrons dont la circulation est rendue visible au dessin par des flèches pointillées) est ramené au substrat du circuit, S, au travers du multiplicateur de tension  $MT_2$ , du transistor Tr et du multiplicateur  $MT_1$ . Puisque le multiplicateur  $MT_2$  est déjà chargé par le courant  $I_G$ , l'influence du courant  $I_i$  sur sa tension est insignifiante.

Le fonctionnement du dispositif de réglage qui vient d'être décrit sera maintenant expliqué en se référant au diagramme représenté par la fig. 4, lequel montre, d'une part, la variation du courant de saturation  $I_R$  du transistor de réglage R en fonction de sa tension de polarisation  $V_{\rm MS}$ , appliquée entre sa source et le substrat, et, d'autre part, la variation du courant supposé  $I_G$  du générateur de courant de référence G, en fonction de cette même tension.

Comme décrit, les particularités constructives de générateurs de courant qui débitent un courant dont la valeur est, dans une large mesure, indépendante de leur tension d'alimentation et d'une éventuelle tension de polarisation  $C_{DS}$  appliquée entre le point commun d'un tel générateur et le substrat, seront indiquées plus loin. Etant donné que la tension  $V_{DM}$  appliquée entre les points D et M (fig. 3) se compose de la tension créée par le multiplicateur de tension  $MT_3$  et de la tension existant entre l'électrode de commande et la source du transistor  $T_r$ , toutes deux de valeur réduite, la valeur de  $V_{DM}$  est faible. Ainsi la dépendance de ce courant  $I_G$  de la tension  $V_{MS}$  et de  $V_{DS}$  est, dans un large domaine, la même. Il est donc possible de reporter sur un même diagramme, en l'occurrence précisément celui de la fig. 4, la variation du courant du transistor R et celui du générateur G en fonction de la tension de polarisation  $V_{MS}$  du transistor de réglage R.

Pour un circuit CI constituant un système complet englobant un oscillateur et un diviseur de fréquence, tel que mentionné précédemment, on choisit donc de préférence un substrat faiblement doté, de manière que, sans polarisation, les transistors aient une tension de seuil de valeur négative, pour le cas de transistors de type de conduction n; grâce à la polarisation cette valeur va donc devenir positive. C'est lorsque la valeur de la tension  $V_{DS}$  est encore faible que le courant  $I_G$  décroît en augmentant la valeur de la tension  $V_{DS}$  pour devenir, pour des tensions  $V_{DS}$  plus élevées, pratiquement indépendant de  $V_{DS}$  (et de  $V_{MS}$ ) et pour décroître à nouveau pour des valeurs très élevées.

Le principe de fonctionnement du dispositif décrit exige, en état d'équilibre, que le courant I<sub>R</sub> traversant le transistor de réglage R soit égal à celui, I<sub>G</sub>, débité par le générateur de courant G. La tension de polarisation pour laquelle cette exigence sera remplie correspondra ainsi à celle déterminée par l'intersection des deux courbes illustrées par le diagramme de la fig. 4.

On peut donc, avec des moyens très simples, compléter par exemple un système oscillateur-diviseur de fréquence polarisé, du type décrit dans le brevet des Etats-Unis d'Amérique N° 3848200, de telle sorte que la tension de seuil de ses transistors soit réglée avec précision à une valeur déterminée et cela pour un large domaine de la tension de seuil à l'état non polarisé. Mis à part le transistor de réglage R, ces moyens sont essentiellement constitués par de simples multiplicateurs de tension et par un générateur de courant. Ces composants sont alimentés par l'oscillateur et font donc partie du circuit résonnant. De ce fait, et vu que les courants continus en jeu sont de valeur extrêmement faible, la consommation causée par ce système de réglage est très réduite, de quelques dixièmes de microampère seulement.

Le dispositif de réglage de la tension de seuil des transistors MOS décrit fait appel à un générateur de courant de référence de valeur très faible.

La disponibilité d'une source de tension périodique d'amplitude et de fréquence stables, en l'occurrence un oscillateur, rend possible la réalisation de tels générateurs sous forme de circuits intégrés MOS structurellement simples, ne comportant que des transistors d'un seul type de conduction et des condensateurs.

Les fig. 5 et 6 du dessin annexé montrent deux exécutions de générateurs dans lesquels on charge, avec la périodicité de la tension de la source de tension périodique qui les alimente, un condensateur de faible capacité à la tension stable délivrée par cette source ou à une fraction de celle-ci, et on transfère ensuite, vers la sortie de chaque générateur considéré, avec la même périodicité et au travers d'un transistor, la charge de ce condensateur ou une partie de cette dernière. Ces générateurs débitent ainsi l'intégrale de ces charges transférées sous forme, en moyenne, d'un courant continu de valeur constante.

Dans l'exécution de la fig. 5, le générateur de courant comprend un condensateur C<sub>1</sub>, destiné à être relié à une source de

tension périodique, non représentée, délivrant une tension

d'amplitude V<sub>0</sub>, de préférence f, un premier transistor IGFET,

T<sub>1</sub>, branché en série entre ce condensateur et une ligne D constituant le point commun du générateur, l'électrode de commande

de ce transistor étant reliée à son drain, et un second transistor

IGFET, T<sub>2</sub>, branché, par ses électrodes secondaires, entre ce drain

et une sortie M du générateur et, par son électrode de commande,

au point commun. L'ensemble de ces composants est, bien

entendu, obtenu par intégration dans le substrat même du circuit CI déjà décrit. De plus, les transistors T<sub>1</sub> et T<sub>2</sub> sont de même

type de conduction que celui des transistors qu'englobe ce circuit,

ainsi que celui du transistor de réglage R déjà cité.

Le condensateur C<sub>h</sub> représente la capacité parasitaire des composants du circuit par rapport au substrat, qui sont reliés à ce point h, intermédiaire entre le premier transistor et le condensateur C<sub>1</sub>. Il faut noter que la capacité associée aux points D et M par rapport au substrat est très grande de sorte qu'il n'y a pratiquement aucune tension alternative sur ces points.

Le générateur décrit fonctionne comme suit: pendant chaque demi-période de la tension  $V_0$ , le condensateur  $C_1$  est chargé à travers le transistor  $T_1$ . Durant chaque demi-période suivante, cette charge est transférée par le transistor T, vers la sortie M. La valeur du courant qui résulte de ces paquets de charge périodiques

est pratiquement indépendante de la tension entre les points D et M, dès que cette dernière dépasse l'ordre du dixième de volt. Pour des tensions de seuil V<sub>T</sub> plus grandes que zéro, le courant I<sub>G</sub> de ce générateur se calcule, par la relation

$$I_{G} \approx 2 \cdot [C_{1} V_{0} - (C_{1} + C_{b}) V_{T}] \cdot f \tag{7}$$

La dépendance de ce courant I<sub>G</sub> d'une variation éventuelle de la tension de seuil V<sub>T</sub> est donnée par la relation

$$\frac{\mathrm{dI_G}}{\mathrm{dV_T}} \approx -2(C_1 + C_h)f \tag{8}$$

Dans un circuit intégré, les valeurs des capacités C<sub>1</sub> et C<sub>h</sub> peuvent être de l'ordre de 0,04 pF, pour la première capacité, et de 0,1 pF, pour la seconde. Pour des valeurs de  $V_0 = 1,4 \text{ V}$ ,  $V_T$ =0,2 V et f=780 kHz (oscillateur avec un quartz de coupe SL),

on obtiendra  $I_G = 4 \cdot 10^{-8}$  et  $\frac{dI_G}{dV_T} = 2 \cdot 10^{-7}$  A/V ou une dépendance

de courant  $I_G$  de la tension de seuil  $V_T$  de  $2 \cdot 10^8$  A par dixième de volt. En vue de l'utilisation du courant  $I_G$  comme courant imposé au transistor de référence R d'un dispositif de réglage de la tension de seuil de transistors, cette dépendance peut être considérée comme relativement faible puisqu'il faudrait que le courant I<sub>G</sub> change de plus d'un ordre de grandeur pour changer la tension de seuil réglée d'un dixième de volt.

La précision du réglage de la tension de seuil peut être améliorée en faisant usage du générateur dont le circuit est représenté

Ce générateur comprend trois condensateurs  $C_1$ ,  $C_2$  et  $C_3$ , et tors du circuit CI déjà cité en se référant aux fig. 1, 2 et 3, intégrés dans le substrat même de ce circuit.

Ces condensateurs C<sub>1</sub> et C<sub>2</sub> sont destinés à être reliés, par une armature, à des sources de tension périodique, non représentées, délivrant les signaux  $V_{01}$ , pour le condensateur  $C_1$ , et  $V_{02}$ , pour le condensateur C<sub>2</sub>, signaux en opposition de phase de source à source.

Le condensateur C<sub>1</sub> est branché en série avec les électrodes secondaires du transistor  $T_1$ , en liaison avec le drain de celui-ci, l'électrode de commande de ce transistor étant rattachée à ce drain. Quant au transistor T2, il est relié, par une électrode secondaire, au point H de liaison du transistor T<sub>1</sub> avec le condensateur C<sub>1</sub> et, par l'autre électrode secondaire, avec le point M du circuit

du dispositif de réglage auquel le générateur est destiné (fig. 1, 2

En ce qui concerne le condensateur C2, celui-ci est branché en série avec le transistor T3, en particulier avec le drain de ce trans-5 istor, drain auquel est également rattachée l'électrode de commande de ce transistor, la source de celui-ci étant reliée à la ligne D du circuit, elle-même rattachée soit au substrat du circuit intégré CI (fig. 2), soit au multiplicateur MT<sub>3</sub> (fig. 2 ou 3).

L'électrode de commande du transistor T<sub>2</sub> déjà cité est ratta-(8) 10 chée au point de liaison du condensateur C<sub>2</sub> et du transistor T<sub>3</sub>, comme c'est du reste également le cas pour l'une des électrodes secondaires du transistor T4 dont l'autre électrode secondaire est rattachée à la source du transistor T<sub>1</sub>. L'électrode de commande du transistor  $T_4$  est reliée à la ligne D.

En ce qui concerne enfin le condensateur  $C_3$  et le transistor  $T_5$ , ceux-ci sont branchés en parallèle entre cette même ligne D et la source du transistor T<sub>1</sub>, l'électrode de commande du transistor T<sub>5</sub> étant rattachée à la ligne D. On signalera à ce point que le condensateur C3 présente une valeur relativement élevée, de 20 l'ordre de 1 pF par exemple.

Etant donné que le transistor T<sub>3</sub> est connecté comme diode (électrode de commande reliée au drain), la tension sur le point a par rapport au point D ne dépasse guère, lors de la montée de la tension V<sub>02</sub>, la tension de seuil V<sub>T</sub>. Quand V<sub>02</sub> décroît, une 25 tension de signe opposé à celui de V<sub>T</sub> s'établit à ce point a de sorte que la valeur la plus négative de la tension  $V_a$  dépasse même  $-V_T$ . Dès que la tension  $V_a$  est plus négative que  $-V_T$ , le transistor T<sub>4</sub> conduit et le courant au travers de ce transistor charge le condensateur C<sub>3</sub> à une tension également négative par rapport au cinq transistors IGFET, T<sub>1</sub> à T<sub>5</sub>, de même polarité que les transis- 30 point D. Cette tension V<sub>b</sub> est limitée par le transistor T<sub>5</sub> à environ

> Lorsque le transistor T<sub>1</sub> conduit, l'effet de sa tension de seuil est compensé par la tension  $V_b = -V_T$  et ainsi le condensateur  $C_1$ se charge jusqu'à une valeur égale à 2 V<sub>01</sub>. Lorsque le transis-35 tor T<sub>2</sub> conduit, celui-ci est commandé par la tension que prend alors le point a par rapport au point D, tension devenant également V<sub>T</sub>. L'effet des tensions de seuil des transistors T<sub>1</sub> et T<sub>2</sub> est ainsi compensé et le courant devient indépendant de ces dernières de sorte que

$$I_G \approx 2 \cdot C_1 \cdot V_{01} \cdot f$$

Il faudra, bien entendu, dimensionner le circuit de sorte que la tension du point a puisse effectivement atteindre la valeur + V<sub>T</sub>.