(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4002554号

(P4002554)

(45) 発行日 平成19年11月7日(2007.11.7)

(24) 登録日 平成19年8月24日(2007.8.24)

(51) Int.C1.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G06F</b> | <b>17/16</b> | <b>(2006.01)</b> | <b>G06F</b> | <b>17/16</b> | <b>G</b>    |

| <b>G06F</b> | <b>9/38</b>  | <b>(2006.01)</b> | <b>G06F</b> | <b>9/38</b>  | <b>310G</b> |

| <b>G06F</b> | <b>9/45</b>  | <b>(2006.01)</b> | <b>G06F</b> | <b>9/44</b>  | <b>322G</b> |

請求項の数 5 (全 59 頁)

(21) 出願番号 特願2003-586743 (P2003-586743)

(86) (22) 出願日 平成15年4月14日 (2003.4.14)

(65) 公表番号 特表2006-508414 (P2006-508414A)

(43) 公表日 平成18年3月9日 (2006.3.9)

(86) 國際出願番号 PCT/US2003/011571

(87) 國際公開番号 WO2003/090067

(87) 國際公開日 平成15年10月30日 (2003.10.30)

審査請求日 平成18年3月29日 (2006.3.29)

(31) 優先権主張番号 10/127,087

(32) 優先日 平成14年4月22日 (2002.4.22)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 リー、リーウォン

アメリカ合衆国 78758 テキサス州

オースティン クエイルウッド ドライ

ブ 9303 ナンバーエイ

最終頁に続く

(54) 【発明の名称】拡張命令エンコーディングのシステムおよびその方法

## (57) 【特許請求の範囲】

## 【請求項1】

繰り返し処理を行うプログラム・ループ命令、プログラム・ループ命令を実行や停止する標準命令、および標準命令を変更する増補命令、からなる複数の命令(405)を受け取るステップと、

同複数の命令(405)の中から、擬似ベクトル数値命令を識別することによって、繰り返し処理を行うプログラム・ループ(480)命令グループを識別するステップと、データ処理の時に、該プログラム・ループ(480)命令グループに属する命令には、3オペランド以上の第1命令サイズを使用するステップと、

データ処理の時に、該プログラム・ループ(480)命令グループ以外の命令には、標準命令グループ、および同標準命令グループの命令を増強し補完して、早期終了、継続、または条件実行のうちの少なくとも1つを命令する増補命令グループが使用され、同標準命令グループおよび増補命令グループには、第1命令サイズよりもオペランドの少ない第2命令サイズを使用するステップと、

からなる方法。

## 【請求項2】

データ処理の時の動作がベクトル・モードである時に、データ処理が、

標準命令を受け取るステップと、

第1デコーダ(430)を使用して該標準命令をデコードするステップと、

データ処理の時の動作が擬ベクトル・モードである時に、データ処理システムが、

10

20

該標準命令、および外部メモリから増補命令部分を含む命令セットを受け取るステップであって、標準命令グループの命令を増強し補完する該増補命令部分は、早期終了、継続、または条件実行、のうちの少なくとも1つからなる制御情報を含む前記ステップと、該第1デコーダ(430)を使用して該標準命令をデコードするステップと、該第2デコーダ(440)を使用して該増補命令部分をデコードするステップと、からなる方法。

#### 【請求項3】

第1命令サイズを有する第1命令、および第2命令サイズを有する第2命令の、標準命令部分をデコードする第1のデコーダ(430)であって、該第1命令サイズが該第2命令サイズと同一であって、該第2命令は擬ベクトル数値命令を含む、前記第1のデコーダと

、該第2命令の擬標準命令部分をデコードする、該第1のデコーダと異なる第2のデコーダ(440)であって、該第2命令の第2部分はプログラム・ループを実行するための条件制御情報を含み、同条件制御情報は早期終了、継続、または条件実行、のうちの少なくとも1つを含む前記第2デコーダと、

からなるシステム。

#### 【請求項4】

データ処理システムが、繰り返し処理を行うプログラム・ループ命令、プログラム・ループ命令を実行や停止する標準命令、および標準命令を変更する増補命令、からなる複数の命令を受け取るステップと、

同複数の命令のうち、擬似ベクトル数値命令を識別することによって、該命令が、繰り返し処理を行うプログラム・ループを表す命令グループを判定するステップと、

該プログラム・ループを表す命令グループ以外の命令を標準命令に変換するステップと、

、該命令グループの命令を、標準命令部分と、標準命令グループの命令を増強し補完する増補命令部分とを有する増補命令に変換するステップ、であって、該増補命令部分は、プログラム・ループを実行するための条件制御情報を含み、同条件制御情報は早期終了、継続、または条件実行、のうちの少なくとも1つを含む前記ステップと、からなる方法。

#### 【請求項5】

データ処理システムが、コマンドを受け取るステップと、該コマンドにおいて擬似ベクトル数値命令を識別することによって、該命令が、繰り返し処理を行うプログラム・ループに関連するかどうかを判定するステップと、

該コマンドがプログラム・ループに関連しない場合に、該コマンドを標準命令にコンパイルするステップと、

該コマンドがプログラム・ループに関連する場合に、該コマンドを、標準命令部分および、標準命令グループの命令を増強し補完する増補命令部分を有する増補命令にコンパイルするステップであって、該増補命令部分は、プログラム・ループを実行するための条件制御情報を含み、同条件制御情報は早期終了、継続、または条件実行、のうちの少なくとも1つを含む前記ステップと、

からなる方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、一般的にはデータ処理システムでの命令実行に関し、具体的にはループ実行中の拡張長さ命令実行に関する。

##### 【背景技術】

##### 【0002】

最近、ポケット・ベル、セルラ電話機など、ミッドレンジからローエンドの組み込み応

10

20

30

40

50

用向けの低成本、低電力、高性能プロセッサの設計が注目されている。これらの組込み応用の多くが、ディジタル信号処理（DSP）機能など、データ処理システムが高度の繰り返し機能を実行することを必要とし、これらの機能では、大量の命令レベル並列性（Instruction Level Parallelism、ILP）を利用し得ると同時に、システムが制御集中機能を実行する必要もある。

#### 【0003】

この必要に対処するために、一部にシステムで、デュアルコア・ソリューションが使用され、この場合に、一方のコアが、制御集中機能を実行し、他方のコアが、特殊化されたDSP機能を実行する。この手法では、プロセッサ・コアが、共用メモリなどのシステム内で実施される通信チャネルを介して互いに通信する。これらのシステムは、しばしば、実行コアごとに1つのデュアル命令ストリームを使用する。これらのデュアル・コア・システムは、通常は、より高いハードウェア・コストおよび開発コストを有する。10

#### 【0004】

さらに、多くの組込み応用では、一部のループが非常にベクトル化可能であり、他のループが、ベクトル化が困難である。非常にベクトル化可能なループは、「Cray-1 Computer System Hardware Reference Manual」、クレイリサーチ社（Cray Research, Inc.）[米国ミネソタ州ブルーミントン（Bloomington）]、出版番号2240004、1977に記載のものなどの伝統的なベクトル処理パラダイムを使用することによって効率的に処理され得る。これは、ベクトル化可能なループに適用可能であるが、ベクトル化が困難なループには拡張されない。20

#### 【0005】

ベクトル化が困難なループについては、ループ実行の最適化に焦点を合わせたDSPスタイルの処理パラダイムが、より適する。ADSP-2106x SHARC User's Manual、アナログ・デバイセズ社（Analog Devices Inc.）1997年に記載のSHARC製品が、ループ最適化を使用するシステムの例である。。

【非特許文献1】「Cray-1 Computer System Hardware Reference Manual」、クレイリサーチ社（Cray Research, Inc.）[米国ミネソタ州ブルーミントン（Bloomington）]、出版番号2240004、197730

【非特許文献2】ADSP-2106x SHARC User's Manual、アナログ・デバイセズ社（Analog Devices Inc.）1997年

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0006】

ベクトル化が困難なループの効率的な性能を提供するが、この手法は、非常にベクトル化可能なループについて効率的でない。

#### 【課題を解決するための手段】

#### 【0007】

多くの組込み応用例は、その実行時間の大半を、少数のクリティカル・プログラム・ループの実行に費やす。これらのクリティカル・ループは、しばしば、静的コード側のわずかな部分だけを構成する。そのようなシステムでは、性能とシステム・コスト（コード・サイズ）の間の最適トレードオフが、少数のクリティカル・プログラム・ループを除いて、密命令エンコーディング（dense instruction-encoding）方式をプログラム全体について使用した場合に達成され得ることが多い。上の議論から、命令エンコーディングの改善された方法が必要であることは明白である。40

#### 【0008】

本発明の特定の実施形態を、本明細書で提示する図面に示し、説明する。本発明の様々な目的、長所、特徴、および特性、ならびに構造の関連する要素の方法、動作、および機

能と、部分および製造の経済の組合せは、そのすべてが本明細書の一部を形成する、添付図面を参照して以下の説明および請求項を考慮する際に明らかになる。

#### 【発明を実施するための最良の形態】

##### 【0009】

16ビット固定命令長エンコーディングを使用するISA (Instruction Set Architecture)を有する普通のシステムでは、しばしば、命令エンコーディングに対する様々な制限によって性能が悪影響を受ける。たとえば、ISAでは、通常は、3オペランド命令フォーマットではなく、2オペランド命令フォーマットが使用される。この場合に、命令は、通常、オペコード、Ra、Rbというフォーマットを有し、ここで、Raは、ソース・オペランドならびにデスティネーション・オペランドである。その結果、Raの元の値を保存する必要がある場合には、この命令のオペランド自己破壊的性質に起因して、追加の「move」命令が必要である。このISAの命令は、「即」値フィールドをエンコードするのに限られた幅も有する。さらに、ISAは、条件実行機能（たとえば、条件コードがある値である場合に命令を条件的に実行し得ること）をエンコードし得ない。この機能は、短い順方向分岐を除去するのに有利である。命令エンコーディングでのこれらの制限を有するので、16ビット固定命令長エンコーディングを使用するISAは、通常、32ビット固定命令長エンコーディングを使用するISAより低い性能を有する。しかし、前者は、後者より高いコード密度（したがって低いシステム・コスト）を有する。

##### 【0010】

クリティカル・ループについて、本発明では、拡張された命令幅エンコーディングを使用して、大量のプログラム・コードに使用される狭い命令エンコーディングに関連する性能劣化を防ぐ。下記の例を検討されたい。組込みシステムは、その実行時間の約40%を、少数のクリティカル・ループの実行に費やす。これらのループは、プログラムの静的コード・サイズの約1%を構成する。これらのループだけについて命令エンコーディングを拡張することによって、これらのループのサイズを100%だけ増やす。それと同時に、このループの実行時間を100%だけ改善することも可能である。全体として、20%だけ性能が向上する。この例の静的コード・サイズは、1%増えるのみである。

##### 【0011】

本発明は、統合されたデータ・バスでスカラ機能およびベクトル機能を実行する方法を提供する。スカラ機能は、制御機能とみなすことも可能であり、ベクトル機能は、通常は、反復プログラム・ループを置換し、実行するためのものである。この方法では、ループの性質に応じて、従来のベクトル処理パラダイムまたはDSPスタイルの処理パラダイムの間で選択する。プログラム・ループに関するこれらの処理パラダイムの両方を実行する能力を提供することによって、個々のパラダイムより高い性能改善を達成し得る。さらに、ベクトル機能の命令に関連する機能を、増補命令部分の使用を介して拡張し得る。増補命令部分は、ベクトル機能に関連する命令と共に提供される。

##### 【0012】

本明細書で使用する用語「バス」は、データ、アドレス、制御、または状況など、1つまたは複数の様々なタイプの情報を転送するのに使用し得る、複数の信号または導体を指すのに使用される。用語「アサート」および「ネゲート」は、信号、状況ビット、または類似する装置を、論理的に真の状態および論理的に偽の状態にすることを指す時に使用される。論理的に真の状態が、論理レベル1である場合に、論理的に偽の状態は、論理レベル0である。論理的に真の状態が、論理レベル0である場合には、論理的に偽の状態は、論理レベル1である。

##### 【0013】

大括弧は、バスの導体または値のビット位置を示すのに使用される。たとえば、「バス60[0から7]」または「バス60の導体[0から7]」は、バス60の8つの下位導体を示し、「アドレス・ビット[0から7]」または「アドレス[0から7]」は、アドレス値の下位8ビットを指す。数字の前の記号「\$」は、その数が16進数または16を

10

20

30

40

50

底とする形で表されることを示す。数字の前の記号「%」は、その数が2進数または2を底とする形で表されることを示す。

#### 【0014】

ベクトル処理パラダイムで、データは、メモリまたはベクトル・レジスタから継続的に流れ、非常にパイプライン化された形の一連の機能ユニットによって処理される。処理されたデータは、メモリに継続的に流れる。上で述べた Cray アーキテクチャが、このパラダイムを使用するシステムの初期の例である。

#### 【0015】

ベクトル処理パラダイムの威力を、次の例のループを使用して示し得る。

#### 【実施例1】

#### 【0016】

#### 【数1】

L1:

```

addi      R2,2      // update stride value

ld.h      R7,(R2)   // load with stride of 2

addi      R3,1      // update stride value

ld.b      R6,(R3)   // load with stride of 1

mul      R7,R6     // multiply

st.h      R7,(R2)   // store with stride of 2

dec.ne   R1        // decrement loop index r1

// set c bit if r1 not equals zero

bt       L1        // branch to L1 if c bit is set

```

このループは、2つのベクトルに対して要素単位の乗算を実行する。このループは、ベクトル形式で、ベクトルA、B、Cについて  $C[i] = A[i] * B[i]$ 、 $i = 0, \dots, n - 1$  を実行する。

#### 【0017】

この例では、中間値が、作られ、即座に消費される。これらの値は、連続的にレジスタ  $r_6$  および  $r_7$  に書き戻され、読み取られる。これらは、作られ、1回だけ消費されるので、これらの値を、しばしば限られているレジスタ記憶空間に蓄積することは非効率的である。この状況は、残念ながら、ベクトル動作が load-store ISA (Instruction Set Architecture) を使用して表される時に、不可避である。

#### 【0018】

より効率的な手法は、複数の機能ユニットを一緒にチェーンにし、各ユニットが特定のタスクを実行することである。この形で、中間値が機能ユニットによって作られる時に、その値が、チェーン内の次の機能ユニットに直接に渡され、これによって、値のストアおよび検索に関連するレジスタ・ファイルへの読み取りトライフィックおよび書き込みトライフィックが回避される。

#### 【0019】

ベクトル動作またはベクトル実行をパイプライン化し、すべてのサイクルに1つの結果を作り得るようにすることも可能である。一般に、ベクトル動作を実行するのに必要な時間は、 $T_s + n / T_r$  によって与えられ、ここで、 $T_s$  は、初期セットアップ・コストであり、 $n$  は、ベクトルの長さであり、 $T_r$  は、各サイクルに作られる結果の個数単位のスループット・レートである。スカラ計算機が、同等のプログラム・ループの1つの反復を実行するのに  $m$  サイクルを要する場合に、ベクトル計算機を使用することによる速度向上

10

20

30

40

50

は、 $n m / (T s + n / T r)$  または  $T r = 1$  の場合に  $n m / (T s + n)$  によって与えられる。最大の速度向上は、 $T s$  が十分に小さく、 $n$  が十分に大きい時に達成し得る。この場合に、速度向上が  $m$  に達し、これは、スカラ計算機がプログラム・ループの 1 つの反復を実行するのに要するサイクル数である。

#### 【0020】

ベクトル処理は、複数の効果を有する。様々な動作を单一のデータ・ストリームでパイプライン化し、改善された性能をもたらし得る。効率的なデータのストレージおよび移動がもたらされる。というのは、大量の一時データが作られ、レジスタ・ファイルまたはメモリ・システムを通らずに、隣接する機能ユニットによって消費されるからである。さらに、ベクトル処理では、小さいルーティング区域が使用される。というのは、データ・バス全体にプロードキャストするのではなく、機能ユニットが、デステイネーション機能ユニットに直接にルーティングされるからである。効率的なデータ移動およびより小さいルーティング区域によって、電力消費が減る傾向がある。さらに、ベクトル実行中に命令を要求する必要がないので、より低い命令フェッチ帯域幅が達成される。ベクトル処理パラダイムの威力によって、ベクトル処理パラダイムが、低コスト、低電力組込みコンピュータ・システムに非常に適するようになる。

#### 【0021】

あるベクトル A、B、および C について、

$$C[i] = A[i] * B[i], \quad i = 0, \dots, n - 1$$

によって記述されるベクトル演算を実行するループは、非常にベクトル化可能なループである。ループ・ベクトル化のしやすさは、通常は、ハードウェアおよびシステム構成の関数である。一般に、実行される算術関数を決定するのに実行時情報に依存しないループは、ベクトル化しやすい。本明細書で使用される CVA ( Canonical Vector Arithmetic ) は、非常にベクトル化可能なループによって実行し得るベクトル算術を表す。下に、CVA のもう 1 つの例を示す。

#### 【0022】

$$C[i] = 4 * A[i] + (B[i] >> 1), \quad i = 0, \dots, n - 1$$

この CVA は、次のように複数の CVA に分解し得る。ある一時ベクトル T1 および T2 について、

$$T1[i] = 4 * A[i]; \quad T2[i] = B[i] >> 1; \quad C[i] = T1[i] + T2[i], \quad i = 0, \dots, n - 1 \quad 30$$

DSP アルゴリズムまたは DSP 機能は、組込み計算機で実施される時に、しばしばプログラム・ループに変換される。最適化コンパイラは、ループを再構成し、すべての可能な並列性を計算機によって簡単に利用し得るようにする。しかし、そのようなプログラム・ループは、ベクトル化が簡単でない。そのようなプログラム・ループは、コンパイラによってベクトル処理パラダイムに「あてはまる」ように変換された後にベクトル化可能になる可能性がある。これらの変換には、マスク生成、動作の収集および分散などが含まれる可能性がある、ある追加のベクトル動作の追加が含まれる。

#### 【0023】

たとえば、

$$C[i] = (A[i] > B[i]) ? A[i]^2 : A[i] + B[i], \quad i = 0, \dots, n - 1$$

によって記述されるベクトル動作を実行するループは、ベクトル化が困難であるか高コストである。具体的に言うと、このループは、条件

$$A[i] > B[i]$$

に動的に頼って、結果の要素 C[i] を得るために実行される算術関数を決定する。このタイプの算術を、本明細書では PVA ( Pseudo-Vector Arithmetic ) と称する。

#### 【0024】

DSP タイプの計算機は、プログラム・ループの実行を最適化することによって、PVA

10

20

40

50

A 算術を効率的に実行する。これらの計算機で、( i ) ループ制御機構、( i i ) 定数ストライド・ロード、および( i i i ) 定数ストライド・ストアに関連するオーバーヘッドの多くを除去することによって性能が改善される。

#### 【 0 0 2 5 】

伝統的な D S P プロセッサの命令によって、複数の計算動作およびメモリ動作を並列に実行することを指定し得る。そのようなプロセッサの動作は、複数の動作が並列に発行される V L I W ( V e r y L o n g I n s t r u c t i o n W o r d ) プロセッサの動作に非常に類似する。

#### 【 0 0 2 6 】

本発明は、ベクトル・タイプ処理を使用するベクトル化可能ループおよび D S P タイプの処理を使用するベクトル化が困難または不可能なループの処理の手段を提供する。ループのタイプに応じて、計算機は、ある条件の下ではベクトル・プロセッサのように振る舞い、他の条件の下では D S P プロセッサのように振る舞う。さらに、この計算機は、単一データ・パスを使用して、プログラムのすべてのベクトル算術ならびにスカラ部分（すなわち非ループ部分）を実行し、同一のハードウェア・リソースの効率的な再利用を可能にする。

#### 【 0 0 2 7 】

本発明は、ベクトル・タイプ処理または D S P タイプ処理のどちらを使用するかを決定する判断機構としてベクトル化を組み込む。前者を、 C V A 実行とも称する。後者を、 P V A 実行とも称する。この新しい処理パラダイムを、本明細書では「擬似ベクトル計算機 ( P s e u d o - V e c t o r M a c h i n e ) 」と称する。

#### 【 0 0 2 8 】

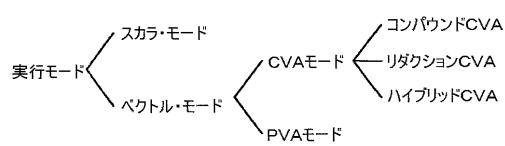

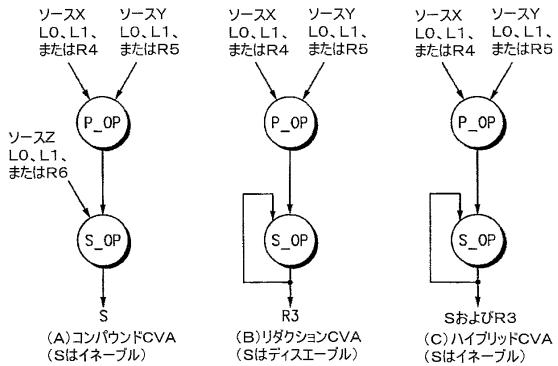

この新しい処理パラダイムによれば、実行モデルが、2つのモードすなわち、( i ) 制御機能に関するスカラ実行モードおよび( i i ) 命令レベル並列性 ( i n s t r u c t i o n l e v e l p a r a l l e l i s m , I L P ) を利用するベクトル実行モードで動作し得る。図 1 に、本発明の 1 実施形態の実行モードを示す。2つの基本モードが、スカラおよびベクトルであり、ベクトル・モードには、さらに特定の実行モードが含まれる。 C V A および P V A は、ベクトル・モードでのみ使用可能であり、 C V A モード実行には、( i ) コンパウンド ( c o m p o u n d ) 、( i i ) リダクション ( r e d u c t i o n ) 、および( i i i ) ハイブリッド ( h y b r i d ) という 3 つのタイプがある。それに対応して、この計算機には、2つのベクトル命令すなわち、 C V A 命令および P V A 命令がある。

#### 【 0 0 2 9 】

図 1 の実行モデルでは、スカラ・モードおよびベクトル・モードが、時間的にオーバーラップしない。モデルは、単一の命令ストリームを使用して、単一のデータ・パスでこの 2 つのモードを実行する。このストリーム内の各命令は、スカラ命令またはベクトル命令のいずれかとして分類し得る。ベクトル命令がフェッチされ、デコードされる時に、計算機は、ベクトル実行モードに入る。計算機は、少数の事前定義の機構を介してのみベクトル・モードから出る。

#### 【 0 0 3 0 】

非常にベクトル化可能であるループに関して、計算機は、 C V A 実行モードすなわち、「真の」ベクトル処理パラダイムを使用して、ループを処理する。ベクトル化が困難または不可能であるループに関して、計算機は、 P V A 実行モードすなわち、 D S P スタイルの処理に似た「擬似」ベクトル処理パラダイムを使用して、ループを処理する。最適化コンパイラは、この場合に、所与のプログラム・ループにどの実行モードが最も適するかを判断する。一般に、コンパイラは、まず、ベクトル処理パラダイムの低電力態様および高性能態様を利用することを試みて、真のベクトル命令または C V A 命令を使用するループのベクトル化を試みる。これが可能でない場合には、コンパイラは、 P V A 命令または両方の組合せを使用して、 D S P スタイルのループベース実行にフォール・バックする。

#### 【 0 0 3 1 】

10

20

20

30

40

50

普通の意味でのベクトル化は、ベクトル化可能プログラム・ループを識別し、ある同等のベクトル演算と置換することを指す。さらに、本発明は、プログラム・ループを識別し、D S Pスタイルのループ構造と置換するベクトル化を提供する。これには、D O U N T I L命令またはD O W H I L E命令を含め得る。そのようなループは、普通の意味ではベクトル化が困難または不可能である可能性がある。擬似ベクトル計算機で、P V A命令が、D S Pタイプ・プログラム・ループの構成およびベクトル化に使用される。

#### 【0032】

プログラム・ループが、1つまたは複数のベクトル命令（C V A命令および／またはP V A命令）からなる同等のコードに置換される時に、そのプログラム・ループを、ベクトル化されたという。このベクトル化されたコード・セグメントを、元のスカラ・プログラム・ループと同等の機能を実行するので、元のスカラ・プログラム・ループのベクトル同等物とも称する。ベクトル化は、アセンブリ・レベルまたはソース・コード・レベルで行い得る。

#### 【0033】

ループが、C V A構成を使用してベクトル化可能である場合に、これをC V Aベクトル化可能という。ループが、P V A構成を使用してベクトル化可能である場合に、これをP V Aベクトル化可能という。ループが、C V Aベクトル化可能である場合に、そのループは、P V Aベクトル化可能でもある。しかし、逆は一般に真でない。P V A構成は、より一般的なベクトル化機構を表す。同等のハードウェア・コストで、C V A実行は、通常は、非常にベクトル化可能であるループのより高い性能の利益を提供する。ベクトル化が不可能またはコストが高すぎるループについて、P V A実行が、よりよい性能の利益を提供する。

#### 【0034】

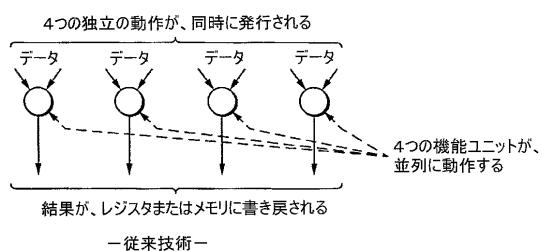

D S Pタイプ実行および／またはV L I Wタイプ実行と、ベクトル・タイプ実行との間の区別を、図2および3に示す。図2に、D S Pタイプ実行の動作を示すが、ここでは、複数の独立の動作が、複数の機能ユニットに同時に発行される。これらの独立の機能ユニットによって作られた結果が、あるアーキテクチャ的レジスタおよび／またはメモリ・システムに書き戻される。図2に示された動作によって、V L I W計算機の動作も記述されることに留意されたい。

#### 【0035】

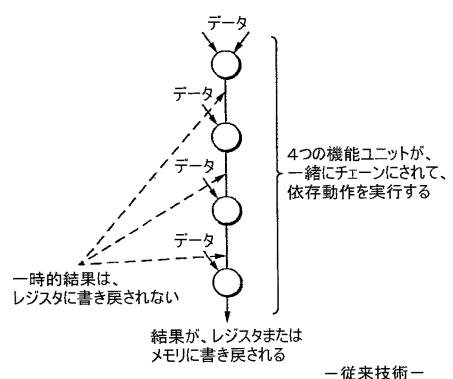

図3に、伝統的なベクトル実行を示すが、ここでは、複数の機能ユニットが、一緒にチェーンにされて、依存する動作を実行する。チェーンされた機能ユニットの間の一時的结果は、アーキテクチャ的レジスタに書き戻されず、メモリ・システムにも書き込まれない。さらに、ベクトル実行は、ベクトル命令の最初のフェッチおよびデコードの後に、そのベクトル実行の残りについてさらなる命令要求をまったく行わないという事実も特徴とする。

#### 【0036】

本発明は、D S Pタイプ実行とベクトル実行を1つの統合されたデータ・バスで組み合わせる方法を提供する。本明細書で使用されるP V A実行は、D S Pタイプ実行であり、C V A実行は、ベクトル実行である。したがって、本発明は、1つの処理システム内の各タイプの実行の利益を利用する。

#### 【0037】

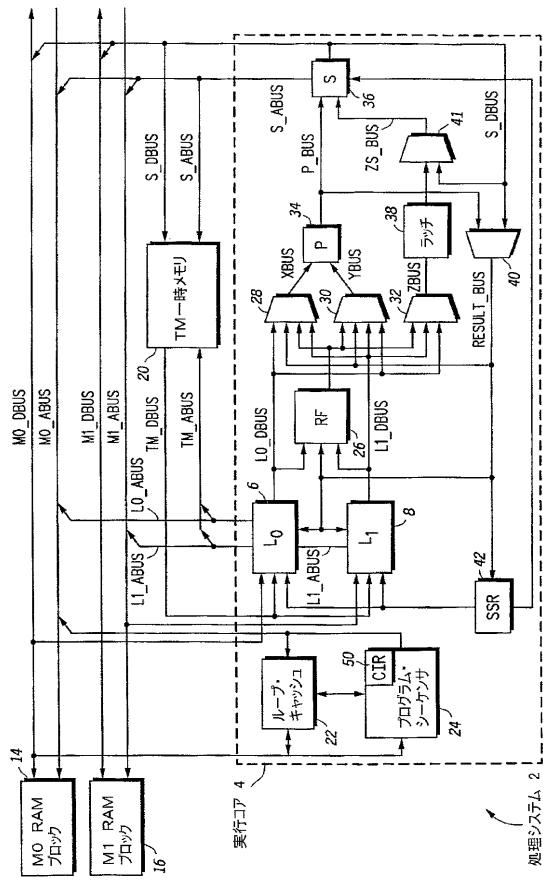

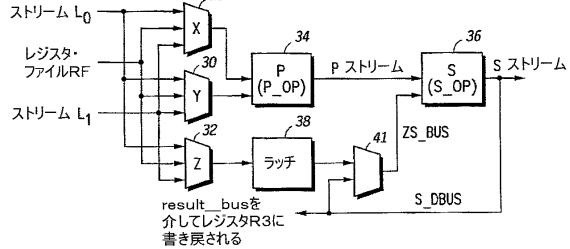

図4に、本発明の1実施形態による処理システム2を示す。処理システム2には、単一のデータ・バスでスカラ実行、C V A実行、およびP V A実行を実行する処理アーキテクチャが組み込まれる。実行コア4に、第1ロード・ユニットL<sub>0</sub>～L<sub>6</sub>および第2ロード・ユニットL<sub>1</sub>～L<sub>8</sub>が含まれる。情報は、メモリM<sub>0</sub>～M<sub>14</sub>からL<sub>0</sub>～L<sub>6</sub>に、およびメモリM<sub>1</sub>～M<sub>16</sub>からL<sub>1</sub>～L<sub>8</sub>にロードされる。

#### 【0038】

本発明の1実施形態で、M<sub>0</sub>～M<sub>14</sub>およびM<sub>1</sub>～M<sub>16</sub>が、ランダム・アクセス・メモリ(R A M)ブロックであるが、他のタイプのメモリ・ストレージ・デバイスを使用して実

10

20

30

30

40

50

施し得る。メモリ M0\_14 は、M0\_d bus を介してデータ情報を、M0\_a bus を介してアドレス情報を、処理システム 2 の残りと通信する。同様に、M1\_16 は、M1\_d bus を介してデータ情報を、M1\_a bus を介してアドレス情報を通信する。

〔 0 0 3 9 〕

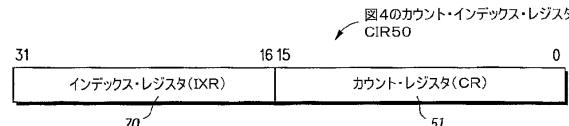

実行コア4に、プログラム・シーケンサ24、M0\_d bus、およびM0\_a busに結合されたループ・キャッシュ22も含まれる。プログラム・シーケンサ24は、M0\_d busおよびM0\_a busにも結合され、プログラム・シーケンサ24には、さらに、カウント・インデックス・レジスタ(CIR)50が含まれる。CIR50には、2つの独立のレジスタすなわち(i)カウント・レジスタ(CR)および(ii)インデックス・レジスタ(IXR)が含まれる。CIR50は、図11にも示されており、この図では、CR51が、CVA実行のベクトル長またはPVA実行の反復回数を指定するのに使用される。ループ・キャッシュは、M0\_d busを介してデータを受け取るように結合される。プログラム・シーケンサ24は、M0\_a busを介してM0\_14にアドレス情報を提供する。

〔 0 0 4 0 〕

レジスタ・ファイル( R F ) 2 6 も設けられ、データが、 L<sub>0</sub> 6 から L 0 \_ d b u s を介して、および L<sub>1</sub> 8 から L 1 \_ d b u s を介して R F 2 6 に供給される。 R F 2 6 、 L<sub>0</sub> 6 、および L<sub>1</sub> 8 のすべてが、マルチプレクサ 2 8 、 3 0 、および 3 2 に結合される。マルチプレクサ 2 8 は、 x b u s を介して主算術ユニット( P ) 3 4 に情報を供給する。 1 実施形態で、 P 3 4 は、汎用機能ユニットである。 P 3 4 は、基礎になる I S A で定義されたスカラ算術機能のすべてを実行し得る。マルチプレクサ 3 0 は、 y b u s を介して P 3 4 に情報を供給する。 20

〔 0 0 4 1 〕

P 3 4 の結果は、p\_busを介して副算術／ストア・ユニット(S)36に供給される。P 3 4 の結果は、マルチプレクサ40にも供給される。メモリ・ストア動作を実行するほかに、S 3 6 は、「add」、「and」、「or」、「xor」などの単純な算術論理ユニット(ALU)算術も実行し得る。マルチプレクサ32は、zbusを介してラッチ38に情報を供給し、この情報は、ラッチ38からマルチプレクサ41に供給される。マルチプレクサ41の出力は、zs\_busを介してS 3 6 に情報を供給する。S 3 6 のデータ出力は、s\_dbusを介してマルチプレクサ40、マルチプレクサ41、M 1 \_dbus、M 0 \_dbus、および一時メモリ(商標)20に供給される。S 3 6 のアドレス出力は、s\_abusを介してM 0 \_abus、M 1 \_abus、および一時メモリ(TM)20にも供給される。マルチプレクサ40の出力は、result\_busを介して、RF26、L<sub>0</sub>6、L<sub>1</sub>8、SSR42、マルチプレクサ28、およびマルチプレクサ30に情報を供給する。

[ 0 0 4 2 ]

スカラ・モードで実行する時に、実行コアは、単一発行パイプライン式計算機のように振る舞う。実行コアは、スカラ計算にレジスタ・ファイルRF26およびP34を使用し、メモリ・ロード／ストア動作にL<sub>0</sub>6、L<sub>1</sub>8、およびS36を使用する。具体的に言うと、これらのロード／ストア動作のメモリ・アドレスが、S36によって、TM20、M014、およびM116を含むメモリ・システムに供給される。メモリ・ストア動作について、データが、S36ユニットによって供給される。メモリ・ロード動作について、データは、メモリ・システムによって、L<sub>0</sub>6およびL<sub>1</sub>8を介し、L0\_d busおよびL1\_d busを介して、RF26およびP34に供給される。

[ 0 0 4 3 ]

ベクトル・モードで実行する時に、ベクトル命令すなわち、CVA命令またはPVA命令によって、任意選択として、2つまでの入力データ・ストリーム $L_0$ および $L_1$ および1つのデータ・ストリームをイネーブルし得る。

[ 0 0 4 4 ]

ベクトル：モードで実行する時に、`データを、M 0 1 4 から L 6 および L 0 d b 50`

$u_s$  を介して継続的にフェッチし、RF26、P34、またはS36への複数のパスのいずれかによって供給し得る。第1パスは、L0\_dbusを介してRF26にデータをストリーミングするのに使用される。第2パスは、マルチプレクサ28を介してP34にデータをストリーミングするのに使用され、第3パスは、マルチプレクサ30を介してP34にデータをストリーミングするのに使用される。第4パスは、マルチプレクサ32、ラッチ38、およびマルチプレクサ41を介してS36にデータをストリーミングするのに使用される。PVA実行に関して、第1パス、第2パス、および第3パスの1つまたは複数を、PVA命令に応じて使用し得る。CVA命令に関して、第2パス、第3パス、および第4パスの1つまたは複数を、CVA命令に応じて使用し得る。これらのデータ・ストリームのどれをも、入力データ・ストリーム  $L_0$  と称する。

10

#### 【0045】

同様に、ベクトル・モードで実行する時に、データを、 $L_1$  8 および  $L_1_dbus$  を介して M1 16 から継続的にフェッチし、複数のパスのいずれかによって RF26、P34、または S36 に供給し得る。第1パスは、 $L_1_dbus$  を介して RF26 にデータをストリーミングするのに使用される。第2パスは、マルチプレクサ28を介してP34にデータをストリーミングするのに使用され、第3パスは、マルチプレクサ30を介してP34にデータをストリーミングするのに使用される。第4パスは、マルチプレクサ32、ラッチ38、およびマルチプレクサ41を介してS36にデータをストリーミングするのに使用される。PVA実行に関して、第1パス、第2パス、および第3パスの1つまたは複数を、PVA命令に応じて使用し得る。CVA命令に関して、第2パス、第3パス、および第4パスの1つまたは複数を、CVA命令に応じて使用し得る。これらのデータ・ストリームのどれをも、入力データ・ストリーム  $L_1$  と称する。

20

#### 【0046】

また、ベクトル・モードでは、データを、S36 からメモリ・モジュール M0 14、M1 16、または TM20 の1つに継続的にストアし得る。この出力データ・ストリームを、出力データ・ストリーム  $S$  と称する。

#### 【0047】

実行コア4に、さらに、対応するロード／ストア動作がイネーブルされる場合に  $L_0$  ストリーム、 $L_1$  ストリーム、および  $S$  ストリームのストライドおよびオペランド・サイズを指定するストライド・サイズ・レジスタ (SSR) 42 が含まれる。SSR42 は、 $L_0$  6、 $L_1$  8、RF26 および S36 に結合される。SSR42 は、さらに、result\_bus を介して情報を受け取るためにマルチプレクサ40に結合される。一時メモリ・ストレージ・ユニット、TM20 が、S36、 $L_0$  6、および  $L_1$  8 に結合される。TM20 は、一時ベクトルまたは任意のデータのストアに使用し得る。TM20 にストアされるベクトルは、固定ベクトル長に制限されない。

30

#### 【0048】

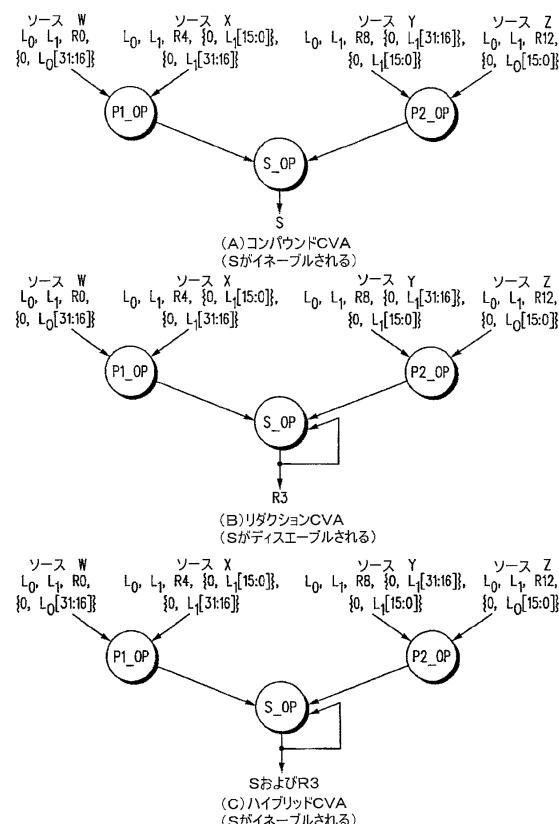

処理システム2で実行されるCVAの3つのタイプを表すデータ依存性グラフを、図5に示す。図5に示されたCVAの3つのタイプのすべてで、2つの入力の近くで実行される第1算術を、主算術と呼び、 $p_{op}$  と表す。この算術は、図3のP34によって実行される。出力の近くで実行される第2算術を、副算術と呼び、 $s_{op}$  と表す。この算術は、図3のS36によって実行される。

40

#### 【0049】

図5に、本発明の1実施形態に関する、CVAの入力データ・ストリーム  $L_0$  および  $L_1$  とソース・オペランド X、Y、および Z の間の関係を示す。オペランド X は、 $L_0$  ストリーム、 $L_1$  ストリーム、またはレジスタ  $r_4$  からソーシングし得る。オペランド Y は、 $L_0$  ストリーム、 $L_1$  ストリーム、またはレジスタ  $r_5$  からソーシングし得る。オペランド Z は、 $L_0$  ストリーム、 $L_1$  ストリーム、またはレジスタ  $r_6$  からソーシングし得る。X オペランドおよび Y オペランドは、主算術  $p_{op}$  で使用される。主算術の結果が、副算術  $s_{op}$  に転送される。CVAのタイプに応じて、副算術  $s_{op}$  は、オペランド Z または  $s_{op}$  自体の出力からソーシングし得る。

50

## 【0050】

図5の(A)に示されたコンパウンドCVAは、ベクトル計算の結果としてデスティネーション・ベクトルを作る。コンパウンドCVAの一般形式を次のように表し得る。

ソースXおよびソースYがすべてベクトルである場合に

$$R_i = (X_i \ p_o p \ Y_i) s_o p \ Z_i, i = 0, \dots, n - 1$$

ここで、nは、ベクトルの長さを表し、 $p_o p$ は、主算術を表し、 $s_o p$ は、副算術を表し、 $R_i$ は、デスティネーション・ベクトルの第*i*要素を表し、 $X_i$ 、 $Y_i$ 、および $Z_i$ は、それぞれベクトルX、Y、およびZの第*i*要素である。

## 【0051】

ソースXが、スカラ×定数であり、ソースYがベクトルである場合には

$$R_i = (x \ p_o p \ Y_i) s_o p \ Z_i, i = 0, \dots, n - 1$$

である。

## 【0052】

ソースXが、ベクトルであり、ソースYが、スカラ定数yである場合には、

$$R_i = (X_i \ p_o p \ y) s_o p \ Z_i, i = 0, \dots, n - 1$$

である。副算術 $s_o p$ を、「ノー・オペレーション」にすることも可能であることに留意されたい。

## 【0053】

リダクションCVAについて、図5の(B)に示されているように、XオペランドおよびYオペランドのソースは、コンパウンド・タイプと同一であるが、Zオペランドは使用されない。副算術の出力が、 $s_o p$ 自体への入力としてフィードバックされる。この場合に、Sストリームはディスエーブルされる。リダクションCVAは、ベクトル・リダクション演算を実行し、この動作では、1つまたは複数のベクトルが、ベクトル演算の結果として、スカラ結果に換算される。リダクションCVAの一般形式を、次のように表し得る。

## 【0054】

ソースXおよびソースYのすべてがベクトルである場合に、

$$S_0 = (X_0 \ p_o p \ Y_0)$$

$$S_i = (X_i \ p_o p \ Y_i) s_o p \ S_{i-1}, i = 1, \dots, n - 1;$$

$$r = S_{n-1}$$

ここで、 $S_i$ は、*i*番目の部分的結果を表し、 $r$ は、ベクトル・リダクション演算のスカラ結果を表す。

## 【0055】

ソースXが、スカラ定数xであり、ソースYがベクトルである場合には、

$$S_0 = (x \ p_o p \ Y_0)$$

$$S_i = (x \ p_o p \ Y_i) s_o p \ S_{i-1}, i = 1, \dots, n - 1;$$

$$r = S_{n-1}$$

ソースXが、ベクトルであり、ソースYが、スカラ定数yである場合には、

$$S_0 = (X_0 \ p_o p \ y)$$

$$S_i = (X_i \ p_o p \ y) s_o p \ S_{i-1}, i = 1, n - 1;$$

$$r = S_{n-1}$$

である。

## 【0056】

副算術に関するフィードバック・パスは、部分的結果を計算し、累算し、最終的に最後のスカラ結果を作る責任を負う。そのようなリダクション演算の例が、 $A[i] * B[i]$ によって記述される、2つのベクトルの内積である。この場合に、主算術は、「乗算」関数であり、副算術は、累算的「加算」関数である。

## 【0057】

図5を継続すると、(C)として示されたハイブリッドCVAを用いると、リダクションの場合と同一の、XオペランドおよびYオペランドのソースならびに副算術のフィード

バックが可能になるが、ハイブリッドの場合には、Sストリームがイネーブルされる。ハイブリッドCVAは、中間の部分的結果が、Sストリームを介してデスティネーション・ベクトルに継続的に書き込まれることを除いて、リダクションCVAと同一である。ハイブリッドCVAの一般形式は、部分的結果  $S_i$ 、 $i = 0, \dots, n - 1$  も、デスティネーション・ベクトル  $R$  を形成し、 $R_i = S_i$ 、 $i = 0, \dots, n - 1$  であることを除いて、リダクションCVAと同一である。ハイブリッドCVAについて、2つのデスティネーションすなわち、スカラ・デスティネーションおよびベクトル・デスティネーションがある。

#### 【0058】

ハードウェア・コストを制限するために、本発明の1実施形態では、複数の制約を課す。第1に、コンパウンドCVAでは、組み合わされる2つの算術が、2つまでの別個のベクトルからソーシングすることだけが可能である。しかし、この制約は、2つまでの別個のベクトルからソーシングする限り、3つのすべてのソース・オペランドがベクトルである場合を除外しない。たとえば、 $C[i] = A[i] * A[i] + B[i]$  によって記述されるベクトル演算は、2つの別個のベクトル  $A$  および  $B$  からソーシングする、3つのソース・ベクトル・オペランドを有する。別個のソース・ベクトルの数に関するこの制約によって、最大メモリ帯域幅要件が、1サイクルあたり3つのデータ・フェッチから1サイクルあたり2つのデータ・フェッチに減る。

#### 【0059】

上記の制約のほかに、副算術を、少数の単純な可換ALU関数に制限し得る(ALU関数  $o_p$  は、すべてのスカラ  $x$  および  $y$  について  $x o_p y == y o_p x$  である場合に、可換という)。この関数に、add、and、or、または xor などが含まれる。

#### 【0060】

CVAの少数の例を、下の表に示す。

10

20

【表1】

表1. CVAの例

| 例               | ベクトル算術                                      | 説明                | CVA ベクトル命令                                   | イネーブルされるストリーム |    |   |

|-----------------|---------------------------------------------|-------------------|----------------------------------------------|---------------|----|---|

|                 |                                             |                   |                                              | L0            | L1 | S |

| (i) コンパウンドCVA   |                                             |                   |                                              |               |    |   |

| (a)             | $C[i]=sA[i]+B[i]$                           | ベクトル定数の乗算および加算    | CVA mul r4, @L0, @P, add @P, @L1, @S;        | Y             | Y  | Y |

| (b)             | $C[i]=(A[i])^2+B[i]$                        | 要素単位の二乗および加算      | CVA mul @L0, @L0, @P, add @P, @L1, @S;       | Y             | Y  | Y |

| (c)             | $C[i]=(A[i])^2$                             | 要素単位の二乗           | CVA mul @L0, @L0, @S;                        | Y             | N  | Y |

| (d)             | $C[i]=abs(A[i])$                            | 要素単位の絶対値          | CVA abs @L0, @S;                             | Y             | N  | Y |

| (e)             | $C[i]=A[i]$                                 | ベクトル代入            | CVA mov @L0, @S;                             | Y             | N  | Y |

| (f)             | $C[i]=0$                                    | メモリ・ブロック初期化       | CVA mov 0, @S;                               | N             | N  | Y |

| (ii) リダクションCVA  |                                             |                   |                                              |               |    |   |

| (g)             | $IP=\sum_i(A[i]*B[i])$                      | ベクトル内積            | CVA mul @L0, @L1, @P, add r3, @P, r3;        | Y             | Y  | N |

| (h)             | $Norm^2=\sum_i(A[i])^2$                     | ベクトル A の「ノルム」の二乗  | CVA mul @L0, @L0, @P, add r3, @P, r3;        | Y             | N  | N |

| (i)             | $Sum=\sum_i A[i]$                           | 合計を介するベクトル・リダクション | CVA mov @L0, @P, add r3, @P, r3;             | Y             | N  | N |

| (iii) ハイブリッドCVA |                                             |                   |                                              |               |    |   |

| (j)             | $C[i]=A[i]*B[i];$<br>$IP=\sum_i(A[i]*B[i])$ | ベクトル乗算およびベクトル内積   | CVA mul @L0, @L1, @P, add r3, @P, { @S, r3}; | Y             | Y  | Y |

この例のそれぞれに、対応する CVA 命令ならびに L<sub>0</sub> ストリーム、L<sub>1</sub> ストリーム、および S ストリームのイネーブル設定およびディスエーブル設定も詳細に示されている。この CVA 命令で、「@」は、データ・ストリームを表す。具体的に言うと、「@ L<sub>0</sub>」は、メモリからの第 1 入力データ・ストリーム L<sub>0</sub> を表し、「@ L<sub>1</sub>」は、メモリからの第 2 入力データ・ストリーム L<sub>1</sub> を表し、「@ P」は、主算術 p\_o\_p によって作られる中間結果ストリームを表し、「@ S」は、メモリへの出力データ・ストリーム S を表す。1 実施形態で、L<sub>0</sub> ストリーム、L<sub>1</sub> ストリーム、および S ストリームのすべてが、一定のストライドのメモリ動作である。

10

20

30

40

50

## 【0061】

コンパウンドCVA動作に関して、CVA命令で、上の表1の(a)および(b)に示されているように、主算術と副算術の両方を指定し得る。この2つの算術は、CVA命令で、それらを区切るコンマを用いて指定され、主算術が先に指定され(この例では、主算術が、3番目のコンマの左に、単語「add」の前に配置される)、副算術がそれに続く(この例では、副算術が、3番目のコンマの右に、単語「add」から始めて配置される)。命令は、「;」記号で終わる。この例では、「@P」ストリームが、主算術のデスティネーションとして現れ、副算術にもソースとして現れる。

## 【0062】

コンパウンドCVA動作に関して、CVA命令で、上の表1の(c)から(f)のように、主算術を指定するが、副算術を指定しないことが可能である。副算術、この例ではs\_0pは、「ノー・オペレーション」であり、主算術によって作られた結果が、「@S」ストリームを介してメモリに直接にストアされる。「@P」ストリームは、これらの命令で指定されない。

10

## 【0063】

リダクションCVAについて、CVA命令では、上の表1の(g)から(i)のように、主算術と副算術の両方が指定される。この例では、「@P」ストリームが、主算術のデスティネーションとして現れ、副算術にもソース・オペランドの1つとして現れる。副算術のデスティネーションおよび第2ソース・オペランドは、レジスタR3である。リダクションCVAに関して、R3が、リダクション演算の部分的結果ならびに最終スカラ結果をストアするように指定される。

20

## 【0064】

副算術は可換なので、速記表記を使用して、リダクションCVAを記述し得る。この場合に、副算術式全体が、s\_0pの関数名によって置換される。たとえば、内積を計算するCVA命令(上の表1の例(g))を、下記のように書き得る。

## 【0065】

CVA mul @L0、@L1、add ; // リダクションCVAの速記表記

ハイブリッドCVAについて、命令構文は、副算術が2つのデスティネーションすなわちSストリームおよびレジスタR3を有することを除いて、リダクションCVAの構文に類似する。2つのデスティネーションは、CVA命令では「{@S, R3}」という形で現れる。ハイブリッドCVAの速記表記はない。

30

## 【0066】

図6に、1実施形態による、図4の実行コア4によって3タイプのCVA(図5に図示)がどのように実行されるかを示す。ストリームL<sub>0</sub>が、L<sub>0</sub>\_dbusを介してL<sub>0</sub>6に供給され、ストリームL<sub>1</sub>が、L<sub>1</sub>\_dbusを介してL<sub>1</sub>8に供給される。図6では、オペランドX、Y、およびZが、ストリームL<sub>0</sub>、ストリームL<sub>1</sub>、またはRF26の指定されたレジスタからソーシングし得る。具体的に言うと、Zオペランドが、マルチプレクサ32、ラッチ38、マルチプレクサ41、およびzs\_busを介してS36に供給される。さらに、s\_dbus、マルチプレクサ41、およびzs\_busが、リダクションCVAおよびハイブリッドCVAの部分的結果を累算するフィードバック・パスとして使用される。リダクションCVAおよびハイブリッドCVAについて、これらの部分的結果は、常に、s\_dbusおよびresult\_busを介してレジスタR3に書き戻される。

40

## 【0067】

図7に、本発明の1実施形態による、CVA命令のフォーマットを示す。この命令には、イネーブル・フィールドが含まれ、E<sub>0</sub>、E<sub>1</sub>、およびE<sub>S</sub>が、それぞれL<sub>0</sub>ストリーム、L<sub>1</sub>ストリーム、およびSストリームのイネーブル・ビットである。V<sub>x0</sub> / V<sub>x1</sub>、V<sub>y0</sub> / V<sub>y1</sub>、およびV<sub>z0</sub> / V<sub>z1</sub>ビットは、それぞれ、CVA命令のオペランドX、Y、およびZがその入力をどのようにソーシングし得るかを指定する。具体的に言うと、これらのビットによって、ストリームL<sub>0</sub>、L<sub>1</sub>、または指定されたレジスタからの

50

これらのオペランドのソーシングが選択される。 $V_{z_0}$  ビット、 $V_{z_1}$  ビット、および $E_s$  ビットの組合せによって、実行される CVA のタイプが定義される。 $p\_o\ p$  フィールドおよび $s\_o\ p$  フィールドによって、それぞれ P34 および S36 で実行される主算術および副算術のオペコードが指定される。

## 【0068】

CVA 実行に関して、カウント・レジスタ (CR) 51 と称する特殊なレジスタが、ベクトル長の指定に使用される。CR51 の 1 実施形態が、図 4 の CIR50 の下位半分として図 11 に示されている。CIR50 の上位半分は、インデックス・レジスタ (IXR) 70 と称し、PVA 実行だけに使用される。

## 【0069】

1 実施形態で、CIR50 は、特殊な「move-to-control-register」命令または「move-from-control-register」命令を使用してソフトウェア・プログラムによってアクセスされる特殊な制御レジスタとして実施される。他の実施形態では、CR51 および IXR70 を、2 つの別々のレジスタとして実施し得る。

## 【0070】

CVA 実行について、CR51 を、CVA 実行の前に適当なベクトル長を用いてソフトウェアによって初期化しなければならない。CVA 実行中に、処理されるベクトル要素ごとに、CR51 が、自動的に 1 つ減分される。CR51 が 0 に達し、ベクトル全体が処理されていることが示される時に、CVA 実行が終了する。計算機は、命令ストリームで、CVA 命令または PVA 命令のいずれかである次のベクトル命令に出会うまで、スカラ・モードに入る。

## 【0071】

あるスカラ s に関するベクトル演算  $C[i] = sA[i] + B[i]$  を、次のように CVA 命令を使用してベクトル化し得る。

## 【0072】

## 【数 2】

## Some initialization code

```

// assign L0 to vector A; assign L1 to vector B; assign S to vector C

```

```

// initialize R5 with the scalar s

```

```

CVA mul @L0, R5, @P, add @P, @L1, @S;

```

これは、コンパウンド CVA である。この例では、 $L_0$  ストリーム、 $L_1$  ストリーム、および S ストリームのすべてがイネーブルされる。ストリーム  $L_0$  は、ベクトル A に割り当てられ、ストリーム  $L_1$  は、ベクトル B に割り当てられ、ストリーム S は、ベクトル C に割り当てられる。レジスタ R5 は、CVA 実行の前に、スカラ s に初期化される。主算術は、「乗算」関数であり、副演算は、「加算」関数である。

## 【0073】

CVA 命令の前に、 $L_0$  ストリームをベクトル A に割り当て、 $L_1$  ストリームをベクトル B に割り当て、S ストリームをベクトル C に割り当てる初期化コードがある。この「割り当て」は、ある特別に指定されたレジスタを、ベクトル A、B、および C にアクセスするための適当な開始ベクトル位置、ストライド値、および要素サイズに初期化することを指す。

## 【0074】

次のプログラム・ループの例を検討されたい。

## 【実施例 2】

## 【0075】

10

20

20

30

40

## 【数3】

L6:

```

ldw      R10,(R14)

addi    R14,4

mov     R7,R10

lsr     R7,R9

mov     R3,R10

lsl     R3,R8

or      R7,R3

stw     R7,(R13)

addi    R13,4

dec.ne R4

bt      L6

```

10

20

このベクトル演算は、次の式によって記述し得る。

$$C[i] = (lsl(A[i], R9) | lsr(A[i], R8))$$

このループでは、1時に1要素ずつベクトルAを読み込み、各要素に対して、右論理シフト(lsr)演算および左論理シフト(lsl)演算を実行する。2つのシフト演算の結果に対して「or」関数を実行し、その結果をデスティネーション・ベクトルCに書き込む。このループは、次のようにベクトル化し得る。

【0076】

## 【数4】

Some initialization code

30

// assign L0 to vector A; assign S to a temporary vector

mov R5, R9

CVA lsr @L0, R5, @S

Some initialization code

// assign L0 to the temporary vector; assign L1 to vector A.

// assign S to vector C.

mov R5, R8

40

CVA lsl @L0, R5, @P, or @L1, @P, @S

例2のループは、2つのコンパウンドCVA命令を使用することによってベクトル化される。第1のCVA命令は、ソース・ベクトルAに対して「lsr」演算を実行し、一時ベクトルを作る。第2のCVA命令は、主算術として「lsl」、副算術として「or」を実行する。後者の命令は、L<sub>0</sub>を介して一時ベクトルを読み取り、これに対して「lsl」演算を実行する。この命令は、L<sub>1</sub>を介して元のソース・ベクトルAを読み取り、主算術から作られた結果との「or」関数を実行する。この命令は、その後、Sを介して結果をベクトルCに書き戻す。この実施形態で、両方のCVA命令のソース・オペランドYが

50

、必ずレジスタ R 5 からソーシングされることに留意されたい。したがって、R 5 を初期化する C V A 実行の前に、追加の「mov」命令が必要である。

#### 【0077】

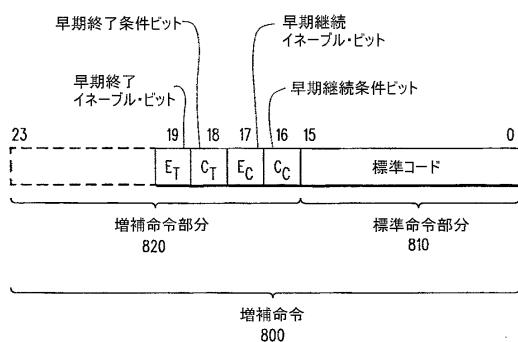

C V A 実行は、C R が 0 になる前に終了することも可能である。C V A 命令は、図 7 に示されているように、E<sub>T</sub> ビットおよびC<sub>T</sub> ビットを含む早期終了フィールドも有する。E<sub>T</sub> ビットは、C V A 計算の早期終了機能をイネーブルまたはディスエーブルする。C<sub>T</sub> ビットは、この機能がイネーブルされる (E<sub>T</sub> = 1) 場合に、これを行う条件コードを指定する。次の例に、この機能をベクトル計算についてどのように使用し得るかを示す。この例では、「c」ビットが、条件コードを指す。

#### 【実施例 3】

#### 【0078】

#### 【数 5】

L1:

```

addi      R2,2

ld.h     R7,(R2)      // load A[i]

addi      R3,1

ld.b     R6,(R3)      // load B[i]

cmplt  R6,R7 // compare less than: is A[i]>B[i]?

bt       EXIT        // if so, exit the loop

dec.ne R1      // decrement loop index R1

// set c bit if r1 not equals zero

bt       L1          // branch to L1 if c bit is set

EXIT

```

このループの対応する高水準ソース・コードを下に示す。

#### 【0079】

#### 【数 6】

```

for (i=0; i<n; i++) {

if (A[i] > B[i]) {break;}

}

```

このループは、ベクトル A と B の間の要素単位の比較を実行する。このループは、ある i について A [ i ] > B [ i ] になるや否や終了する。そのような要素の対がない場合には、ループを終了する前に、ベクトル A と B のすべての要素が処理されている。

#### 【0080】

あるプログラム・ループが、固定長ベクトルに対してある算術関数を実行し、ベクトルの最後の要素が処理される前であっても計算が終了し得る場合に、そのような動作を、早期終了を有するベクトル算術と称する。

#### 【0081】

早期終了を有するベクトル算術には、2つの終了条件すなわち (i) ソース・ベクトルのすべての要素が処理された時、および (i i) ある算術条件が満たされる時がある。後者の条件は、最後のベクトル要素が処理される前に満たされる可能性があり、通常は、データ依存であり、先駆的には判定されない。

10

20

30

40

50

## 【0082】

例3に示されたループは、早期終了を有するベクトル算術である。このループは、CVA構造を使用して下記のようにベクトル化し得る。

## 【0083】

## 【数7】

```

<Some initialization code>

// assign L0 to B, and L1 to A

CVA cmplt.ct=1 @L0, @L1;

```

10

このCVA命令では、 $L_0$ ストリームおよび $L_1$ ストリームの両方がイネーブルされるが、Sストリームはディスエーブルされる。具体的に言うと、 $L_0$ ストリームは、ベクトルBに割り当てられ、 $L_1$ ストリームは、ベクトルAに割り当てられる。副算術は、指定されない（すなわち、「ノーオペレーション」である）。命令は、 $E_T = 1$ および $C_T = 1$ を有する。CVA命令の構文「.ct=x」によって、 $E_T = 1$ であることがアセンブラーに指示される。

## 【0084】

主算術「cmplt」またはcompare-less-thanは、 $L_0$ ストリームと $L_1$ ストリームの先頭を継続的に比較する。実際には、ベクトルAとベクトルBを要素単位で比較している。ある*i*について $B[i] < A[i]$ である場合に、条件コードに1がセットされ、CVA実行が終了する。そのような要素対が見つからない場合には、2つのソース・ベクトルを使い果たすまで実行が継続する。

20

## 【0085】

早期終了をイネーブルされた( $E_T = 1$ )CVA実行を実行するために、主算術 $p\_o_p$ (図4の機能ユニットP34で実行される)は、条件コードを変更し得る算術関数である。ベクトル実行の過程中に、条件コードに事前に指定された値(C<sub>T</sub>ビットによって与えられる)がセットされる場合に、ベクトル実行は、即座に終了する。この終了は、ベクトルの全長が処理される前すなわち、CR51が0になる前であっても、発生し得る。この実施形態では条件コードが単一のビットであるが、代替実施形態で、条件コードを表す複数のビットおよび/またはエンコーディングを使用し得ることに留意されたい。

30

## 【0086】

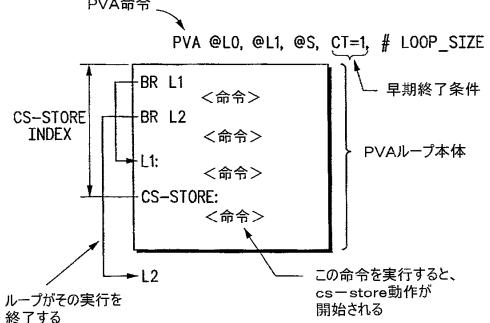

PVA命令は、伝統的なDSPプロセッサでのDO UNTIL命令またはDO WHILE命令によく似ている。そのDSP対応物と同様に、PVA命令を使用して構成されるプログラム・ループは、PVA命令と、それに続く複数のスカラ命令から構成されるループ本体からなる。

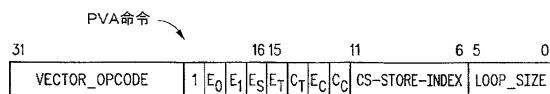

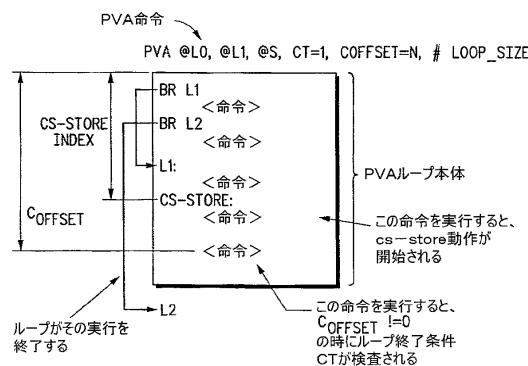

## 【0087】

図8に、PVA命令のフォーマットを示す。図9に、PVA命令を使用して構成されるプログラム・ループの構造を示す。PVAモードで実行する時に、実行コア4は、PVA命令が、任意選択として、2つまでの入力データ・ストリーム $L_0$ および $L_1$ ならびに出力データ・ストリームSをイネーブルして、PVAループ実行中に自動的に実行され得ることを除いて、单一発行パイプライン式計算機のように振る舞う。これらのデータ・ストリームは、一定ストライドのメモリ・ロード/ストア動作である。PVA実行について、 $L_0$ 、 $L_1$ 、およびSのいずれかまたはすべてをディスエーブルし得る。

40

## 【0088】

CVA実行に似て、入力ストリーム $L_0$ および $L_1$ は、それぞれ、ロード・ユニット $L_0$ 6および $L_1$ 8を介して、メモリM0 14およびM1 16からRF26および/またはP34にデータをストリーム・インする。しかし、PVA実行では、ストリーム $L_0$ およびストリーム $L_1$ を介してプリフェッチされるデータは、それRF26のレジスターR0およびR1に書き込まれる。これらのデータを、P34に直接にフィードフォワー

50

ドすることも可能である。PVA 実行では、マルチブレクサ 32、ラッチ 38、およびマルチブレクサ 41 は、使用されない。

#### 【0089】

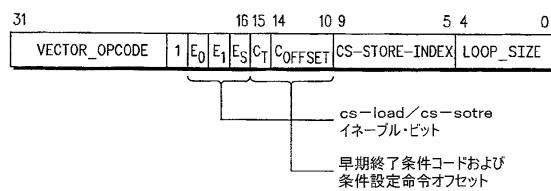

図 8 を参照すると、PVA 命令に、 $E_0$ 、 $E_1$ 、および $E_S$  を有するイネーブル・フィールドが含まれ、これらは、それぞれデータ・ストリーム  $L_0$ 、 $L_1$ 、および S のイネーブル・ビットである。PVA 命令は、 $E_T$  ビットおよび $C_T$  ビットを有する早期終了フィールドも有する。CVA 命令の  $E_T$  ビットに似て、 $E_T$  ビットは、PVA 実行の早期終了機能をイネーブルまたはディスエーブルする。 $C_T$  は、この機能がイネーブルされる ( $E_T = 1$ ) 場合に、これが行われる条件コードを指定する。

#### 【0090】

PVA 命令の  $\text{loop\_size}$  フィールドは、スカラ命令の個数単位で、ループ本体のサイズを指定する。PVA 命令の  $\text{cs-store-index}$  フィールドは、ループ本体の中で、実行される時に定数ストライド・ストア ( $\text{cs-store}$ ) 動作を自動的に開始する命令を指定する。この  $\text{cs-store}$  動作のデータは、この命令によって書き戻されるデータである。1 実施形態で、PVA ループの最初の命令のインデックス値が、1 であり、2 番目の命令のインデックス値が、2 であり、以下同様である。PVA ループ内の最後の命令のインデックス値は、 $\text{loop_size}$  である。この実施形態のインデックス値は、PVA 命令に関する命令位置である。他の命令インデクシング方式も可能である。

#### 【0091】

PVA プログラム・ループでは、条件分岐および無条件分岐が、ループ本体内で許容される。ループ本体の中で分岐が採用され、分岐のターゲットがまだループ本体の中にある場合に、PVA 実行が継続される。ループ本体の中で分岐が採用され、分岐のターゲットがループ本体の外にある場合に、PVA 実行が自動的に終了する。

#### 【0092】

図 11 で CIR50 の下位半分として示された CR51 も、PVA 実行に使用される。具体的に言うと、これは、実行されるループ反復の回数を指定するのに使用される。その CVA 対応物に似て、CR51 は、その実行の前に、適当な反復カウントを用いてソフトウェアによって初期化されることを必要とする。PVA 実行中に、CR51 は、実行される反復ごとに 1 つだけ自動的に減分される。CR51 が 0 に達した時に、PVA 実行が終了する。計算機は、命令ストリームで次のベクトル命令に出会うまで、スカラ・モードに入る。

#### 【0093】

PVA 実行は、3 つの機構すなわち (i) CR51 が 0 に達する時、(ii) PVA 命令の  $E_T$  ビットおよび  $C_T$  ビットが早期終了条件を示す時、または (iii) 分岐がループ本体内で採用され、分岐のターゲットがループの外にある時の 1 つを介して終了し得る。3 つの終了条件のすべてが、単一のプログラム・ループ内に共存し得る。すなわち、ループは、実行時条件に基づいて、上の 3 つの終了機構の 1 つを介して終了し得る。終了機構 (ii) および (iii) を、集合的に、PVA 実行の早期終了と称する。

#### 【0094】

例 3 に示されたプログラム・ループは、上で説明した早期終了機能 (ii) を使用して、PVA 構成を使用してベクトル化し得る。

#### 【0095】

10

20

30

40

## 【数8】

```

<Some initialization code>

// assign L0 to B, and L1 to A

PVA    @L0, @L1, ct=1, #1;          // PVA instruction

cmplt R0, R1;                      // loop body with one instruction

```

記号「@L0」および「@L1」は、両方ともPVA命令で指定される。これによって、アセンブラに、 $L_0$ ストリームと $L_1$ ストリームの両方がイネーブルされることが示される。 $S$ ストリームは、ループ本体に「cs-store」ラベルが現れないで、ディスエーブルされる。この命令では、 $E_T = 1$ かつ $C_T = 1$ である。 $E_T = 1$ をセットすることによって、上で説明した早期終了機能(iii)がイネーブルされる。PVA命令の構文「ct=x」によって、アセンブラに、 $E_T = 1$ であることが指示される。

## 【0096】

PVAプログラム・ループのサイズは、PVA命令の「#1」表記によって指定されるように、1命令である。このループには、単一のスカラ命令「cmplt」が含まれ、この命令は、レジスタR0およびR1から継続的に読み取り、この2つの値を比較する。

## 【0097】

PVA実行について、ループ本体内でR0(またはR1)から読み取ることによって、データ項目が $L_0$ (または $L_1$ )入力ストリームから自動的にデキューされる。 $L_0$ (または $L_1$ )からのデータ項目のデキューによって、デキュー動作によって残された空のスロットを埋めるために、定数ストライド・ロード(cs-load)動作が自動的に実行される。したがって、ループ本体でレジスタR0(またはR1)から継続的に読み取ることによって、M0 14(またはM1 16)からのデータの連続的ストリームのフェッチおよびレジスタR0(またはR1)へのロードがトリガされる。R0(またはR1)は、単一のループ反復で複数回読み取り得る。

## 【0098】

PVA実行について、 $L_0$ (または $L_1$ )ストリームがイネーブルされる時に、R0(またはR1)が、読取専用レジスタになり、このレジスタへの書き込みは、ハードウェアによって無視される。

## 【0099】

実質的に、上のループ本体の「cmplt」命令は、ベクトルAおよびBを要素単位で比較する。この例では、R0の内容がR1の内容より小さい(すなわち $B[i] < A[i]$ である)場合に、条件コードに1がセットされ、事前に指定された値 $C_T = 1$ と等しくなり、PVAループ実行が即座に終了する( $E_T = 1$ なので)。この終了は、CR51が0に達する前であっても発生し得る。

## 【0100】

代替案では、例3に示されたプログラム・ループを、下のようにPVA構成を使用してベクトル化することも可能である。この例では、前に説明した早期終了機構(iii)を使用して、どのようにしてPVAループを終了し得るかを示す。

## 【0101】

10

20

30

40

## 【数9】

```

<Some initialization code>

// assign L0 to B, and L1 to A

PVA    @L0, @L1, #2;      // PVA instruction

cmplt R0, R1;           // part of PVA loop

bt EXIT                 // part of PVA loop

EXIT

```

10

この代替案では、PVA命令で $E_T = 0$ である。ループ本体には、2つの命令「cmp」および「bt」がある。第1の命令が、ベクトルAとBの間の比較動作の結果として条件コードをセットする場合に、第2の命令（「bt EXIT」）が採用される。この分岐のターゲットは、ループ本体の外にあるので、PVA実行が即座に終了する。そうではなく、条件コードがセットされず、分岐命令「bt」が採用されない場合に、実行は、次の反復の第1命令（この場合では「cmp」命令）から継続される。

## 【0102】

前に示したPVAベクトル化されたループの第1版（終了機構（ii）を使用する）は、上で示したPVAベクトル化されたループの第2版（終了機構（iii）を使用する）より効率的である。前者は、ループ本体の中に1つのスカラ命令だけを有するが、後者は、ループ本体の中に2つのスカラ命令を有する。

20

## 【0103】

「exit-by-conditional-branch（条件分岐による終了）」手法が、通常、条件コードも使用するループ本体内で条件実行と共にプログラム・ループによって使用される。

## 【0104】

例3に示された元のプログラム・ループでは、反復ごとに8つの命令が、ループ実行中に実行コアによって要求される。PVA構成を使用してループをベクトル化した後には、反復ごとに2つから3つの命令だけが、ループ実行中に実行コアによって要求される。

30

## 【0105】

代替案では、早期終了をもたらすために、PVA命令によって、図23に示されているように、ループを早期に終了し得る条件設定命令のオフセットを指定し得る。図23のPVA命令を使用して構成されるプログラム・ループの構造を、図24に示す。図23では、非0のCoffsetフィールドによって、早期終了機能がイネーブルされることが示される（図8のフォーマットで $E_T = 1$ をセットすることに似る）。このフィールドによって、条件設定命令のオフセット（PVA命令からの命令数単位）が指定される。条件コード（またはcビット）に、条件設定命令の実行の結果として、PVA命令のCTフィールドによって指定される値がセットされた時に、PVA実行が即座に終了する。下に例を示す。

40

## 【0106】

## 【数10】

Some initialization code // assign A[i] to L0; assign B[i] to L1.

PVA @L0, @L1, #5, CT=1, C\_offset=4

cmplt R0, R1 //part of loop body

bt SKIP //part of loop body

sub R3, R4 //part of loop body

SKIP

cmpnei R3, #2 //part of loop body, check R3

add R5, R3 //part of loop body

EXIT

この代替案では、PVA命令のC\_offset = 4である。ループ本体には5つの命令（「cmplt」、「bt」、「sub」、「cmpnei」、および「add」）がある。cmplt命令は、R0およびR1の値を比較し、条件コード（またはcビット）をセットする。「bt」命令は、結果のcビットの値を検査し、セットされている場合に、「sub」命令を迂回して分岐する。ループの4番目の命令は、比較命令であり、これは、減算命令の結果（レジスタR3内）を比較して、それが値「2」と等しくないかどうかを調べる。比較の結果が真である場合には、cビットに「1」がセットされ、PVA命令のCTフィールドにも「1」がセットされているので、PVA実行は即座に終了する。そうでない場合には、実行は、次の命令「add」から継続される。add命令に続いて、実行は、次のループ反復（「cmplt」）で継続される。PVA命令のC\_offsetフィールドによって、ループ終了の制御に「cmpnei」命令（PVA命令に関してループ内で4のオフセット）が使用されることと、ループ終了に影響せずに、ループ内の他の命令（この場合には「cmplt」命令）によってcビットが影響を受ける可能性があることが示されることに留意されたい。この機能は、ループ終了に影響せずにループ内で複数の条件をテストしなければならない時に有用である。

## 【0107】

以下の例を使用して、Sストリームを介してcs-store動作をPVA実行についてどのように実行し得るかを示す。

## 【実施例4】

## 【0108】

10

20

30

【数 1 1】

```

mov      R4,4

mov      R8,8

mov      R6,16

```

L1:

```

ld.w    R7,(R3)    // load A[i]          10

addi   R3,4

mov    R2, R8

cmplt R6,R7    // is A[i] > 16?

movt   R2, R4    // conditional move:

// R2 = (A[i]>16)? R4 : R8;

st.w    R2,(R10)   // store result to C[i]

addi   R10, 4

dec.ne R5        // decrement loop index R5

// set c bit if R5 not equals zero

bt     L1        // branch to L1 if c bit is set      20

```

上のループの高水準ソース・コードを下に示す。

【0 1 0 9】

【数 1 2】

```

for (i=0; i<n; i++) {

if (A[i] > 16) C[i] = 4; else C[i] = 8;

}

```

このループは、PVA構成を使用して、下記のようにベクトル化し得る。

【0 1 1 0】

## 【数13】

```

<Some initialization code>

// assign L0 to vector A; assign S to vector C.

mov      R4, 4

mov      R8, 8

mov      R6, 16

PVA     @L0, @S, #3;      // PVA instruction          10

mov      R2, R8

cmplt   R6, R0      // is A[i] > 16?

cs-store:

movt    R2, R4      // conditional move:

// R2 = (A[i]>16)? R4:R8;

// cs-store performed here

```

20

このループでは、 $L_0$ ストリームおよび $S$ ストリームがイネーブルされるが、 $L_1$ ストリームはイネーブルされない。PVAループ・サイズは、3命令である。各反復で、「cmp1t」命令は、R0（または要素 $A[i]$ ）を読み取り、R6にストアされた定数値16と比較する。「movt」命令は、cビット（または条件コード）がセットされている場合に、R4をR2へ条件付きで移動する。そうでない場合に、「movt」命令は、R2をR2に移動し、値は変化しない。

## 【0111】

「movt」命令は、ループ本体の中の「cs-store」ラベルに配置されている。Sストリームを介するcs-store動作は、この「movt」命令が実行される時に、必ず自動的に開始される。このcs-store動作に使用されるデータは、「movt」命令によって書き戻されるものと同一のデータである。このPVAループを実行する時に、「movt」命令によって作られる結果が、P34によってp\_busに駆動され、マルチブレクサ40およびresul\_t\_busを介してRF26に常に書き戻される。S36は、p\_busでこの結果を取り込み、これらの取り込まれたデータを使用してメモリ・システムへのcs-store動作を実行する。 30

## 【0112】

この例では、「movt」命令に関連するストア動作が、アセンブリ・コードで、ループ本体の中のプログラム・ラベル「cs-store」を使用して指定される。しかし、機械コード（またはアセンブルされたバイナリ・コード）では、そのようなストア動作は、「movt」命令にエンコードされない。そうではなく、ストア動作は、ループを構成するのに使用されるPVA命令で暗黙のうちに指定される。この場合には、PVA命令が、 $E_S = 1$ にされ、その「cs-store-index」フィールドが、「movt」命令をポイントしている。このタイプのストア動作を、「暗黙ストア」動作と称する。このストア動作をトリガし得るループ本体内の命令（この例では「movt」）を、暗黙ストア命令と称する。 40

## 【0113】

上の実施形態では、PVA命令内に「cs-store-index」フィールドが1つだけあり、したがって、1つの「cs-store」ラベルだけが、ループ本体の中で許容される。その結果、1つの暗黙ストア動作だけが、各反復で許容される。代替実施形態では、複数の暗黙ストア動作を、特殊なマスク・レジスタを使用することによって実行 50

し得る。そのような代替実施形態では、マスク・レジスタを 16 ビット・レジスタとすることが可能であり、このレジスタの各ビットは、ループ本体内のスカラ命令に対応する。このレジスタの各ビットによって、命令内の対応するスカラ命令に関する `cs-store` 動作がイネーブルまたはディスエーブルされる。したがって、ループ本体の 16 個までの命令によって、各反復で `cs-store` 動作を開始し得る。ソフトウェアは、PVA 実行の前にこのマスク・レジスタを初期化する。PVA 実行中に、命令が結果を書き戻し、それに対応するマスク・レジスタ内のビットをセットする時に、その命令によって書き戻されたデータを使用して、`cs-store` 動作が開始される。16 個の `cs-store` データ・アドレス、ストライド、およびオペランド・サイズを指定するために、ハードウェア・サポートが必要である。

10

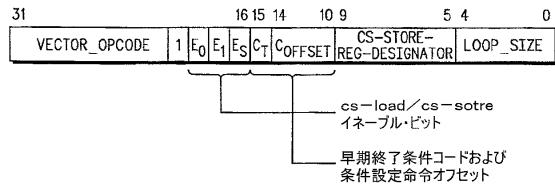

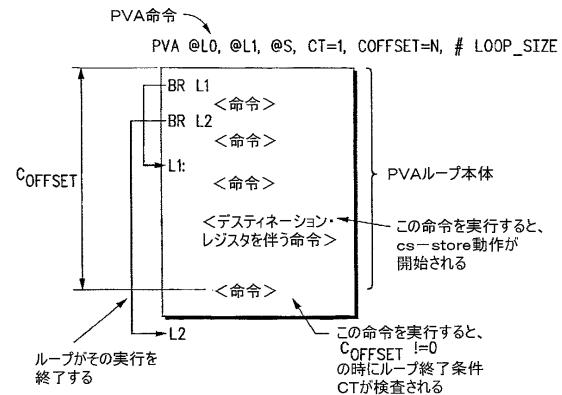

#### 【0114】

暗黙ストア動作を使用するもう 1 つの実施形態では、`cs-store-index` ではなく、`cs-store-reg-designator` (`cs-store` レジスタ指定子) フィールド (レジスタ・フィールドとも称する) を PVA 命令で指定し得る。たとえば、図 25 に、`cs-store-reg-designator` フィールドを有する PVA 命令の 1 実施形態を示し、図 26 に、図 25 の PVA 命令フォーマットを使用して構成されるプログラム・ループを示す。この `cs-store-reg-designator` フィールドによって、ループ本体の内部の命令のデスティネーション・レジスタの関数としての暗黙ストア動作が定義される。たとえば、`cs-store-reg-designator` フィールドによってレジスタ 3 が示される場合に、デスティネーションとしてレジスタ 3 を有するすべての命令が、暗黙ストアを呼び出す。例の命令が、「`add R3, R5`」であり、これは、「命令デスティネーション、ソース」というフォーマットを有する。この `add` 命令では、レジスタ 3 がデスティネーション・レジスタとして使用され、したがって、この `add` 命令は、暗黙ストア動作に対応する。ループ本体の中の複数の命令が、デスティネーション・レジスタとしてレジスタ 3 を使用する場合には、複数の命令が、暗黙ストア動作を開始し得る。しかし、「`cmpnei R3, #2`」などの命令は、この例では R3 がデスティネーション・レジスタとして使用されないので、暗黙ストア動作に対応し得ない。「`cmpnei`」命令 (ならびに他の命令) は、デスティネーション・レジスタに書き込まれる結果値を生成せず、このフォーマットは、この例ではソース値の対を指定している。さらに、代替実施形態では、PVA 命令で複数のレジスタを定義することを可能にして、より多くの暗黙ストアを可能にし得る。

20

#### 【0115】

もう 1 つの実施形態で、PVA 命令に、継続機能を組み込むことも可能である。この機能を有する PVA 命令のフォーマットを、図 20 に示す。この PVA 命令には、早期継続フィールド内の 2 つの追加ビットすなわち  $E_c$  ビットおよび  $C_c$  ビットがある。 $E_c$  ビットによって、早期継続機能がイネーブルまたはディスエーブルされ、 $C_c$  ビットによって、この機能がイネーブルされる場合に、この早期継続が行われる条件コードの値が指定される。

30

#### 【0116】

次の高水準コードに、プログラム・ループの残りの実行をスキップするのにこの早期継続機能をどのように使用し得るかを示す。

40

#### 【0117】

#### 【数 1 4】

```

for (i=0; i<n; i++) {

if (A[i] < s) continue;

<more code>

}

```

50

この例では、ベクトル A の要素が、スカラ s と比較される。ある i について A [ i ] < s である場合に、上で「<さらなるコード>」と示されたプログラム・ループの残りの部分が、スキップされ、実行は、次の反復の先頭から継続される。これは、事前に指定された条件が満たされる時にループの実行が即座に終了する、前に説明した「早期終了機能」と対照的である。

## 【0118】

このループを、次のようにベクトル化し得る。

## 【0119】

## 【数15】

```

<Some initialization code> 10

// assign L0 to A; initialize R1 with scalar s.

PVA    @L0, cc=1, #Loop_size; // PVA instruction

cmplt R0, R1;                // A[i] < s?

<more code>                  // The rest of the loop body

```

この PVA 命令では、 $E_c = 1$  かつ  $C_c = 1$  である。PVA 命令の構文「 $c c = x$ 」によって、 $E_c = 1$  であることがアセンブラーに指示される。「cmplt」命令によって条件コードに 1 がセットされる時に、必ず、その  $A [ i ]$  と  $s$  の間の比較動作の結果として、実行が、即座に次の反復から継続され、「<さらなるコード>」の実行がスキップされる。

## 【0120】

早期終了機能および早期継続機能の両方がイネーブルされた ( $E_T = E_c = 1$ ) PVA 命令では、ループ本体内の命令が、条件コードを変更することが可能であり、これによって、現在の反復の実行が終わる。条件コードに、 $C_T$  ビットによって指定される値がセットされている場合には、ループ実行が、完全に終了する。条件コードに、 $C_c$  ビットによって指定される値がセットされている場合には、ループ実行は、次の反復から継続される。条件コードに、 $C_T$  ビットおよび  $C_c$  ビットの両方によって指定される値がセットされている（両方が条件コードについて同一の値を指定する）場合には、ループ実行が終了する。すなわち、この実施形態では、早期終了機能が、早期継続機能の地位を奪う。他の実施形態では、早期継続機能が、早期終了機能の地位を奪う。図示されていないが、早期継続機能を、早期終了について図 23 に示したものに似た形で設けることも可能である。 $C_{offset\_c}$  フィールドおよび  $C_c$  ビットを命令フォーマットに加えることが可能であり、あるいは、 $C_{offset}$  指定子および  $C_T$  指定子と置換し得る。 $C_{offset\_c}$  フィールドおよび  $C_c$  ビットによって、条件設定命令の PVA 命令からの命令単位のオフセットと、指定された命令が PVA 命令でセットされた  $C_c$  ビットと一致する条件コードを生成する時にループの早期継続をもたらすのに使用される条件値を指定し得る。 30 40

## 【0121】

PVA 構成は、一般に、(i) ループ制御機構、(ii) cs-load を介する入力データ・ストリーム化、および(iii) cs-store を介する出力データ・ストリーム化に関連するある種の実行オーバーヘッドを除去し得る。PVA 命令に、システムの必要に応じて、上で説明した諸フィールドの組合せを、適当に含めることも可能である。たとえば、代替実施形態で、暗黙ストア動作を実行する、上で説明したものと異なるフィールドおよび方法を使用し得る。

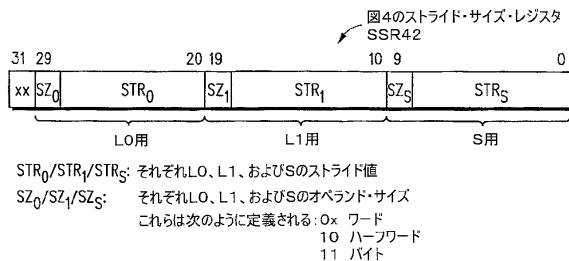

## 【0122】

図 10 に、データ・ストリーム  $L_0$ 、 $L_1$ 、および  $S$  のストライド値およびオペランド

10

20

30

40

50

・サイズを指定する S S R 4 2 の 1 実施形態を示す。このレジスタは、 C V A 実行と P V A 実行の両方に使用される。この実施形態では、レジスタが、 3 つのデータ・ストリーム  $L_0$  、  $L_1$  、および  $S$  のそれぞれに 1 つの 3 つの部分に区分される。ストライド・フィールド  $S T R_0$  、  $S T R_1$  、および  $S T R_S$  は、 9 ビット幅である。サイズ・フィールド  $S Z_0$  、  $S Z_1$  、および  $S Z_S$  は、 2 ビット幅であり、それぞれによってバイト、ハーフワード、またはフルワードが指定される。

#### 【 0 1 2 3 】

2 つのベクトルの内積、 $\sum_i (A[i] * B[i])$  を実施する下記の例を検討されたい。この動作は、 C V A 命令を使用して下記のように実行し得る。この例では、 S S R [  $S T R_0$  ] が、 S S R レジスタの  $S T R_0$  フィールドを表し、他も同様である。

10

#### 【 0 1 2 4 】

C R をベクトル長に初期化する。

S S R [  $S T R_0$  ] をベクトル A のストライド値に初期化する。

S S R [  $S T R_1$  ] をベクトル B のストライド値に初期化する。

#### 【 0 1 2 5 】

R 0 をベクトル A の開始アドレスに初期化する。

R 1 をベクトル B の開始アドレスに初期化する。

C V A m u l @ L 0 、 @ L 1 、 a d d ;

この例では、  $L_0$  および  $L_1$  がイネーブルされ、  $S$  がディスエーブルされ、したがって、これはリダクション C V A である。このリダクション演算の主算術は、「 m u l 」関数であり、副算術は、「 a d d 」関数である。 C V A 実行中に、部分的結果が、継続的にレジスタ R 3 に書き戻される。ベクトル計算が完了した時に、最終結果すなわち内積が、 R 3 に暗黙ストアされる。この例の C V A は、  $V_{x1} / V_{x0} = 01$  、  $V_{y1} / V_{y0} = 10$  、  $V_{z1} = V_{z0} = 11$  、  $E_S = 0$  、  $E_T = 0$  、  $C_T =$  「ドント・ケア」という設定を有する。

20

#### 【 0 1 2 6 】

この例では、ベクトル実行が割り込まれる場合に、レジスタ R 3 に、内積計算の中間の部分的結果が含まれる。割込みからリターンする時に、計算が、中断されたところから継続され、最初の部分的結果としてレジスタ R 3 の内容が使用される。

#### 【 0 1 2 7 】

もう 1 つの例で、すべての i に関するベクトル算術  $C[i] = s A[i]$  を実施する。

C R をベクトル長に初期化する。

S S R [  $S T R_0$  ] をベクトル A のストライド値に初期化する。

#### 【 0 1 2 8 】

S S R [  $S T R_S$  ] をベクトル C のストライド値に初期化する。

R 0 をベクトル A の開始アドレスに初期化する。

R 2 をベクトル C の開始アドレスに初期化する。

#### 【 0 1 2 9 】

R 5 を s に初期化する。

C V A m u l @ L 0 、 R 5 、 @ S ;

40

これはコンパウンド C V A である。第 2 算術は「ノー・オペレーション」である。この場合に、  $L_0$  ストリームおよび  $S$  ストリームは、イネーブルされるが、  $L_1$  ストリームはイネーブルされない。ベクトル実行の前に、 R 5 が、スカラ定数 s によって初期化される。この例の C V A 命令は、  $V_{x1} / V_{x0} = 01$  、  $V_{y1} / V_{y0} = 00$  、  $V_{z0} / V_{z1} = 00$  、  $E_S = 1$  、  $E_T = 0$  、  $C_T =$  「ドント・ケア」という設定を有する。

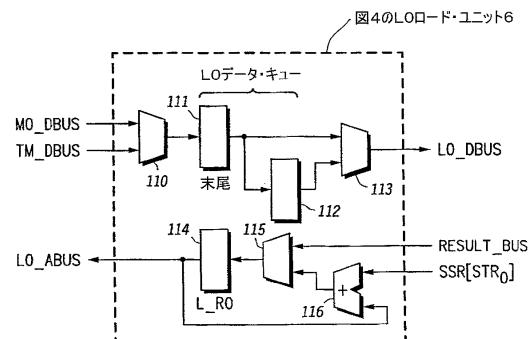

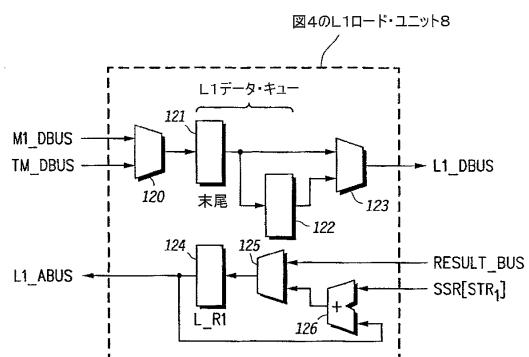

#### 【 0 1 3 0 】

図 1 2 から 1 4 に、  $L_0 6$  、  $L_1 8$  、および  $S 3 6$  の 1 つの可能な実施形態を示す。  $L_0 6$  、  $L_1 8$  、および  $S 3 6$  のそれぞれが、それぞれレジスタ R 0 、 R 1 、および R 2 のローカル・コピーを有する。このローカル・コピーを、  $L\_R 0 114$  、  $L\_R 1 124$  、および  $L\_R 2 136$  と表す。

50

**【0131】**

スカラ実行中に、 $L_0\ 6$ （または $L_1\ 8$ ）ユニットは、レジスタ $R_0$ （または $R_1$ ）への書き戻しアクティビティについて $resul t\_bus$ を常時スヌープし、レジスタのローカル・コピー $L\_R_0\ 114$ （または $L\_R_1\ 124$ ）を更新する。同様に、 $S_36$ は、レジスタ $R_2$ への書き戻しアクティビティについて $p\_bus$ を常時スヌープし、レジスタのローカル・コピー $L\_R_2\ 136$ を更新する（図14参照）。

**【0132】**

$CVA$ 実行中または $PVA$ 実行中に、これらのローカル・レジスタの内容が、メモリ・ロックのロード・アドレスまたはストア・アドレスとして適当に使用される。これらのレジスタは、対応するデータ・ストリームがイネーブルされている時に、適当なストライド値を加算することによって、ハードウェアによって常時更新される。すなわち、 $L\_R_0\ 114$ 、 $L\_R_1\ 124$ 、および $L\_R_2\ 136$ は、それぞれ、実行される $cs\_load$ 動作または $cs\_store$ 動作のそれぞれについて、 $SSR[STR_0]$ 、 $SSR[STR_1]$ 、および $SSR[STR_s]$ によって指定される量と合計される。

**【0133】**

ベクトル命令（ $CVA$ 命令または $PVA$ 命令）が、その $E_0$ （または $E_1$ ）ビットをセットされて最初にデコードされる時に、第1ロード・アドレスとして $L\_R_0\ 114$ （または $L\_R_1\ 124$ ）を使用して、 $cs\_load$ が即座に開始される。その後、メモリからプリフェッчされるデータごとに、 $L\_R_0\ 114$ （または $L\_R_1\ 124$ ）が更新される。

**【0134】**

図12および13に示された実施形態では、ロード・ユニット $L_0\ 6$ および $L_1\ 8$ 内のデータ・キューが、2つだけの深さである。 $L_0\ 6$ への入力に、 $M0\_dbus$ および $TM\_dbus$ が含まれる。この2つの入力が、マルチプレクサ110に供給される。マルチプレクサ110の出力は、データ・キューの末尾111に供給される。データ・キューの末尾111は、マルチプレクサ113およびデータ・キューの第2エントリ112にデータを供給する。この第2エントリ112も、マルチプレクサ113にデータを供給する。データは、マルチプレクサ113から $L0\_dbus$ に供給される。

**【0135】**

ロード・ユニット $L_0\ 6$ 内で、 $M0\_dbus$ および $TM\_dbus$ からのデータを、マルチプレクサ110を介し、末尾エントリ111およびマルチプレクサ113を介し、第2データエントリ112をバイパスして、 $L0\_dbus$ に供給し得る。データを、第2エントリ112からマルチプレクサ113を介して $L0\_dbus$ に供給することも可能である。

**【0136】**

図12を継続すると、加算器116が、 $SSR42$ 、 $SSR[STR_0]$ 、およびロード・アドレスを $L\_R_0\ 114$ から受け取る。加算器116の出力は、マルチプレクサ115に結合される。 $resul t\_bus$ も、マルチプレクサ115に結合される。マルチプレクサ115の出力は、 $L\_R_0\ 114$ に結合され、 $L\_R_0\ 114$ は、 $L0\_abus$ に結合される。ベクトル実行中に、 $SSR[STR_0]$ によって指定される量が、ストリーム $L_0$ を介して実行される $cs\_load$ 動作ごとに、 $L\_R_0\ 114$ に加算される。マルチプレクサ115および $L\_R_0\ 114$ を用いると、ロード・ユニット $L_0\ 6$ が、レジスタ $R_0$ へのすべての書き戻しについて $resul t\_bus$ をスヌープし得るようになる。スカラ実行中には、 $L\_R_0\ 114$ が、 $RF26$ のレジスタ0と同一の値に維持される。同様の動作および接続性が、図13に示されたロード・ユニット $L_1\ 8$ にもあてはまる。

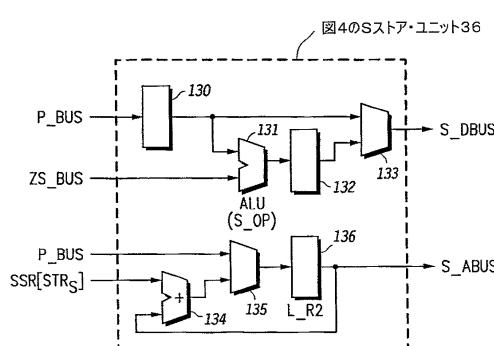

**【0137】**

図14を参照すると、ストア・ユニット $S_36$ 内で、 $p\_bus$ によって、データがラッチ130に供給される。このラッチおよび $zs\_bus$ の出力によって、 $ALU131$ にデータが供給される。 $ALU131$ は、ラッチ132にデータを供給し、ラッチ132

10

20

30

40

50

は、マルチプレクサ 133 にデータを供給する。マルチプレクサ 133 は、ラッチ 130 およびラッチ 132 からデータをとり、 $s\_d\ b\ u\ s$  にデータを供給する。

#### 【0138】

データを、 $p\_b\ u\ s$  から、ラッチ 130 およびマルチプレクサ 133 を介して  $s\_d\ b\ u\ s$  に供給することも可能である。このバスによって、ストア・ユニット S36 内の ALU131 の計算がバイパスされる。データを、ALU131 の出力からラッチ 132 およびマルチプレクサ 133 を介して  $s\_d\ b\ u\ s$  に供給することも可能である。このバスでは、ALU131 の結果が、受け取られ、 $s\_d\ b\ u\ s$  に渡される。

#### 【0139】

ベクトル算術では、メモリから定数ストライド・ロードを介してロードされるほとんどのデータが、単一の反復で消費され、絶対に再利用されないという意味で、一時的でしかない。ベクトル算術への割込みが許容される場合に、ベクトル実行に関連するすべての定数ストライド・ロード / ストア・アドレスを保存して、割込みからのリターンの後にロード / ストア動作を再開し得るようにする必要がある。

#### 【0140】

メモリからプリフェッчされるすべての一時的なものならびにロード / ストア・アドレスを、汎用レジスタ・ファイルまたは制御レジスタなどのアーキテクチャ的に可視の記憶空間を使用してストアすることは、これらの貴重なリソースの非効率的な使用になる可能性がある。本発明は、レジスタ・オーバーレイを使用して、この問題に対処する。この手法では、PVA 実行モードに入る時に、アーキテクチャ的に可視のレジスタ・ファイルの一部が、レジスタの新しい組によって「オーバーレイ」される。レジスタは、オーバーレイされる時に、(i) オーバーレイされたインスタンスおよび(ii) 一時的インスタンスという 2 つのインスタンスを有する。PVA モードでは、その一時的インスタンスだけが、プログラマに可視であり、オーバーレイされたインスタンスは不可視である。逆に、実行が、PVA モードを出てスカラ・モードに入る時に、オーバーレイされたインスタンスが、再び可視になり、一時的インスタンスは、存在しなくなる。

#### 【0141】

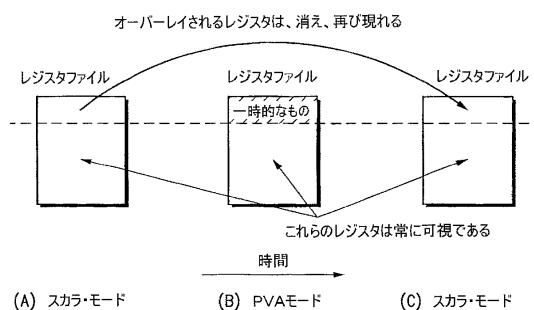

図 15 に、3 つの実行モードすなわちスカラ、PVA、およびスカラのシーケンスにまたがる、オーバーレイされたレジスタの可視性を示す。1 実施形態で、レジスタ R0 および R1 が、PVA 実行中にオーバーレイされ得るレジスタの組として指定される。これを、下の表 2 に示す。これらのレジスタのオーバーレイされたインスタンスは、対応する  $c\ s - l\ o\ a\ d$  ロード・アドレスをストアするのに使用される。これらのレジスタの一時的インスタンスは、 $c\ s - l\ o\ a\ d\ L_0$  および  $L_1$  を介してメモリからプリフェッчされるデータをストアするのに使用される。

#### 【0142】

##### 【表 2】

表 2. レジスタの割振りとアクセス可能性

| レジスタ | オーバーレイされるインスタンス<br>(スカラ・モードでのみ可視) | 一時的インスタンス (PVA モードでのみ可視) |      |

|------|-----------------------------------|--------------------------|------|

|      |                                   | 内容                       | 動作   |

| R0   | $L_0$ のロード・アドレス                   | $L_0$ のプリフェッчされたデータ      | 読み専用 |

| R1   | $L_1$ のロード・アドレス                   | $L_1$ のプリフェッчされたデータ      | 読み専用 |

R0 および R1 の一時的インスタンスを、それぞれ  $T\_R0$  および  $T\_R1$  と表す。R0 および R1 のオーバーレイされるインスタンスを、それぞれ  $O\_R0$  および  $O\_R1$  と表す。

#### 【0143】

$T\_R0$  および  $T\_R1$  は、読み専用レジスタである。ループ本体内でのこの一時レジ

10

20

30

40

50

スタへの書込は、ハードウェアによって無視される。これらの一時レジスタは、PVA実行中に限って定義される。PVAループが、その実行を終了する時に、これらの一時レジスタに含まれるデータは、失われる。その時点でのそのようなレジスタへのアクセスによって、レジスタのオーバーレイされたインスタンスが検索され、これは、最後に実行されたcs-1oad動作のロード・アドレスである。

#### 【0144】

また、PVA実行が割り込まれる時に、TR0およびTR1は、コンテキストの一部として保存されない。割込みからリターンする時に、データをTR0およびTR1にプリフェッチしたcs-1oad動作が、OR0およびOR1にストアされたロード・アドレスを使用して再初期化される。レジスタTR0およびTR1は、普通のPVA実行を再開し得るようになる前に再初期化される。

10

#### 【0145】

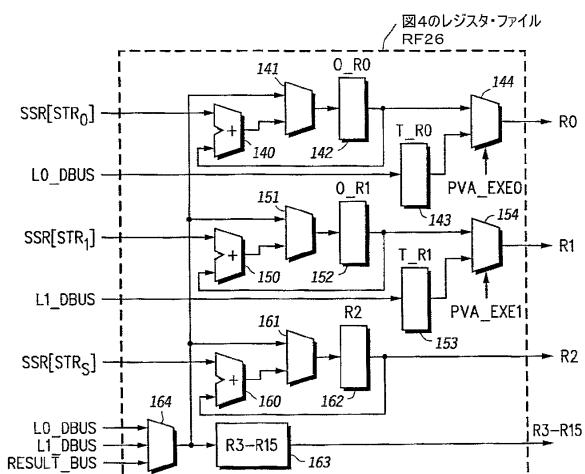

図16に、図4のレジスタ・ファイルRFの1実施形態を示す。RF26には、他のレジスタの中でも、OR0 142、TR0 143、OR1 152、およびTR1 153が含まれる。RF26内では、レジスタOR0 142、OR1 152、およびR2 162が、それぞれ加算器140、150、および160を使用して更新される。

#### 【0146】

レジスタOR0 142の値が、マルチプレクサ144に供給される。この値は、加算器140の入力にもフィードバックされる。加算器140のもう1つの入力は、SSR[STR<sub>0</sub>]に結合される。加算器140の出力は、入力としてマルチプレクサ141に供給される。マルチプレクサ141の出力は、OR0 142の入力に結合される。マルチプレクサ164が、もう1つの入力としてマルチプレクサ141に供給される。TR0 143は、その入力をL0\_d busから取り、その出力をマルチプレクサ144のもう1つの入力に供給する。マルチプレクサ144の出力は、RF26の出力R0として供給される。加算器140、マルチプレクサ141、およびOR0 142を使用することによって、OR0 142を、各サイクルにSSR[STR<sub>0</sub>]によって指定される量だけ増分し得る。

20

#### 【0147】

同一の機構を使用して、各サイクルに、OR1 152およびR2 162を、それぞれストライド値SSR[STR<sub>1</sub>]およびSSR[STR<sub>s</sub>]を加算することによって、類似するハードウェア構成によって更新し得る。

30

#### 【0148】

PVA実行中に、OR0 142およびTR0 143の更新が、対応するcs-1oad動作がRF26にコミットされるのと同時に行われる。同様に、OR1 152およびTR1 153の更新は、対応するcs-1oad動作がRF26にコミットされるのと同時に行われる。R2 162の更新は、対応するcs-storeがメモリにコミットされるのと同時に行われる。任意の所与の時点で、TR0 143(またはTR1 153)に、メモリからプリフェッチされたデータが含まれ、アドレスは、OR0 142(またはOR1 152)にストアされる。この一貫性は、PVA実行中の命令境界にまたがって維持される。一時レジスタTR0 144およびTR1 154が、CVA実行またはスカラ実行に不要であることに留意されたい。

40

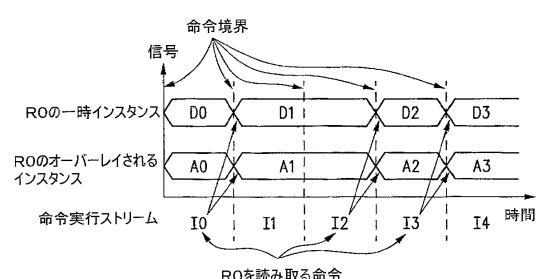

#### 【0149】

PVA実行中の一時インスタンスおよびオーバーレイされるインスタンスの一貫性を、図17に示す。5命令の実行シーケンスが示されている。水平軸は、時間を表し、レジスタR0の一時的インスタンスおよびオーバーレイされるインスタンスが、それぞれ垂直軸に表されている。命令境界は、垂直の破線によって示されている。この例では、ストリームL<sub>0</sub>を介してストリーミングされるデータが、D0、D1、D2、D3、...であり、A0、A1、A2、A3、...が、対応するロード・アドレスである。この5つの命令の中で、I0、I2、およびI3が、レジスタR0を読み取る命令である。R0からの

50

読み取りは、図 17 に示されているように、次の命令境界の先頭での新しい「アドレス - データ」対による O\_R0\_142 および T\_R0\_143 の同時更新を引き起こす。命令 I1 は、R0 を読み取らない命令であり、したがって、O\_R0\_142 および T\_R0\_143 は、次の命令境界で更新されない。レジスタ O\_R0\_142 および T\_R0\_143 は、レジスタ R0 の読み取りに続く次の命令境界で更新される。それまでは、このレジスタは最後に更新された値を維持する。レジスタ O\_R1\_152 および T\_R1\_153 は、類似する形でハードウェアによって更新される。

#### 【0150】

図 16 に戻って、RF26 からの R0 の読み取りは、T\_R0\_143 と O\_R0\_142 の間で選択される。この選択は、マルチプレクサ 144 によって、PVA\_exeo と称する制御信号を使用して制御される。この信号は、計算機が PVA モードで実行しており、ストリーム L<sub>0</sub> がイネーブルされる時にアサートされる。RF26 からの R0 の読み取りによって、この場合には、T\_R0\_143 の内容が出力される。それ以外で、PVA\_exeo がアサートされない時には、R0 からの読み取りによって、O\_R0\_142 の内容が出力される。類似する制御機構が、PVA 実行中の RF26 からの R1 読み取りに関して存在する。

#### 【0151】

レジスタ R2\_162 は、オーバーレイされない。RF26 のレジスタ R3 から R15 と同様に、R2 は、単一のインスタンスを有する。しかし、R2 は、Sストリームがイネーブルされた PVA 実行中に、レジスタ O\_R0\_142 および O\_R1\_152 に類似する形で更新される。

#### 【0152】

スカラ実行に関して、メモリ・ロードは、メモリ・ブロック M0\_14 から L<sub>0</sub>\_6 を介して L<sub>0</sub>\_dbus に、または M1\_16 から L<sub>1</sub>\_8 を介して L<sub>1</sub>\_dbus に、データをフェッチすることと、その後、RF26 のレジスタのいずれかに書き込むことによって実行される。したがって、L<sub>0</sub>\_dbus または L<sub>1</sub>\_dbus から RF26 のレジスタのいずれかにデータを書き込むバスが必要である。このバスは、図 16 に示されているように、RF26 内のマルチプレクサ 164 によって提供される。マルチプレクサ 164 は、その入力を L<sub>0</sub>\_dbus、L<sub>1</sub>\_dbus、および result\_bus から取り、その出力をマルチプレクサ 141、マルチプレクサ 151、マルチプレクサ 161、およびレジスタ・アレイ 163 に供給する。レジスタ・アレイ 163 によって、アーキテクチャ的レジスタ R3 から R15 が実施される。マルチプレクサ 164 を介して、L<sub>0</sub>\_dbus および L<sub>1</sub>\_dbus が、T\_R0\_143 および T\_R1\_153 を除く、RF26 内のレジスタのいずれかに書き込み得る。この実施形態では、一時レジスタ T\_R0\_143 および T\_R1\_153 が、スカラ実行中に使用可能でない。

#### 【0153】

ベクトル実行 (CVA 実行または PVA 実行) の前に、あるレジスタを、正しく初期化する必要がある。これらの特殊なレジスタには、ハードウェアが正しいベクトル実行を実行するのに必要なすべての情報が含まれる。表 3 に、これらの特殊なレジスタを詳細に示す。

#### 【0154】

10

20

30

40

## 【表3】

表3. ベクトル実行に関する特殊なレジスタ

| レジスタ             | 表記   | レジスタ内容                                              |

|------------------|------|-----------------------------------------------------|

| ストライドおよびサイズ・レジスタ | SSR  | $L_0$ 、 $L_1$ 、および $S^1$ に関するストライド値<br>およびオペランド・サイズ |

| カウント・インデックス・レジスタ | CIR  | CR: 実行される反復の回数<br>IXR: PVA ループの「ローカル PC」            |

| 汎用レジスタ R0        | O_R0 | $L_0$ のローカル・アドレス <sup>1, 2</sup>                    |

| 汎用レジスタ R1        | O_R1 | $L_1$ のローカル・アドレス <sup>1, 2</sup>                    |

| 汎用レジスタ R2        | R2   | S のストア・アドレス <sup>1</sup>                            |

| 汎用レジスタ R3        | R3   | リダクション CVA またはハイブリッド CVA の部分的結果および最終結果 <sup>1</sup> |

| 汎用レジスタ R4        | R4   | オペランド X のソース <sup>1</sup>                           |

| 汎用レジスタ R5        | R5   | オペランド Y のソース <sup>1</sup>                           |

| 汎用レジスタ R6        | R6   | オペランド Z のソース <sup>1</sup>                           |

1. 適用可能な場合に。

2. これらはオーバーレイされるインスタンスのみである。

10

20

30

40

この実施形態では、SSR42 および CIR50 だけが、特殊な制御レジスタである。他のすべてのレジスタが、汎用レジスタである。ベクトル演算に応じて、これらのレジスタが、ベクトル動作中に特殊な意味を伝える場合とそうでない場合がある。たとえば、R2 は、ベクトル実行中に S ストリームがイネーブルされる時に特殊な意味を有するが、この特殊な意味は、S ストリームに関する最新の c s - s t o r e アドレスがストアされることを指す。

## 【0155】

表3には、R0 および R1 のオーバーレイされるインスタンスだけが含まれる。割込みまたは例外の時に、SSR42 および CIR50 が、ハードウェアによって保存される。これらの特殊な制御レジスタを保存するために、追加のハードウェア・サポートが必要である。レジスタ R0 から R6 は、汎用レジスタなので、ハードウェアによって自動的に保存される。一時レジスタ T\_R0\_143 および T\_R1\_153（表3に示さず）だけが、ハードウェアによって保存されない。

## 【0156】

割込みからリターンする時に、通常の実行を再開する前に、下記の情報を計算機に復元する必要がある。O\_R0\_142、O\_R1\_152、および R2\_162 の内容を、RF26 から、それぞれ L\_R0\_114 ( $L_0$  6 内)、L\_R1\_124 ( $L_1$  8 内)、および L\_R2\_136 (S36 内) コピーする必要がある。後者の 3 つのローカル・レジスタは、それぞれ図12 から 14 に示されている。

## 【0157】

さらに、リダクション CVA およびハイブリッド CVA について、R3 にストアされた中間の部分的結果を、S36 内のラッチ 130 に復元し、さらに、マルチプレクサ 133 を介して s\_d\_b\_u\_s に復元する必要がある（図14 参照）。この部分的結果の復元には、RF26 から R3 を読み取り、そのデータを P34 を介し、p\_b\_u\_s に、さらに S36 を介して s\_d\_b\_u\_s に転送することが含まれる（図4 参照）。

## 【0158】

図4 からわかるように、3つの独立のオンチップ・メモリ・ブロック、M0\_14、M1\_16、および TM20 がある。PVA 実行中にプログラム・ループ命令をストアするループ・キャッシュ 22 もある。M0\_14 および M1\_16 は、メインのオンチップ・

50

メモリである。M0 14は、命令およびデータのストアに使用される。M1 16は、データのみのストアに使用される。TM20も、データのみのストアに使用され、具体的には、ベクトル実行中に一時ベクトルをストアするのに使用される。

#### 【0159】

図4に示された1実施形態のメモリ・システムでは、ロード・ユニットL<sub>0</sub>6が、M0 14およびTM20への読み取りアクセスを有し、ロード・ユニットL<sub>1</sub>8が、M1 16およびTM20への読み取りアクセスを有し、S36が、M0 14、M1 16、およびTM20のすべてへの書き込みアクセスを有する。M0 14およびM1 16は、単一ポート式メモリであるが、TM20は、1つの読み取りポートおよび1つの書き込みポートを有する。これらのメモリ・ブロックの内容、アクセシビリティ、ならびに読み取りポートおよび書き込みポートの数を、表4に示す。代替実施形態で、スカラ動作およびベクトル動作を許容する他のメモリ構成を実施し得る。

#### 【0160】

#### 【表4】

表4. メモリの詳細

| メモリ・ブロック | 内容          | データ・ストリーム |      |      | 読み取り/書き込みポートの数     | ストリーム間のアービトレイション                |

|----------|-------------|-----------|------|------|--------------------|---------------------------------|

|          |             | L0        | L1   | S    |                    |                                 |

| M0       | 命令およびデータ    | 読み取り      | -    | 書き込み | 1(読み取りまたは書き込み)     | L <sub>0</sub> 対 S              |

| M1       | データ         | -         | 読み取り | 書き込み | 1(読み取りまたは書き込み)     | L <sub>1</sub> 対 S              |

| TM       | データ(一時ベクトル) | 読み取り      | 読み取り | 書き込み | 2(1つの読み取りと1つの書き込み) | L <sub>0</sub> 対 L <sub>1</sub> |

ストリームL<sub>0</sub>、L<sub>1</sub>、およびSをイネーブルされたコンパウンドCVAまたはハイブリッドCVAを実行するために、メモリ・システムは、1サイクルあたり1結果のピーク・スループット・レートを維持するために、1サイクルあたり2つのデータ読み取りおよび1つのデータ書き込みをサポートする必要がある。CVA実行中には命令要求がない。これは、CVA命令がデコードされ、実行されたならば、CVA実行の残りに関してさらなる命令が不要であるからである。2つのデータ読み取りおよび1つのデータ書き込みに加えて、PVA実行では、各サイクルに1つの命令フェッチも必要になる可能性がある。

#### 【0161】

各サイクルに、図4に示されたメモリ・システムは、M0 14、M1 16、およびTM20を介する2つのデータ読み取りおよび1つのデータ書き込みまでをサポートすることが可能であり、同一のサイクルに、ループ・キャッシュ22の使用を介する1つの命令フェッチもサポートすることが可能である。3つのメモリ・ブロックM0 14、M1 16、およびTM20は、ある事前定義のメモリ空間を参照することによってアクセスし得る、すなわち、これらは、メモリ・マッピングされたブロックである。

#### 【0162】

1実施形態によれば、図4に示されたTM20は、ベクトル実行中に一時ベクトルをストアするのに使用される小さいRAMメモリである。TM20は、ディジタル・フィルタリングの係数ベクトルなど、頻繁に使用される定数ベクトルに使用することも可能である。TM20は、一時ベクトルを保持する、従来のベクトル計算機のベクトル・レジスタの拡張である。従来のベクトル計算機の最適化コンパイラと同様に、最適化コンパイラは、メモリに書き戻す前に、可能な限りこれらの一時ベクトルを操作することを試みる。TM20は、M0 14およびM1 16に対するメモリ帯域幅圧力を減らすのに役立つ。TM20は、これらのより大きいメモリ・ブロックの電力消費を減らすのにも役立つ。

#### 【0163】

TM20へのアクセスは、ベクトル・レジスタ番号など、ベクトル命令で指定される明

10

20

30

40

50

示的な参照ではなく、適当なメモリ空間を参照することによって行われる。具体的に言うと、これらのアクセスは、ストリーム  $L_0$ 、 $L_1$ 、および  $S$  をセットアップすることによって行われる。

#### 【0164】

これらの一時ベクトルを構成し、割り振り、使用する時に、コンパイラは、一時記憶空間の編成においてより高い柔軟性を有する。たとえば、TM20または他の類似する一時メモリが、n要素のベクトルをストアし得る場合に、そのメモリを、それぞれがn/m要素の長さを有するm個のベクトルの記憶空間として編成することも可能である。TM20を、異なる長さの複数のベクトルの記憶空間として編成することも可能である。この場合に、コンパイラは、TM20内のフラグメンテーションを最小にするようにベクトル割振りを管理することを試みる。

#### 【0165】

次の例では、TM20が、1つの読み取りポートおよび1つの書き込みポートを有する直接マッピングされる512バイトであると仮定する。TM20を使用して、この例では、ベクトル実行を高速化し得る。

#### 【0166】

やはり、例2に示されたループを検討されたい。このループが、 $C[i] = (lsr(A[i], R9) | lsl(A[i], R8))$  を実行していることを想起されたい。ベクトル化されたコードを、下に示す。

#### 【0167】

#### 【数16】

Some initialization code

```

// assign L0 to vector A; assign S to a temporary vector in TM

```

```

mov R5, R9

```

```

CVA lsr @L0, R5, @S

```

Some initialization code

```

//assign L0 to vector A; assign L1 to the temporary vector in TM

```

```

//assign S to vector C.

```

```

mov R5, R8

```

```

CVA lsl @L0, R5, @P, or @L1, @P, @S

```

この例では、一時ベクトルが、TM20内で作成され、割り振られる。第1のCVA命令のデスティネーションおよび第2のCVA命令のソース・オペランドの1つによって、TM20を介して一時ベクトルがアクセスされる。第1のCVA命令は、M0 14から $L_0$ ストリームを介してベクトルAをソーシングし、Sストリームを介して一時ベクトルをTM20に書き込む。第2のCVA命令は、M0 14から $L_0$ ストリームを介してベクトルAをソーシングし、 $L_1$ ストリームを介してTM20から一時ベクトルをソーシングする。また、この命令は、Sストリームを介してM1 16に結果ベクトルを書き込む。

#### 【0168】

この例では、第2のCVA命令で、3つのデータ・ストリームすなわち、2つの入力、および1つの出力が使用される。これらのベクトル実行では、メモリ衝突は生じない。M0 14およびM1 16だけを使用すると、メモリ衝突が引き起こされる。TM20がなければ、第2のCVA命令は、各結果要素を作るのに2サイクルを要する。

#### 【0169】

10

20

30

40

50

処理されるベクトルのサイズが、TM20のサイズより大きい時には、ベクトル動作が、ソフトウェア制御の下で複数のベクトル動作に分割され、各ベクトル動作が、TM20のストレージで使用可能な長さのベクトルを操作する。この意味で、TM20の使用は、ベクトル・レジスタの「ストリップマイニング(s trip-mining)」に類似する。しかし、固定長ベクトル・レジスタと異なって、コンパイラは、この場合に、割振りと使用が可能な一時ベクトルの数とストリップマイニング反復の間のトレードオフに対する柔軟性を有する。

#### 【0170】

もう1つの例として、ベクトル長がコンパイル時に未知であると仮定して、上のループのストリップマイニングおよびベクトル化を行う。要素サイズは、ワード(4バイト)であることが既知である。各ベクトル要素が、4バイト長であり、TM20が512バイトなので、128要素を超える長さのベクトルは、TM20のオーバーフローを避けるために、多少のストリップマイニングを必要とする。

#### 【0171】

この例では、2つのCVA命令および1つの一時ベクトルだけが使用され、TM20全体を、128以下の長さの一時ベクトルのストア専用にし得る。下に、C風の言語での、未知のベクトル長nを有するストリップマイニングされたコードを示す。

#### 【0172】

#### 【数17】

```

low = 1;                                20

VL = (n mod 128);                      // find the odd size piece first

for (j=0; j<n/128; j++) {

for (i=low; i<low+VL-1; i++) {      // runs for length VL

C[i] = (lsr(A[i],R9) | lsl(A[i],R8)); //main CVA operations

}

low = low + VL;

VL = 128;                          // reset VL to 128 after the first

// odd size piece

}

```

ある独立のベクトルA、B、C、およびDに関して、ベクトル・リダクション演算 $\sum_i ((A[i] * B[i] + C[i]) * A[i] * B[i] * D[i])$ の実行の例のように、最高の可能な性能レベルを維持しながら電力消費を減らすのにTM20を使用することも可能である。ベクトルAおよびCが、M0 14内にあり、ベクトルBおよびDが、M1 16内にあると仮定する。

#### 【0173】

3つの一時ベクトルおよび4つのCVA命令(3つのコンパウンドCVAおよび1つのリダクションCVA)を使用する、実行時間に関する最適解を下に示す。

```

(1) T1[i] = A[i] * B[i];

(2) T2[i] = T1[i] + C[i];

(3) T3[i] = T1[i] * D[i];

(4) リダクション結果 =  $\sum_i (T2[i] * T3[i])$

```

ベクトルAおよびBは、M0 14およびM1 16にあるので、ベクトルT1は、TM20内で割り振られなければならない。したがって、ベクトルT3は、ベクトルDがM1 16内にあるものとして、M0 14内になければならない。ベクトルCはM0 14

10

20

30

40

50

にあるので、ベクトル T 2 は、M 1 1 6 または TM 2 0 内に置き得る。表 5 に、一時ベクトル T 1 および T 2 の割振りの 2 つの可能な解決を示す。

#### 【0174】

【表 5】

表 5. 一時メモリ割振り

| 一時ベクトル | 解決 (I) |    |    | 解決 (II) |    |    |

|--------|--------|----|----|---------|----|----|

|        | M0     | M1 | TM | M0      | M1 | TM |

| T1     |        |    | X  |         |    | X  |

| T2     |        | X  |    |         |    | X  |

| T3     | X      |    |    | X       |    |    |

この解決の両方が、メモリ衝突をこうむらない。両方の解決が、この計算機での最適性能レベルを達成する。しかし、表 5 の解決 (I) は、ベクトル T 2 が TM 2 0 に割り振られるので、より低電力の解決を与える。解決 (II) の短所は、一時ベクトル T 1 および T 2 の両方が同時に TM 2 0 に存在することを必要とすることである。TM 2 0 が、両方のベクトルを保持するのに十分に大きくはない場合に、解決 (I) が、唯一の実行可能な解決である。TM 2 0 が、単一のベクトルにも小さすぎる場合には、解決 (I) をストリップマイニングする必要がある。

#### 【0175】

本発明の 1 実施形態のベクトル実行のすべてが、割込み可能である。割込みは、ベクトル計算の完了の前のベクトル実行の一時的中断を引き起こし得る。スカラ・コンテキストに加えて、追加のベクトル・コンテキストを保存し、その結果、割込みからのリターンの際にベクトル実行を正しく再開可能にする必要がある。割り込み時に、これらのベクトル・コンテキストの一部は保存され、一部は破棄される。保存されるベクトル・コンテキストに、表 3 に示されたすべてのレジスタが含まれる。このレジスタには、SSR42、CIR50、オーバーレイされるインスタンス O\_R0 142 および O\_R1 152、R2 162、および RF26 内の他のレジスタすなわち、T\_R0 143 および T\_R1 153 を除く RF26 内のすべてのレジスタが含まれる。

#### 【0176】

CVA 実行に関して、各ベクトル要素に対する動作は、あるベクトル要素に対する動作の結果が割込み発生時に書き戻されない場合に、すべての中間結果が破棄されるという意味で、「アトミック」である。この 1 つまたは複数の要素に対して実行されるすべての動作が、割込みからのリターンの際に繰り返されなければならない。リダクション CVA 実行またはハイブリッド CVA 実行に関して、各サイクルに作られる部分的結果が、RF26 内のレジスタ R3 に継続的に書き戻される。割込み時に、部分的結果が既に RF26 にあるので、したがって、部分的結果は自動的に保存される。これによって、部分的結果を保存するための追加の浪費される時間が除去される。しかし、割込みからのリターンの時に、RF26 内のレジスタ R3 の内容が、通常の CVA 実行を再会する前に s\_d\_b\_u\_s に復元される。

#### 【0177】

PVA 実行に関して、ループ本体で作られるすべての中間結果が、レジスタ・ファイル、RF26 にストアされる。したがって、中間結果を保存するために追加の時間は浪費されない。一時レジスタ T\_R0 143 および T\_R1 153 は、ベクトル・コンテキストの一部として保存されない。割込みからリターンする時に、これらの一時物をフェッチした cs - load 命令は、入力ストリームがイネーブルされる場合に再初期化される。その後、一時レジスタ T\_R0 143 および T\_R1 153 が、通常の PVA 実行を再会する前にそれ相応に更新される。この場合に、ハードウェアは、割込みをサービスする過程の間にメモリ位置が変更されなかつたと仮定する。

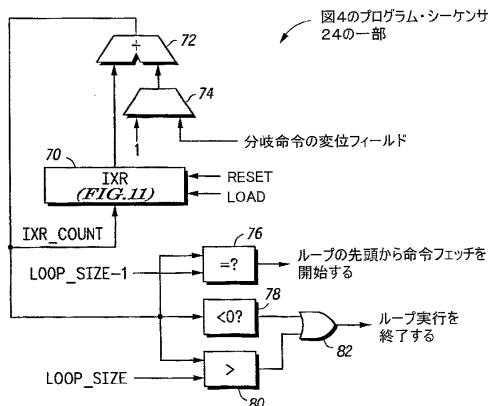

## 【0178】

図18に、図4のプログラム・シーケンサ24の一部を示す。ループ実行おおび分岐のターゲットを監視するために、カウンタ・ベースの方式を使用し得る。PVA命令に出会う時に、その命令で指定されるLoop\_sizeが、図4のプログラム・シーケンサ24などのハードウェアによって取り込まれる。さらに、IXR70(図11参照)を使用して、ループ本体のどの命令が現在実行されているかを追跡する。IXRの実施の1実施形態を、図18に示す。IXR70は、ループ本体の中でローカル・プログラム・カウンタ(PC)のように振る舞う。ループの最初の命令が実行されている時に、IXR70に1がセットされる。順次実行される命令ごとに、IXR70が1つ増分される。ループの最後の命令が実行されている時に、IXR70はLoop\_sizeと等しい。IXR70が(Loop\_size - 1)と等しい時に、命令フェッチが、ループの最初の命令に向けられる。最後の命令が、シーケンシャル命令であるか、命令が制御フローの変更を引き起こさない(ターゲットがループ本体の外部にある)場合に、実行が、ループの先頭に転送され、IXR70が、1にリセットされる。

## 【0179】

IXR70は、加算器72の出力であるIXR\_count値を受け取る。IXR70にストアされた値は、一方の入力として加算器72に供給され、他方の入力は、マルチプレクサ74から来る。マルチプレクサ74への一方の入力は、1であり、他方の入力は、分岐命令の変位フィールドである。この形で、加算器72は、次の順次値または分岐変位値のいずれかを出力する。IXR70は、IXR70を1にリセットするreset信号と、次のIXR\_countを受け入れるload信号も受け取る。

## 【0180】

分岐がPVA実行中に採用される(順方向または逆方向のいずれか)場合に、分岐命令の分岐変位フィールドが、IXR70に加算される。この加算演算は、マルチプレクサ74および加算器72によって実行される。マルチプレクサ74は、この場合に、加算器72への分岐命令の変位フィールドを選択する。このレジスタ値と分岐変位の合計が負またはループ・サイズを超える場合には、分岐ターゲットがループ本体の外部にあることが示され、PVAループ実行が終了する。

## 【0181】

図18を続けると、IXR\_count値も、入力としてブロック76、78、および80に供給される。IXR\_countは、継続的に0、Loop\_size、およびLoop\_size - 1と比較される。(IXR\_count < 0)または(IXR\_count > Loop\_size)である場合に、命令がループ本体の外で実行されようとしていることが示される。ブロック78で(IXR\_count < 0)と判定される場合に、ブロック78の出力が、「or」ゲート82への入力としてアサートされる。同様に、ブロック80で(IXR\_count > Loop\_size)と判定される場合に、ブロック80の出力が、「or」ゲート82にアサートされる。どちらの場合でも、「or」ゲート82の出力によって、ループ実行が終了される。また、ブロック76で(IXR\_count == Loop\_size - 1)と判定される場合に、ループの先頭からの命令フェッチが開始される。

## 【0182】

PVA命令の最後の反復の終りに向かって、ループ内の最後の命令が、ループ本体の外のターゲット・アドレスを有する採用される条件分岐である場合に、ループの最初の命令を誤ってフェッチし、実行することに関する1サイクルのペナルティをこうむる。この場合に、この命令の実行の結果が、却下される、すなわち、結果が、破棄され、書き戻されない。分岐ターゲットを使用する新しい命令フェッチが開始される。

## 【0183】

割込みからPVA実行を再開する時に、まず、必要なループ制御情報を回復しなければならない。これは、複数の形で行い得る。1実施形態で、PVA命令に最初に出会う時に、PC(PVA命令のアドレス)が、一時ハードウェア位置に保存される。割込み時に、

このハードウェア・コピーが P C として保存される。割込みからリターンする時に、まず P C を使用して P V A 命令をフェッチして、 L o o p \_ s i z e 、 c s - s t o r e - i n d e xなどを含むループ制御情報のすべてを回復する。この情報が回復された後に、 I X R 7 0 の内容が P C に加算される。 P V A ループ実行が、新しい P C によってポイントされる命令から継続される。

#### 【 0 1 8 4 】

もう 1 つの実施形態で、 P V A 実行が割り込まれる時に、 P C は、ループ本体の中の、実行が割り込まれた命令をポイントする。この P C を、実行コンテキストの一部として保存する。割込みからリターンする時に、 I X R 7 2 の内容を P C から減算して、 P V A 命令アドレスを得る。次に、 P V A 命令をフェッチして、 c s - s t o r e - i n d e x 、 L o o p \_ s i z eなどを含むループ制御情報のすべてを回復する。

10

#### 【 0 1 8 5 】

P V A 実行では、「 c s - s t o r e 」ラベルに配置された命令およびそれに関連する c s - s t o r e 動作の実行が、「アトミック」動作である。例 4 からのベクトル化された P V A ループをもう一度検討されたい。

#### 【 0 1 8 6 】

#### 【 数 1 8 】

<Some initialization code>

// assign L0 to vector A; assign S to C[i].

```

mov      R4, 4

mov      R8, 8

mov    R6, 16

```

20

PVA @L0, @S, #4; // PVA instruction

mov R2, R8

cmplt R6, R0 // is A[i] > 16?

30

cs-store:

movt R2, R4 // R2 = (A[i]>16)? R4:R8;

// cs-store performed here

「 m o v t 」命令および関連する c s - s t o r e 動作は、「アトミック」である。 c s - s t o r e が、割込みに起因して完了しない場合に、「 m o v t 」命令も、「実行されない」と考えられる。割込みからリターンする時に、「 m o v t 」命令から実行が再開される。

40

#### 【 0 1 8 7 】

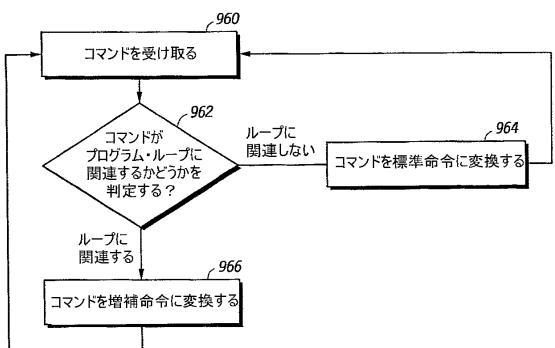

上で示したベクトル化された例のそれぞれについて、コンパイラは、元のコードを評価するが、このコードは、高水準言語プログラミング言語またはアセンブリ・コードで記述され得る。コンパイラは、コードを分析して、 C V A 命令および / または P V A 命令に適用可能なループおよび他の構成を探す。本発明の 1 実施形態によるコンパイルの処理フローを、図 1 9 に示す。

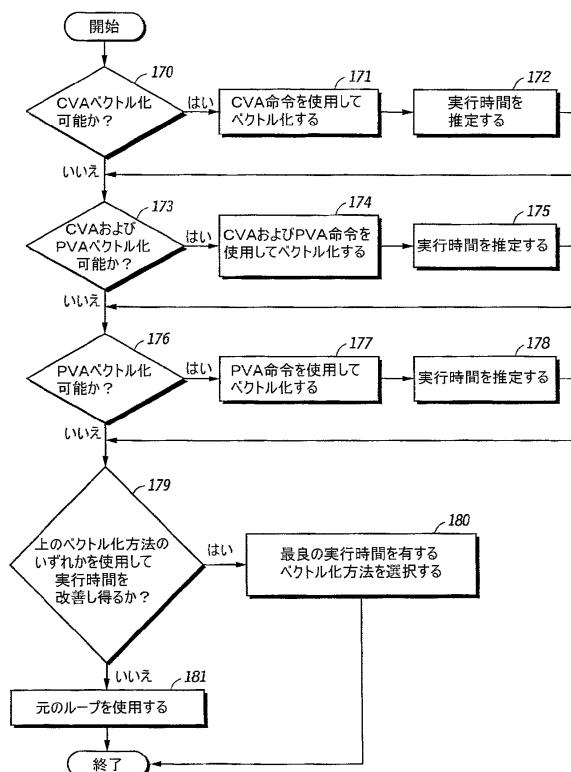

#### 【 0 1 8 8 】

図 1 9 からわかるように、この処理では、まず、判断菱形 1 7 0 で、ループまたはコードのセクションが、 C V A 実行を使用してベクトル化可能であるかどうかを判断し、そうである場合に、ブロック 1 7 1 で、少なくとも 1 つの C V A 命令を使用してコードをベク

50

トル化する。次に、ブロック 172 で、CVA ベクトル化されたループの実行時間を推定する。次に、判断菱形 173 に継続する。

#### 【0189】

その代わりに、コードが CVA ベクトル化可能でない場合にも、判断菱形 173 に継続されて、CVA 実行および PVA 実行の組合せを使用してコードをベクトル化可能であるかどうかを判定する。そうである場合には、ブロック 174 でそのような組合せを使用してコードをベクトル化し、ブロック 175 で、その実行速度を推定する。その後、処理フローは判断菱形 176 で継続される。

#### 【0190】

コードが、CVA 単独または CVA / PVA 組合せのいずれによってもベクトル化可能でない場合にも、処理は、判断菱形 176 に継続されて、コードが PVA ベクトル化可能であるかどうかを判定する。そうである場合には、ブロック 177 で、少なくとも 1 つの PVA 命令を使用してコードをベクトル化する。ブロック 178 で、その実行時間を推定する。

10

#### 【0191】

判断菱形 179 では、ベクトル化されたコードの実行速度が、上で述べたベクトル化方法のいずれかを使用して、元のループより改善されるかどうかを判定する。改善がない場合には、ブロック 181 で、元のコードを変更しない。実行速度が改善された場合には、ステップ 180 で、最短の実行時間を有する最良のベクトル化方法を使用するコードを実施する。この実施形態では、コンパイラが、可能なすべてのベクトル化方法を試行し、その中から最良の方法を選択する。この実施形態では、実行時間が、唯一の選択判断基準として使用される。他の実施形態では、電力消費などの他の判断基準の使用を組み込んで、最良のベクトル化方法を選択することも可能である。

20

#### 【0192】

代替実施形態に、まず CVA 構成だけを使用することによるコードのベクトル化を組み込むことも可能であることに留意されたい。この実施形態では、次に、コードが CVA ベクトル化可能でない場合に限って CVA / PVA の組合せを試行する。CVA / PVA の組合せを使用してもコードがベクトル化可能でない場合には、PVA 構成を使用するベクトル化を試行する。この代替実施形態では、最も頻繁に、CVA ベクトル化が実行速度の最大の改善を作り、次が CVA / PVA の組合せであり、最後が PVA ベクトル化であることが認識されている。この処理は、コードをベクトル化し得る最初の方法を見つけた時に終了する。この代替実施形態は、実行時間を推定するのに使用されるプロファイル情報が入手可能でない時に有利である。他の代替実施形態で、所与のアプリケーションに適する他の順序付けを見つける。

30

#### 【0193】

この実施形態によれば、PVA 実行は、各サイクルに 1 つの命令を発行することに制限される。代替実施形態では、PVA 実行を、図 2 に示されたものに類似する、各サイクルに複数の独立の命令を発行する機能を組み込むように拡張し得る。

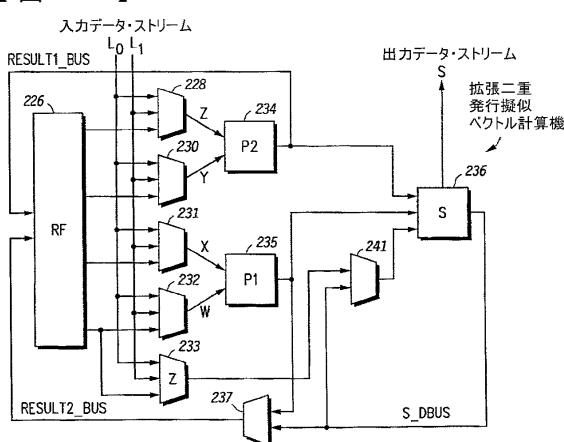

#### 【0194】

そのような拡張の 1 つである二重発行擬似ベクトル計算機を、図 21 に示すが、この図では、各サイクルに、2 つの独立の命令を、2 つの独立の計算ユニット、P1\_235 および P2\_234 に発行し得る。スカラ・モードまたは PVA モードで実行される時に、2 つの結果を、レジスタ・ファイル RF236 またはメモリに書き戻し得る。

40

#### 【0195】

図 21 で、レジスタ・ファイル RF226 ならびにデータ・ストリーム L<sub>0</sub> および L<sub>1</sub> は、独立に、マルチプレクサ 228、230、231、232、および 233 にデータを供給する。マルチプレクサ 228 および 230 は、機能ユニット P2\_234 にデータを供給する。マルチプレクサ 231 および 232 は、機能ユニット P1\_235 にデータを供給する。P2\_234 は、result1\_bus を介して S236 および RF226 にデータを供給する。P1\_235 は、マルチプレクサ 237 および S236 にデータを

50

供給する。マルチプレクサ 241 は、S236 にデータを供給する。S236 は、データ・ストリーム S を介してメモリ・システムに、ならびにマルチプレクサ 237 および 241 にデータを供給する。マルチプレクサ 237 は、result2\_bus を介して RF226 にデータを供給する。RF226 も、マルチプレクサ 228、230、231、および 232 にデータを供給する。

#### 【0196】

この二重発行擬似ベクトル計算機では、3 タイプの CVA すなわち、コンパウンド CVA、リダクション CVA、およびハイブリッド CVA がある。この 3 タイプの CVA の依存性グラフを、図 22 に示す。図 5 の依存性グラフと対照的に、この計算機では、リダクション CVA およびハイブリッド CVA に、下記の一般形式を有する 3 入力算術関数 s\_op が含まれる。

#### 【0197】

スカラ T、U、および V について、T s\_op U s\_op V

この依存性グラフでは、オペランド W、X、Y、および Z が、独立に、入力ストリーム L<sub>0</sub>、入力ストリーム L<sub>1</sub>、または指定されたレジスタからソーシングし得る。このオペランド・ソーシング・モードを、本明細書では独立ソーシング・モードと称する。その代わりに、これらのオペランドのそれぞれが、入力ストリーム L<sub>0</sub> または L<sub>1</sub> の 0 拡張された上位ハーフワードまたは下位ハーフワードからソーシングすることも可能である。このオペランド・ソーシング・モードを、本明細書ではクロス・ソーシング・モードと称する。表 6 に、独立ソーシング・モードおよび 2 つの異なるクロス・ソーシング・モード（クロス・ソーシング・モード I および II）を示す。

#### 【0198】

#### 【表 6】

表 6. オペランド W、X、Y、および Z の可能なソース

| オペランド | オペランド・ソーシング・モード                     |                             |                             |

|-------|-------------------------------------|-----------------------------|-----------------------------|

|       | 独立ソーシング・モード                         | クロス・ソーシング・モード I             | クロス・ソーシング・モード II            |

| W     | L <sub>0</sub> 、L <sub>1</sub> 、R0  | {0, L <sub>0</sub> [31:16]} | {0, L <sub>0</sub> [31:16]} |

| X     | L <sub>0</sub> 、L <sub>1</sub> 、R4  | {0, L <sub>1</sub> [15:0]}  | {0, L <sub>1</sub> [31:16]} |

| Y     | L <sub>0</sub> 、L <sub>1</sub> 、R8  | {0, L <sub>1</sub> [31:16]} | {0, L <sub>1</sub> [15:0]}  |

| Z     | L <sub>0</sub> 、L <sub>1</sub> 、R12 | {0, L <sub>0</sub> [15:0]}  | {0, L <sub>0</sub> [15:0]}  |

この表で、{0, L<sub>0</sub>[15:0]} は、入力データ・ストリーム L<sub>0</sub> からの 0 拡張された下位ハーフワードを表す。{0, L<sub>0</sub>[31:16]} は、入力データ・ストリーム L<sub>1</sub> からの 0 拡張された上位ハーフワードを表す。類似する表記が、L<sub>1</sub> ストリームに使用される。これらの 0 拡張動作の結果は、32 ビット・オペランドである。コンパウンド CVA の一般形式は、次のように表し得る。

#### 【0199】

S<sub>i</sub> = (W<sub>i</sub> p1\_op X<sub>i</sub>) s\_op (Y<sub>i</sub> p2\_op Z<sub>i</sub>) i = 0

、 . . . 、 n - 1

リダクション CVA の一般形式は、次のように表し得る。

#### 【0200】

S<sub>0</sub> = (W<sub>0</sub> p1\_op X<sub>0</sub>) s\_op (Y<sub>0</sub> p2\_op Z<sub>0</sub>) ;

S<sub>i</sub> = (W<sub>i</sub> p1\_op X<sub>i</sub>) s\_op (Y<sub>i</sub> p2\_op Z<sub>i</sub>) s\_op

S<sub>i - 1</sub> 、 i = 1 、 . . . 、 n - 1 ;

R = S<sub>n - 1</sub>

ここで、S<sub>i</sub> は、i 番目の部分的結果を表し、R は、ベクトル・リダクション演算のスカ

10

30

40

50

ラ結果を表す。

#### 【0201】

ハイブリッドCVAの一般形式は、 $S_i$ 、 $i = 0, \dots, n - 1$ が、Sストリームを介してメモリに書き込まれることを除いて、リダクションCVAと同一である。

クロス・ソーシング・モードの多数の使用の1つが、ベクトルA、B、およびCの要素のすべてが複素数である複素ベクトル乗算  $C[i] = A[i] * B[i]$ 、 $i = 0, \dots, n - 1$  である。複素数は、メモリ・システム内で2つの16ビット・ハーフワードの連結として表すことが可能であり、上位ハーフワードは、複素数の実数部を表し、下位ハーフワードは、複数数の虚数部を表す。この表現を使用すると、複素数が、32ビット・データによって完全に表される。

10

#### 【0202】

2つの複素数XおよびYの乗算の結果は、 $(Re X * Re Y - Im X * Im Y) + j(Re X * Im Y + Im X * Re Y)$  によって与えられ、ここで、「Re W」は、複素数Wの実数部を表し、「Im W」は、複素数Wの虚数部を表す。

#### 【0203】

図21に戻ると、2つの複素ベクトルAおよびBの間の乗算を、2つのコンパウンドCVAを使用することによって実行し得る。これらのCVAの両方が、 $L_0$ ストリームを介するベクトルAおよび $L_1$ ストリームを介するベクトルBでストリーム化される。このCVAの両方で、 $p1\_op$ および $p2\_op$ が、乗算関数であり、 $s\_op$ が、加算関数である。第1CVA命令では、クロス・ソーシング・モードIを使用し、結果ベクトルCの虚数部を含む結果ベクトルが作られる。第2CVA命令では、クロス・ソーシング・モードIIを使用し、結果ベクトルCの実数部を含む結果ベクトルが作られる。ストリームSについて2のオペランド・サイズ(ハーフワード)および4のストライド値(1ワード離れる)を使用することによって、この2つのCVA命令を、同一のベクトル位置Cに書き込むことが可能であり、具体的には、2つのCVA命令を、互いの結果を上書きせずにベクトルCに書き込み得る。2つのCVA命令の実行の後に、ベクトルCの各要素に、要求された実数値および虚数値が含まれる。

20

#### 【0204】

上で説明したクロス・ソーシング・モードを、PVA実行にも使用し得る。この場合に、 $p1\_op$ を実行するP1 235と、 $p2\_op$ を実行するP2 234によって作られる2つの結果が、レジスタ・ファイルRF 226内の2つの別個のレジスタおよび/またはメモリ・システムに独立に書き戻される。

30

#### 【0205】

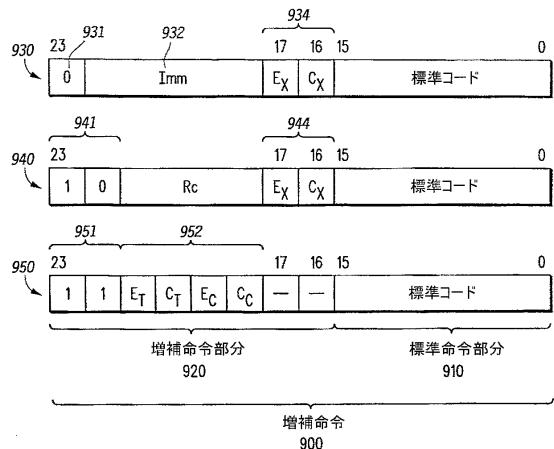

図27から36に、あるプログラム・ループ命令に関連するサイズまたは長さを拡張することによって、PVA実行に関連する能力を高める方法を示す。本発明の1実施形態では、PVA実行中に処理される命令などのループ実行に関連するある命令に、標準命令サイズを使用する標準部分と、第2の命令サイズを使用する増補命令部分が含まれる。増補命令部分の追加によって、ループ実行中に処理される増補命令の総合的なサイズが、強化された実行能力を提供するように拡張される。本発明のいくつかの実施形態は、あるプログラム・ループの命令に伴う追加の機能性を含めることによって、クリティカル・ループ実行の性能を高めるという長所を有する。

40

#### 【0206】

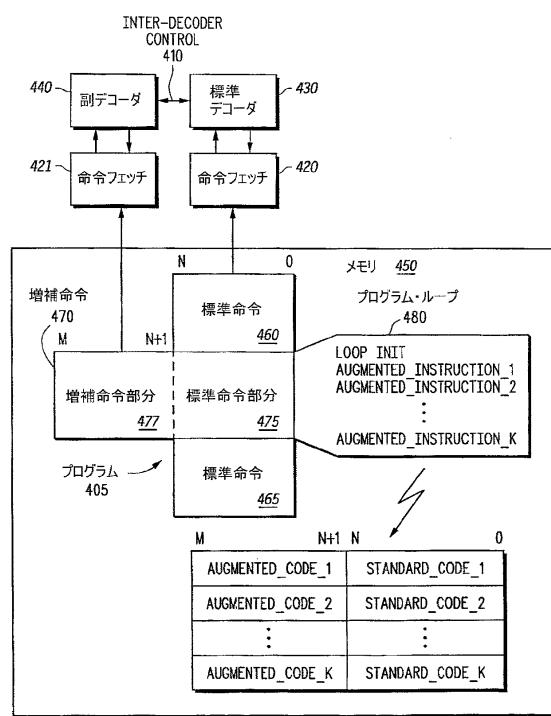

図27を参照すると、本発明の1実施形態による、標準命令および増補命令を処理するシステムを示すブロック図が示され、システム400として全体的に参照される。デコーダ430および440は、プログラム405の命令を処理するのに使用される。プログラム405は、メモリ450にストアされる。プログラム405には標準命令460および465ならびに増補命令470が含まれる。増補命令470には、標準命令部分すなわち標準命令部分475と、増補命令部分である増補命令部分477が含まれる。標準デコーダ430は、標準命令460および465ならびに増補命令470の標準命令部分475の処理に使用される。副デコーダ440は、増補命令470の増補命令部分477の処理

50

に使用される。

#### 【0207】

1実施形態で、標準デコーダ430が、標準命令460および465など、命令の特定のグループに関する標準コマンドの処理に使用される。命令フェッチ・コンポーネント420が、メモリ450から次の命令にアクセスするのに使用される。たとえば、標準デコーダ430は、プログラム405の次に処理される命令にアクセスするように命令フェッチ・コンポーネント420に指示し得る。次の命令のアドレスに関するメモリ・アドレスを命令フェッチ・コンポーネント420に供給して、メモリ450内の次の命令の位置を示し得る。代替案では、命令フェッチ・コンポーネント420が、プログラム・カウンタ(図示せず)を監視して、次に処理される命令のアドレスを判定し得る。

10

#### 【0208】

1実施形態で、命令フェッチ・コンポーネント420が、標準命令460の命令にアクセスする。したがって、命令フェッチ・コンポーネント420は、処理のために標準デコーダ430に命令を供給する。1実施形態で、標準命令460および465の命令に、スカラ命令または非ループ命令が含まれる。増補命令470の命令に、プログラム・ループ命令が含まれる。したがって、システム400は、増補命令470を処理するためにループ実行モードまたはPVA実行モードに切り替え得る。1実施形態で、ループ実行モードまたはPVA実行モードが、PVA命令またはループ初期化命令によってトリガされる。たとえば、増補命令470の最初の命令または標準命令460の最後の命令を、PVA実行を開始するのに使用されるPVA命令とすることが可能である。その代わりに、ループ実行またはPVA実行を、「WHILE」コマンドまたは「DO UNTIL」コマンドなどのプログラム・ループ命令によってトリガし得る。ループ実行モードまたはPVA実行モードをトリガする他の方法を、本発明の範囲から逸脱せずに使用可能であることに留意されたい。さらに、システムは、コンパイル処理中に、標準命令の代わりに増補命令を使用可能にし得る。コンパイラは、後で説明するように、ループまたはループ開始コマンドに出会う時に、増補命令の使用を可能にし得る。

20

#### 【0209】

システム400が、PVA実行モードまたはループ実行モードに入ったならば、副デコーダ440がイネーブルされる。1実施形態で、副デコーダ440は、INTER-DECODER CONTROL信号410を介するなど、標準デコーダ430によってイネーブルまたはディスエーブルされる。したがって、1実施形態で、副デコーダは、命令フェッチ・コンポーネント420に類似する命令フェッチ・コンポーネント421を使用して、標準デコーダ430によってアクセスされる標準命令部分475の標準命令部分に関する増補命令部分477の増補命令部分にアクセスする。代替実施形態では、単一の命令フェッチ・コンポーネント420だけが、標準命令部分475ならびに増補命令部分477の両方をメモリ450からフェッチするのに使用し得る。そのような実施形態では、副デコーダ440が、命令フェッチ・コンポーネント420および標準デコーダ430によって増補命令470の増補命令部分477を受け取り得る。そのような代替実施形態では、標準デコーダ430が、修正またはデコードを実行せずに、副デコーダ440に増補命令部分477を供給し得る。代替案では、命令フェッチ・コンポーネント420が、副デコーダ440に増補命令部分477を直接に供給し得る。

30

#### 【0210】

1実施形態で、増補命令470が、プログラム・ループ480の一部である。プログラム・ループ480には、ループ初期化コマンドと、それに続くK個の増補命令の組が含まれ、ここで、Kは、1を超える、増補命令の数である。1実施形態で、ループ初期化コマンドが、ループ実行を初期化するために含まれる。たとえば、ループ初期化コマンドは、K個の増補命令が処理される反復の回数を示し得る。他のプログラム・ループに関する命令を、標準命令460および465内に含め得ることに留意されたい。しかし、標準命令460および465のプログラム・ループ命令は、増補命令470のプログラム・ループ命令と比較して、増補命令部分を有しない。K個の増補命令は、標準コードおよび増補

40

50

コードの K 個の組に分解される。

**【 0 2 1 1 】**

標準コードには、フォーマットにおいて標準命令 460 および 465 の少なくとも一部の命令に似るコードが含まれる。たとえば、標準コードに、オペコードおよび 1つまたは複数のオペランドを含めることが可能であり、オペコードは、オペランドに対して実行される動作を指定し得る。標準コードは、標準デコーダ 430 を使用して処理される。1 実施形態で、標準命令部分 475 の標準コードに、増補命令 470 の命令に関連する、ビット 0 から N などのビットの第 1 の組が含まれる。増補命令部分 477 の増補コードに、増補命令 470 の命令の、ビット N + 1 から M などのビットの第 2 の組が含まれる。本発明の範囲から逸脱せずに、標準コードで、他のフォーマットを使用し得ることを諒解されたい。

N および M は、特定のビット位置を指定するのに使用され、M は N より大きい。1 実施形態で、標準命令 460 および 465 ならびに標準命令部分 475 が、同一の固定サイズを有し、類似するか同一の命令エンコーディングを使用し得る。

10

**【 0 2 1 2 】**

増補命令部分 477 のコードによって、標準命令部分 475 の処理コードに関連する特定の拡張機能性を指定することが可能である。1 実施形態で、標準命令部分 475 の処理が、増補命令部分 477 の処理に基づく。1 実施形態で、標準デコーダ 430 が、 standard\_code\_1 などの特定の標準命令部分 475 にアクセスするので、副デコーダ 440 は、 augmented\_code\_1 などの関連する増補命令部分 477 にアクセスする。standard\_code\_1 の処理は、 augmented\_code\_1 の処理に依存し得る。たとえば、1 実施形態で、 augmented\_code\_1 を使用して、 standard\_code\_1 の条件実行が指定される。システム 400 の条件コードと augmented\_code\_1 によって指定される条件とのマッチングに応じて、副デコーダ 440 は、 INTER - DECODER CONTROL 信号 410 を使用して、標準デコーダ 430 での standard\_code\_1 の処理を取り消し得る。

20

**【 0 2 1 3 】**

増補命令部分 477 は、標準命令部分 475 に関連する実行の他の形を指定するのに使用し得る。たとえば、増補命令部分 477 の個々のコードによって、標準命令部分 475 の個々のコードに関連する早期終了を指定し得る。したがって、増補命令部分 477 の命令によって、プログラム・ループ 480 のさらなる実行を終了しなければならないことを示し得る。したがって、システム 400 の条件コードと増補命令部分 477 の命令によって指定される条件に応じて、副デコーダ 440 は、 INTER - DECODER CONTROL 信号 410 を提供して、増補命令 470 のさらなる命令をスキップし得る。たとえば、標準デコーダ 430 に、増補命令 470 の代わりに標準命令 465 の最初の命令を処理するように指令し得る。

30

**【 0 2 1 4 】**

増補命令部分 477 のコードによって、標準命令部分 475 の関連コードを処理する時の早期継続を指定することも可能である。たとえば、システム 400 の条件コード値と、副デコーダ 440 によって処理されている増補命令部分 477 の現在のコードによって指定される条件とに応じて、副デコーダ 440 は、共通の標準デコーダ 430 に INTER - DECODER CONTROL 信号 410 を供給して、プログラム・ループ 480 の次の反復をスキップし得る。

40

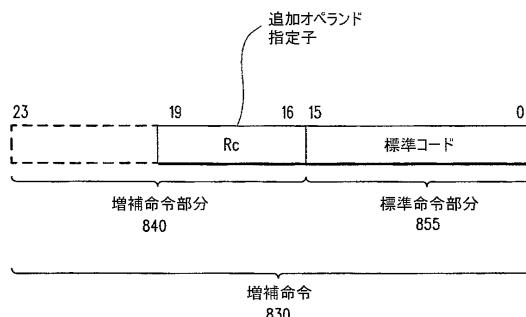

**【 0 2 1 5 】**

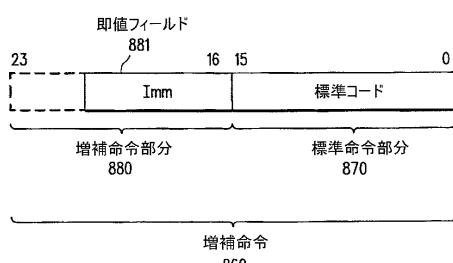

増補命令部分 477 のコードを使用して、標準命令部分 475 のコードを処理するための追加のオペランド指定子を提供することも可能である。1 実施形態で、増補命令の増補コードによって、第 1 オペランドおよび第 2 オペランドの処理からの値が返される第 3 レジスタ・オペランドを指定し得る。1 実施形態で、増補コードにイネーブル・ビットを含めて、デスティネーション・オペランドとしての第 3 オペランドの使用をイネーブルすることも可能である。増補命令部分 477 に関連するコードによって、標準命令部分 475

50

のコードの処理に関するオペランドとして使用される即値フィールドをエンコードすることも可能である。代替案では、増補命令部分 477 によって、標準命令部分 475 で既にエンコードされている即値フィールドの長さを拡張するのに使用される即値フィールドをエンコードすることも可能である。この拡張の結果として、即値フィールド・オペランドの結果の長さが増やされる。

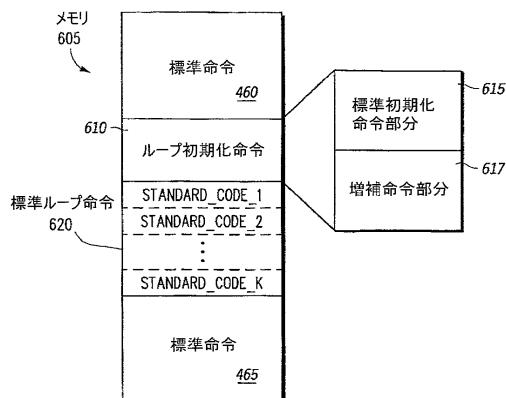

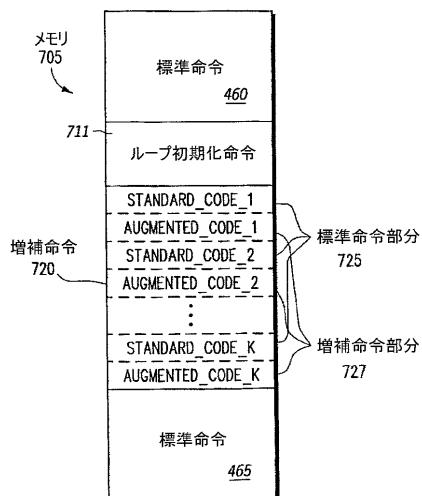

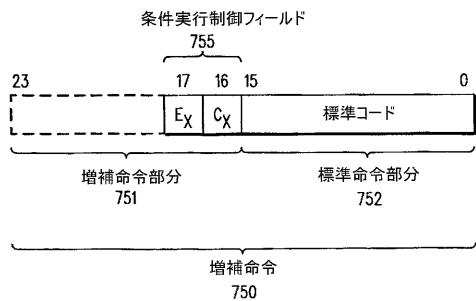

#### 【0216】

本発明の 1 実施形態では、増補命令部分 477 を、後で図 28 で示すように、関連する標準命令部分 475 からメモリ 450 に別々にストアし得る。増補命令部分 477 を、後で図 29 で示すように、標準命令 460 の命令などの別々のコマンドを介して指定し得る。代替案では、標準命令部分 475 を、後で図 30 で示すように、標準命令部分 475 の各関連する部分に隣接して提供し得る。

10

#### 【0217】

本発明の 1 実施形態で、増補命令部分 477 が、標準デコーダ 430 で処理される関連する標準命令部分 475 と時間的に並行して副デコーダ 440 によって処理される。

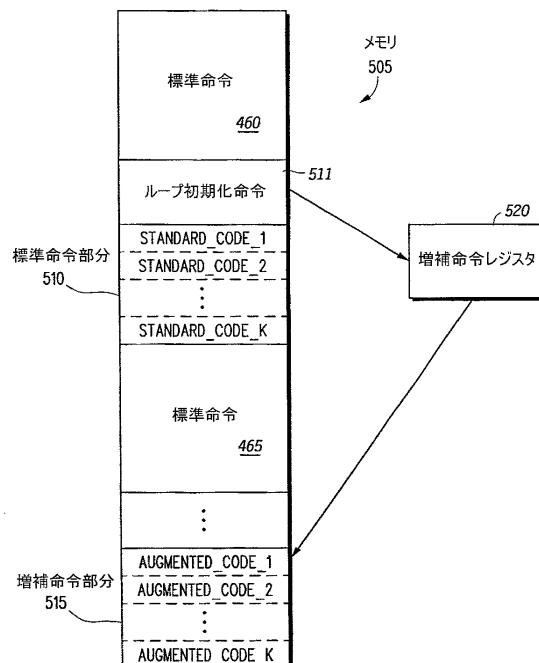

図 28 を参照すると、本発明の 1 実施形態による、メモリに増補命令部分をストアする形を示すブロック図が示されている。標準命令 460 および 465 に、標準デコーダ 430 (図 27) などの標準命令デコーダを使用して処理される標準命令が含まれる。1 実施形態で、標準命令 460 および 465 に、同一の固定命令長が含まれる。増補命令が、特定の命令に関連する機能性を拡張するために提供され、この増補命令には、標準命令 460 および 465 の固定命令長より長い命令長が含まれる。増補命令は、標準命令部分 510 および増補命令部分 515 からなる。図示の実施形態では、増補命令部分 515 が、メモリ 505 のうちで、関連する標準命令部分 510 と異なる部分にストアされる。

20

#### 【0218】