(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-316647

(P2005-316647A)

(43) 公開日 平成17年11月10日(2005.11.10)

(51) Int.C1.<sup>7</sup>**G06F 17/50**

**H01L 21/82**

F 1

G06F 17/50

H01L 21/82

H01L 21/82666Z

C

T

テーマコード(参考)

5B046

5FO64

審査請求 未請求 請求項の数 12 O L (全 16 頁)

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2004-132748 (P2004-132748) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日  | 平成16年4月28日 (2004.4.28)       | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                          |

|           |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                          |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                          |

|           |                              | (72) 発明者 | 定兼 利行<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

|           |                              | (72) 発明者 | 齊藤 健<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内        |

|           |                              |          | 最終頁に続く                                          |

(54) 【発明の名称】集積回路の配線解析方法、論理合成方法、回路分割方法

## (57) 【要約】

【課題】本発明は、予測の精度が高い配線困難指數を算出できる集積回路の配線解析方法を提供する。

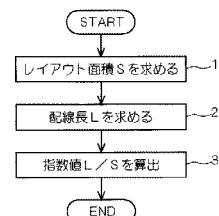

【解決手段】本発明に係る解決手段は、集積回路を構成する複数のセル及びセルの間を接続する配線の情報であるネットリストから集積回路の配線解析を行う方法であって、ネットリストから、複数のセルの面積の合計、あるいは、複数のセルの数、あるいは、接続する配線の数を求めてこれを定数Cとし、定数Cを所定の定数Uで割って正方形のレイアウト領域の面積であるレイアウト面積Sを求める工程(ステップ1)と、面積がステップ1工程で求めたレイアウト面積Sとなるようなレイアウト領域の半周囲長Hに所定の係数を掛けて総配線長Lを求め工程(ステップ2)と、総配線長Lをレイアウト面積Sで割ることにより配線困難指數を算出する工程(ステップ3)とを備える。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

集積回路を構成する複数のセル及び前記セルの間を接続する配線の情報であるネットリストから集積回路の配線解析を行う方法であって、

(a) 前記ネットリストから、複数の前記セルの面積の合計、あるいは、複数の前記セルの数、あるいは、前記接続する配線の数を求めてこれを定数  $C$  とし、前記定数  $C$  を所定の定数  $U$  で割ってレイアウト領域の面積であるレイアウト面積  $S$  を求める工程と、

(b) 面積が前記工程 (a) で求めた前記レイアウト面積  $S$  となるような前記レイアウト領域の所定の周囲長  $H$  に所定の係数  $n$  を掛けて総配線長  $L$  を求める工程と、

(c) 前記総配線長  $L$  を前記レイアウト面積  $S$  で割ることにより配線困難指数を算出する工程とを備える集積回路の配線解析方法。 10

**【請求項 2】**

請求項 1 に記載の集積回路の配線解析方法であって、

前記所定の係数  $n$  は、所定の半周囲長を有する前記レイアウト領域に、前記セルを概略配置して測定された前記総配線長を前記所定の半周囲長で割ることにより求められることを特徴とする集積回路の配線解析方法。

**【請求項 3】**

請求項 1 に記載の集積回路の配線解析方法であって、

前記工程 (b) に代えて、前記レイアウト領域の半周囲長に各ネットの所定の係数  $n$  を掛けて各ネットの配線長  $L_n$  を求め、各ネットの配線長  $L_n$  を積算することで総配線長  $L$  を求める工程を備えることを特徴とする集積回路の配線解析方法。 20

**【請求項 4】**

請求項 3 に記載の集積回路の配線解析方法であって、

前記所定の係数  $n$  は、所定の半周囲長を有する前記レイアウト領域に、前記セルを概略配置して測定された前記ネットの配線長を前記所定の半周囲長で割ることにより求められることを特徴とする集積回路の配線解析方法。

**【請求項 5】**

集積回路が複数の階層モジュールで構成され、ネットリストが階層的に記載される集積回路の配線解析を行う方法であって、

(j) 前記階層モジュールの全体回路は、当該前記階層モジュールより下層に位置する前記階層モジュールの回路を含めた回路であり、各階層の前記階層モジュールの全体回路に対して、配線困難指数を算出する工程とを備える集積回路の配線解析方法。 30

**【請求項 6】**

請求項 5 に記載の集積回路の配線解析方法であって、

前記配線困難指数は、請求項 1 乃至請求項 4 のいずれか 1 つに記載した集積回路の配線解析方法を用いて算出することを特徴とする集積回路の配線解析方法。

**【請求項 7】**

請求項 5 に記載の集積回路の配線解析方法であって、

(k) 各階層に対して、前記階層モジュールの全体回路の前記配線困難指数から、当該前記階層モジュールより下層に位置する前記階層モジュールの全体回路の前記配線困難指数に所定の重み係数を掛けた値を差し引いた値を、当該前記階層モジュールにおける上層回路の前記配線困難指数とする工程をさらに備える集積回路の配線解析方法。 40

**【請求項 8】**

ハードマクロセルを含む集積回路の配線解析を行う方法であって、

(l) 前記集積回路のネットリストから前記ハードマクロセルを削除し、削除後の前記ネットリストは、前記ハードマクロセルと接続していた部分を外部接続ピンとして置き換られる工程と、

(m) 前記工程 (l) 後の前記ネットリストに対して、配線解析を行う工程とを備える集積回路の配線解析方法。

**【請求項 9】**

請求項 8 に記載の集積回路の配線解析方法であって、

前記工程 (m) の前記配線解析は、請求項 1 乃至請求項 8 のいずれか 1 つに記載した集積回路の配線解析方法を用いることを特徴とする集積回路の配線解析方法。

#### 【請求項 10】

集積回路が複数の階層モジュールで構成され、ネットリストが階層的に記載される集積回路の配線解析を行う方法であって、

(n) 前記ネットリストの一部に不完全部分又は欠落部分が存在する場合、当該部分を所定のセルモデルで置換する工程と、

(o) 前記工程 (n) 後の前記ネットリストに対して、請求項 1 乃至請求項 8 のいずれか 1 つに記載した集積回路の配線解析方法を用いる工程とを備える集積回路の配線解析方法。10

#### 【請求項 11】

集積回路のネットリストを生成する論理合成方法であって、

(p) 論理合成されたネットリストに対して請求項 8 に記載した集積回路の配線解析方法を用いて、各階層における前記階層モジュールの全体回路の前記配線困難指数と各階層における前記階層モジュールの上層回路の前記配線困難指数を算出する工程と、

(q) 所定の値より大きい前記配線困難指数を有する前記階層モジュールの回路に対して、回路構成を再構成し、再度論理合成を行い前記ネットリストを生成する工程とを備える論理合成方法。20

#### 【請求項 12】

複数の階層モジュールで構成された集積回路を、複数の部分回路に分割する方法であって、

(r) 各階層の前記階層モジュールのレイアウト面積 S を求める工程であって、

(r1) 前記階層モジュールに配置されるセルが格子を占有する数を示すセル格子使用数と、前記階層モジュールに配置される配線の単位長あたりの格子数 Lg と、単位面積あたりの格子数 Sg と、前記レイアウト領域の占有する格子数に対して前記セル及び前記配線が占有する格子数の割合を示す格子使用率 GU とをテーブルに格納する工程と、

(r2) 前記セルの一覧及び前記セル格子使用数から、複数の前記セルが使用する格子数の合計 GP を求める工程と、30

(r3) 前記配線の接続情報及び前記格子数 Lg から、前記配線が使用する格子数の合計 GR を求める工程と、

(r4) 前記単位面積あたりの格子数 Sg 及び前記格子使用率 GU 並びに前記格子数の合計 GP, GR から、前記レイアウト面積 S を  $(GP + GR) / GU / Sg$  として求める工程とを備え、40

(s) 各階層の前記階層モジュールに対して、当該前記階層モジュールより下層に位置する前記階層モジュールの前記レイアウト面積 S の和が当該前記階層モジュールの前記レイアウト面積 S となるように、下層に位置する前記階層モジュールの前記レイアウト面積 S を変更する工程と、

(t) 前記工程 (s) 後の前記集積回路に対して回路分割を行う工程とを備える回路分割方法。40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、集積回路の配線解析方法、論理合成方法、回路分割方法に係る発明である。

##### 【背景技術】

##### 【0002】

集積回路の配線解析方法において、集積回路を構成するセル及びセル間の接続情報であるネットリストから、集積回路のレイアウト領域に配線を配置した場合の配線の困難さを示す指標である配線困難指標を算出する方法である。従来、ネットリストから配線困難指標を算出する方法として、ネット数や端子間接続数、あるいはネット数や端子間接続数と

セル数との比を求める方法が用いられていた。

【0003】

なお、一般的な配線解析方法等について記載した公知文献を特許文献1に示す。

【0004】

【特許文献1】特開平10-116915号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

従来、ネットリストから求めた配線困難指数は、ネット数や端子間接続数、あるいはネット数や端子間接続数とセル数との比であった、しかし、ネット数や端子間接続数が多いネットリストであっても、実際に配線を行った場合、予測された配線長より短く配線されることもあり配線の困難さは低いこともあった。そのため、従来の配線困難指数は、予測の精度が低いという問題があった。

【0006】

そこで、本発明は、予測の精度が高い配線困難指数を算出できる集積回路の配線解析方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る解決手段は、集積回路を構成する複数のセル及びセルの間を接続する配線の情報であるネットリストから集積回路の配線解析を行う方法であって、(a)ネットリストから、複数のセルの面積の合計、あるいは、複数のセルの数、あるいは、接続する配線の数を求めてこれを定数Cとし、定数Cを所定の定数Uで割ってレイアウト領域の面積であるレイアウト面積Sを求める工程と、(b)面積が工程(a)で求めたレイアウト面積Sとなるようなレイアウト領域の所定の周囲長Hに所定の係数を掛けて総配線長Lを求める工程と、(c)総配線長Lをレイアウト面積Sで割ることにより配線困難指数を算出する工程とを備える。

【発明の効果】

【0008】

本発明に記載の集積回路の配線解析方法は、総配線長Lをレイアウト面積Sで割ることにより配線困難指数を算出するので、単にネット数や端子間接続数を配線困難指数とする場合に比べより精度良く配線の混雑を見積もることができる効果がある。

【発明を実施するための最良の形態】

【0009】

(実施の形態1)

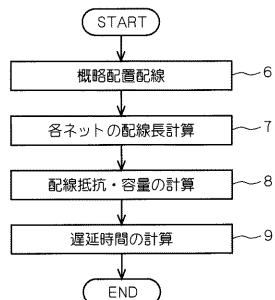

本実施の形態に係る集積回路の配線解析方法では、集積回路を構成するセル及びセル間の接続情報であるネットリストから、集積回路のレイアウト領域に配線を配置した場合の配線の困難さを示す指標である配線困難指数を算出する方法である。図1に、本実施の形態に係る集積回路の配線解析方法のフロー図を示す。

【0010】

まず、図1では、ステップ1として、レイアウト領域の面積(以下、レイアウト面積ともいう)を求める。レイアウト面積を求める方法は、集積回路を構成する複数のセルについて面積を合計して求めたセル面積Cを、所定の定数Uで割って正方形のレイアウト領域の面積であるレイアウト面積Sを求める。つまり、 $S = C / U$ の式によりレイアウト面積Sを求めることができる。なお、上記ではレイアウト領域の面積の一例として正方形としたが、本発明はこれに限られない(以下、同じ)。

【0011】

ここで、所定の定数Uは、集積回路の集積度を示す定数であり、配線困難指数を算出する方法においては、集積回路に依らず同一の値を用いる。また、所定の定数Uは、単位面積のレイアウト領域に配置できるセルの面積の割合を表す数値である。なお、セル面積Cに代えてセル数やネット数からレイアウト面積を求めることができる。

## 【0012】

上述した方法でレイアウト面積  $S$  を求めた後に、図1のフロー図ではステップ2において、総配線長  $L$  を求める。ステップ2では、レイアウト領域の半周囲長  $H$  に所定の係数を掛けて総配線長  $L$  を求めている。ここで、レイアウト領域の半周囲長  $H$  とは、正方形のレイアウト領域のうち2辺分の長さをいう。なお、上記では所定の周囲長を半周囲長  $H$  としたが、本発明はこれに限られず全周囲長を所定の周囲長としても良い。

## 【0013】

また、所定の係数  $\alpha$  は、ある所定の半周囲長  $H_0$  を有するレイアウト領域に、セルを概略配置した場合に、測定して得られる総配線長  $L_0$  を所定の半周囲長  $H_0$  で割ることにより求められる。つまり、所定の係数  $\alpha$  は、総配線長  $L$  とレイアウト領域の半周囲長  $H$  との比例定数であり、ある任意のレイアウト領域にセルを概略配置した場合に得られる総配線長  $L_0$  と半周囲長  $H_0$  を用いて  $\alpha = L_0 / H_0$  を算出する。ここで、概略配置して配線長を求めるとは、ネットリストに記載されたセルをレイアウト領域に配置し、セルの配置位置に基づいて配線長を推定することである。また、配線長の推定方法としては、各配線を配置して配線長を測定する方法や、配線を配置せず、セルの配置位置座標から推定配線長を求める方法（例えば、配線が接続する全てのセルの配置座標を含む最小の矩形をつくり、その矩形の半周囲長を求める方法）などが含まれる。

## 【0014】

なお、上記以外に所定の係数  $\alpha$  を求める方法として、例えば、所定の係数  $\alpha$  が回路の単位面積あたりの配線必要量の関数となることを利用して求める方法がある。具体的には、回路の配線量を示す値である回路の端子間接続数  $PP$  とセル総面積  $CS$  とにより、所定の係数  $\alpha$  は実験式として、 $\alpha = \beta \cdot PP / CS^{1/\sqrt{2}}$  と表すことができる。ここで、 $\sqrt{x}$  は、 $x$  の平方根を表す。その結果、この式に基づいて所定の係数  $\alpha$  を求めることができる。なお、 $\beta$  は実験的に決定される係数である。

## 【0015】

次に、図1のフロー図に示すステップ3では、ステップ2で求めた総配線長  $L$  をステップ1で求めたレイアウト面積  $S$  で割ることにより配線困難指數を算出している。つまり、本実施の形態では、配線困難指數 =  $L / S$  となる。本実施の形態で求めた配線困難指數は、正方形のレイアウト領域に集積度が1となるようにセル及び配線を配置した場合に、単位面積あたりに配置される配線長を示す指標となる。すなわち、単位面積あたりに必要な配線長を表す指標であり、この指標によって集積回路の配線困難性又は接続の複雑度を表すことができる。

## 【0016】

また、本実施の形態で求めた配線困難指數は、セルを概略配置した結果に基づいて求められた総配線長  $L$  を用いているので、従来のように、単にネット数や端子間接続数を配線困難指數に用いる場合に比べて、配線後の結果をより反映することができ精度を高くすることができる。

## 【0017】

以上のように、本実施の形態に係る集積回路の解析方法は、セルを概略配置した結果に基づいて求められた総配線長  $L$  をレイアウト面積  $S$  で割ることにより算出された配線困難指數であるので、単にネット数や端子間接続数を配線困難指數とする場合に比べより精度良く配線の混雑を見積もることができる。また、配線困難指數を精度良く見積もることができれば、配線困難指數が高い値を示す場合にネットリストを修正したり、レイアウト領域の面積を広げるなどの対策を容易に判断することができ、配線の混雑や配線ショートを発生させることがない集積回路の配置配線設計が可能となる。

## 【0018】

## (実施の形態2)

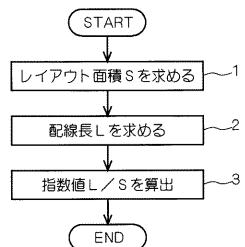

本実施の形態では、集積回路が複数の階層モジュールで構成され、ネットリストが階層的に記載された集積回路の配線解析を行う方法である。図2に、本実施の形態に係る集積回路の配線解析方法のフロー図を示す。

## 【0019】

まず、図2では、ステップ4として、各階層の階層モジュールの全体回路に対して実施の形態1で用いた方法に基づいて、配線困難指数を算出する。ここで、階層モジュールの全体回路とは、指数の算出対象となる階層モジュールより下層に位置する階層モジュールの回路を含めた全体の回路のことである。

## 【0020】

具体的に説明すると、ある階層モジュールMの下層に階層モジュールM1があり、さらに階層モジュールM1の下層に階層モジュールM2がある場合、階層モジュールMの全体回路は、階層モジュールM1及び階層モジュールM2の回路を含むことになる。また、階層モジュールM1の全体回路は、階層モジュールM2の回路を含むことになる。

10

## 【0021】

ステップ4では、全ての階層モジュールの全体回路に対して配線困難指数を算出する。なお、本実施の形態では、配線困難指数の算出方法を実施の形態1に限定されず、従来の算出方法も含まれる。上記の具体例では、階層モジュールMの全体回路の配線困難指数<sub>1</sub>、階層モジュールM1の全体回路の配線困難指数<sub>1</sub>、階層モジュールM2の全体回路の配線困難指数<sub>2</sub>のそれぞれを算出することになる。

## 【0022】

次に、各階層に対して、階層モジュールの全体回路の配線困難指数から、指数の算出対象となる当該階層モジュールより下層に位置する階層モジュールの全体回路の配線困難指数に所定の重み係数を掛けた値を差し引いた値を算出する。算出された値が、各階層の階層モジュールにおける上層回路の配線困難指数となる(ステップ5)。

20

## 【0023】

具体的に説明すると、ある階層モジュールMの全体回路の配線困難指数を<sub>1</sub>とし、当該階層モジュールのモジュール面積をMSとする。なお、モジュール面積は、当該階層モジュールに属するセル面積の総和とする。また、当該階層モジュールより下層に位置する階層モジュールとしてM1とM2が存在し、それぞれの配線困難指数を<sub>1</sub>、<sub>2</sub>、モジュール面積をMS1、MS2とする。このとき、当該階層モジュールにおける上層回路の配線困難指数Tは、 $T = \times MS - 1 \times MS1 - 2 \times MS2$ として算出される。なお、上記の具体例では、所定の重み係数をMS、MS1、MS2としているが、本発明はこれに限られず他の重み係数を用いても良い。

30

## 【0024】

図3に、本実施の形態に係る集積回路の配線解析方法の算出結果リストを示す。図3では、1行毎に1つの階層モジュールの算出結果が記載されており、各行の左からモジュール面積、配線困難指数、階層構造を示す関係及びモジュール名の順で記載されている。

## 【0025】

ここで、配線困難指数とモジュール面積の積である $\times MS$ 、 $1 \times MS1$ 、 $2 \times MS2$ のそれぞれは、階層モジュールM、M1、M2のそれぞれがMS、MS1、MS2の面積となるように配置された場合の配線長を示すことになる。そのため、階層モジュールMをある集積度となるように正方形のレイアウト領域に配置して、階層モジュールM及び下層の階層モジュールM1、M2のそれぞれがMS及びMS1、MS2の面積となる場合、上層回路の配線困難指数Tは、階層モジュールMの全体回路から下層の回路部分を除いた上層回路における単位面積あたりの配線長を示すことになる。つまり、本実施の形態で算出した上層回路の配線困難指数Tは、階層モジュールの上層回路に属する配線の困難さを示す指標として妥当性を有すると考えられる。なお、階層モジュールM1、M2はある領域にまとまって配置されるものとする。

40

## 【0026】

以上のように、本実施の形態に係る集積回路の解析方法は、階層モジュールの上層回路の配線困難指数を算出しているので、全ての階層を含めた回路に対して配線困難指数を求める場合に比べてより詳細で精度の良い配線の混雑を見積もることができる。また、各階層の階層モジュールの全体回路及び上層回路の配線困難指数を精度良く見積もることが

50

できるので、配線困難指数が高い値を示す階層モジュールに対してネットリストを修正したり、配線が混雑しないようなフロアプランの作成やセルの再配置を行うことで、配線の混雑や配線ショートを発生させることがない集積回路の配置配線設計を可能となる。

#### 【0027】

##### (実施の形態3)

実施の形態1では、総配線長 $L$ をレイアウト領域の半周囲長 $H$ に所定の係数 $n$ を掛けて求めていた。そして、所定の係数 $n$ は、ある所定の半周囲長 $H_0$ を有するレイアウト領域にセルを概略配置した場合に、測定される総配線長 $L_0$ を所定の半周囲長 $H_0$ で割ることにより求められていた。

#### 【0028】

本実施の形態では、ある所定の半周囲長 $H_0$ を有するレイアウト領域にセルを概略配置した場合に、総配線長 $L_0$ を求めずに各ネットに対する配線長 $L_{0n}$ を求める。そして、この各ネットに対する配線長 $L_{0n}$ を所定の半周囲長 $H_0$ で割ることにより、各ネットに対する所定の係数 $n$ を求めている。この各ネットに対する所定の係数 $n$ に、解析対象となるレイアウト領域の半周囲長 $H$ を掛けることで、各ネットに対する配線長 $L_n$ を求めることができる。

#### 【0029】

各ネットに対する配線長 $L_n$ を積算することで、解析対象となる集積回路の総配線長 $L$ を求めることができる。この総配線長 $L$ を実施の形態1に用いて配線困難指数を算出することができる。

#### 【0030】

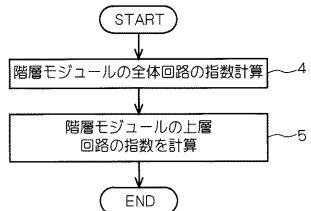

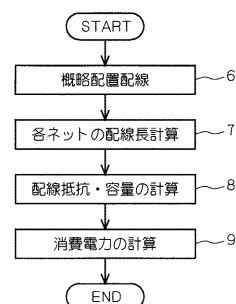

さらに、本実施の形態では、配線困難指数を算出する以外に、各ネットに対する配線長 $L_n$ に基づいて集積回路の消費電力を求める方法を配線解析方法に追加することができる。図4に、本実施の形態に係る集積回路の消費電力を求め方法のフロー図を示す。

#### 【0031】

図4に示すフロー図では、まず、ステップ6において、ある所定の半周囲長 $H_0$ を有するレイアウト領域に、セルを概略配置した場合の各ネットに対する配線長 $L_{0n}$ を求める。これにより、各ネットに対する所定の係数 $n$ 求めることができる。

#### 【0032】

次に、レイアウト領域の半周囲長が $H$ である集積回路に配線を配置した場合の各ネット配線長 $L_n$ を $L_n = n \times H$ で求める(ステップ7)。求められた各ネット配線長 $L_n$ に基づいて配線抵抗と配線容量を求める(ステップ8)。例えば、配線抵抗を求める方法としては、配線の単位長さあたりの配線抵抗値 $R_s$ に各ネット配線長 $L_n$ を掛けることで求められることがある。同様に、配線容量を求める方法としては、配線の単位長さあたりの配線容量値 $C_s$ に各ネット配線長 $L_n$ を掛けることで求められることがある。なお、配線の単位長さあたりの配線抵抗値 $R_s$ 及び配線の単位長さあたりの配線容量値 $C_s$ は、予めテーブルに記憶されている。

#### 【0033】

次に、求められた配線抵抗と配線容量に基づいて消費電力を計算する(ステップ9)。例えば、消費電力は、各セルの消費電力 $P_c$ と各ネット配線の消費電力 $P_w$ との積算で求めることができる。ここで、セルの消費電力 $P_c$ は出力端子に繋がる配線の容量 $C_w$ から求めることができる。つまり、 $P_c = F(C_w)$ となる。ここで、関数 $F$ は、出力端子に繋がる配線の容量 $C_w$ と消費電力 $P_c$ との関係を表す関数で、その関係は予めテーブルに記憶されている。ネット配線の消費電力 $P_w$ は、 $P_w = 1/2 \times f \times C \times V^2$ で求めることができる。ここで、 $C$ は配線容量、 $V$ は電源電圧、 $f$ は配線のトグル率(1秒間に信号が変化する回数)である。

#### 【0034】

従来は、消費電力を算出する場合、実際に配線を配置してから計算されていた。そのため、消費電力が求められるまでに時間がかかり、消費電力の問題を発見するまでに時間を要するために設計工期自体が長くなる問題があった。また、配線を配置することなくWire L

10

20

20

30

40

50

oad Modelを用いて総配線長から消費電力を算出する方法もあるが、この方法では、ネットリストの固有の特徴を考慮することができないために、精度が悪くなる問題があった。しかし、本実施の形態では、実際に配線を行う前の概略配線から消費電力を求めることができるために、設計工期を短縮することができる。また、本実施の形態では、総配線長から消費電力を算出するのではなく、各ネットの配線に基づいて消費電力を算出するためネット固有の特徴を考慮することができ、精度良く算出することができる。

#### 【0035】

以上のように、本実施の形態では各ネット配線長  $L_n$  を求めてから総配線長  $L$  を求めるので、総配線長から求められた消費電力に比べ消費電力を精度良く算出できる。なお、本実施の形態では、各ネットに対する所定の係数  $n$  を求めるために概略配置を行うが、この概略配置は、適当なサイズのレイアウト領域に対して実施すれば良く、従来のように測定対象となるサイズのレイアウト領域に対して実施す必要がない。そのため、レイアウト領域のサイズが確定していない設計初期段階から、本実施の形態の方法を用いることができ、正確な消費電力を見積もることができる。

#### 【0036】

##### (実施の形態4)

本実施の形態でも、実施の形態3同様、各ネット配線長  $L_n$  に基づいて遅延時間を求める方法を配線解析方法に追加することができる。図5に、本実施の形態に係る集積回路の遅延時間を求め方法のフロー図を示す。

#### 【0037】

図5では、図4と同じステップについては同一の符号を付している。ステップ6～ステップ8までは、実施の形態3と同じであるため詳細な説明は省略する。本実施の形態では、ステップ8で求められた配線抵抗と配線容量に基づいて集積回路の遅延時間を求める(ステップ10)。例えば、セルの遅延時間  $T_c$  及び配線の遅延時間  $T_w$  は、以下のようにして求めることができます。セルの遅延時間  $T_c$  は、セル固有の遅延時間  $K_1$  とセル出力の駆動能力  $K_2$  に配線容量  $C$  を掛けた値との和で求められる。つまり、 $T_c = K_1 + K_2 \times C$  となる。なお、セル固有の遅延時間  $K_1$  及びセル出力の駆動能力  $K_2$  は、予めテーブルに記憶しておく。配線の遅延時間  $T_w$  は、配線容量  $C$  に配線抵抗値  $R$  で求められる。つまり、 $T_w = R \times C$  となる。

#### 【0038】

以上のように、本実施の形態では各ネット配線長  $L_n$  に基づいた遅延時間を算出できるので、ネットリストを反映することができ、総配線長から求められた遅延時間に比べ測定精度を向上させることができます。なお、本実施の形態でも、概略配置は、適当なサイズのレイアウト領域に対して実施すれば良く、従来のように測定対象となるサイズのレイアウト領域に対して実施す必要がない。そのため、レイアウト領域のサイズが確定していない設計初期段階から、本実施の形態の方法を用いることができ、正確な遅延時間を見積もることができます。

#### 【0039】

##### (実施の形態5)

本実施の形態でも、実施の形態3同様、各ネット配線長  $L_n$  に基づいてCustom Wire Load Modelに用いられるネットのファンアウト数及び配線容量の対応を示すテーブル(以下、単にCWL Mともいう)を作成する方法を配線解析方法に追加することができる。図6に、本実施の形態に係る集積回路のCWL Mを作成する方法のフロー図を示す。

#### 【0040】

図6では、図4と同じステップについては同一の符号を付している。ステップ6～ステップ8までは、実施の形態3と同じであるため詳細な説明は省略する。本実施の形態では、ステップ8で求められた配線抵抗と配線容量に基づいて集積回路のCWL Mを作成する(ステップ11)。

#### 【0041】

ステップ11では、従来より知られているいくつかの計算方法を用いることができる。

10

20

30

40

50

例えば、ファンアウト数Nのネットにおける配線容量を、集積回路中のファンアウト数Nに対する全てのネットにおける配線容量を平均した値として求め、テーブルを作成する方法がある。

#### 【0042】

以上のように、本実施の形態では各ネット配線長 $L_n$ に基づいたCWL Mを作成できるので、ネットリストを反映することができ、総配線長から作成されたCWL Mに比べ測定精度を向上させることができる。なお、本実施の形態でも、概略配置は、適当なサイズのレイアウト領域に対して実施すれば良く、従来のように測定対象となるサイズのレイアウト領域に対して実施す必要がない。そのため、レイアウト領域のサイズが確定していない設計初期段階から、本実施の形態の方法を用いることができ、正確なCWL Mを作成することができる。10

#### 【0043】

##### (実施の形態6)

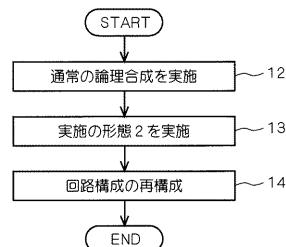

本実施の形態では、実施の形態2で説明した階層モジュールの全体回路の配線困難指數と、階層モジュールにおける上層回路の配線困難指數とを利用して、集積回路のネットリストを生成する論理合成方法である。図7に、本実施の形態に係る集積回路の論理合成方法のフロー図を示す。

#### 【0044】

図7に示すフロー図では、まず、ステップ12において、通常行われている論理合成方法によってネットリストを生成する。通常行われている論理合成方法とは、タイミング制約違反と回路のセル面積のみを考慮して論理合成である。なお、本実施の形態では、例えばRegister Transfer Level(RTL)の回路記述からネットリストを論理合成する。ここで、RTLの回路記述とは、レジスタ及びレジスタ間を組み合わせ回路により結び付けてデータ転送経路を明確にした回路記述である。20

#### 【0045】

ステップ12により得られたネットリストに対して、実施の形態2で説明した方法を用いて、階層モジュールの全体回路の配線困難指數と階層モジュールにおける上層回路の配線困難指數とを算出する(ステップ13)。

#### 【0046】

ステップ13で求めた配線困難指數が所定の値より大きい階層モジュールの場合、階層モジュールの回路構成を再構成し、再度論理合成を行ってネットリストを生成する(ステップ14)。ここで、所定の値とは、例えば集積回路の製造条件から制限される配線困難指數の上限値が考えられる。30

#### 【0047】

ステップ14において、階層モジュールの回路構成を再構成する方法としては、いろいろ考えることができる。例えば、回路中の特定の機能(例えば、加算や乗算)を実現する回路構成を予め複数用意しておき、配線困難指數が所定の値より大きい階層モジュールの回路に対して予め用意した回路と置き換える方法がある。この方法においては、予め用意した回路構成のそれについて、実施の形態1で説明した配線困難指數を求めておくことで、再構成後のネットリストの配線困難指數が小さくなる回路構成を即座に選択することができる。40

#### 【0048】

従来の論理合成方法では、タイミング制約違反と回路のセル面積のみを考慮して論理合成を行っていた。そのため、従来の論理合成方法により生成されたネットリストは、配線の混雑した回路を含むネットリストとなる場合があり、配置配線時に配線がショートするなどの問題が発生していた。そこで、本実施の形態の論理合成方法のように、従来の論理合成方法を行った後に、配線困難指數を算出し所定の値より大きければ回路構成を変更する工程を追加することで上記の問題を解決している。

#### 【0049】

以上のように、本実施の形態では、配線困難指數を算出し所定の値より大きければ回路50

構成を変更する工程を追加しているので、配線混雑を防止することができる論理合成方法とすることができます。また、本実施の形態では、配線困難指標が所定の値より大きい階層モジュールに対して回路構成の再構成を行うので、局所的に発生する配線混雑をネットリストを生成する段階で防止することができる。特にレイアウト領域の面積と配線層が限定されるような設計の場合は、配線が混雑した部分には配線ができなくなる可能性が高いため、ネットリスト生成段階で、一定の基準以下の配線困難指標となる回路構成が可能となる本実施の形態に係る方法は有効である。

#### 【0050】

##### (実施の形態7)

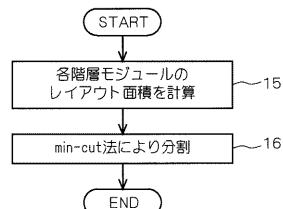

本実施の形態では、実施の形態1の方法により求めたレイアウト面積に基づいてネットリストを修正し、複数の部分回路に分割する方法である。図8に、本実施の形態に係る集積回路の回路分割方法のフロー図を示す。

#### 【0051】

図8に示すフロー図では、まず、ステップ15において、以下に示す方法を用いて階層モジュール毎にレイアウト面積を求める。

#### 【0052】

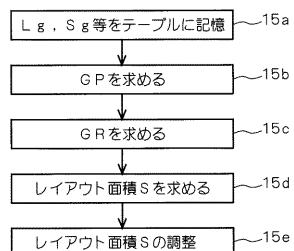

階層モジュールのレイアウト面積Sを求める方法として、図9のフロー図に示す方法がある。図9のフロー図では、まず、階層モジュールに配置されるセルが格子を占有する数を示すセル格子使用数と、階層モジュールに配置される配線の単位長あたりの格子数Lgと、単位面積あたりの格子数Sgと、レイアウト領域の占有する格子数に対してセル及び配線が占有する格子数の割合を示す格子使用率GUとをテーブルに記憶する(ステップ15a)。

#### 【0053】

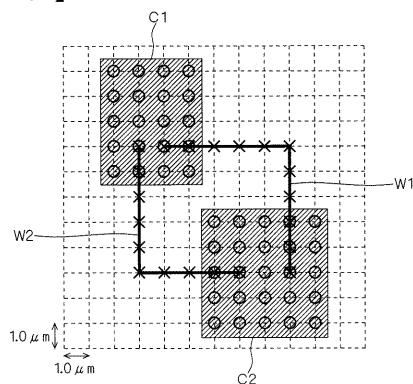

具体的に説明するために、図10に集積回路の回路図を示す。図10では、セルC1のセル格子使用数は20、セルC2のセル格子使用数は25である。そして、図10では、配線の単位長(1.0μm)あたりの格子数Lg=1.0、単位面積(1.0μm×1.0μm)あたりの格子数Sg=1.0である。さらに、図10では、格子使用率GUを0.458とする。

#### 【0054】

図9のフロー図では、次に、ネットリストにおけるセルの一覧とテーブルに基づくセル格子使用数とから、セルが使用する格子数の合計GPを求める(ステップ15b)。図10の例では、セルの一覧としてセルC1及びセルC2が存在し、それぞれのセル格子使用数は、ステップ15aに示したテーブルから20及び25となる。そのため、GPは、 $20 + 25 = 45$ と求めることができる。

#### 【0055】

図9のフロー図では、次に、ネットリストにおける配線の接続情報とテーブルに基づく格子数Lgとから、配線が使用する格子数の合計GRを求める(ステップ15c)。図10の例では、配線の接続情報として、配線W1の長さが11μm、配線W2の長さが10μmである。そのため、GRは、配線W1及び配線W2の長さに配線の単位長あたりの格子数Lg=1.0を掛けることで求まる。つまり、 $GR = (11 + 10) \times 1.0 = 21$ と求めることができる。

#### 【0056】

図9のフロー図では、次に、単位面積あたりの格子数Sg及び格子使用率GU並びに格子数の合計GP、GRから、レイアウト面積Sを $(GP + GR) / GU / Sg$ として求める(ステップ15d)。図10の例では、レイアウト面積Sは、 $S = (45 + 21) / 0.458 / 1.0 = 約 14.4 (\mu m^2)$ となる。

#### 【0057】

さらに、本実施の形態では、各階層モジュールにおいて、当該階層モジュールの下層に位置する複数の階層モジュールのレイアウト面積Sを合計した面積が当該階層モジュールのレイアウト面積Sとなるように、下層に位置する複数の階層モジュールのレイアウト面

10

20

30

40

50

積 S を一律の割合で変更し調整する（ステップ 15 e）。

【0058】

例えば、ある階層モジュールのレイアウト面積が  $100 \mu\text{m}^2$  で、当該階層モジュールの下層に位置する複数の階層モジュールのレイアウト面積が  $45 \mu\text{m}^2$ ,  $75 \mu\text{m}^2$  である場合、下層に位置する複数の階層モジュールのレイアウト面積の単純合計は  $120 \mu\text{m}^2$  となる。単純合計のレイアウト面積と、ある階層モジュールのレイアウト面積とが異なるので、下層に位置する複数の階層モジュールのレイアウト面積を一律の割合で削減する。上記の場合、下層に位置する複数の階層モジュールのレイアウト面積は、 $45 \times 100 / 120 = 37.5 \mu\text{m}^2$ ,  $75 \times 100 / 120 = 62.5 \mu\text{m}^2$  と変更する。

【0059】

次に、ステップ 15において変更されたレイアウト面積の集積回路（ネットリスト）を、複数の部分回路に分割する処理を行う（ステップ 16）。部分回路に分割する処理方法としては、例えば min-cut 法がある。ここで、min-cut 法とは、分割後の部分回路間を接続するネットがなるべく少なくなるように、且つ、各部分回路のサイズが指定した許容範囲内になるように分割する方法である。なお、本実施の形態では、従来のようにセル面積に基づくのではなく、ステップ 15において求められ変更されたレイアウト面積に基づいて min-cut 法が用いられる。

【0060】

従来ではセル面積に基づいて min-cut 法を用いていた。この方法では、分割されてできた各部分回路のセル面積は指定された許容範囲内になることが保証されるが、その部分回路の配線の占める面積も考慮したレイアウト面積は前記セル面積と必ずしも一致しないので許容範囲内にならない場合があり、再度分割処理を行ったりレイアウトの修正等の処理を行う必要があった。そこで、本実施の形態では、レイアウト面積に基づいて min-cut 法を用いている。これにより、配線等を考慮したレイアウト面積に基づいて分割するので、上記の問題が解消される。

【0061】

以上のように、本実施の形態では、下層に位置する複数の階層モジュールのレイアウト面積を変更した後に、レイアウト面積に基づいて複数の部分回路に分割する処理を行うので、従来のセル面積に基づく分割処理に比べて、再度分割処理等を行う必要が軽減される。

【0062】

（実施の形態 8）

集積回路は、通常複数の機能ブロックによって構成されている。これらの機能ブロックのうち、RAM 等の汎用性の高い機能ブロックは、様々なアプリケーションに用いることができるよう機能ブロック単位でライブラリ化される。このようにライブラリ化された機能ブロックを以下ではハードマクロセルという。本実施の形態では、このハードマクロセルと標準セル（実施の形態 1 等で説明したセル）の両方を含むネットリストに対する配線解析方法を示す。

【0063】

以下の説明では、ハードマクロセルと標準セルの両方を含むネットリストから総配線長 L を計算する方法について説明する。なお、総配線長 L を求めることができれば、実施の形態 1 乃至実施の形態 5 で説明した配線解析方法を適用することができる。

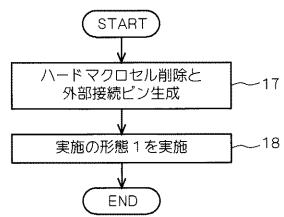

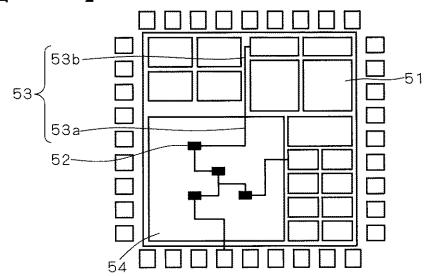

【0064】

図 11 に示すフロー図では、まず、ステップ 17において、ネットリストからハードマクロセルを削除し、標準セルのみのネットリストにする。なお、標準セルのみのネットリストとハードマクロセルとの接合部分については、外部接続ピンに置き換える処理を行う。図 12 に、ハードマクロセルと標準セルの両方を含む集積回路を配置配線した結果を示す。図 12 では、ハードマクロセル 51, 標準セル 52 及びこれらを繋ぐ配線 53 で構成されている。図 12 では、標準セル 52 が設けられている領域を標準セル配置領域 54 としている。そして、標準セル配置領域 54 内の配線 53 を標準セル内配線 53a とし、そ

10

20

30

40

50

れ以外の配線 5 3 をハードマクロ間配線 5 3 b としている。

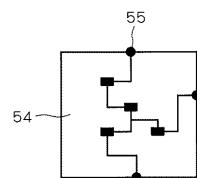

#### 【0065】

ステップ 17 では、図 12 に示す集積回路のネットリストからハードマクロセル 5 1 を削除し、標準セルのみにする。図 13 に、標準セルのみの回路を長方形領域に配置配線した結果を示す。図 13 では、図 12 でハードマクロに接続していた配線 5 3 が、あらたに設けられた外部接続ピン 5 5 に接続するように修正されている。

#### 【0066】

上記のように、ハードマクロセルと標準セルの両方を含むネットリストから総配線長 L を計算する場合、ハードマクロセルを削除し、標準セルのみの領域について総配線長 L を測定するのは、一般的にハードマクロ間では配線混雑が発生しない場合が多く、発生してもハードマクロセルの配置位置を変更することで容易に解消できるためである。10

#### 【0067】

次に、ステップ 18 では、ステップ 17 において求めた標準セル配置領域 5 4 に対して、実施の形態 1 で説明した方法を用いて、標準セル配置領域 5 4 内の総配線長 L を求める。本実施の形態に係る方法で総配線長 L を求めると、標準セル配置領域 5 4 内の配線 5 3 は外部接続ピン 5 4 までの配線 5 3 a のみの総配線長となる。そのため、求める総配線長からハードマクロ間配線 5 3 b を排除することができる。なお、本実施の形態では、ステップ 17 において求めた標準セル配置領域 5 4 に対して、実施の形態 1 で説明した配線解析方法を用いたが、本発明はこれに限られず、他の配線解析方法を適用しても良い。20

#### 【0068】

以上のように本実施の形態では、ネットリストからハードマクロセルを削除し、ハードマクロセルと接続していた部分を外部接続ピンとするので、実施の形態 1 乃至実施の形態 5 で説明した方法（配線困難指数、消費電力、遅延時間、CWL M）を含む配線解析が適用でき、ハードマクロセルと標準セルの両方を含むネットリスト対しても、同様の配線解析をより簡単に行うことができる。

#### 【0069】

なお、集積回路全体として消費電力、遅延時間、CWL M を求める場合は、ハードマクロセル領域について別途求めて、上記結果と一緒にする必要がある。従来では、ハードマクロセルと標準セルの両方を含む集積回路であっても回路全体に対して同じ方法を用いて消費電力、遅延時間、CWL M を求めていた。しかし、ハードマクロセル領域については、標準セル配置領域 5 4 とは異なり、消費電力、遅延時間、CWL M の値がハードマクロセルの配置結果に大きく依存する。そのため、ハードマクロセル領域と標準セル配置領域 5 4 とは異なる方法で別々に計算する方が精度良く計算することができる。そこで、本実施の形態では、標準セル配置領域 5 4 に実施の形態 1 乃至実施の形態 5 を適用する部分について説明している。30

#### 【0070】

また、ステップ 17 において求めた標準セル配置領域 5 4 に対して、実施の形態 1 の図 9 で示した方法を用いて、標準セル配置領域 5 4 のレイアウト面積を求めることができる。なお、ハードマクロセル領域のレイアウト面積は、配線混雑よりも電源配線等の他の要因により決まるため、標準セル配置領域 5 4 とは異なる方法で別途求める方が精度良く求めることができる。40

#### 【0071】

ハードマクロセルと標準セルの両方を含む集積回路は、上記方法で求めた標準セル配置領域 5 4 のレイアウト面積と、別の方で求めたハードマクロセル領域のレイアウト面積とを合計した面積を当該集積回路のレイアウト面積とする。そして、実施の形態 7 で説明した回路分割方法を、このレイアウト面積に対して適用することで、ハードマクロセルと標準セルの両方を含む集積回路にも適用できる。

#### 【0072】

（実施の形態 9）

上記の実施の形態では、問題なく生成されたネットリストに対して行われる配線解析方50

法等を示したものである。しかし、生成されるネットリストが常に問題がないとは限られず、一部の階層モジュールについてネットリストが不完全であったり、欠落していたりするような不備のあるネットリストが生成される場合がある。そこで、本実施の形態では、不備のあるネットリストに対して行う配線解析方法について説明する。

#### 【0073】

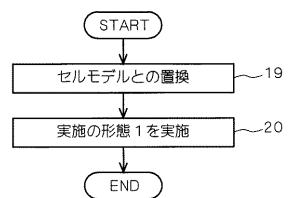

図14に、本実施の形態に係る集積回路の配線解析方法のフロー図を示す。図14に示すフロー図では、まず、ステップ19において、不備の部分を有する階層モジュールを所定のセルモデルに置換する。ここで、所定のセルモデルは、与えられたセル面積を有する正方形の形状で、且つ当該領域の全ての配線層において配線を通過禁止としたセルモデルである。

10

#### 【0074】

次に、ステップ20では、不備の部分を有する階層モジュールを所定のセルモデルに置換した後のネットセルに対して、実施の形態1で説明した配線解析方法を適用して、配線困難指數を算出する。

#### 【0075】

以上のように、本実施の形態では、不備の部分を有する階層モジュールを所定のセルモデルに置換するので、不備のあるネットリストに対しても、実施の形態1で説明した配線解析方法を適用することができる。

#### 【0076】

また、不備の部分を有する階層モジュールを所定のセルモデルに置換したネットリストに対して、実施の形態2乃至実施の形態7の方法を適用することができる。

20

#### 【図面の簡単な説明】

#### 【0077】

【図1】本発明の実施の形態1に係る集積回路の配線解析方法を示すフロー図である。

【図2】本発明の実施の形態2に係る集積回路の配線解析方法を示すフロー図である。

【図3】本発明の実施の形態2に係る集積回路の配線解析結果を示す図である。

【図4】本発明の実施の形態3に係る集積回路の配線解析方法を示すフロー図である。

【図5】本発明の実施の形態4に係る集積回路の配線解析方法を示すフロー図である。

【図6】本発明の実施の形態5に係る集積回路の配線解析方法を示すフロー図である。

【図7】本発明の実施の形態6に係る集積回路の論理合成方法を示すフロー図である。

30

【図8】本発明の実施の形態7に係る集積回路の回路分割方法を示すフロー図である。

【図9】本発明の実施の形態7に係る集積回路のレイアウト面積を求める方法を示すフロー図である。

【図10】本発明の実施の形態7に係る集積回路の回路図である。

【図11】本発明の実施の形態8に係る集積回路の配線解析方法を示すフロー図である。

【図12】本発明の実施の形態8に係る集積回路を配置配線した結果を示す図である。

【図13】本発明の実施の形態8に係る集積回路を配置配線した結果を示す図である。

【図14】本発明の実施の形態9に係る集積回路の配線解析方法を示すフロー図である。

#### 【符号の説明】

#### 【0078】

51 ハードマクロセル、52 標準セル、53 配線、54 標準セル配置領域、55 外部接続ピン。

40

【図1】

【図2】

【図3】

| cellarea Beta modulation |     |

|--------------------------|-----|

| 2904321                  | 2.1 |

| 16635                    | 1.0 |

| 13646                    | 0.7 |

| 11631                    | 1.0 |

| 2807239                  | 2.2 |

| 35445                    | 0.6 |

| 15177                    | 0.7 |

| 1290130                  | 2.5 |

| 1212208                  | 2.5 |

| 1212208                  | 2.5 |

| 727471                   | 2.0 |

| 136929                   | 1.9 |

| 94826                    | 1.1 |

| 366544                   | 4.3 |

| 20806                    | 0.6 |

| 25494                    | 1.2 |

| 21170                    | 1.3 |

| 26511                    | 1.2 |

～top module

|-BCBLK

|-BBBLK

|-BDBLK

|-BEBLK

|-BE\_a

|-BE\_b

|-BE\_c

|-BE\_c1

|-BE\_c1\_a

|-BE\_c1\_aa

|-BE\_c1\_aaa

|-BE\_c1\_ab

|-BE\_c1\_ac

|-BE\_c1\_ad

|-BE\_c2

|-BE\_c2\_a

|-BE\_c3

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 井上 善雄

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5B046 AA08 BA06

5F064 DD13 EE08 EE42 EE43 EE47 HH06 HH09 HH10